# Electrical characterization of high k-dielectrics for 4H-SiC MIS devices

Downloaded from: https://research.chalmers.se, 2019-08-13 09:39 UTC

Citation for the original published paper (version of record):

Khosa, R., Chen, J., Winters, M. et al (2019) Electrical characterization of high k-dielectrics for 4H-SiC MIS devices Materials Science in Semiconductor Processing, 98: 55-58 http://dx.doi.org/10.1016/j.mssp.2019.03.025

N.B. When citing this work, cite the original published paper.

research.chalmers.se offers the possibility of retrieving research publications produced at Chalmers University of Technology. It covers all kind of research output: articles, dissertations, conference papers, reports etc. since 2004. research.chalmers.se is administrated and maintained by Chalmers Library

Contents lists available at ScienceDirect

Materials Science in Semiconductor Processing

journal homepage: www.elsevier.com/locate/mssp

## Electrical characterization of high k-dielectrics for 4H-SiC MIS devices

R.Y. Khosa<sup>a,b,\*</sup>, J.T. Chen<sup>c</sup>, M. Winters<sup>d</sup>, K. Pálsson<sup>a</sup>, R. Karhu<sup>c</sup>, J. Hassan<sup>c</sup>, N. Rorsman<sup>d</sup>, E.Ö. Sveinbjörnsson<sup>a,c</sup>

<sup>a</sup> Science Institute, University of Iceland, Iceland

<sup>b</sup> Department of Physics, University of Education Lahore, Dera Ghazi Khan Campus, 32200, Dera Ghazi Khan, Pakistan

<sup>c</sup> Department of Physics, Chemistry and Biology (IFM), Semiconductor Materials Division, Linköping University, SE-58183, Linköping, Sweden

<sup>d</sup> Department of Microtechnology and Nanoscience, Chalmers University of Technology, SE-41296, Göteborg, Sweden

| ARTICLEINFO                                                                                                               | A B S T R A C T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords:<br>Interface traps<br>AIN/4H-SiC interface<br>Al <sub>2</sub> O <sub>3</sub> /4H-SiC interface<br>MIS structure | We report promising results regarding the possible use of AlN or $Al_2O_3$ as a gate dielectric in 4H-SiC MISFETs.<br>The crystalline AlN films are grown by hot wall metal organic chemical vapor deposition (MOCVD) at 1100 °C.<br>The amorphous $Al_2O_3$ films are grown by repeated deposition and subsequent low temperature (200 °C) oxi-<br>dation of thin Al layers using a hot plate. Our investigation shows a very low density of interface traps at the<br>AlN/4H-SiC and the $Al_2O_3/4H$ -SiC interface estimated from capacitance-voltage (CV) analysis of MIS capacitors.<br>Current-voltage (IV) analysis shows that the breakdown electric field across the AlN or $Al_2O_3$ is ~ 3 MV/cm<br>or ~ 5 MV/cm respectively. By depositing an additional SiO <sub>2</sub> layer by plasma enhanced chemical vapor de-<br>position at 300 °C on top of the AlN or $Al_2O_3$ layers, it is possible to increase the breakdown voltage of the MIS<br>capacitors significantly without having pronounced impact on the quality of the AlN/SiC or $Al_2O_3/SiC$ inter-<br>faces. |

#### 1. Introduction

The great potential of 4H-SiC MISFETs for power electronics is hampered by low channel mobility mainly due to high density of interface states at the SiO<sub>2</sub>/SiC interface. The quality of the SiO<sub>2</sub>/SiC interface has been improved by various oxidation and nitridation methods but more reduction in interface traps is needed [1–3]. Beside SiO<sub>2</sub> as a gate dielectric, the use of high-k dielectrics on SiC has also been investigated. AlN and Al<sub>2</sub>O<sub>3</sub> have reasonably large band gap (~ 6.2 eV and ~7 eV respectively) and high dielectric constant. The conduction band offset of AlN or Al<sub>2</sub>O<sub>3</sub> to 4H-SiC of ~ 1.7 eV is expected to be sufficient for n-channel MISFET operation [4–9]. High quality single crystalline AlN can be grown on SiC because of only 1% lattice mismatch to SiC [10]. However, an amorphous Al<sub>2</sub>O<sub>3</sub> is considered to be better than poly-crystalline  $\alpha$ -Al<sub>2</sub>O<sub>3</sub> as a gate dielectric on 4H-SiC because of leakage through grain boundaries [11].

A crystalline AlN grown by molecular beam epitaxy (MBE) has been reported as a gate dielectric for 4H-SiC MISFETs but very low channel mobility ( $< 1 \text{ cm}^2/\text{V}$ ) was obtained because of the leaky structure [12]. The irradiation of atomic nitrogen or HCl gas etching before the growth of AlN has been used to improve the quality of MBE grown AlN films

[13,14]. The growth of AlN layers by MOCVD on 4H- and 6H-SiC has also been reported and a significant density of fixed charge and interface traps is observed in such AlN layers [15,16].

An amorphous Al<sub>2</sub>O<sub>3</sub> grown by atomic layer deposition (ALD) or thermal oxidation of metallic Al has been used as a gate dielectric in graphene field effect transistors with some success [17,18]. The ALD as grown Al<sub>2</sub>O<sub>3</sub> on 4H-SiC typically contains a large number density of negative charges which are reduced after annealing in Ar at 1000 °C but the Al<sub>2</sub>O<sub>3</sub>/SiC interface contains a high density of interface traps after such treatment due to growth of an interfacial  $SiO_x$  (0 < x < 2) layer [19]. To improve the quality of ALD grown Al<sub>2</sub>O<sub>3</sub>, pre-deposition surface cleaning and post deposition annealing has been performed in N2O or N<sub>2</sub> ambient [20,21]. A MOSFET with ALD grown Al<sub>2</sub>O<sub>3</sub>, that was post-annealed in hydrogen at 400 °C, is reported with a field effect mobility of 57  $\text{cm}^2/\text{V}$ . Even though these results are promising, large threshold voltage shifts are observed due to the sensitivity of the  $Al_2O_2$ layers to electron injection [22]. There is another report on a very high peak field effect mobility of 300 cm<sup>2</sup>/V in SiC MOSFETs using Al<sub>2</sub>O<sub>3</sub> made by MOCVD with a thin SiO<sub>2</sub> interfacial layer to the SiC [23]. But, the mobility drops very rapidly with gate voltage and is less than 50 cm<sup>2</sup>/V at moderate gate voltages.

https://doi.org/10.1016/j.mssp.2019.03.025

Received 5 September 2018; Received in revised form 7 February 2019; Accepted 20 March 2019

Available online 28 March 2019

1369-8001/ © 2019 The Authors. Published by Elsevier Ltd. This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/BY-NC-ND/4.0/).

<sup>\*</sup> Corresponding author. Science Institute, University of Iceland, Iceland.

E-mail addresses: ryk2@hi.is (R.Y. Khosa), jrche@ifm.liu.se (J.T. Chen), micwinte@chalmers.se (M. Winters), kjp9@hi.is (K. Pálsson),

robka36@ifm.liu.se (R. Karhu), jawul@ifm.liu.se (J. Hassan), niklas.rorsman@chalmers.se (N. Rorsman), einars@hi.is (E.Ö. Sveinbjörnsson).

In this study, we grow crystalline AlN by hot wall MOCVD and amorphous  $Al_2O_3$  by low temperature oxidation of Al on n-type 4H-SiC. On few selected samples, an additional layer of SiO<sub>2</sub> is deposited on top of the AlN or  $Al_2O_3$  layer by plasma enhanced chemical vapor deposition (PECVD). The interface traps at the AlN/SiC and  $Al_2O_3/SiC$  interfaces are investigated by capacitance voltage (CV) measurements on MIS capacitors. The dielectric breakdown properties are extracted from current voltage (IV) measurements. We find that both the AlN/SiC and the  $Al_2O_3/SiC$  interface contain very low density of interface traps and the use of SiO<sub>2</sub>/AlN or SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> dielectric stack improves the breakdown voltage of the MIS devices.

#### 2. Experimental methods

Two sets of n-type 4H-SiC MIS capacitors were made. One with single crystalline AlN and other with amorphous Al<sub>2</sub>O<sub>3</sub> as a dielectric. The 4H-SiC used in this study have 10 µm thick n-type epitaxial layers with a net doping concentration of  $\sim 1 \times 10^{16}$  cm<sup>-3</sup> grown on 4° offaxis (0001) highly doped ~  $1 \times 10^{18}$  cm<sup>-3</sup> 4H-SiC substrates. A single crystalline 10 nm thick AlN layer was grown on 4H-SiC in a horizontal hot-wall MOCVD reactor at 1100 °C. Ammonia and Al2(CH3)6 were used as a precursor for nitrogen and aluminum respectively. Prior to deposition of AlN, the SiC surface was exposed in H<sub>2</sub> ambient at 1320 °C, in order to obtain a native oxide-free surface. The details of the AlN growth process and structural characterization of the crystalline AlN layers are given in Ref. [24]. The amorphous Al<sub>2</sub>O<sub>3</sub> is grown by depositing few monolayers of pure Al by electron beam evaporation at a rate of  $\sim 0.5$  Å/s and then the sample is baked on a hot plate in room environment at a temperature of 200 °C for 5 min to form Al<sub>2</sub>O<sub>3</sub> layer. This process of deposition and subsequent low temperature oxidation was repeated twelve times resulting in a film thickness of 15 nm as determined by X-ray reflectivity (XRR) and Atomic Force Microscopy. Prior to growth of Al<sub>2</sub>O<sub>3</sub>, the SiC was cleaned with HF in order to remove the native oxide. Further details of the Al<sub>2</sub>O<sub>3</sub> growth process are given in Ref. [25]. An additional layer of SiO<sub>2</sub> with thickness of 40 nm was deposited on selected samples from both sets by PECVD at 300 °C using source gases of nitrous oxide and silane. Reference MIS capacitors with thermal SiO<sub>2</sub> grown in dry oxygen or in N<sub>2</sub>O ambient were also analyzed. Samples with identical reference oxides have previously been used in SiC MOSFETs [26]. The dielectric thickness of all samples was estimated using X-ray reflectivity (XRR) and the crystallinity was investigated with X-ray diffraction (XRD). Our Al<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub> films are amorphous, no crystallization is observed by XRD apart from the AlN samples [24].

Circular MIS capacitors are made using Al as a gate metal and back contact as well. The interface quality is characterized by conventional CV analysis using Agilent E4980A LCR meter. The dielectric breakdown strength of the MIS samples is determined by IV measurements using a Keithley 617 electrometer. CV and IV measurements are performed in vacuum of  $10^{-3}$  mbar in a cryostat.

### 3. Results and discussion

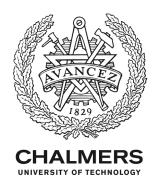

Fig. 1 shows CV spectra of MIS capacitors having AlN and Al<sub>2</sub>O<sub>3</sub> dielectrics measured at room temperature and at frequencies of 1 kHz and 1 MHz. The gate bias is swept from depletion (negative bias) to accumulation (positive bias) and the capacitance signal for both frequencies is recorded simultaneously at each gate bias point. Fig. 1a shows the CV curves for AlN sample. The dielectric constant deduced from the accumulation capacitance is about 8.7. Fig. 1b shows the CV spectra of the Al<sub>2</sub>O<sub>3</sub>. The dielectric constant for Al<sub>2</sub>O<sub>3</sub> is ~ 6.5. The flatband voltage in both AlN and Al<sub>2</sub>O<sub>3</sub> is ~ 0.7 V which is close to the theoretical flatband voltage (i.e. ~ 0.4 V) which shows that initially the AlN and Al<sub>2</sub>O<sub>3</sub> layers contain insignificant amount of fixed charge. A first estimate of the interface trap density is extracted from frequency dispersion of CV curves [27]. In the AlN and Al<sub>2</sub>O<sub>3</sub> case, such dispersion

is hardly visible indicating a low interface state density.

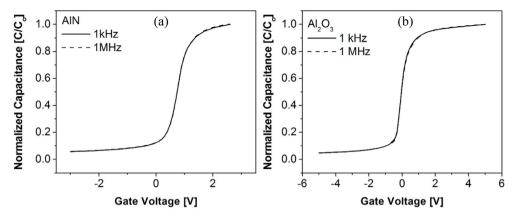

The interface quality of AlN or Al<sub>2</sub>O<sub>3</sub> dielectric with 4H-SiC can be estimated by investigating the frequency dispersion of the CV spectra of an MIS capacitor. Electron capture into interface states is most often a fast process while electron emission from interface traps is normally much slower and is a thermal process which depends on the difference  $E_c$ -E (where E is the energy level of the interface trap and  $E_c$  denotes the SiC conduction band edge). If an electron is captured and not emitted again, this is detected as a shift of the CV curve to higher gate voltages. If the test frequency is high (1 MHz) then more traps will not emit their electrons and the curve is shifted as compared to the low frequency (1 kHz) curve. The extraction of D<sub>it</sub> follows the method of Berglund [27]. The interface trap density  $(D_{it})$  is determined by well-known High-Low-Capacitance method using an equation:  $D_{it} = \frac{1}{q} \left( \frac{C_d C_{lf}}{C_d - C_{lf}} - \frac{C_d C_{hf}}{C_d - C_{hf}} \right).$  Where  $C_d$  is dielectric capacitance,  $C_{lf}$  and  $C_{hf}$  are low and high frequency capacitance respectively.

Fig. 2 shows  $D_{it}$  extracted from room temperature CV dispersion data for MIS samples with AlN or  $Al_2O_3$  as a dielectric as well as reference SiO<sub>2</sub> samples. The single layer AlN and  $Al_2O_3$  samples contain the lowest  $D_{it}$ . The detrimental interface states that exist within this energy range for thermally grown oxides are virtually absent at the AlN/SiC or the  $Al_2O_3$ /SiC interface. It is clear that the addition of a SiO<sub>2</sub> dielectric layer on the top of AlN or  $Al_2O_3$  affects the AlN/SiC and  $Al_2O_3$ /SiC interfaces. However, the single AlN and the SiO<sub>2</sub>/AlN stack both have lower  $D_{it}$  than reference samples. The  $D_{it}$  of the SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> stack is comparable to the reference  $N_2O$  grown SiO<sub>2</sub>.

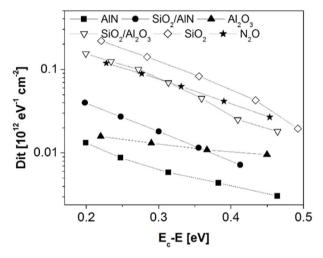

A sensitivity to electron injection is observed in both AlN and  $Al_2O_3$  samples. This is detected as a flatband shift in subsequent 100 kHz CV curves when the samples are repeatedly biased into accumulation. The magnitude of the shift depends on the maximum applied accumulation voltage. An example of such behavior is shown in Fig. 3 for single layer AlN and  $Al_2O_3$  MIS samples. Such behavior is also reported in literature for AlN and  $Al_2O_3$  MIS samples [14,19]. This flatband shift can be a result of trapping of electrons in defects located within the dielectric. Similar electron injection is also observed in the dielectric stacks (not shown here).

However, in this work the process is reversible since the trapped electrons can be released back to the SiC at room temperature by applying depletion bias stress and UV illumination for a certain time to the MIS capacitors [28-30]. An example of such an experiment is shown in Fig. 4 for AlN/SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> stack samples. In the case of the AlN/SiO<sub>2</sub> sample (Fig. 4a), the MIS capacitor is initially kept in accumulation (+11 V) for 30 min at room temperature and then sequentially the bias with 100 kHz frequency is swept to depletion (-10 V)and the CV is recorded seen as the black solid curve. Electrons are intentionally injected into the AlN layer during the bias stress. Next, a UV light is shined on the sample under depletion bias of -10 V for 30 min to examine if electrons are released from AlN traps. A broken black 100 kHz CV curve is recorded directly thereafter. A stretch-out of the CV curve at gate voltage from -5 V to 7 V suggests that electrons are released from traps during UV exposure, but they are recaptured to traps as the gate voltage leads the device to accumulation. The same procedure is applied to the Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> sample with accumulation and depletion bias of +5 V and -5 V respectively (shown in Fig. 4b) and the results are similar to the AlN/SiO<sub>2</sub> sample. This experiment shows that the AlN and Al<sub>2</sub>O<sub>3</sub> layers have traps which capture free electrons during accumulation bias stress and re-emission of the captured electrons is made possible by UV illumination. Applying depletion bias in the same manner but without applying UV light results in a negligible shift of the CV curves (not shown).

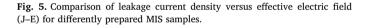

IV measurements are used to estimate the critical breakdown field of the dielectrics. Fig. 5 compares the dielectric breakdown field of the AlN and Al<sub>2</sub>O<sub>3</sub> samples as well as of reference dry SiO<sub>2</sub> sample based on current density measurement as a function of the effective electric field (J-E) across the gate dielectric. A breakdown field of  $\sim 3$  MV/cm (solid

Fig. 1. Room temperature CV curves for (a) AlN and (b) Al<sub>2</sub>O<sub>3</sub> samples at test signal frequencies of 1 kHz and 1 MHz.

Fig. 2. Comparison of the density of interface states  $(D_{it})$  estimated from CV (at 298 K) as a function of energy for AlN and  $Al_2O_3$  based MIS capacitors along with reference SiO<sub>2</sub> MIS capacitors.

curve) or 5 MV/cm (dotted curve) is recorded for the single layer AlN or Al<sub>2</sub>O<sub>3</sub> sample respectively. A sharp current leakage is observed for single layer AlN even at low dielectric electric fields. This suggests the AlN layers have higher density of bulk traps compared to Al<sub>2</sub>O<sub>3</sub> that cause trap assisted leakage across dielectric. The breakdown field of the reference thermal SiO<sub>2</sub> sample is ~ 9 MV/cm (dash double dotted curve). The physical origin of the electron traps within the AlN and Al<sub>2</sub>O<sub>3</sub> layers is unknown. Our postulate is that the AlN layer has either very high density of intrinsic point defects (e.g silicon and oxygen point

defects) or extended defects like dislocations [31]. The  $Al_2O_3$  layer is expected to contain oxygen related intrinsic defects [32]. These defects are presumably the cause of the current leakage through the AlN and  $Al_2O_3$  layers.

The SiO<sub>2</sub>/AlN and SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> stack samples have effective breakdown field, if we consider the dual dielectric as a single dielectric, of ~ 8 MV/cm (dashed curve for SiO<sub>2</sub>/AlN and dash dotted curve for the SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> sample). However, the breakdown electric field across the AlN or Al<sub>2</sub>O<sub>3</sub> layer in the stack is ~ 4 MV/cm or ~ 5.5 MV/cm. Addition of SiO<sub>2</sub> on the top of AlN layer does not significantly improve the breakdown properties of the AlN or Al<sub>2</sub>O<sub>3</sub> but allows the use of higher gate voltages for device operation.

#### 4. Conclusions

CV analysis at room temperature shows that single crystalline AlN and amorphous  $Al_2O_3$  layer have good interface quality in terms of low density of interface states in n-type 4H-SiC MIS capacitors. A significant electron trapping is observed within the AlN or  $Al_2O_3$  when the MIS capacitors are biased into accumulation resulting in a large flatband voltage shift towards higher gate voltages. This can be connected to the relatively low breakdown field (~ 3 MV/cm or ~ 5 MV/cm) of the AlN or  $Al_2O_3$  layers. It is possible to slightly improve the breakdown field of the MIS devices by depositing a SiO<sub>2</sub> layer on top of the AlN or  $Al_2O_3$ . More work is needed in optimizing the growth conditions of the dielectrics and resolving the question of electron trapping within the AlN and  $Al_2O_3$  layers. In summary, the AlN and  $Al_2O_3$  MIS samples show very promising results in terms of interface state densities but electron injection into both layers is currently preventing their practical use.

Fig. 3. Subsequent 100 kHz CV sweeps for single layer (a) AlN and (b) Al<sub>2</sub>O<sub>3</sub> sample at room temperature.

Materials Science in Semiconductor Processing 98 (2019) 55-58

Fig. 4. Electron injection and emission in and out of traps located within (a) the AlN or (b) Al<sub>2</sub>O<sub>3</sub> layer. The black solid 100 kHz CV curves are recorded after which electrons are intentionally injected into the AlN or Al<sub>2</sub>O<sub>3</sub> by accumulation bias stress for certain period. The dotted 100 kHz CV curves are recorded after applying negative bias stress with UV illumination to the samples for 30 min.

- [6] R.D. Vispute, A. Patel, K. Baynes, B. Ming, R.P. Sharma, T. Venkatesan, C.J. Scozzie, A. Lelis, T. Zheleva, K.A. Jones, MRS Online Proc. Libr. 595 (1999) F99W11.3.

- J. Choi, R. Puthenkovilakam, J.P. Chang, Appl. Phys. Lett. 86 (2005) 192101.

6

- [8] V.V. Afanasev, F. Ciobanu, S. Dimitrijev, G. Pensl, A. Stesmans, J. Phys. Condens Matter, 16 (2004) 1839.

- [9] F. Zheng, G. Sun, L. Zheng, S. Liu, B. Liu, L. Dong, L. Wang, W. Zhao, X. Liu, G. Yan, L. Tian, Y. Zeng, J. Appl. Phys. 113 (2013) 044112.

- [10] K. Wongchotigul, N. Chen, D.P. Zhang, X. Tang, M.G. Spencer, Mater. Lett. 26

- [11] C.M. Tanner, Y.-C. Perng, C. Frewin, S. Saddow, J.P. Chang, Appl. Phys. Lett. 91

- [12] M. Horita, M. Noborio, T. Kimoto, J. Suda, IEEE Trans. Electron Dev. 35 (2014) 339. [13] N. Onojima, J. Kaido, J. Suda, T. Kimoto, H. Matsunami, Mater. Sci. Forum 457-460

- [14] N. Onojima, J. Suda, H. Matsunami, Appl. Phys. Lett. 80 (2002) 76.

- C.M. Zetterling, M. Östling, N. Nordell, O. Schön, M. Deschler, Appl. Phys. Lett. 70

- [16] C.M. Zetterling, M. Östling, K. Wongchotigul, M.G. Spencer, X. Tang, C.I. Harris, N. Nordell, S.S. Wong, J. Appl. Phys. 82 (1997) 2990.

- Z. Feng, C. Yu, J. Li, Q. Liu, Z. He, X. Song, J. Wang, S. Cai, Carbon 75 (2014) 249.

- [18] A. Badmaev, Y. Che, Z. Li, C. Wang, C. Zhou, ACS Nano 6 (2012) 3371.

- [19] M. Avice, U. Grossner, I. Pintilie, B.G. Svensson, M. Servidori, R. Nipoti, O. Nilsen, H. Fjellvag, J. Appl. Phys. 102 (2007) 054513.

- [20] S.S. Suvanam, M. Usman, D. Martin, M.G. Yazdi, M. Linnarsson, A. Tempez, M. Götelid, A. Hallén, Appl. Surf. Sci. 433 (2018) 108.

- [21] M. Usman, S.S. Suvanam, M.K. Linnarsson, A. Hallén, Mater. Sci. Semicond. Process. 81 (2018) 118.

- [22] H. Yoshioka, M. Yamazaki, S. Harada, AIP Adv. 6 (2016) 105206.

- [23] T. Hatayama, S. Hino, N. Miura, T. Oomori, E. Tokumitsu, IEEE Trans. Electron Devices 55 (2008) 2041.

- [24] J.T. Chen, J.W. Pomeroy, N. Rorsman, C. Xia, C. Virojanadara, U. Forsberg, M. Kuball, E. Janzén, J. Cryst. Growth 428 (2015) 54.

- [25] R.Y. Khosa, E.B. Thorsteinsson, M. Winters, N. Rorsman, R. Karhu, J. Hassan, E.Ö. Sveinbjörnsson, AIP Adv. 8 (2018) 025304.

- [26] F. Allerstam, G. Gudjonsson, H.Ö. Ólafsson, E.Ö. Sveinbjörnsson, T. Rödle, R. Jos, Semicond. Sci. Technol. 22 (2007) 307.

- [27] E.H. Nicollian, J.R. Brews, MIS (Metal Oxide Semiconductor) Physics and Technology, John Wiley & Sons, New York, USA, 1982.

- [28] J.A. Cooper Jr., Phys. Status Solidi 162 (1997) 305.

- [29] M. Sadeghi, O. Engström, Microelectron. Eng. 36 (1997) 183.

- [30] S. Berberich, P. Godignon, M.L. Locatelli, J. Millán, H.L. Hartnagel, Solid-State Electron. 42 (1998) 915.

- [31] L. Gordon, J.L. Lyons, A. Janotti, C.G. Van de Walle, Phys. Rev. B 89 (2014) 085204.

- L.X. Yu, W.Y. Yu, P.Z. Yang, L.C. Zhan, W. Jia, B. Yun, T.Y. Dan, L.K. An, S.H. Jun, [32] Chin. Phys. B 24 (2015) 087304.

#### Acknowledgements

This work was financially supported by The Icelandic Research Fund. We also acknowledge support from the Swedish Foundation for Strategic Research (SSF), and the Knut and Alice Wallenberg Foundation (KAW).

#### References

- [1] Y. Jia, H. Lv, Q. Song, X. Tang, L. Xiao, L. Wang, G. Tang, Y. Zhang, Appl. Surf. Sci. 397 (2017) 175

- [2] S.R. Kodigala, S. Chattopadhyay, S. Overton, I. Ardoin, B.J. Gordon, D. Johnstone, D. Roy, D. Barone, Appl. Surf. Sci. 330 (2015) 465.

- [3] T. Kimoto, Jpn. J. Appl. Phys. 54 (2015) 040103.

- [4] M. Nawaz, Hindawi Publishing Corporation Active and Passive Electronic Components, (2015), p. 1 (2015).

- [5] M.O. Aboelfotoh, R.S. Kern, S. Tanaka, R.F. Davis, C.I. Harris, Appl. Phys. Lett. 69 (1996) 2873.