Modelling of the shoot-through phenomenon introduced by the next generation IGBT in inverter applications

| 著者                | Abe S., Hasegawa K., Tsukuda M., Wada K.,<br>Omura I., Ninomiya T. |

|-------------------|--------------------------------------------------------------------|

| journal or        | Microelectronics Reliability                                       |

| publication title |                                                                    |

| volume            | 76-77                                                              |

| page range        | 465-469                                                            |

| year              | 2017-07-04                                                         |

| URL               | http://hdl.handle.net/10228/00007279                               |

doi: info:doi/10.1016/j.microrel.2017.06.087

# Modelling of the shoot-through phenomenon introduced by the next generation IGBT in inverter applications

S. Abe<sup>a,\*</sup>, K. Hasegawa<sup>a</sup>, M. Tsukuda<sup>b</sup>, K. Wada<sup>c</sup>, I. Omura<sup>a</sup>, T. Ninomiya<sup>b</sup>

<sup>a</sup> Department of Life Science and System Engineering, Kyushu Institute of Technology, Kitakyushu, Japan <sup>b</sup> Green Electronics Research Institute, Kitakyushu, Japan <sup>c</sup> Department of Electrical and Electronic Engineering, Tokyo Metropolitan University, Tokyo, Japan

#### Abstract

The shoot-through phenomenon has not been fully discussed for high-power inverters with IGBTs. This is because a negative gate voltage is applied to IGBTs during off states. Recently, attention is paid to an improved gate driver with only a positive gate voltage in order to meet demands for simplification, integration, and reduction in power consumption as well as in cost of the gate driver. Moreover, the threshold voltage of the next-generation IGBT will decrease with microfabrication techniques of the gate structure. This will make the shoot-through phenomenon severer and degrade the inverter reliability with the next-generation IGBTs. The influence of the parasitic parameters in both the IGBT and circuit on the shoot-through mechanism has not been investigated so far.

This paper clarifies the shoot-through mechanism and investigates the impact of the next generation IGBTs on the inverter reliability. The influence of the internal capacitance of IGBT including stray inductance on inverter reliability is experimentally confirmed.

#### **Corresponding author.**

s\_abe@life.kyutech.ac.jp Tel: +81 (93) 695 6235 ; Fax: +81 (93) 695 6235

<sup>© 2017.</sup> This manuscript version is made available under the CC-BY-NC-ND 4.0 license http:// creativecommons.org/licenses/by-nc-nd/4.0/

## Modelling of the shoot-through phenomenon introduced by the next generation IGBT in inverter applications

### S. Abe<sup>a,\*</sup>, K. Hasegawa<sup>a</sup>, M. Tsukuda<sup>b</sup>, K. Wada<sup>c</sup>, I. Omura<sup>d</sup>, T. Ninomiya<sup>b</sup>

#### 1. Introduction

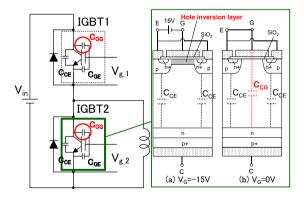

Applications of power semiconductor devices like automotive, power delivery, and industrial motor drive always face a significantly long operating time and high reliability <sup>[1]</sup>. Attentions have been paid to reliability-oriented issues such as failure analysis in open- or short-circuit [2], thermal design of power modules <sup>[3]</sup>, life-time estimation <sup>[4]</sup>, and the so-called shoot-through phenomena <sup>[5-9]</sup>. The gate drivers of present IGBTs in inverters usually provides a negative gate voltage during off intervals to prevent the shoot-through phenomenon. As shown in Fig. 1 (a), the negative gate voltage results in no net reverse transfer capacitance C<sub>CG</sub> because a hole inversion layer is formed between the N-base layer and gate oxide interface, and the reverse transfer capacitance C<sub>CG</sub> is shielded from the gate terminal. Thus, the negative gate voltage not only prevents the shoot-through problem but also improves the reliability of the inverter operation.

On the other hand, in case that the gate voltage is zero during off intervals, a large amount of reverse transfer capacitance exists, and there will be a path of the noise current as shown in Fig. 1 (b). Hence, only a positive gate-driving voltage will suffer from the shoot-through phenomenon. Moreover, attention has been paid to microfabrication techniques for the next-generation IGBT toward CMOS compatible wafer processes <sup>[10]</sup>. This IGBT has a lower threshold voltage when compared with the conventional IGBTs, so that it has higher sensitivity to the high-frequency noise current flowing through C<sub>CG</sub>. Therefore, the shoot-through phenomenon will be severer for the next-generation IGBTs, and a significant reduction of the reliability is concerned by inverters with next generation Si-IGBTs. However, the influence of the parasitic parameters in both the device and circuit on the shoot-through mechanism has not been investigated so far.

This paper clarifies a shoot-through mechanism and investigates the impact of the next generation IGBTs on the inverter reliability. The shoot-through mechanism is obtained from an intensive analysis of a one-leg inverter, considering parasitic circuit parameters including stray inductances and junction capacitances in the IGBT.

#### 2. Mechanism of Shoot-Through Phenomenon

This section discusses the mechanism of the shoot-through phenomenon for a simple one-leg inverter. When a high-frequency noise current occurs in the high-side switch with a high dv/dt, it flows into the reverse transfer capacitance  $C_{CG}$  of the low-side switch, of which the gate voltage varies. This gate noise voltage causes the shoot-through phenomena when the gate noise voltage exceeds the gate threshold voltage of the low-side switch.

Existing models for shoot–through phenomenon consist only of parasitic capacitances of power devices <sup>[1-5]</sup>.

Fig. 1. Shoot-through occurrence for IGBT.

In this case, the peak value of the noise voltage across gate and emitter terminals  $V_{GE}$  peak is given by the following equation<sup>[8]</sup>;

)

$$V_{GE\_peak} = \frac{C_{GC}}{C_{GE} + C_{GC}} V_{in} \qquad (1)$$

In actual inverters, parasitic inductances exist around everywhere on the circuit pattern, so the parasitic inductance may have an influence to the noise voltage.

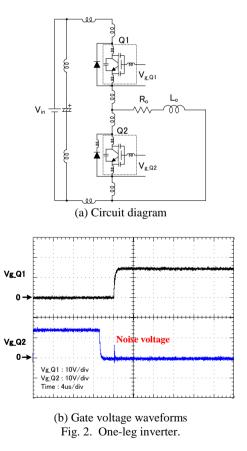

This paper investigates the mechanism of the gate noise voltage including parasitic inductances, and also examines the noise model not only in time domain (waveforms) but also in frequency domain (spectrums). An analytical model is built in order to clarify the shoot-through criterion. Figure 2 shows a one-leg inverter used for analysis and experiment, and the gate voltage waveform of each switch. The noise voltage occurs at the gate terminal of the low-side switch  $Q_2$  as shown in Fig. 2 (b).

#### 3. Shoot-Through Analysis

At first, the following conditions are assumed:

- 1. The switching speed (dv/dt) is enough fast, so that the input source Vin is a step voltage source.

- 2. The load behaves as a current source because the noise voltage happens in a greatly short time interval compared with a period of the inverter output current frequency.

- 3. The low-side switch is completely turned off when the noise voltage occurs, so it consists of a capacitor network.

- 4. A silicon carbide Schottky barrier diode (SiC-SBD) is used for the freewheeling diode, which has no net reverse recovery current. Therefore, the freewheeling diode acts as an ideal switch and its equivalent model after turning off consists only of its junction capacitance.

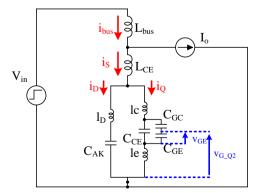

Figure 3 shows an analytical model of the one-leg inverter. The circuit equations are given as follows:

$$\begin{cases} V_{in} = L_{bus} \frac{di_{bus}(t)}{dt} + L_{CE} \frac{d}{dt} (i_D(t) + i_Q(t)) + l_D \frac{di_D(t)}{dt} + \frac{1}{C_{AK}} \int i_D(t) dt \\ l_D \frac{di_D(t)}{dt} + \frac{1}{C_{AK}} \int i_D(t) dt = (l_C + l_E) \frac{di_Q(t)}{dt} + \frac{1}{C_Q} \int i_Q(t) dt \\ i_{bus}(t) = I_o + i_D(t) + i_Q(t) \end{cases}$$

where,

$$C_{\varrho} = \frac{C_{GE}C_{GC}}{C_{GE} + C_{GC}} + C_{CE}$$

(3)

(2)

the initial condition of Eq. (2) is given by,

$$\begin{cases} i_{bus}(0) = I_o \\ i_D(0) = i_Q(0) = 0 \end{cases}$$

(4)

The Laplace transform of Eq. (2) is given by

$$I_{\mathcal{Q}}(s) = L_{bus}\left(sI_{bus}(s) - I_{o}\right) + L_{CE}\left(I_{D}(s) + I_{\mathcal{Q}}(s)\right)$$

(5)

The inverse Laplace transform of Eq(5) gives the current flowing through the low-side switch  $i_Q(t)$  in time domain. as follows:

$$i_{Q}(t) = A_{HF} \sin \omega_{HF} t + A_{LF} \sin \omega_{LF} t$$

(6)

The resonant angular frequency  $\omega_{HF}$  and  $\omega_{LF}$  are given as follows:

$$\omega_{HF} = \sqrt{\frac{h + \sqrt{h^2 - 4g}}{2g}}, \quad \omega_{LF} = \sqrt{\frac{h - \sqrt{h^2 - 4g}}{2g}}$$

(7)

where, h and g are approximately given by the following equations:

$$\begin{cases} h \approx C_{AK} \left( L_{bus} + L_{CE} \right) + C_{Q} \left( L_{bus} + L_{CE} \right) \\ g \approx C_{Q} C_{AK} \left\{ l_{D} \left( L_{bus} + L_{CE} \right) + \left( l_{C} + l_{E} \right) \left( L_{bus} + L_{CE} \right) \right\} \end{cases}$$

(8)

From these results, the resonant angular frequency  $\omega_{HF}$  and  $\omega_{LF}$  are approximated by the following equations:

$$\begin{cases} \omega_{HF} \approx \sqrt{\frac{h}{g}} = \frac{1}{\sqrt{\frac{C_{AK}C_Q}{C_{AK} + C_Q} \cdot (l_D + l_C + l_E)}}} \\ \omega_{LF} \approx \frac{1}{\sqrt{h}} = \frac{1}{\sqrt{(C_{AK} + C_Q) \cdot (L_{bus} + L_{CE})}} \end{cases}$$

(9)

The amplitudes of  $A_{HF}$  and  $A_{LF}$  are given as follows:

$$A_{HF} = \frac{M - K\omega_{HF}^{2}}{\omega_{HF} \left(\omega_{LF}^{2} - \omega_{HF}^{2}\right)}, \quad A_{LF} = \frac{M - K\omega_{LF}^{2}}{\omega_{LF} \left(\omega_{HF}^{2} - \omega_{LF}^{2}\right)}$$

(10)

where,

$$\begin{cases} M \approx \frac{V_{in}}{C_{AK} \left\{ l_D \left( L_{bus} + L_{CE} \right) + \left( l_C + l_E \right) \left( L_{bus} + L_{CE} \right) \right\}} \\ K \approx \frac{l_D V_{in}}{l_D \left( L_{bus} + L_{CE} \right) + \left( l_C + l_E \right) \left( L_{bus} + L_{CE} \right)} \end{cases}$$

(11)

The current flowing through the low-side switch has two frequency components as shown in Eq. (6) -(11). The high-frequency component  $\omega_{HF}$  is generated by the switch loop formed from the lowside switch and its free-wheeling diode, whereas the low-frequency component  $\omega_{LF}$  is generated by the main loop including bus line inductances.

Although the gate noise voltage contains the high-frequency component, the impedance of gate capacitance at the high frequency is significantly small. Therefore, the voltage variation of gate terminal resulting from the high-frequency component can be neglected. Hence, the gate noise voltage can be approximately given by Eq. (12) which includes only low-frequency component.

$$v_{GE}(t) = \frac{C_{GC}}{C_{GC} + C_{GE}} V_{in} \left( 1 - \cos \omega_{LF} t \right)$$

(12)

Moreover, the peak value of the gate noise voltage is given by the following equation:

$$V_{GE_{peak}} = \frac{C_{GC}}{C_{GC} + C_{GE}} 2V_{in}$$

(13)

The gate noise voltage is the product of twice the input voltage  $2V_{in}$  and a division ratio of  $C_{GC}$  and  $C_{GE}$ .

Fig. 3. Analytical model for the shoot-through criterion.

In practice, the inductance between the gate and emitter terminals includes the common emitter inductance for measurement as shown in Fig. 3, so the measurement gate voltage is given as follows:

$v_{G_{-Q2}}(t) = \alpha A_{HF} \cos \omega_{HF} t + \beta A_{LF} \cos \omega_{LF} t$ (14) where,

$$\alpha = \left( l_E \omega_{HF} - \frac{1}{C_{GE} \omega_{HF}} \right), \quad \beta = \left( l_E \omega_{LF} - \frac{1}{C_{GE} \omega_{LF}} \right)$$

(15)

The high-frequency component appears between the gate and emitter terminals even though the actual gate-emitter voltage  $v_{GE}$  has only the low-frequency component as shown in Eq. (12). Hence, the high-frequency component would confuse an observer. Even though the shoot-through phenomenon does not occur, it seems to occur from the measurement waveform.

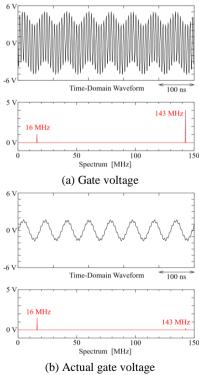

In order to evaluate the mentioned above discussions, a numerical analysis is performed using the circuit parameters as shown in Table 1, which are the same parameters of the experiment described in the next section. Figure 4 shows the time-domain waveforms and its spectrum obtained by the analytical results. The gate noise spectrum of the time-domain waveform, as well as that of the measurement gate-source voltage, has two peaks at 16 MHz and 143 MHz as shown in Fig. 4 (a). The amplitude of the 143 MHz component of the time-domain waveform is around 4.0 V, whereas that of the actual gate-source voltage waveform is around 0.2 V. Moreover, actual gate voltage peak is around 1.7 V as shown in Fig. 4 (b).

#### 4. Experimental Verifications

In order to evaluate the validity of the analytical model, a prototype test board was constructed and tested.

| Table 1 |            |

|---------|------------|

| Circuit | parameters |

| Symbol            | Descriptions                      | Value  |  |

|-------------------|-----------------------------------|--------|--|

| $V_{in}$          | Input voltage                     | 100V   |  |

| $\mathbf{f}_{sw}$ | Switching frequency               | 12kHz  |  |

| Lbus              | Bus line inductance               | 160nH  |  |

| $l_{\rm D}$       | Diode internal inductance         | 10nH   |  |

| $l_{\rm C}$       | Collector internal inductance     | 3nH    |  |

| $l_{\rm E}$       | Emitter internal inductance       | 6nH    |  |

| LCE               | Collector-Emitter line inductance | 30nH   |  |

| Сак               | Diode junction capacitance        | 390pF  |  |

| $C_{GE}$          | Gate-Emitter capacitance          | 4700pF |  |

| CGC               | Gate-Collector capacitance        | 25pF   |  |

| CCE               | Collector-Emitter capacitance     | 55pF   |  |

|                   |                                   |        |  |

To improve the consistency of experimental noise measurement, the test board has been constructed by a printed-circuit board (PCB), the line inductance is calculated by vector potential in theory. Moreover, the capacitances of switching devices are obtained from their date sheet.

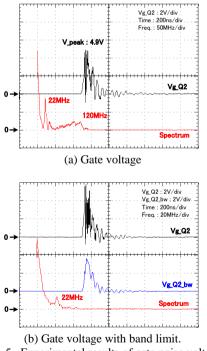

Figure 5 shows the gate voltage waveform and its spectrum of the low-side switch  $Q_2$ . The gate noise voltage contained a high-frequency component of 120 MHz and a low-frequency component of 22 MHz.

Moreover, a band limitation function of the oscilloscope enabled to show almost the same waveforms as the actual gate-emitter voltage  $V_{GE}$  because the high-frequency component caused by the common emitter inductance was almost removed as shown in Fig. 5 (b). This waveform was not exactly the same as actual waveform but would be a reference for the shoot-trough phenomenon. The peak voltage of the band-limitation gate voltage was around 4 V.

The threshold voltage of the IGBT used for the experiment is around 6 V that is obtained from its data sheet. From the analytical result, the gate noise voltage peak is 4.5 V. In this case, the shoot-through phenomenon do not occur.

In order to confirm the shoot-through phenomena, a capacitor was intentionally added between the collector and gate terminals.

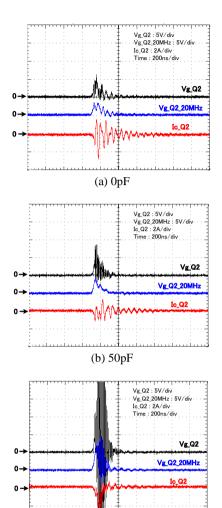

Figure 6 shows the experimental waveforms which confirmed the influence of additional capacitors.

The noise voltage peak without any additional capacitors was around 3.5 V, and that with an additional capacitor of 50 pF was around 4.5 V as shown in Fig. 6 (a) and (b), respectively.

The voltage peak with an additional capacitor of 200 pF was around 9 V, where the noise voltage peak was over the threshold voltage, then the shoot-through phenomena occurred and a short current flowed through the IGBT as shown in Fig. 6 (c).

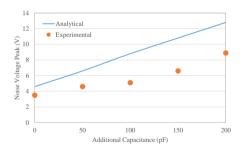

Figure 7 shows the relationship between the gate noise voltage peak and the additional capacitances. When the larger additional capacitor was introduced, the difference between analytical and experimental results became larger. This is because the additional capacitor was connected in parallel between the collector and gate terminals including the collector inductance  $L_{\rm C}$ . The gate noise voltage peak reached the threshold voltage at 150 pF additional capacitor.

Fig. 4. Analytical results of gate noise voltage.

Fig. 5. Experimental results of gate noise voltage

(c) 200pF Fig. 6. Gate voltage waveforms with additional capacitors.

Fig. 7. Gate noise voltage peak with additional capacitors

#### 5. Conclusions

This paper has clarified a shoot-through mechanism. Moreover, the influence of the parasitic inductances on inverter reliability was analytically investigated and examined by a simplified one-leg noise model.

As a result, the validity of the one-leg simplified model has been experimentally confirmed.

#### Acknowledgements

This paper is based on results obtained from a project commissioned by the New Energy and Industrial Technology Development Organization (NEDO)

#### References

- F. Iannuzzoa, M. Ciappac, "Reliability issues in power electronics," Microelectron. Rel., Vol. 58, pp. 1-2, Mar. 2016.

- [2] R. Wu, F. Blaabjerg, H. Wang, M. Liserre, "Overview of catastrophic failures of freewheeling diodes in power electronic circuits," Microelectron. Rel., Vol. 53, no. 9-11, pp. 1788–1792, Sep.-Nov., 2013.

- [3] X. Perpiñà, A. Castellazzi, M. Piton, M. Mermet-Guyennet, J. Millán, "Failure-relevant abnormal events in power inverters considering measured IGBT module temperature inhomogeneities," Microelectron. Rel., Vol. 47, no. 9-11, pp. 1784–1789, Sep.-Nov., 2007.

- [4] N.C. Sintamarean, H. Wang, F. Blaabjerg, P.de P. Rimmen, "A design tool to study the impact of mission-profile on the reliability of SiCbased PV-inverter devices," Microelectron. Rel., Vol. 54, no. 9-10, pp. 1655–1660, Sep./Oct., 2014.

- [5] S. Jahdi, O. Alatise, J. A. O. Gonzalez, R. Bonyadi, L. Ran, and P. Mawby, "Temperature and Switching Rate Dependence of Crosstalk in Si-IGBT and SiC Power Modules," IEEE Trans. Ind. Elecron., vol. 63, no. 2, pp.849-863, Feb. 2016

- [6] Z. Wang, X. Shi, Y. Xue, L. M. Tolbert, F. Wang, and B. J. Blalock, "Design and performance evaluation of overcurrent protection schemes for SiC power mosfets," IEEE Trans. Ind. Electron., vol. 61, no. 10, pp. 5570-5581, Oct. 2014

- [7] K. Murata and K. Harada, "Analysis of a self turn on phenomenon on the synchronous rectifier in a dc dc converter," in Proc. 25th IEEE Int. Telecommun. Energy Conf. (INTELEC), Oct. 2003, pp. 199-204.

- [8] T. Nishiwaki, T. Hara, K. Kaganoi, M. Yokota, Y. Hokomoto, and Y. Kawaguchi, "Design Criteria for Shoot-Through Elimination in Trench Field Plate Power MOSFET," International Symposium on Power Semiconductor Devices & IC's (ISPSD), pp. 382-385, 2014.

- [9] T. Funaki, "Comparative study of self turn-on phenomenon in highvoltage Si and SiC power MOSFETs," IEICE Electronics Express Letter, vol. 10, no. 21. pp. 1-6, 2013.

- [10] M. Tanaka and I. Omura, "IGBT scaling principle toward CMOS compatible wafer processes," Solid-State Electron., vol. 80, pp. 118-123, 2013.