# RADAR

### Research Archive and Digital Asset Repository

Tammam, A, Hayatleh, K, Sebu, C, Lidgey, F, Terzopoulos, N and Ben-Esmael, M

Wide-Bandwidth CFOA with High CMRR Performance

Tammam, A, Hayatleh, K, Sebu, C, Lidgey, F, Terzopoulos, N and Ben-Esmael, M (2013) Wide-Bandwidth CFOA with High CMRR Performance. *AEÜ - International Journal of Electronics and Communications / Archiv für Elektronik und Übertragungstechnik*, 68 (4). pp. 329-335.

doi: 10.1016/j.aeue.2013.09.010

This version is available: https://radar.brookes.ac.uk/radar/items/a7583bdb-a623-441c-a326-15d96e89ff87/1/

Available on RADAR: October 2016

Copyright © and Moral Rights are retained by the author(s) and/ or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This item cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder(s). The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

This document is the post print version of the journal article. Some differences between the published version and this version may remain and you are advised to consult the published version if you wish to cite from it.

## Wide-Bandwidth CFOA with High CMRR Performance

A. A. Tammam, K. Hayatleh, C. Sebu, F. J Lidgey, N. Terzopoulos and M. Ben-Esmael

Oxford Brookes University, Wheatley Campus, Oxford, OX33 1HX, UK <u>khayatleh@brookes.ac.uk</u>

#### Abstract

In this paper the authors analyse the conventional current-feedback operational amplifier (CFOA) in terms of commonmode-rejection ratio (CMRR) performance, and having identified the mechanism primarily responsible for the CMRR, they propose two new architecture CFOAs. These new CFOAs are further developed, and modified to provide improved bandwidth, AC gain accuracy and high CMRR performance. The key features of the two proposed new CFOAs are the designs of the internal voltage followers which have two separate biasing currents with a similar dynamic architecture to that of the conventional CFOA. The magnitude of one bias current determines the value of the maximum CMRR, and the second can be used to maximise bandwidth.

Keywords: (CFOA; CMRR; Bandwidth; Input referred offset voltage; Slew-rate; VOA, DAC/ADC buffers, Medical applications)

#### 1. Introduction

In electronic circuit design, there are many occasions where a general-purpose voltage operational amplifier (VOA) is useful [1]. If the application calls for differential inputs, high input impedance, low output impedance, high common-mode rejection ratio (CMRR), and low input referred offset voltage, the VOA provides a basic topology for achieving these requirements [2]. Unfortunately it has inherent limitations in both the gain-bandwidth trade-off and slew-rate [3]. Typically, the gain-bandwidth product is a constant and the slew-rate is limited to a maximum value determined by input stage bias current. The slew-rate limitations of the VOA are overcome in relatively new architecture op-amps, commonly referred to as the current-feedback op-amp (CFOA) [4], and [5]. CFOAs have been around approximately 30 years, but their popularity has increased only in the last 10 years. CFOAs are receiving increasing attention as basic building blocks in analog system design, and they are now recognized for their excellent performance in high speed and high slew-rate analog signal processing applications [6]. Despite excellent high frequency and high speed performance, CFOAs generally exhibit poorer common-mode rejection (CMRR) properties, compared with their voltage-mode counterpart, which limits their utility [7].

Electronics manufacturers and telecommunications systems engineers are endeavoring to achieve the highest specifications for a voltage follower [8]. The differential pair is inherently good in providing high CMRR. However, applications such as DAC/ADC buffers, high-quality video front-end, RF/IF drivers, ATE pin drivers, video-line drivers, some medical applications and video switchers showed that having high CMRR, and low DC voltage offset was not enough [9], and [10]. The need for a high-slew-rate voltage follower with a high bandwidth, and low settling-time is desirable for such applications [11], and [12]. In this paper the authors analyse the conventional CFOA and identify the main reasons for the poor CMRR performance. These results were used to inform the development of a new architecture design which addresses the shortcomings in terms of CMRR and gain accuracy. The two new voltage followers proposed in this paper maintain both high slew-rate and good CMRR performance.

#### 2. Analysis of differential-mode operation

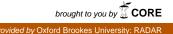

A detailed analysis of the input stage is presented in this section to obtain a clear understanding of the operation of the amplifier and gain insight into ways that the circuit can be modified to improve its performance. A simplified schematic of the standard CFOA architecture is shown in Fig. 1 where the noninverting and inverting nodes are connected to a differential input signal  $V_2$  and  $V_1$  respectively. The positive differential input signals are  $V_2 = +\frac{V_{in}}{2}$  and the negative differential input signal is  $V_1 = -\frac{V_{in}}{2}$ . When the positive signal (V<sub>2</sub>) is applied, the voltage at the base of Q1 will rise, and the voltage at the emitter of Q1 will fall due to the negative signal ( $V_1$ ), increasing  $V_{BE1}$  of  $Q_1$  and resulting in an increase of I<sub>C1</sub>. Similarly, V<sub>BE2</sub> of Q<sub>2</sub> decreases and I<sub>C2</sub> reduces. Under small-signal the collector current I<sub>C1</sub> of Q1 will rise by  $\Delta I$  and, similarly, the collector current  $I_{C2}$  of  $Q_2$  will fall by  $\Delta I$  [13]. Currents I<sub>C1</sub> and I<sub>C2</sub> are then mirrored by CM1 and CM2 to a high impedance gain-node (Z), where they subtract, giving a total signal current  $I_z = 2\Delta I$ , resulting in an output voltage  $V_{out} = 2\Delta I Z_Z$ .

Fig. 1. Simplified schematic of a standard CFOA.

Transistors  $Q_1$  and  $Q_2$  are configured as a class-AB complementary-pair stage. The operating point of these transistors is in the active region and class-AB with the DC current set by the bias network comprising the two diodes  $D_1$  and  $D_2$  and the two current sources,  $I_{BIAS}$ .

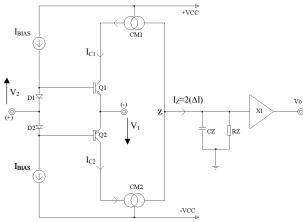

Fig. 2. Small-signal differential-mode half circuit.

Fig. 2 shows the small-signal differential-mode half circuit, which can be analysed to predict the circuit behaviour.  $V_d = V_2 - V_1$ . The output current  $i_{C1} = i_{out(dm)}$  is given by

$$i_{C1} = g_m V_{BE1} + \frac{v_d}{2r_{ce1}}$$

(1)

Since  $V_{BE} \approx v_d$  and  $r_{cel}$  is very large compared with  $1/g_m$ , equation (1) can be reduced to

$$g_{Tdm} \approx \frac{2i_{C1}}{v_d} = 2g_m \approx \frac{2}{r_e} \approx \frac{2I_{CQ}}{V_T}$$

(2)

where  $g_{Tdm}$  is the transconductance of the differential-mode operation,  $g_m$  is the transconductance of one particular transistor at a time in the input class-AB complementary-pair,  $I_{CQ}$  is the dc bias current, and  $V_T$  is the thermal-voltage. Thus the differential-mode gain,  $A_{dm}$ , of the CFOA is approximately

$$A_{dm} = \frac{2i_{C1}Z_Z}{v_d} = g_{Tdm}Z_Z , \qquad (3)$$

where  $Z_z$  is the high impedance of the gain-node of the CFOA.

#### 3. Analysis of common-mode operation

The input stage of the CFOA is the main factor in determining the CMRR performance of the CFOA [9], and [13]. A further study has been made to investigate the parameter that has a direct responsibility towards the common-mode operation, in order to fully understand the inner working of the CFOA, when a common-mode signal is applied to its input. It has been reported that the drawback of the CMRR performance of the CFOA is due to the output impedances of transistors in the input stage [13], [14], and [15]. The currents  $i_1$  and  $i_2$  which flow through the output impedance of Q<sub>1</sub> and Q<sub>2</sub>, respectively, as a direct result of the common-mode input voltage  $V_{cm}$ , are given by

$$i_1 = \frac{V_{cm}}{r_{cel}} \text{ and } i_2 = \frac{V_{cm}}{r_{ce2}}.$$

(4)

These currents are then mirrored to a high impedance gainnode (Z), where they add algebraically. Thus a high commonmode voltage gain is generated, and a low value of the CMRR is produced, normally in the region of 50dB.

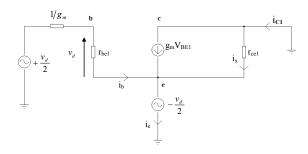

Fig. 3. Circuit schematic of the CFOA with a common-mode input signal,  $V_{cm}$ .

Fig. 3 shows a circuit schematic of the CFOA with a commonmode input signal. Applying a positive common-mode input signal decreases the value of  $V_{CB}$  of  $Q_1$ , and as the Early voltage of this transistor is finite it results in a decrease in the collector current  $I_{C1}$  of  $Q_1$  by an amount  $\Delta I_{CM}$ . Furthermore, the positive common-mode input voltage will cause the value of  $V_{CB}$  of  $Q_2$  to rise and, thus, the collector current  $I_{C2}$  of  $Q_2$  to increase by the same amount [13], and [15].

Hence, when the collector currents of  $Q_1$  and  $Q_2$  are mirrored by CM1 and CM2 to a high impedance gain-node (Z), the net current into the Z-node is

$$I_Z \approx I_{C2} - I_{C1} = (\Delta I_{CM}) - (-\Delta I_{CM}) = 2\Delta I_{CM}$$

(5)

Since  $I_{C1} \approx I_{E1}$  and  $I_{C1} \approx I_{E1}$ , then  $I_{(-)} = I_{C2} - I_{C1}$ , where  $I_{(-)}$  is the inverting node input current. Thus,

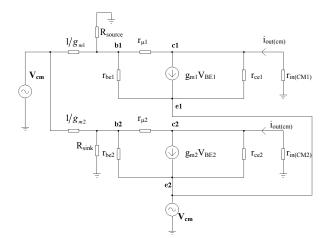

Fig. 4. Small-signal equivalent circuit of the CFOA input stage for common-mode analysis.

$$I_Z \approx I_{(-)} \approx I_{C2} - I_{C1} = 2\Delta I_{CM}$$

(6)

To obtain a better understanding, the class AB bias voltage follower (shown in Fig. 3) was analysed using small-signal modelling.

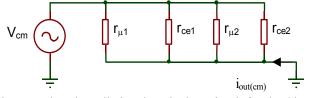

Fig. 4 shows the small-signal equivalent circuit for the input stage of the CFOA driven by an input common-mode voltage signal. Since  $1/g_m$ ,  $r_{in(CM1)}$  and  $r_{in(CM2)}$  are small, and the bases of Q<sub>1</sub> and Q<sub>2</sub> are connected together, there will be negligible signal voltage across the base to emitter terminals of these two input transistors in Fig. 4 when a common-mode input voltage is applied to the circuit. Hence, both  $g_{m1}V_{BE1}$  and  $g_{m2}V_{BE2}$  signal current generators are virtually inactive. The net result is that the circuit in Fig. 4 simplifies to the one shown in Fig. 5, and the output current from the coupled current-mirrors,  $i_{out(cm)}$ , is given by

$$i_{out(cm)} = -2V_{cm} \left[ \frac{I_{Q}}{V_{AN}} + \frac{1}{r_{\mu 1}} + \frac{I_{Q}}{V_{AP}} + \frac{1}{r_{\mu 2}} \right] \approx -2V_{cm} \left[ \frac{I_{Q}}{V_{AN}} + \frac{I_{Q}}{V_{AP}} \right],$$

(7)

where  $V_{AN}$  and  $V_{AP}$  are the Early voltages for  $Q_1$  and  $Q_2$ , respectively.

Since  $r_{\mu 1} \approx r_{\mu 2} \gg r_{ce1} \approx r_{ce2} = r_{ce}$ , the common-mode transconductance,  $g_{T_{CM}}$ , is given by

$$g_{T_{CM}} \approx \frac{i_{out(cm)}}{V_{cm}} = -2 \left[ \frac{I_Q}{V_{AN}} + \frac{I_Q}{V_{AP}} \right].$$

(8)

Thus, the values  $r_{ce}$  of Q<sub>1</sub> and Q<sub>2</sub> directly determine the common mode gain,  $A_{cm}$ . From equation (8),  $(A_{cm}=Vout/V_{cm})$  of the CFOA can be written as

$$A_{cm} = g_{Tcm} Z_Z = \frac{i_{out(cm)} Z_Z}{V_{cm}} .$$

<sup>(9)</sup>

Fig. 5. Reduced small-signal equivalent circuit for the Class AB Bias Voltage Follower.

#### 4. Common-Mode Rejection Ratio (CMRR)

The common-mode rejection ratio (CMRR) is defined as the ratio of the magnitude of the differential gain to the magnitude of the common mode gain [16], and it can be expressed as:

$$CMRR = \left| \frac{A_{dm}}{A_{cm}} \right| \tag{10}$$

where  $A_{dm}$  and  $A_{cm}$  are the differential mode gain and the common mode gain, respectively. Therefore, by substituting equations (3) and (9) into equation (10) we obtain

$$CMRR = \left| \frac{\frac{i_{out(dm)}Z_Z}{V_d}}{\frac{i_{out(cm)}Z_Z}{V_{cm}}} \right| = \left| \frac{\frac{i_{out(dm)}}{V_d}}{\frac{i_{out(cm)}}{V_{cm}}} \right| = \left| \frac{g_{Tdm}}{g_{Tcm}} \right|.$$

(11)

Note that the expression of CMRR in equation (11) is independent of the high impedance gain-node  $Z_z$ . Thus, having a higher, or lower, impedance gain-node  $Z_z$  does not influence the CMRR. Now by substituting the expressions of the transconductance of the differential-mode operation of the CFOA,  $g_{Tdm}$ , given in equation (2), and of the transconductance of the common-mode operation of the CFOA,  $g_{Tcm}$ , given in equation (8), into equation (11) we obtain

$$CMRR = \left| \frac{g_{Tdm}}{g_{Tcm}} \right| = \left| \frac{2I_{Q}}{V_{T}} \frac{1}{2 \left[ \frac{I_{Q}}{V_{AN}} + \frac{I_{Q}}{V_{AP}} \right]} \right| = \left| \frac{I_{Q}}{V_{T} \left[ \frac{I_{Q}}{V_{AN}} + \frac{I_{Q}}{V_{AP}} \right]} \right|.$$

(12)

In the special case where  $V_{AN} = V_{AP} = V_A$ , the expression of CMRR given in equation (12) becomes

$$CMRR = \left| \frac{V_A}{2V_T} \right| \tag{13}$$

4

Table 1 Variations of CMRR,  $A_{dm}$  and  $A_{cm}$  with changing values of  $r_{ce1}$ ,  $r_{ce2}$ ,  $r_{e1}$  and  $r_{e2}$ .

| Increase<br>parameter     | CMRR      | A <sub>dm</sub> | $A_{cm}$  |

|---------------------------|-----------|-----------------|-----------|

| $r_{ce1}$ , and $r_{ce2}$ | Increases | No change       | Decreases |

| $r_{e1}$ , and $r_{e2}$   | Decreases | Decreases       | No change |

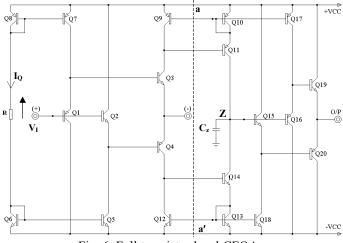

Table 1 shows the variations of CMRR,  $A_{dm}$  and  $A_{cm}$  with changing values of  $r_{ce1}$ ,  $r_{ce2}$ ,  $r_{e1}$  and  $r_{e2}$ . To test this theoretical result the full transistor level CFOA shown in Fig. 6 was simulated using SPICE.

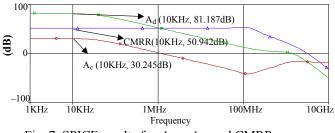

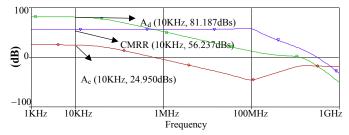

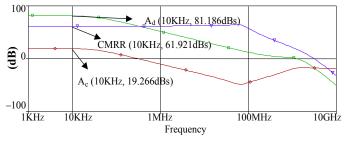

This was undertaken using Analog Devices XFCB device parameters. The variations of CMRR,  $A_{dm}$  and  $A_{cm}$  with changing values of  $r_{ce1}$ ,  $r_{ce2}$ ,  $r_{e1}$  and  $r_{e2}$  are listed in Table 1. The obtained frequency responses of  $A_{dm}$ ,  $A_{cm}$  and CMRR are shown in Fig. 7. The values of the Early voltages  $V_{AP}$  of the PNP devices Q<sub>7</sub> and Q<sub>4</sub>, and  $V_{AN}$  of the NPN device Q<sub>5</sub> and Q<sub>3</sub> were then doubled and the simulation repeated.

These results are shown in Fig. 8. The results presented in Fig. 9 correspond to Early voltages of the input transistors four times greater than the actual AD-XFCB parameters. Although changing the values of V<sub>A</sub> in practice is virtually impossible, as a simulation exercise since  $r_{ce} \approx V_A/I_{CQ}$ , comparison of the results does confirm the anticipated significance of  $r_{ce}$  in determining the CMRR of the CFOA.

Comparing the results in Figs. 7 and 8, the values of  $A_{cm}$  decreased as expected by 6dB, the values of  $A_{dm}$  remained almost unchanged and the CMRR increased by 6dB for each step in doubling of V<sub>A</sub>.

Fig. 6. Full transistor level CFOA.

Fig. 7. SPICE results for  $A_{dm}$ ,  $A_{cm}$  and CMRR versus frequency for Fig. 6 using AD-XCFB process parameters.

Fig. 8.  $A_{dm}$ ,  $A_{cm}$  and CMRR versus frequency, as in Fig. 7, except that  $V_A$  has been doubled for the input stage devices.

Fig. 9.  $A_{dm}$ ,  $A_{cm}$  and CMRR versus frequency, as in Fig. 8 except that  $V_A$  has been quadrupled for the input stage devices.

#### 5. New current feedback operational amplifier

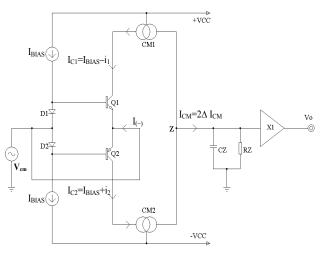

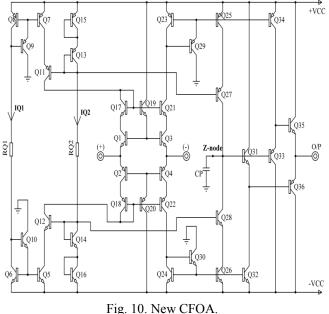

A new CFOA topology is presented in Fig. 10. In theory, the input stage of the CFOA provides an unlimited slew-rate capability. However, in practice the current available to drive the Z-node will always be limited by the biasing currents capabilities in the circuit [17]. But there is trade off relationship between the slew- rate, and the CMRR in the case of the voltage followers. and CFOA [18]. Decreasing the biasing current which is fed to the CFOA circuit seems appropriate since it will minimize the common-mode current flowing through the transistors output resistance of the entire input stage of the CFOA, and hence the common mode will be reduced, which will result in a higher CMRR. Therefore the idea of deploying two biasing currents sources into the CFOA was a step in the right direction of retaining a high bandwidth, and simultaneously increasing CMRR. In addition, to introduce the current-transfer cell that was implemented to cascode the entire input stage, which bleeds for increasing the output impedances of the entire input stage of the CFOA.

Moreover the idea of the new CFOA design is to obtain a good dynamic output range. Transistors  $Q_{19}/Q_{20}$  are to give a good slew-rate, while the bootstrapping transistors  $Q_9/Q_{10}$  are to

maintain a good CMRR. As for the DC voltage offset each pair transistors  $Q_1/Q_3$ ,  $Q_2/Q_4$  operate at the same  $V_{CB}$ ·  $(V_2-V_1)\approx 0$ , and virtually the same bias currents so that the DC voltage offset is predicted to be very small.

#### rig. 10. New CrO.

#### 6. Modified CFOA

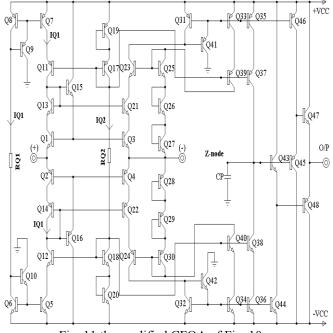

Redesigning the input core a significant improvement will be obtained. This modified circuit of Fig. 10 is shown above in Fig. 11. In this new design the CMRR performance can be further improved, dramatically, by adopting common–mode bootstrapping to the complementary pair transistors  $Q_3/Q_4$ . Adding  $Q_{21}/Q_{23}$  as well as  $Q_{22}/Q_{24}$ , in association with diode-connected transistors  $Q_{25}/Q_{26}/Q_{27}$  and  $Q_{28}/Q_{29}/Q_{30}$ , bootstraps,  $Q_3/Q_4$  by keeping their collector- base voltages virtually constant [19].

Fig. 11 the modified CFOA of Fig. 10.

#### 7. Simulation Results

SPICE was used to verify the operation and performance of the circuit of Fig 10, and Fig. 11. The technology used in the simulation was the complementary bipolar XFCB process from Analog Devices, Santa Clara. The power supply voltages were set to  $\pm 3.8V$ . For comparative assessment three CFOAs were simulated, namely (i) a conventional CFOA shown in Fig. 6, (ii) the new CFOA deploying two current sources shown in Fig. 10 and (iii) the modified CFOA shown in Fig. 11.

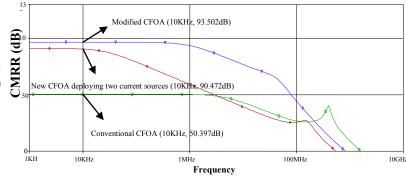

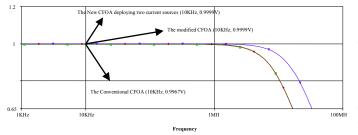

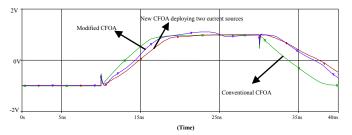

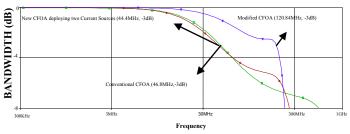

All three CFOA designs were simulated with the same technology parameters, and were set to operate at a bias current equal to 0.14mA. The CMRR simulated results for the conventional CFOA, the modified CFOA and the new CFOA are shown in Fig. 12. Moreover, their individual characteristics are Note that the CMRR is increased to summarized in Table 2. 93.5dB for the modified CFOA and to 90.5dB for the new CFOA while the CMRR for the conventional CFOA remains 50.4dB. Furthermore, the AC gain accuracy has been enhanced for both new CFOAs. Fig. 13 shows the comparisons the graphs of the AC versus frequency for the three CFOAs. With the significant improvements of the bandwidth (see Fig. 17) and CMRR, the modified CFOA shown in Fig. 11 has a superior performance over both the new CFOA deploying two current sources. Moreover, the input referred offset voltage has been reduced for both new CFOAs compared with the conventional design. However, the slew-rate of the conventional amplifier is better than the other two as shown in Fig. 14 as a trade-off. These results are confirmed in Table 2.

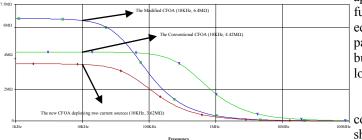

By looking at the simulated non-inverting input impedance in Fig. 15, it is clear that the new CFOA deploying two current sources has the poorest non-input impedance of  $3.6M\Omega$ . The next best is the conventional CFOA with a non-inverting input impedance of  $4.4M\Omega$ . This is about  $2M\Omega$  below the non-inverting input impedance of  $6.4M\Omega$ . Fig. 16 shows the frequency responses of all three CFOAs. The bandwidths of the conventional and the new CFOA deploying two current sources, each configured as a unity closed-loop gain amplifier are almost the same. However, the modified CFOA has the widest bandwidth of all three.

Fig. 12. CMRR~Frequency comparisons

|                                         | Conventional<br>CFOA of Fig. 6 [20], [21] | New CFOA deploying two Current<br>Source of Fig. 10 | Modified CFOA<br>of Fig. 11 |

|-----------------------------------------|-------------------------------------------|-----------------------------------------------------|-----------------------------|

| CMRR                                    | 50.4dB                                    | 90.4dB                                              | 93.5dB                      |

| Bandwidth                               | 46.8MHz                                   | 44.4MHz                                             | 120MHz                      |

| Non-inverting buffer input resistance   | 4.4MΩ                                     | 3.6ΜΩ                                               | 6.4MΩ                       |

| AC gain error (Unity gain, Vin = 1V pp) | 3.4mV                                     | 100µV                                               | 100µV                       |

| Input offset voltage                    | ±12.3mV                                   | ±1.2mV                                              | ±1.4mV                      |

| Slew rates                              | $SR+=300.2V/\mu s$                        | SR+ =229.1V/µs                                      | $SR+=274.5V/\mu s$          |

|                                         | $SR = 260.9V/\mu s$                       | SR- =173.5V/µs                                      | SR-=200.8V/µs               |

Table 2 Characteristics of the conventional and improved CFOAs for  $Vcc = \pm 3.8V$

Fig. 13. AC gain accuracy ~ Frequency comparisons.

Fig. 14. Voltage ~Time comparisons (The Slew Rate).

Fig. 15. Input impedance~frequency for the CFOAs, each configured as a non-inverting unity gain amplifier.

Fig. 16. Bandwidth~ Frequency for unity closed-loop gain comparisons.

#### 9. Conclusion

Two novel CFOA designs have been presented for high accuracy, speed, and CMRR performance. Both new circuits deploy two current sources, one to set the CMRR and the other to set the slew-rate in order to achieve greatly enhanced performance.

The modified CFOA shown in Fig. 11 yields higher noninverting buffer input resistance with the structure that exhibits an acceptably high slew-rate. In comparison with both CFOAs, the modified CFOA is more efficient. Also other characteristic have been improved, such as higher bandwidth and non-inverting input resistance.

In this paper a MOSFET differential amplifier has been considered because of the growing importance of CMOS in analogue circuit design. However, depending on the application, there may be advantages in implementation in a fully bipolar design. In this case, if Q3, Q4 are the bipolar equivalents of M3, M4, then the presence of Q4 not only partially compensates of the collector-base capacitance of Q3 but it also increases the incremental output resistance seen looking into its collector [7].

The addition of only one transistor, plus bias, into a conventional source-coupled differential amplifer has been shown to extend the CMRR bandwidth substantially. This performance improvement is a result of local feedback reducing the source-coupled node capacitance of the differential pair.

This technique is primarily applicable to an integrated circuit realization of the source coupled differential amplifier because closely matched transistors operating at the same temperature are essential for satisfactory operation. Also the technique can be applied to monolithic instrumentation amplifiers (IAs). Initial results applying the technique to IAs are promising and this work will be the subject of a further publication.

#### Acknowledgments

We gratefully acknowledge Analog Devices, Santa Clara, CA for providing device model data for the transistors used in this theoretical discussion. We would also like to thank Dr. Bryan Hart for his useful suggestions and advice.

#### References

- C. Toumazou, F J Lidgey, & D G Haigh, 'Analogue design: the current-mode approach', IEE Circuits and systems series, Peter peregrinus, 1990.

- [2] AH. Madian, SA. Mahmoud, AM. Soliman, 'Configurable analog block based on CFOA and its application', WSEAS Tans Electron 5:220–225, 2008.

- [3] J.G. Graeme, G. E. Tobey, L. P, Huelsman, 'Operational amplifiers design and applications', Burr-Brown Research Corporation, USA, 1971, p.xvii.

- [4] B. Maundy, S. Gift, S. Magierowski, 'Constant bandwidth current feedback amplifier from two operational amplifiers', Int J Electron 94: 605–615, 2007.

- [5] Ananda Mohan PV, 'Comments on avoiding the gain-bandwidth trade off in feedback amplifiers', IEEE Trans Circ Syst-I 58(9): 2114–2116, 2011.

- [6] S. Franco, 'Current-feedback amplifiers benefit high speed designs', EDN, January 5, 1989, pp.161-172.

- [7] A.F. Arbel, and L. Goldminz, 'Output Stage for Current-Mode Feedback Amplifier, Theory and Applications', Analog Integrated Circuits and Signal processing, Vol.2, pp.243-255, 1992.

- [8] E. Bruun, 'High speed, current-conveyor based voltage mode operational amplifier', Electronics Letter, Vol.28, pp.742-744, April 1992.

- [9] K. Hayatleh, A. A. Tammam, And B. L. Hart "Open-Loop Output Characteristics of a Current Feedback Operational Amplifier", International Journal of Electronics and Communications, 12<sup>th</sup> November 2009, Volume 63, pages 1434–1441.

- [10] E. Yuce, S. Minaei, 'A modified CFOA and its applications to simulated inductors, capacitance multipliers, and analog filters', IEEE Trans Circ Syst-I 55(2): 266–275, 2008.

- [11] A. Soliman, 'Applications of the Current Feedback Operational Amplifier', Analog Integrated Circuits and Signal Processing N.11, 1996, pp. 265-302.

- [12] M. Siripruchyanun, C. Chanapromma, P. Silapan, W. Jaikla, 'BiCMOS current-controlled current feedback amplifier (CC–CFA) and its applications', WSEAS Trans Electron 5: 203–219, 2008.

- [13] K. Hayatleh, A. A. Tammam and B. Hart "Novel input stages for current feedback operational amplifiers". Analog Integrated Circuits and Signal Processing, Volume 50, Number 3, March 2007, pp. 163-183.

- [14] N. Terzopoulos, K. Hayatleh, B. L. Hart., F. J. Lidgey., 'A novel bipolar drive circuit for medical applications', Institute of Physics Publishing, Journal of Physiological Measurements, 2005, Vol.26, pp.21-27.

- [15] K. Hayatleh, A. A. Tammam, B. L. Hart, and F. J. Lidgey, 'A novel current-feedback op-amp exploiting bootstrapping techniques', International Journal of Electronics, Vol.94, issue 12, December 2007, pp23-29.

- [16] P. R. Gray, and R. G. Meyer, 1993, Analysis and Design of Analog Integrated Circuits, 3<sup>rd</sup> Edition (New York: Wiley).

- [17] F. J. Lidgey, and K. Hayatleh: 'Are current conveyors finally coming of age', part 2, Electrons and wireless world, in April 2000, Vol. 106, No 1768, pp322- 324.

- [18] D. Smith, etc.: 'Evolution of high-speed op-amp architectures', IEEE J. Solid-State Circuits, Vol.29, No.10, Oct. 1994 pp1166-1179.

- [19] M. A. Vere Hunt, and F. J. Lidgey: 'a high slew-rate voltage-mode opamp', Proc. International Symposium on Circuits and Systems (ISCAS), San Diego, pp.2872-2875.

- [20] S. Franco, "Design with Operational Amplifiers and Analog Ics," Mc Graw Hill, 3<sup>rd</sup> edition, Chapter 6, p. 294, 2002.

- [21] A. Tammam, K. Hayatleh, B. Hart and F. J. Lidgey, "A Hierarchy of Input Stages for Current Feedback Operational Amplifiers". Proceeding of the International Symposium on circuits and systems, Vancouver, British Columbia, Canada, 2004.

**A A Tammam** received his BEng and completed his PhD at the University of Oxford Brookes in September 2000 and December 2005 respectively. Dr. Tammam is member of the IET and has published several papers in international journals and a similar number of conference presentations.

Dr Tammam, is a visiting research fellow in the Analog Circuit Design Research Team at Oxford Brookes University.

His research interests include Analog integrated circuit theory, Analog and Video signal processing, Design and Development of current feedback op-amp, Instrumentation Amplifiers, Analogue circuit design, and transconductance amplifier design for high frequency RF and biomedical application.

**K Hayatleh** (M'2000–SM'2006, CEng, MIET) received his BEng in June 1992 from Oxford Brookes University and subsequent PhD in March 1996 from Oxford Brookes University in collaboration with Imperial College, London.

His research interests are in the area of electronic circuit and system for RF and Biomedical applications. Current projects are in transconductance amplifier design for high frequency RF applications, amplifier linearisation, current feedback op-amp development, RF LNA design, high accuracy voltage buffer and high output impedance current source design and a Low-Voltage High-Speed CMOS Line Driver for SerDes Applications

He has over 80 publications in the above areas of research. Professor Hayatleh is currently the Head of the Electronic Circuit and Systems Design Research Group, and the Postgraduate Research Tutor at Oxford Brookes University, UK.

Cristiana Sebu obtained her bachelor in Theoretical Physics in

2000, followed by a Master degree in Theoretical Physics in 2002 at the University of Bucharest, Romania. She received her PhD in Applied Mathematics in 2004 at Université Montpellier II, France, with a thesis entitled *Problèmes Inverses dans la Physique Classique et Quantique*. Dr Sebu began her academic career in 2004 as a Postdoctoral Research Fellow in Mathematical Sciences at Oxford Brookes University. In 2005, she became a Lecturer in Mathematical Sciences, and since 2006 she has been a Senior Lecturer at Oxford Brookes University.

Dr Sebu's research interests are: Mathematical Modelling, Biomedical Imaging and Instrumentation, Electrical Impedance Tomography, Inverse Problems, Integral Equation Methods for Partial Differential Equations, Theoretical Physics.

Dr Sebu is the lead Mathematician of the research groups in Biomedical Imaging and Instrumentation and Applied Mathematics at Oxford Brookes University.

**F J Lidgey** completed his PhD at the University of Surrey in 1973 and after four years at the University of Newcastle, Australia returned to England in 1978 to join Oxford Brookes University, where he is now Emeritus Professor of Electronics.

His research interests within the Electronic Circuit and Systems Design Research Group and teaching are in the same area of analogue electronics. He has contributed to many novel circuit and system developments that fall under the general heading of current-mode analog design and published over 150 papers in this area.

In 1991 he was joint winner of the IEE's Rayleigh Best Book prize for his contribution to, 'Analog Signal Processing: the current-mode approach', published by Peter Peregrinus Limited. Also he has a long term interest in using computers in education and in recent years has focused on development of computer-based-learning for teaching undergraduate electronics.

**Nikolaos Terzopoulos**, PhD, MBA, MSc, BEng received his MSc and PhD degree Oxford Brookes University, Oxford, UK in 2002 and 2006 respectively. He worked as an Analogue IC Design Engineer at Texas Instruments, UK and he is now a Senior IC designer developing high-speed, low power analog cells for state of the art serial interfaces.

Dr. Terzopoulos is also a Research Fellow at Oxford Brookes University, Oxford, UK being actively involved in several research projects such as: Low Noise Amplifiers (LNA's), Power Amplifiers, High Output Impedance Current Source Circuits and PLL's that publishing the findings of his research activities at world class international journals and conferences.

**Mohamed Ben-Esmael** received both his bachelor degree in Electronic Systems Design in 2009 and his Master degree in Wireless Communication systems in 2010 from Oxford Brookes University.

He is currently working towards a PhD degree in the field of bioelectronics engineering within the Electronic Circuit and Systems Design and the Biomedical Imaging and Instrumentation Reading Group at Oxford Brookes University, UK.

He is a member of Institute of Electrical and Electronics Engineers (IEEE) and Institution of Engineering and Technology (IET). His research interests include bioelectronics circuits and systems, Circuit techniques at high frequencies to achieve high output impedance.