# Purdue University Purdue e-Pubs

Department of Electrical and Computer Engineering Technical Reports Department of Electrical and Computer Engineering

5-1-1991

## Silicon Nitride Deposition, Chromium Corrosion Mechanisms and Source/Drain Parasitic Resistance in Amorphous Silicon Thin Film transistors

Shengwen Luan Purdue University

Gerold W. Neudeck

Purdue University

Follow this and additional works at: https://docs.lib.purdue.edu/ecetr

Luan, Shengwen and Neudeck, Gerold W., "Silicon Nitride Deposition, Chromium Corrosion Mechanisms and Source/Drain Parasitic Resistance in Amorphous Silicon Thin Film transistors" (1991). Department of Electrical and Computer Engineering Technical Reports. Paper 739.

https://docs.lib.purdue.edu/ecetr/739

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

# SILICON NITRIDE DEPOSITION, CHROMIUM CORROSION MECHANISMS AND SOURCE/DRAIN PARASITIC RESISTANCE IN AMORPHOUS SILICON THIN FILM TRANSISTORS

Shengwen Luan Gerold W. Neudeck

May 1991

### TABLE OF CONTENTS

|                                            | Page |

|--------------------------------------------|------|

| LIST OF TABLES                             | vii  |

| LIST OF FIGURES                            | viii |

| ABSTRACT                                   | xiv  |

| CHAPTER 1 - INTRODUCTION                   |      |

| 1.1 Background                             |      |

| 1.2 Thesis Overview                        | 2    |

| CHAPTER 2 - LITERATURE REVIEW              |      |

| 2.1 Introduction                           | 4    |

| 2.2 The Active Semiconductor Layer         |      |

| 2.2.1 Basic Properties of a-Si:H           |      |

| 2.2.2 Deposition of a-Si:H Films           |      |

| 2.2.4 Contacts to a-Si:H                   |      |

| 2.3 The Gate Insulator                     |      |

| 2.4 a-S:H TFT Technologies                 |      |

| 2.4.1 Basic TFT Configurations             | 23   |

| 2.4.2 Novel a-Si:H TFT Technologies        |      |

| 2.5 Characteristics of a-Si:H Thin Film Tr | •    |

| 2.5.1 Introduction                         |      |

| 2.5.2 Physics and Operation                |      |

| 2.6 a-Si:H TFT Applications                |      |

| 2.6.2 Electrical Requirements              |      |

| 2.6.3 a-Si:H TFT Technologies in AMI       |      |

|                                                             | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.7 Problems and Future Developments                        | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.7 Problems and Future Developments                        | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.7.2 Speed Consideration                                   | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.7.3 Stability Consideration                               | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CHAPTER 3 - a-Si:H THIN FILM TRANSISTOR PROCES DEVELOPMENT  | <b>S</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DEVELOFMENT                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.1 Introduction                                            | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

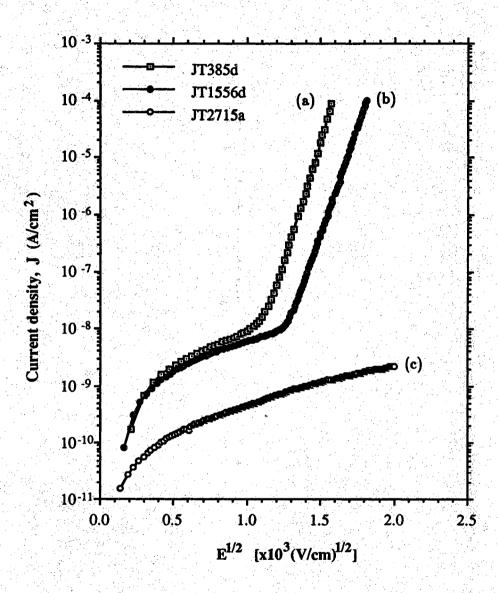

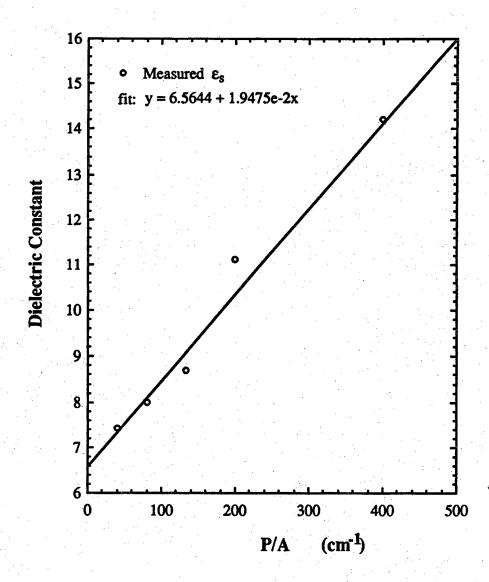

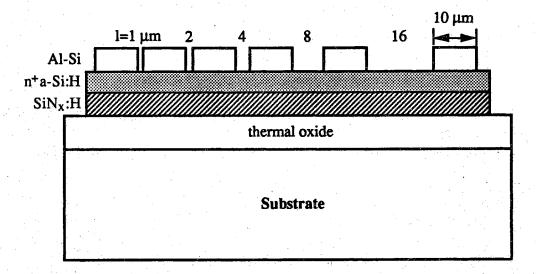

| 3.2 Development of High Quality PECVD a-SiNx:H              | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.2.1 Test Structure                                        | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.2.2 Plasma Deposition of a-SiN <sub>x</sub> :H            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.2.3 Electrical Characterization of the MIM Capacito       | and the second s |

| 3.3 Fabrication and Performance of Initial a-Si:H TFTs      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.3.1 Introduction                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

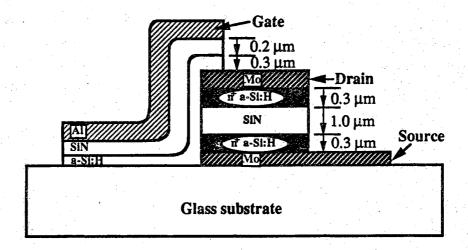

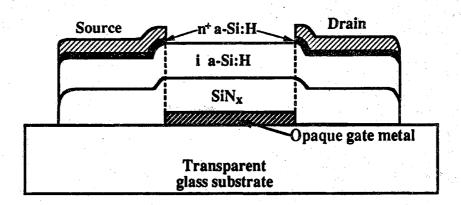

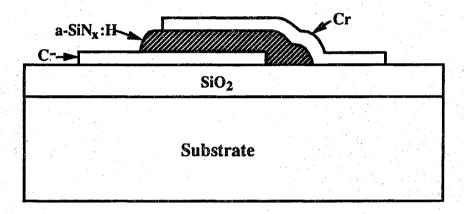

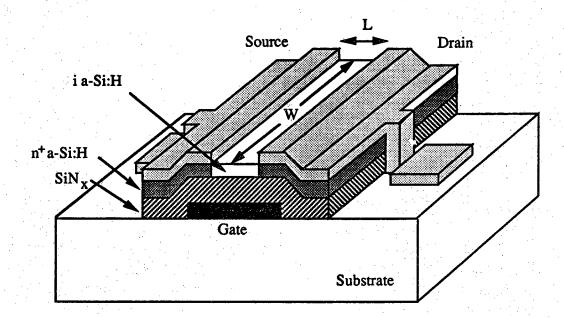

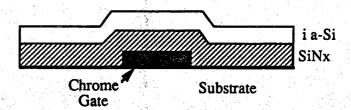

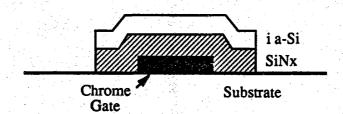

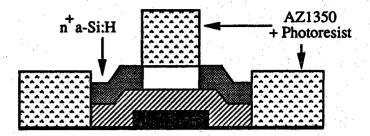

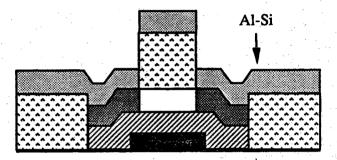

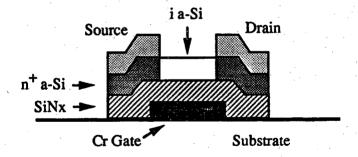

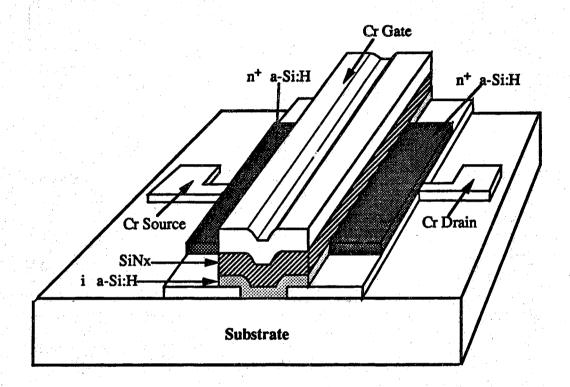

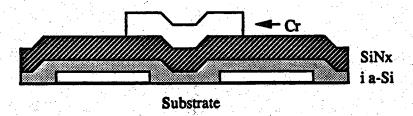

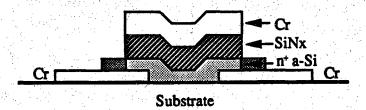

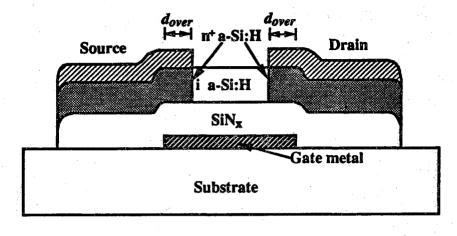

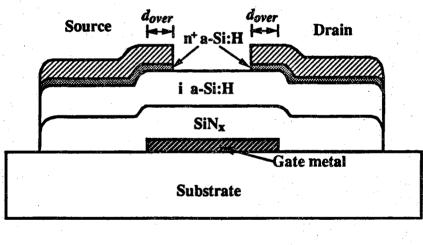

| 3.3.2 Device Structure and Fabrication Steps                | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.3.2 Device Structure and Fabrication Steps                | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

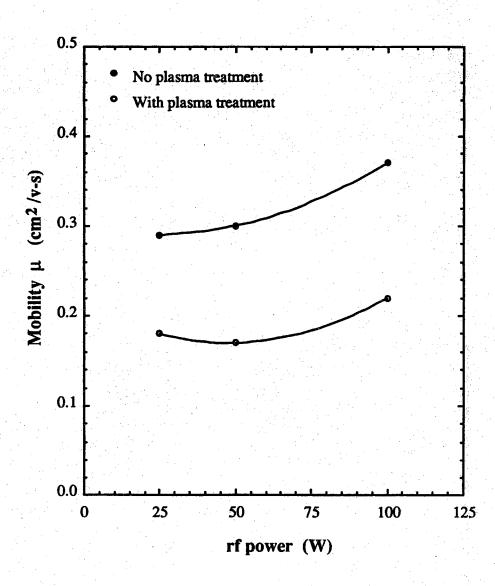

| 3.4 Effect of RF Power and NH <sub>2</sub> Plasma Treatment |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| of the Gate Nitride                                         | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.4.1 Introduction                                          | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.4.2 Device Fabrication and Characterization               | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

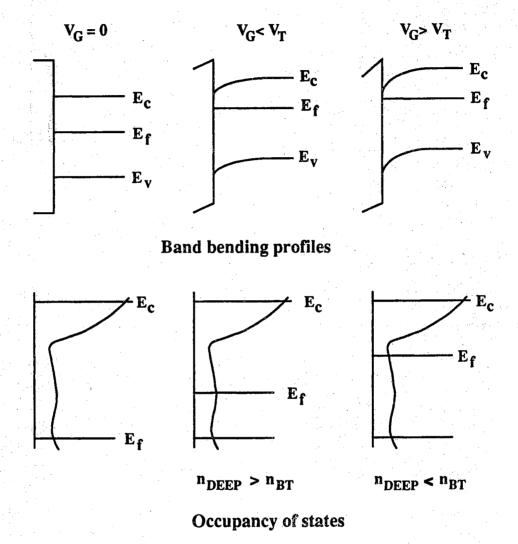

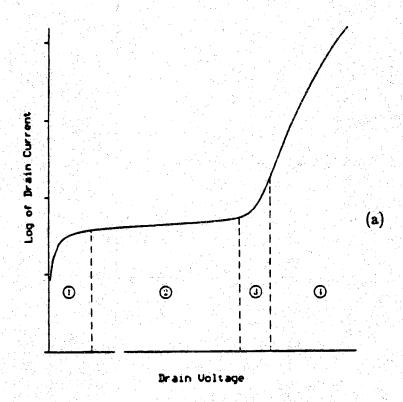

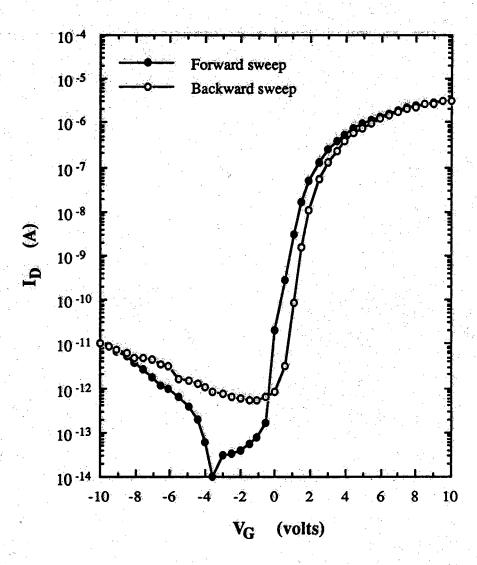

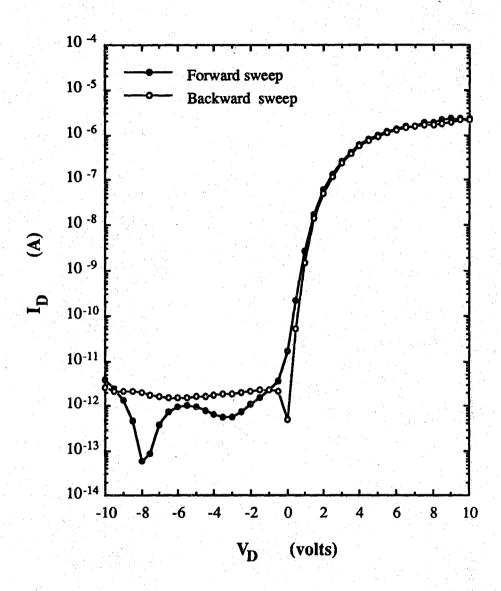

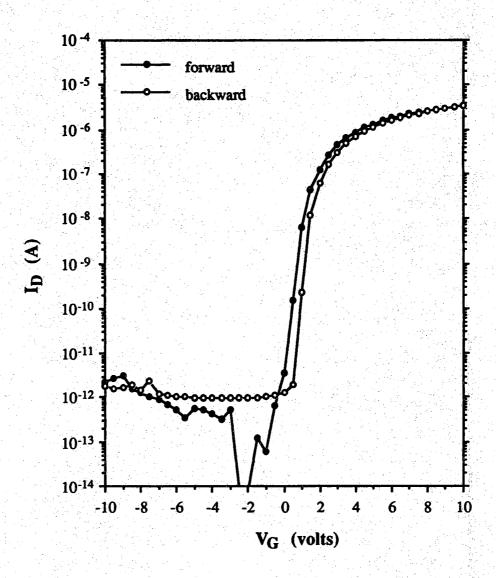

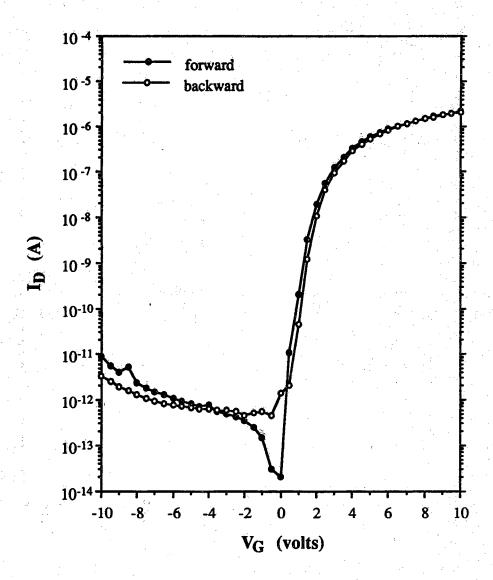

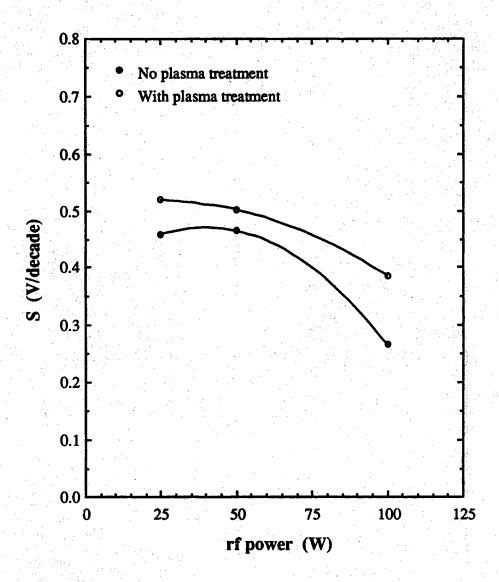

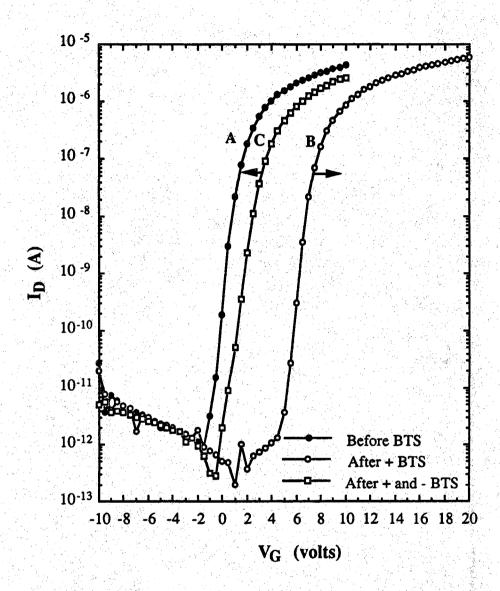

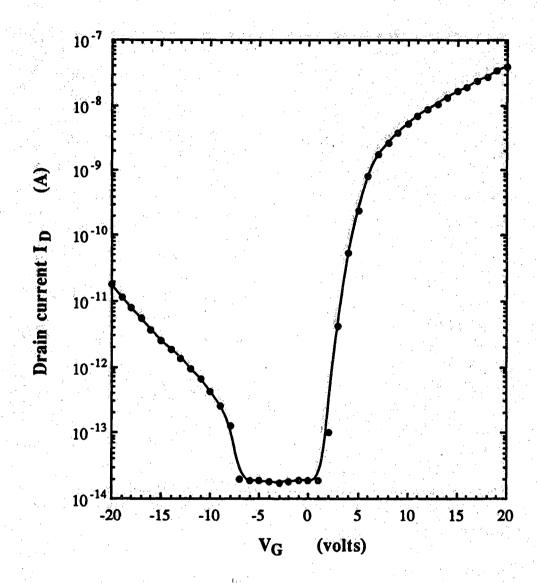

| 3.4.3 TFT Subthreshold Characteristics                      | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

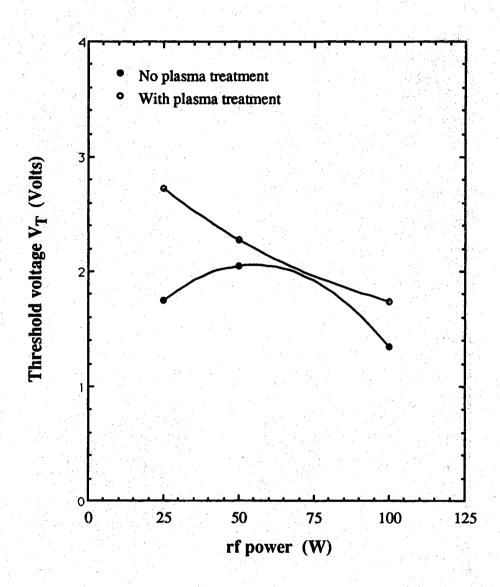

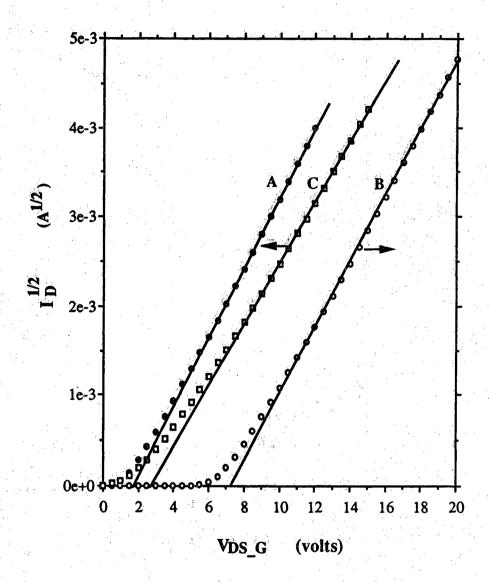

| 3.4.4 Threshold Voltage and Field Effect Mobility           | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

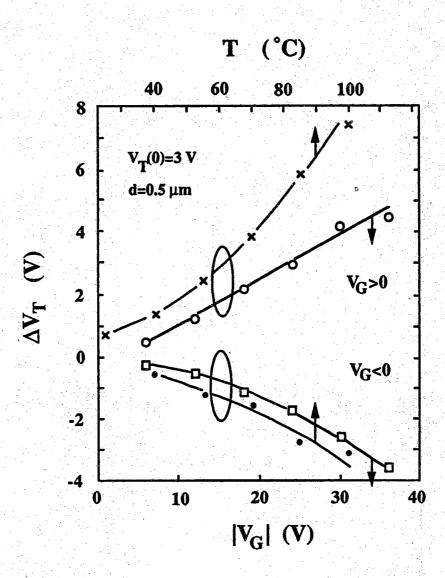

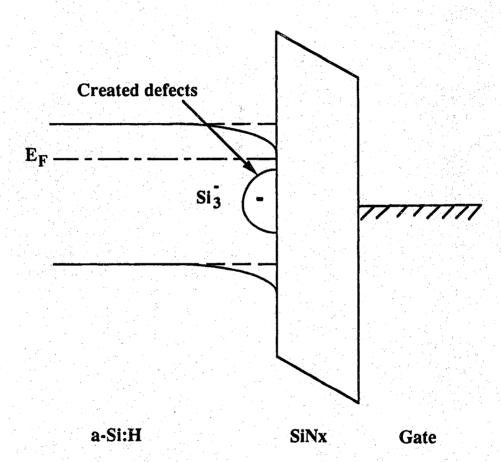

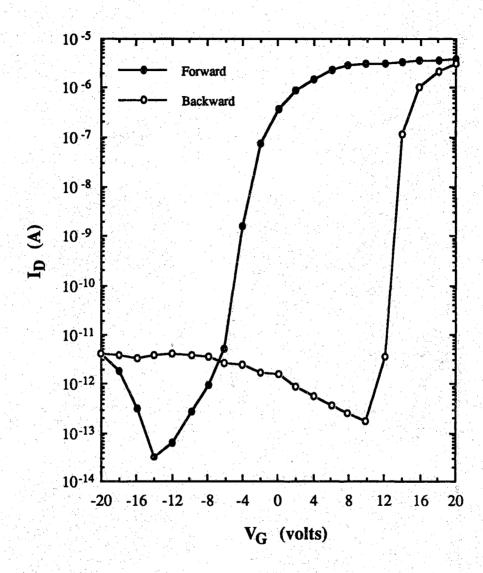

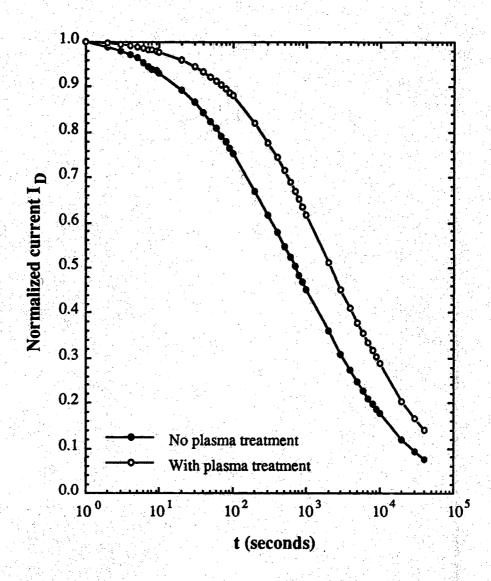

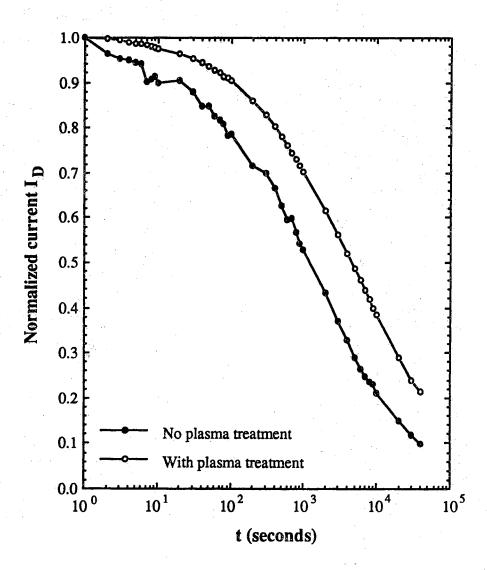

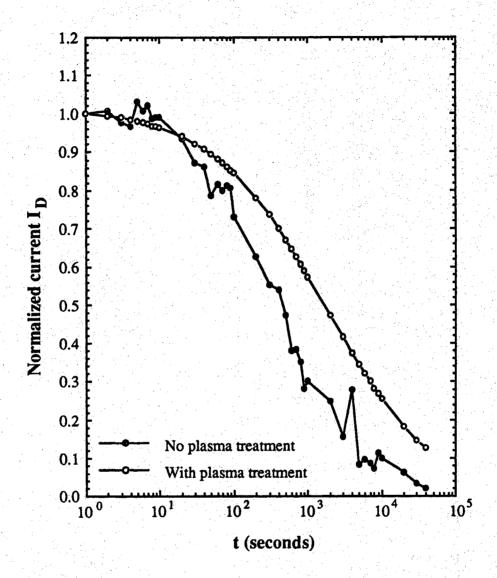

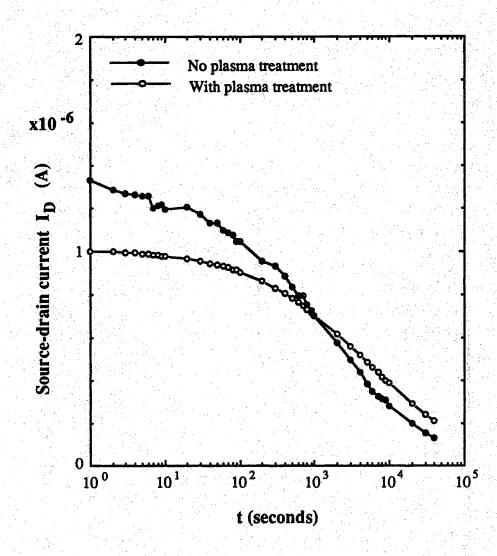

| 3.4.5 Field Induced Instability                             | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.4.6 Conclusion                                            | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

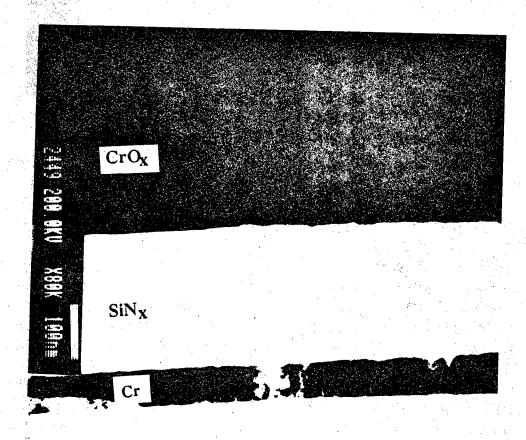

| CHAPTER 4 - STAGGERED 2-Si:H TFTs AND FAILURE               | MECHANISMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.1 Introduction                                            | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

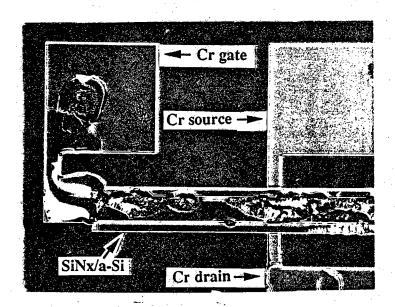

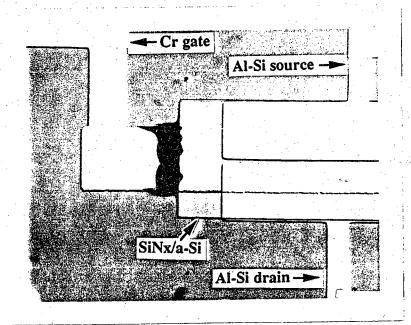

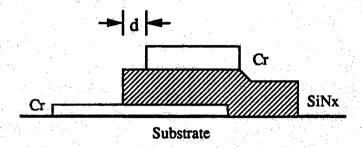

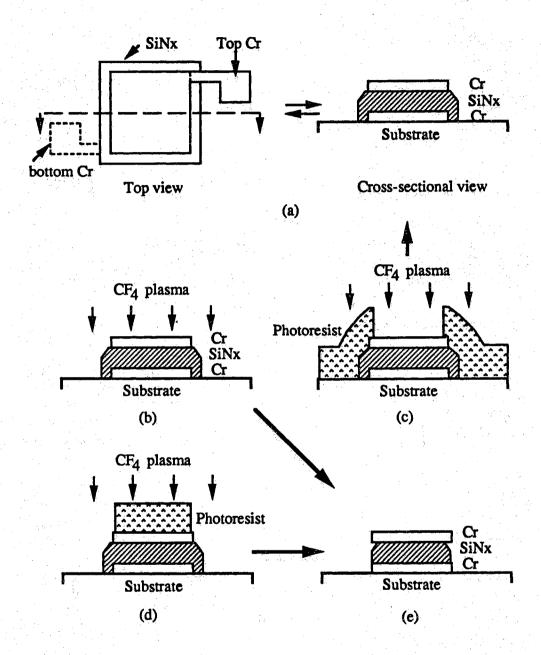

| 4.2 Staggered a-Si:H TFT structures and Processing          | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

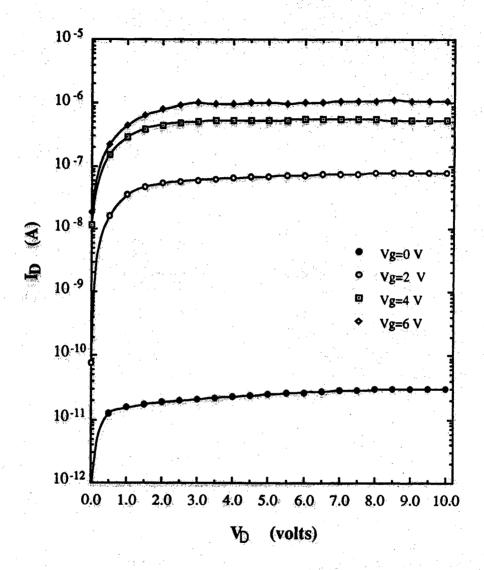

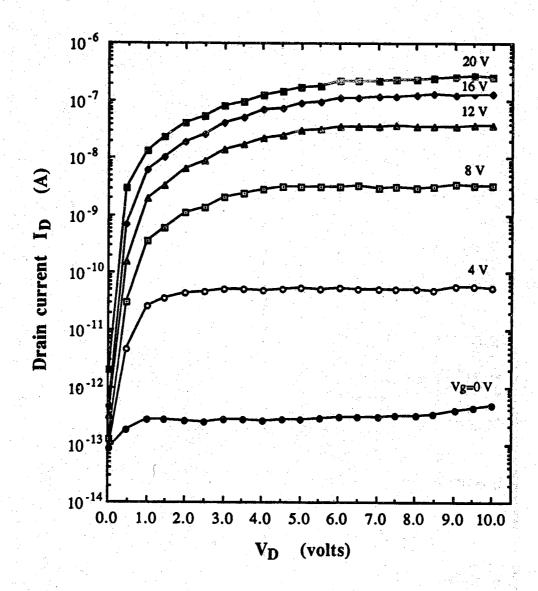

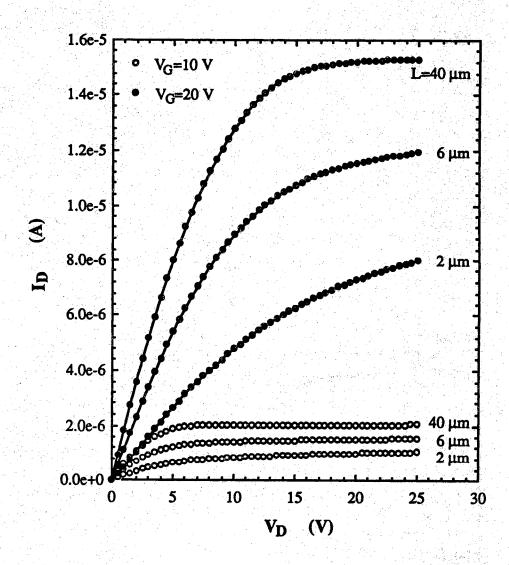

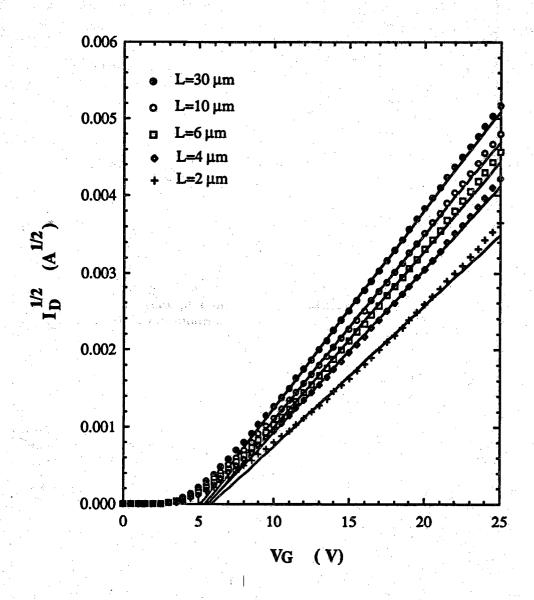

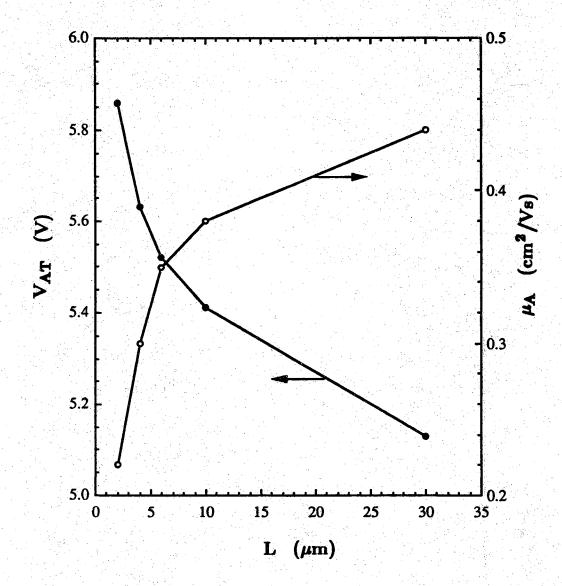

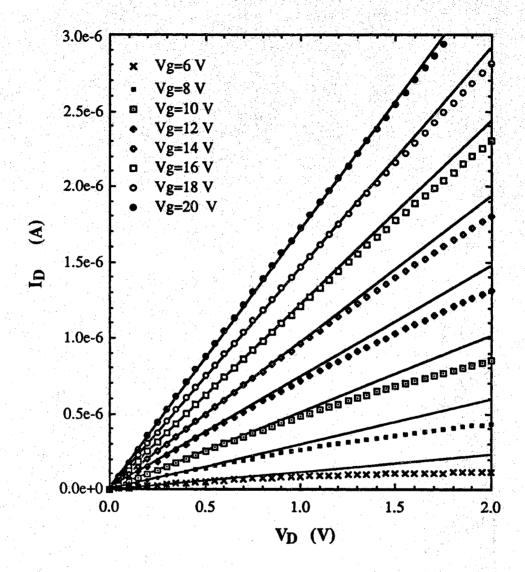

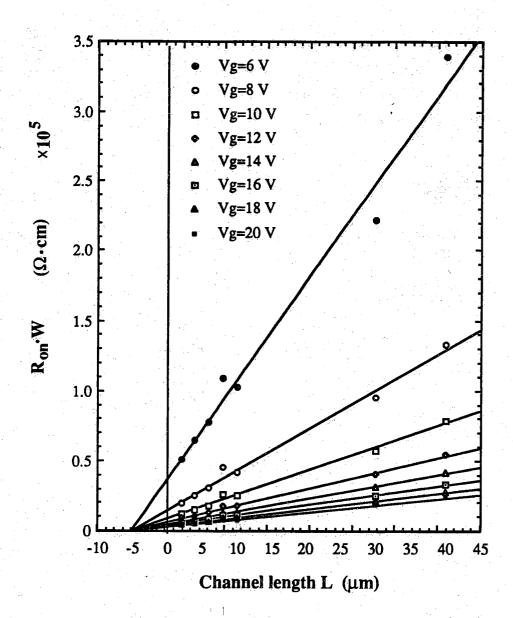

| 4.3 Characteristics of Staggered a-Si:H TFTs                | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A A Distance control Communication of Coto Co.              | 07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.4.1 Introduction                                          | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.4.2 Experimental Structures and Characterization          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Mathoda                                                     | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

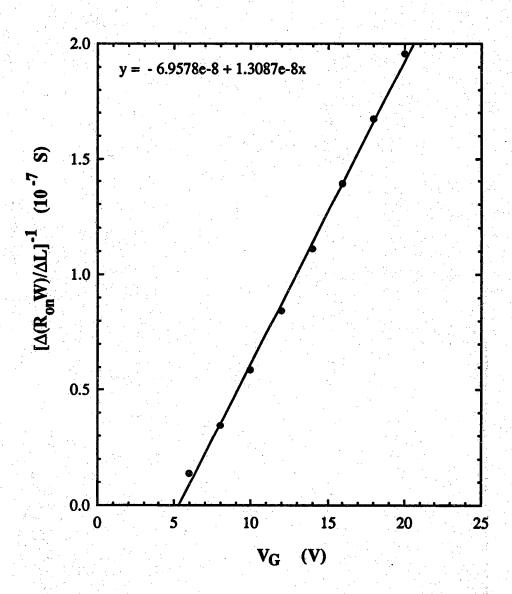

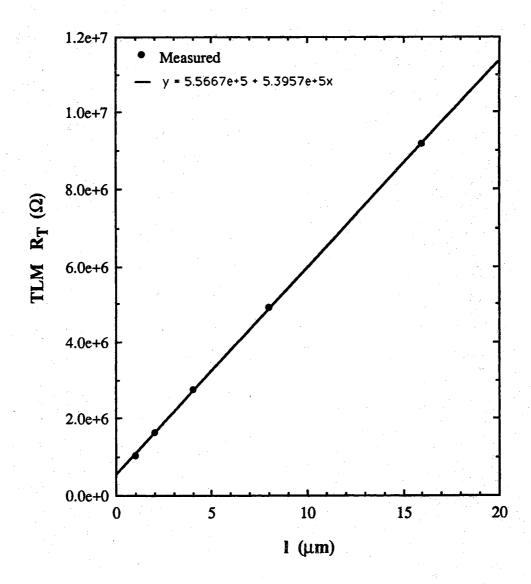

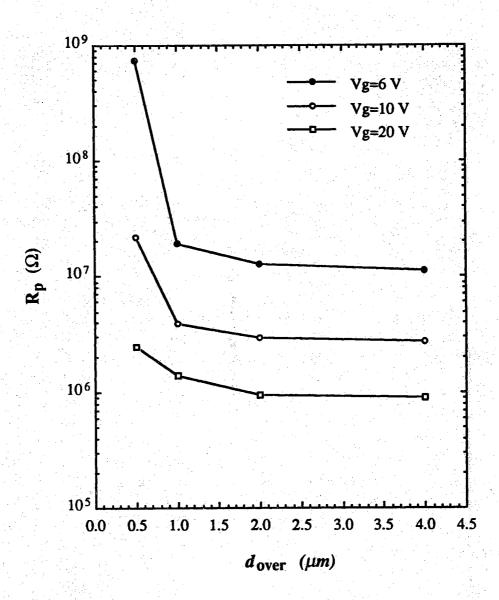

| 4.4.3 Experimental Results                                  | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.4.4 Discussion                                            | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.5 Summary                                                 | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

VITA ......170

## LIST OF TABLES

| Table         |                                    |                   |                 |     | Page |

|---------------|------------------------------------|-------------------|-----------------|-----|------|

| 3.1 Subthresh | old slope and mo                   | bility ratios aft | er and before l | 3TS | 90   |

|               |                                    |                   |                 |     |      |

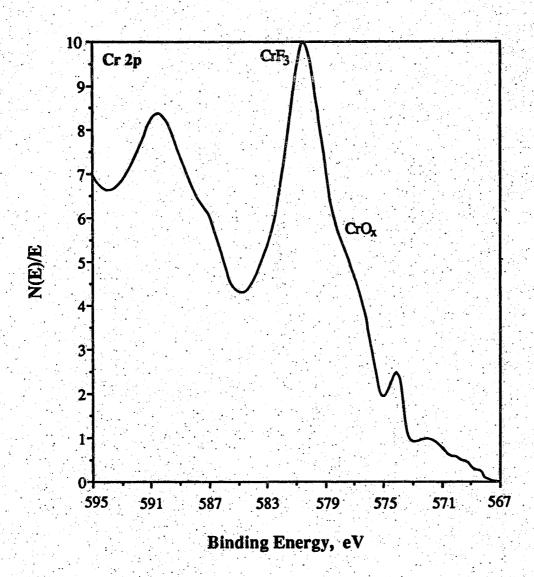

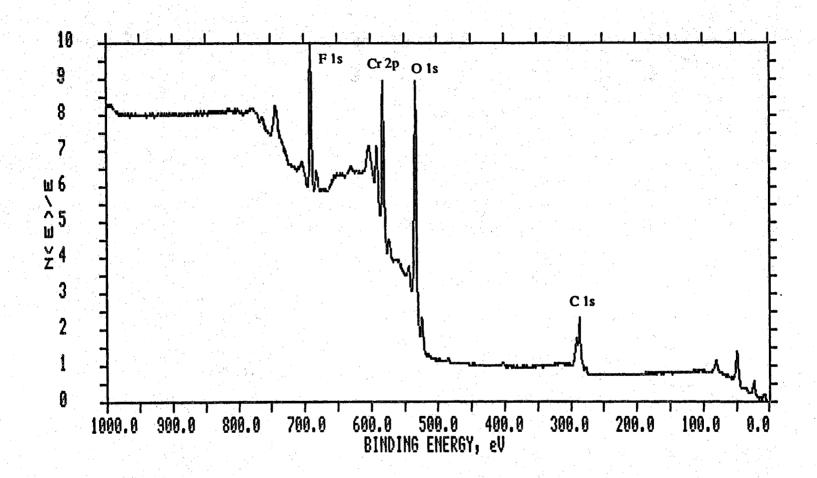

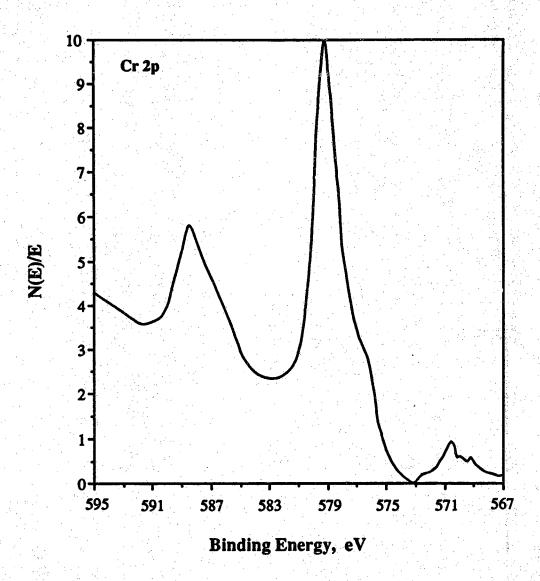

|               | ergies of Cr 2p<br>r some O- and F |                   |                 | )   | 112  |

## LIST OF FIGURES

| Figure                                                         | Page                                    |

|----------------------------------------------------------------|-----------------------------------------|

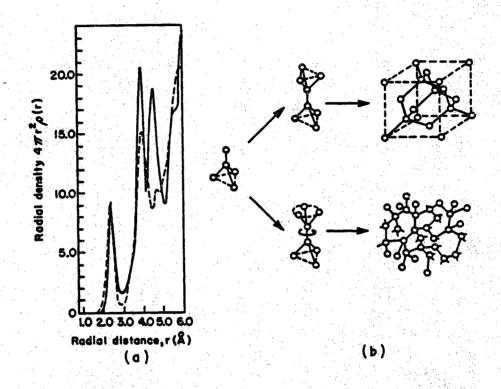

| 2.1 (a) Radial distribution curves for an amorphous Si (       | )<br>                                   |

| and crystalline Si (). (b) The manner in which                 |                                         |

| the basic tetrahedral unit can lead to a crystal or to         |                                         |

| an amorphous, random network material [8]                      | 7                                       |

| an amorphous, random nevwork maserial [0].                     | • • • • • • • • • • • • • • • • • • • • |

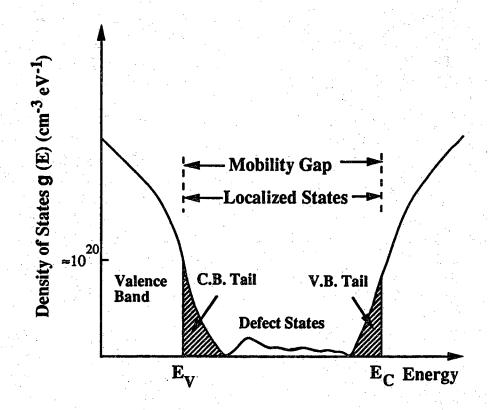

| 2.2 Band model of a-Si. $E_v$ and $E_c$ are the mobility edges | of                                      |

| the valence band and of the conduction band, respectiv         |                                         |

| From Ref. [10]                                                 | 8                                       |

|                                                                |                                         |

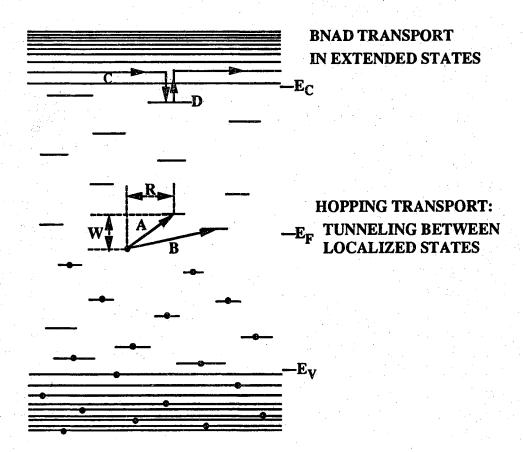

| 2.3 Energy level schematic for electronic conduction mechanic  | anisms                                  |

| in an a-Si. Energy is represented in the vertical directio     | n,                                      |

| distance in the horizontal direction. From Ref. [16]           | 10                                      |

|                                                                |                                         |

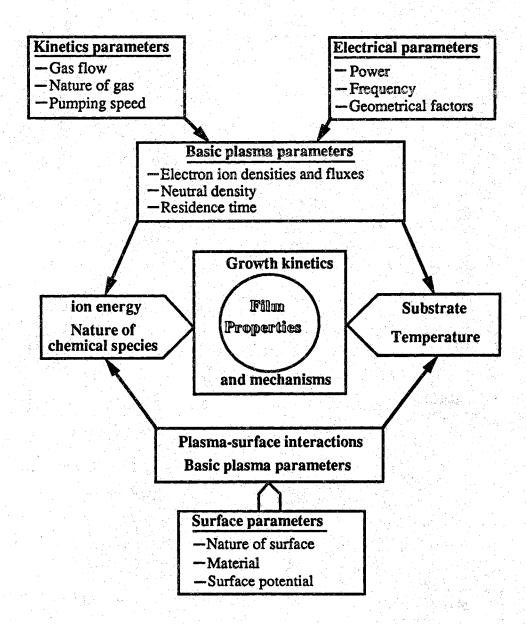

| 2.4 Interaction complexity of homogeneous and heterogene       |                                         |

| plasma processes that determine film properties in PEC         | VD15                                    |

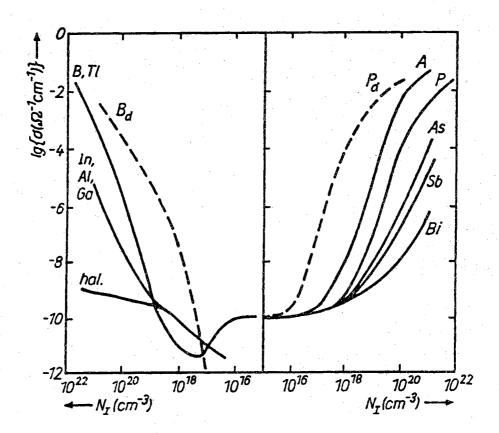

| 2.5 Dependence of the electrical conductivity of a-Si:H on     | the                                     |

| concentration of gas-phase doping and implanted imput          |                                         |

|                                                                | -                                       |

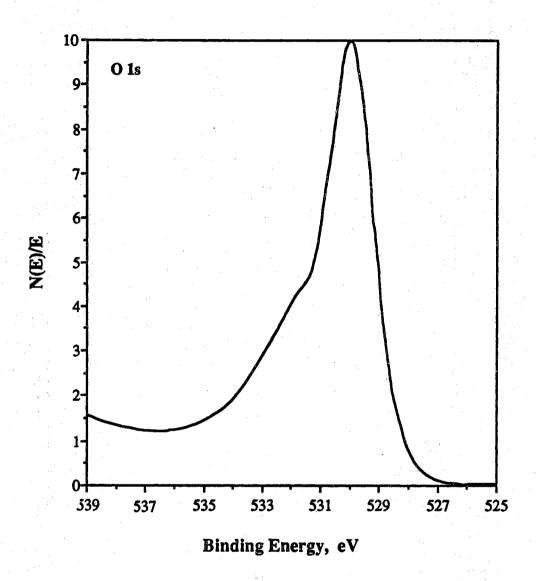

| Including dopant from groups I(A), III, V, and VII (hale       | - · · ·                                 |

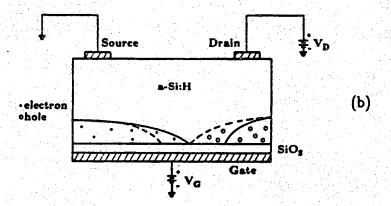

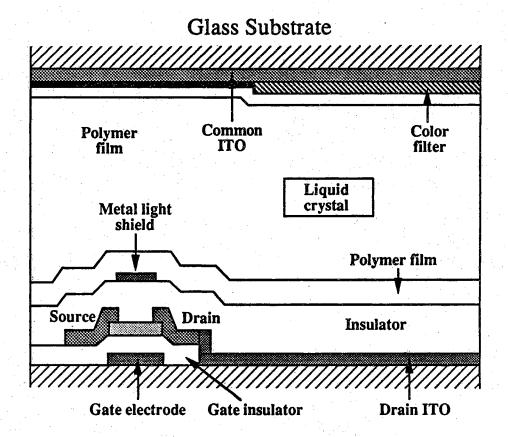

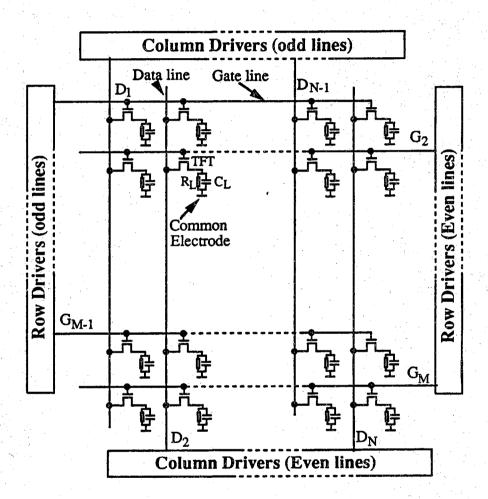

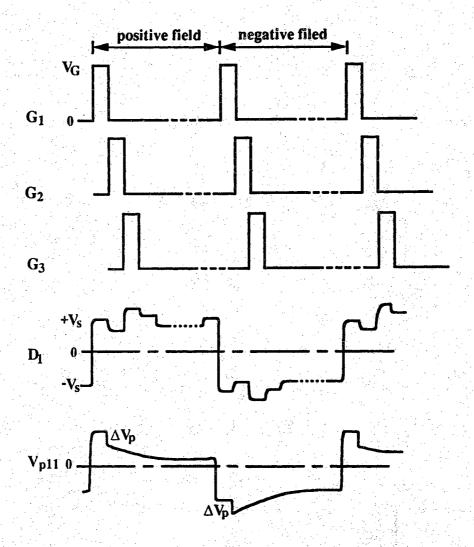

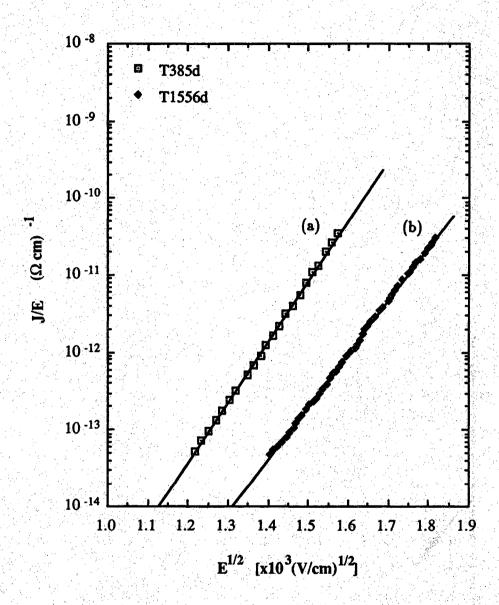

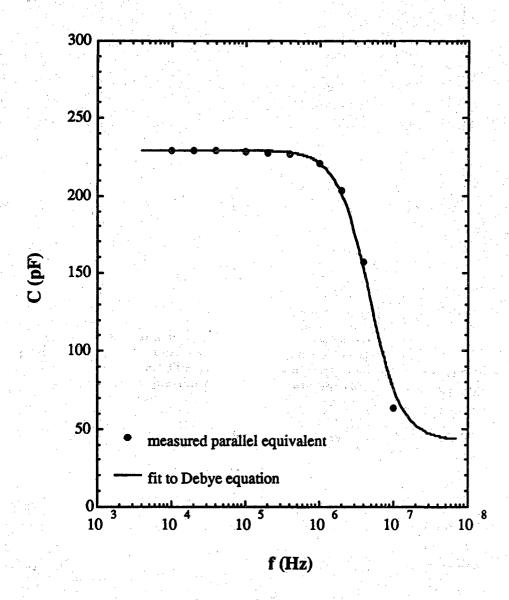

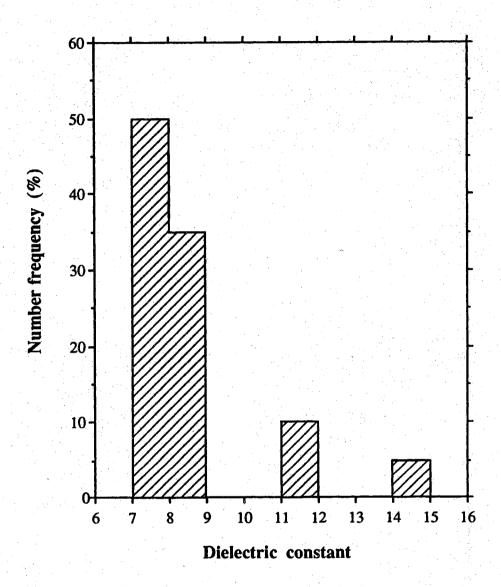

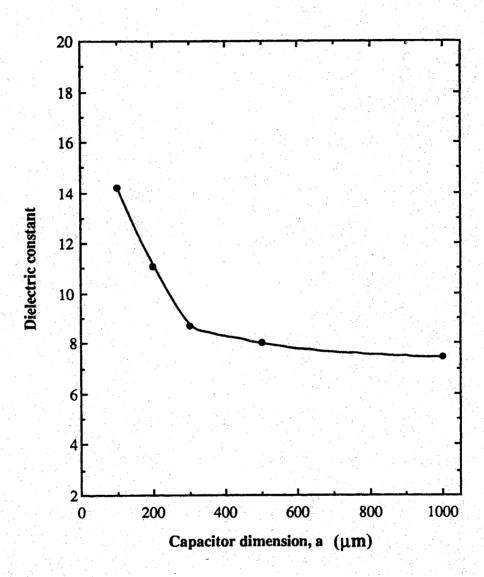

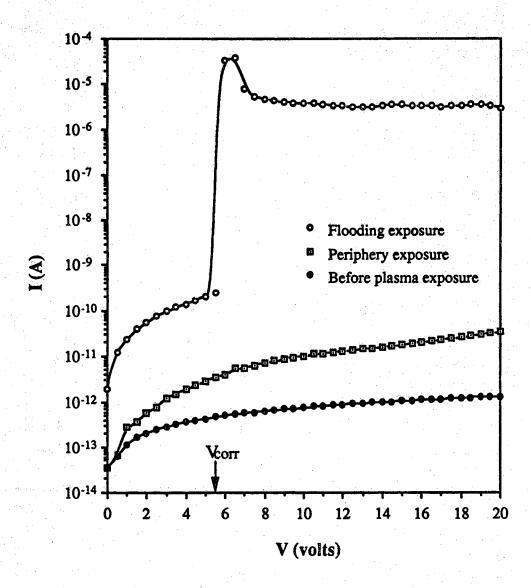

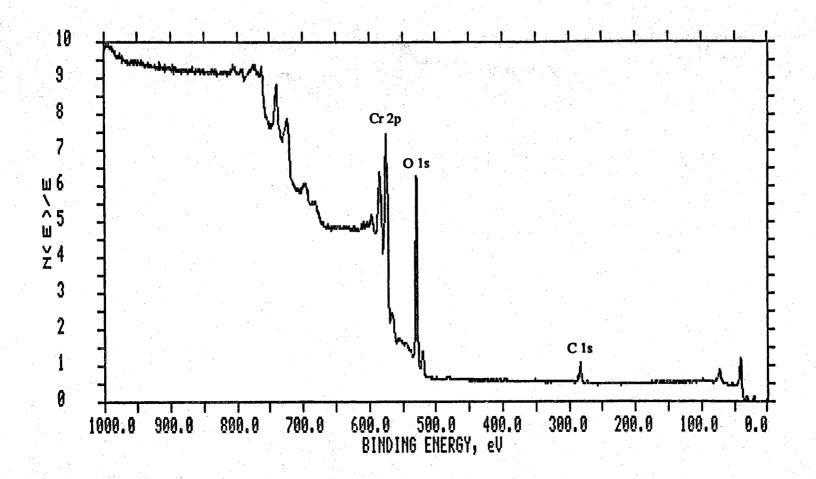

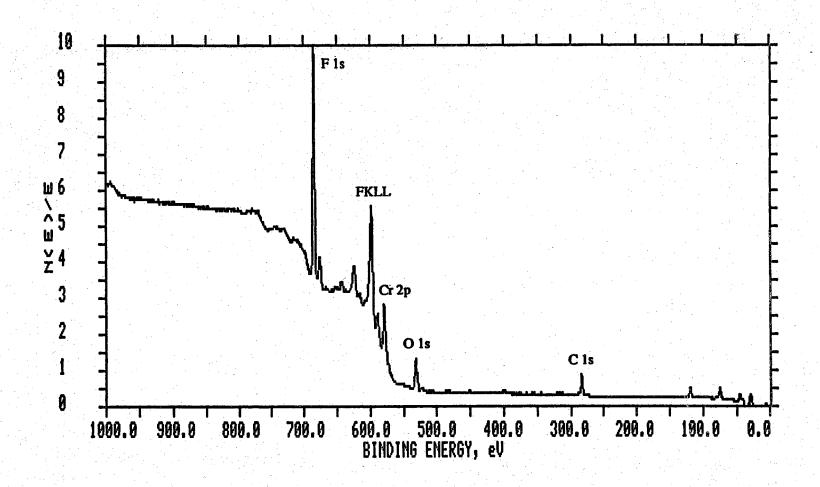

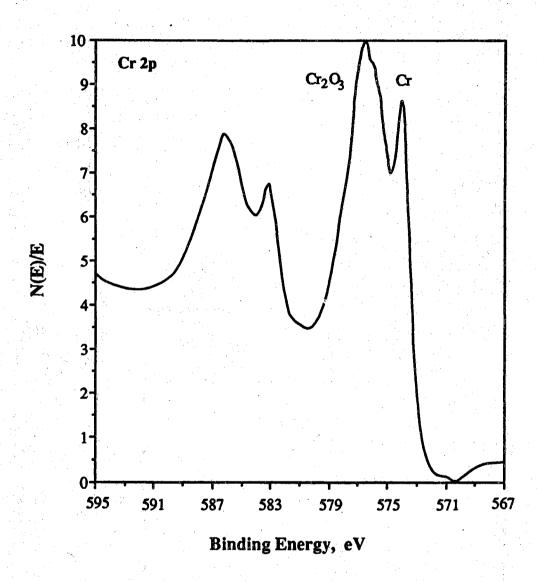

| of the Periodic Table. Dashed lines are for gas-phase do       |                                         |