### Purdue University Purdue e-Pubs

| Department of Electrical and Computer | Department of Electrical and Computer |

|---------------------------------------|---------------------------------------|

| Engineering Technical Reports         | Engineering                           |

8-1-1989

# Development of Process Technology for GaAs E/ D MODFET Logic Circuits

Kai Chen Purdue University

James A. Cooper Jr *Purdue University*

Follow this and additional works at: https://docs.lib.purdue.edu/ecetr

Chen, Kai and Cooper, James A. Jr, "Development of Process Technology for GaAs E/D MODFET Logic Circuits" (1989). Department of Electrical and Computer Engineering Technical Reports. Paper 681. https://docs.lib.purdue.edu/ecetr/681

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

# **Development of Process Technology for GaAs E/D MODFET Logic Circuits**

Kai Chen James A. Cooper, Jr.

TR-EE 89-57 August, 1989

School of Electrical Engineering Purdue University West Lafayette, Indiana 47907

\* Supported by the Indiana Corporation for Science & Technology

## TABLE OF CONTENTS

|                   | 승규는 그 물건이 많다. 그 것 같은 것 가지 않는 것 같아. 것이 같아.                                                                                                     | Page     |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                   | TABLES                                                                                                                                        |          |

| LIST OF           | FIGURES                                                                                                                                       | <b>v</b> |

| ABSTRAC           | T                                                                                                                                             | . viii   |

| CHAPTER           | 1 - INTRODUCTION                                                                                                                              | 1        |

| 1.3 I<br>1.4 I    | MODFET Review<br>MODFET Overview<br>MODFET Circuit Implementation<br>Feasibility of MODFET Technology<br>The Organization of Thesis           | . 5<br>7 |

| CHAPTER           | 2 - THEORY OF MODFET                                                                                                                          | 10       |

| 2.2<br>2.3<br>2.4 | Heterojunction Electrostatics<br>The 2DEG<br>Schottky Gate Charge Control Regime<br>DC Current-Voltage Model of MODFET<br>Discussion of Model | 12       |

| CAHPTER           | 3 - TEST CHIP DESIGN                                                                                                                          | 30       |

| 3.2 (<br>3.3 I    | MODFET Device Design,<br>Circuit Design<br>Process Overview<br>Mask Design                                                                    | 32<br>45 |

| CHAPTER 4         | 4 - PROCESS DEVELOPMENT AND FABRICATION                                                                                                       | 53       |

| 4.3 (<br>4.4 (    | Photolithography and Lift-off<br>Wet Chemical Etch<br>Ohmic Contact<br>Gate Metallization<br>Summary                                          | 60<br>65 |

|         |                                                                                                                                 |           |                                                                                                                                                                                                                                                                                                                                                       | Page  |

|---------|---------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| CHAPTER | 5 - ELECTRICAL CHARACT                                                                                                          | ERIZATION | 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 -<br>1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 -<br>1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - | 71    |

| 5.4     | Diagnostic Devices<br>D-mode and E-mode Transis<br>DCFL E/D Type Inverters<br>Other MODFET DCFL Circu<br>Discussion and Summary | tors      |                                                                                                                                                                                                                                                                                                                                                       | . 86  |

|         | 6 - CONCLUSION AND RECOM<br>FOR FUTURE WORK                                                                                     | MENDATION |                                                                                                                                                                                                                                                                                                                                                       | . 104 |

| REFERE  | NCES                                                                                                                            | •••••     | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                 | . 108 |

| APPEND  | IX                                                                                                                              |           |                                                                                                                                                                                                                                                                                                                                                       | . 112 |

iii

# LIST OF TABLES

# Table

# Page

| 1.1. | Comparison of MODFET and MESFET microwave figures                     | 7  |

|------|-----------------------------------------------------------------------|----|

| 1.2  | Device technology comparison and 1 (                                  | 8  |

|      | The 2DEG carrier concentration $n_s$ (cm <sup>-2</sup> )              | 19 |

| 3.1. | The truth table of 3-input NAND $(Z_1)$ and NOR $(Z_2)$ logic         | 43 |

| 3.2. | Summary of design results for various circuits built on the test chip | 44 |

| 4.1. | Comparison of alloy contact through different alloy cycles            | 65 |

| 5.1  | Threshold voltages Vth (V) of E-mode MODFET's across the entire wafer | 81 |

| 5.2  | Transconductances versus gate length L and source-to-drain spacing SD | 83 |

|      | Characterization of E/D inverters with etched and unetched loads      | 02 |

# LIST OF FIGURES

# Figure

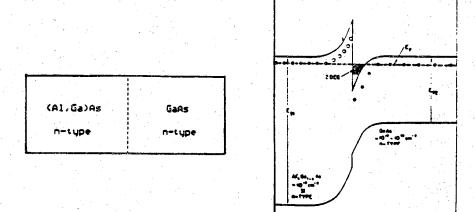

| 1.1.         | The heterostructure and its energy band diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2.         | (a) The MODFET heterojunction and, (b) its energy band diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3  |

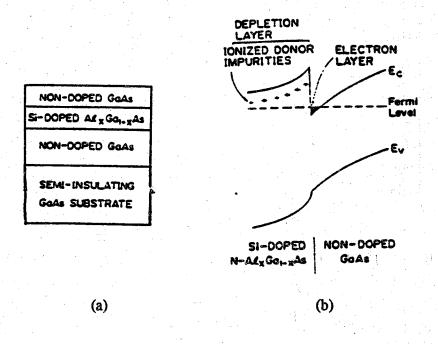

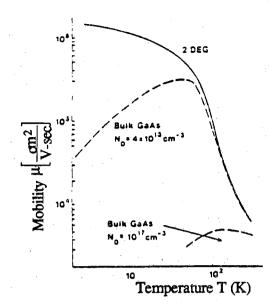

| 1.3.         | The 2DEG and bulk GaAs carrier mobilities vs. temperatures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

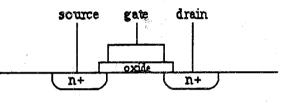

| 1.4.         | (a) Si MOSFET and, (b) GaAs MODFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4  |

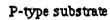

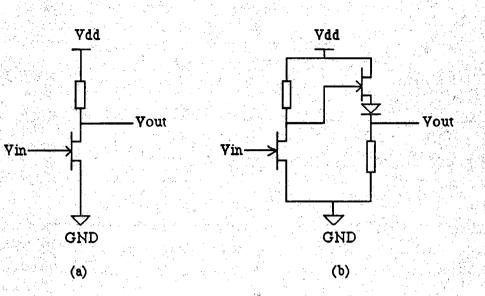

| 1.5.         | (a) Direct-coupled FET logic and, (b) buffered FET logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6  |

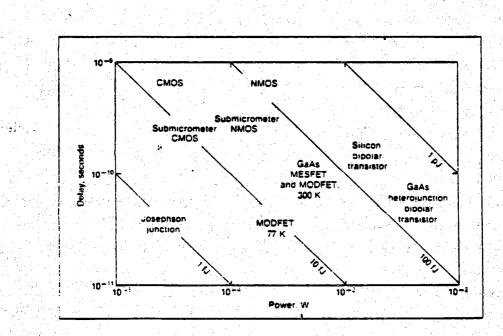

| 1.6.         | A comparison of various device technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8  |

| 2.1.         | Heterojunction electrostatics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11 |

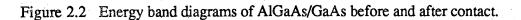

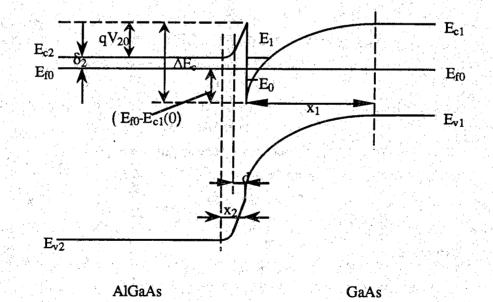

| 2.2.         | Energy band diagrams of AlGaAs/GaAs before and after contact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13 |

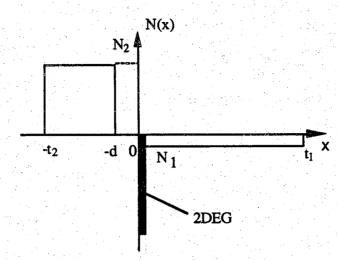

| 2.3.         | Space charge distribution of MODFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14 |

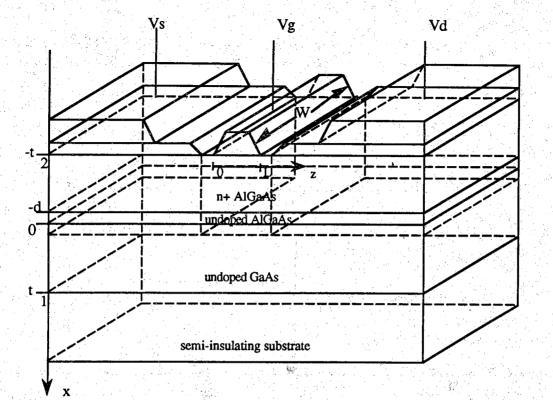

| 2.4.         | MODFET structure with defined notations and coordinates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

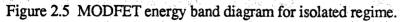

| 2.5.         | MODFET energy band diagram for isolated regime                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15 |

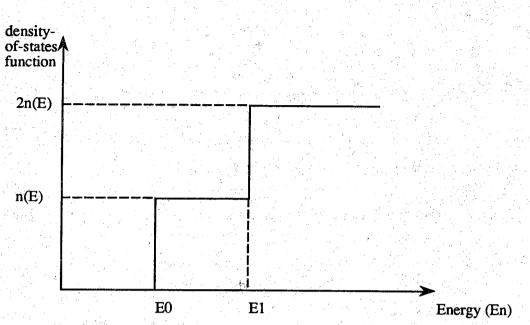

| 2.6.         | Density-of-states function vs. energy En                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17 |

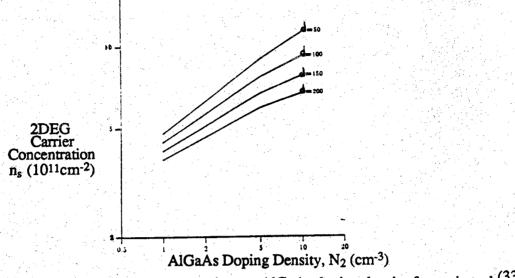

| 2.7.         | 2DEG carrier concentration vs. AlGaAs doping density for various d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20 |

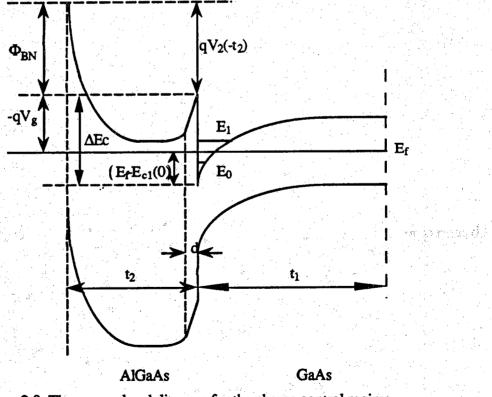

| 2.8.         | The energy band diagram for the charge control regime                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| 2.9.         | The energy band diagrams with regard to etching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23 |

| 2.10.        | $N_2$ vs. threshold voltages for (a) optimal D-mode and,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24 |

| 2.1          | (b) E-mode MODFET's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

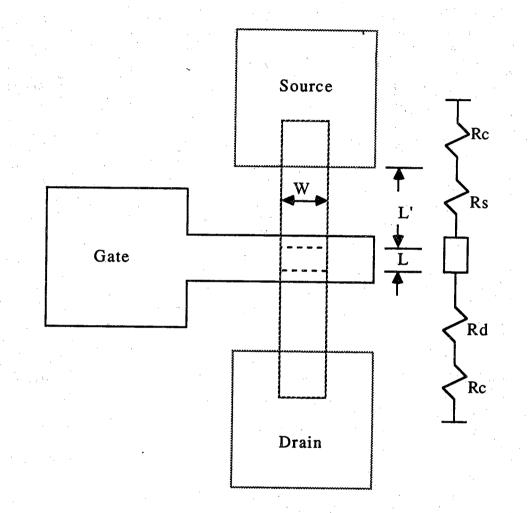

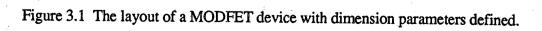

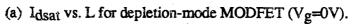

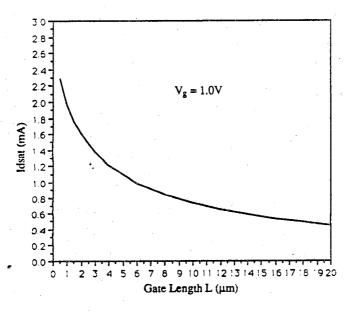

| 3.1.<br>3.2. | The layout of a MODFET device with dimension parameters defined<br>Idsat vs. gate length L for (a) D-mode and, (b) E-mode MODFET's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| e            | 그는 물건물건 이 것 같아요. 그는 것 같아요. 이 집에 가지 않는 것 같아요. 이 집에 가지 않는 것 같아요. 이 것 같아요. 이 것 같아요. 이 것 같아요. 이 집에 있는 것 같아요. 이 집에 가 있는 것 같아요. 이 집에 있 |    |

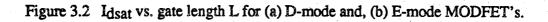

| 3.3.         | Inverter elements with various types of loads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

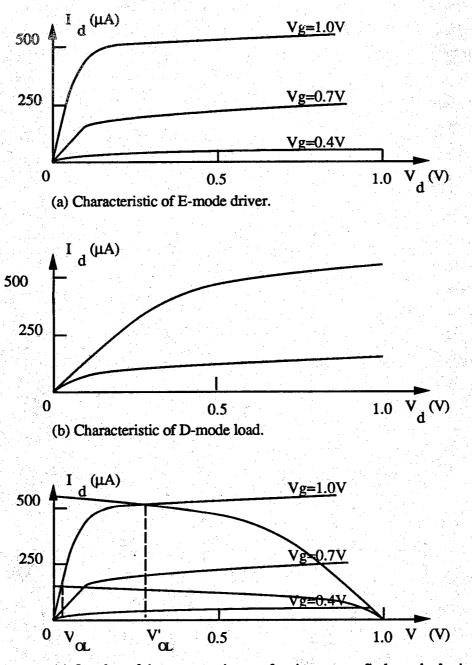

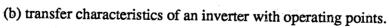

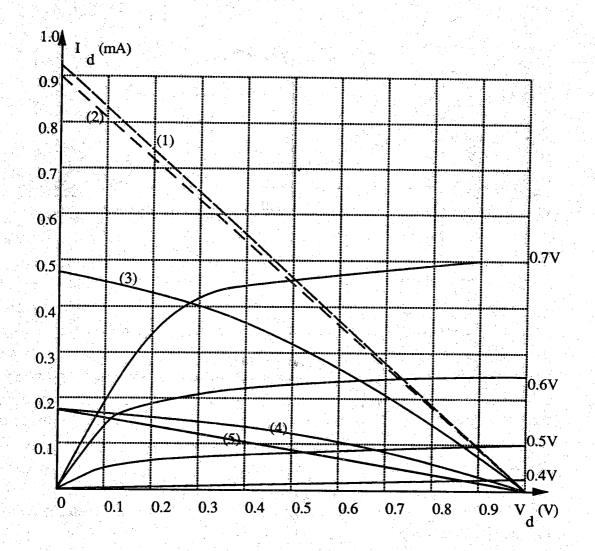

| 3.4.         | Characteristics of E-driver and D-load for an inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

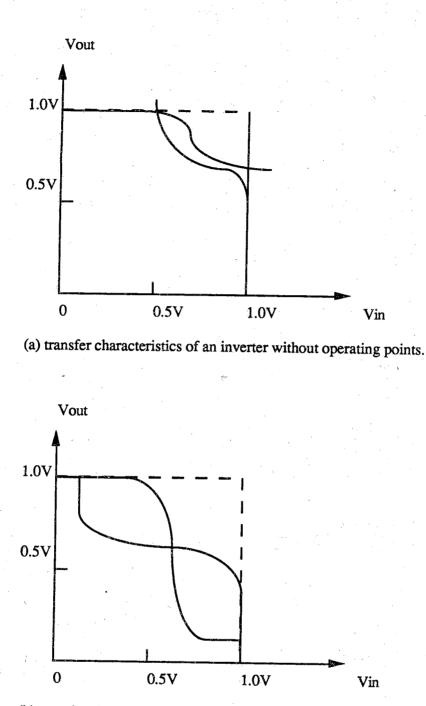

| 3.5.         | Transfer characteristics of (a) without and (b) with operating points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| 3.6.         | Characteristics with load lines corresponding to different etching times                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

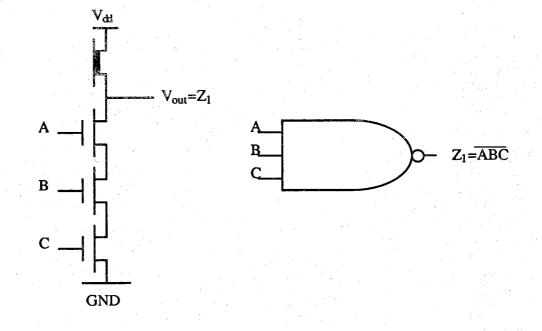

| 3.7.         | Circuit and logic symbol of three-input NAND logic gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

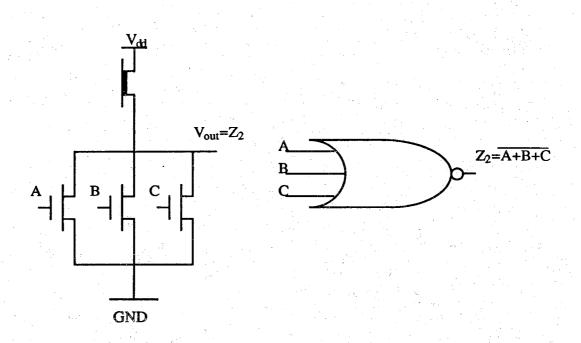

| 3.8.         | Circuit and logic symbol of three-input NOR logic gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 42 |

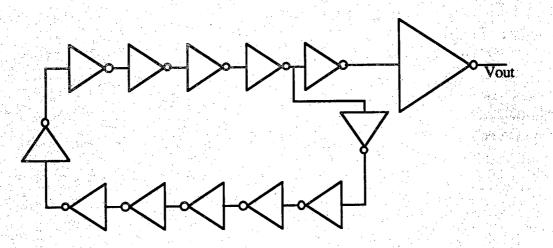

| 3.9.         | Logic diagram of an eleven-stage ring oscillator with two output stages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 46 |

Page <sup>·</sup>

v

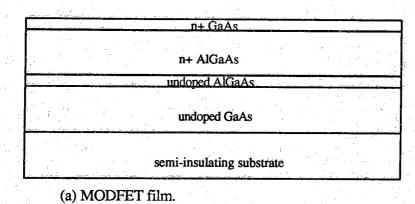

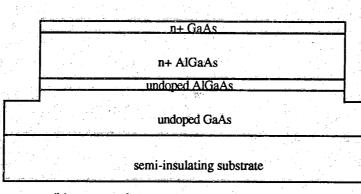

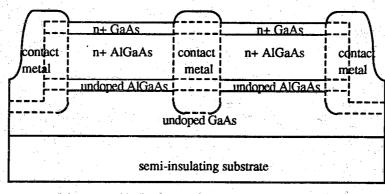

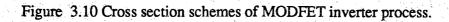

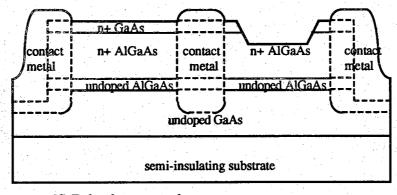

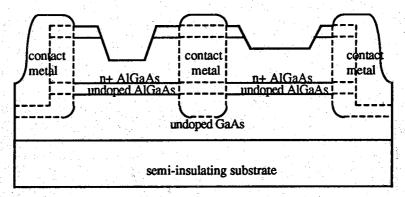

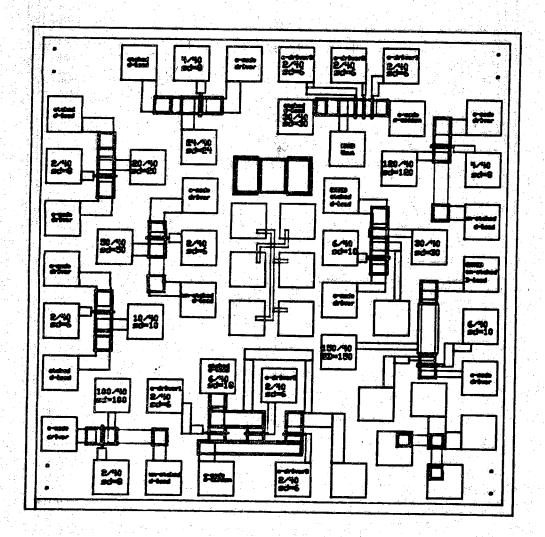

| 3.10  | . Cross section schemes of MODFET inverter process                                               | . 47 |

|-------|--------------------------------------------------------------------------------------------------|------|

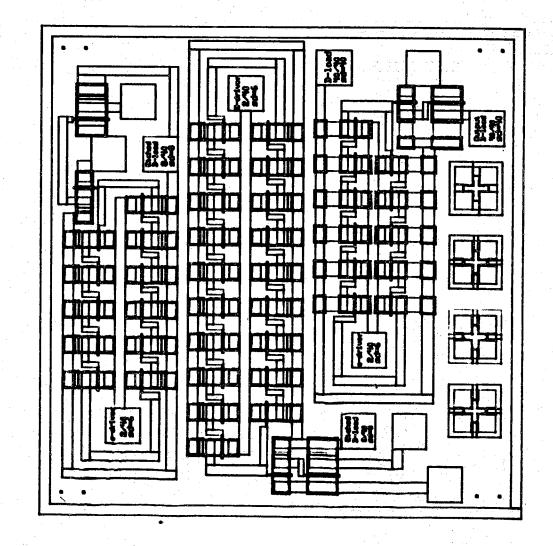

| 3.11  | Layout of (a) logic circuit chip and, (b) ring oscillator chip                                   | 51   |

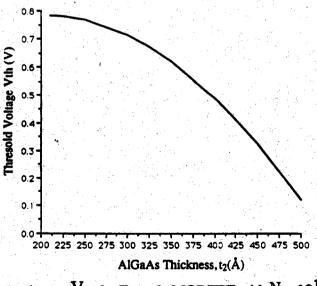

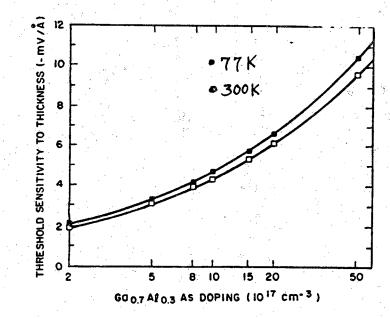

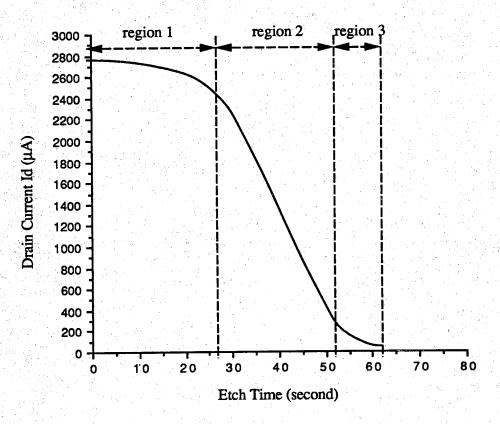

| 4.1.  | Sensitivity of threshold voltage V <sub>th</sub> vs. thickness of AlGaAs, t <sub>2</sub>         | 56   |

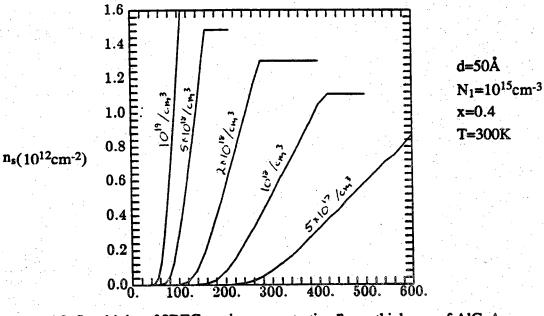

| 4.2.  | Sensitivity of 2DEG carrier concentration n <sub>s</sub> vs. thickness of AlGaAs, t <sub>2</sub> | . 56 |

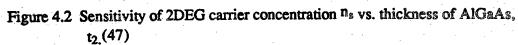

| 4.3.  | Measurement of drain current Id vs. etch times                                                   |      |

|       | (ungated D-mode device: $W/L=40/8$ , $V_d=4.0V$ )                                                |      |

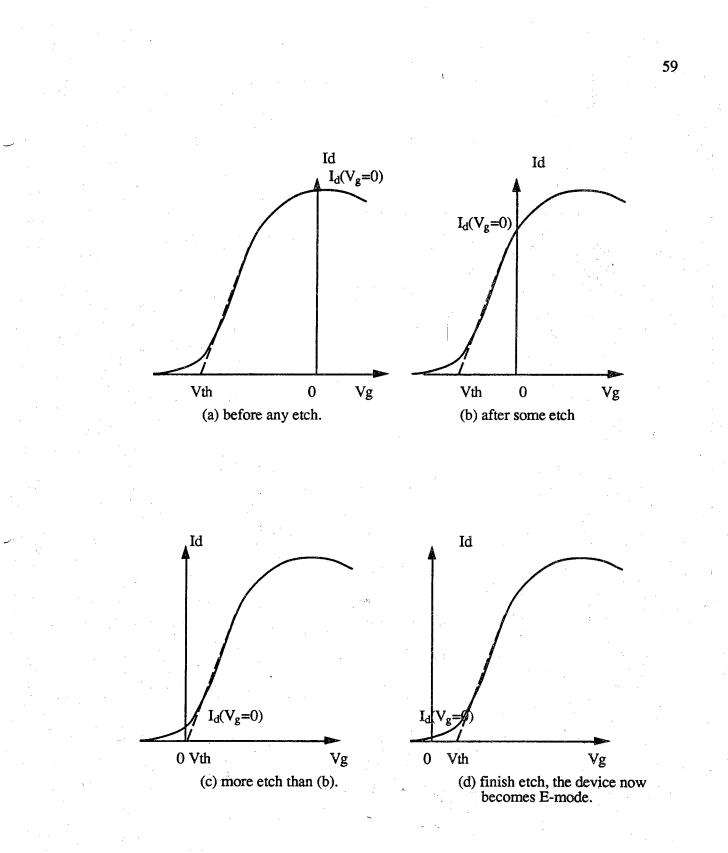

| 4,4.  | Curve of $I_d$ vs. $V_g$ changes with different recess etch times                                |      |

| 4.5.  | Heterostructure energy band diagram                                                              | 61   |

| 4.6.  | Comparison of surfaces alloyed (a) with and, (b) without Ni                                      | 63   |

| 4.7.  | SEM photographs of E/D type inverter process steps                                               | 69   |

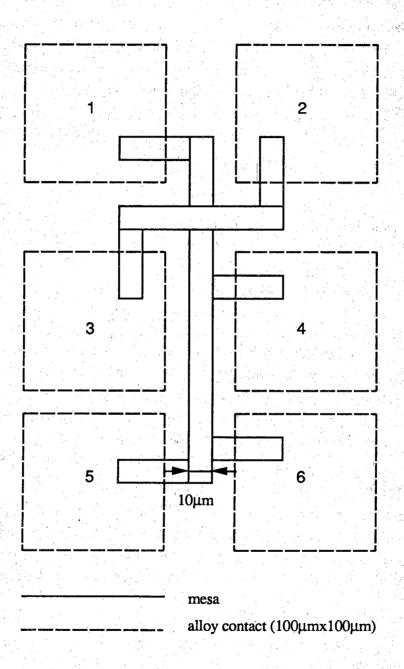

| 5.1.  | Greek-cross test structure                                                                       | 73   |

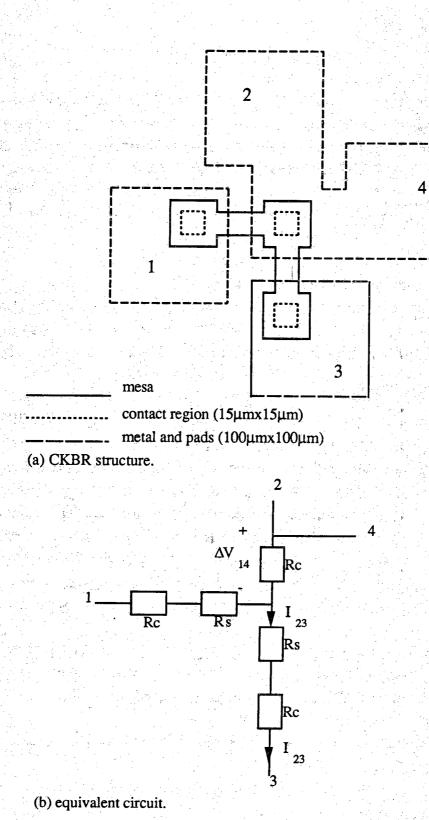

| 5.2.  | CBKR and its equivalent circuit                                                                  | 75   |

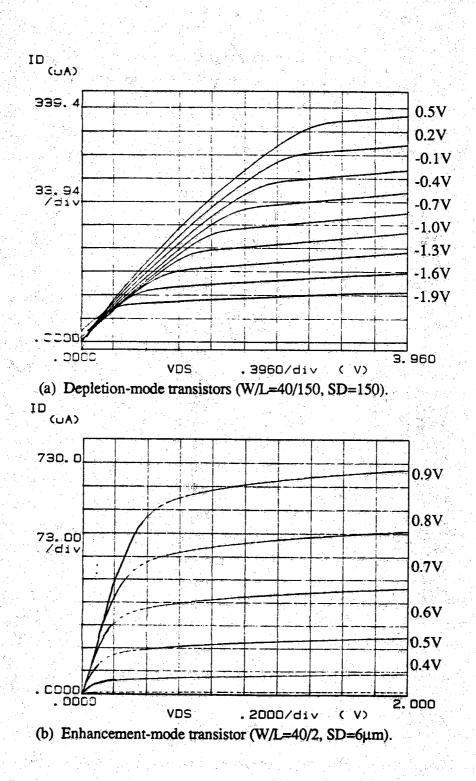

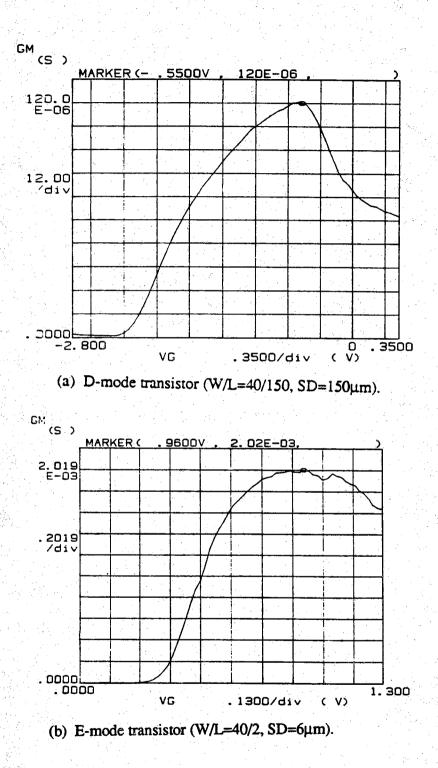

| 5.3.  | Characteristic curves of (a) D-mode and, (b) E-mode MODFET's                                     |      |

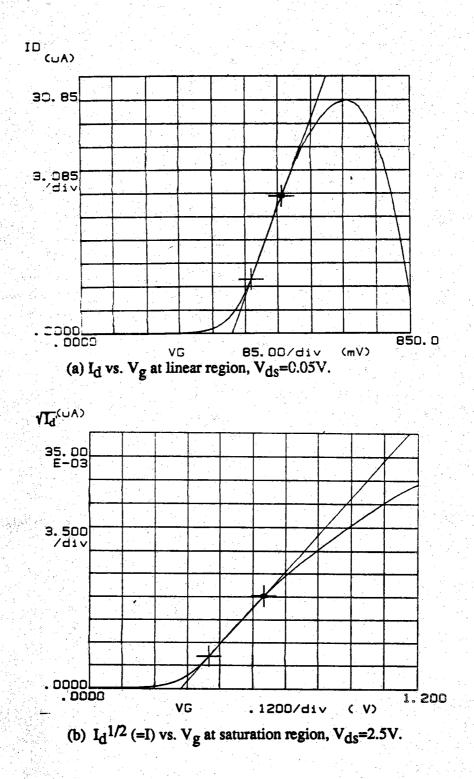

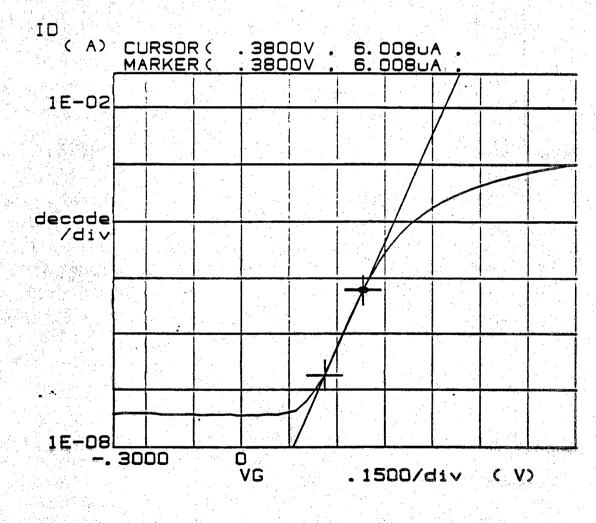

| 5.4.  | Id vs. Vg at two operation regions of an E-mode transistor (W/L=40/2,                            |      |

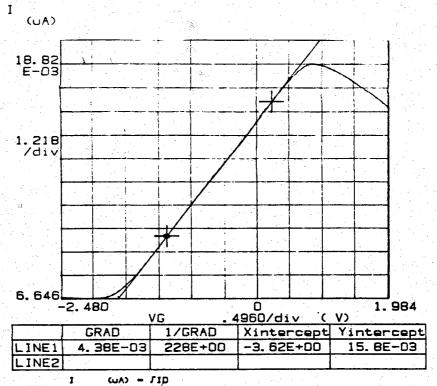

| 5.5.  | $I_d^{1/2}$ vs. $V_g$ for the D-mode transistor                                                  | 80   |

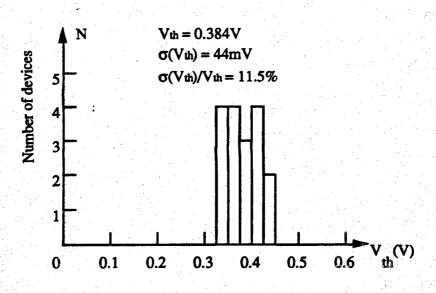

| 5.6.  | Histogram of V <sub>th</sub> of E-mode transistors across the wafer                              |      |

| 5.7.  | Transconductances at V <sub>dd</sub> =2.0V                                                       |      |

| 5.8.  | Subthreshold current at $V_d=2.0V$<br>(E-mode device: W/L=40/2, SD=6 $\mu$ m)                    |      |

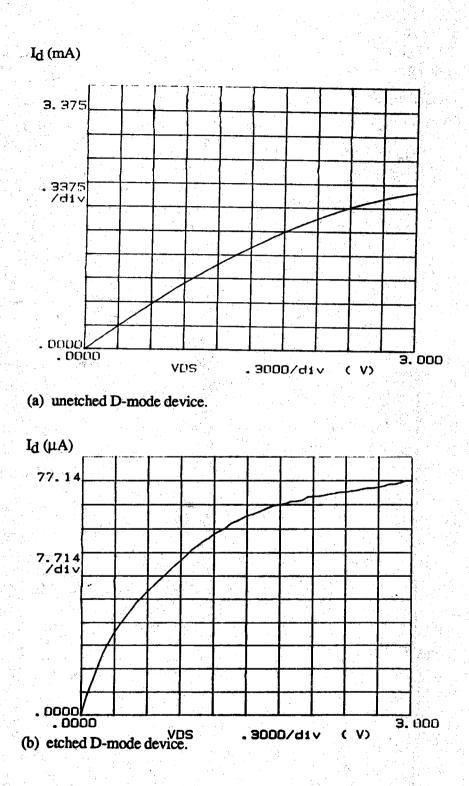

| 5.9.  | Characteristic curves of ungated D-mode transistors $(W/L=40/8, SD=14\mu m)$ .                   |      |

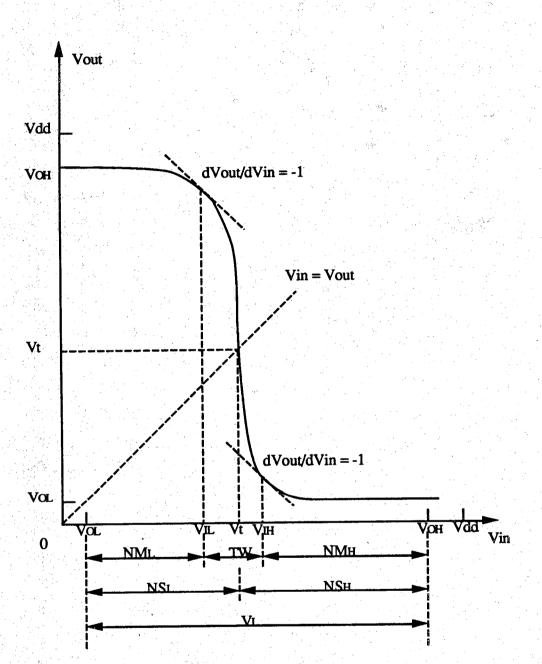

| 5.10. | Inverter transfer characteristic with notations defined                                          |      |

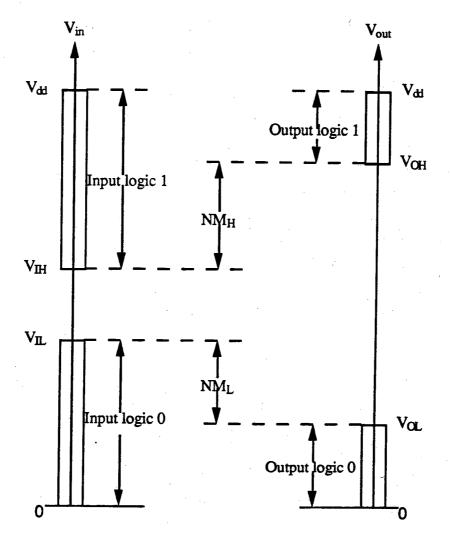

|       | Intepretation of noise margin                                                                    |      |

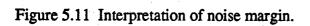

|       | Transfer characteristic of E/D inverter with unetched load                                       |      |

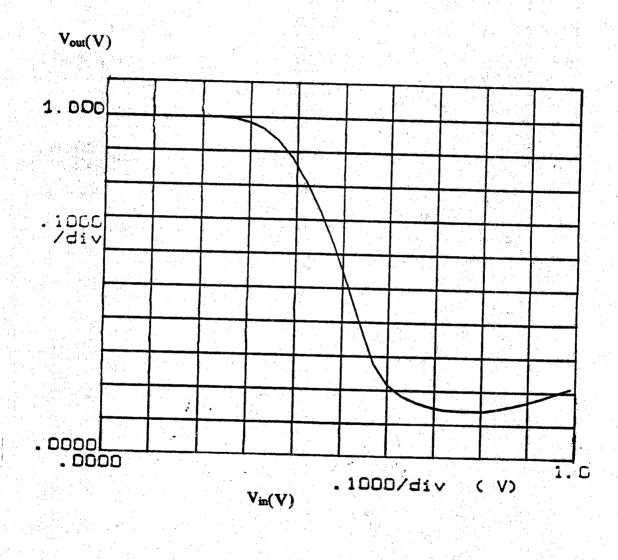

|       | Transfor abare statistic of T/D                                                                  |      |

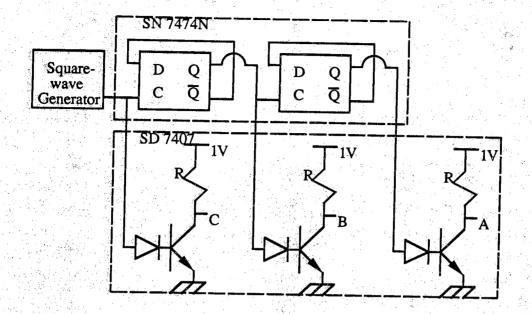

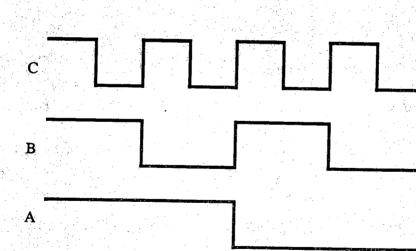

|       | Waveform generator and its output timing sequences                                               |      |

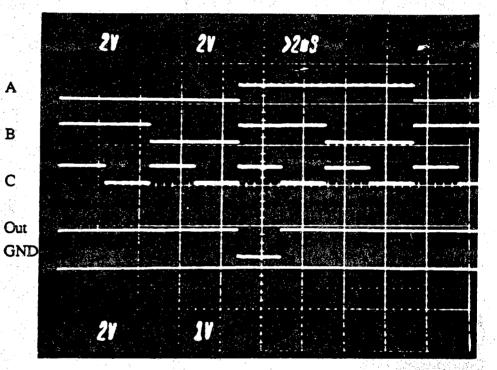

| 5.15. | Input and output of a 3-input MODFET NAND logic gate                                             | 96   |

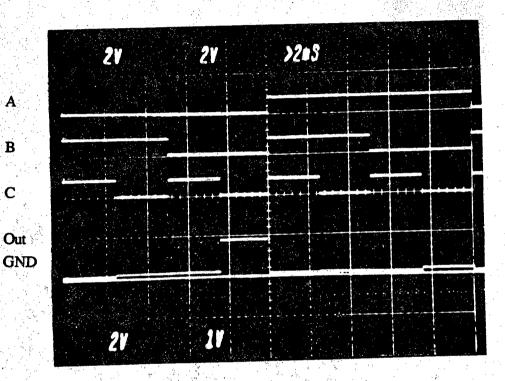

|       | Input and output of a 3-input MODFET NOR logic gate                                              |      |

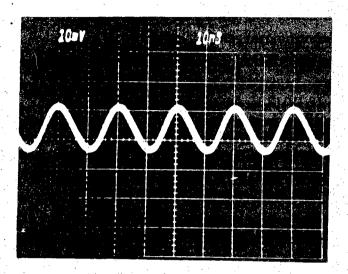

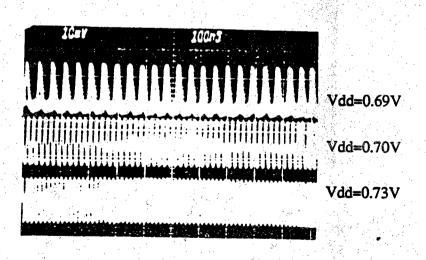

|       | Oscillation waveforms of a MODFET ring oscillator (E-drivers: W/L=40/2,                          |      |

|       | SD=6µm, unetched D-loads: W/L=40/40, SD=40µm)                                                    | 98   |

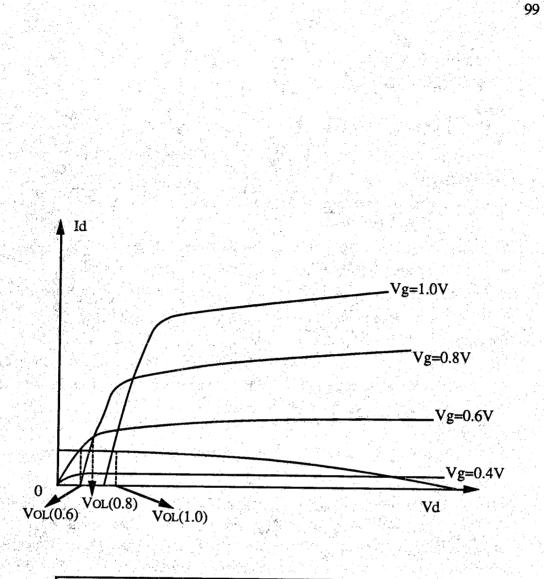

| 5.18. | Effect of E-driver's gate leakage on inverter's output low region                                | 00   |

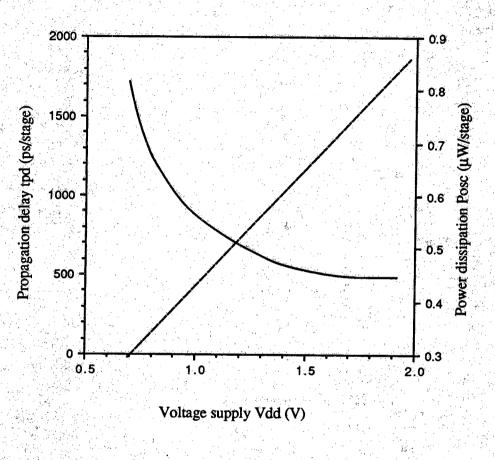

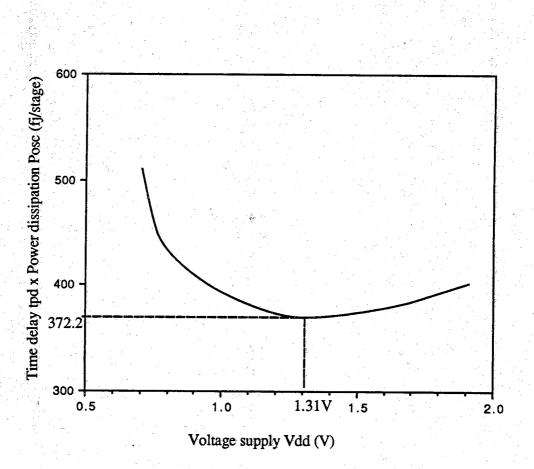

| 5.19. | t <sub>pd</sub> , P <sub>osc</sub> versus V <sub>dd</sub>                                        | 101  |

| 5.20. | $t_{pd}$ , $P_{osc}$ versus $V_{dd}$                                                             | 103  |

vi

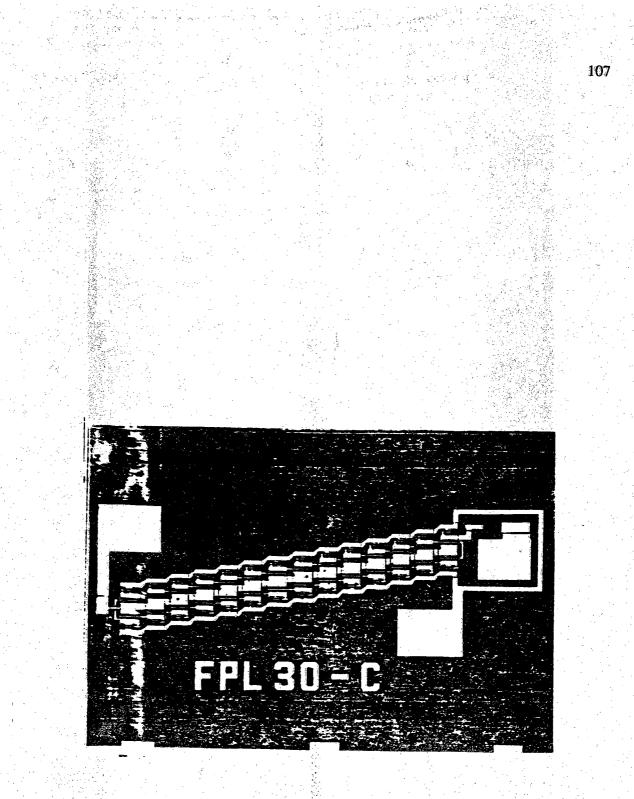

6.1. A ring oscillator designed with the reduced load capacitances ...... 107

#### ABSTRACT

Chen, Kai. MSEE, Purdue University, December 1989. Development of GaAs MODFET DCFL circuits and Process Technology. Major Professor: James A. Cooper, Jr.

The GaAs MODFET device is one of the prominent candidates for very high speed circuit applications. This thesis presents the MODFET DCFL inverter and other logic circuit design and process development. Working circuits of E/D type inverters, three-input NAND and NOR logic gates and ring oscillators are reported.

#### CHAPTER 1.

1

#### INTRODUCTION

For more than three decades, silicon has been the dominant material for the semiconductor industry. But since the late 1950s, gallium arsenide (GaAs) has been considered a semiconductor with the potential to replace silicon because of the following properties of GaAs:

- (1) the very high low-field electron mobility (six times that of Si (1)) which give GaAs the possible high-frequency performance;

- (2) the large bandgap coupled with a short minority carrier lifetime which gives GaAs an advantage over Si in high-radiation environment;

- (3) GaAs substrates grown with very high resistivities can be used as a dielectric medium for high-frequency microwave and millimeter-wave IC.

Since the early 1980's, a new promising transistor made of GaAs has been developed. This device is now known as the MOdulation-Doped Field Effect Transistor (MODFET), which held the record as the fastest logic switching device<sup>(2)</sup> since 1984 until a recently reported faster result made by a GaAs Heterojunction Bipolar Transistor (HBT).<sup>(3)</sup> Several other names such as the Selectively-Doped Heterojunction Transistor (SDHT), the High Electron Mobility Transistor (HEMT), the Two-Dimensional Electron Gas FET (TEGFET), have also been used for MODFET by different groups who have developed MODFET's. Excellent performance has been demonstrated by AlGaAs/GaAs MODFET's.

On the basis of the baseline of MODFET process fabrication technology developed by Mark Whiteside at Purdue, the purpose of this thesis is to present one way to build MODFET Enhancement-mode driver/Depletion-mode load (E/D type) inverters and other simple logic circuits such as three input NAND and NOR gates as well as ring oscillators. More complex MODFET circuits can be built by the design and process technology developed from this research.

#### **1.1 MODFET Review**

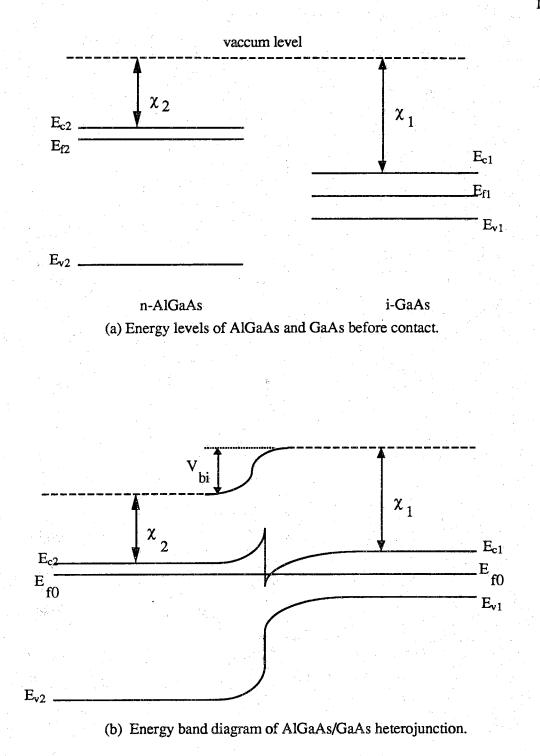

The MODFET device evolved from the work on AlGaAs/GaAs superlattices (thin alternating layers of differing materials sharing the same crystalline lattice) pioneered by Esaki and Tsu at IBM in the late 1960's.<sup>(4)</sup> It was predicted that high mobilities in GaAs could be accomplished if electrons were translated from the highly doped AlGaAs to an adjacent undoped GaAs layer, because of less Coulomb scattering, a process now known as modulation doping. The mobility enhancement behavior was first demonstrated by a single modulation doping heterojunction structure shown in Figure 1.1 in 1978, by Dingle, et al, of AT&T Bell Labs.<sup>(5)</sup> The electron layer confined on the GaAs side of the interface was proven to have a quasi two-dimensional character<sup>(6)</sup> and is referred to as a two-dimensional electron gas (2DEG). In 1980, the first MODFET device, shown in Fig. 1.2, was successfully fabricated by Fujitsu.<sup>(7)</sup> In 1986, the state-of-the-art devices with gate lengths of 0.1 $\mu$ m demonstrated transconductance (g<sub>m</sub>) of 500ms/mm (77K), propagation delay (t<sub>pd</sub>) of 12ps (300K), and maximum current density (J<sub>max</sub>) of 500mA/mm.<sup>(8)</sup>

#### **1.2 MODFET Overview**

From Fig. 1.2, it is clear that because of the higher electron affinity of GaAs, the free electrons ionized from the donors in the wider band gap AlGaAs are transferred and confined in the undoped GaAs layer, forming the 2DEG conducting layer across the whole wafer. The advantage of this 2DEG layer is that the mobility of electrons in this layer is obviously higher than that of the bulk GaAs doped to a comparable level, as illustrated by Figure  $1.3.^{(9)}$

Fig. 1.4 shows a typical cross sectional diagram of a MODFET, which is similar to a Si MOSFET in drain/gate/source structure. The gate, which modulates the 2DEG channel that is normally hundreds of angstroms below the gate, is a metal-semiconductor Schottky barrier junction. The channel is modulated by the gate voltage, which changes the depth of the depletion region of the Schottky barrier into the semiconductor. The device will be shut off when the gate voltage is negative enough so that the depletion region extends into the 2DEG, eliminating the conducting channel between the drain and the source.

Similar to the Si MOSFET, there are two types of MODFET, enhancement-mode and depletion-mode devices. The enhancement-mode is a normally-off device, which means the conducting channel is cut off when the gate is zero biased. This mode is built with a smaller gate-to-channel separation than the zero-bias depletion width of the gate Schottky

Figure 1.1 The heterostructure and its energy band diagram.<sup>(5)</sup>

Figure 1.2. (a) The MODFET heterojunction and, (b) its energy band diagram .(7)

Figure 1.3 The 2DEG and bulk GaAs carrier mobilities vs. temperatures.<sup>(9)</sup>

### (b) MODFET

Figure 1.4 (a) Si MOSFET and, (b) GaAs MODFET.

4

barrier. The other type is the depletion-mode, which is a normally-on device. It is built with a larger gate-to-channel separation than the zero-bias depletion width of the gate Schottky barrier.

Similar to CMOS in silicon, a complementary MODFET technology, that is a p-MODFET coupled with an n-MODFET can be of interest at temperatures below  $77K^{(10)}$ . Below this temperature, the mobility of holes in the two-dimensional hole gas (2DHG), formed in undoped GaAs when the AlGaAs is p-doped, is on the same order as the electron mobility in bulk GaAs.

Recently, new interest has arisen in pseudomorphic MODFET's, in which a mismatched lattice layer of (In,Ga)As is grown between the (Al,Ga)As spacer and the undoped GaAs layer. The 2DEG is thus formed in this newly included (In,Ga)As layer. In 1989, the devices of this structure with 0.2 $\mu$ m gate length exhibited a maximum channel current (I<sub>max</sub>) of 550mA/mm, peak transconductance (g<sub>m</sub>) of 550ms/mm, and peak current gain cutoff frequency (f<sub>T</sub>) of 122 GHZ<sup>(11)</sup>. Transconductance as high as 930ms/mm at 300K was also reported<sup>(12)</sup>.

#### **1.3 MODFET Circuit Implementation**

The universally used MODFET circuit type is the direct coupled FET logic (DCFL, Fig. 1.5 (a)). Its prominent advantages are:

- (1) the basic DCFL circuit has the simpler (minimal number of two transistors) inverter gate than the buffered FET logic (BFL, Figure 1.5 (b));

- (2) E/D type DCFL circuit consumes less power than the depletion driver circuit;

- (3) from circuit design point of view, DCFL is very attractive since its enhancement-mode driver (E-driver) results in a direct-coupled scheme identical to that employed in silicon MOS circuitry.

A big disadvantage of DCFL is that it is very sensitive to the threshold voltage. The control of the threshold voltage across the wafer is a major challenge to build a working MODFET circuit with DCFL. A control of threshold voltage better than 30mV across the wafer is equivalent to a control of gate recess etching of better than  $10\text{\AA}$  --- a very difficult prescription to fill.<sup>(13)</sup> This will be discussed later in the chapter on process development.

The first circuit manifestations of high speed, low power capabilities of MODFET applications, a ring oscillator with 27-stages and DCFL configuration, was reported in 1981 by Fujitsu.<sup>(14)</sup> Since then, impressive improvements have been achieved.<sup>(15)</sup> In 1986, a switching time of 5.8 ps/stage at 77K was achieved with 0.35µm gate length

6

Figure 1.5 (a) Direct-coupled FET logic and, (b) buffered FET logic.

devices<sup>(16)</sup>. This is the fastest FET ring oscillator switching speed ever reported. With the use of MODFET NOR logic gates, a high-frequency divider, another application of DCFL circuits, can be built using D flip-flops. The results of such a circuit with device gate length of 1 μm were first reported by Kiehl et al <sup>(17)</sup> in 1983. A maximum operating frequency of 3.7 GHz at 300 K (30 mW total power with 1.3V bias) and 5.9 GHz at 77K (19mW total power with 1.4V bias) were demonstrated.

The first MODFET static RAM (4-bit) with 1- $\mu$ m gate lengths was built in 1984<sup>(18)</sup>. In the same year, a 4-kbit MODFET SRAM with a typical access time of 2ns was successfully built<sup>(19)</sup>. This was also the fastest access time ever reported for a 4-kbit SRAM up to then. In 1987, a 1-kbit MODFET SRAM with access time of 0.6ns was achieved<sup>(20)</sup>.

In 1986, a self-aligned gate superlattice AlGaAs/n+ GaAs MODFET 5x5-bit parallel multiplier with multiplication times of 1.80ns at 300K (power dissipation of 0.43mW/gate) and 1.08ns at 77K (power dissipation of 0.75mW/gate), using DCFL circuits, was reported<sup>(21)</sup>.

In microwave applications, extremely impressive results have been shown by MODFETs as compared to GaAs MESFETs. Table 1.1 <sup>(8)</sup> shows some data for this

| PARAMETERS                                            | 1    | MODFET |     | MESFET |

|-------------------------------------------------------|------|--------|-----|--------|

| Gate length L (µm)                                    | 0.35 | 0.50   | 1.0 | 1.0    |

| Transconductances gm<br>(ms/mm)                       | 230  | 235    | 140 | 100    |

| Current-gain cutoff<br>frequency f <sub>T</sub> (GHz) | 47   | 35     | 18  | 14     |

| Power-gain cutoff<br>frequency f <sub>max</sub> (GHz) | 75   | 96     | 38  | 30     |

Table 1.1. Comparison of MODFET and MESFET microwave figures.<sup>(8)</sup>

comparison. Contrary to the digital application, the uniformity requirement of threshold voltage is more relaxed since only discrete FET devices are involved in microwave applications. This makes the MODFET a more favorable candidate for microwave circuits.

#### 1.4 Feasibility of MODFET Technology

When evaluating a new device technology, four key factors need to be considered. They are speed and energy consumption, complexity of the process, yield, and the scaling potential into the submicron range.

The intrinsic speed and energy requirements are related to the drift velocity of the electrons in the channel, therefore the MODFET is expected to be the best among the existing FET technologies because of its mobility advantage of the 2DEG (even though this mobility advantage disappears for drift fields above a few hundred  $V/cm^{(22)(23)}$ ), as proven by the actual measurements shown in Fig. 1.6<sup>(8)</sup> and Table 1.2.<sup>(2)</sup>

The complexity of the process and yield of the MODFET technology are still far from mature. Two major problems, quality of the epitaxial layer and threshold voltage uniformity, need to be solved. Some progresses have been made. Defect density below 100 cm<sup>-2</sup> (24) and threshold voltage standard deviation of only 4mV at I<sub>d</sub>=10 $\mu$ A (25) have been reported. At present, the recess etching problem is solved at the expense of increasing process complexity. The method that is widely used is to introduce a self-terminating-layer during MBE growth. Dry ion reactive etch (RIE) is then used to do the etch quite uniformly. More details of this method will be discussed in Chapter 6. Further efforts in these techniques are needed for the economically feasible MODFET technology.

|                          | GaAs   |        |              |     | Si      |     |  |

|--------------------------|--------|--------|--------------|-----|---------|-----|--|

|                          | MODFET | MESFET | Vertical FET | HBT | CMOSFET | BJT |  |

| Speed                    | 1      | 3      | 1            | 2   | 5       | 4   |  |

| Power delay product      | 1      | 2      | 2            | 4   | 5       | 4   |  |

| Lithographic requirement | 2      | 3      | 5            | 1   | 1       | 4   |  |

| Doping control           | 4      | 4      | 4            | 1   | 2       | 1   |  |

| Processing complexity    | 2      | 1      | 4            | 5   | 3       | 5   |  |

| Materials problems       | 4      | 3      | 5            | 4   | 1       | 2   |  |

Table 1.2 Device technology comparison graded 1 (best) through 5.(2)

÷.

Figure 1.6 A comparison of various device technologies.<sup>(8)</sup>

Both vertical and lateral dimensions limit the ultimate extent to which a FET can be scaled down. Vertically, similar to Si MOSFETs whose minimum oxide thicknesses are limited to about 40Å by electron tunneling, the minimum thickness of AlGaAs in the MODFET is approximately 200Å by the same token. Another limit to decreasing the n+AlGaAs layer comes from the requirement that enough donors in the n+AlGaAs, i.e., N2 (doping density in AlGaAs) x t2 (n+AlGaAs thickness), are needed to provide the carrier concentration in the 2DEG,  $n_s$ , as high as possible (usually  $\approx 10^{12}$  cm<sup>-2</sup>). The third limit is due to the necessity of the spacer layer (~50Å to 200Å) between the n+AlGaAs and the undoped GaAs to ensure the high electron mobility in the 2DEG. The lateral scaling of the MODFET depends physically somehow on the vertical dimension. This can be explained by fringing effects as follows: One of the primary reasons to reduce the gate length is to reduce the gate capacitance. As the gate length is decreased to the order of the gate-to-channel separation, the fringing effects become dominant. There will be no further gate capacitance reduction, nor further speed improvement by squeezing the gate length. Another factor to limit the lateral dimension for III-V compound channels is the ballastic transport effect. This comes into play when the gate length is below 0.5µm.

MODFETs, on the basis of the above discussion, clearly indicate a superiority over other FET technologies in terms of achieving operation of ultrafast transistors, lower power dissipation, and lower noise. The continuous improvement in MODFET technology is expected to make it a very bright candidate for superfast circuit applications.

#### **1.5** The Organization of Thesis

In Chapter 2, theory and equations describing MODFETs will be discussed. Chapter 3 will present the circuit and mask design of the MODFET logic gates and circuits. A detailed discussion on development of fabrication process and related experimental results will be given in Chapter 4. Chapter 5 will present the electrical characterizations of all circuits (inverters, three-input NAND, NOR logic gates, and ring oscillators) fabricated. Some recommendations for future work will be suggested in Chapter 6.

#### **CHAPTER 2**

#### THEORY OF MODFET

This chapter discusses theories of MODFETs. The model of calculations presented here is basically developed by Delagebeaudeuf and Linh.<sup>(25)</sup> In this model, the subband splitting and the existence of an undoped AlGaAs spacer layer between the doped AlGaAs and undoped GaAs are considered.

Section 2.1 will discuss the electrostatics of a normal heterojunction. Section 2.2 will consider the 2DEG which is isolated from the effect of the Schottky gate on top of the doped AlGaAs layer, refered to as the isolated regime. Section 2.3 will present a discussion on the charge control regime, where the effect of the Schottky gate on the 2DEG will be considered. Section 2.4 will present the analytical formula of current-voltage relationship of the MODFET. Finally, the modifications of the model under some conditions, such as second order effects, and the correspondence between the MOSFET and MODFET will be discussed in Section 2.5.

#### 2.1 Heterojunction Electrostatics

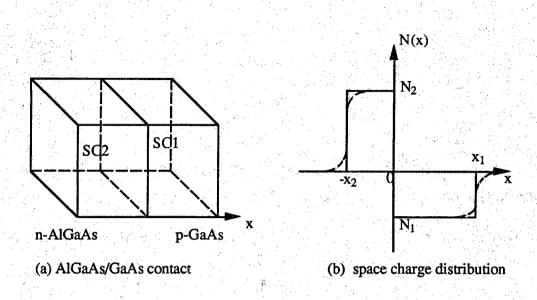

The depletion approximation shown by the solid line in Fig. 2.1 (b) (the actual case is shown by the dashed line) is used to find the relationship between the doping densities,  $N_1$  and  $N_2$ , and depletion widths,  $x_1$  and  $x_2$ , of the heterojunction formed by AlGaAs and GaAs. (Note: subscripts 1 and 2 refer to the quantities in GaAs and AlGaAs, respectively).

The charge neutrality relationship gives

$$qN_1x_1 = qN_2x_2$$

(2.1)

The Poisson equations of both sides are

$$\frac{\partial E_1(x)}{\partial x} = -\frac{qN_1}{\epsilon_1}$$

$$\frac{\partial E_2(x)}{\partial x} = \frac{qN_2}{\epsilon_2}$$

(2.2)

(2.3)

10

(c) electric field

(d) potential

11

Figure 2.1 Heterojunction electrostatics.

Integrating these two equations and using the depletion approximation, we obtain:

$$E_1(x) = \frac{qN_1(x_1-x)}{\varepsilon_1}$$

(2.4)

$$E_{2}(x) = \frac{qN_{2}(x_{2}+x)}{\epsilon_{2}}$$

(2.5)

as shown in Fig. 2.1 (c). Integrating the following equations:

$$V_{1}(x) = \int_{x}^{x} E_{1}(x)dx$$

(2.6)

$$V_{2}(x) = \int_{-\infty}^{x} E_{2}(x)dx$$

(2.7)

where  $V_1$ ,  $V_2$ , the built-in potential,  $V_{bi}$ , and the applied voltage across the heterojunction,  $V_A$ , are defined in Fig. 2.1 (d). These quantities are related as:

$$V(0) = \frac{qN_1x_1^2}{2\epsilon_1} = (V_{bi} - V_A) - \frac{qN_2x_2^2}{2\epsilon_2}$$

(2.8)

Solving (2.8) and (2.1) for  $x_1$  and  $x_2$ , we obtain:

$$\begin{aligned} \mathbf{x}_{1} &= \left[ \frac{2\varepsilon_{1}\varepsilon_{2}N_{2}(\mathbf{V}_{bi} - \mathbf{V}_{A})}{qN_{1}(\varepsilon_{1}N_{1} + \varepsilon_{2}N_{2})} \right]^{\frac{1}{2}} \end{aligned} \tag{2.9}$$

$$\mathbf{x}_{2} &= \left[ \frac{2\varepsilon_{1}\varepsilon_{2}N_{1}(\mathbf{V}_{bi} - \mathbf{V}_{A})}{qN_{2}(\varepsilon_{1}N_{1} + \varepsilon_{2}N_{2})} \right]^{\frac{1}{2}} \tag{2.10}$$

The energy band diagram of AlGaAs and GaAs before and after contact are shown in Fig. 2.2.

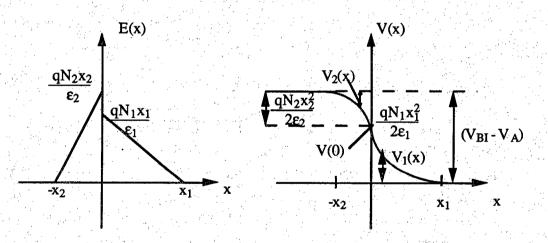

The MODFET heterojunction is much more complicated than what we have discussed above. The appropriate space charge distribution for a MODFET AlGaAs/GaAs heterojunction is illustrated by Fig. 2.3. An extra layer of electrons (the 2DEG) as well as an electrically neutral spacer layer are added to Fig. 2.1 (b).

The very thin 2DEG layer (approximately 100Å) implies the electrons are confined in a potential well with a dimension comparable to the carrier's effective Bohr radius, therefore quantum mechanics must be used to describe the 2DEG's behavior.

#### 2.2 The 2DEG

To solve the Schrodinger equation of an electron in the 2DEG, the potential energy must consist of the contributions from both ionized donors in AlGaAs and other electrons in the 2DEG. A very important assumption is the so-called quasi-constant electric

14

Figure 2.3 Space charge distribution of MODFET.

field E in the potential well or triangular potential. It is deduced from the fact that the electric field E contributed by the other electrons in the 2DEG can be introduced as an average constant value while the linear electric field due to ionized donors can be approximated by a constant when the extremely small segment (which is the thickness of the 2DEG  $\approx 100$ Å, as compared to the whole depletion width of  $\approx 5000$ Å in GaAs) is considered. With this assumption, the self-consistent Schrodinger-Poisson equations can be solved<sup>(27)</sup>(28)(29) and the longitudinal quantized energy is obtained:

$$E_{n}(eV) = \left[\frac{h^{2}}{8\pi^{2}m_{1}^{*}}\right]^{\frac{1}{3}} [3\pi qE]_{3}^{\frac{2}{3}} [n+\frac{3}{4}]^{\frac{2}{3}}$$

(2.11)

where  $m_1^*$  is the longitudinal effective mass, h is the Planck's constant, E is the electric field and n is the quantum number of the energy level.

The 2DEG is characterized by three physical parameters for the equilibrium state: The Fermi-level position in the 2DEG  $E_{f0}$ , the sheet density of 2DEG carriers  $n_s$ , and the electric field at the interface in GaAs  $E_{1i}$ . The relationship between them will be established. The notations are defined by Fig. 2.4 and Fig. 2.5.

## 2.2.1 n<sub>s</sub> versus E<sub>1i</sub>

The Poisson equation of the GaAs depletion region is

$$\frac{dE}{dx} = \left(\frac{q}{\epsilon_1}\right)(n(x)-N_1)$$

(2.12)

Figure 2.4 MODFET structure with defined notations and coordinates.

$$\varepsilon_1 E_{1i} = q(n_s + N_1 x_1) \tag{2.13}$$

Typically,

$$N_1 x_1 \approx 10^{14} \text{cm}^{-3} x_{0.5} \mu \text{m} = 10^{10} \text{cm}^{-2} << n_s \approx 10^{12} \text{cm}^{-2}$$

, thus

$\epsilon_1 E_{1i} \approx qn_s$

Likewise, we have the similar relationship for the undoped AlGaAs:

$$\varepsilon_2 E_{2i} \approx qn_s$$

(2.15)

Substituting (2.14) into (2.11) for GaAs, we have the first two energy levels:  $E_0(eV) \approx \gamma_0(n_s)^{2/3}$

$$E_1(eV) \approx \gamma_1(n_s)^{2/3}$$

(2.16)

The two constants obtained here:

$\begin{aligned} \gamma_0 &= 2.26 \times 10^{-12} \\ \gamma_1 &= 4.0 \times 10^{-12} \end{aligned} \text{(SI)}$

are adjustable. They are experimentally estimated as:(6)(30)(31)

$$\begin{split} \gamma_0 &= 2.50 \times 10^{-12} \\ \gamma_1 &= 3.20 \times 10^{-12} \end{split} \text{(SI)}$$

#### 2.2.2 n<sub>s</sub> vs. E<sub>f</sub>

The density of states  $\Delta n(E)$  for a two dimensional system is

$$\Delta n(E) = \frac{4\pi q m^{-}}{h^2}$$

(2.17)

The density-of-states function is shown by Fig. 2.6. Using Fermi-Dirac statistics, we get:

$$n_{s} = \Delta n(E) \int_{E_{0}}^{E_{1}} \frac{dE}{1 + e\frac{(E - E_{\ell})}{kT}} + 2\Delta n(E) \int_{E_{1}}^{+\infty} \frac{dE}{1 + e\frac{(E - E_{\ell})}{kT}}$$

$$= \frac{\Delta n(E)kT}{q} \ln(1 + e\frac{(E_{\Gamma} - E_{0})}{kT})(1 + e\frac{(E_{\Gamma} - E_{1})}{kT})$$

(2.18)

This expression applies to a two-level system. It is also a valid approximation to the Nlevel system because typically only the first 2 levels are significantly filled.

More practically, we desire to establish a function in terms of donor density in the AlGaAs  $N_2$  and the thickness of the undoped AlGaAs spacer layer d.

(2.14)

Figure 2.6 Density-of-states function vs. energy En.

### 2.2.3 $n_s = f(d, N_2)$

The Poisson equation for the depletion region in AlGaAs is  $\frac{d^2 V_2}{dx^2} = -\frac{qN_2(x)}{\epsilon_2}$ (2.19)

where  $V_2$  is the potential drop in AlGaAs from the AlGaAs/GaAs interface and  $N_2$  is the donor density in AlGaAs, with the boundary conditions:

$$V_{2}(x=0) = 0$$

$$\left[\frac{dV_{2}}{dx}\right]_{x=-x_{2}} = -E_{2}(x=-x_{2}) = 0$$

$$\left(\frac{dV_{2}}{dx}\right)_{x=0} = -E_{2i}$$

(2.20)

and

$N_2(x)=0, -d < x < 0$  $N_2(x)=N_2, -x_2 < x < -d$  (2.21) where  $x_2$  is the depletion width of doped n+ AlGaAs plus the thickness of the spacer layer and is determined by (2.10). Solving these equations, we find the band bending in AlGaAs, V<sub>20</sub>, as defined in Fig. 2.5:

$$\varepsilon_2 E_{i2} = q N_2(x_2 - d) \tag{2.22}$$

$$V_{20} = \frac{qN_2(x_2^2 - d^2)}{2\varepsilon_2}$$

(2.23)

Combining (2.22) and (2.23) gives:

$$\varepsilon_2 E_{2i} = \sqrt{2q} \varepsilon_2 N_2 V_{20} + q^2 N_2^2 d^2 - q N_2 d$$

(2.24)

From the energy band diagram of Fig. 2.5 we have:

$$qV_{20} = \Delta E_c - E_{f0} + E_{c1}(0) - \delta_2$$

(2.25)

Additionally, with the interface states neglected, Gauss's Law can be applied to get  $\epsilon_2 E_{2i} \approx \epsilon_1 E_{1i} = qn_s$  (2.26)

The final expression is then obtained from (2.18), (2.24) and (2.26):  $\sqrt{2q\epsilon_2N_2V_{20}+q^2N_2^2d^2}-qN_2d=qn_s$

$$= \Delta n(E)kTln(1 + e^{\frac{(E_{t0}-E_{c1}(0)-E_{0})}{kT}})(1 + e^{\frac{(E_{t0}-E_{c2}(0)-E_{1})}{kT}})$$

(2.27)

Here,  $E_0$  (or  $E_1$ ) are energy difference between the ground level (or the first level) and the valence energy band at x=0, i.e.,  $E_{c1}(0)$ . This equation can only be solved numerically. The procedure is to pick an arbitrary low value for  $E_{f0}$ - $E_{c1}(0)$  to determine  $n_s$  by (2.24), (2.25) and (2.26).  $E_0$  and  $E_1$  are computed by (2.16) and are then substituted back to (2.18) to calculate a new  $n_s$ . Iterate this procedure until the two  $n_s$ 's calculated above are equal.

Given some basic constants:

$N_c=2(2\pi m_n^*kT/h^2)^{3/2}=9.15 \times 10^{17} cm^{-3},$  $\delta_2=(E_c-E_f)_{AlGaAs}=kT \times ln(N_c/N_d) (eV),$

$$\Delta E_{c} = 1.06 x (V) = 0.32 eV$$

where the mole fraction of Al, x, is assumped to be 0.3, and

kT=0.0259eV (300K),

$m_n^* = 0.11 m_0$

$\epsilon_2 = 1.08 \times 10^{-12}$  F/cm,

$\Delta n(E) = 2.75 \times 10^{13} \text{ V}^{-1} \text{ cm}^{-2}$

the carrier concentration can be calculated in terms of spacer thickness d and doping density in AlGaAs, N<sub>2</sub>, as shown in Table  $2.1^{(33)}$  and Fig.  $2.7.^{(33)}$

### 2.3 Schottky Gate Charge Control Regime

In this section, the effects of the Schottky gate on the 2DEG will be investigated. Suppose the AlGaAs layer is thin enough or the gate voltage is negative enough that the AlGaAs layer is completely depleted. The band diagram of the influence of the Schottky

| d (Å) | AlGaAs doping density N <sub>2</sub> (cm <sup>-3</sup> ) |                       |                       |  |  |  |

|-------|----------------------------------------------------------|-----------------------|-----------------------|--|--|--|

|       | 1x10 <sup>17</sup>                                       | 5x10 <sup>17</sup>    | 1x10 <sup>18</sup>    |  |  |  |

| 50    | 4.79x10 <sup>11</sup>                                    | 9.00x10 <sup>11</sup> | 1.13x10 <sup>12</sup> |  |  |  |

| 100   | $4.44 \times 10^{11}$                                    | 7.73x10 <sup>11</sup> | 9.27x1011             |  |  |  |

| 150   | $4.12 \times 10^{11}$                                    | 6.73x10 <sup>11</sup> | 7.84x10 <sup>11</sup> |  |  |  |

| 200   | 3.83x10 <sup>11</sup>                                    | 5.95x10 <sup>11</sup> | 6.77x10 <sup>11</sup> |  |  |  |

| Table 2.1 | The 2DEG | carrier con | centration | n <sub>e</sub> ( | $(cm^{-2})$ | ) (3 | 33) | ) |

|-----------|----------|-------------|------------|------------------|-------------|------|-----|---|

|           |          |             |            |                  |             |      |     |   |

gate is shown in Fig. 2.8. The Poisson equation is then:  $N_{ON}(x)$

$$\frac{d^2 V}{dx^2} = -\frac{q N_2(x)}{\epsilon_2}$$

(2.28)

with the conditions

$$N_2(x)=0, -d < x < 0$$

$N_2(x)=N_2, -t_2 < x < -d$  (2.29)

and the potential reference point is taken at the interface:  $V_2(x=0)=0$ , then

$$V_{2}(-t_{2}) = \frac{qN_{2}(t_{2}-d)^{2}}{2\varepsilon_{2}} - E_{2i}t_{2} = V_{p2} - E_{2i}t_{2}$$

(2.30)

where t<sub>2</sub> is the thickness of the entire doped and undoped AlGaAs layer and

$$V_{p2} = \frac{qN_2(t_2 - d)^2}{2\epsilon_2}$$

(2.31)

From Fig. 2.8, we also have the relationship

$$qV_2(-t_2) = \Phi_{BN} - qV_g + E_f - E_{c1}(0) - \Delta E_c$$

(2.32)

where  $\Phi_{BN}$  is the metal-semiconductor work function difference. Substituting (2.32) into (2.30), we get

$$\varepsilon_{2}E_{2i} = \frac{\varepsilon_{2}(V_{p2}+V_{g}+\frac{-E_{f}-\Phi_{BN}+E_{c1}(0)+\Delta E_{c}}{q})}{t_{2}}$$

(2.33)

From (2.26) and (2.33), we have:

30.

Figure 2.7 2DEG carrier concentration vs. AlGaAs doping density for various d.<sup>(33)</sup>

Figure 2.8 The energy band diagram for the charge control regime.

20

$$Q_{s} = -qn_{s} = -C_{2}(V_{p2} + V_{g} + \frac{-\Phi_{BN} - E_{f} + E_{c1}(0) + \Delta E_{c}}{q})$$

(2.34)

where  $C_2 = \varepsilon_2/t_2$  can be considered as the capacitance of AlGaAs. Since  $E_f \cdot E_c(0)$  is always very small compared with the other terms (its dependence on the gate voltage will be discussed later), (2.34) can be reduced to

$$Q_s \approx -C_2(V_g - V_{th}) \tag{2.35}$$

$$V_{\rm th} = \frac{\Phi_{\rm BN} - \Delta E_{\rm c}}{q} - V_{\rm p2}$$

Obviously  $Q_s=0$ , i.e., the 2DEG is eliminated when  $V_g=V_{th}$ , therefore the  $V_{th}$  is defined as the threshold voltage.

By examination of above equations, several comments or conclusions can be made here.

#### 2.3.1 The effect of interface states

If the interface states  $Q_i$  are taken into account, the threshold voltage  $V_{th}$  of (2.35) would be shifted as

$$V_{\rm th} = \frac{\Phi_{\rm BN} - \Delta E_{\rm c}}{q} - V_{\rm p2} - \frac{Q_{\rm i}}{C_2}$$

(2.37)

#### 2.3.2 Control of V<sub>th</sub>

For a given device the terms  $\Phi_{BN}$  and  $\Delta E_c$  in (2.36) are fixed, therefore the threshold voltage  $V_{th}$  is controlled by the term  $V_{p2}=qN_2(t_2-d)^2/2\epsilon_2$ .  $V_{p2}$  can be changed by changing either the doping of AlGaAs, N<sub>2</sub>, or the thickness of the doped AlGaAs layer,  $t_2$ -d. A higher doping N<sub>2</sub> is usually used to provide a high carrier concentration (Note through (2.27) that the maximum 2DEG density depends on N<sub>2</sub>). Thus, the thickness of the AlGaAs is most often used to control the V<sub>th</sub>.

If the thickness of the doped AlGaAs layer,  $t_2$ , is large enough so  $V_{th}$  is a large negative number (see (2.31) and (2.37)), then the  $Q_s$  of the 2DEG is not zero, and a reverse bias voltage on the Schottky gate is needed to shut off the channel of the device. The device is then "depletion-mode". When the thickness  $t_2$  is decreased,  $V_{p2}$  is decreased and  $V_{th}$  becomes less negative. At a point where  $t_2$  is decreased to such a value that  $V_{th}=0$ , from (2.35) a forward bias gate voltage is now needed to create a 2DEG channel to turn on the device. After this point the device becomes "enhancement-mode".

Physically the transition that from the isolated regime to the charge control regime occurs when the gate-to-channel separation is equal to the depletion region width contributed by both Schottky gate and AlGaAs/GaAs heterojunction. Alternatively, for a given thickness  $t_2$ , the transition gate voltage  $V_{gtr}$  between the two regimes can be found by equating (2.24) to (2.33),

$$V_{gtr} = \frac{\Phi_{BN} - \delta_2}{q} \left[ \sqrt{\frac{qN_2 t_2^2}{2\varepsilon_2}} - \sqrt{\frac{\Delta E_c - \delta_2 - E_{f0} + E_{c1}(0)}{q} + \frac{qN_2 d^2}{2\varepsilon_2}} \right]^2$$

(2.38)

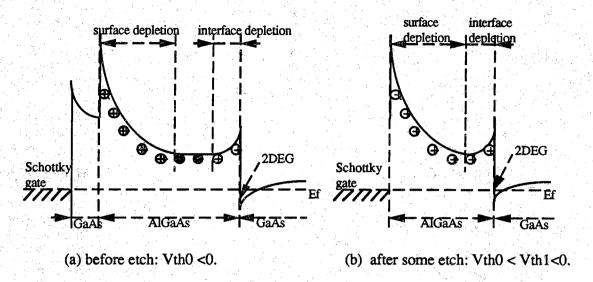

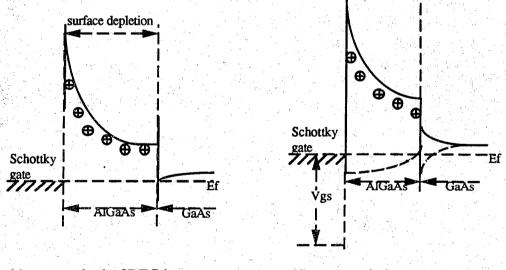

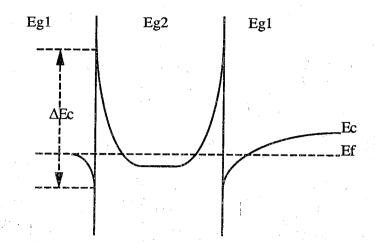

A decreased thickness of the doped AlGaAs layer will lead to an increased threshold voltage. This also makes sense from the band diagram point of view. Fig. 2.9 (a) shows that before etch, the n+AlGaAs layer is partially depleted by surface (the outside face for metal contact) and interface (between AlGaAs and undoped GaAs) depletion. The device now is depletion-mode,  $V_{th} < 0$ , because it is conducting when  $V_g=0$ . After some of n+AlGaAs layer is etched away, the total number of donors is decreased so that more neutral donors are ionized. After all donors are ionized when the etch continues, the density of carriers in the 2DEG will begin to decrease. The interface bands of GaAs will become more flat (in Fig. 2.9 (b)) than in Fig. 2.9 (a). The device now is still depletionmode because a 2DEG is still there, but V<sub>th</sub> has become less negative. As the etch is continued further, the band bending in the GaAs becomes more and more flat until it touches the interface Fermi level (Fig. 2.9 (c)). At this point, any small change in gate bias will turn the transistor on or off, by positive or negative gate voltage, respectively, therefore V<sub>th</sub>=0 now. The transistor becomes enhancement-mode from this point on. Further etch after this will cause the space charge region in the AlGaAs to extend into the GaAs layer until the 2DEG disappears, as shown in Fig. 2.9 (d).  $V_{th} > 0$  now because the transistor will be turned on only when a positive  $V_{gs}$  (>  $V_{th}$ ) is applied, as shown by the dashed line in Fig. 2.9 (d).

#### 2.3.3 Depletion-mode and enhancement-mode Device

For the depletion-mode device, the optimal AlGaAs thickness  $t_2$  is chosen such that  $V_{gtr}=0$ :

$$t_{2op} = \sqrt{\frac{2\varepsilon_2(\Phi_{BN}-\delta_2)}{q^2N_2}} + \sqrt{\frac{2\varepsilon_2}{q^2N_2}}(\Delta E_c - \delta_2 - E_{f0} + E_{c1}(0)) + d^2}$$

(2.39)

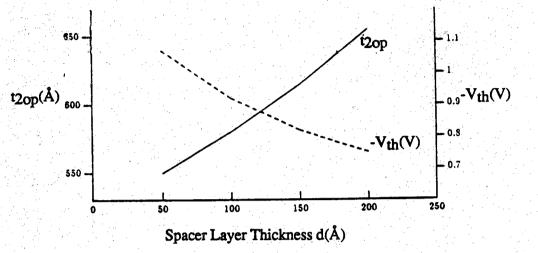

This  $t_{20p}$  enables the 2DEG be affected by any negative gate voltage. Given the Schottky barrier height  $\Phi_{BN=1.106eV}(34)$  and typical AlGaAs doping N<sub>2</sub>=1x10<sup>18</sup>cm<sup>-3</sup>, for various spacer layer thickness d, the  $t_{20p}$  and corresponding threshold voltage V<sub>th</sub> for the depletion-mode device can be calculated by (2.39) and (2.36), respectively, as shown

(c) more etch: the 2DEG is about to dissappear, Vth2 = 0.

(d) more etch than (c): E-mode device formed, Vth3 > 0.

Figure 2.9 The energy-band diagrams with regard to etching.

(b) t<sub>2</sub> vs. Vth for E-mode MODFET with  $N_2=10^{18}$  cm<sup>-3</sup>, d=200Å.

Figure 2.10 N<sub>2</sub> vs. threshold voltages for (a) optimal D-mode and, (b) E-mode MODFET's.

in Fig. 2.10 (a). A thicker  $t_2$  will produce a more negative V<sub>th</sub> because part of the gate voltage must be used to deplete the extra thickness of AlGaAs,  $t_2$ - $t_{2op}$ .

Similarly, for the enhancement-mode device, given spacer layer thickness d and AlGaAs doping N<sub>2</sub>, a series of V<sub>th</sub> vs. the various  $t_2$  can be calculated from (2.31) and (2.36). The result is illustrated in Fig. 2.10 (b).

A final comment is about the choice of the spacer layer thickness, d. The trade-off is that a thinner d will lead to a higher 2DEG carrier concentration  $n_s$  but a lower mobility  $\mu$  because of closer physical separation between the ionized impurity centers in AlGaAs and the carriers in 2DEG.

#### 2.4 DC Current-Voltage Model of MODFET

The coordinate system used for this analysis is illustrated by Fig. 2.4. When a voltage  $V_d$  is applied between the grounded source and the positive drain, the effective voltage for charge control by the gate at any point of the channel,  $V_{eff}(z)$ , can be expressed in terms of the gate voltage  $V_g$  and the potential at the corresponding point in the channel  $V_c(z)$ :

$$V_{\text{eff}}(z) = V_{\text{g}} - V_{\text{c}}(z)$$

(2.40)

so (2.35) becomes

$$Q_{s}(z) \approx -C_{2}(V_{g}-V_{c}(z)-V_{th})$$

(2.41)

The current in the channel at any point x is given by