# Purdue University Purdue e-Pubs

| Department of Electrical and Computer |  |

|---------------------------------------|--|

| Engineering Technical Reports         |  |

Department of Electrical and Computer Engineering

6-1-1989

# Detailed Modeling and Reliability Analysis of Fault-Tolerant Processor Arrays

Noe Lopez-Benitez Purdue University

Jose A. B. Fortes *Purdue University*

Follow this and additional works at: https://docs.lib.purdue.edu/ecetr

Lopez-Benitez, Noe and Fortes, Jose A. B., "Detailed Modeling and Reliability Analysis of Fault-Tolerant Processor Arrays" (1989). Department of Electrical and Computer Engineering Technical Reports. Paper 662. https://docs.lib.purdue.edu/ecetr/662

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

Detailed Modeling and Reliability Analysis of Fault-Tolerant Processor Arrays

Noe Lopez-Benitez Jose A. B. Fortes

TR-EE 89-31 June, 1989

School of Electrical Engineering Purdue University West Lafayette, Indiana 47907

# DETAILED MODELING AND RELIABILITY ANALYSIS OF FAULT-TOLERANT PROCESSOR ARRAYS

Noe Lopez-Benitez and Jose A. B. Fortes<sup>†</sup>

School of Electrical Engineering Purdue University West Lafayette, IN 47907

#### ABSTRACT

Recent advances in VLSI/WSI technology have led to the design of processor arrays with a large number of processing elements confined in small areas. The use of redundancy to increase fault-tolerance has the effect of reducing the ratio of area dedicated to processing elements over the area occupied by other resources in the array. The assumption of fault-free hardware support (switches, buses, interconnection links, etc.,), leads at best to conservative reliability estimates. However, detailed modeling entails not only an explosive growth in the model state space but also a difficult model construction process. To address the latter problem, a systematic method to construct Markov models for the reliability evaluation of processor arrays is proposed. This method is based on the premise that the fault behavior of a processor array can be modeled by a Stochastic Petri Net (SPN). However, in order to obtain a more compact representation, a set of attributes is associated with each transition in the Petri net model. This representation is referred to as a Modified Stochastic Petri Net (MSPN) model. A MSPN allows the construction of the corresponding Markov model as the reachability graph is being generated. The Markov model generated can include the effect of failures of several different components of the array as well as the effect of a peculiar distribution of faults when the reconfiguration occurs. Specific reconfiguration schemes such as Successive Row Elimination (SRE), Alternate Row-Column Elimination (ARCE) and Direct Reconfiguration (DR), are analyzed

<sup>&</sup>lt;sup>†</sup> This research was supported in part by the National Science Foundation under Grant DC1-8419745 and in part by the Innovative Science and Technology Office of the Strategic Defense Initiative Organization and was administered through the Office of Naval Research under contracts No. 00014-85-k-0588 and No. 00014-88-k-0723.

in detail. Randomization techniques are used to solve the inherently large models that can be generated via a MSPN representation. A model reduction technique based on the discrimination of states with low mean holding times is discussed. Finally, an analysis of hierarchical structures formed with variations of the schemes analyzed, is presented. The results reported in this work were obtained using MGRE (Model Generation and Reliability Evaluator) which is a software package designed to analyze fault-tolerant processor arrays for which a MSPN representation is given.

# CHAPTER I INTRODUCTION

# 1.1. Objectives

Recent advances in VLSI/WSI technology have led to the design of processor arrays with a large number of processing elements (PE's) confined in small areas. At wafer level, the elimination of interchip connections and faster signal propagation due to shorter interconnections between PE's results in higher processing speed. However, large densities and hardware complexity increase the likelihood of faults during the fabrication process. In addition, a large number of active elements involved in a single computation cycle, increases the possibility of failures at any time during the operational life of the array. Increased likelihood of faults during the fabrication process results in low production yield whereas large number of active elements involved in the functional operation of the array, decreases reliability. Research efforts have been directed not only to yield improvement but also to increase fault-tolerance [KoB84,KoP87]. To increase both yield and reliability, several reconfiguration algorithms which use the available redundancy in the array have been proposed. In addition, fault detection and recovery upon the occurrence of faults is required during the fabrication process or the functional operation of the array. Because of their susceptibility to faults and the added hardware complexity on the overall array, components other than processing elements become very important in the analysis

of fault-tolerant processor arrays. However, there is a tendency to limit the reliability analysis of processor arrays to failures of processing elements only [RaA84]. The assumption of fault-free support hardware in the form of switches, buses, interconnection links, etc., for the analysis of fault-tolerant processor arrays leads at best to conservative reliability estimations. The need to construct more general models is recognized in the mathematical framework derived by Koren et al [KoB84,KoP87,KoP86] to evaluate yield improvement and performance-related measures of different array architectures.

A number of analytic models and methods for the reliability analysis of fault tolerant computer systems currently exists [Tri85,GeT83,HiE83]. Combinatorial analysis and Markov models are the most common methods used to develop analytical models for the reliability analysis of fault tolerant systems. In the case of combinatorial methods, if the system can be divided into several modules, they are assumed independent (i.e. no faults or repair dependencies exist) and reliability estimations can be derived using fault trees and series-parallel structures for which definite mathematical tools exist [Tri82]. Markov models on the other hand offer the alternative of analyzing systems with interdependent components. A fault-tolerant processor array can be considered a system with interdependent components in the sense that the failure of one component may or may not affect other components of the array. The manner in which the components of the array are interdependent varies with the topology implemented and the reconfiguration algorithm that takes place when a faulty component is detected.

In this work the problem of evaluating the reliability of processor arrays using Markov models is addressed. However, a detailed modeling that takes into consideration failure interdependencies of several components, entails not only an

4

explosive growth in the model state space but also a difficult model construction process. To address the latter problem, a systematic method to construct Markov models for the reliability evaluation of processor arrays is proposed. This method is based on the premise that the fault behavior of a processor array can be modeled by a Stochastic Petri Net (SPN). In order to achieve a complete mapping from places and transitions in an SPN-like representation of small size to states and transition rates in the Markov model, a modified version of SPN's is proposed. However a more compact representation is obtained by associating a set of attributes with each transition in the Petri net. This representation is referred to as a Modified Stochastic Petri Net (MSPN) model. The set of attributes includes a probability function such that the effect of faulty spares in the reconfiguration algorithm is captured each a time a configuration change occurs. This distribution includes the probabilities of survival given that a number of components required by the reconfiguration process is faulty. Depending on the type of component and the reconfiguration scheme, probabilities of survival can be determined using closed form expressions or via simulation. Reconfiguration schemes such as Successive Row Elimination (SRE) Alternate Row-Column Elimination (ARCE) [FoR85] and Direct Reconfiguration (DR) [SaS86a], [SaS86b] are analyzed in detail using MSPN's.

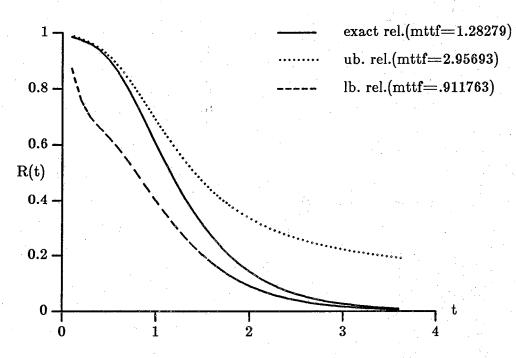

Once the Petri net model and the corresponding reachability graph have been obtained, all the information required to build the transition matrix of the corresponding Markov chain is available. At this stage, figures of merit such as reliability, performability, etc., can be readily addressed. Reliability evaluation tools such as ARIES [MaA82] and SHARPE [ShT86] can be used to evaluate the models developed here. However the use of these packages is limited to the evaluation of models with a relatively low number of states. To circumvent the problems involved in the numerical evaluation of large models, a software implementation based on the randomization procedure, has been used to generate the reliability results reported in this work. A software package (MGRE) has been developed [Lop89] to analyze fault-tolerant processor arrays based on the approach presented in this report. By the execution of appropriate commands, MGRE can generate Markov models, evaluate reliability and MTTF given the size of the processor array and a set of failure rates.

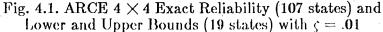

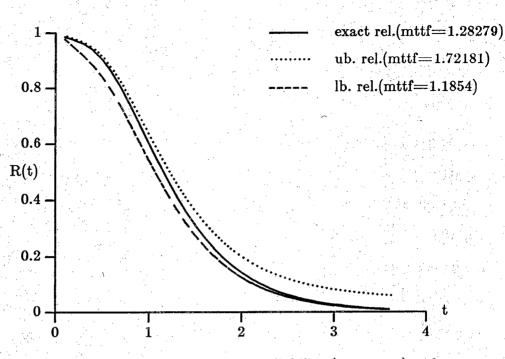

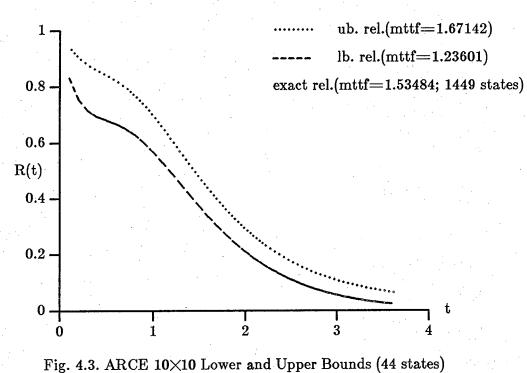

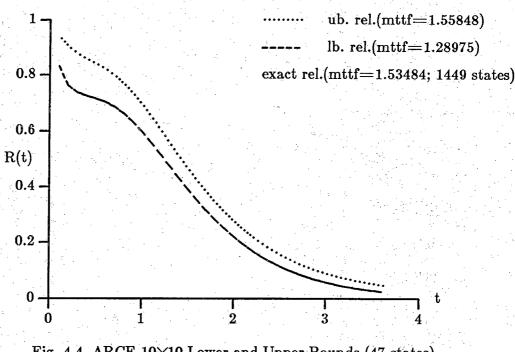

#### 1.2. Overview

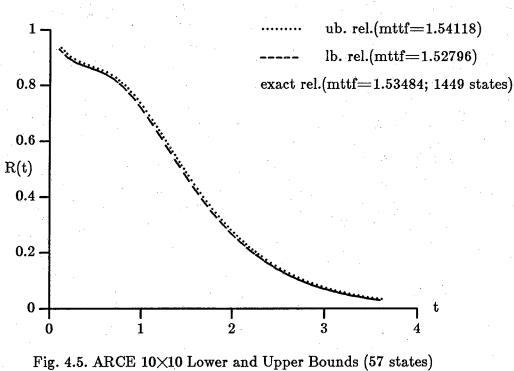

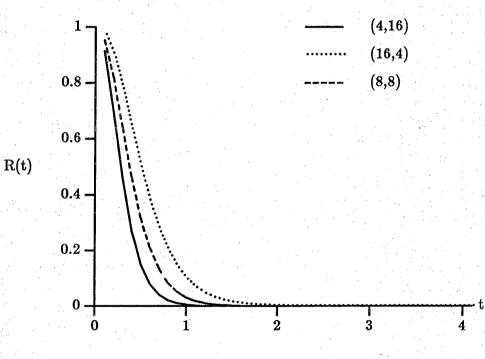

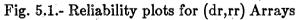

In the second chapter the main topic of this report is developed. A modified version of stochastic Petri nets is presented and its application is illustrated by the generation of a model corresponding to the SRE reconfiguration scheme. In the third chapter the ARCE and DR reconfiguration schemes are analyzed in detail. Also, expressions required to calculate probabilities of survival in the presence of faults, are derived. Results concerning the state space and reliability analysis of these schemes are also reported. The fourth chapter discusses software algorithms for the numerical evaluation of large Markov models. In chapter five, several hierarchical configurations are compared with respect to their MTTF and reliability performance.

# CHAPTER II

# MODIFIED STOCHASTIC PETRI NETS

#### 2.1. Introduction

As is the case with many systems, Markov models can be used to evaluate the reliability of processor arrays. However, reliability estimations are mostly based only on the failures of processing elements [RaA84]. Components other than processing elements become very important in the analysis of fault-tolerant processor arrays because of their susceptibility to faults and the added hardware complexity of the overall array. This fact has played an important role in the derivation of a mathematical framework developed by Koren et al [KoB84,KoP86,KoP87] to evaluate yield improvement and performance-related measures of different array architectures. However, a detailed modeling of faulttolerant processor arrays, which explicitly takes into consideration the failure statistics of each component as well as their possible interdependencies, entails not only an explosive growth in the model state space but also a difficult model construction process. Therefore, in this chapter the latter problem is emphasized and a systematic method to construct Markov models to evaluate the reliability of processor arrays is discussed. This method is based on the premise that the fault behavior of a processor array can be modeled by a Stochastic Petri Net (SPN) However, in order to obtain a more compact representation, a set of attributes is associated with each transition in the Petri net model. The resulting model is referred to as a Modified Stochastic Petri Net (MSPN) representation. An MSPN representation allows the construction of the corresponding Markov model as the generation of the reachability graph takes place. Included in the set of attributes associated with each transition in a MSPN, is a discrete probability distribution such that the effect of faulty spares in the reconfiguration algorithm is captured each time a configuration change occurs. This distribution includes the probabilities of survival given that a number of components required by the reconfiguration process are faulty. Depending on the type of component and the reconfiguration scheme, probabilities of survival are determined using simulation or closed form expressions.

Once the Petri net model and the corresponding reachability graph have been obtained, all the information required to build the transition matrix of the corresponding Markov chain is available. At this stage, figures of merit such as reliability, performability, etc., can be readily addressed. Reliability evaluation tools such as ARIES [MaA82] and SHARPE [ShT86] can be used to evaluate the models developed here.

The second section of this chapter discusses some basic notation and concepts related to array configurations. An SPN representation is derived using as an example the SRE reconfiguration scheme. The third section of this chapter discusses Modified Stochastic Petri Nets (MSPN's) and an MSPN representation for the SRE scheme is derived; also a procedure to construct MSPN's is outlined. In the fourth section, the correspondence between markings in an MSPN representation and the states in a Markov chain is described; a procedure to construct the reachability graph of a given MSPN is outlined.

8

#### 2.2. Concepts and Notation

In this section a representation of array configurations using a SPN is discussed. For illustration, examples using the SRE reconfiguration scheme are presented.

## **2.2.1.** Array Configurations

To analyze a fault-tolerant array architecture with k types of components, the configuration of an array is represented as a k-tuple:

$$C_i = (\eta_{1i}, \eta_{2i}, \cdots, \eta_{ki})$$

$i = 0, 1, \cdots, |C|$

where  $\eta_{li}$  denotes the number of elements of component type l and C is the set of all possible configurations of the array. Examples of component types include processing elements, links, switches, spare links and spare processing elements. The occurrence of faults and the application of the reconfiguration algorithm define a sequence of configurations that begins with  $C_0$  as the *initial configuration*; any other configuration can correspond to the failure state or an operational state of the array. The latter will be referred to as an *operational configuration*.

Upon detection of a faulty component, the reconfiguration algorithm may not send the array to an operational configuration if any of the following happens:

1) The reconfiguration circuitry failed. This possibility can be considered through a coverage factor (denoted by c) defined as the probability of successful reconfiguration given that a fault has occurred [BoC69]. This is a measure of the probability of successful operation of all circuitry related to fault detection, isolation and reconfiguration. The coverage factor is assumed constant and it will be associated with failures of active components only. 2) Redundancy is exhausted. This information can be inferred from  $C_i$ .

3) The presence of faults in non-active components (redundancy) hinders a successful reconfiguration. Redundant components are present in  $C_i$  as spare processing elements, spare switches, spare links, spare buses, etc. Some of these components become active in the new configuration.

In a given configuration with a number of faulty components, successful reconfiguration will depend not only on the type of faults but also on their distribution in the array. Thus, the probability of correct reconfiguration in the presence of faults is referred to as the *probability of survival* [SaS86b]. Because the reconfiguration algorithm may choose one of several new configurations (including a non-operational one), a probability is assigned to each possible new configuration. The probability of survival corresponds to the sum of probabilities assigned to new operational configurations.

#### 2.2.2. SPN Representation

While Markov models provide an analytical basis to derive reliability estimations of complex systems, their inherently large state space is difficult to construct and cannot be directly described in a convenient manner. On the other hand, SPN's provide a succinct representation of the system and support a mechanized construction of the Markov model, because markings in an SPN correspond bijectively to states in the Markov chain [Mol82]. In the case of fault-tolerant processor arrays, an operational configuration corresponds to an operational state in the Markov chain; thus, to derive all possible operational configurations of the array, a marking in the SPN must correspond to an operational configuration of the array. Each place  $p_i$  identifies components of type *i* and, at a given marking  $M_q$ , the number of tokens  $m_{iq}$  corresponds to  $\eta_{iq}$  which is the number of components of type *i*. Two or more distinct component types may identify the same physical component; for example, a physical spare is a component of the type "active spare" when it is used to replace a faulty part and it is a component of the type "non-active spare" otherwise.

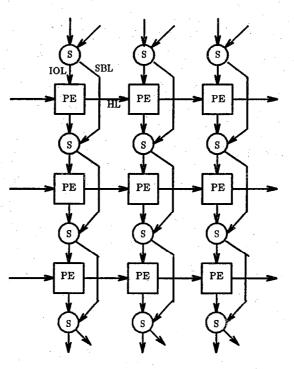

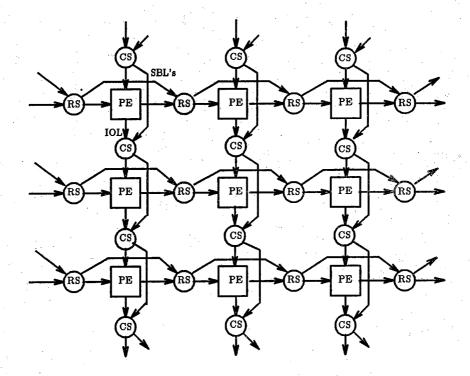

Consider for example an  $n \times n$  array that supports the Successive-Row-Elimination (SRE) reconfiguration scheme with a layout as in Figure 2.1. The SRE scheme as presented in [FoR85], is based on the successive elimination of rows. Row elimination is done by using switches (S's) and redundant links to bypass all processing elements (PE's) of any row containing at least one faulty PE or at least one faulty horizontal link (HL) or at least one faulty input/output link (I0L); spare bypass links (SBL's) become active bypass links (BL's) which are used to bypass faulty rows; the array fails when rows are exhausted or if either one active bypass link or a switch fails. A marking q is described as:

$$M_q = (\#PE, \#IOL, \#S, \#BL, \#HL, \#SBL) = (m_{1q}, m_{2q}, m_{3q}, \ldots, m_{6q})$$

where the symbol "#" is used to denote "number of".

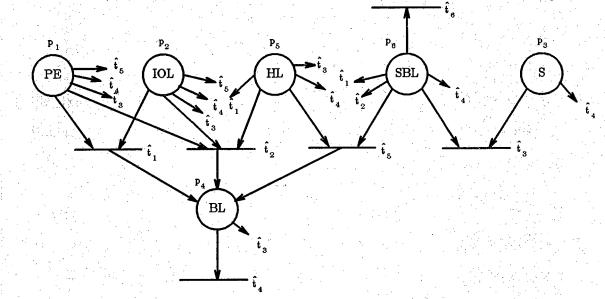

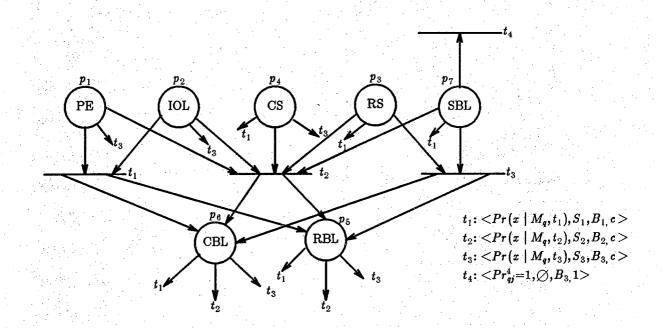

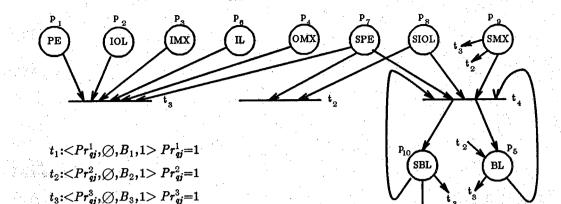

A possible SPN representation is given in Figure 2.2. The firing of  $\hat{t}_1$ , represents the occurrence of a fault in a PE, a fault in an IOL is represented by the firing of  $\hat{t}_2$  and so on. In general, the firing of  $\hat{t}_i$  represents a fault occurrence in a component of type i where  $1 \le i \le k$  and k is the number of places and transitions. In SRE, component types 1 through 6 correspond to PE, IOL, S, BL, HL, SBL and k=6, respectively.

Input and output places with respect to  $\hat{t}_i$ , represent the effect of a fault on the corresponding components; i.e., each transition  $\hat{t}_i$ , involves a set of I/0functions  $A_i = \{I(\hat{t}_i), O(\hat{t}_i)\}$  and a set  $V_i$  of multiplicities  $\mu$  such that when  $\hat{t}_i$ fires in  $M_q$ , the number of tokens  $m_{lq}$  in each place  $p_l \in A_i$  is modified as follows:

$$m_{lj} = m_{lq} - \mu_l^I + \mu_l^O$$

Figure 2.1. Schematic Layout of the SRE Structure

where  $m_{lj}$  is the modified number of tokens in  $p_l$  in a new marking  $M_j$ . If  $\mu_l^O = 0$ ,  $p_l$  is only an input place and if  $\mu_l^I = 0$ ,  $p_l$  is only an output place. For example in Fig. 2.2, the failure of a PE  $(\hat{t}_1)$ , affects the following components: PE's, IOL's, HL's, SBL's and BL's; therefore, a set of input and output places with respect to  $t_1$  is given as:

$$A_1 = \{\{p_1, p_2, p_5, p_6\}, \{p_4\}\}$$

Assuming an  $n \times n$  processor array, the set of multiplicities associated with  $A_1$  is given as:

$$V_1 = \{\mu_1^I = n; \, \mu_2^I = 2n; \, \mu_5^I = n-1; \, \mu_6^I = n; \, \mu_4^O = n\}.$$

If less than the number of spares required for reconfiguration are available, then the array fails to reconfigure and the resulting marking is characterized by the fact that  $m_6 < 0$ . The negative value of  $m_6$  can be used to identify a failure marking reached due to exhaustion of spares. Some schemes require that specific transitions be enabled or disabled depending on the current configuration and the reconfiguration algorithm. Assume for example, that not only rows but also columns are eliminated during the reconfiguration process. In these cases, each  $\mu_l$ becomes a function of the current marking; e.g.,  $\mu_1^I$  equals the number of columns in the current configuration. Hence, in order to include all possible cases,  $\mu_l$  must be regarded as a variable multiplicity (this concept is an extension of the usual notion of "multiplicities" in Petri Net theory).

Although the SPN in Fig. 2.2, might provide the number of operational configurations required, it fails to consider the cases when enough spares are available but reconfiguration cannot take place (due for example to a peculiar distribution of faults). As a consequence, this approach might provide overly optimistic reliability estimates. Conceivably, a different SPN model can be used to accurately represent the dependency of successful reconfiguration on fault distributions. However, such an SPN would itself consist of a very large number of places and transitions which increases with the size of the array. One of the intents in this chapter is to provide an extension of the SPN concept so that dependence on fault-distribution can be accounted for in a model with a complexity comparable to that of Figure 2.2 regardless of the size of the array and reconfiguration scheme used.

#### 2.3. MSPN Representation

The fact that several types of faults affect the array in the same manner, suggests the possibility of a more compact SPN-like representation, which is referred to as Modified SPN (MSPN). A MSPN takes into account different fault

Figure 2.2. SPN of the SRE Scheme

distributions by associating with each transition  $t_i$ , a set of attributes described as follows:

$$t_i: \langle P(x \mid M_g, t_i), S_i(M_g), B_i c_i \rangle$$

where:

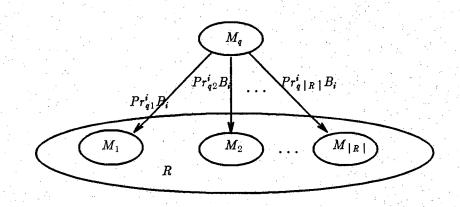

$P(x \mid M_q, t_i)$  defines a discrete probability function where x represents a random marking  $M_j$  in a set R directly reachable from a particular marking  $M_q$ ; the notation  $Pr_{qj}^i$  is used to denote the probability of reconfiguration  $P(x = M_j \mid M_q, t_i)$ , i.e., the probability that the net is in marking  $M_j$  after  $t_i$ fires when the net is in marking  $M_q$ . The advantage of assigning a probability function to each transition  $t_i$ , is the ability to determine correct transition rates between states in the corresponding Markov model as the reachability function is assigned to the marking generated, another value is assigned to another marking that can be generated by the immediate firing of a possibly different transition and so on. This sequence of firings is dictated by the current marking and the reconfiguration scheme modeled. Notice that the markings generated could have been generated previously and the probabilities of reconfiguration are only used to modify the transition rates;

$S_i(M_q)$  is a sequence of transitions that will fire immediately after  $t_i$  fires. If no immediate firing is required then  $S_i(M_q)$  is a null sequence. Depending on the reconfiguration scheme,  $S_i$  can be unique for all markings or is determined in terms of  $M_q$ ;

$B_i$  is a Binary Transition Vector with k elements  $b_l$  such that,  $b_l = 1$  if the failure of the *lth* component triggers the transition  $t_i$  and  $b_l = 0$  otherwise. This vector is used to identify those components that can trigger the corresponding transition  $t_i$ ; it facilitates the merging of non-distinct markings, the derivation of probability transition vectors (defined in section 2.4) and the derivation of flags (i.e., failure rate conditions) that signal a possible non-occurrence of a transition;

The term  $c_i$  is a coverage factor associated with  $t_i$ , such that if  $t_i$  is triggered by the failure of a spare (inactive) component then  $c_i = 1$ ; thus, the possibility of array failure at the time that one of these components fails is non-existent; if  $t_i$  is triggered by the failure of an active component then  $c_i$ corresponds to the probability of detection given that a fault occurs (i.e.,  $c_i \leq 1$ ).

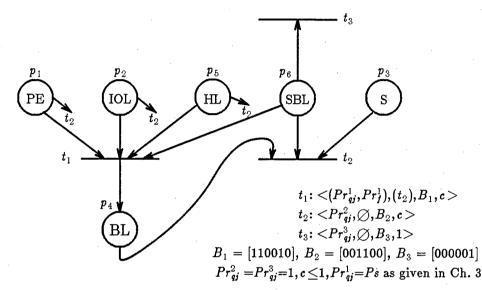

To illustrate the set of transition attributes just discussed, consider the SRE scheme in Fig. 2.1 and the SPN of Fig. 2.2. Since  $\hat{t}_1$ ,  $\hat{t}_2$  and  $\hat{t}_5$ , have the same

effect on the array, a single transition  $t_1$  is defined in a MSPN with a vector  $B_1 = [1\ 1\ 0\ 0\ 1\ 0]$  to indicate that either the failure of a PE, IOL or a HL, can cause  $t_1$  to fire. Likewise,  $\hat{t}_3$  and  $\hat{t}_4$  become  $t_2$  with a vector  $B_2 = [0\ 0\ 1\ 1\ 0\ 0]$ . The firing of  $t_2$  represents the failure of a BL or a S either of which is fatal. Transition  $\hat{t}_6$  becomes  $t_3$  and represents the failure of a SBL with a vector  $B_3 = [0\ 0\ 0\ 0\ 0\ 1]$ .

Consider now the case when a given operational configuration contains faulty SBL's. The probability that none of them lies in the row that is eliminated when  $t_1$  fires, corresponds to the probability of reconfiguration  $Pr_{qj}^1$ . If at least one SBL is faulty in the row deleted, the array fails to reconfigure with a probability  $Pr_{qf}^1 = 1 - Pr_{qj}^1$  (the failure marking is denoted as  $M_f$ ). In general, probabilities of reconfiguration are complicated functions of the characteristics of each scheme (e.g., replacement rules, hardware requirements, reconfiguration dependencies on fault distributions, etc.) and the size and shape of the array. They must be derived for each scheme and in some cases extensive simulation is required due to the complexity of the combinatorial analysis involved. Examples where suitable expressions can be derived include SRE, ARCE and DR. Since different markings may correspond to different number of SBL's,  $Pr_{qj}^1$  is a function of the current marking (i.e.,  $M_q$ ). Let Ps denote the probability of survival, then for SRE,  $Ps = Pr_{qj}^1$  and can be estimated via equation (3.8) or (3.9) which are derived in chapter 3 in terms of the number N of faulty SBL's, present in the current marking  $M_q$ . Some transitions in a MSPN will exhibit a dual nature: they can be fired exponentially or immediatedly; once a transition fires exponentially, a sequence of immediate firings (specified by  $S_i$ ) of possibly different transitions may follow. Therefore, in SRE, when  $t_1$  fires exponentially,  $t_2$  will fire immediately to generate a failure marking and  $S_1 = (t_2)$ . This follows from the fact that when  $t_1$  fires, the required SBL's become BL's and if one of

them is faulty  $t_2$  fires immediately. When  $t_2$  or  $t_3$  fire exponentially no immediate sequence is required and  $S_2$  and  $S_3$  are null sequences. It will be seen that in some applications such as ARCE, the sequence of immediate firings is not unique as it is selected depending on the current marking.

Figure 2.3. MSPN of the SRE scheme

Considering the coverage factors, the sets of attributes associated with the transitions in the MSPN of the SRE scheme, are summarized in Figure 2.3.

#### 2.3.1. I/O Places and Variable Multiplicities

Associated with each  $t_i$  in the MSPN there is a set of I/O places  $A_i^* = \{I(t_i), O(t_i)\}$  and a set of multiplicities:

$$V_i^* = \{\mu_l^I, \mu_k^O \mid p_l \in \{I(t_i)\}, p_k \in \{O(t_i)\}\}$$

Two transitions in the SPN, can have the same set of I/O places and different set of multiplicities; i.e. two distinct faults may affect the same components in different ways. In order for distinct transitions in the SPN to be

merged in a single transition in the MSPN, they must have the same set of I/O places and the same set of multiplicities. Because a coverage factor is associated with each transition in the MSPN, components whose failures fire a given transition must all correspond to either active or non-active components only (i.e., components of both types can not be present).

Example 2.1: Consider the SPN in Fig. 2.2. The failure of a PE  $(\hat{t}_1)$ , the failure of a IOL  $(\hat{t}_2)$  or the failure of an HL  $(\hat{t}_5)$  affect the same components of the array and the set of multiplicities for each set of arcs is the same; therefore transitions  $\hat{t}_1$ ,  $\hat{t}_2$  and  $\hat{t}_5$  can be merged into a single transition  $t_1$  such that  $A_1^* = \{ I(t_1), O(t_1) \} = A_1 = A_2 = A_5 = \{ \{ p_1, p_2, p_5, p_6 \}, \{ p_4 \} \}$  and

$$V_1^* = V_1 = V_2 = V_5 = \{\mu_1^I = n; \, \mu_2^I = 2n; \, \mu_5^I = n-1; \, \mu_6^I = n; \, \mu_4^O = n\}.$$

Likewise,  $A_3 = A_4$ ; i.e., the failure of either a S or a BL  $(\hat{t}_3 \text{ or } \hat{t}_4)$  causes the array to fail affecting all components in the same way; i.e., transitions  $\hat{t}_3$  and  $\hat{t}_4$  can be merged into a single transition  $t_2$  such that

$$A_2^* = \{I(t_2), O(t_2)\} = \{\{p_1, p_2, p_3, p_4, p_5, p_6\}, \emptyset\}$$

and a set of multiplicities

$$\begin{split} V_2^* &= V_3 = V_4 = \; \{ \mu_1^I = \# PE_q; \; \mu_2^I = \# IOl_q; \; \mu_3^I = \# S_q; \; \mu_4^I = \# BL_q; \; \mu_5^I = \# HL_q; \\ \mu_6^I &= \# SBL_q \}; \end{split}$$

Finally, we have that the failure of a SBL  $(\hat{t}_6)$  affects only SBL's; i.e.,

$$A_3^* = \{I(t_3), O(t_3)\} = A_6 = \{\{p_6\}, \{0\}\} \text{ with } V_3^* = V_6 = \{\mu_6 = 1\}$$

where  $t_3$  in the MSPN replaces  $\hat{t}_6$ .  $\Box$ .

In summary, an MSPN model is an extension of a SPN with the purpose of representing fault-tolerant processor arrays and can be defined as follows:

$$MSPN = (P, T, A, M, Pr, Sq, B, Cv)$$

where Pr is a set of probability functions  $P(x \mid M_q, t_i)$  associated to transitions  $t_i \in T$ ; Sq is a set of sequences  $S_i$  of of transitions that fire immediately after an exponential firing of  $t_i \in T$ ; B is the set of binary transition vectors  $B_i$  defined for each  $t_i \in T$ ; Cv is the set of coverage constants  $c_i$  associated with each  $t_i \in T$ .

#### 2.3.2. MSPN Construction

Given a processor array and a reconfiguration scheme, an informal procedure to construct the corresponding MSPN is as follows:

# **Procedure** MSPN

Inputs:

Array size;

Initial configuration  $C_0 = (\eta_1 \ \eta_2 \ \cdots \ \eta_k);$

Set of rules that determine the actions of the reconfiguration algorithm in response to faults; i.e., a rule  $r_{il}$  specifies the type and number of components added or subtracted if a component type *i* fails in an operational configuration  $C_l$ ;

Coverage factors for the failures of both active and non-active components;

Tables of probabilities of reconfiguration for each non-active component type. (For each different non-active component type, a probability of successful reconfiguration is conditioned by the number of faults of each type; the probability of configuration is then the product of these conditional probabilities).

Output: MSPN representation: (P, T, A, M, Pr, Sq, B, Cv)

Begin

Step 1:

Assign a place  $p_i$  and a transition  $\hat{t}_i$  to component type *i*.

Step 2:

for each rule  $r_{il}$  do

Group the component types affected by the failure of component type i into a set  $A_i$  as the set of I/O places with respect to transition  $\hat{t}_i$ .

Determine the multiplicity of each  $p \in A_i$  and let  $V_i$  be the set of multiplicities associated with  $A_i$ .

end for

Step 3:

Group those transition  $\hat{t}_i$  that: a) are fired by components which are all of type active or all of type non-active b) have the same set of input and output places c) have the same set of multiplicities and d) have same coverage factor.

For each group i do

Define transition  $t_i$ , sets  $A_i^*$  and  $V_i^*$ .

Specify  $S_i(M_q)$ .

Form the binary transition vector  $B_i$  such that a component  $b_l$  of  $B_i$  is one if the failure of a component type l can fire  $t_i$  and zero otherwise.

end for

end procedure

As pointed out previously a discrete probability distribution is associated with each transition such that a number of faulty spare components present in the current configuration is taken into account when the firing occurs. These probabilities are estimated using simulation or by closed form expressions.

#### 2.4. Reachability Graph

In this section the generation of the reachability graph is discussed. A mapping from the transitions in the MSPN to the transitions between states in the corresponding Markov model is established. An implementation procedure to generate the reachability graph is also described.

# 2.4.1. Probability Transition Vectors

For each marking  $M_{qj}\epsilon R$  generated when  $t_i$  fires (as stated previously R is the set of markings that can be directly generated from the same marking  $M_q$ ),  $B_i$ and the distribution function  $P(x \mid M_q, t_i)$  defined previously can be used to generate vectors of the form:

$$Pr_{qj}^i B_i = [pr_1 \cdots pr_k]$$

where  $pr_l = Pr_{qj}^i$  if  $b_l = 1$  and  $pr_l = 0$  if  $b_l = 0$ . These vectors are referred to as the Probability Transition Vectors (PTV's). The use of PTV's is illustrated in Fig. 2.4; assuming j=1,2,..., |R| identifies the markings that can be directly generated from the same marking  $M_q$ , then  $\sum_{j=1}^{|R|} Pr_{qj}^i = 1$ . In the event that two

or more non-distinct new markings are generated from the same marking, a merging to a single new marking is carried out by a vector addition of the corresponding probability transition vectors.

Figure 2.4.- Marking Generation with  $Pr_{qi}^{i}$

Example 2.2: Analyzing a particular marking (in a 4×4 array with a MSPN as in Figure 2.3) say  $M_{18} = [12 \ 24 \ 20 \ 4 \ 9 \ 11]$ , then if  $t_1$  fires (i.e. either a PE, a

IOL or a HL failed) the marking  $M_{30} = [8 \ 16 \ 20 \ 8 \ 6 \ 7]$  results with  $Pr_{18,30}^1 = 0.667$ . Thus, a PTV is given by  $Pr_{18,30}^1 B_1 = [0.667 \ 0.667 \ 0 \ 0.667 \ 0]$ . However the array may fail with  $Pr_{30,f}^1 = 0.333$  due to the existence of one faulty SBL (#PE's - #SBL's = 12 - 11 = 1). Thus, a PTV is given by  $Pr_{18,f}^1 B_1 = [0.333 \ 0.333 \ 0 \ 0.333 \ 0]$

When  $t_2$  fires (i.e a S or a BL failed), the array fails with probability  $Pr_{18,f}^2 = 1$ , the corresponding PTV is given by:  $Pr_{18,f}^2B_2 = [0\ 0\ 1\ 1\ 0\ 0]$ . Therefore, the

overall PTV associated with the transition to the failure marking when  $t_1$  or  $t_2$ fires is obtained as follows:  $Pr_{18,f}^1B_1 + Pr_{18,f}^2B_2 = [0.333\ 0.333\ 1\ 1\ 0.333\ 0]$ . The probability of survival is obtained by applying equation (3.9) derived in chapter 3.  $\Box$ .

# 2.4.2. Failure Rate Condition

Any transition in the MSPN can fire on every possible marking that represents an operational configuration. However, if all components whose failures fire a particular transition never fail, that transition will never fire. In the process of generating the reachability graph, a flag  $s_i$  signals this condition for each transition  $t_i$ . Let  $\underline{\alpha}$  be a vector with components  $\alpha_l$  where each  $\alpha_l$  is the failure rate of the component type l and  $\hat{\alpha}_i = B_i \underline{\alpha}^t$ . The flag  $s_i$  is set to one if  $\hat{\alpha}_i > 0$  and zero otherwise.

## 2.4.3. Derivation of Transition Rates

Let  $\{X(t), t \ge 0\}$  denote a continuous time homogeneous Markov process on a finite state space  $S = \{1, 2, \dots, s\}$  and denote the state probability vector at time t by  $P(t) = [P_1(t), P_2(t), \dots, P_s(t)]$ , where  $P_i(t) = P\{X(t)=i\}$ ,  $i \in S$ . The process is characterized by the following set of Chapman-Kolmogorov differential equations:

$$\frac{dP_j(t)}{dt} = \sum_i a_{ij} P_i(t) - a_{jj} P_j(t)$$

where  $a_{ij}$  are the transition rates from previous states *i* and  $a_{jj} = \sum_{k} a_{jk}$ , where  $a_{jk}$

are transitions rates from state j to states k. The solution for the set of differential equations is given in matrix form as follows:

$$P(t) = P(0)e^{A}$$

where A is the transition rate matrix with elements  $a_{ij}$  and  $P(0) = (1,0, \dots, 0)^t$ is the initial vector state. Assuming there is only one absorbing state (i.e., failure state) and indexing transient (operational) states by  $1, \dots, s-1$ , then the reliability of the system is given by:  $R(t) = \sum_{i=1}^{s} P_i(t)$

The transition rates  $a_{ij}$  can be expressed in terms of the attributes associated with the transitions in the MSPN, i.e.,  $a_{qx} = f(P(x \mid M_q, t_i), B_i, c_i)$ .

Denote by  $\alpha$  a diagonal transition rate matrix with elements  $\alpha_{ii} = \alpha_i$  and  $\alpha_{ij} = 0$  for  $i \neq j$  ( $\alpha_i$  is the failure rate of the *ith* component). Let  $\hat{M}_q = M_q \alpha$  where  $M_q = [m_{1q}, m_{2q}, \cdots m_{kq}]$  denotes as before, a particular marking q, then

$$a_{ql} = \sum_{i} c_i Pr_{ql}^i b_j; \ b_j \in B_i, j=1,...,k] \hat{\boldsymbol{M}}_q^T$$

$$(2.1)$$

defines the transition rate from state q to an operational state l. The summation is defined over all transitions that fire exponentially and generate the same marking l. It is interesting to notice the relationship of equation (2.1) with the firing rate of a particular transition  $t_i$  given by the vector product  $B_i \hat{M}_q^T$ . A transition to the failure state occurs for lack of support (i.e., enough spares) or lack of coverage. In the first case, lack of support occurs if the reconfiguration algorithm failed due to exhaustion of spare components or the fact that the array fails to reconfigure if a given distribution of faults is not supported by the reconfiguration algorithm. Denote by  $\lambda_{qf}$  the transition to the failure state (f) for lack of support, then

$$\lambda_{qf} = [\sum_{i} Pr^{i}_{qf}b_{j}; b_{j} \in B_{i}, j=1,...,k] \hat{M}_{q}^{T}$$

Let  $\lambda_{qf}^{c}$  be the transition to f for lack of coverage then:

$$\lambda_{qf}^{c} = \sum_{l} \left( \left[ \sum_{i} (1 - c_{i}) Pr_{ql}^{i} b_{j}; b_{j} \in B_{i}, j = 1, ..., k \right] \hat{M}_{q}^{T} \right)$$

The overall transition rate to the failure state is:

$$\hat{\lambda}_{qf} = \lambda_{qf} + \lambda_{qf}^c$$

The diagonal term of the matrix A is calculated as follows:

$$a_{qq} = -(\sum_{l \neq q} a_{ql} + \hat{\lambda}_{qf}) = -(\sum_{l \neq q} \lambda_{ql} + \lambda_{qf})$$

where:

$$\lambda_{ql} = [\sum_{i} Pr^{i}_{ql}b_{j}; b_{j} \in B_{i}, j=1,...,k] \hat{M}_{q}^{T}$$

*Example 2.3:* Consider a particular marking say  $M_{18} = [12 \ 24 \ 20 \ 4 \ 9 \ 11]$ , then with the following failure rates:  $\alpha_0 = 1$ ,  $\alpha_1 = \alpha_2 = \cdots = \alpha_k = .01$ , yield

$\hat{M}_{18} = [12 .24 .20 .04 .09 .11]$ . As in example 2.2, the following probabilities are used:  $Pr_{18,30}^1 = 0.667$ ,  $Pr_{18,f}^1 = 0.333$ ,  $Pr_{18,f}^2 = 1$ . Let  $c_1 = c_2 = c$  then, when  $t_1$ fires the following transition rates in the Markov chain are generated:

$a_{18,f} = c[.667 \ .667 \ 0 \ 0 \ .667 \ 0] \hat{M}_{18}^T = 8.2241c$ . The transition to the failure state due to lack of support when  $t_1$  and  $t_2$  fire is

$\lambda_{18,f} = ([.333 .333 0 0 .333 0] + [0 0 1 1 0 0]) \hat{M}_{18}^{T} = 4.34589$ . For lack of coverage  $\lambda_{qf}^{c} = (1-c)[.667 .667 0 0 .667 0] \hat{M}_{4}^{T} = 8.2241(1-c)$ . The overall transition rate to the failure state is given as  $\hat{\lambda}_{18,f} = 8.2241^{*}(1-c) + 4.34589$ . Considering that a

failure of a SBL  $(t_0)$  yields a transition rate  $a_{18,19} = [0 \ 0 \ 0 \ 0 \ 0 \ 1] M_{18}^T = 0.11$  then the diagonal term is calculated as:  $a_{18,18} = 8.2241 + .11 + 4.34589 = 12.68$ .  $\Box$

# 2.4.4. Implementation Procedure

The implementation procedure MODELGEN outlined below merges repeated markings as they are being generated and calculates or modifies the transition rates in the process. The new markings generated every iteration, are targets of the currently visited marking; they are inserted into a linked list of markings. As they are generated, markings are sorted with respect to the sum of those components indicated by the user through comparison flags previously set. An array of pointers to the newly created targets is updated. A pointer to the current marking is denoted by cm. A pointer to the next marking in the list is referred to by next. A systematic indexing of markings is carried out such that the resulting transition rate matrix is always upper triangular; a marking number is assigned to every next marking fetched from the sorted list; a pointer nxtopr points to markings which are candidates to be printed or saved in a file. If all its targets have been numbered, then a marking is saved or printed out; therefore, no significant amount of memory is required to generate large models. The procedure stops when all markings have been fetched from the sorted list. Notice that the linked list corresponds to the reachability graph and as it is formed, both the transition rate matrix representation of the Markov model and the reachability graph are printed out or saved as requested by the user.

#### Procedure MODELGEN

Inputs: Set of failure rates  $(\alpha_i)$ ; File names (to save the matrix representation of the Markov model); An MSPN representation of the reconfiguration algorithm (Procedure MSPN outlined previously).

Outputs: Reachability graph description; Matrix representation of the Markov model.

Begin

Set a coverage flag for each transition that it is fired by non-active components. (this allows the evaluation of a symbolic matrix for different coverage values).

Set comparison flags (to select those components by which the list of markings is sorted).

Load initial marking

for each  $t_i$  let  $s_i = B_i \underline{\alpha}^T$

Let *cm* point to initial marking

nxtopr = cm

while not end of list do

fetch current marking

assign a number to current marking

for each  $t_i$  and if  $s_i > 0$  do

get  $P(x \mid M_a, t_i)$

fire  $t_i$  and those transitions  $t_l \epsilon S_i$

calculate transition rates

store targets in temporary table

end for

merge repeated targets

insert new targets in sorted list

insert pointers to new targets in current marking

while all targets of nxtopr are numbered do

output nxtopr marking

```

let nxtopr = nxtopr \rightarrow next

```

end while

let  $cm = cm \rightarrow next$

end while

end procedure

The execution time of MODELGEN is proportional to the number of states generated and therefore depends on the reconfiguration algorithm. For the cases given in Table 3.2 in chapter 3 the execution time is  $O(n^3)$  for  $n \times n$  processor arrays.

#### 2.5. Summary

A systematic procedure to construct Markov models was discussed in this chapter. Using an SPN-like representation, transition firing represents the occurrence of faults; A place contains a number of tokens tokens which correspond to the number of components of a single type; thus, the collection of different components is represented by a marking in an SPN-like representation and a marking corresponds to an operational configuration of the array. However an SPN-like representation fails to take into account the distribution of faulty spares that exist when reconfiguration takes place and may cause the array to fail. Also the fact that several component types causes the same effect in the array when it reconfigures, leads to a more compact representation of the array which is referred to as an MSPN representation.

A mapping from transitions and markings in an MSPN representation to transitions and states in the Markov model was derived. This mapping allows the construction of the corresponding Markov model as the generation of the reachability graph is taking place.

The more the detail (number of components or places in the MSPN representation) that is included in the model the larger is the state space in the resulting Markov model. In summary the application of this method entails two interrelated problems. In the first place a thorough analysis of the array is required such that all interdependencies of failures of different components are defined; this can be a difficult task for complex reconfiguration schemes; secondly, in some applications a detailed modeling may be limited to small size arrays because of the large number of states generated. Finally, considering the fact that reconfiguration algorithms are primarily designed to treat failures of PE's elements only, an MSPN representation for a given reconfiguration scheme, will depend on the assumptions made as to how the algorithm treats failures on component types other than PE's.

# CHAPTER III MSPN APPLICATIONS

# 3.1. Introduction

In this chapter three reconfiguration schemes are analyzed in detail. Algorithms to calculate probabilities of reconfiguration are derived. As stated in the previous chapter, probability functions  $P(x \mid M_q, t_i)$  are associated with each transition  $t_i$  in the MSPN; probabilities of reconfiguration are used to determine Probability Transition Vectors which are in turn used to calculate transition rates in the Markov model. The probability of survival corresponds to the sum of probabilities of reconfiguration if the new markings generated are all operational; i.e. if the new markings correspond to operational configurations. In the second section of this chapter two algorithms are derived to calculate probabilities of reconfiguration for the SRE scheme. The third and fourth sections deal in detail with the ARCE and DR reconfiguration schemes, respectively. Expressions to determine the number of states for each reconfiguration scheme are given in section five. Also, in this section, results of the reliability analysis of each scheme are reported.

#### 3.2. SRE Reconfiguration Scheme

In chapter 2, the basic concepts underlining MSPN's representations of fault tolerant processor arrays were thoroughly discussed. Concurrently and for the purpose of illustration, the SRE reconfiguration scheme was analyzed. Hence, in this section, expressions to estimate probabilities of reconfiguration for this scheme are derived.

The process of generating the reachability graph which describes the corresponding Markov model of an SRE scheme, starts with an initial marking given as follows:

$p_{1:} \#PE = n^{2}$   $p_{2:} \#IOL = 2n^{2}$   $p_{3:} \#S = n + n^{2}$   $p_{4:} \#BL = 0$   $p_{5:} \#HL = n(n-1)$   $p_{6:} \#SBL = n^{2}$

A failure marking corresponds to the case when #PE=0 or #SBL<0. Transition  $t_1$  will take place if either  $\alpha_1$ ,  $\alpha_2$  or  $\alpha_5$  is greater than zero;  $t_2$  will take place if either  $\alpha_3$  or  $\alpha_4$  is greater than zero. Likewise,  $t_3$  takes place if  $\alpha_5>0$ .

# 3.2.1. Probability Transition Vectors in SRE

To derive PTV's, estimations of probabilities of reconfiguration are required for each reconfiguration scheme. In the SRE case, its MSPN indicates (Fig. 3) that when  $t_1$  fires, two transitions in the Markov model may occur (corresponding to a sequence of two firings in the MSPN:  $t_1$  followed by  $t_2$ ); one with probability  $Pr_{qj}^{1}$  which corresponds to the probability of survival denoted by Ps. The other transition fires immediately and will lead the processor array to a failure state with probability  $Pr_{qj}^{1}$ . The array will survive with probability Ps if the failure of a PE or an IOL that triggers the reconfiguration algorithm occurs in a row that contains no faulty SBL. Let N denote the number of faulty SBL in a marking  $M_q$  then N is determined by:

$$N = \#PE_q - \#SBL_q = m_{1q} - m_{6q}$$

where  $0 \leq N \leq n \times n$ .

To estimate Ps, it is necessary to find all the possible ways in which N faulty SBL's can be mapped into a total of  $r \times c$  SBL's in the array with a current configuration containing r rows and c columns. To simplify this problem we count all the possible partitions of N into r parts with a value not greater than c columns. Because each row contains c SBL's, up to c faulty SBL's per row are possible.

Each partition of N is a k-tuple  $(a_1, a_2, \ldots, a_k)$ , such that:

$$N = a_1 + a_2 + \dots + a_k \tag{3.1}$$

where:  $c \ge a_i \ge a_{i+1} \ge 1$  for  $1 \le i \le k-1$  and  $1 \le k \le r$ .

In [Ber81] it is shown that the number of partitions of N with k or less parts and  $N \ge a_i \ge a_{i+1} \ge 1$ , is given by the recurrence relations:

$$F(N-k,k) = F(N,1) + F(N,2) + \dots + F(N,k)$$

(3.2)

$$F(N,1) = F(N,N) = 1$$

The function F(N,k) is interpreted as the number of partitions of N with k parts.

Theorem 1: Let us denote by F(N) the number of wanted partitions of N; i.e. those partitions with at least one part  $a_i > c$  are excluded. Then F(N) is given by:

$$F(N) = F(N, c, 1) + ... + F(N, c, r)$$

(3.3)

where:

$$F(N,c,k) = \begin{cases} 0 & \text{if } N > kc \\ \sum_{l=\lfloor N/k \rfloor}^{c} F(N-l,l,k-1) & otherwise \end{cases}$$

(3.4)

and

$$F(N, c, 1) = F(N, c, N) = 1 \text{ if } N \le c$$

$$F(N, c, k) = 0 \text{ if } k > N$$

(3.5)

(3.6)

*Proof:* Let us consider first the case when N > kc. Each term in the summation is recursively decomposed until the functions generated satisfy equations (3.5) and (3.6). The value of l in each term of the summation corresponds to a part  $a_i$  in the ith iteration. The partitions generated will contain a part  $a_i$  such that  $\left[N/k\right] \leq a_i \leq c$ . Hence, if N/k > c implies all partitions will have at least the first part  $a_1 \geq c$  and F(N,c,k) = 0 follows.

Let us examine now the case when  $N \leq ck$ . F(N, c, k) is decomposed into  $(c - \lfloor N/k \rfloor + 1)$  functions, which in turn are recursively decomposed until the cases of equations (3.5) or (3.6) are reached. In the process those functions in which N > kc or k > N are eliminated.

The number of terms in the sum corresponds to all the possible values a part may take and since the minimum at every iteration is  $a_i = \left\lceil N/k \right\rceil$ , we let  $a_1 \leq c$  as an upper bound for the first iteration which gives the number of summands

33

indicated previously. For the next iteration the process is repeated. At the *ith* iteration,  $N = N - a_i$  and k has been decremented to indicate that now the new value of N is to be partitioned in k-i parts such that  $\left[N/k\right] \leq a_i \leq a_{i-1}$ .

Equations (3.3-3.6) can also be used to determine the value of each part in a particular partition since in the *ith* iteration the index l in equation (3.4) corresponds to the value of  $a_i$  whereas N-l corresponds to the remaining value to be partitioned among the k-1 remaining parts.  $\Box$

Example 3.1: To illustrate the application of the above relations, let us find all the possible distributions of 8 faulty SBL's in a  $4 \times 4$  array (r=c=n). Solution: With N = 8, n = 4 and r = 4 we have:

$$F(8) = F(8,4,1) + F(8,4,2) + F(8,4,3) + F(8,4,4)$$

$$F(8,4,1) = 0 \text{ since } 8 > 4$$

$$F(8,4,2) = F(4,4,1) = 1$$

$$F(8,4,3) = F(5,3,2) + F(4,4,2)$$

$$= F(2,3,1) + F(2,2,1) + F(1,3,1) + F(0,4,1) = 1 + 1 + 1 = 3$$

$$F(8,4,4) = F(6,2,3) + F(5,3,3) + F(4,4,3)$$

$$= F(4,2,2) + F(3,2,2) + F(2,3,2) + F(2,2,2) + F(1,3,2) + F(0,4,2)$$

$$= F(2,2,1) + F(1,2,1) + F(1,1,1) + F(1,1,1) + 0 + 0 = 4$$

And  $F(8) = 0 + 1 + 3 + 4 = 8$

Table 3.1, shows the order of the resulting partitions, where partition 1) is given by F(8,4,2); partitions 2-4 are given by F(8,4,3); and partitions 5-8 are given by F(8,4,4).  $\Box$

| Partition | Parts                 |       |                       |            |

|-----------|-----------------------|-------|-----------------------|------------|

| No.       | <i>a</i> <sub>1</sub> | $a_2$ | <i>a</i> <sub>3</sub> | <u>a</u> 4 |

| 1         | 4                     | 4     | 0                     | 0          |

| 2         | 3                     | 3     | 2                     | Ö.         |

| 3         | ·· 4                  | 2     | 2                     | 0          |

| 4         | <b>4</b>              | 3     | 1                     | 0          |

| 5.        | -2                    | 2     | 2                     | 2          |

| 6         | 3                     | 2     | 2                     | 1          |

| 7         | 3                     | 3     | 1                     | 1          |

| 8         | 4                     | 2     | 1                     | 1          |

Table 3.1. Partitions of N = 8

The probability of survival Ps can be found by two methods using in both cases the Total Probability Theorem [Tri82]. In the first method:

$$Ps = \sum_{i=1}^{F(N)} P(s \mid i) P(i)$$

(3.7)

The term  $P(s \mid i)$  is the probability of success given the *i*th partition occurs and P(i) is the probability that the *i*th partition occurs. These probabilities are obtained as follows:

$$P(s \mid i) = \frac{z_i}{r}$$

$P(i) = \frac{\pi_i}{\pi}$

where  $z_i$  is the number of zeros in the *i*th partition,  $\pi_i = \begin{pmatrix} r \\ \tau_1 \tau_2 & \cdots & \tau_m \end{pmatrix}_{i=0}^{r-1} \begin{pmatrix} c \\ a_i \end{pmatrix}$

corresponds to the number of mappings represented by the *ith* partition with m

distinct parts repeated  $\tau_l$   $(1 \le l \le m)$  times. The term  $\pi = \sum_{i=1}^{F(N)} \pi_i = \begin{pmatrix} rc \\ N \end{pmatrix}$  is the total

number of possible mappings of N faulty SBL's into an array with  $r \times c$  number of PE's. After some manipulations on equation (3.7), the following expression results:

$$Ps = \frac{1}{r\pi} \sum_{i=1}^{F(N)} z_i \pi_i$$

(3.8)

A drawback in this procedure is that an enumeration of the possible partitions of N is required and this is a lengthy task for large processor arrays. A second method more attractive for large arrays is given in the following:

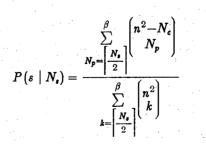

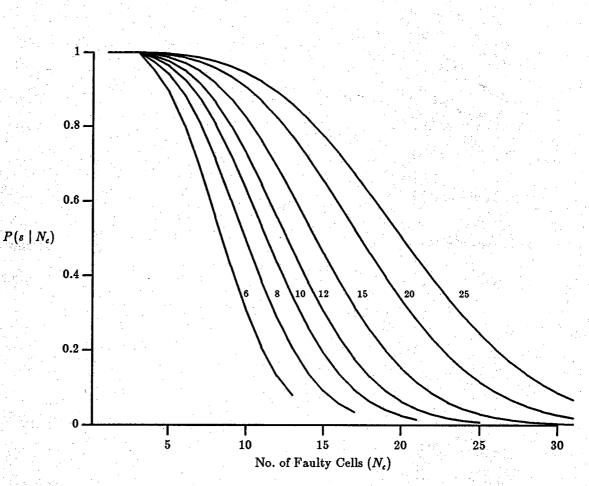

Theorem 3.2: Denote by k the number of rows (number of parts in the partition) with *i* faults (k parts with same value *i*), let  $\pi$  be defined as above and let  $\theta(k, i)$  be the total number of mappings with exactly k rows with *i* faults then the probability of survival is given by the following expression:

$$Ps = \sum_{k=1}^{m} \left(\frac{k}{r}\right) \frac{\theta(k,i)}{\pi}$$

(3.9)

where

$$\theta(k,i) = \sum_{j=k}^{m} (-1)^{j+k} {j \choose k} {r \choose j} {(r-j)c \choose N-ij} {c \choose i}^{j}$$

where  $0 \le i \le c$  and *m* is determined such that  $0 \le N-im \le (r-m)c$ . *Proof:* To find  $\theta(k,i)$ , denote by  $A_k$  the number of mappings with at least *k* rows with *i* faults, then

$$A_{k} = \binom{r}{k} \binom{(r-k)c}{N-ik} \binom{c}{i}^{l}$$

The first binomial corresponds to the number of ways k is combined in r rows; the second binomial gives the number of mappings of the remaining faults into the remaining spots (PE's) in the array; the last binomial corresponds to the number of ways in which i faults are mapped into c PE's in one column in each of the k

rows. Because  $A_k$  counts also  $A_l$  for  $k < l \le m$  by a factor of  $\begin{pmatrix} l \\ k \end{pmatrix}$ ,  $\theta(k, i)$  can be

obtained subtracting all mappings with *l* rows; i.e.:

$$\theta(k,i) = A_k - \sum_{l=k+1}^m \binom{l}{k} \theta(l,i)$$

By letting  $\theta(m, i) = A_m$  an expression of  $\theta(k, i)$  is obtained recursively in terms of  $A_k$ . After substituting  $A_k$  the expression for  $\theta(k, i)$  given above follows.

To obtain Ps, let  $a_{k,i}$  be the set of partitions with k rows with i faults then the probability of survival given  $a_{k,i}$  is k/r and using the Total Probability Theorem the probability of survival is given by:

$$Ps = P(s) = \sum_{k=1}^{m} P(s \mid a_{k,i}) P(a_{k,i})$$

where  $P(a_{k,i}) = \frac{\theta(k,i)}{\pi}$  and equation (3.9) follows.  $\Box$

In the particular case of the SRE scheme, Ps is obtained by letting i=0 in equation (3.9).

#### **3.3.** ARCE Reconfiguration Scheme

In the ARCE scheme, a row elimination is followed by a column elimination [FoR85]. Figure 3.1, shows a section of an n×n array supporting ARCE. Since the number of rows and columns varies with each configuration, then at a given configuration, r denotes the number of rows and c the number of columns. The array is in a *r*-configuration (r=c) if the reconfiguration algorithm deletes a row; Likewise, it is in a *c*-configuration (r < c) if the reconfiguration algorithm deletes a column; In Figure 3.1, the following components are identified: PE's; I/O Links, which are the interconnections between switches and PE's; Column Switches (CS), which are the switches in the current c columns of the array; Row Switches (RS), these are the switches in the current r rows of the array. The spare bypass links (SBL) used to bypass a faulty row become active links used to bypass a faulty column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as Column become active links and are referred to as

In the case of ARCE, the following assumptions are made:

- 1) The failure of a PE or an IOL, causes the elimination of a row if the array is in a r-configuration; it causes the elimination of a column if it is in a cconfiguration.

- 2) All switches in the current configuration are considered active.

- 3) The failure of a RS in a r-configuration, causes the elimination of that row; in a c-configuration, a column is eliminated followed by the affected row to comply with the alternate column-row deletion process.

- 4) The failure of a CS in a c-configuration, causes the deletion of the affected column; in a r-configuration a row and the affected column are eliminated.

- 5) The failure of a RBL, causes the same effect as the failure of a RS.

- 6) The failure of a CBL, causes the same effect as the failure of a CS.

- 7) If a row is deleted, the spare bypass links used to bypass that row must be fault free. Otherwise, the row is deleted followed by the column deletion with the faulty spare link; this sequence is referred to as a row-column deletion sequence. Likewise, if a column is deleted the spare bypass links used to bypass that column must be fault free; otherwise, the column is deleted followed by the row with the faulty spare link; this sequence is referred to as *column-row deletion* sequence.

## 3.3.1. MSPN Representation of the ARCE Scheme

Any operational configuration  $C_i$  for the ARCE scheme is described as follows:

$$C_i = (\eta_{1i}, \eta_{2i}, ..., \eta_{7i}) = (\#PE, \#IOL, \#CS, \#RS, \#RBL, \#CBL, \#SBL)$$

An operational configuration  $C_i$  corresponds to an operational marking  $M_i$ .

Figure 3.1.- Schematic Layout of the ARCE Structure

An initial configuration  $C_0$  in terms of the size n of the array, is given by the following set of equations:

- $p_1: \#PE = n^2,$

- $p_2: \#IOL = 4n^2,$

- $p_3: \#RS = (n+1)n,$

$p_4: #CS = (n+1)n,$

- $p_5: \#RBL = 0,$

- $p_6: \#CBL = 0,$

$p_7: \#SBL = 2n^2.$

In any configuration  $C_i$  described by a marking  $M_i$ , the number of rows rand columns c are calculated as follows:

$$r = \left\lfloor (m_{1i})^{\frac{1}{2}} \right\rfloor \qquad c = \left\lceil (m_{1i})^{\frac{1}{2}} \right\rceil$$

The difference d = c - r = 0 identifies r-configurations and d = 1 identifies c-configurations.

A transition to a failure marking occurs if the current marking contains not enough PE's or not enough SBL's. To identify this condition in each marking  $M_q$ , a flag x is set or reset accordingly:

$$x = \begin{cases} 1 & \text{if } m_1 > m \text{ and } m_6 \ge 2m \\ 0 & otherwise \end{cases}$$

where m and 2m refer to the number of PE's and SBL's, respectively, eliminated by the reconfiguration scheme. Notice that m takes values depending on the type of the current configuration.

A place  $p_i$  and a transition  $\hat{t}_i$  is assigned to each component type as listed above. For each  $\hat{t}_i$  the corresponding set  $A_i$  of I/O places and set of multiplicities  $V_i$  are determined next.

According to assumption 1),  $\hat{t}_1$  (failure of a PE) affects all the components in a column or a row; hence:

$$A_1 = \{I(\hat{t}_1), O(\hat{t}_1)\} = \{\{p_1, p_2, p_3, p_4, p_5, p_6, p_7\}, \{p_6, p_7\}\}$$

The set  $V_1$  of variable multiplicities is given by the following set of equations:

- a)  $\mu_1^I = rx + m_{1q}(1-x)$

- b)  $\mu_2^I = 4rx + m_{2q}(1-x)$

- c)  $\mu_3^I = (n+1)dx + m_{3q}(1-x)$

- d)  $\mu_4^I = (n+1)(1-d)x + m_{4q}(1-x)$

e)

$$\mu_5^I = (n-r)dx + m_{5q}(1-x)$$

f)  $\mu_6^I = (n-c)(1-d)x + m_{6q}(1-x)$

g)  $\mu_7^I = 2rx + m_{7q}(1-x)$

h)  $\mu_5^O = r(1-d)x - m_{5q}(1-x)$

i)  $\mu_6^O = rdx - m_{6q}(1-x)$

This set of equations indicate that when  $\hat{t}_1$  fires then: a) r PE's are deleted; b) 4 IOL's for each PE eliminated are also eliminated; c) in a c-configuration, n+1 CS's are deleted; d) in a r-configuration n+1 RS's are deleted; e) n-r RBL's are deleted in a r-configuration; this number corresponds to the RBL's bypassing the PE's in the rows already eliminated; however, no RBL's are deleted if the current configuration is a c-configuration; f) no CBL's are deleted in a cconfiguration but in a r-configuration, n-c CBL's need to be deleted which are those CBL's bypassing PE's in the columns already eliminated; g) since there are two SBL's for each PE, 2r SBL's are deleted in either configuration; h) the number of RBL added corresponds to the number of PE's in a deleted row; i) the number of CBL's added corresponds to the number of PE's in a deleted column.

The failure of an IOL  $(\hat{t}_2)$ , as stated in assumption 1) causes the same effect as  $\hat{t}_1$ . Therefore  $A_2 = A_1$  and  $V_2 = V_1$ .

The failure of a CS  $(\hat{t}_3)$  as stated in assumption 4), will have the following set  $A_3$ :

$$A_3 = \{I(\hat{t}_3), O(\hat{t}_3)\} = \{\{p_1, p_2, p_3, p_4, p_5, p_6, p_7\}, \{p_5, p_6\}\}$$

Let m=r+(c-1)(1-d) then the set  $V_3$  of variable multiplicities is given as follows:

a)  $\mu_1^I = mx + m_{1q}(1-x)$

b)

$$\mu_2^I = 4mx + m_{2q}(1-x)$$

c)  $\mu_3^I = (n+1)x + m_{3q}(1-x)$

d)  $\mu_4^I = (n+1)(1-d)x + m_{4q}(1-x)$

e)  $\mu_5^I = (n-r)x + m_{5q}(1-x)$

f)  $\mu_6^I = (n-c)(1-d)x + m_{6q}(1-x)$

g)  $\mu_7^I = 2mx + m_{7q}(1-x)$

h)  $\mu_5^O = (c-1)(1-d)x - m_{5q}(1-x)$

i)  $\mu_6^O = (r+d-1)x - m_{6q}(1-x)$

Thus when  $\hat{t}_3$  fires, equation a) shows that in a c-configuration, only r PE's are eliminated; however in a row configuration, to delete a column a row must be deleted first giving a total of r+(c-1) PE's eliminated. In general given a rconfiguration, to delete a column, the sequence row-column deletion applies and given a c-configuration, to delete a row, the sequence column-row deletion applies. In equation b), for every PE that is eliminated 4 IOL's are also eliminated. In c) shows that in either configuration, all the CS's in the affected column are eliminated. Equation d) shows that in a r-configuration all the RS's in the affected row are eliminated. Equation e) indicates that in either configuration (n - r)RBL's are eliminated. Equation f) shows that in a c-configuration, n-c is the number of rows that have been eliminated, so the same number of active CBL's is eliminated. However none are eliminated if a column is deleted. Equation g) deletes 2 SBL's for each PE deleted. Equation h) shows that in a c-configuration the row-column sequence activates only c-1 RBL's; none is activated in a rconfiguration. Equation i) shows that r-1 CBL's are activated corresponding to the column deleted in a row-column sequence that applies in a c-configuration; in a r-configuration only a column is eliminated and so are the r CBL's in it.

The effect of the failure of a RS  $(\hat{t}_4)$ , as stated in assumption 3), is described by the following set  $A_4$ :

$$A_4 = \{I(\hat{t}_4), O(\hat{t}_4)\} = \{\{p_1, p_2, p_3, p_4, p_5, p_6, p_7\}, \{p_5, p_6\}\}$$

with the following set of variable multiplicities  $V_4$  where m=r+(c-1)d:

a)

$$\mu_1^I = mx + m_{1q}(1-x)$$

b)  $\mu_2^I = 4mx + m_{2q}(1-x)$

c)  $\mu_3^I = (n+1)dx + m_{3q}(1-x)$

d)  $\mu_4^I = (n+1)x + m_{4q}(1-x)$

e)  $\mu_5^I = (n-r)dx + m_{5q}(1-x)$

f)  $\mu_6^I = (n-c)x + m_{6q}(1-x)$

g)  $\mu_7^I = 2mx + m_{7q}(1-x)$

h)  $\mu_5^O = mx - m_{5q}(1-x)$

i)

$$\mu_6^O = (r-1)dx - m_{6q}(1-x)$$

These equations are essentially the same as for  $t_3$ , except that in case of a cconfiguration, the failure of a RS, implies the deletion of the affected row therefore the sequence column-row deletion applies. Note that equation h) shows that the number of CBL's activated corresponds to the number of PE's eliminated in a c-configuration; i.e. c CBL's; in the case of a r-configuration r=c-1 CBL's are activated. Likewise, the number of RBL's activated by equation i), corresponds to the number of PE's eliminated in a r-configuration; none in a c-configuration.

The failure of a RBL  $(\hat{t}_5)$  as stated in assumption 6), will have the same effect as the failure of CS; therefore  $A_5 = A_3$  and  $V_5 = V_3$ .

The failure of a CBL  $(\hat{t}_6)$ , has the same effect as the failure of a RS; therefore  $A_6 = A_4$  and  $V_6 = V_4$ .

The failure of a SBL  $(\hat{t}_7)$ , will decrease the number of SBL's by one and:

$$A_7 = \{I(\hat{t}_7), O(\hat{t}_7)\} = \{\{p_7\}, \{\emptyset\}\}$$

With a set  $V_7$  of variable multiplicities as follows:

$$\mu_{7}^{I} = 1$$

Transitions  $\hat{t}_1$  and  $\hat{t}_2$  have same set of I/O places and same set of multiplicities; therefore transition  $t_1$  of the MSPN is defined with  $A_1^* = A_1 = A_2$  and  $V_1^* = V_1 = V_2$ .

Likewise  $\hat{t}_3$  and  $\hat{t}_5$  define transition  $t_2$  of the MSPN with  $A_2^* = A_3 = A_5$ and  $V_2^* = V_3 = V_5$ .

Transitions  $\hat{t}_4$  and  $\hat{t}_6$  define transition  $t_3$  of the MSPN with  $A_3^* = A_4 = A_6$ and  $V_3^* = V_4 = V_6$ .

Finally transition  $\hat{t}_7$  define  $t_4$  with  $A_4^* = A_7$  and  $V_4^* = V_7$ .

The set of transitions t thus obtained with the corresponding sets of I/O places and variable multiplicities describe the MSPN of the ARCE scheme shown in Figure 3.2.

The transition vectors associated with the transitions t are the following:

$B_1 = [1 \ 1 \ 0 \ 0 \ 0 \ 0]$  $B_2 = [0 \ 0 \ 1 \ 0 \ 1 \ 0 \ 0]$  $B_3 = [0 \ 0 \ 0 \ 1 \ 0 \ 1 \ 0]$  $B_4 = [0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 1]$

Notice that in ARCE,  $t_1$  will not occur if  $\alpha_1 = \alpha_2 = 0$ ,  $t_2$  will not occur if  $\alpha_3 = \alpha_5 = 0$ ,  $t_3$  will not occur if  $\alpha_4 = \alpha_6 = 0$  and  $t_4$  will not occur if  $\alpha_7 = 0$ .

# 3.3.2. Probability Transition Vectors in ARCE

In ARCE, a successful reconfiguration takes place if 1) In a r-configuration (r=c), all r RBL's in the row to be deleted are fault free and 2) in a c-configuration (r < c), all r CBL's, in the column to be deleted are fault free.

In either case we are interested in the distribution of  $N_1$  faulty spare RBL's and  $N_2$  faulty spare CBL's, such that  $N = N_1 + N_2$  is the total number of faulty spare links where  $0 \leq N_1 \leq rc$ ,  $0 \leq N_2 \leq rc$ . In a marking q, the number N of faulty SBL's is obtained as follows:

$$N = 2m_{1q} - m_{7q}$$

where  $m_{1q} = rc$  and  $0 \le N \le 2rc$ . The number of SBL's that must be fault free for a successful reconfiguration is always r. Let H(N) be the number of partitions of N into parts  $N_1$  and  $N_2$  such that  $0 \le N_1, N_2 \le rc$ , then

$$H(N) = \begin{cases} N+1 & N \leq rc \\ 2rc - (N-1) & N > rc \end{cases}$$

Assuming all possible partitions of N are equally likely, the probability that any  $\hat{n}th$  partition will occur is  $pr(\hat{n}) = 1/H(N)$ .

Let X be a random variable which denotes the number of faulty sbl's (column spares in case of a r-configuration and row spares bypass links in case of c-configuration). Then  $Pr(X=i \mid \hat{n})$  is the probability that there are *i* faulty spare links in the row or column to be deleted given the  $\hat{n}th$  partition occurs; this probability is given by equation (3.9).

The total probability Pr(X=i), which corresponds to the probability that *i* spare row/column links are faulty in the row/column to be deleted out of a total of N faulty spare links is given by:

$$Pr(X=i) = \sum_{\hat{n}=1}^{H(N)} Pr(X=i \mid \hat{n}) pr(\hat{n}) = \frac{1}{H(N)} \sum_{\hat{n}=1}^{H(N)} Pr(X=i \mid \hat{n})$$

$$= \frac{1}{H(N)} \sum_{\hat{n}=1}^{H(N)} \sum_{\hat{n}=1}^{m} \left(\frac{k}{r}\right) \frac{\theta(k,i)}{\pi}$$

(3.10)

Since  $0 \le i \le r$ , expression (3.10) implies that there will be at most r+1 transitions from a given state to up to r+1 different new states. Each transition is weighted by Pr(X=i) such that  $\sum_{x=0}^{r} Pr(X=i) = 1$ . Every term in this summation corresponds to a transition probability as stated previously. The size of the set R of states directly reachable from any given state is for this case up to r+1 and includes the failure state if X=r.

Because every possible value of X, may trigger a different reconfiguration the following cases are observed:

1) Case of transition  $t_1$ .- If i=0, a row or column is deleted in a c or rconfiguration respectively. However if i>0, i sequences of rc-deletions are required: in a r-configuration i faulty spare row bypass links become faulty active row bypass links so  $t_2$  is applied i times; In a c-configuration i faulty spare column bypass links become faulty active column bypass links so  $t_3$  is applied itimes.

2) Case of transition  $t_2$ .- The application of  $t_2$  implies rc-deletions in a rconfiguration for all *i*. In a c-configuration however, if i=0, only the column affected is deleted; if i>0, then *i* rc-deletions occur and since the column spare bypass links in the columns deleted become active column bypass links then  $t_3$  is applied i times.

3) Case of transition  $t_3$ .- In this case, *i* rc-deletions are required in a cconfiguration. However in a r-configuration, if i=0, only the affected row is deleted, otherwise *i* rc-deletions are necessary and since the faulty spare row bypass links become active row bypass links,  $t_2$  is applied *i* times.

In summary, to capture these cases in an MSPN representation the sequences  $S_1, S_2$  and  $S_3$  are defined as follows:

$$S_1 = S_2 = S_3 = \begin{cases} (t_2, \ \cdots, \ t_2) & \text{if } d = 0 \\ (t_3, \ \cdots, \ t_3) & otherwise \end{cases}$$

i.e., whenever  $t_1$ ,  $t_2$  or  $t_3$  fire exponentially, a sequence of r immediate firings of  $t_2$  or  $t_3$  will follow depending whether the current marking corresponds to a r-configuration or a c-configuration.

Finally, we adopt the following criteria to determine the number of faulty spares that are passed on to the new configuration. When a single row or column is eliminated, the number of faulty spares passed on to the new configuration is given by:

$$N_1 = N_0 - r$$

In general after k firings of a sequence  $S_i$  have occurred, the following recursion can be applied:

$$N_k = N_{k-1} - m$$

where

$$m = \begin{cases} r & \text{for } t_1 \\ r + (c-1)d & \text{for } t_2 \\ r + (c-1)(1-d) & \text{for } t_3 \end{cases}$$

These expressions assure that the spares that become active and make the new configuration possible must be fault-free. The number of faults in a current configuration are distributed in the array between the rows and columns deleted and the new configuration. Therefore the new configuration will contain non-faulty spares if  $N_k \leq 0$  otherwise  $N_k$  faulty spares are passed on to the new configuration. To represent this condition every time  $t_1$ ,  $t_2$  or  $t_3$  fires, let a flag y be set or reset as follows:

$$y = \begin{cases} 1 & \text{if } N_k \leq 0 \\ 0 & otherwise \end{cases}$$

then the desired number of SBL's  $(m_{7j})$  in a new marking j is obtained by modifying the input multiplicities associated with SBL's as follows:

$$\mu_7^I = ((2m - N_{k-1})y - m(1-y))x + m_7(1-x)$$

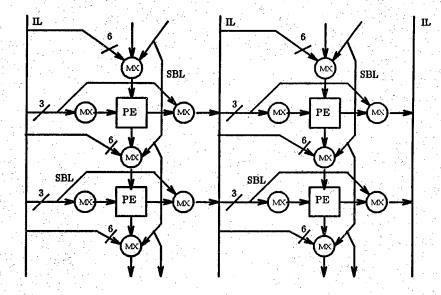

#### **3.4.** Direct Reconfiguration Scheme

In this section an specific case of reconfigurable processor arrays that follow a systematic chained replacement of faulty cells [SaS86a,SaS86b] is analyzed. Figure 3.3 shows a schematic layout of the hardware requirements for the Direct Reconfiguration in an  $n \times n$  array where interconnections are implemented through multiplexers. For illustration, the Direct Reconfiguration (DR) algorithm is emphasized, since other schemes within this class (fixed fault-stealing, variable fault-stealing, complex fault-stealing, etc.,) [SaS86a,SaS86b] can be analyzed in a similar way.

Upon the application of the reconfiguration algorithm (which considers the total number of non-faulty cells), a faulty cell is replaced by a spare cell by simply reindexing non-faulty cells and bypassing the faulty one. Thus, a shift of

Figure 3.2. MSPN of the ARCE Scheme

functional cells or chained replacement is carried out when a faulty cell is detected. For the case of a single spare row and a single spare column, the reconfiguration algorithm scans each column of the array upwards and marks the first faulty cell as a vertical fault. All other faults are classified as horizontal faults. If one row has more than one horizontal faulty, reconfiguration is not possible along that row and the reconfiguration fails.

To analyze the DR scheme, the following components are considered: active cells (PE's); I/O links (IOL's); for each cell there are two Input Multiplexers (IMX's); for each cell there is one Output Multiplexer (OMX); Bypass Links (BL's) are active links which are used to bypass faulty cells; the Interconnection Links (IL's) are sets of links that define the interconnection network and it is assumed (to simplify the analysis) that there is one set per column and that the corresponding failure statistics can be provided; spare cells (SPE's); Spare IOL's (SIOL's); Spare Multiplexers (SMX's) which are the non-active multiplexers associated with spare cells; Spare Bypass Links (SBL's) are non-active bypass links.

In the analysis of this scheme the following assumptions are made:

- 1) The reconfiguration algorithm is applied to replace either spare or nominal faulty cells. In this analysis only one spare row and one spare column are assumed.

- 2) A cell is bypassed by any one of the spare bypass links shown in the diagram depending weather the reconfiguration is vertical or horizontal [SaS86a]. Since the functions of the bypassed cell are replaced by another cell, a link in the IL is activated acting as a bypass. Therefore, it can be assumed that always two bypass links will be used to bypass a faulty cell. Also, for a successful reconfiguration both spare bypass links must be fault-free.

- 3) The failure of an IL or an OMX or a BL is fatal.

- 5) The failure of an SMX or an SIOL disables the spare cell to which they are attached.

- 4) The failure of an IMX or an IOL disables the cell to which they are attached.

# 3.4.1. MSPN of the DR Scheme

The following set of equations shows the initial configuration of an  $n \times n$  array that supports the DR scheme with one spare row and one spare column. A place assigned to each component type is also indicated:

$p_1: \#PE = n^2$

Figure 3.3.- Schematic Layout of the DR Structure

$p_{2}: \#IOL = 4n^{2}$   $p_{3}: \#IMX = 2n^{2}$   $p_{4}: \#OMX = n^{2}$   $p_{5}: \#BL = 2n$   $p_{6}: \#IL = n+1$   $p_{7}: \#SPE = 2n+1$   $p_{8}: \#SIOL = 4*(2n+1)$   $p_{9}: \#SMX = 3(2n+1)$   $p_{10}: \#SBL = 2n^{2}+2(n+1)$

Note that in the initial configuration the number of BL's is given by those active links required to bypass both the spare row and the spare column. The number of SMX's correspond to those multiplexers attached to spare cells; since they are not active a single place is assigned to them assuming all have the same failure rate; when a cell becomes active then its 3 SMX's are separated into 2 IMX's and 1 OMX. The total number of SBL's is given by those existing in the nominal array plus (n+1) in the spare row and (n+1) in the spare column.

To construct the MSPN, let us denote by  $t_1$  the failure of an SBL  $(\hat{t}_{10})$  with  $A_1^* = A_{10} = \{\{p_{10}\}, \emptyset\}$  and  $V_1^* = V_{10}$  which contains only the equation  $\mu_{10}^I = 1$ .