## Purdue University Purdue e-Pubs

Department of Electrical and Computer Engineering Technical Reports Department of Electrical and Computer Engineering

2-1-1989

## Three-Dimensional MOS Process Development

J. A. Friedrich *Purdue University*

G. W. Neudeck *Purdue University*

Follow this and additional works at: https://docs.lib.purdue.edu/ecetr

Friedrich, J. A. and Neudeck, G. W., "Three-Dimensional MOS Process Development" (1989). *Department of Electrical and Computer Engineering Technical Reports*. Paper 639. https://docs.lib.purdue.edu/ecetr/639

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

# Three-Dimensional MOS Process Development

J. A. Friedrich G. W. Neudeck

TR-EE 89-7 February, 1989

School of Electrical Engineering Purdue University West Lafayette, Indiana 47907

## TABLE OF CONTENTS

|                                       |       |                                                                                                                | 112 - 1   |    |

|---------------------------------------|-------|----------------------------------------------------------------------------------------------------------------|-----------|----|

| LIST OF TABLES                        | ••••• | •••••                                                                                                          | •••••     | v  |

|                                       |       |                                                                                                                | •         |    |

| LIST OF FIGURES                       | ••••• | •••••                                                                                                          | •••••     | vi |

| ABSTRACT                              |       |                                                                                                                |           | xi |

|                                       |       |                                                                                                                |           |    |

| CHAPTER 1 - INTRODUCTION              |       |                                                                                                                |           | 1  |

|                                       |       |                                                                                                                |           |    |

| 1.1 Background                        |       |                                                                                                                |           |    |

| 1.2 Statement of Purpose              |       |                                                                                                                |           |    |

| 1.3 Proposed Structure                |       | • • • • • • • • • • • • • • • • • • • •                                                                        | •••••     | 3  |

| 1.4 Thesis Overview                   |       | • • • • • • • • • • • • • • • • • • • •                                                                        | •••••     | 5  |

|                                       |       |                                                                                                                |           |    |

| CHAPTER 2 - LITERATURE REVIEW         |       | ••••                                                                                                           | •••••     | 7  |

|                                       | :     |                                                                                                                |           |    |

| 2.1 Introduction                      |       | ••••••                                                                                                         | ••••••    | 7  |

| 2.2 Background                        |       |                                                                                                                |           |    |

| 2.3 CMOS Circuit Design               |       |                                                                                                                | · · · · · |    |

| 2.3.1 Fully Complementary CMOS        | ••••• | •••••••                                                                                                        |           | 10 |

| 2.3.2 Clocked CMOS                    |       | •••••                                                                                                          |           | 10 |

| 2.3.3 Complex CMOS Circuits           |       |                                                                                                                |           |    |

| 2.4 CMOS Technology                   |       |                                                                                                                |           |    |

| 2.5 SOI Technologies                  |       |                                                                                                                |           |    |

| 2.5.1 Full Insulation by Porous Oxidi |       |                                                                                                                |           |    |

| 2.5.2 Polysilicon Recrystallization   |       |                                                                                                                |           |    |

| 2.5.3 Separation by Implanted Oxyge   |       |                                                                                                                |           |    |

| 2.5.4 Lateral Solid-Phase Epitaxial G |       | the second s |           |    |

| 2.5.5 Heteroepitaxial SOI             |       |                                                                                                                |           |    |

| 2.5.6 Wafer Bonding and Wafer Thin    | ning  |                                                                                                                |           | 30 |

|                                                 | •      |

|-------------------------------------------------|--------|

| 2.6 Epitaxial Lateral Overgrowth                | 30     |

| 2.6.1 Basic Terminology                         | 31     |

| 2.6.2 Transport and Fluid Dynamics              | 35     |

| 2.6.3 Chemical Reactions in Si-Epitaxy          | 38     |

| 2.6.4 Applied SEG and ELO                       | 41     |

| 2.7 Summary                                     | 46     |

| CHAPTER 3 - PROCESS DEVELOPMENT I: TEST STRUCTU | JRES46 |

| 3.1 Introduction                                | 47     |

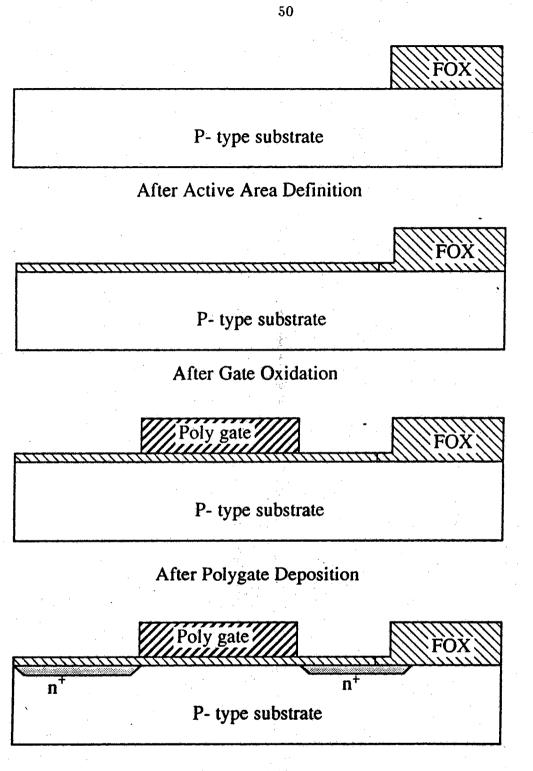

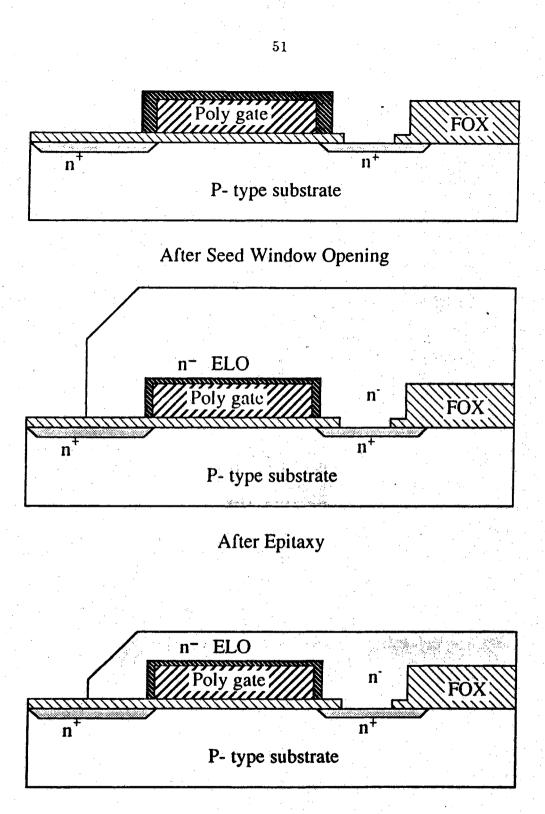

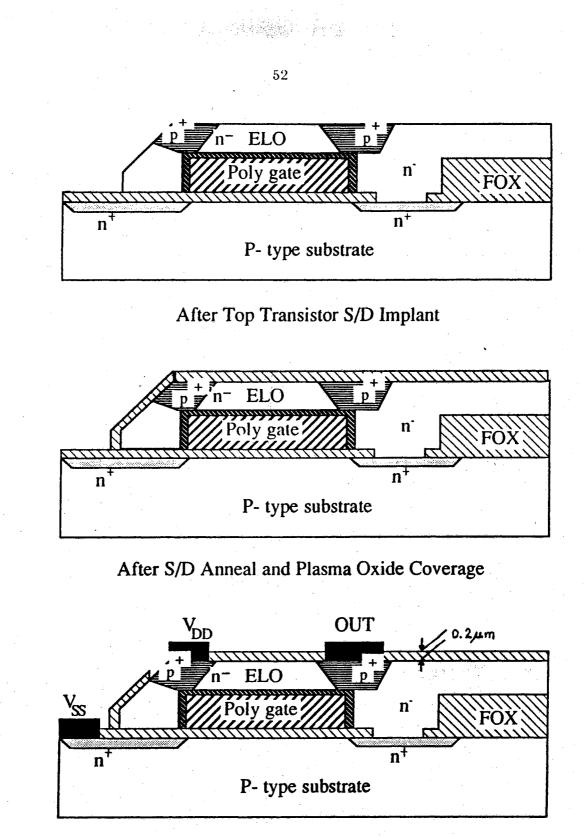

| 3.2 3-D CMOS Process Flow                       |        |

| 3.3 Test Device Structures                      | 53     |

| 3.3.1 ELO Growth and Planarization              | 53     |

| 3.3.2 Electronic Device Structures              | 55     |

| 3.4 Process Simulation                          | 63     |

| 3.4.1 3-D Capacitor Simulation                  | 63     |

| 3.4.2 3-D CMOS Inverter Simulation              |        |

| CHAPTER 4 - PROCESS DEVELOPMENT II: EXPERIMENTA | L72    |

| 4.1 Introduction                                | 72     |

| 4.2 Polysilicon                                 | 73     |

| 4.3 Oxide Degradation During SEG                | 76     |

| 4.4 Silicon Epitaxy                             |        |

| 4.4.1 Crystalline Quality                       |        |

| 4.4.2 Growth Rate Characteristics               |        |

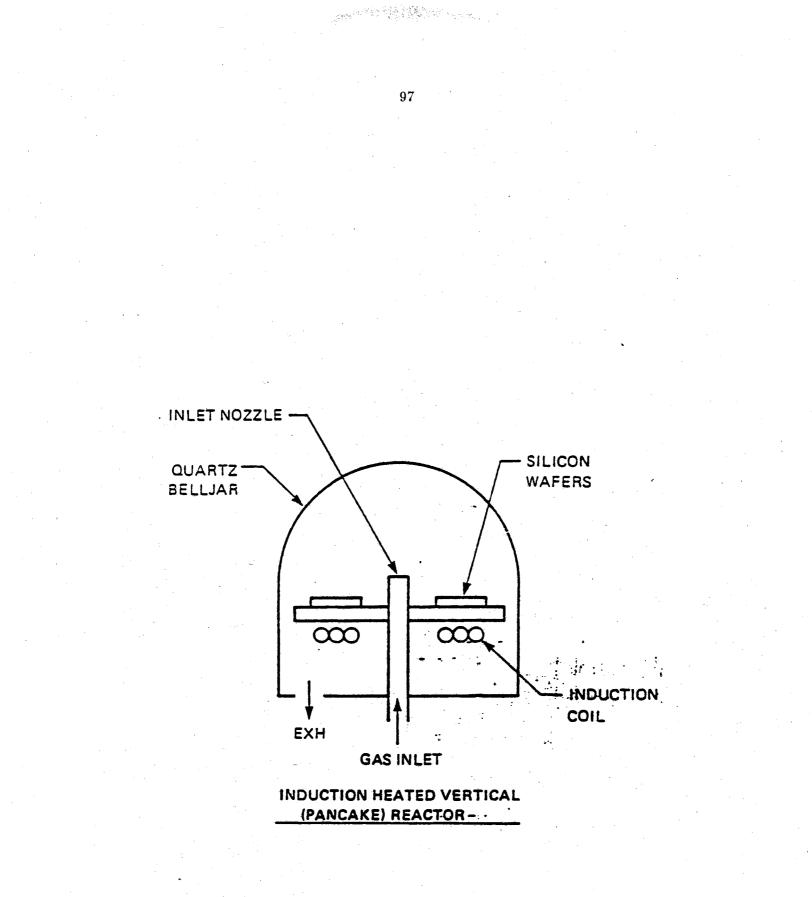

| 4.4.2.1 Reactor Description                     | 96     |

| 4.4.2.2 Reactor Feed Composition Dependence     |        |

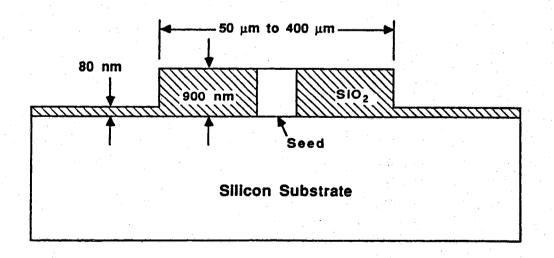

| 4.4.2.3 Masking Oxide Dependence                | 102    |

| 4.4.2.4 Temperature Dependence                  |        |

| 4.4.2.5 Total Flow Dependence                   | 112    |

| 4.4.2.6 Area Dependence                         | 113    |

| 4.4.3 Growth Mechanism                          |        |

| 4.5 ELO Planarization                           |        |

Page

|                                               | 19 A.                              |           | 1                                     |                                         | Page |

|-----------------------------------------------|------------------------------------|-----------|---------------------------------------|-----------------------------------------|------|

| CHAPTER 5 - ELECTR                            | ONIC DE                            | VICES     | -                                     | •••••                                   | 123  |

| 5.1 Introduction                              |                                    | *****     |                                       |                                         | 123  |

| 5.2 Interface States                          |                                    | ••••••••• |                                       |                                         | 123  |

| 5.3 Quasistatic D <sub>it</sub> Mea           | surement                           |           |                                       | •••••                                   | 126  |

| 5.3.1 Data Acquisiti                          | on                                 |           | · · · · · · · · · · · · · · · · · · · | •••••                                   | 127  |

|                                               |                                    |           |                                       |                                         |      |

| 5.3.2 Data Analysis<br>5.4 SOI Interface Char | acteristics                        |           |                                       | ••••••                                  | 136  |

| 5.5 3-D PMOS Transis                          | tors                               | •••••     | ••••••                                | • • • • • • • • • • • • • • • • • • • • | 144  |

| CHAPTER 6 - SUMMAR                            | and the<br>anti-<br>anti-<br>anti- |           |                                       |                                         |      |

|                                               | E.,                                |           |                                       |                                         |      |

| APPENDICES                                    | •••••                              | •••••     | ••••••                                |                                         | 178  |

| Appendix A                                    |                                    | •         |                                       |                                         | 178  |

| Appendix B                                    |                                    |           |                                       |                                         | 184  |

| Appendix C                                    |                                    |           | · · · · · · · · · · · · · · · · · · · |                                         | 192  |

| Appendix D                                    |                                    |           |                                       |                                         |      |

iv

## LIST OF TABLES

| Ta | ble Page                                                                                                                                                          |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | SOI technologies26                                                                                                                                                |

| 2  | Summary of device and material properties45                                                                                                                       |

| 3  | Polyoxide leakage at 5V Bias after 40 min.<br>exposure to SEG ambient at 950°C and 150 torr77                                                                     |

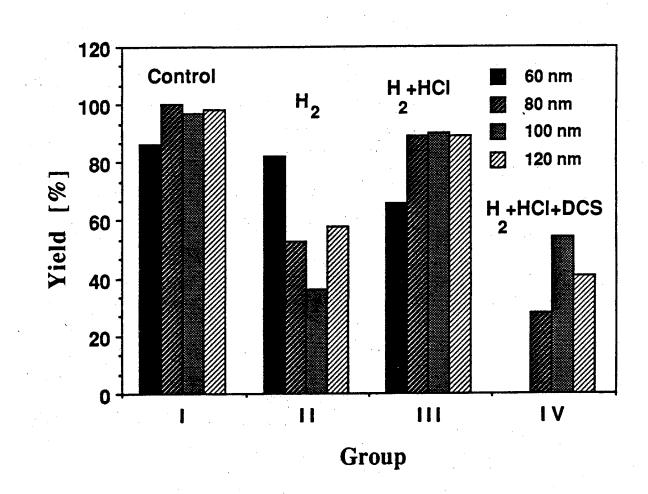

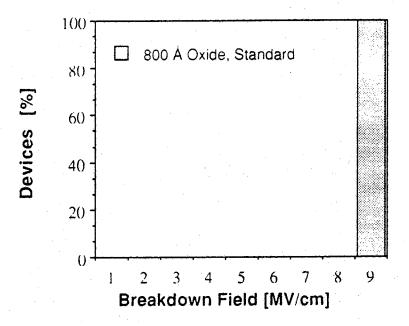

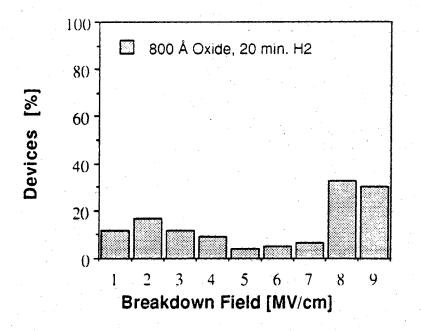

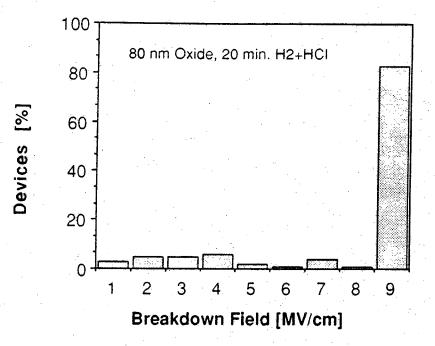

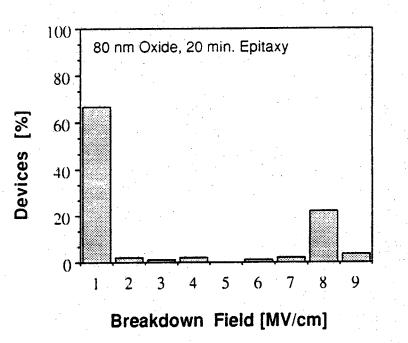

| 4  | Average breakdown field $\overline{E}$ , defect<br>density D, and standard deviation of breakdown<br>field $\sigma$ for the four different groups of 80 nm oxides |

| 5  | Preclean experiment matrix94                                                                                                                                      |

| 6  | Growth experiment matrix95                                                                                                                                        |

| 7  | Defects delineated by Secco etching95                                                                                                                             |

| 8  | Temperature dependence of growth from 0.36 vol % DCS in $H_2$ at 150 Torr109                                                                                      |

| 9  | Effect of total flow on growth rate113                                                                                                                            |

| 10 | Effect of wafer oxide coverage on growth rate and uniformity115                                                                                                   |

| 11 | Parameters of capacitors<br>fabricated under different processing conditions140                                                                                   |

## LIST OF FIGURES

Page

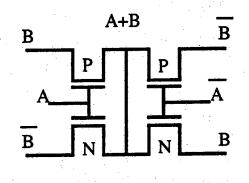

| 1.1 3-D CMOS Inverter                                             |    |

|-------------------------------------------------------------------|----|

| 1.2 Compact 3-D CMOS Inverter                                     | 4  |

|                                                                   |    |

| 2.1 Comparison of operational amplifier circuits in NMOS and CMOS | 9  |

| 2.2 Basic CMOS inverter circuit diagram                           | 11 |

| 2.3 CMOS EXOR circuit diagram                                     | 11 |

| 2.4 Two-input CMOS NAND gate                                      | 13 |

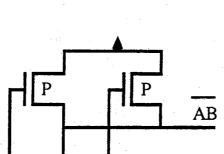

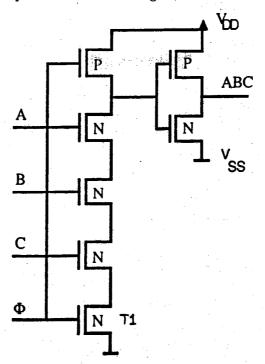

| 2.5 Three-input clocked CMOS NAND gate                            | 13 |

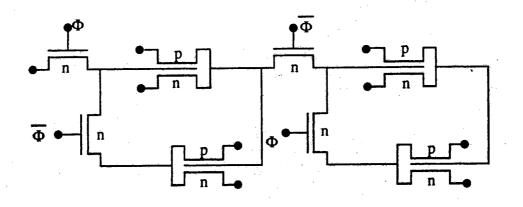

| 2.6 CMOS master-slave flip-flop                                   | 14 |

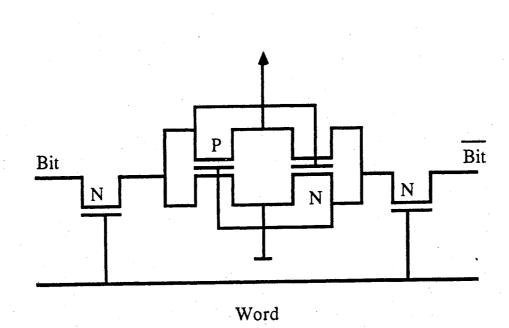

| 2.7 CMOS static RAM                                               | 16 |

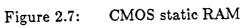

| 2.8 CMOS content addressable memory                               | 16 |

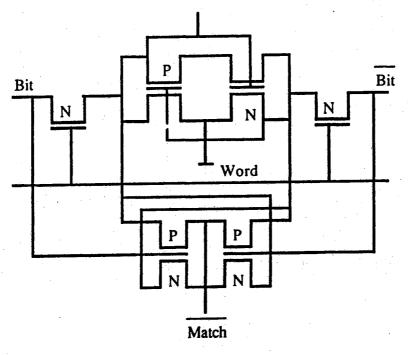

| 2.9 Twin-tub CMOS inverter cross section                          | 17 |

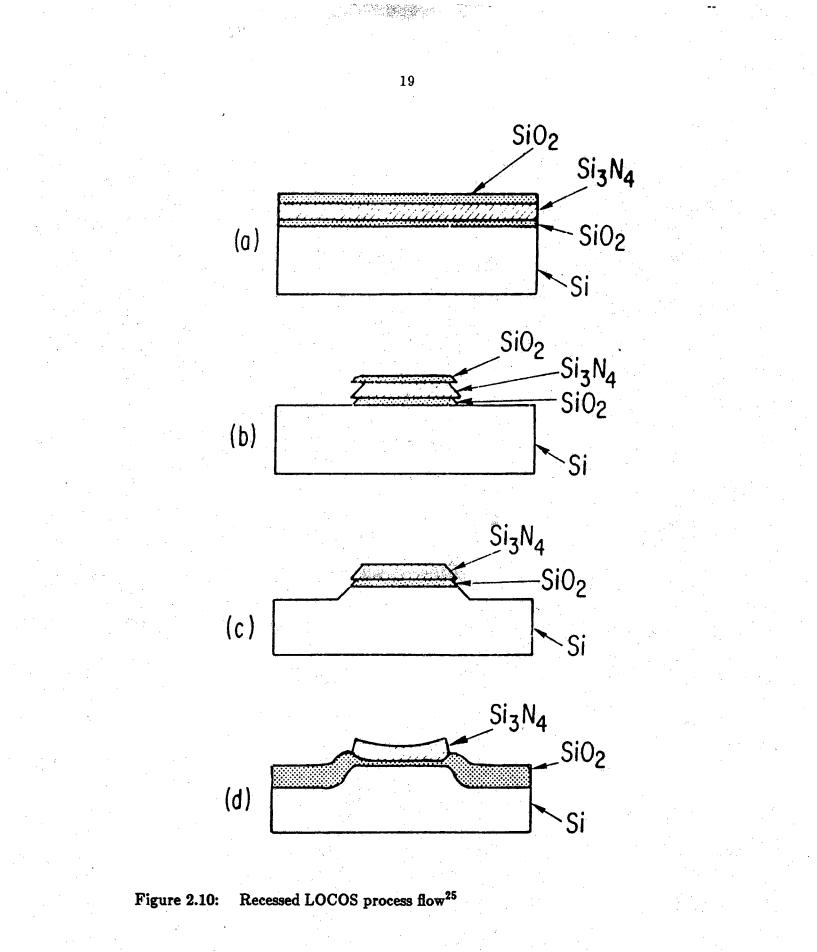

| 2.10 Recessed LOCOS process flow                                  |    |

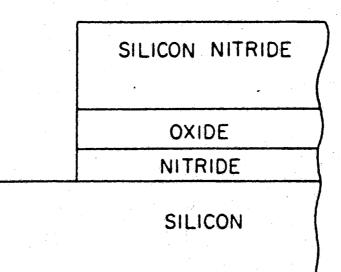

| 2.11 Sealed Interface Local Oxidation (SILO) structure            | 20 |

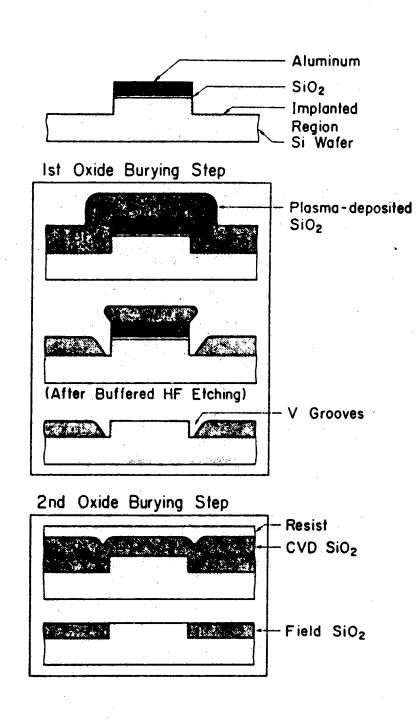

| 2.12 BOX fabrication sequence                                     |    |

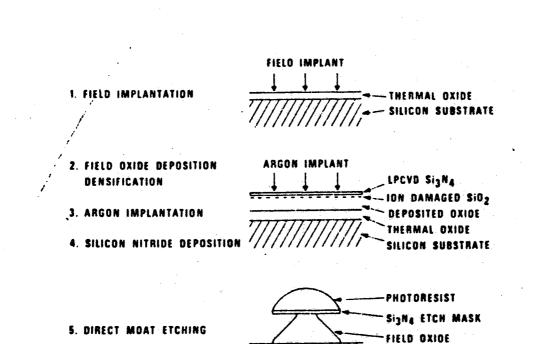

| 2.13 Direct moat isolation process sequence                       | 22 |

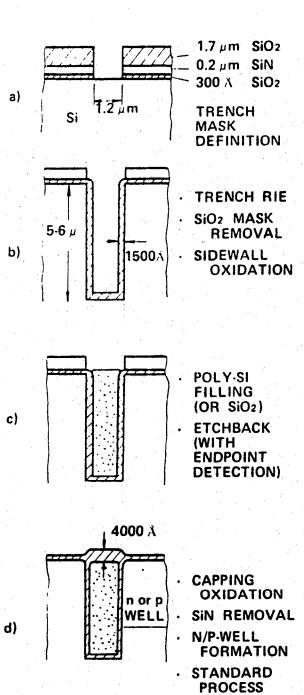

| 2.14 Trench isolation process flow                                | 23 |

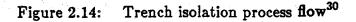

| 2.15 Dielectric isolation by Selective Epitaxial Growth           | 24 |

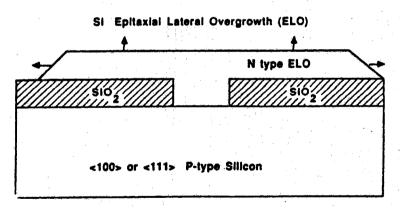

| 2.16 Selective epitaxy and epitaxial lateral overgrowth           | 32 |

| 2.17 Basic model of the epitaxial growth process                  | 33 |

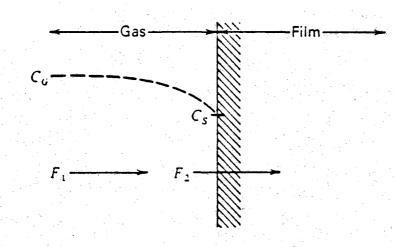

| 2.18 Growth rates of silicon films as a                           |    |

| function of temperature for various silicon gas sources           | 35 |

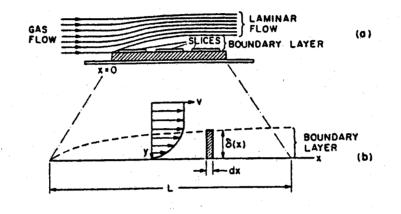

| 2.19 Development of a boundary layer in gas flowing over a flat   |    |

| plate and expanded view of boundary layer                         | 36 |

| 2.20 Undercutting of the $SiO_2/Si$ interface at 1150 ° C         |    |

| during a conventional in situ preclean in $H_2$ at 50 Torr        | 43 |

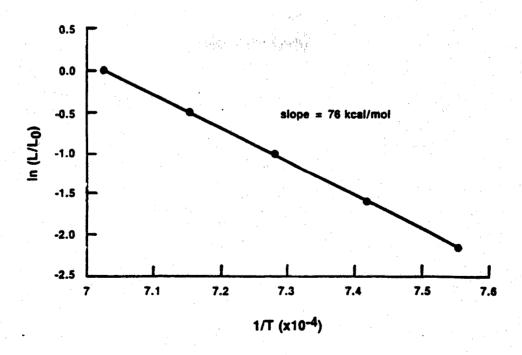

| 2.21 Arrhenius plot of undercutting length for                    |    |

| preclean in H <sub>2</sub> at 50 Torr                             | 43 |

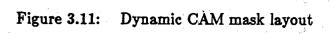

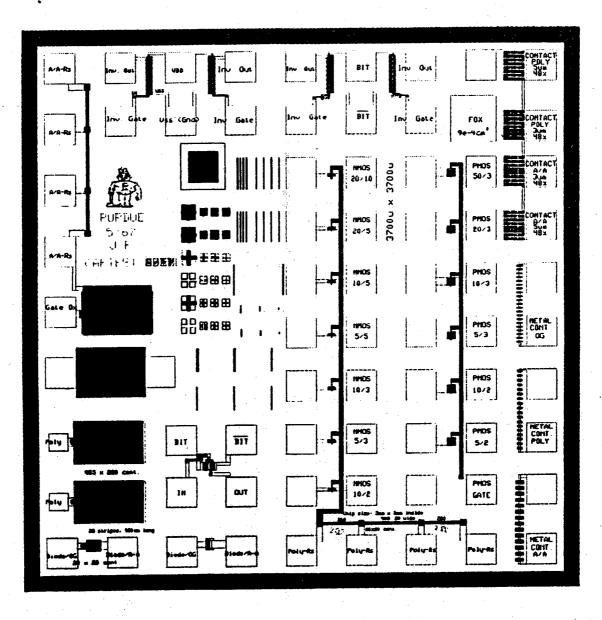

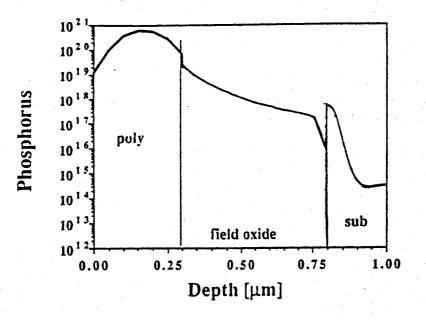

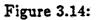

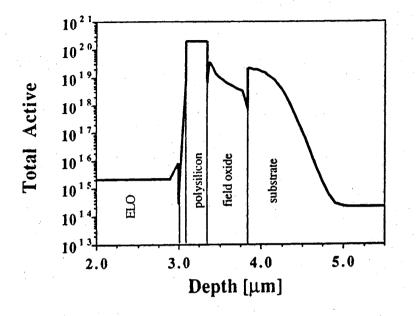

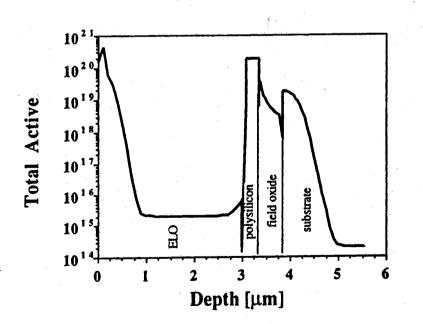

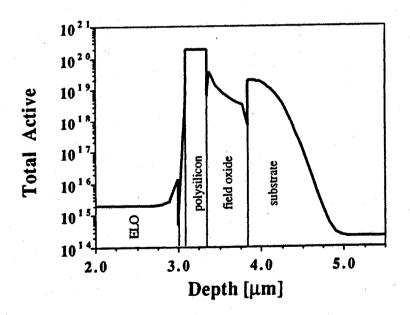

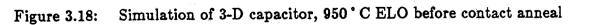

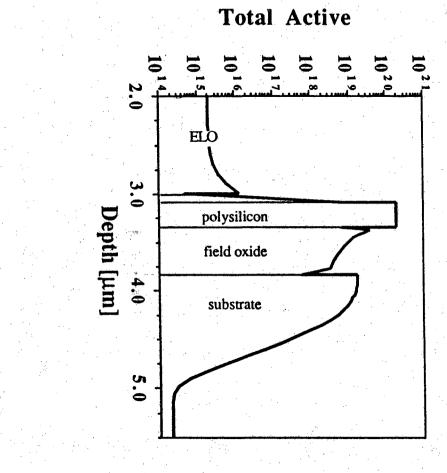

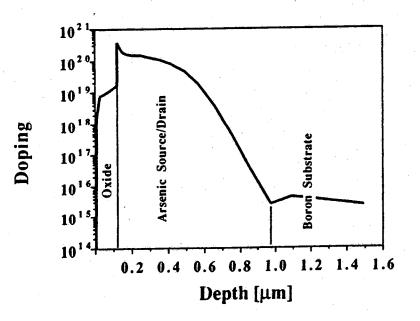

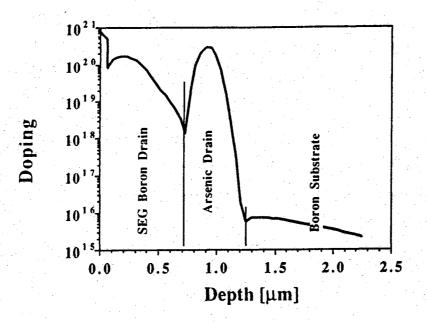

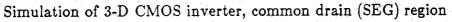

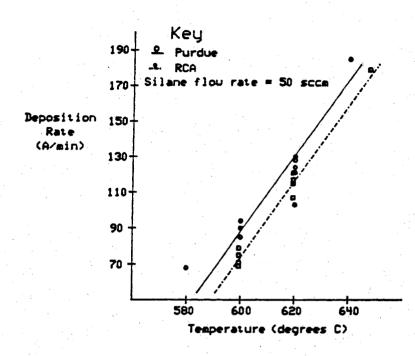

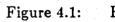

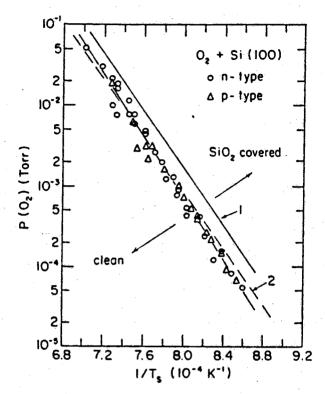

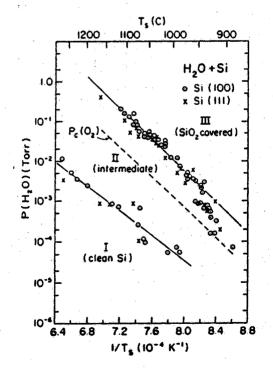

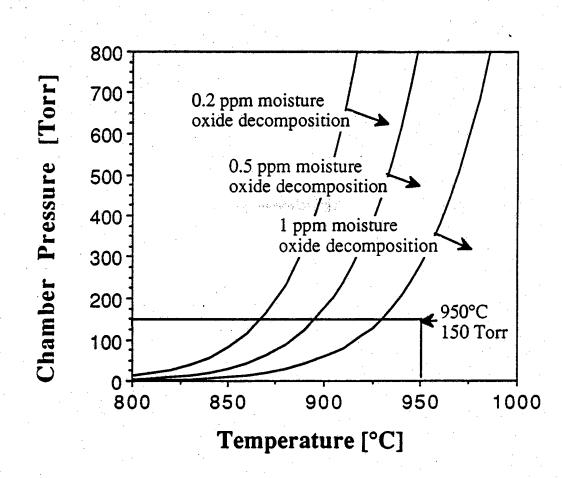

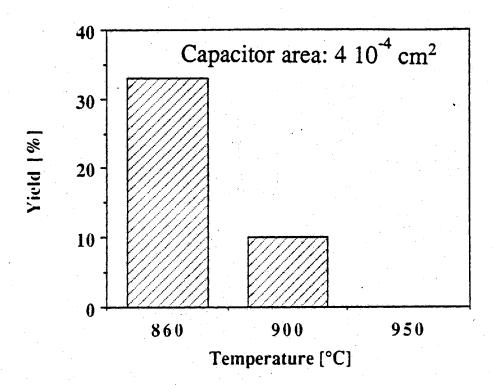

## 3.11 Dynamic CAM mask layout ......61 3.16 Simulation of 3-D capacitor, 860 °C ELO after 920 °C contact anneal ......65 3.20 Simulation of 3-D CMOS inverter, field oxide region ......70 3.21 Simulation of 3-D CMOS inverter, source/drain region ......70 3.22 Simulation of 3-D CMOS inverter, common drain (SEG) region......71 3.23 Simulation of 3-D CMOS inverter, gate/ELO region ......71 4.1 Polysilicon growth rate as a function of temperature ......74 4.2 Polysilicon growth rate as a function of doping......74 4.4 Breakdown field distribution for 80-nm control oxides (group I) ......81 4.5 Breakdown field distribution for 80-nm H<sub>2</sub> bake oxides (group II) ......81 4.6 Breakdown field distribution for 80-nm $H_2$ + HCl oxides (group III)......82 4.7 Breakdown field distribution for 80-nm $H_2$ + HCl + DCS oxides (group IV)......82 4.8 Regions of silicon dioxide growth as a 4.9 Regions of silicon dioxide growth as a

Page

## Page

ر د منی

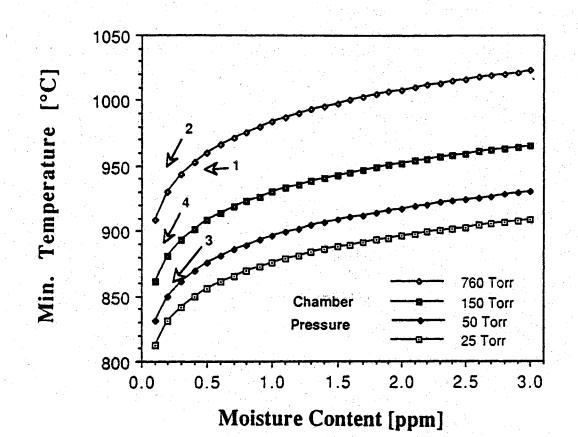

|   | 4.10 Critical conditions for oxide                                           |   |

|---|------------------------------------------------------------------------------|---|

|   | decomposition by SiO formation to take place                                 |   |

|   | 4.11 Yield for 3-D capacitors with epitaxy grown at                          |   |

|   | 860 ° C, 900 ° C, and 950 ° C87                                              |   |

|   | 4.12 Critical temperature vs carrier gas moisture content,                   |   |

|   | with reactor chamber pressure as a parameter90                               |   |

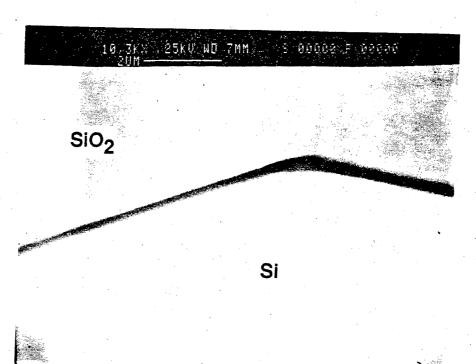

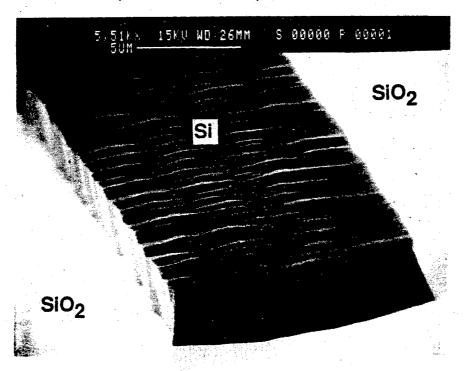

|   | 4.13 SEM of a seed precleaned at 150 Torr, above the                         |   |

|   | required minimum temperature (point 2 in Fig. 4.12)92                        |   |

| • | 4.14 SEM of a seed precleaned at 760 Torr, just below the                    |   |

|   | required minimum temperature (point 1 in Fig. 4.12)92                        |   |

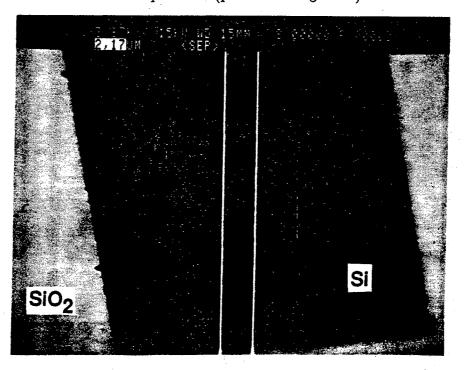

|   | 4.15 SEM of growth at 150 Torr, above the                                    | ÷ |

|   | required minimum temperature (point 4 in Fig. 4.12)                          |   |

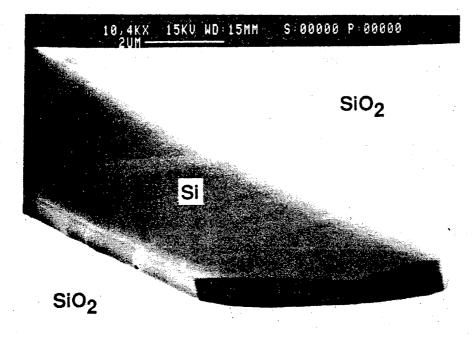

|   | 4.16 SEM of growth at 150 Torr, below the                                    |   |

|   | required minimum temperature (point 3 in Fig. 4.12)                          | • |

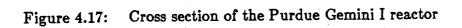

|   | 4.17 Cross section of the Purdue Gemini I reactor                            |   |

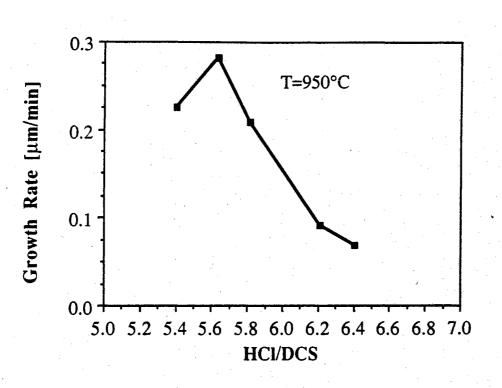

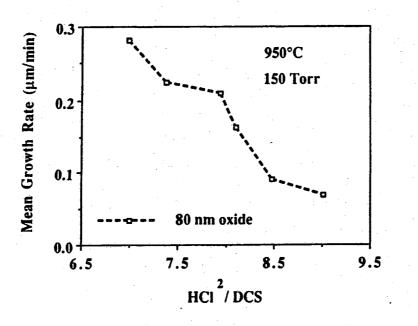

| • | 4.18 Growth rate vs. HCl/DCS ratio of feed100                                |   |

|   | 4.19 Growth rate vs. HCl <sup>2</sup> /DCS ratio of feed100                  |   |

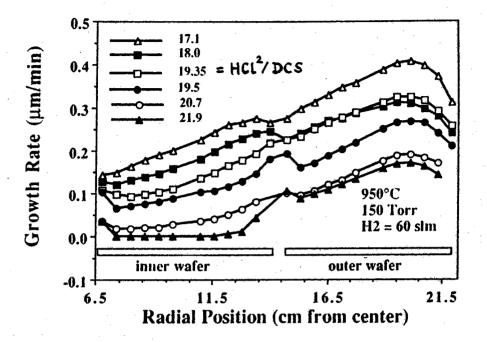

|   | 4.20 Growth rate profile for various feed gas compositions101                |   |

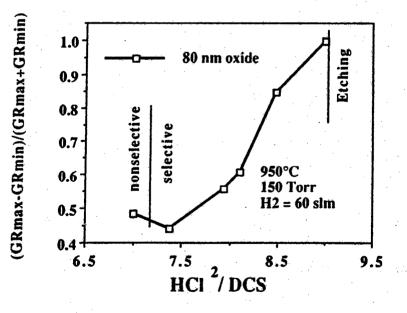

|   | 4.21 Non-uniformity as a function of feed gas composition101                 | 4 |

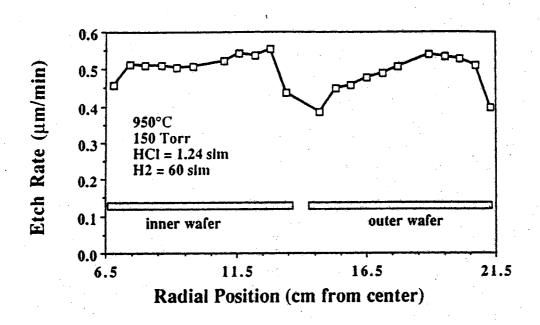

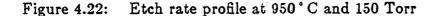

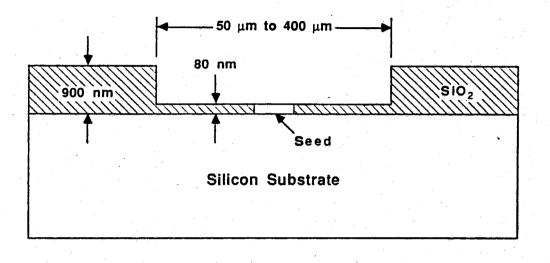

|   | 4.22 Etch rate profile at 950 °C and 150 Torr103                             |   |

|   | 4.23 Oxide thickness characterization test pattern cross section104          |   |

|   | 4.24 Oxide thickness characterization inverted test pattern104               |   |

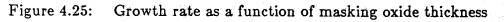

|   | 4.25 Growth rate as a function of masking oxide thickness106                 |   |

|   | 4.26 Growth rate as a function of masking oxide thickness                    |   |

|   | compared to a model where only thermal conduction is considered106           |   |

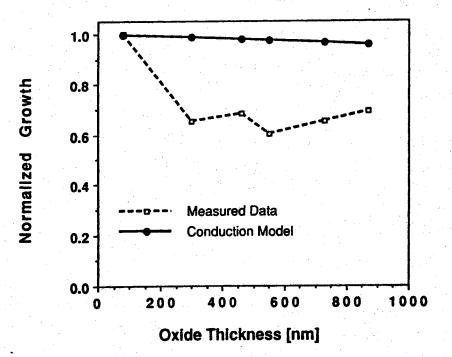

|   | 4.27 Bulk (unmasked) silicon growth rate                                     |   |

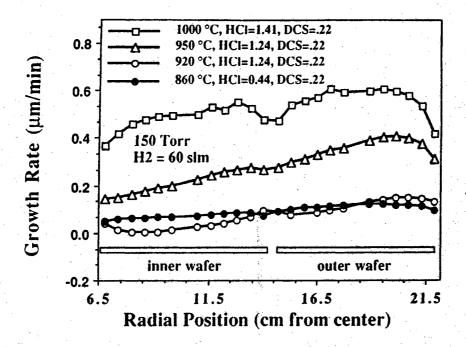

|   | profiles at 920 ° C, 950 ° C, and 1000 ° C110                                |   |

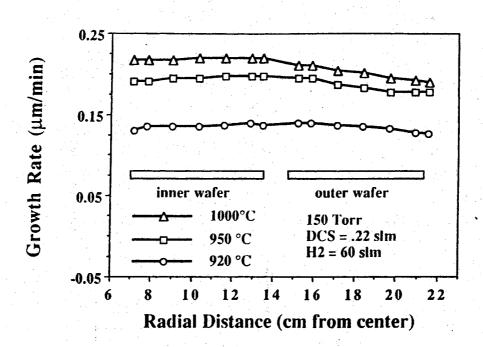

|   | 4.28 Selective epitaxy growth rate profile                                   |   |

|   | on unpatterned wafers at 950 °C and 1000 °C110                               |   |

|   | 4.29 Selective epitaxy growth rate profile on                                |   |

|   | patterned wafers at 860 °C, 920 °C, 950 °C, and 1000 °C112                   |   |

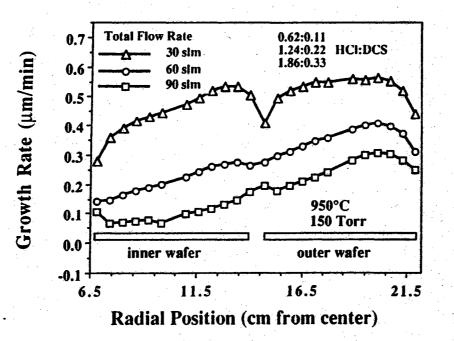

|   | 4.30 Effect of total gas flow on selective epitaxial growth rate profile112  |   |

|   | 4.31 Effect of masking oxide coverage                                        |   |

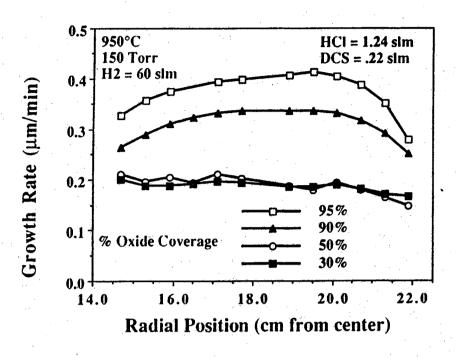

|   | on selective epitaxial growth rate profile114                                |   |

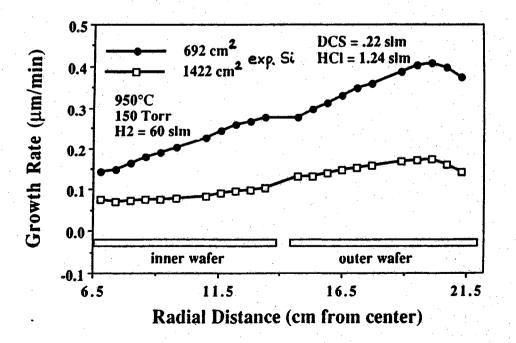

|   | 4.32 Effect of reactor loading on selective epitaxial growth rate profile114 |   |

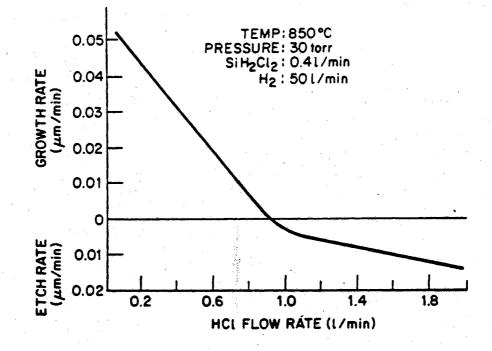

|   | 4.33 Growth rate as a function of HCl/DCS ratio at 850 °C and 30 Torr117     |   |

|   |                                                                              |   |

viii

$\epsilon_{\rm eff}$

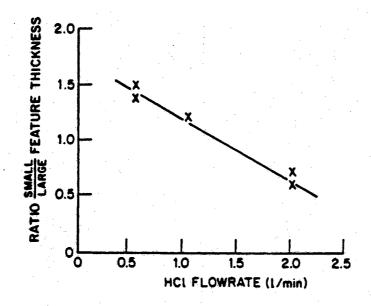

| 4.34 | Effect of HCl flow on the thickness ratio between a $5\mu m$ and a |

|------|--------------------------------------------------------------------|

|      | 50 $\mu$ m aperture on a patterned wafer117                        |

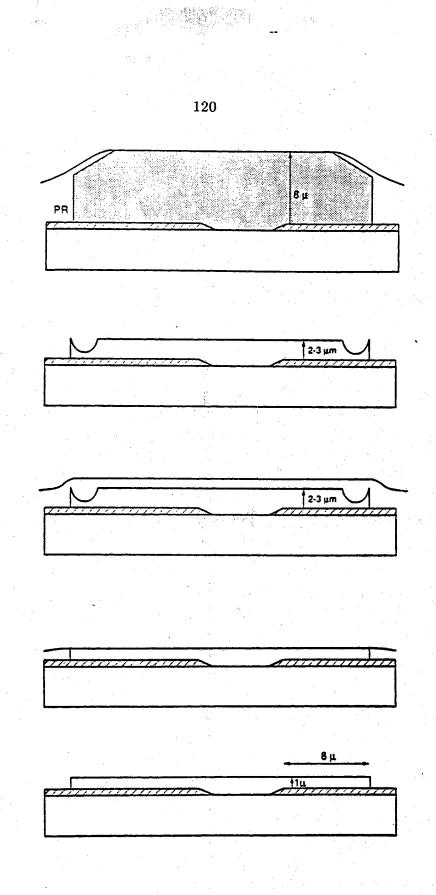

| 4.35 | Planarization procedure by resist reflow and plasma etching120     |

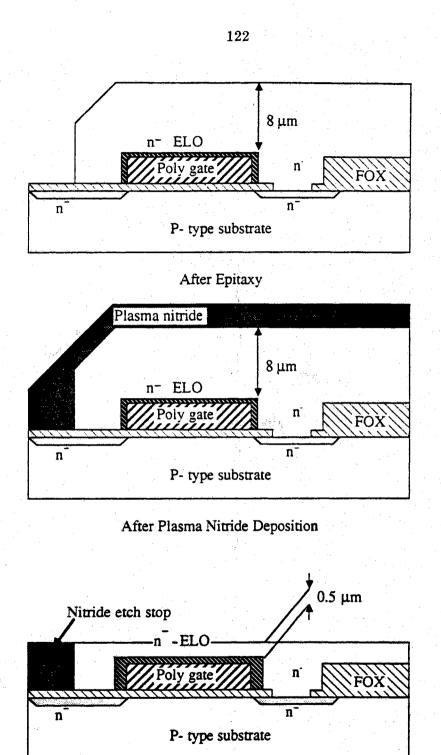

| 4.36 | Planarization by preferential polishing122                         |

|      |                                                                    |

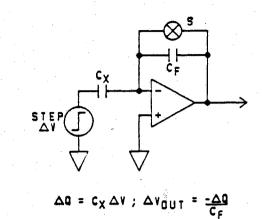

| 5.1  | Quasi-static C-V measurement instrumentation128                    |

| 5.2  | Quasi-static C-V measurement timing diagram128                     |

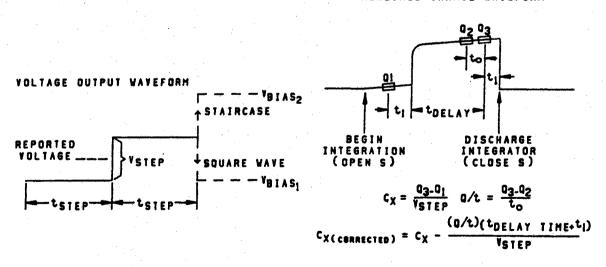

| 5.3  | HF-LF C-V measurement instrumentation set-up129                    |

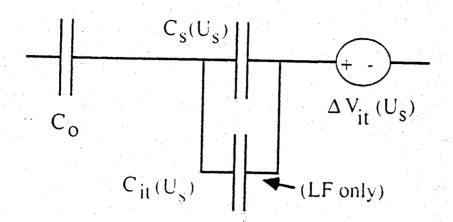

| 5.4  | MOS capacitor small signal equivalent circuit131                   |

| 5.5  | Overetched polysilicon finger structure134                         |

| 5.6  | Total high-frequency capacitance exhibiting lateral effects        |

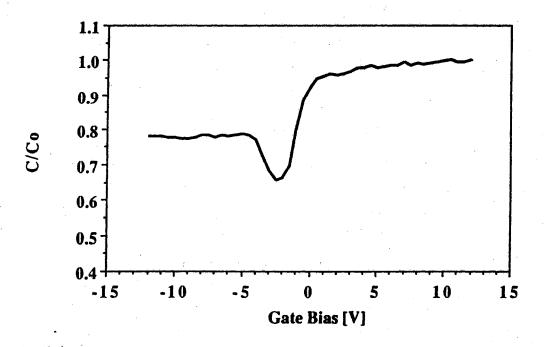

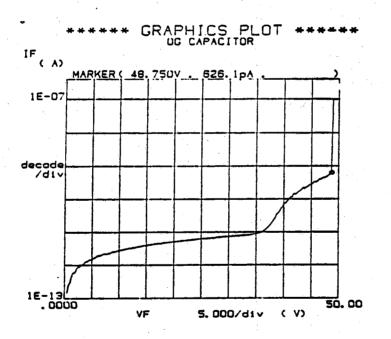

| 5.7  | I-V curve for ELO capacitor with epitaxy grown at 900 ° C137       |

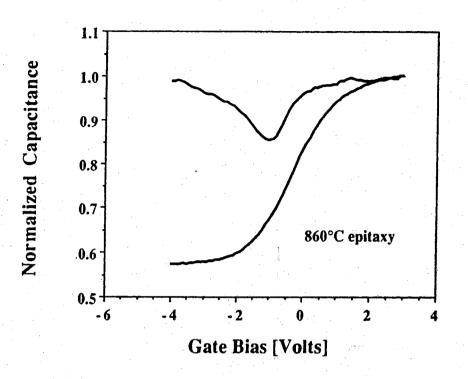

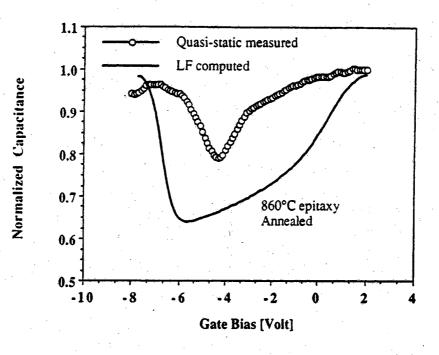

| 5.8  | Capacitance $C_{ELO}$ for epitaxy grown at 860 ° C                 |

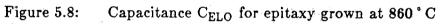

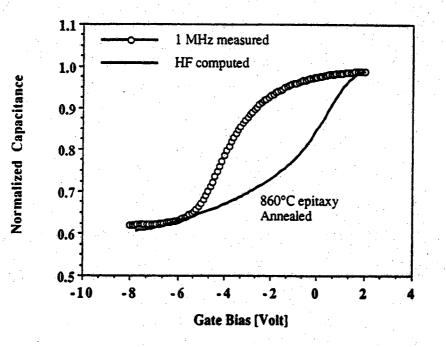

| 5.9  | Capacitance C <sub>ELO</sub> for epitaxy grown at 900 ° C139       |

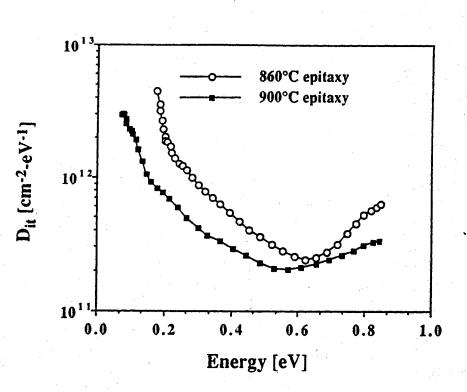

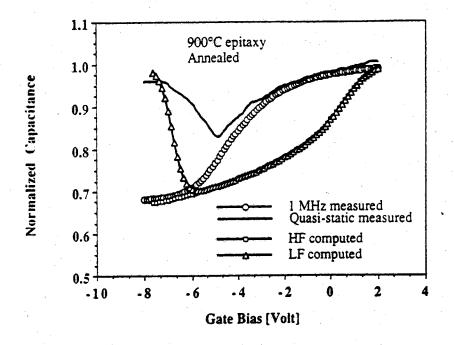

| 5.10 | Interface state density $D_{it}$ as a function of band gap energy  |

|      | for epitaxy done at 860 ° C and 900 ° C141                         |

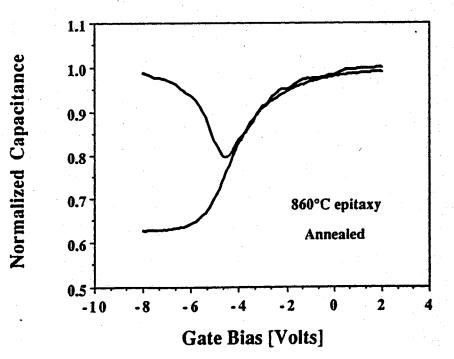

| 5.11 | Capacitance $C_{ELO}$ for epitaxy grown at 860 ° C,                |

|      | after 10 min. anneal in H <sub>2</sub> at 1000 $^{\circ}$ C141     |

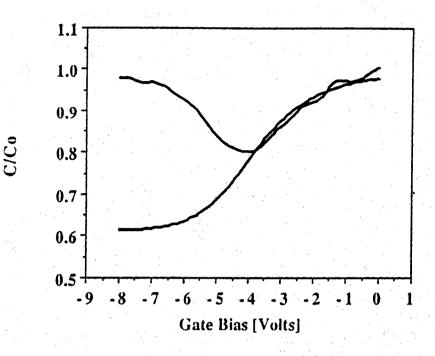

| 5.12 | Capacitance $C_{ELO}$ for epitaxy grown at 900 ° C                 |

|      | after 10 min. anneal in H <sub>2</sub> at 1000 ° C143              |

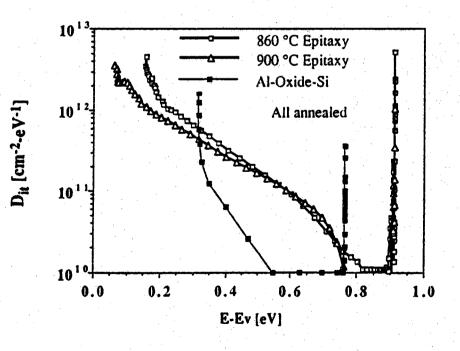

| 5.13 | Interface state density $D_{it}$ as a function of band gap energy  |

|      | for epitaxy done at 860 °C and 900 °C, after 10 min. anneal        |

|      | in H <sub>2</sub> at 1000 ° C143                                   |

| 5.14 | Comparison of experimental and ideal LF C-V curve for epitaxy      |

|      | grown at 860 ° C145                                                |

| 5.15 | Comparison of experimental and ideal HF C-V curve for epitaxy      |

|      | grown at 860 ° C145                                                |

| 5.16 | Comparison of experimental and ideal LF and HF C-V curves          |

|      | for epitaxy grown at 900 ° C146                                    |

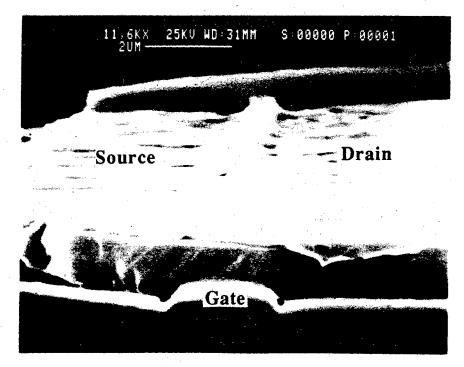

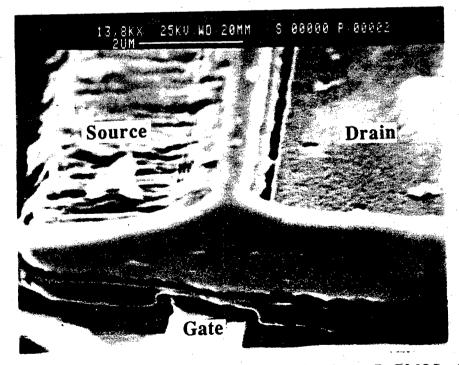

| 5.17 | Scanning electron beam micrograph of a 3-D PMOS stacked            |

|      | transistor with 1.4 $\mu m$ thick overgrowth146                    |

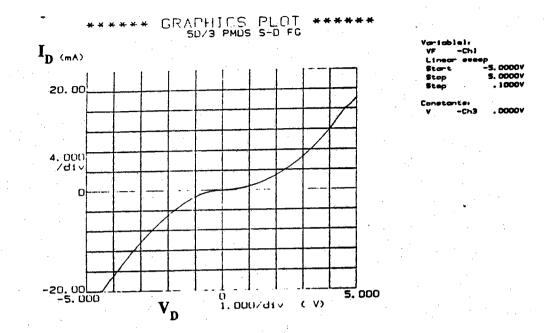

| 5.18 | I-V characteristics of bad 3-D stacked PMOS transistor             |

|      | with source-drain short circuit149                                 |

Page

. 13.

ann e

2

| 5.19 Scanning electron beam micrograph of a 3-D 1                    | PMOS stacked    |

|----------------------------------------------------------------------|-----------------|

| transistor with 0.8 $\mu m$ thick overgrowth                         |                 |

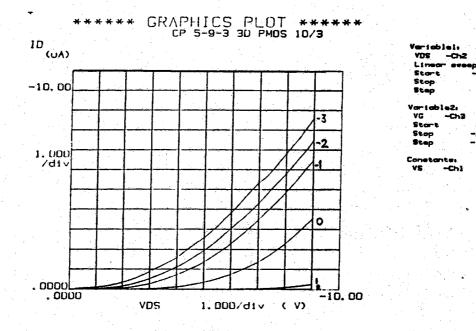

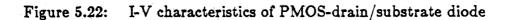

| 5.20 $I_D$ vs $V_{DS}$ characteristics of field effect modula        | ated            |

| 3-D stacked PMOS transistor                                          |                 |

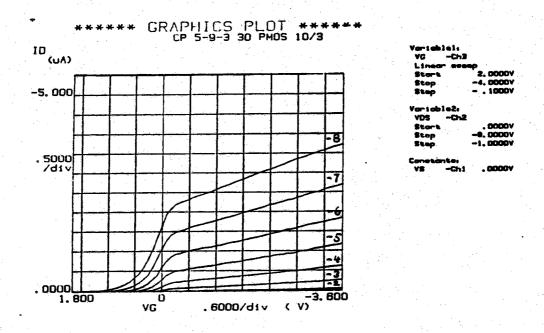

| 5.21 $I_D$ vs V <sub>G</sub> characteristics of field effect modulat | ted             |

| 3-D stacked PMOS transistor                                          |                 |

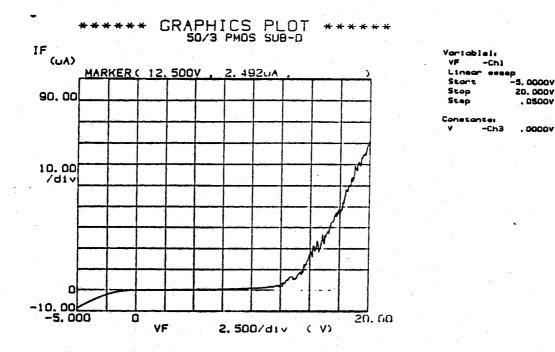

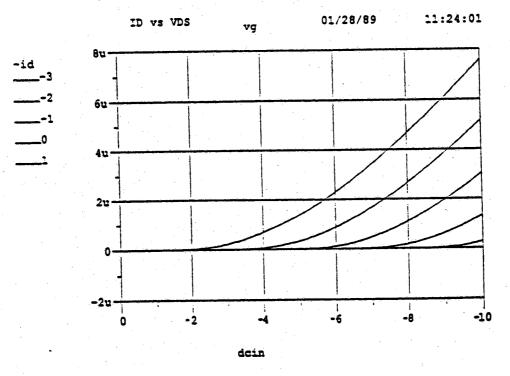

| 5.22 I-V characteristics of PMOS-drain/substrate of                  | liode152        |

| 5.23 SPICE simulation output of extreme short cha                    | annel MOSFET152 |

X

## ABSTRACT

Friedrich, Joerg, Purdue University. May 1989. Three-Dimensional MOS Process Development. Major Professor: Neudeck, Gerold W.

A novel MOS technology for three-dimensional integration of electronic circuits on silicon substrates was developed. Selective epitaxial growth and epitaxial lateral overgrowth of monocrystalline silicon over oxidized silicon were employed to create locally restricted silicon-on-insulator device islands.

Thin gate oxides were discovered to deteriorate in ambients typically used for selective epitaxial growth. Conditions of general applicability to silicon epitaxy systems were determined under which this deterioration was greatly reduced.

Selective epitaxial growth needed to be carried out at low temperatures. However, crystalline defects increase as deposition temperatures are decreased. An exact dependence between the residual moisture content in epitaxial growth ambients, deposition pressure, and deposition temperature was determined which is also generally applicable to silicon epitaxy systems.

The dependences of growth rates and growth rate uniformity on loading, temperature, flow rates, gas composition, and masking oxide thickness were investigated for a pancake type epitaxy reactor. A conceptual model was discussed attempting to describe the effects peculiar to selective epitaxial growth.

The newly developed processing steps were assembled to fabricate threedimensional silicon-on-insulator capacitors. These capacitors were electrically evaluated. Surface state densities were in the order of  $10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup> and therefore within the range of applicability for a practical CMOS process.

Oxidized polysilicon gates were overgrown with silicon by epitaxial lateral overgrowth. The epitaxial silicon was planarized and source and drain regions were formed above the polysilicon gates in silicon-on-insulator material. The modulation of the source-drain current by bias changes of the buried gate was demonstrated.

## CHAPTER 1

#### INTRODUCTION

### 1.1 Background

Initial attempts to build active solid-state transistors that operated on a field effect principle were undertaken by J.E. Lilienfeld in the early 1930s. Patents on a metal-oxide-semiconductor (MOS) structure were filed in 1935 by O. Heil and later by D. Kahng and M.M. Atalla who proposed a Si-SiO<sub>2</sub> based field effect transistor. Not until the early 1960s however was the fabrication of MOSFETs successful because of the lack of a controllable and stable silicon surface. With the introduction of the silicon planar process it became possible to create stable insulating layers on top of silicon by means of thermal oxidation. In 1964 the first simple integrated circuits (ICs) with MOS transistors were fabricated.

The first complex circuits were built using p-channel, and later n-channel transistors. In 1962, C.T. Sah and F. Wanlass proposed the pairing of complementary n-channel and p-channel transistors to form low-power integrated circuits. For over a decade after its invention, this technology, which in fact is as much a circuit technology as a processing technology, called "Complementary MOS" or CMOS, had its primary use only in specialty applications where the benefits of low power consumption and high noise immunity outweighed the higher production costs.

With the need for increased device density and shrinking dimensions, NMOS technologies became more and more complex. In the late 1970's it became apparent that power dissipation would set a limit on the level of integration of NMOS circuits. At that time, the complexities of advanced NMOS and CMOS process technologies were comparable, and CMOS became a viable alternative to NMOS which had been dominating the field. Today CMOS has developed into the technology of choice for Very Large Scale Integration (VLSI) and Ultra Large Scale Integration (ULSI). Currently it is possible to integrate more than 500000 transistors in non-repetitive circuit designs such as microprocessors, and more than 4 million transistors in regular circuit designs such as random access memories.

### 1.2 Statement of Purpose

The development of process technologies is driven by the demand for more powerful systems, such as computers and signal processing equipment. Current two-dimensional planar CMOS technologies will have reached their performance limits soon, making it necessary to develop more sophisticated processes that eliminate or greatly reduce the key problems found in conventional technologies. Three-dimensional integration, first at the interconnect level, and later at the active device level, has potential to significantly increase the complexity of monolithically integrated systems.

In addition to lithographic restrictions, scaling of CMOS technologies is limited by the required large spacing between transistors of different type, in order to prevent latch-up which can render a circuit temporarily or permanently inoperable. Furthermore, susceptibility to radiation increases as device dimensions shrink. Studies on VLSI interconnects suggest that as the lateral spacing between adjacent metal lines approaches the 0.5  $\mu$ m level, the increased mutual capacitance between neighbouring lines and not the intrinsic switching speed of the active devices themselves will become the limiting factor in circuit performance, density and power dissipation for integrated circuits fabricated using two-dimensional planar silicon technology. <sup>1,2</sup> For these reasons, there has long been interest in silicon-on-insulator (SOI) and threedimensional technologies, which would imply higher operating speed, lower dynamic power consumption, greater packing density, increased radiation hardness, more layout flexibility, and immunity to latch-up.

However, single crystalline silicon is not easily formed on top of amorphous insulating material such as  $SiO_2$ . Crystalline insulators have been devised, such as sapphire and calcium fluorides, which match the lattice spacing of silicon reasonably close. Other methods of creating SOI include zonemelting recrystallization of polysilicon deposited by standard chemical vapor deposition techniques, separation by implanted oxygen, lateral solid-phase epitaxy, and full insulation by porous oxidized silicon. All these methods have in common that they are either prohibitively expensive, lead to poor quality SOI layers, or are incompatible with common clean room processing technologies.

3

The primary goal in SOI is to realize perfect silicon on top of an insulator. There exist stringent requirements that SOI technologies have to meet. For example, all SOI processing steps have to be IC compatible which would exclude the use of extreme high temperature anneal steps. All SOI processing has to be clean room compatible, which may exclude technologies such as SOI by wafer bonding and thinning by polishing. Also, an SOI technology should be economically feasible. For that reason batch processing capability would be preferred over single wafer processing. Lastly, the SOI technology should allow for three-dimensional integration of active device layers.

To date, no single SOI technology has been able to meet all these demands. The purpose of this work was to develop a new CMOS SOI technology, by epitaxial lateral overgrowth of silicon over oxidized silicon to form a second active device layer. This new SOI technology was designed to meet most of the demands stated above.

#### **1.3** Proposed Structure

There is a need to have a CMOS technology that allows for the threedimensional integration of active devices, where stringent boundary conditions limit the methods by which the required SOI layers can be obtained. In 1982, J.F. Gibbons and K.F. Lee<sup>3</sup> proposed a CMOS inverter with stacked transistors to form silicon-on-insulator device islands. Their method of 3-D integration included the recrystallization of the polysilicon top substrate. Although the design was simple and basically compatible with well established IC fabrications methods, this approach lead to high defect densities in the recrystallized material itself and to damage of the underlying layers.

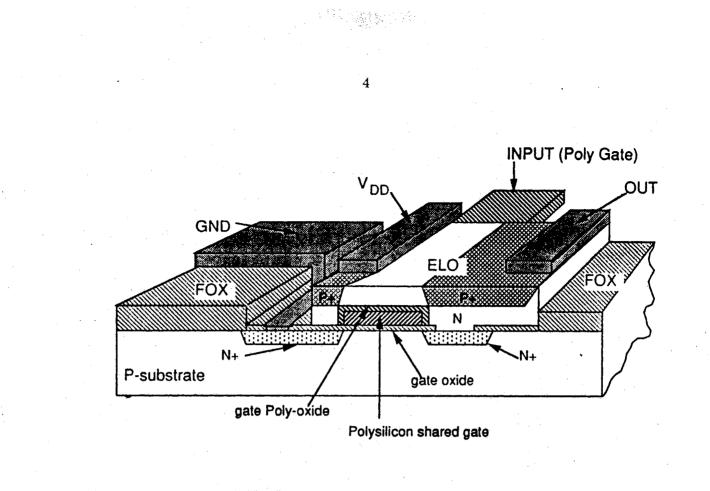

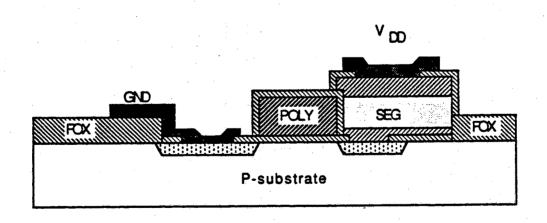

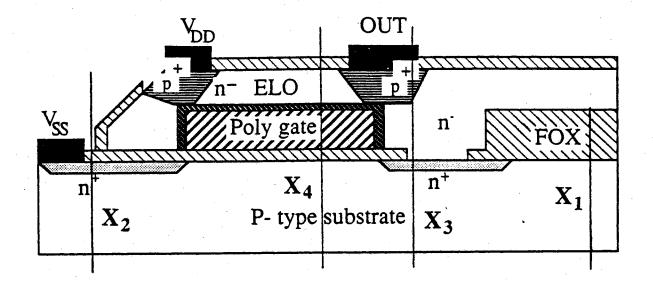

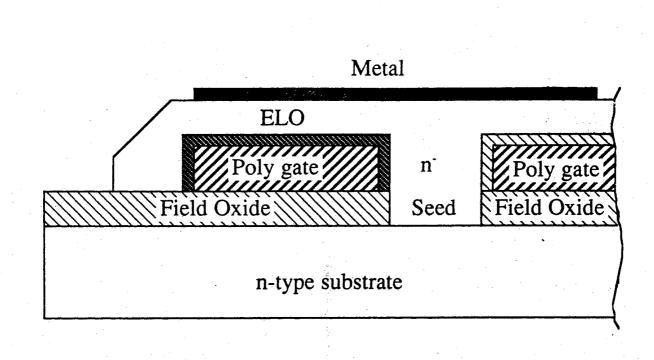

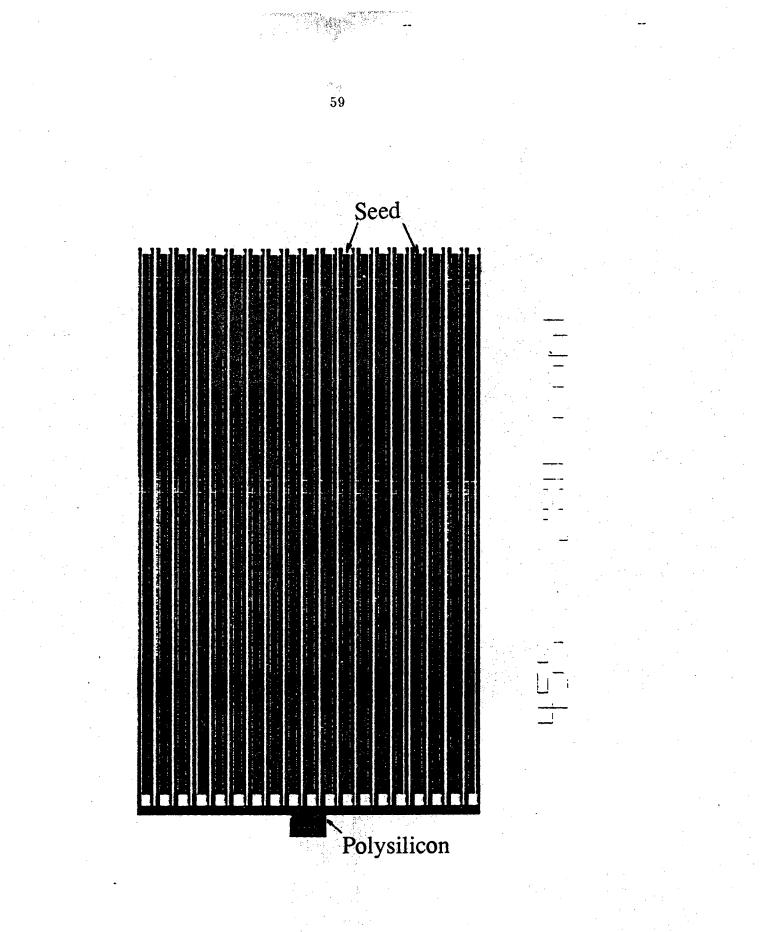

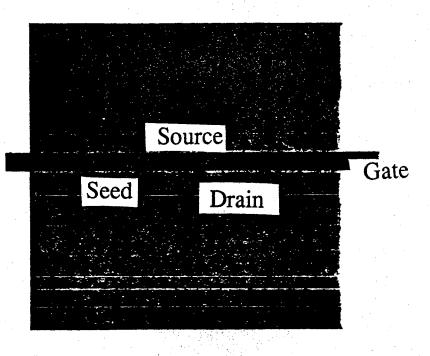

Also in 1982, K. Tanno *et al.*<sup>4</sup> reported on selective epitaxial growth (SEG) of silicon in a reduced temperature, reduced pressure epitaxial reactor. Soon thereafter methods were proposed to create SOI structures by extending the SEG of silicon towards epitaxial lateral overgrowth (ELO). In 1984, B. Hoefflinger and S.T. Liu proposed to build CMOS inverters with stacked transistors, structurally similar to the design by Gibbons and Lee, but where the second active device layer was to be formed by epitaxial lateral overgrowth (Fig. 1.1). A more planar structure by S.T. Liu following a similar approach is shown in Fig. 1.2. Here the SEG is not extended over the polysilicon gate, and the PMOS transistor is formed along the gate sidewall.

Figure 1.1: 3-D CMOS Inverter

## Figure 1.2: Compact 3-D CMOS Inverter

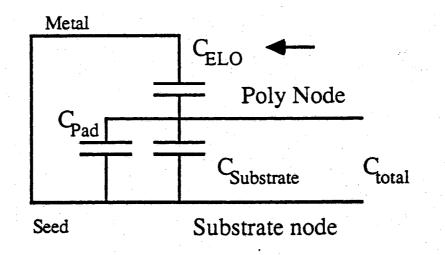

The stacking of transistors can greatly reduce the area required to build circuits. The method by which this stacking is accomplished inherently leads to a monocrystalline second active device layer. For the structure as shown in Fig. 1.2, the sidewall transistor can have effective gate lengths that are much smaller than the lithographical resolution. The key steps in this new process technology are selective epitaxial growth and epitaxial lateral overgrowth of monocrystalline silicon. These methods are economical batch processes, and integrate well into clean room environments. Epitaxy can be carried out at low temperatures, so that significant movement of junctions already incorporated in the substrate can be avoided.

## 1.4 Thesis Overview

This thesis describes the development and investigation of a process technology that allows for the fabrication of three-dimensional silicon-on-insulator MOS structures created by the epitaxial lateral overgrowth or selective epitaxial growth of single crystalline silicon over thermally oxidized polysilicon gates, as shown in Fig. 1.1 and Fig. 1.2. The electronic interface of the stacked PMOS transistor, created by the epitaxial overgrowth of thermally oxidized polysilicon rather than by conventional thermal oxidation of monocrystalline silicon is investigated in depth. This novel ELO-Si/polyoxide/polysilicon interface is not just important for active devices in SOI but also for dielectric device isolation techniques by selective epitaxial growth that have already been proposed and realized elsewhere.

Chapter 2 contains a review of the relevant literature on conventional CMOS technologies and advanced device isolation concepts, including currently known SOI technologies, selective epitaxial growth, and epitaxial lateral overgrowth.

Chapters 3 and 4 describe the process sequence development for the shared gate silicon-on-insulator structure by epitaxial lateral overgrowth. In Chapter 3 test devices and structures are discussed and process simulations are contemplated. Also, the test pattern layout used throughout the experimental work is presented.

Chapter 4 reports on the various steps of the new technology and their development. Focus is placed on an in-depth investigation of epitaxy at reduced pressures and temperatures and gate oxide quality. The electrical characterization of the fabricated test structures, namely 3-D stacked capacitors and 3-D PMOS transistors, is reported in Chapter 5. The measurement apparatus is described, and functionality of the test devices is demonstrated. In Chapter 6, the investigation is summarized and recommendations for future work are given.

## CHAPTER 2

### LITERATURE REVIEW

## 2.1 Introduction

Over the last several years, integrated circuit technology, driven by demanding new applications, has advanced at a rapid pace. During the last 20 years, the functional density of integrated circuits has increased 200-fold, and speed has increased 20-fold. VLSI has been employed in solving computationally intensive problems in the fields of artificial intelligence and signal processing. In many cases particularly in the field of information processing it is now more cost effective to design application specific integrated circuits (ASIC) than to employ a high-performance general purpose computer.

From all the available processing technologies, CMOS has emerged as the single most important one for VLSI and ULSI.<sup>5-11</sup> The SOI technology developed in this thesis work is essentially part of a CMOS technology. For this reason, two areas of research are reviewed. The first part of this chapter summarizes issues regarding conventional CMOS circuit<sup>12-14</sup> and process design methodologies. The second part gives a brief overview over different SOI technologies, and then focuses on SOI by ELO and on epitaxy itself, as they constitute key processing steps in the newly developed SOI technology. General processing subjects such as oxidation, chemical vapor deposition (with the exception of epitaxy), and lithography are not within the scope of this review.

### 2.2 Background

CMOS devices were first fabricated employing metal gate electrodes. The principal merit of CMOS technology at that time was its low power consumption as compared to the less complex, more cost effective, and widely used unipolar MOS technologies. For that reason it found its principal applications in battery powered consumer appliances such as wrist watches and pocket calculators, and in aeronautical equipment. During the 1970's, NMOS became the dominant technology for Large Scale Integration (LSI), with refinements such as polysilicon gates, self aligned source and drain regions, and highly resistive polysilicon loads. As device dimensions shrunk and the complexity of systems that could be integrated monolithically rapidly increased it became apparent that power dissipation due to the required steady current flow through the transistors would soon limit the level of integration possible in NMOS technologies. Because of its near-zero quiescent current, CMOS became the technology of choice for VLSI circuit integration.

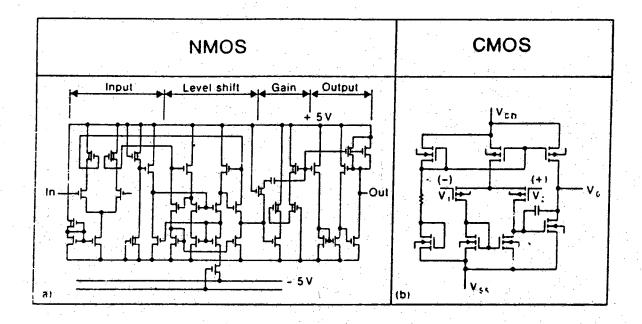

Beside its low power consumption, CMOS has several other important advantages over bipolar and unipolar MOS technologies. It accepts a wide tolerance in parameter variations such as power supply voltage and temperature. CMOS requires only small drive currents and is less sensitive to backgate biasing than NMOS or PMOS. No bootstrapping is required to feed a signal through a chain of clocked inverters, since no threshold voltage loss occurs. It has excellent noise immunity and soft error protection. The ratio-less design allows for flexibility in circuit layout, which facilitates the use of cell libraries and automated design environments. The high layout symmetry of CMOS is of advantage in analog circuits, thereby making it easy to integrate analog and digital function on the same chip. Operational amplifiers can be integrated in CMOS occupying considerable less area than bipolar or NMOS amplifiers, as illustrated in Fig. 2.1. CMOS furthermore allows for the symmetric operation about the ground potential, and CMOS switches have no offset voltage.

CMOS process technologies are challenging with regard to obtaining high-quality n- and p-channel devices on the same wafer. CMOS also introduces a unique problem named "latchup", where a parasitic bipolar structure can short-circuit transistors of opposite polarity and render the circuit temporarily or permanently inoperable. CMOS usually requires more transistors per function than unipolar technologies, although circuit design methods exist where this is circumvented. Compared with bipolar technologies, CMOS has smaller current drive capabilities, is sensitive to electrostatic discharge, has less gain, and exhibits higher 1/f noise, mostly due to surface states. These disadvantages are the main reason that considerable development work is put into combined bipolar-CMOS (BiCMOS) technologies, <sup>15</sup> since there the strength of each technology can be exploited without having to deal with the restrictions.

Figure 2.1: Comparison of operational amplifier circuits in NMOS and CMOS<sup>12</sup>

Today, MOSFETs with good characteristics have been fabricated with effective gate lengths down to 0.1  $\mu$ m. The estimated propagation delay time for gates in these technologies is in the order of 20 ps.

## 2.3 CMOS Circuit Design

As has been mentioned previously, CMOS is as much a processing technology as it is a circuit technology. The link between circuit and process design has become increasingly more important, as circuit and system performance ultimately set the requirements for device and process technology performance. Generally one likes to have systems operate at great speed, and because of cost reasons the minimization of the wafer area occupied by a given circuit is desirable. This can be accomplished by scaling<sup>16</sup> of an existing technology, by the development of a new technology, as pursued in this thesis work, or by new circuit design concepts. Oftentimes it is found that new circuit design concepts require new processing technologies, and vice versa. Dynamic random access memories are a good example for circuits that strongly depend on a particular fabrication technology.

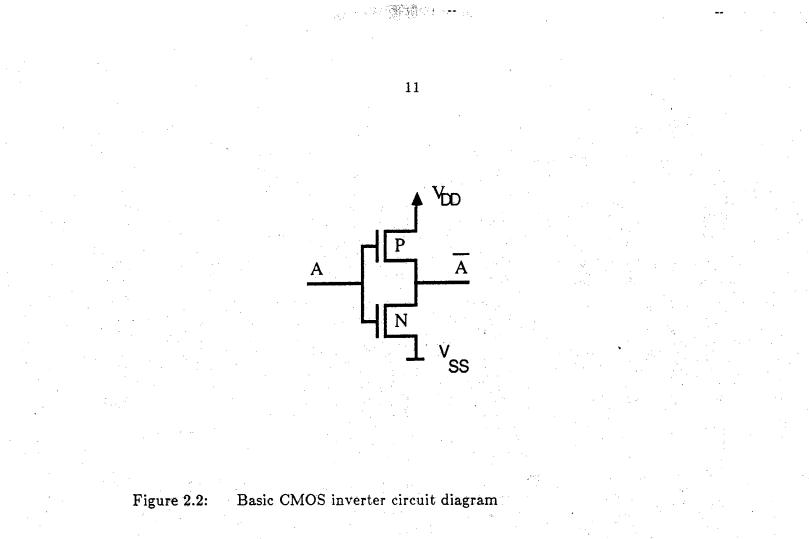

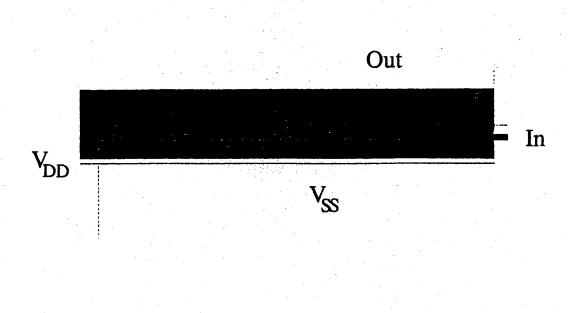

### 2.3.1 Fully Complementary CMOS

The most basic circuit in CMOS is the inverter (Fig. 2.2). The inverter is composed of a PMOS transistor, whose source is connected to the positive supply voltage, and an NMOS transistor with its source connected to ground. The gates and drains of both transistors are connected together, respectively. When a positive voltage is supplied to the input, the NMOS transistor will open a conducting path from the output to ground. Respectively, if ground potential is supplied to the input, the NMOS transistor will not conduct, and the PMOS transistor will open a path to the positive supply voltage. Therefore, at any one time only one of the transistors will be conducting.

The mobility of holes in silicon is smaller than that of electrons. Since the gain of a transistor is proportional to the carrier mobility, the PMOS transistor in an inverter has usually twice the width of the complementary NMOS transistor to compensate for its smaller gain and to achieve the same current for a given gate and drain voltage. If two inverters are connected as shown in Fig. 2.3, an EXOR gate is obtained. As inputs the logic levels and their complements have to be supplied. A two-input CMOS NAND is given in Fig. 2.4. This also demonstrates one of the drawbacks found in conventional CMOS circuit design: four transistors are needed for the two-input NAND, imposing four capacitive gate loads on the driving circuitry. This problem of fully complementary CMOS designs, resulting in lower speed and greater area compared to equivalent NMOS circuits, can be circumvented by a different approach to CMOS circuit design.

## 2.3.2 Clocked CMOS

Because of the good electrical isolation of MOS transistor gates with regard to drain, source, and bulk it is possible to employ the capacitor composed of the gate-oxide-bulk structure to store small charges on the gate nodes. <sup>17</sup> Now, for each logic gate its respective output node is precharged to the positive supply voltage (i.e. logical "1"). During this precharge phase the logical function evaluation network is disabled. When the precharge is completed the charging current is switched off and the logical network is enabled. If the input signals satisfy the condition for a logical "0" the precharged output node is discharged over the network. If the input configuration does not satisfy the "0" condition nothing will happen and the precharged output node keeps its logic level. The output node has a valid logic level only after the logical function network has been enabled. It therefore has to be made certain

en and state of the

44.14

## Figure 2.3:

CMOS EXOR circuit diagram

that successive logic processes the output signal of the previous stage only at the end of the conditional discharge phase.<sup>18-20</sup>

To illustrate the dynamic CMOS circuit design consider Fig. 2.5. During the precharge time the CLOCK ( $\Phi$ ) signal is at logic level "0" and thus enables the PMOS precharge transistor, charging the gate node of the output buffer to the positive supply voltage such that the output node is at logic level "0". The precharge phase is terminated when the CLOCK signal goes to logic level "1", thereby disabling the PMOS precharge transistor and enabling the logical function network via the NMOS transistor T1. If the input signals are such that a conducting path is opened between the precharged inverter input node and ground, the inverter output will go from logic level "0" to one. If the input signal configuration does not meet the requirements of the logic network to evaluate to "1", the precharged node will stay charged and the inverter output will remain at logic level "0".

In this technique, only two PMOS transistors per gate are needed, independent of the complexity of the logic function network. There never is a dc path to ground opened and therefore the low power dissipation of fully complementary CMOS is preserved. There are some drawbacks to this approach, however.

First, the load is always driven by a PMOS transistor, since the transition of the output node is always from ground potential to the supply voltage. This transition is caused by the flow of current through the PMOS transistor of the output buffer, which has a smaller current driving capability than an NMOS transistor. Secondly, because of the non-inverting nature of this design technique, not every logic function can be implemented. However, because clocked CMOS and fully complementary CMOS are compatible, in such cases a conventional design could be used to implement such gates. The third problem stems from the dynamic operation of the circuit. This can lead to charge sharing between the precharge node capacitance and parasitic capacitances of the logic function network, thus jeopardizing proper gate function.

### 2.3.3 Complex CMOS Circuits

The basic CMOS circuits such as inverter, NAND, and EXOR gates have been reviewed in the last two subchapters. This was to demonstrate that there is a class of circuits that contain the CMOS inverter structure as their basic building block. Another class of circuits, such as multiple input AND and NAND gates, are not easily built from inverters, but most often contain

Two-input CMOS NAND gate

N

A

B

Three-input clocked CMOS NAND gate

inverter like structures.

A third important class of circuit modules is that of bistable storage elements, e.g. master-slave flip flops, random access memories, D-flip flops, and J-K flip flops. Also mentioned should be content addressable memory cells.

Figure 2.6 shows an MS flip flop, consisting of four inverters and four transfer gate transistors.

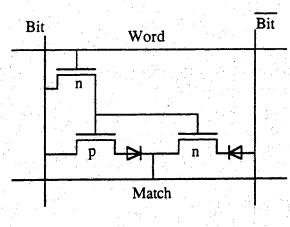

Figure 2.6: CMOS master-slave flip-flop

The static random access memory cell (SRAM) in Fig. 2.7 employs two inverters and two transfer gate transistors that connect the data bit lines to the bistable memory element of two cross coupled inverters. By connecting an EXOR to the SRAM cell such that one input probes into one of the two storage nodes comprised of a cross coupled inverter pair and the other senses the bit line, the output of the EXOR will indicate if the bit line data will match the stored data. This is the function of a content addressable memory cell (CAM) as shown in Fig. 2.8.

It should be noted that a full CMOS SRAM cell requires 6 transistors. Adding the EXOR as shown in Fig. 2.3 would require an additional 4 transistors, bringing the total transistor count of the CAM cell to 10. Making use of the specific properties of the proposed 3-D technology we have proposed a CAM design that only needs three transistors, two of which form an inverter. <sup>21</sup> In conventional CMOS technologies the PMOS transistors of the storage cell are oftentimes substituted by highly resistive polysilicon loads in order to

14

make the cells smaller. This can be done because the current driving capability of the PMOS transistors is not critical in terms of circuit function. The relaxation on the requirements for the PMOS transistor could be exploited in designing a technology tailored towards the fabrication of SRAMs or CAMs. It demonstrates the need to understand the relationship between circuit design requirements and requirements imposed on a specific fabrication technology by the desired circuit function.

### 2.4 CMOS Technology

In CMOS, n-type and p-type transistors are combined on the same substrate. Special wells or tubs must be created for one of the transistor types, where the semiconductor type is opposite to the substrate type. For example, an NMOS transistor could be defined in a p-type substrate, and the complementary PMOS transistor would have to be defined in an n-type well. Modern CMOS processes however oftentimes employ a twin-well process, <sup>22</sup> where both, n-type and p-type regions are formed in a lightly doped substrate. The benefits of such an arrangement include the close placement of the NMOS and PMOS devices, the need for only a single lithographic mask step to form both well types, the independent doping control of the bodies of each of the CMOS device types, and the choice of either substrate type for different circuit applications with basically no change in process flow. Generally, a p-type substrate is preferred to an n-type because it is less sensitive to process induced material defects. In addition, the p-type material provides higher conductivity under the NMOS device compared to the conductivity of a p-well in an n-type substrate. For certain applications it is beneficial to use n-type substrates. In static random access memories for example, the p-well to n-type substrate junction provides protection against radiation induced charge loss at the storage nodes.

As device dimensions shrink the problem of device degradation by hot electron injection into the gate oxide increases. This problem is related to the long term stability of the devices. For gate lengths of less than about 2  $\mu$ m lightly doped drain and source regions are required to minimize threshold voltage shift and oxide deterioration.

To increase operating speeds it is important to keep interconnect resistances as small as possible. The sheet resistance of the polysilicon interconnect level with typical values between 40 and 100  $\Omega$ -cm can be reduced to less than 10  $\Omega$ -cm by deploying a silicide on top of it.

CMOS content addressable memory

16

A cross section of an advanced twin-tub CMOS inverter is given in Fig. 2.9.

Here devices are isolated from each other by a field oxide region that was created by local oxidation of silicon <sup>24</sup> (LOCOS). In LOCOS, the active device areas are masked by silicon nitride. Prior to the field oxidation a channel stop implant is performed which is selfaligned to the active areas. The nitride mask prevents oxygen from diffusing to the active areas on the substrate, thus permitting to selectively oxidize the wafer. However, because some lateral oxidant diffusion underneath the nitride layer takes place, a "bird's beak" develops, leading to lateral encroachment of the active area. The resulting structure is more planar than that resulting from oxidation and following active area definition by etching of the oxide. The masking nitride can damage the underlying silicon and can lead to problems in subsequent gate oxide formation. For that reason a stress relief oxide is usually grown prior to nitride deposition, or a sacrificial oxide is grown after nitride removal. The outdiffusion of the channel stop dopant into the active area can contribute further to lateral encroachment by reducing effective channel width.

Because of the shortcomings of regular LOCOS other ways of electrically isolating active device areas have been devised. In recessed LOCOS <sup>25</sup> the wafer substrate is anisotropically etched after the silicon nitride deposition and active device area definition. The local oxidation is carried out following the silicon etch (Fig. 2.10). This leads to desirable improved surface planarity compared to the standard LOCOS process. Surface planarity becomes more important as minimum line widths become smaller. Steps in the surface can lead to local line width loss during lithography.

Sidewall Masked Isolation (SWAMI) was first proposed by K.Y. Chiu et al. .<sup>26</sup> It takes full advantage of LOCOS processing without suffering the drawbacks such as bird's beak formation and lateral encroachment. The SWAMI process sequence is similar to that of recessed LOCOS, except that after the anisotropic silicon etch the developed sidewalls are masked by a stress relief nitride. This can be accomplished without additional masking steps and leads to a defect free local oxidation isolation technique.

The undesirable bird's beak formation in conventional LOCOS has been found to be due to lateral oxidation underneath the stress relief oxide. To eliminate this effect a technique called Sealed Interface Local Oxidation (SILO) <sup>27</sup> was developed. In SILO technology, a sandwich layer consisting of plasma enhanced silicon nitride, LPCVD oxide, and LPCVD nitride is used to mask portions of the substrate from oxidation (Fig. 2.11). The LPCVD oxide film serves as a stress relief between the rigid LPCVD nitride on the top of the sandwich and the substrate, while the bottom nitride film seals off the silicon/silicon dioxide interface from oxidant diffusion. The plasma enhanced bottom nitride is quite thin and less rigid, so that intrinsic nitride stress and volume expansion induced stress are kept small.

Yet another way of circumventing the problems associated with LOCOS was suggested by K. Kurosawa *et al.*, called Buried Oxide <sup>28</sup> (BOX). They masked active device geometries by aluminum and etched the unmasked silicon field regions by reactive ion etching. Then they plasma-deposited  $SiO_2$  and etched it in a buffered HF solution. This led to preferential etching of the oxide at the side walls forming V-grooves there. After removal of the aluminum mask and another oxide deposition, the wafer was planarized using a conventional resist reflow and etch back process (Fig. 2.12).

In Direct Moat Isolation (Fig. 2.13)<sup>29</sup> the wafer is completely oxidized. After the oxidation the top region of the oxide film is damaged by ion implantation. Successively the field regions are masked by a thin nitride layer, and an isotropic wet etch is performed. Because of the damaged top oxide layer, the resulting profiles are tapered off. Straight wet etching of thick field oxides would lead to sharp profiles that would impose serious limitations on succeeding fine line lithography and high yield metallization.

Figure 2.11: Sealed Interface Local Oxidation (SILO) structure<sup>27</sup>

20

Figure 2.12: BOX fabrication sequence<sup>28</sup>

SILICON SUBSTRATE

Figure 2.13: Direct moat isolation process sequence<sup>29</sup>

23

--

An almost latch-up free isolation technique allowing very densely packed devices was presented with the Trench Isolation concept as shown in Fig. 2.14.<sup>30</sup> The devices are separated by a deep (> 5  $\mu$ m) trench which is anisotropically etched into the silicon substrate and then refilled with insulating and non-insulating material. This procedure has found recent application in proposed 4 and 16 MBit DRAM technologies and advanced BiCMOS processes.<sup>15,31,32</sup> One of the key problems with this approach are the parasitic channels that form where active devices touch the vertical trench sidewall. This leads to increased subthreshold leakage currents.<sup>33</sup> One way around this is to fill the trenches with heavily doped polysilicon. To avoid outdiffusion of dopants out of the trench during subsequent processing, the trench has to be lined with a thin nitride prior to its filling with polysilicon.

Novel isolation techniques that are not yet established in production lines include device isolation by selective epitaxial growth of monocrystalline silicon (Fig. 2.15).<sup>34-43</sup>

Figure 2.15: Dielectric isolation by Selective Epitaxial Growth<sup>34</sup>

Here problems are similar to that of trench isolation, namely enhanced leakage along the sidewall silicon/silicon dioxide interface. In addition, the problem of non-planarity introduced by faceting during the epitaxial growth has not yet been completely solved. Since selective epitaxial growth is one of the key processing steps in the newly developed 3-dimensional CMOS technology we will review principles and research results in epitaxial depositions of silicon on silicon in one of the following subchapters.

#### 2.5 SOI Technologies

25

でで おね。

As device dimension shrink into the submicron range with increasingly better lithographical methods and improved process control, circuit performance is less and less limited by the characteristics of the active devices but by parasitics inherent in todays planar technologies.<sup>44</sup> New device isolation techniques will be required to prevent parasitic coupling between adjacent devices through the Si substrate. To further increase the complexity of systems that can be integrated, a step towards vertical or three-dimensional integration is seen as necessary. <sup>45-47</sup> All these issues are addressed by siliconon-insulator technologies.

In silicon-on-insulator (SOI), devices are built in a thin monocrystalline silicon film on top of an insulator. One of the few SOI processes employed for commercial purposes today is silicon-on-sapphire (SOS), where sapphire  $(Al_2O_3)$  serves as the insulating film as well as the substrate for CMOS circuits. The high costs and complexity associated with SOS technology has so far prevented it from being widely used. Short term objectives of current SOI development efforts are to provide thin films of dielectrically isolated silicon with good semiconductor properties at reasonable costs, particularly to prevent latch-up in advanced bipolar and CMOS circuits. Long term goal of these efforts is the production of vertically integrated circuits. <sup>48</sup>

The methods by which SOI has been obtained are oxidation of porous silicon (FIPOS), seeded or unseeded recrystallization of molten polysilicon, separation by implanted oxygen (SIMOX), lateral solid-phase epitaxial growth, wafer bonding and wafer thinning, heteroepitaxial SOI, and epitaxial lateral overgrowth. These technologies will be briefly reviewed in the following subchapters, with a focus on silicon epitaxial lateral overgrowth as it was one of the main subjects of this research.

#### 2.5.1 Full Insulation by Porous Oxidized Silicon (FIPOS)

High quality SOI layers can be fabricated by the method of oxidation of porous silicon. Here n-type islands are surrounded by  $p^+$  regions formed by conventional processing such as ion implantation, diffusion or epitaxy. Then the substrates are etched electrochemically such that porous silicon is formed in the  $p^+$  layer while the n-type regions are basically not altered. Since porous silicon oxidizes about one order of magnitude faster than monocrystalline

## Table 1

# 44 SOI technologies

| SOI Technology                                                 | Usable<br>SOI area                    | 3-D<br>candidate | SOI perfectness                                                                                                                                                                                              | Particularities                                                                                                                                       |  |

|----------------------------------------------------------------|---------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Laser<br>recrystallization                                     | small                                 | yes              | entrainment<br>defects                                                                                                                                                                                       | Technology to be applied during IC processing;<br>careful engineering required to prevent device degrading;<br>submicron MOS; low throughput.         |  |

| Electron-beam<br>recrystallization                             | small                                 | yes              | entrainment<br>defects<br>Technology to be applied during 1C processing;<br>vacuum environment; careful engineering required to pre<br>device degrading; submicron MOS; low throughput;<br>pseudo line scan. |                                                                                                                                                       |  |

| Graphite-strip heater<br>recrystallization                     | larger<br>up to full<br>scale         | , no             | carbon contamination;<br>can be made<br>defect free                                                                                                                                                          | made higher throughput; lower defect density; submicron MOS;                                                                                          |  |

| Tungsten-halogen lamps<br>recrystallization                    | larger<br>up to full<br>scale         | ñO               | can be made<br>defect free                                                                                                                                                                                   | Technology to be applied in early stage of IC processing;<br>well suited for thicker SOI layers (> 10 $\mu$ m);<br>higher throughput; wafer warpage.  |  |

| SOI by O <sup>+</sup> ion implantation<br>and annealing; SIMOX | full<br>wafer                         | NO               | dislocations to be pre-<br>vented; oxide precipi-<br>tates to be annealed                                                                                                                                    | A technology for wafer suppliers before IC processing;<br>most adapted to existing silicon technology; submicron MOS.                                 |  |

| Full insulation of porous<br>oxidized SI; FIPOS                | small<br>islands<br>fully<br>isolated | no               | not dislocation free                                                                                                                                                                                         | A technology with a limited applicability due to the smallness<br>of the islands; a technology before IC processing;<br>submicron and thicker layers. |  |

| Lateral solid-phase<br>epitaxial growth; L-SPEG                | smalt<br>stripes                      | yes              | twins A technology with a limited applicability due to the smallness of the stripes; processing IC compatible; submicron Si-layer.                                                                           |                                                                                                                                                       |  |

| SOI by wafer bonding<br>and thinning                           | full<br>wafer                         | yes              | comparable to<br>bulk silicon                                                                                                                                                                                | Advanced technology of wafer production; thicker SOI layers (1 - 5 $\mu$ m); technology for wafer suppliers.                                          |  |

| Heteroepitaxy                                                  | substrate<br>scale                    | probably<br>yes  | so far not defect free<br>due to lattice mismatch<br>and dilatation                                                                                                                                          | Technology to be evaluated; IC compatibility dependent on substrate material.                                                                         |  |

silicon, oxide forms mainly underneath the n-type silicon islands during the subsequent oxidation. Material created by this method can have defect densities comparable to those of bulk-Si. It has successfully been used to build VLSI circuits. The major disadvantage of this method of creating SOI is its incompatibility with established IC fabrication steps. Also, the buried  $SiO_2$  does not exhibit good insulating characteristics and the SOI islands are stressed by the oxide layer, inducing defects. The islands fabricated so far by this method were narrow stripes, of only a few hundred microns width. This method is not suited to obtain a continuous film of SOI over an entire wafer area.

#### 2.5.2 Polysilicon Recrystallization

A method to create SOI which has received much attention is the recrystallization of polysilicon deposited over an amorphous insulating layer.  $^{49-55}$  The deposition of polysilicon by chemical vapor deposition is a well established procedure employed in almost all modern bipolar and MOS processes. Polysilicon is usually deposited at temperatures between 580 °C and 630 °C such that grain sizes between 10 and 100 nm result. Inside the grains, polysilicon has a regular crystal structure. By heating the polysilicon up to its melting point over an entire wafer area or locally restricted, and subsequently cooling it down, monocrystalline silicon is formed out of the melt over insulating material, which usually is SiO<sub>2</sub>. The melting can be accomplished by different means.<sup>56</sup>

As heat sources lasers,<sup>57-61</sup> electron beams,<sup>62</sup> high-intensity lamps,<sup>63</sup> and graphite strip heaters <sup>64</sup> are used. The required high temperatures for the melting of the silicon leads to large horizontal temperature gradients and can damage underlying layers, making vertical integration problematic.<sup>65</sup> The unseeded melting of polycrystalline silicon leads to a random crystal orientation of the resulting SOI layer. Seeding of the polysilicon by contact with the silicon substrate is required to obtain a preferred crystal orientation. <sup>66</sup> To reduce stress induced defects, pattern relief structures can be employed. Although considerable effort has been invested into the development of this technology, only functional models of integrated circuits making use of this process have been demonstrated.

27

#### 2.5.3 Separation by Implanted Oxygen (SIMOX)

In the SIMOX technique, an oxide is formed underneath a silicon layer by high energy, high dose implantation of oxygen into a silicon wafer. Implantation energies are typically 150 keV to 200 keV and a dose in the order of  $10^{18}$  atoms cm<sup>-2</sup> is required. During the implant wafers are held at temperatures between 400-600 °C to keep the silicon out of the amorphization range due to in situ annealing. Following the implant, a high temperature (>1300 ° C) anneal step is carried out to restore the implantation damaged silicon surface layer and to eliminate precipitates of  $SiO_2$  by dissolving them and by diffusing oxygen atoms into the buried oxide layer. Even after the anneal, the SOI layer is saturated with oxygen atoms up to its solid solubility limit, and dislocations with densities of typically  $10^9 \text{ cm}^{-2}$  are present. While oxygen precipitates can be dissolved, the dislocations cannot be annealed out, even if anneal temperatures are close to the melting point of silicon. High temperatures are not only required to anneal implantation damage in the SOI layer but also to form a good quality, low leakage buried oxide. Anneal temperatures of about 1300 °C result in oxide leakage currents of nA/cm<sup>2</sup>, while thermally grown oxide has leakage currents of typically  $pA/cm^2$ . To achieve lower defect densities in the SOI layer, different schemes have been devised. The channeling of implants leads to smaller implant damage of the silicon surface layer. Several subsequent low-dose implantations with successive anneals lead to a low-dislocation SOI layer. By these means defect densities could be reduced to  $10^5$  cm<sup>-2</sup>.

SIMOX has to be considered a 2-dimensional SOI technology. It is unlikely that more than one active device layer can be created by this method. SIMOX is most suited for very thin (100 nm) SOI layers, as they are required in SOI CMOS, where SOI layers thinner than the depletion layer are needed. In this case high defect densities are not as critical, since junction areas are very small. Hall mobilities in SIMOX SOI layers are comparable to those in bulk silicon, and acceptable low interface state densities and leakage currents have been demonstrated.

One of the most serious drawbacks of this technique is the high dose of oxygen implant required to form the buried oxide. Even with modern high current implanters the implantation time is in the order of hours. This leads to high wafer costs.

#### 2.5.4 Lateral Solid-Phase Epitaxial Growth

In lateral solid-phase epitaxy (L-SPEG) polycrystalline or amorphous silicon is deposited on an insulating material. In the case of a polycrystalline layer, a channeled silicon ion beam is employed to amorphize most of the polysilicon and to leave grains with major crystallographic axes aligned along the channeling direction. The structures are then subjected to a heat treatment during which these grains act as a seed for the solid-phase epitaxial regrowth. Instead of amorphizing polysilicon by channeled silicon beams, openings in the insulating layer to the silicon substrate can act as seeds for regrowth of the amorphous silicon films.<sup>67-70</sup> During the epitaxial regrowth the temperature has to stay below the temperature at which spontaneous recrystallization of amorphous silicon to polysilicon takes place. This leads to very slow epitaxial regrowth and limits the width of SOI films to a few micron. So far L-SPEG has not been used for integrated circuit or device fabrication.

#### 2.5.5 Heteroepitaxial SOI

Since it is difficult to grow or deposit monocrystalline silicon on top of an amorphous insulating layer, SOI research in the past concentrated on finding an insulating crystalline material that would be compatible to silicon. In particular, lattice constants have to be close, the dilations as a function of temperature have to be matched, and the material surface has to be susceptible to atomic bonding with silicon. Sapphire has properties that come close to these requirements, and commercially available SOI wafers are mostly silicon-onsapphire (SOS). <sup>71</sup> Problems arise however from the imperfect match of the lattice constants, the brittleness of the sapphire, and the outdiffusion of aluminum into the SOI film. Due to lattice strain and stress, minority carrier lifetimes in SOS are small, baring the fabrication of bipolar transistors on these substrates. Other materials have been investigated, among them spinel, zirconia, and calcium fluoride.<sup>72, 73</sup> So far, none of these have been used in commercial applications.

#### 2.5.6 Wafer Bonding and Wafer Thinning

When two clean and flat surfaces of high finish are brought close to each other dipole forces are induced into the two surfaces and Van der Waals bonding occurs. The bonding forces are strong under shear and pressure, but weak under pulling. Van der Waals bonding can be converted towards a stronger chemical bonding by annealing of the structure at elevated temperatures. One can bond wafers with an oxidized surface, thereby burying the oxide. The wafer chosen to later contain active devices can then be thinned to a specified thickness above the buried oxide, usually a few microns, resulting in the desired SOI structure. The key problem in this technology is the thinning of the "active" wafer with high geometrical precision and low damage to its surface. To obtain the required high uniformity one oftentimes introduces stopper areas on the wafer. Upon reaching these stoppers, which can be made of a different material or differently doped silicon, thinning effectively stops.

This technology requires facilities that are not usually found in IC fabrication laboratories. Problems also seem to persist with the reliability of the bonding.

#### 2.6 Epitaxial Lateral Overgrowth

Epitaxy is a process where material is deposited onto a crystalline substrate or seed, and where the crystalline configuration of the structure is maintained. Epitaxy can be classified into four different kinds: Molecular Beam Epitaxy (MBE), Vapor Phase Epitaxy (VPE), Liquid Phase Epitaxy (LPE) and Solid Phase Epitaxy (SPE). <sup>74</sup> Vapor phase epitaxy has found the widest acceptance because impurities can be well controlled and crystalline perfection of the grown layers is obtainable. MBE allows for an even better control of layer thicknesses, but suffers from low throughput and high system cost due to the required high vacuum levels. It has however drawn considerable attention lately, particular for the growth of III-V and II-VI structures. LPE is mostly employed for the growth of III-V compounds as GaAs and InP. SPE has been briefly reviewed in a previous subchapter.

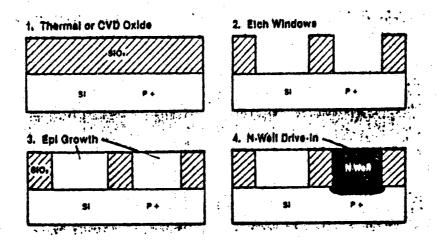

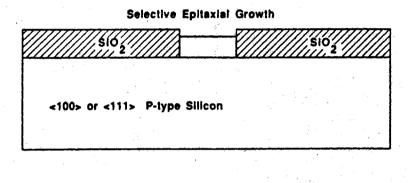

VPE has been used since the early stages of device fabrication because it was the only way by which one could obtain a thin layer of lightly doped material on a heavily doped substrate with a sharp transition in the doping profile. Such a structure was desirable because it improved bipolar transistor and later bipolar IC performance. Lately VPE has been successfully employed in CMOS technologies to reduce latch-up effects. A relatively new branch in VPE is selective epitaxy where the deposition of silicon is confined to certain areas on a wafer. <sup>39,40,75-94</sup> Deposition proceeds from seed openings in a masking oxide (Fig. 2.16). When selective epitaxy is continued even after the growth surface has reached the wafer (oxide) surface, lateral growth occurs. This epitaxial lateral overgrowth forms silicon on the insulating masking oxide and can therefore be considered an SOI technique.

Selective epitaxy and epitaxial lateral overgrowth constitute the key processing steps in the technology developed in the course of this work. This subchapter therefore contains a somewhat detailed review of the principles of silicon VPE from silane and the chlorosilanes.

#### 2.6.1 Basic Terminology

Chemical Vapor Deposition processes, to which VPE is counted, proceed in general according to the following scheme:<sup>95, 96</sup>

- 1) Reactants are transported to the surface

- 2) Reactants are adsorbed on the substrate surface

- 3) A thermally induced chemical reaction takes place at the surface

- 4) Reaction products are desorbed from the surface

- 5) Reaction products are transported away from the surface

In general, the various steps of CVD can be grouped into the kinetics of the chemical reactions taking place at a heated surface and the transport of a silicon containing gas compound (i.e.  $SiH_4$ ,  $SiH_3Cl$ ,  $SiH_2Cl_2$ ,  $SiHCl_3$ ,  $SiCl_4$ ) towards and away from that surface, including the flow dynamics particular to a given reactor geometry. It is difficult to coherently model all important aspects of both transport phenomena and kinetics in silicon epitaxy. The kinetics and transport are closely linked and interact. Therein lies the difficulty in analyzing and modeling CVD reactor systems. Most researchers therefore have focused either on the kinetics of the process alone, or have simplified the system by limiting considerations to steps 1 and 3, namely gas transport towards the reaction surface and reaction rates there. Not even considered here are homogeneous (gas phase) reactions that can occur during or prior to reactant transport to the reaction surface.<sup>97-99</sup>

A simple model was introduced by  $Grove^{100}$  that explains the basic dependencies of growth rates on operating parameters.

1221년 1

Seed Window śíó <100> or <111> P-type Silicon

32

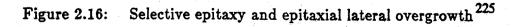

Figure 2.17: Basic model of the epitaxial growth  $process^{72}$

The following notation is used for the different parameters

- h<sub>g</sub> gas-phase mass-transfer coefficient

- $C_s$  concentration of gas at the surface

C<sub>g</sub> concentration of gas far away from the surface

F<sub>1</sub> flux of reactants towards surface

$F_2$  flux of reactants absorbed on the surface

$k_s$  surface reaction rate constant

Then, under the assumption of a linear concentration gradient from the gas bulk to the surface one can write

$$F_1 = h_g(C_g - C_s)$$

(2.1)

and

$$F_2 = k_s C_s \qquad (2.2)$$

At steady state conditions the two fluxes have to be equal and therefore

$$C_{s} = \frac{C_{g}}{1 + \frac{k_{s}}{h_{g}}}$$

(2.3)

The growth rate of the film is given by

$$V = \frac{F}{N_{I}}$$

(2.4)

with  $N_1 = 5x10^{22} \frac{\text{atoms}}{\text{cm}^3}$  for Silicon.

One oftentimes likes to write the concentration of reactants in the gas bulk in terms of its mole fraction of the total gas concentration:

$$C_g = C_T Y \tag{2.5}$$