### Purdue University Purdue e-Pubs

Department of Electrical and Computer Engineering Technical Reports Department of Electrical and Computer Engineering

12-1-1986

## Polysilicon Emitter Fabrication and Modeling

G. W. Neudeck *Purdue University*

J. L. Gray Purdue University

W. Klaasen Purdue University

J. Egley Purdue University

J. Pak Purdue University

See next page for additional authors

Follow this and additional works at: https://docs.lib.purdue.edu/ecetr

Neudeck, G. W.; Gray, J. L.; Klaasen, W.; Egley, J.; Pak, J.; and Bagri, R., "Polysilicon Emitter Fabrication and Modeling" (1986). *Department of Electrical and Computer Engineering Technical Reports*. Paper 556. https://docs.lib.purdue.edu/ecetr/556

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

#### Authors

G. W. Neudeck, J. L. Gray, W. Klaasen, J. Egley, J. Pak, and R. Bagri

## Polysilicon Emitter Fabrication and Modeling

G. W. Neudeck J. L. Gray W. Klaasen J. Egley J. Pak R. Bagri

TR-EE 87-7 January 1, 1986 to December 31, 1986

School of Electrical Engineering Purdue University West Lafayette, Indiana 47907 Polysilicon Emitter Fabrication and Modeling

G. W. Neudeck, J. L. Gray, W. Klaasen, J. Egley, J. Pak, and R. Bagri

TR-EE-87-7

Project Period: January 1, 1986 to December 31, 1986

Supported by Delco Electronics

### Contents

| Executive Summary                                               | 1                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1986 Goals and Progress                                         | 2                                                                                                                                                                                                                                                                                                                                                      |

|                                                                 |                                                                                                                                                                                                                                                                                                                                                        |

| List of Figures                                                 | 4                                                                                                                                                                                                                                                                                                                                                      |

|                                                                 | d and                                                                                                                                                                                                                                                                                                                                                  |

| I. Introduction                                                 | 6                                                                                                                                                                                                                                                                                                                                                      |

|                                                                 | en en                                                                                                                                                                                                                                                                                                                                                  |

| II. The Proposed Research                                       | 7                                                                                                                                                                                                                                                                                                                                                      |

| A. Fabrication<br>B. Computer Modeling                          |                                                                                                                                                                                                                                                                                                                                                        |

| B. Computer Modeling                                            | •••••                                                                                                                                                                                                                                                                                                                                                  |

| III. Summary of Work in 1986                                    | 11                                                                                                                                                                                                                                                                                                                                                     |

| A. Fabrication of Poly-contacted Emitters & Control Transistors |                                                                                                                                                                                                                                                                                                                                                        |

| B. 2D Silicon Bipolar Device Modeling                           |                                                                                                                                                                                                                                                                                                                                                        |

| D. 2D Smeen Dipolar Device Wodening                             |                                                                                                                                                                                                                                                                                                                                                        |

| IV. Proposed Research Goals for 1987                            | 81                                                                                                                                                                                                                                                                                                                                                     |

| A. Fabrication                                                  |                                                                                                                                                                                                                                                                                                                                                        |

| B. Computer Modeling                                            | 82                                                                                                                                                                                                                                                                                                                                                     |

|                                                                 | 1999 - S. 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 19<br>1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1<br>1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - |

| V. Defect Generation Study                                      | 83                                                                                                                                                                                                                                                                                                                                                     |

| A. Study of the Oxidation Stacking Faults and the Dislocation   |                                                                                                                                                                                                                                                                                                                                                        |

| Generation at Si-SiO <sub>2</sub> Interface of Silicon          | 83                                                                                                                                                                                                                                                                                                                                                     |

| B. Role of Sequential Annealing, Oxidation, and Diffusion       |                                                                                                                                                                                                                                                                                                                                                        |

| Upon Defect Generation in Ion-Implanted Silicon Surfaces        | 90                                                                                                                                                                                                                                                                                                                                                     |

| C. Study of Elimination of Stacking Faults                      | 92                                                                                                                                                                                                                                                                                                                                                     |

|                                                                 |                                                                                                                                                                                                                                                                                                                                                        |

| VI. Gettering Study                                             | 95                                                                                                                                                                                                                                                                                                                                                     |

|                                                                 |                                                                                                                                                                                                                                                                                                                                                        |

| VII. Conclusions                                                | 111                                                                                                                                                                                                                                                                                                                                                    |

#### Executive Summary

The research proposed for 1986 was to develop the technology for fabricating, measuring, and computer modeling the polysilicon emitter bipolar transistor. Fabrication consisted of producing three types of bipolar transistors; a regular bipolar device to act as the control, a polysilicon contacted emitter transistor, and a polysilicon emitter directly on the base region with a very thin oxide at the interface. The proposed fabrication research concentrated on investigating a new method of fabricating polysilicon contacted emitter bipolar transistors.

The new fabrication technique uses plasma etching of the emitter location on the base region and, without breaking vacuum, depositing amorphous silicon (a-Si) on the cleaned interface. The a-Si was then to be doped by ion-implantation and heated to  $600-700 \text{ C}^{\circ}$  to produce the polysilicon emitter contact. The controlled interface and the fine grained polysilicon should lead to more uniform and predictable betas for the polycontacted transistors. Both polysilicon contacted emitters and polysilicon emitters were to be investigated over a range of base doping.

We proposed the modeling work in two directions: 1) 2-D simulation so that small geometry transistors can be accurately modeled and 2) simulation of polysilicon contacted emitter transistors. Measurements on the devices described above will be used to develop a polysilicon model. The objective of this part of the project is to develop a numerical device simulator with predictive capability, i.e. one that can be used with confidence in place of actual device fabrication. The numerical device models will be provided to Delco and should find many applications in development and manufacturing.

The fabrication highlights of the 1986 work were the design and fabrication of preliminary bipolar transistors and polysilicon emitters, the design and layout of the test wafer, and the fabrication and measurements on shallow arsenic doped emitter devices. There were 22 sets of fabrication runs made beyond the preliminary devices.

The last results of these runs show that the shallow Arsenic emitter  $(0.05 \ \mu)$  and the very narrow base width  $(0.1 \ \mu)$  control devices with metal emitter contact, have an average peak beta of about 75. Poly contacted emitter devices fabricated at the same time on the same wafer show a beta enhancement to 232, a factor of about 2.7 to 3.0 in the average peak beta. The polysilicon was deposited in a standard way in a LPCVD tube. We are presently fabricating polysilicon devices for studying the effects of the methods used in treating the surfaces before the poly is deposited and the way the poly is formed (amorphous PELPCVD).

#### **1986** Goals/Progress

#### Goal #1. Polysilicon $N^+$ -Contacted Emitter

- (a) Modified existing bipolar process and produced *preliminary* poly emitter and regular BJT devices. Showed good beta enhancement.

- (b) Developed test chip and photo plates for demonstrating the effect of Poly emitters as compared to a control (called substrate device) BJT. Completed successfully with phosphorous emitters.

- (c) Amorphous silicon produced by LPCVD and PELPCVD deposited on emitter structures. Have completed 22 fabrication sets of each of 4 types of devices. The initial results were not as good as expected.

- (d) Modified the bipolar process for the control device to have shallow arsenic emitters (an addition to the 1986 goals) so that base widths would remain constant between poly contacted and control devices for better comparison. We successfully completed a 0.05  $\mu$ m deep As emitter with a 0.1  $\mu$  base with device with peak beta of from 70 to 130.

- (e) Successfully completed the polysilicon contacted devices and measured an average peak beta enhancement of a factor of 3,

- $\frac{232.9}{77.7} = \frac{B(\text{poly})}{B(\text{metal})}$

#### Goal #2. Transistor Evaluations

A test station was designed and assembled using a HP 4145A Semiconductor Parameter Test set with a reconditioned probing station. System automatically takes the I-V and beta vs.  $I_C$  data and loads into the UNIX ECN network for plotting etc. to compare with the simulation results. This system works very well and has been used to measure countless devices.

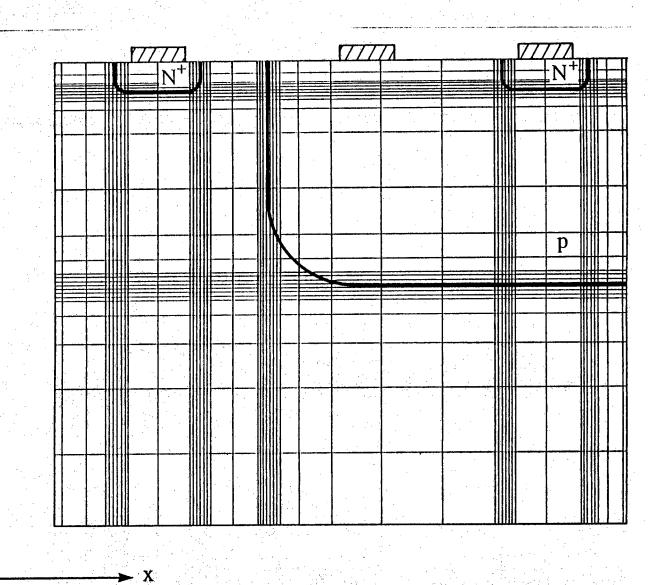

Goal #3. 2D Modeling of Delco Thin Epi

This goal required the modification of an existing two-dimensional simulation code for silicon solar cells to model Delco Electronics "thin epi" silicon bipolar transistors. This involved having the student research assistant familiarize himself with the code (over 10,000 lines of FORTRAN), and then make the necessary modifications. Most of the necessary modifications have been completed. Realistic diffusion profiles, obtained from SUPREM simulations, have been incorporated. In addition, measured or analytic (i.e. ERFC or gaussian) profiles can also be used. A method for accurately extracting the base, collector, and emitter currents has been developed and is now being implemented. Some preliminary two dimensional simulations of Delco's "thin epi" bipolar transistors have been completed.

#### Goal #4. 2D Models of Polysilicon Emitter Contacts

The necessary code for modeling the minority carrier reflecting properties of polysilicon contacts is already incorporated in the simulation program.

### LIST OF FIGURES

Page

| Figure 1.   | Polysilicon Emitter and polysilicon contacted Emitter bipolar             | 8       |

|-------------|---------------------------------------------------------------------------|---------|

|             | transistors.                                                              |         |

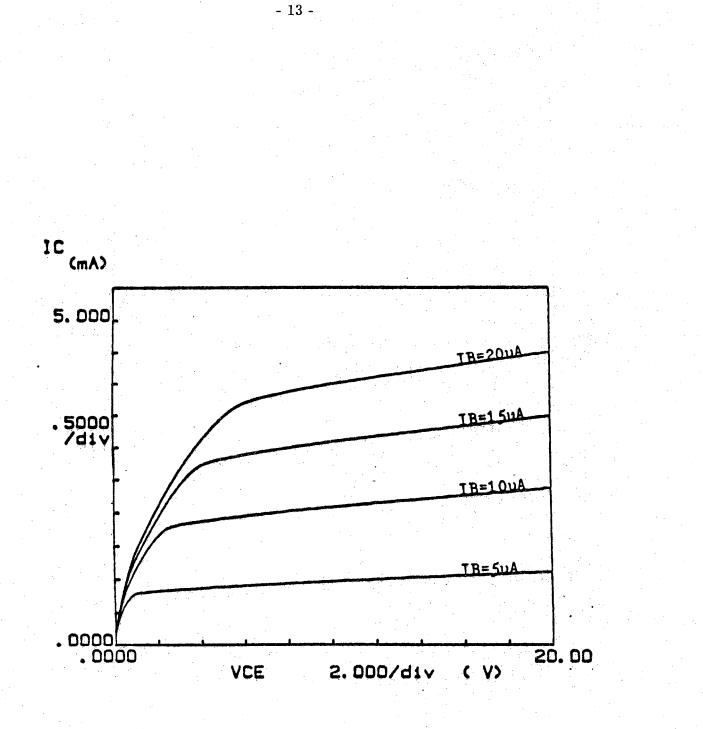

| Figure 2.   | Transistor I-V curves measured on curve tracer. Process #4,               | 13      |

|             | wafer 11.ii, transistor 7 dB.                                             | la en e |

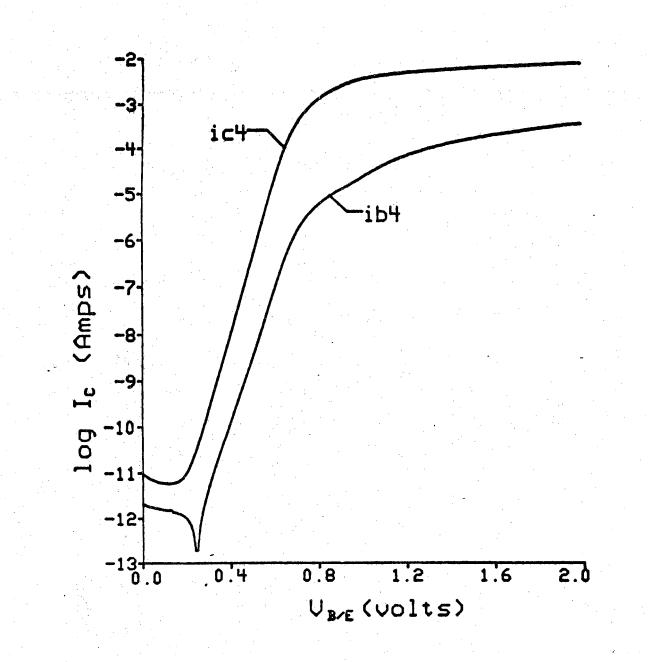

| Figure 3.   | Base and collector currents vs. $V_{BE}$ with $V_{CE} = 4V$ . Process #4, | 14      |

|             | wafer 11,ii, transistor 7 dB.                                             |         |

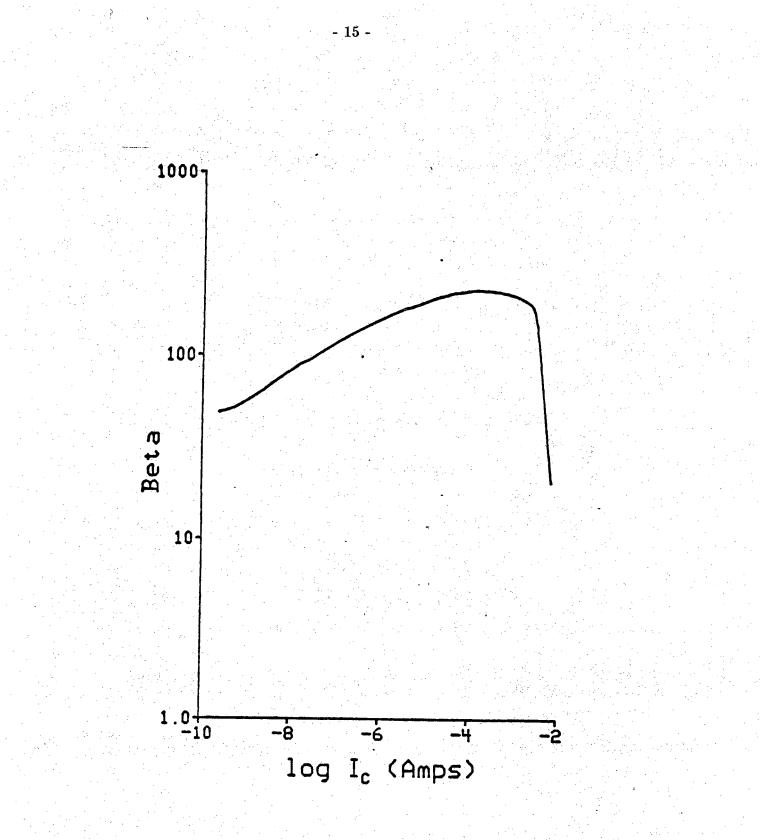

| Figure 4.   | Beta vs. I <sub>C</sub> . Process #4, wafer 11.ii, transistor 7 dB        | 15      |

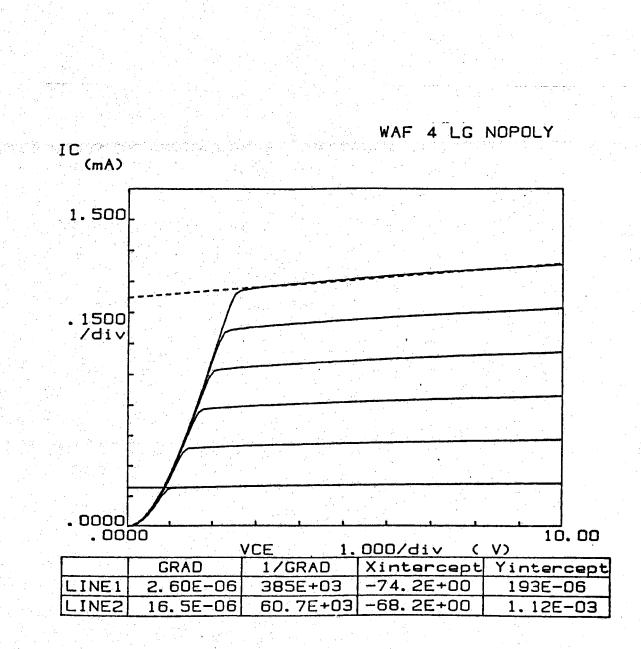

| Figure 5.   | Control BJT I <sub>C</sub> vs. V <sub>CE</sub> .                          | 18      |

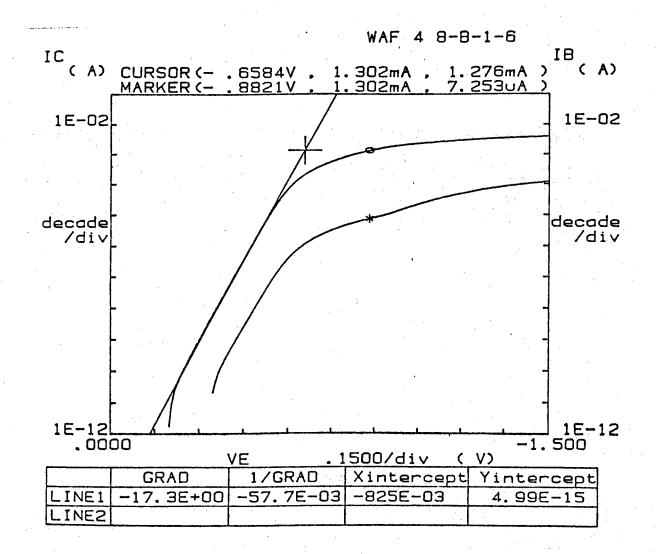

| Figure 6.   | Control BJT I <sub>B</sub> , I <sub>C</sub> vs. V <sub>BE</sub>           | 19      |

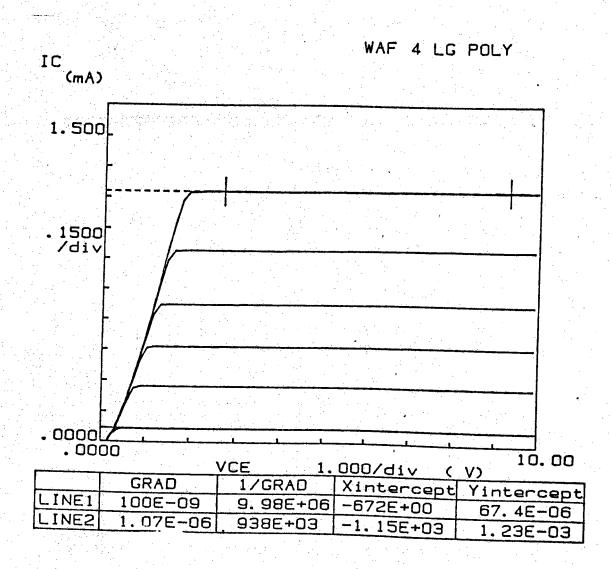

| Figure 7.   | BHF dip Poly Emitter, I <sub>C</sub> vs. V <sub>CE</sub>                  | 20      |

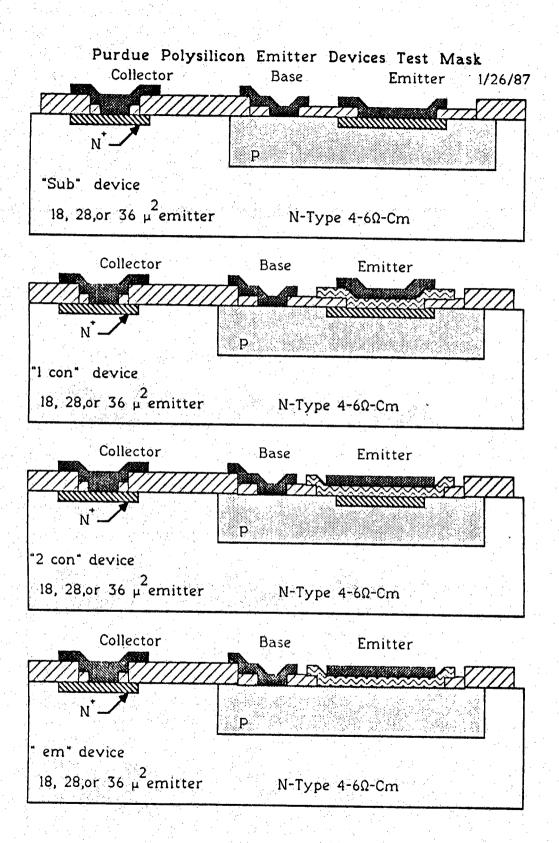

| Figure 8.   | 4 Types of Devices on Test Mask                                           | 22      |

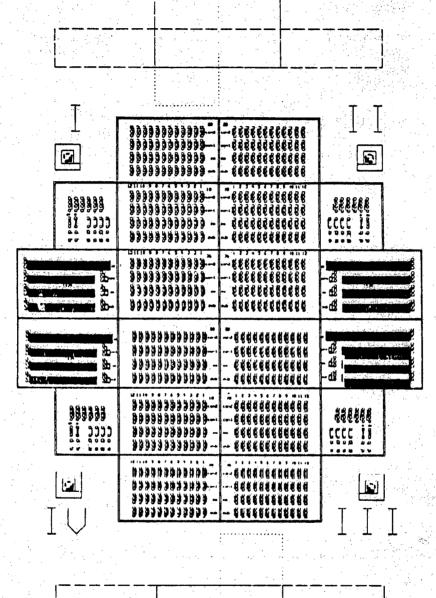

| Figure 9.   | Test Wafer Layout, Full die.                                              | 23      |

| Figure 10.  | Quadrant I of test die.                                                   | 24      |

| Figure 11.  | Wafer set E                                                               | 26      |

| Figure 12.  | Wafer set F with phosphorous emitters                                     | 27      |

| Figure 13.  | Wafer set G with a deep As Emitter                                        | 28      |

| Figure 14.  | Wafer Set H, deep As emitter                                              | 29      |

| Figure 15.  | Wafer Set I                                                               | 30      |

| Figure 16.  | Wafer Set J, Shallow As Emitter                                           | 31      |

| Figure 17.  | Shallow As emitter and a poly-contact                                     | 32      |

| Figure 18.  | Wafer set L shallow As emitter with poly contact anneals                  | 33      |

| Figure 19.  | Wafer set M, shallow As emitter with poly-contact anneals                 | 34      |

| Figure 20.  | Wafer set N, Pd/Al Contacts                                               | 37      |

| Figure 21.  | Wafer set "O".                                                            | 38      |

| Figure 22.  | Wafer Set P, As Emitter with Various, Contacts Metal.                     | 39      |

| Figure 23.  | Wafer Set Q, P-N Diodes                                                   | 40      |

| Figure 24.  | Wafer Set R, Shallow As Emitters                                          | 41      |

| Figure 25.  | Wafer Set S; Gettering                                                    | 42      |

| Figure 26.  | Wafer Set T, gettering study.                                             | 45      |

| Figure 27a. | Wafer Set U.                                                              | 46      |

| Figure 27b. | Wafer Set V, good Poly Contacted and Control Devices.                     | 48      |

| Figure 28.  | Transistor Measured Data.                                                 | 52      |

| Figure 29.  | Wafer V2, Beta Comparison                                                 | 53      |

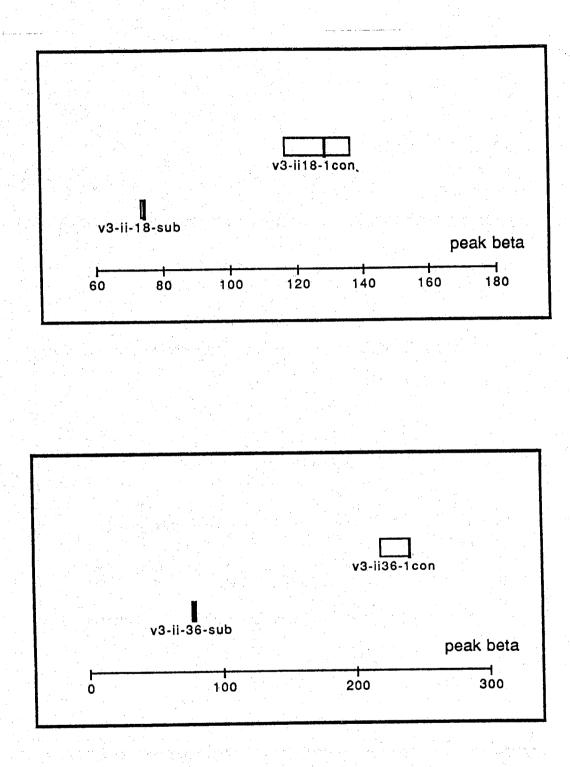

| Figure 30.  | Set U, wafer V3: 18 $\mu$ x 36 $\mu$ Devices                              | 54      |

| Figure 31.  | Statistics of Wafer V3, 18 $\mu$ Devices                                  | 55      |

| Figure 32. | Statistics Set U, Wafer V3, 36 $\mu$ Devices                                              | 56                    |

|------------|-------------------------------------------------------------------------------------------|-----------------------|

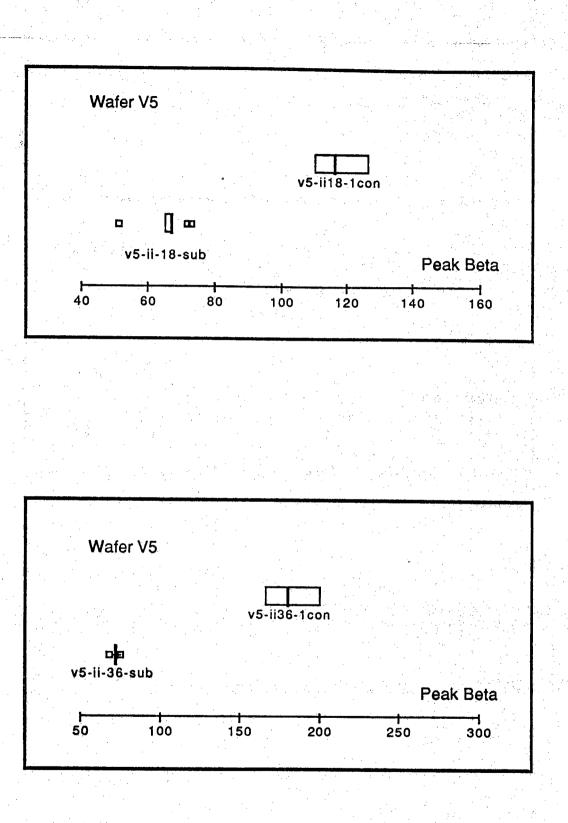

| Figure 33. | Set V, Wafer 5 Devices                                                                    | 57                    |

| Figure 34. | Statistics Set V5, Wafer, 18 $\mu$ Devices                                                | 58                    |

| Figure 35. | Set V5, Wafer, 36 $\mu$ Devices                                                           | 59                    |

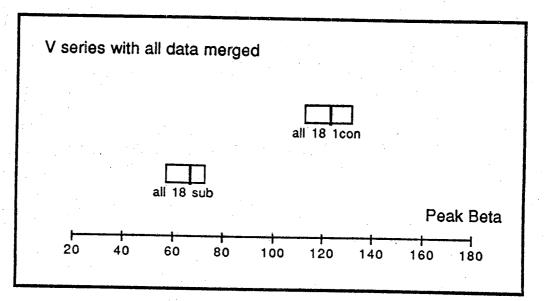

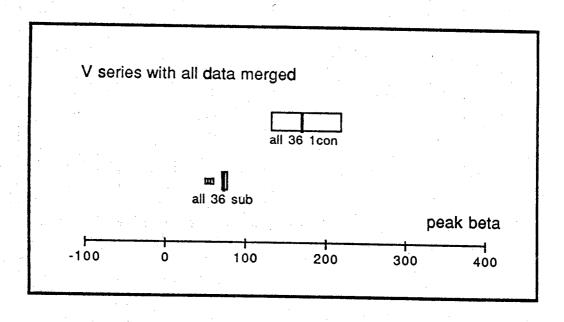

| Figure 36. | All Devices From Set V, V2, V3 and V5                                                     | 60                    |

| Figure 37. | Statistics from All of V2, V3, and V5 Wafers                                              | 61                    |

| Figure 38. | V3 Run Sheet                                                                              | 62                    |

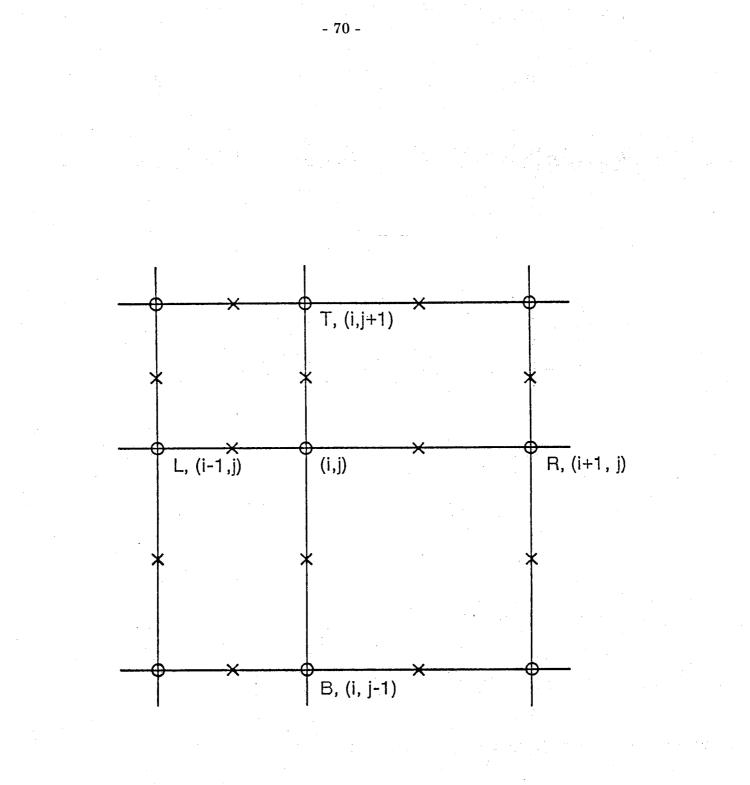

| Figure 39. | Sample Finite Difference Grid                                                             | 69                    |

| Figure 40. | Identification of Interior Node Points                                                    | 70                    |

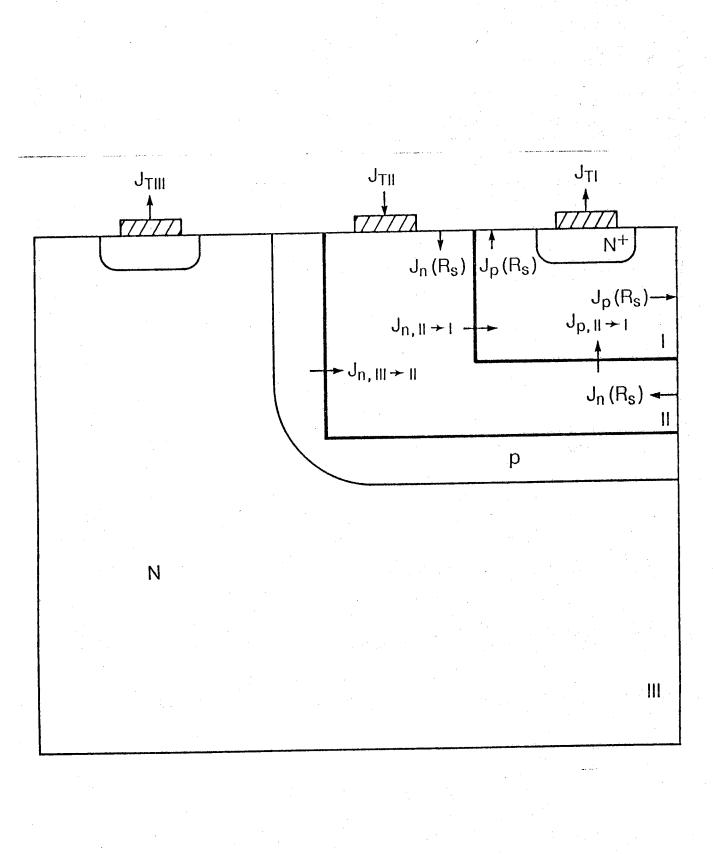

| Figure 41. | Regions of Domain used in Current Calculation                                             | 74                    |

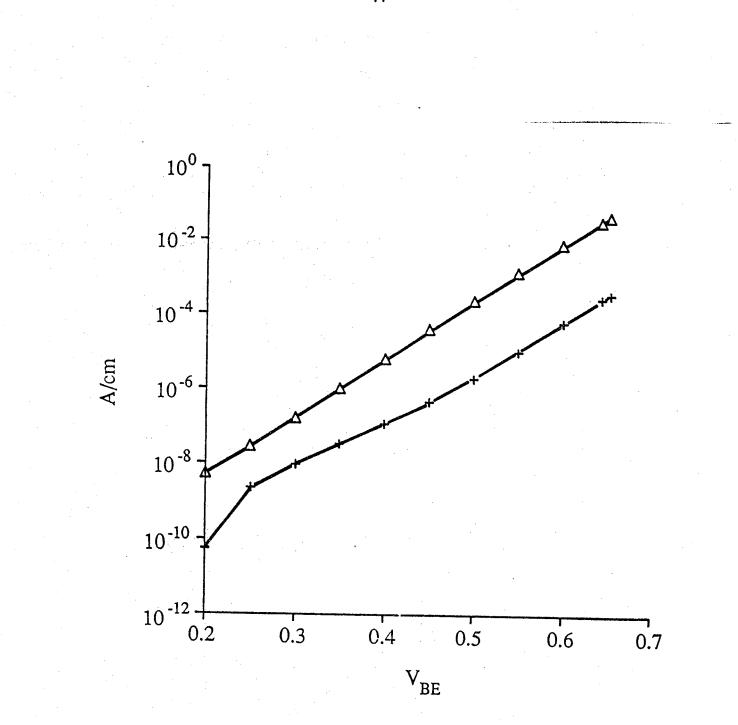

| Figure 42. | Preliminary Simulation Results - $J_B$ vs. $V_{BE}$ and $J_C$ vs. $V_{BE}$ at             | 77                    |

|            | $V_{CE} = 2.5 V$                                                                          |                       |

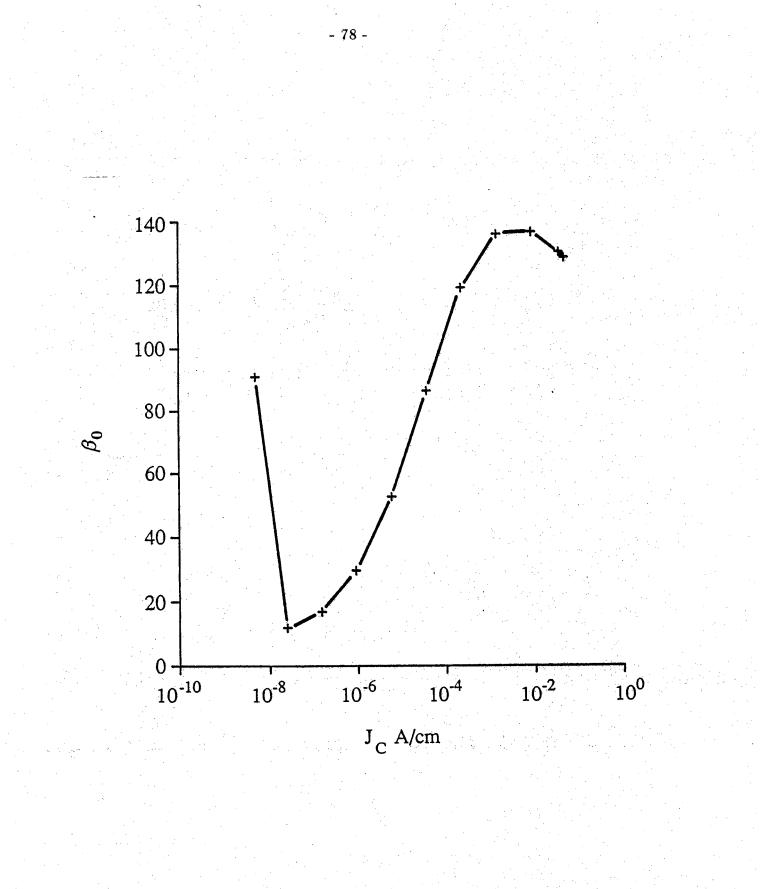

| Figure 43. | Preliminary Simulation Results - $eta_0$ vs. $J_C$ at $V_{CE}=2.5V$                       | 78                    |

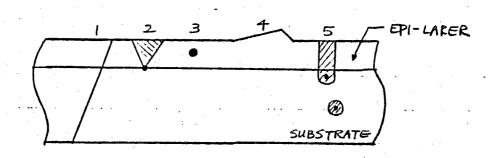

| Figure 44. | Epitaxial Defects                                                                         | 84                    |

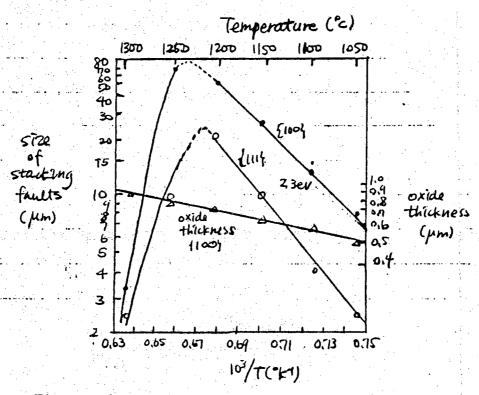

| Figure 45. | The growth vs temperature of oxidation stacking faults in steam                           | 86                    |

|            | for 1 hr.                                                                                 |                       |

| Figure 46. | Defects                                                                                   | 86                    |

| Figure 47. | Stacking Faults                                                                           | 88                    |

| Figure 48. | Stacking Faults                                                                           | 88                    |

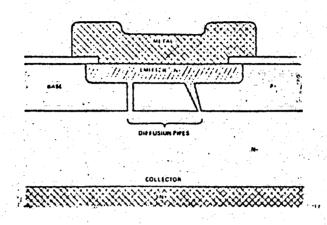

| Figure 49. | Diffusion pipes [1].                                                                      | 97                    |

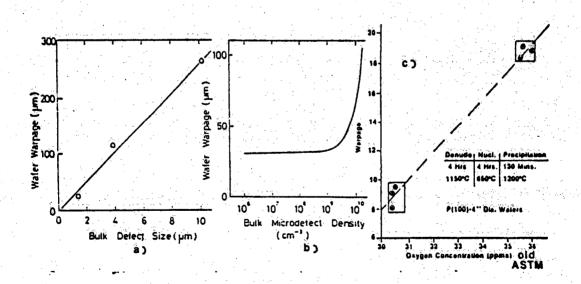

| Figure 50. | (a) Dependence of wafer warpage on bulk microdefect size. (b)                             | 97                    |

|            | Wafer warpage as a function of bulk microdefect density. (c)                              |                       |

|            | Effect of initial oxygen content of wafer on warpage. [17]                                | $a_1^{(1)},a_2^{(2)}$ |

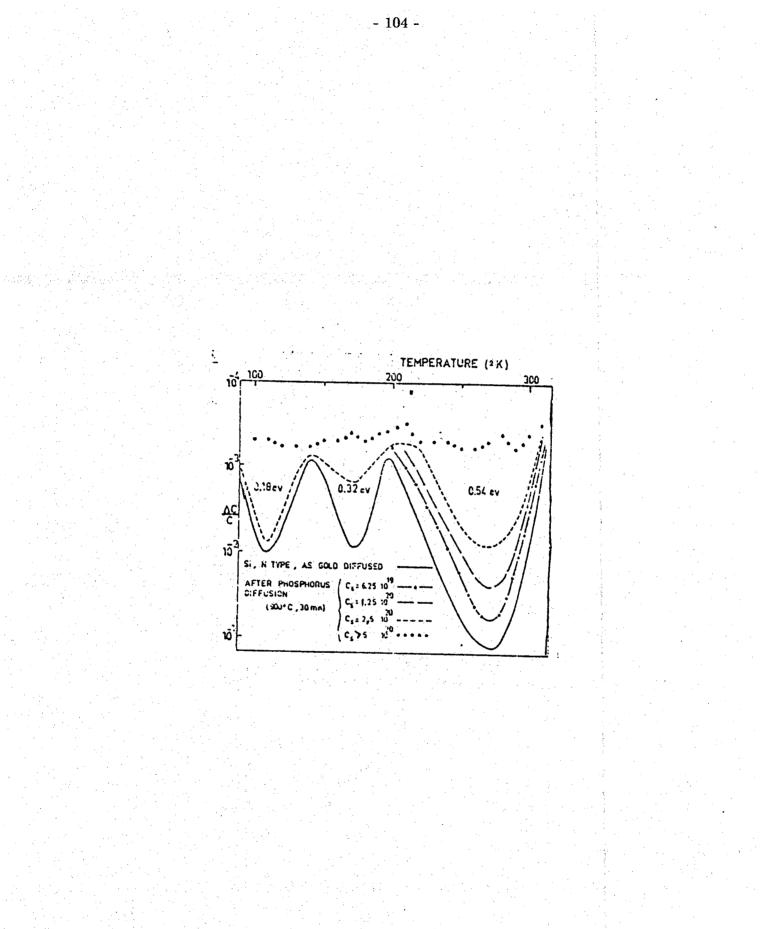

| Figure 51. | DLTS spectra obtained on gold-doped samples gettered with phos-<br>phorus diffusion. [10] | 104                   |

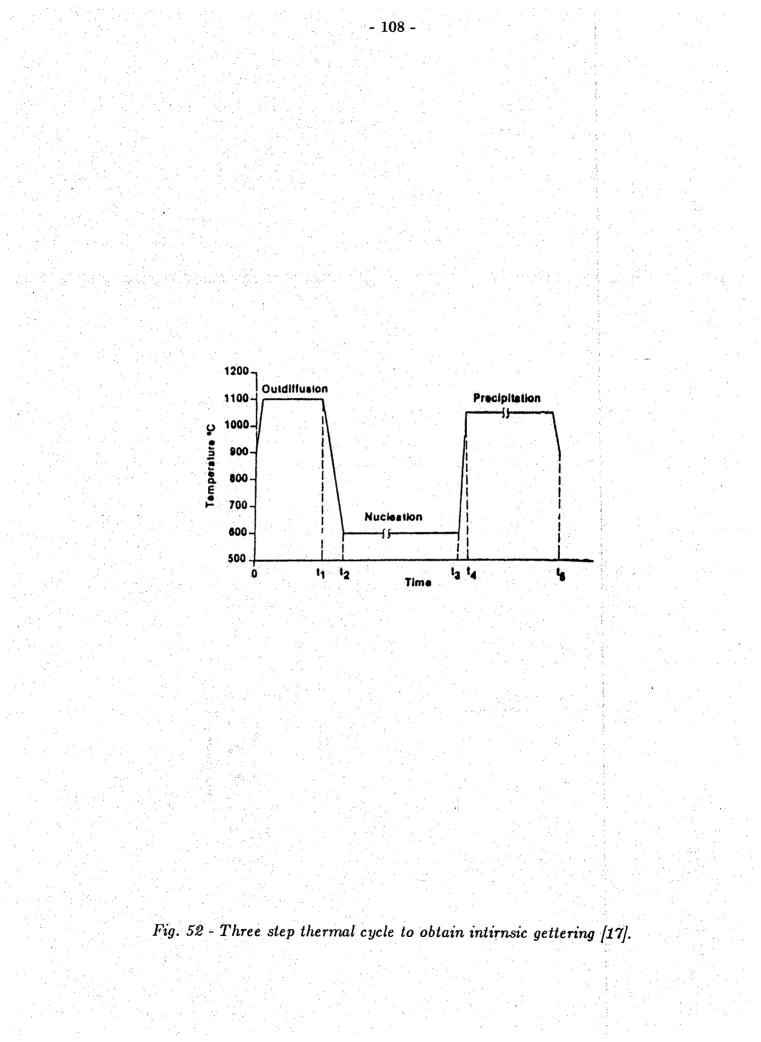

| Figure 52. | Three step thermal cycle to obtain intrinsic gettering [17]                               | 108                   |

- 5 -

#### I. Introduction

The fabrication of extremely small self-aligned emitter structures for bipolar transistors has been realized by using polysilicon in forming the emitter. Two types of emitters are possible. One has polysilicon as part of the very shallow  $N^+$  emitter of the N<sup>+</sup>PN bipolar transistor, i.e. a poly-contacted emitter. The other has the N<sup>+</sup> polysilicon acting as the emitter directly on the P base region, i.e. a true or pure polysilicon emitter. The grain size of the polysilicon and any SiO<sub>2</sub> layer at the polysilicon-emitter base interface will determine the beta of the transistor in an extremely sensitive manner.

- 6

The proposed research was to concentrate on investigating a new method of fabricating polysilicon contacted emitter bipolar transistors and pure poly emitter devices. The technique uses plasma etching the emitter location on the base region and, without breaking vacuum, depositing amorphous silicon (a-Si) on the cleaned interface. The a-Si will then be doped by ion-implantation and heated to 600-700 C<sup>°</sup> to produce the polysilicon emitter, or made polycrystalline and then doped. The controlled interface and the fine grained polysilicon should lead to more uniform and predictable betas for the transistors. Both polysilicon contacted emitters and polysilicon emitters are to be investigated over a range of base doping.

We are proposed to continue the modeling work by extending it in two directions: 1) 2-D simulation so that small geometry transistors can be accurately modeled and 2) simulation of polysilicon emitter transistors. Measurements on the devices described above will be used to develop a polysilicon model. The objective of this part of the project is to develop a numerical device simulator with predictive capability, i.e. one that can be used with confidence in place of actual device fabrication. The numerical device models will be provided to Delco and should find many applications in development and manufacturing.

#### II. The Proposed Research

#### A. Fabrication

Polysilicon contacted emitters have been reported to increase the current gain,  $\beta$ , at a given base charge, Q<sub>B</sub>, or alternatively allow for a much higher base charge at a given  $\beta$  value [1]. The result is the base resistance can be lowered by doping the intrinsic base region heavier, without an overall loss in  $\beta$ . Polysilicon emitters offer an increase in  $\beta$  from 2 to 50 times that of conventional devices. Reproducible fabrication of such enhanced  $\beta$  devices is however still being impeded by the lack of a basic understanding of the physical mechanisms involved at the polysilicon/silicon interface.

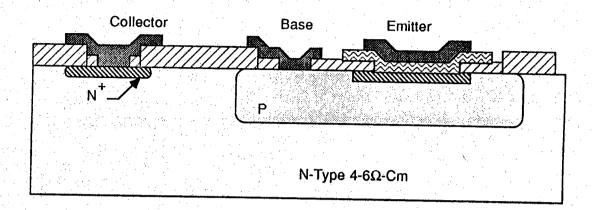

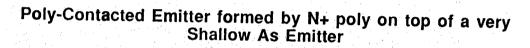

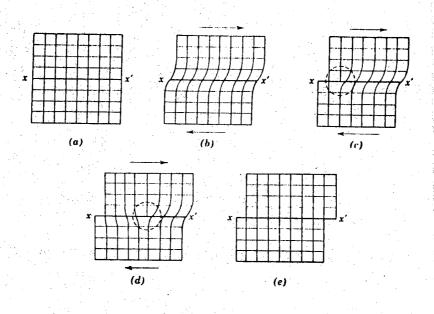

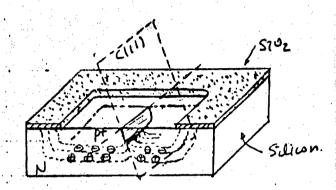

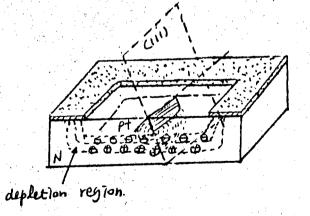

Two types of polysilicon emitter transistors have been identified as illustrated in Figure 1. The pure polysilicon emitter has an intentionally grown layer of SiO<sub>2</sub> (15 to 30 Å thick) at the interface between the polysilicon emitter and the base region [2]. This type of device leads to the largest beta enhancement but is the most unpredictable. The second type of device, the poly-contacted emitter, depends on keeping the interface as free of SiO<sub>2</sub> as possible [3]. In both cases the reduction of base hole current is achieved by reducing the number of holes being injected from the base region to the emitter (a N<sup>+</sup>PN bipolar transistor). The reduced base current yields the  $\beta$  enhancement [4] by improving the emitter injection efficiency. It has been shown that in modern devices with very narrow base widths this base current component is the largest factor in determining beta.

The poly contacted emitter device has applications in very small, very fast digital VLSI devices where  $\beta$  enhancement is not too important but where the self aligned emitters are necessary to get extremely small size transistors and circuits. The self aligned emitter structure reduces the parasitics of the transistor and allows emitter widths of 0.35 micrometers. and have extremely shallow emitter junctions. Another possibility is to increase the base doping to reduce the intrinsic base resistance and speed-up the device without an effective loss in  $\beta$  from the regular transistor. Our work is to concentrate on the poly-contacted emitter. This requires a very shallow emitter and a narrow base width in order to see any beta enhancement.

#### B. Computer Modeling.

Many of the important issues for modeling high performance silicon transistors are already being addressed here at Purdue University. With the experience gained from modeling silicon bipolar transistors in one dimension (under a previous contract with Delco Electronics) and in modeling high efficiency silicon solar cells, we have developed considerable confidence in the accuracy of the physical models used in the simulations. **Polysilicon Emitters**

# Poly Emitter made by N+ poly and a very thin oxide interface between the Poly and P-silicon

Figure 1. Polysilicon Emitter and polysilicon contacted Emitter bipolar transistors.

In order to handle geometry-induced effects, a two-dimensional simulation code must be developed. A 2D code for the simulation of high efficiency silicon solar cells has already been developed and used extensively as an analytic and predictive tool. Modifying the code to handle transistor geometries is a relatively straight forward task. The necessary modifications include handling doubly diffused doping profiles, multiple contacts (as opposed to just two for solar cells), and an accurate method for extracting the terminal currents from the simulation results. Once these modifications are complete, modeling the DC characteristics of Delco's small geometry silicon bipolar transistors will be possible. It is expected that at this stage the code can be used as an analytic and predictive tool.

Further enhancements of the 2D transistor code which will increase the codes usefulness will also be addressed. These are a transient analysis option and a small signal, sinusoidal steady-state analysis option. These enhancements will make the extraction of important device parameters easier and more reliable.

The second phase of the proposed research, to develop such analytic and predictive models for polysilicon emitter transistors, will be considerably more challenging. Two approaches to this problem are proposed. First, for polysilicon contact transistors, the minority carrier reflecting properties of the polysilicon contact will be modeled by an effective surface recombination velocity. This capability already exists in the 2D solar cell code, and so is a logical first step. The second approach, which is considerably more difficult, will be to model the polysilicon as a separate material with its own set of physical characteristics, i.e. bandgap, mobility, lifetime, etc. For this approach, it will be necessary to develop an understanding of the transport properties of polysilicon.

#### References

- 1. Graul, Glasl, & Murrmann, "High Performance Transistors with Arsenic Implanted polysilicon Emitters," *IEEE J. Solid State Circuits*, Vol. SC-11, 1976, pp. 491.

- 2. de Graaff, & de Groots, "The SIS Tunnel Emitter: A Theory for Emitters with Thin Interface Layers," *IEEE Trans. ED*, Vol. ED-26, 1979, pp. 1771.

- 3. Ning & Isaac, "Effect of Emitter Contact on Current Gain of Silicon Bipolar Devices," *IEEE Trans. Ed*, Vol. ED-27, 1980, pp. 2051.

Schaber, Benna, Treitinger, & Wieder, "Conduction Mechanisms of Polysilicon Emitters with Thin Interfacial Oxide Layers," *IEEE IEDM Proceedings*, 1984, pp. 32.1.

- 5. J. W. Slotboom and H. C. De Graaff, "Measurements of Bandgap Narrowing in Si Bipolar Transistors," Solid-State Electron., Vol. 19, pp. 857-862, 1976.

- 6. M. S. Lundstrom, R. J. Schwartz, and J. L. Gray, "Transport Equations for the Analysis of Heavily Doped Semiconductor Devices," Solid-State Electron., Vol. 24, pp. 195-202, 1981.

- H. S. Bennett, "Improved Concepts for Predicting the Electrical Behavior of Bipolar Structure in Silicon," *IEEE Trans. Electron Dev.*, Vol. ED-30, pp. 920-926, 1983.

- 8. A. W. Blakers, M. A. Green, and E. M. Keller, "Experimental Bounds on Band-Gap Narrowing Set by High Open-Circuit Voltage of Silicon Solar Cells," J. Appl. Phys., Vol. 57, pp. 591-599, 1985.

- 9. G. L. Patton, J. C. Bravman, and J. D. Plummer "Physics, Technology and Modeling of Polysilicon Emitter Contacts for VLSI Bipolar Transistors" IEEE Trans. on Electron Devices, vol. ED-33, No. 11 pp. 1754-1768, Nov. 1986.

#### III. Summary of Work in 1986

#### A. Fabrication of Poly-contacted Emitters & Control Transistors

#### Preliminary Control (Substrate) and Polysilicon Devices:

Several standard and polysilicon fabrication runs were made to determine what problems may occur in modifying Purdue's standard bipolar process to accommodate the polysilicon contact to the base region and polysilicon emitter devices. Three types of devices were made; regular, polysilicon ( with a thin oxide interface) and poly emitters ( with little if any oxide at the interface). Once these results were evaluated a set of new photoplate masks and process modifications were designed. The process design was simulated by using the SUPREM III simulator while the test mask set was designed and laid out on our graphics system.

Table I lists the regular phosphorous doped emitter bipolar transistor parameters developed and fabricated in our laboratories. The emitter is 100 microns by 80 microns and the total base is 217 microns by 120 microns. It must be noted that these devices are not made with a buried layer and hence have large collector resistances. The emitter depth is 0.35 microns and the base width is 0.52 microns. Figures 2, 3, and 4 show its main electrical characteristics.

With the substrate device as a reference, several wafers were processed together through the base diffusion and drive steps. For the standard BJT, the collector contact and the emitter are implanted with phosphorous and diffused simultaneously. For the polysilicon devices the emitter window is not opened in the oxide for the implant, but the implant for the collector contact and drive are performed. As a result, the poly-emitter structure has a larger base width by the amount of the emitter diffusion. Suprem II simulations indicated the base widths are 0.46 micrometers and 0.73 micrometers. Therefore we could not expect as large a beta enhancement with the polysilicon emitters as would be the case if the base widths were the same.

The polysilicon was deposited after opening windows in the emitter of the polyemitter devices and trying two types of surface treatment. For one set of wafers the windows were given a buffered HF (BHF) dip to remove as much of the native oxide as possible; the other given the RCA clean which will create a thin 15-20 Å SiO<sub>2</sub> layer. The polysilicon was deposited in the LPCVD tube at 620 °C for 50 minutes and then doped in the phosphorous deposition tube for 20 min at 900 °C.

The poly devices with the BHF will probably have a true oxide free interface and represent the case of some impurities diffusing from the poly to form a very shallow emitter or create the emitter-base junction at the surface of the single crystalline

|                          |                            | Process #4<br>Wafer 11.ii<br>Site 7 |

|--------------------------|----------------------------|-------------------------------------|

| Paramet                  | ers                        | Trans DB                            |

| Peak Be                  | eta                        | 230                                 |

| Early Vol                | tage                       | 60V                                 |

| l <sub>oL</sub>          | b/e                        | 2x10 <sup>-8</sup> A                |

| at -4V                   | b/c                        | 3x10 <sup>-8</sup> A                |

| L <sub>oD</sub>          | b/e                        | 2x10 <sup>-12</sup> A               |

| at -4V                   | b/c                        | 1x10 <sup>-12</sup> A               |

| N                        | b/e                        | 7.25V                               |

| V <sub>BR</sub>          | b/c                        | 46V                                 |

|                          | emit                       | 30                                  |

| Resistance $\Omega/\Box$ | base                       | 1000                                |

| ••/~                     | <sup>.</sup> base<br>pinch | 30,000                              |

|                 | base-emitter   | 1.03                  |

|-----------------|----------------|-----------------------|

| η               | base-collector | 1.21                  |

| •               | base-emitter   | 3x10 <sup>-15</sup> A |

| I <sub>S</sub>  | base-collector | 8x10 <sup>-14</sup> A |

| I <sub>oD</sub> | b/e            | 8x10 <sup>-12</sup> A |

|                 | b/c            | 9x10 <sup>-11</sup> A |

|                 | b/e            | 3x10-4A               |

| I <sub>OL</sub> | b/c            | 5x10 <sup>-8</sup> A  |

| V <sub>BR</sub> | base-emitter   | 7.25V                 |

|                 | base-collector | 46V                   |

Table I.Purdue Process #4 bipolar transistor measured parameters.

Figure 2.

Transistor I-V curves measured on curve tracer. Process #4, wafer 11.ii, transistor 7 dB.

Figure 3. Base and collector currents vs.  $V_{BE}$  with  $V_{CE} = 4V$ . Process #4, wafer 11.ii, transistor 7 dB.

silicon base region. Those with the RCA clean surface treatment will have the oxide barrier to give a heterostructure to the emitter-base and hence a good hole blocking barrier to the base current. Hence the BHF type is expected to have a poor E-B junction (lots of generation-recombination centers) while the RCA type should have beta enhancement.

Table II shows the results of the fabrication runs after measuring the transistor characteristics with the HP 41245A Semiconductor Parameter Analyzer. In the table only the peak betas are recorded and averaged over the number of samples measured. The standard or control BJT has the betas in the range expected from our standard process. Typically they have an Early voltage of about 68 to 74 volts. For the poly emitter device with the BHF dip the betas are much smaller due to the larger base width and the interface region. Our SUPREM II simulations show that the impurity level at the polysilicon/silicon interface is small, which also reduces the beta. The RCA clean device has a maximum beta enhancement of greater than 3 and an average of 2.66. It is actually greater than that because the base width of the poly device is greater than the standard BJT. Figures 5 through 7 illustrate some of the I-V data taken on the devices.

#### Test Wafer Mask Design

The preliminary results were quite encouraging and gave us several insights into how to design a better fabrication process ( to include poly-contacted emitter devices) and to layout a group of test structures and transistors. Four types of transistors were designed, each with a range of emitter sizes formed into an array. The emitter sizes are 18 X 18, 28 X 28, and 36 X 36 microns square. Forty eight devices of each type and size device are available. For example 48 control (substrate) devices with 18 X18 micron square devices are on each wafer. The other 3 types of devices are a polysilicon emitter (em), a poly-contacted emitter completely inside the shallow emitter (1con), and a poly-contacted emitter overlapping the shallow emitter (2con). Figure 8 illustrates the 4 device structures.

| Device      | #  | Beta | Beta | Beta    |

|-------------|----|------|------|---------|

|             |    | max. | min. | average |

| Control BJT | 6  | 206  | 175  | 191.5   |

|             |    | 4 a  |      |         |

| RCA Poly    | 2  | 635  | 386  | 510.5   |

| •           |    |      |      |         |

| BHF Poly    | 11 | 60.4 | 4.2  | 18.55   |

| ~           |    |      |      |         |

Table II. Preliminary Polysilicon Emitter Beta data.

Figure 5. Control BJT  $I_C$  vs.  $V_{CE}$

Figure 6. Control BJT I<sub>B</sub>, I<sub>C</sub> vs. V<sub>BE</sub>

Figure 7. BHF dip Poly Emitter, Ic ws VCE

The test die is shown in Figure 9. Note that it is symmetrical in four quadrants with alignment marks and resolution keys in each. Several large devices of each type have also been included with very large emitters, 576 X 576 microns. The remaining test transistors are 1024 18 X 18 micron emitters in parallel. A section to evaluate the fabrication process parameters is the nearly square section of Figure 10. Sheet resistance, conductance resistance, resistors, four point measurements, etc. have been included. The large features on the outside of the die are for the spreading resistance probe measurements, one for each step of the process.

Figure 8. 4 Types of Devices on Test Mask

Figure 9. Test Wafer Layout, Full die.

÷

-----

| 28<br>2000<br>2000<br>2000<br>2000<br>2000<br>2000<br>2000<br>2        |

|------------------------------------------------------------------------|

|                                                                        |

| 1211 10 9 8 7 6 5 4 3 2 1 36<br>000 000 000 000 000 000 000 000 000 00 |

Figure 10. Quadrant I of test die.

#### Fabrication Runs "E" through "U"

The test die mask set was completed and verified before additional fabrication runs were attempted. The first goal was to establish the control (sub) transistors with the new mask set and with a slightly modified fabrication process. Figure 11 shows the basic process parameters for wafer set "E" with the measured beta for the "sub" devices of about 200. Note the two Boron implants in the base region and this was a phosphorous doped emitter. To further develop the process we attempted to make poly-contacted emitter devices along with the control devices in wafer set "F" as shown in Figure 12. Here the amorphous silicon was deposited by sputtering in the Ion Mill. The betas ranged from 20 to 200.

The requirement that the emitter depth be shallow in order to see the effects (improvement) with a poly-contacted emitter and to compare betas more equally with the control device base width, we attempted to make the emitter much shallower. Wafer set "G" of Figure 13 is the result. Note that again the betas are about 200 and the base width, from SUPREM II, is about 0.5 microns.

## Set E - 4 2'' Wafers Clean Test (solvents/BHF dip)

30 min. 1000 ° H<sub>2</sub> Burn Oxidation Boron Implant,  $3 \times 10^{13}$ /cm<sup>2</sup> @ 140 KeV Boron Implant,  $4 \times 10^{13}$ /cm<sup>2</sup> @ 35 KeV 20 min. 1050 ° H<sub>2</sub> Burn Oxidation Phos. Implant,  $7 \times 10^{15}$ /cm<sup>2</sup> @ 80 KeV 20 min. 900 ° H<sub>2</sub> Burn Oxidation

## $\beta \simeq 200$

| Suprem II |          |             |

|-----------|----------|-------------|

|           | Junction |             |

|           | Depth    | Resistivity |

| E/B       | .34µ     | 39Ω/□       |

| B/C       | .86µ     | 3.5kΩ/□     |

#### Figure 11. Wafer set E

Set F - 8 2" Wafers Phos. Process Development

30 min. 1000 ° H<sub>2</sub> Burn Oxidation

Boron Implant, (varied)

20 min. 1050 ° H<sub>2</sub> Burn Oxidation

or 15 min. 1050 ° H<sub>2</sub> Burn Oxidation

Phos. Implant, 6×10<sup>15</sup>/cm<sup>2</sup> @ 50 KeV

20 min. 900 °  $H_2$  Burn Oxidation  $\alpha$ -Si Deposition (Ion Mill)

$\beta = 20$  to 200

Figure 12. Wafer set F with phosphorous emitters

Set G - 3 2'' Wafers Deep As Emitter Process

30 min. 1000 ° H<sub>2</sub> Burn Oxidation Boron Implant,  $1 \times 10^{14}$ /cm<sup>2</sup> @ 35 KeV 15 min. 1050 ° H<sub>2</sub> Burn Oxidation 30 min. 1050 ° Dry Oxidation As Implant,  $1 \times 10^{16}$ /cm<sup>2</sup> @ 50 KeV 10 min. 1000 ° H<sub>2</sub> Burn Oxidation

## $\beta \simeq 200$

| Suprem II |              |             |

|-----------|--------------|-------------|

|           | Junction     |             |

|           | Depth        | Resistivity |

| E/B       | .15µ         | 60Ω/□       |

| B/C       | .67 <i>µ</i> | 2.5kΩ/□     |

### Figure 13. Wafer set G with a deep As Emitter

## Set H - 8 2'' Wafers Deep As Emitter Process Development

30 min. 1000 ° H<sub>2</sub> Burn Oxidation Boron Implant,  $3 \times 10^{13}$ /cm<sup>2</sup> @ 140 KeV Boron Implant,  $4 \times 10^{13}$ /cm<sup>2</sup> @ 35 KeV 25 min. 1000 ° H<sub>2</sub> Burn Oxidation As Implant,  $3 \times 10^{15}$ /cm<sup>2</sup> @ 35 KeV 15 min. 1000 ° H<sub>2</sub> Burn Oxidation

$\beta \simeq 10$  to 15

| Suprem II |          |             |

|-----------|----------|-------------|

|           | Junction |             |

|           | Depth    | Resistivity |

| E/B       | .14µ     | 70Ω/□       |

| B/C       | .68µ     | 1.4kΩ/□     |

#### Figure 14. Wafer Set H, deep As emitter

## Set I - 12 2" Wafers Deep As Emitter Process Development

30 min. 1000 °  $H_2$  Burn Oxidation Boron Implant,  $1-4 \times 10^{13}/cm^2$  @ 25-80 KeV As Implant,  $3-10 \times 10^{15}/cm^2$  @ 35 KeV 10 min. 1000 °  $H_2$  Burn Oxidation

## $\beta < 1$

| Suprem II |                |             |

|-----------|----------------|-------------|

|           | Junction       |             |

|           | Depth          | Resistivity |

| E/B       | <b>.0</b> 216µ | 45-6800Ω/□  |

| B/C       | .36µ           | 2.5-15kΩ/□  |

Figure 15. Wafer Set I

### Set J - 8, 2" Wafers

### Shallow As Emitter with Poly Contact

30 min. 1000 ° H<sub>2</sub> Burn Oxidation Define Base Regions 10 min. 900 ° H<sub>2</sub> Burn Oxidation Boron Implant,  $1 \times 10^{13}$ /cm<sup>2</sup> @ 35 Kev Define Emitter Regions 10 min. 900 ° H<sub>2</sub> Burn Oxidation As Implant,  $6 \times 10^{15}$  @ 35 Kev 10 min. 1000 ° H<sub>2</sub> Burn Oxidation Define Poly Windows RCA Clean Poly deposition, 24min. @ 620 ° (.1 to .3 $\mu$ ) As Implant,  $1 \times 10^{13}$ - $10^{16}$  @ 35 Kev Define Polysilicon Metallization(Ion Mill), 25min. Al-Si-Cu

### $\beta \sim 60$ to 90

Figure 16. Wafer Set J, Shallow As Emitter

# Set K

4, 2" Wafers, and 4 quarters of 1, 4" Wafer

Shallow As Emitter with Poly Contact

20 min. 1000 ° H<sub>2</sub> Burn Oxidation Define Base Regions 10 min. 900 ° H<sub>2</sub> Burn Oxidation Boron Implant,  $1 \times 10^{13}$ /cm<sup>2</sup> @ 35 Kev Define Emitter Regions 10 min. 900 ° H<sub>2</sub> Burn Oxidation As Implant,  $6 \times 10^{15}$  @ 25-35 Kev 10 min. 1000 ° H<sub>2</sub> Burn Oxidation Define Poly Windows RCA Clean Poly deposition, 24min. @ 620 ° (.1 to .3 $\mu$ ) As Implant,  $1 \times 10^{16}$  @ 35 Kev Define Polysilicon Metallization(Ion Mill), 30min. Al-Si-Cu

# $\beta \simeq 100$ to 170 (Tested in Package)

Figure 17. Shallow As emitter and a poly-contact

# Set L - 4 quarters of 1, 4" Wafer

Shallow As Emitter with Poly Contact Annealed

20 min. 1000 ° H<sub>2</sub> Burn Oxidation Define Base Regions 10 min. 900 ° H<sub>2</sub> Burn Oxidation Boron Implant,  $1 \times 10^{13}/\text{cm}^2$  @ 35 Kev Define Emitter Regions 10 min. 900 ° H<sub>2</sub> Burn Oxidation As Implant,  $6 \times 10^{15}$  @ 35 Kev 10 min. 1000 ° H<sub>2</sub> Burn Oxidation Define Poly Windows RCA Clean Poly deposition, 6min. @ 620 ° (.1 to  $.3\mu$ ) As Implant,  $6 \times 10^{15}$  @ 35 Kev N<sub>2</sub> Anneal, 10min. @ 900-1000 ° Define Polysilicon Metallization(Ion Mill), 30min. Al-Si-Cu

## Bad Contacts

Figure 18. Wafer set L shallow As emitter with poly contact anneals

## Set M - 8 quarters of 2, 4" Wafers

## Shallow As Emitter with Poly Contact Annealed

20 min. 1000  $^\circ$  H\_2 Burn Oxidation **Define Base Regions** 10 min. 900° H<sub>2</sub> Burn Oxidation Boron Implant, 1×10<sup>13</sup>/cm<sup>2</sup> @ 35 Kev **Define Emitter Regions** 10 min. 900 ° H<sub>2</sub> Burn Oxidation As Implant, 6×10<sup>15</sup> @ 35 Kev 10 min. 1000 ° H<sub>2</sub> Burn Oxidation Define Poly Windows (#2-5,7,8)RCA Clean (#2-4), BHF etch (#5,7,8) Poly deposition, 9min. @  $620^{\circ}$  (.1 to  $.3\mu$ ) As Implant,  $6 \times 10^{15}$  @ 35 Kev N<sub>2</sub> Anneal, 10-60min. @ 800-900° **Define** Polysilicon Define Contacts (#1-8)Metallization(Ion Mill), 30min. Al-Si-Cu

$eta=20 ext{ to }40$

Figure 19. Wafer set M, shallow As emitter with poly-contact anneals

The next set of devices were designed to have Arsenic doped emitters for a shallower emitter depth. The diffusion of the emitter Arsenic impurities would be much slower than that of phosphorous. Wafer set H,I,J,K,L, and M are the result of these attempts. Another thing to notice is that the wafer sets J,K,L, and M were cleaned with the RCA cleaning method after their polysilicon window openings are defined. Here the amorphous silicon was deposited in a LPCVD tube and annealed to become polysilicon. Wafer sets "H" and "I" are just attempts to make control devices with As emitters for a shallow emitter depth. The effects of various implant energy, dose, and drive-in temperatures were investigated. The Figure 14 and Figure 15 show process parameters and the measured beta for wafer set "H and "I".

In wafer set "J", the As implant into the polysilicon was performed with various implant doses to investigate this effect. The poly-contact devices of wafer set "J" showed a beta of less than that of the control device. Figure 16 shows the process parameters for wafer set "J" with the measured beta values, which ranged from 60 to 90.

Up to wafer set "J", only 2" wafers were used for making devices. From wafer set "K", 4 inch wafers were often used after being cut into 4 quarters. Wafer set "K" had some variations in As implant energy to make shallower emitter depths. As shown in Figure 17, wafer set "K" had good control BJT's but the poly-contacted emitter had less gain, with the poly-emitter having no gain at all. They were tested after being bonded and packaged.

In wafer set "L, only 4 quarters of a 4" wafer were used and annealing of the polysilicon, after being implanted with As, was performed under different conditions to see the differences. The process parameters are in Figure 18. Wafer set "L" had bad contacts due to too thick an oxide in the window which was not completely etched.

In wafer set "M", part of wafers were cleaned using the RCA cleaning method, and the others were etched with BHF after the polysilicon windows were defined. Also the annealing of polysilicon, after implanted with As, was performed at different temperatures for various time periods. The beta values ranged from 20 to 40 as shown in Figure 19. Wafer set "M" was processed and parts of several wafers were sent to Delco for spreading resistance profiles. The results were somewhat inconclusive as to where the junctions were located due to not having a thick oxide. The test results from the above fabrication runs indicated that we should consider "gettering" as part of the process to reduce the leakage currents and the generation-recombination in the junctions. Additional wafer fabrication sets M,N,O,P,Q, and R have been processed in an attempt to analyze the problem with the As doped emitter fabrication process. Up to wafer set "R", it appeared that we might have a contamination problem in the oxidation furnaces and with the metallization for the contacts. The metallization was solved by going from an evaporator system to a clean sputtering system for the aluminum. Previously we had used an Al-Si-Cu target in the Ion Mill but it degraded for some unknown reason.

In wafer set "N", different gettering methods were performed for comparison; i.e. polysilicon gettering, phosphorous gettering, or both. They were done by depositing those materials on the back of the wafers.

Set N - 4 quarters of 1, 4" Wafer

Gettering, Pd/Al Contacts

30 min. 1000  $^{\circ}$  H<sub>2</sub> Burn Oxidation #2,4 : Poly deposition(back), 40min. @ 660  $^{\circ}$  ( $\simeq 1\mu$ ) #3,4 : Phosphorus deposition(back), 30min. @ 1000° Drive-in, 30min. @ 1000° 20min. 1000 ° H<sub>2</sub> Burn Oxidation **Define Base Regions** 10 min. 900 ° H<sub>2</sub> Burn Oxidation Boron Implant, 1×10<sup>13</sup>/cm<sup>2</sup> @ 35 Kev **Define** Emitter Regions 10 min. 900 ° H<sub>2</sub> Burn Oxidation As Implant,  $6 \times 10^{15}$  @ 35 Kev 10 min. 1000° H<sub>2</sub> Burn Oxidation Define Contacts (#1-4) Metallization (Ion Mill), Sputter Pd/Al Pd: 10min. @ 15mA Al: 20min. @ 20mA

Figure 20. Wafer set N, Pd/Al Contacts

# Set O - 4 quarters of a 4" Wafer

Contacts

30 min. 1000 ° H<sub>2</sub> Burn Oxidation Mask Back, Etch Front Define Contacts Metallization (Ion Mill) #1 : 10min. etch, 30min. coat Al-Si-Cu

#2:30min.coat Al-Si-Cu

#3:10min. etch, 10min. Pd, 30min. Al

#4:10min. Pd coat, 30min. Al coat

| Bre | eakdown V | oltages |

|-----|-----------|---------|

| #   | No        | 600°    |

|     | Anneal    | Anneal  |

| 01  | 13V       | 13V     |

| O2  | 11-12V    | 0-6V    |

| O3  | 2-3V      | 0-4V    |

| 04  | 0-1V      | 0-4V    |

Figure 21. Wafer set "O".

## Set P - 4 quarters of a 4" Wafer

### Shallow As Emitter with Different Contact Methods

### No RCA Clean

Poly Getter (back)

40 min. 1000 °  $H_2$  Burn Oxidation Poly Deposition, 10 min. @ 660° 20 min. 1000 ° H<sub>2</sub> Burn Oxidation Define Base Regions 15-25 min. @ 900-1000 ° Dry Oxidation Boron Implant, 1×10<sup>13</sup>/cm<sup>2</sup> @ 35 Kev Define Emitter Regions 10 min. 900 ° H<sub>2</sub> Burn Oxidation (#1,3) 25 min. 1000 ° Dry Oxidation (#2,4) As Implant,  $6 \times 10^{15}$  @ 35 Kev 10 min. 1000 ° H<sub>2</sub> Burn Oxidation Define Poly Windows RCA Clean, BHF etch Poly deposition, 9min. @ 620° (.1 to  $.3\mu$ ) As Implant, 6×10<sup>15</sup> @ 35 Kev  $N_2$  Anneal, 60min. @ 700 ° Define Polysilicon Define Contacts Metallization(Perkin-Elmer), RF sputter Al

### $\beta = 0$ to 300

#### Some Good Contacts, Still Bad Leakage

Figure 22. Wafer Set P, As Emitter with Various, Contacts Metal.

## Set Q - 4, 2" Wafers

## Boron P/N Diode

Poly Getter-Back (#2)

30 min. 1000° H<sub>2</sub> Burn Oxidation

Poly Deposition, 40 min. @ 660°

30 min. 1000 °  $H_2$  Burn Oxidation

BHF etch

As Implant-Back, 5×10<sup>15</sup>/cm<sup>2</sup> @ 35 Kev

10 min. 900 °  $H_2$  Burn Oxidation

Boron Implant - Front

#1.2 :  $3 \times 10^{13}$ /cm<sup>2</sup>, @ 140 Kev  $4 \times 10^{13}$ /cm<sup>2</sup>, @ 35 Kev

$#3: 1 \times 10^{13} / \text{cm}^2$ , @ 35 Kev

$#4:7\times10^{12}/\text{cm}^2$ , @ 25 Kev

25 min. 1000° Wet Oxidation (#1,2)

20 min. 1000° Dry, 10 min. 1000° wet Oxidation (#3,4)

Define Contacts

Metallization(Perkin-Elmer), RF sputter Al 30 min.

$\begin{array}{l} \#1: \mathrm{N/P} \ \mathrm{Junction} ? \ \mathrm{Front} \ \mathrm{Contact} \ \mathrm{V_{BR}}{\simeq} 4\mathrm{V}, \ \mathrm{Forward} \ \mathrm{O.K.} \\ \#2: \mathrm{P/N} \ \mathrm{Junction} ? \ \mathrm{Front} \ \mathrm{Contact} \ \mathrm{V_{BR}}{\simeq} 4\mathrm{V}, \ \mathrm{Forward} \ \mathrm{O.K.} \\ \#3: \mathrm{P/N}, \ \mathrm{Base} \ \mathrm{-} \ \mathrm{Back} \ \mathrm{V_{BR}} > 4.0, \ \mathrm{Forward} \ \mathrm{Bad} \ \mathrm{Junction} ? \\ \mathrm{Base} \ \mathrm{-} \ \mathrm{Collector} \ \mathrm{V_{BR}} > 10, \ \mathrm{Forward} \ \mathrm{-} \ \mathrm{High} \ \mathrm{Resistance} ? \\ \#4: \mathrm{P/N} \ \mathrm{Best} \ \mathrm{Junctions} \ \mathrm{-} \ \mathrm{Back} \ \mathrm{Contacts} \end{array}$

Figure 23. Wafer Set Q, P-N Diodes

# Set R - 4, 2" Wafers

Shallow As Emitter Process Development

25 min. 1000 °  $H_2$  Burn Oxidation Define Base Regions Boron Implant,  $2 \times 10^{13}/cm^2$  @ 25 Kev 10 min. 1000 °  $H_2$  Burn Oxidation Define Emitter Regions As Implant,  $1 \times 10^{15}$  @ 25 Kev 10 min. 900-1100 °  $H_2$  Burn Oxidation Define Contacts Metallization(P-E), RF sputter Al, 25 min.

Al - not Annealed

## Some Good/Bad Contacts

Figure 24. Wafer Set R, Shallow As Emitters

## Set S - 4, 2" Wafers

## Shallow As Emitter with Different Getterings

Poly Getter (back) - #1 30 min. 1000 ° H<sub>2</sub> Burn Oxidation Poly Deposition, 80 min. @ 620 ° Intrinsic Gettering - #2 30 min. 1000 ° H<sub>2</sub> Burn Oxidation N<sub>2</sub> Anneal, 2-3 days @ 600 ° BHF etch (front) - #1,2 30 min. 1000 ° H<sub>2</sub> Burn Oxidation Define Base Regions Boron Implant,  $2 \times 10^{13}$ /cm<sup>2</sup> @ 25 Kev 10 min. 1000 ° H<sub>2</sub> Burn Oxidation Define Emitter Regions,  $1 \times 10^{15}$ /cm<sup>2</sup> @ 25 Kev Define Contacts Metallization(Perkin-Elmer), RF sputter Al #1,2 : 15 min. Presputter, 5 min. Etch

12 min. Sputter, Lift-off

Contacts still bad,  $\beta = 150$  to 100

#3,4 : 3 min. Etch, 30 min. Presputter and Sputter Lift-off(#3), Wet etch Al(#4)

> Contacts still bad,  $\beta \simeq 20$ Figure 25. Wafer Set S; Gettering

Also, the metallization process was changed in this wafer set from Al-Si-Cu sputtering to Pd/Al sputtering with the hope of preventing Al spiking into the silicon. The change in metallization did not cure of the contact problem.

In wafer set "O", only metallization methods were investigated. Combination of etching and coating of Al-Si-Cu and Pd/Al was applied to the contact area, even for different time periods to figure out the best way for metallization. The process steps and data are shown in Figure 21.

The polysilicon gettering seemed to work consistently better than the phosphorous gettering and it does not cause problems in contaminating the furnace tubes as comparing to phosphorous gettering. Therefore, only polysilicon gettering was applied to wafer set "P". Another large change was that metallization was performed in Perkin-Elmer RF sputtering system instead of in the Ion Mill starting with wafer set "P". With the new metallization system, some devices showed good contacts, but there was still large leakage currents. The bad leakage currents may have come from pure Al sputtering and that it was removed when we used an Al-Si target. Boron (or As) implants were performed through very thin oxides so that we can obtain a narrow base width and a shallow emitter junction with reasonable value of implant energies. The betas of the "sub" devices ranged from 0 to 300 as shown in Figure 22.

Boron P/N diodes were made in wafer set "Q" with several variations of gettering, boron implant dose and energy, and drive-in times and temperatures. We measured P/N junction breakdown voltages and contact resistance. The results are shown in Figure 23.

Wafer set "R" shows another As emitter process development. Boron/As implant was performed after BHF etch of the base/emitter regions. Implant energy became almost the lower limit of the implanter (25 Kev) to make a narrow base width and a shallow emitter junction. Metallization was done by sputtering Al in the Perkin-Elmer, and the Al was not annealed. There were still some bad contacts.

Up to wafer set "R", bad contacts and high leakage current were the main trouble. Dislocations and stacking fault experiments were performed to determine the quality of both the 2" and the 4" wafers. This method is explained in a later chapter. It was found that quarters of 4" wafers had many more dislocations or stacking faults than 2" wafers. The method used to cut 4" wafers into 4 quarters generated large stress on the cutting edge and that turned out to be the main cause for dislocations or stacking faults to occur. Therefore, from wafer set "R", 2" wafers were mainly used for the processing.

In order to reduce the junction leakage current in wafer set "S", both polysilicon and intrinsic gettering were applied. And for the contact problem, 8 different metalization techniques, which includes presputtering, etching, and Al sputtering, were used. The contacts were still bad, but some devices showed fairly good betas with ranges from 100 to 150. They are shown in Figure 25.

Some wafers had polysilicon gettering and some had oxide gettering on wafer set "T". The RCA cleaning method was used for all the wafers after the As implant. The metallization step included pre-etching of the target. Most devices showed poor quality base-emitter junctions as shown in Figure 26.

## Set T - 8, 2" Wafers

### Shallow As Emitter with Different Getterings

All Wafers Cleaned with RCA Clean

2 Wafers : Poly Gettering, 60 min. @ 620°

2 Wafers : Oxide Gettering, 2 days @ 600°

25 min. 1000 °  $H_2$  Burn Oxidation

Define Base Regions

Boron Implant, 2×10<sup>13</sup>/cm<sup>2</sup> @ 25 Kev (#1-7) 3×10<sup>13</sup>/cm<sup>2</sup> @ 25 Kev (#8)

5 min. 1000°  $\mathrm{N}_2$  Anneal (#2-7)

Define Emitter Regions

As Implant, 1×10<sup>15</sup>/cm<sup>2</sup> @ 25 Kev (#1-4,6,8) 6×10<sup>14</sup>/cm<sup>2</sup> @ 25 Kev (#5)

RCA Clean

10 min. 550° N<sub>2</sub> Anneal (#4-8)

10 min. 1000 ° N<sub>2</sub> Anneal (#3-8)

10 min. 1000 °  $H_2$  Burn Oxidation

Define Contacts

Metallization(Perkin-Elmer), RF sputter Al

Etch Wafer, Preetch Target, Coat Al 30 min.

#### Little or No Base-Emitter Junction

Probably Etched Emitter off before Al Deposition

Figure 26. Wafer Set T, gettering study.

## $\operatorname{Set} \mathrm{U}$

- 46 -

6, 2" Wafers and 2 quarters of a 4" Wafer

Shallow As Emitter Process Development

Al-Si & Annealed Contacts

#6 : BHF Etch, RCA Clean

#1-8:30 min. 1000  $^{\circ}$  H<sub>2</sub> Burn Oxidation

#1-4 : Phosphorus Deposition, 15 min. 1000°

Phosphorus Drive, 15 min. 1000° Dry Oxid.

#1-4,5,8: Poly Deposition, 80 min. 620°

25 min. 1000 ° H<sub>2</sub> Burn Oxidation

**Define Base Regions**

Boron Implant, 2-5×10<sup>15</sup>/cm<sup>2</sup> @ 25 Kev

#6 : Clean, BHF Dip, RCA Clean

10 min. 1000 ° H<sub>2</sub> Burn Oxidation)

**Define Emitter Regions**

As Implant, 1×10<sup>15</sup>/cm<sup>2</sup> @ 25 Kev (#1-4,6,8)

#6 : RCA Clean, 10 min. 1000 ° H<sup>2</sup> Burn Oxidation

**Define Contacts**

Metallization(P-E), RF sputter Al-Si 40 min.

$N^2$  Anneal @ 500°  $\rightarrow$  Spiking

$N^2$  Anneal @ 400°  $\rightarrow$  Good Contacts

Figure 27a. Wafer Set U.

From wafer set "U" on, the metallization was done with an Al-Si target instead of a pure Al target. Control devices with different getterings (polysilicon gettering and phosphorous gettering) and changes in the boron implant were fabricated. Also, the RCA cleaning method was used in one wafer. Metallization was done with an Al-Si target, and the devices were annealed at various temperatures. A 400 C° anneal in a nitrogen ambient made good contacts and 500 C° annealing caused spiking to occur. Some results are tabulated in Figure 27a.

#### Wafer Set V

In wafer set "V", all the devices had polysilicon gettering. Boron and As implants were done without any intentional oxide and the implant energy applied was 25 Kev for both materials. The control transistors had a very shallow emitter, reasonable leakage currents, good ideality factors, and betas ranging from of 50 to 70. In polysilicon emitter contact transistors, the As dose level implanted into the polysilicon and the temperature for annealing polysilicon had a large effect on the current gain. In wafer set "V3", we had good control (sub)transistors and polysilicon contact transistors (1 con). The next step will be to change the base doping and observe the difference in current gain for both types of devices.

## Set V - 26, 2" Wafers (#0-25)

## Shallow As Emitter With Poly Contacts

#1-25 : 30 min. 1000 °  $H_2$  Burn Oxidation Poly Gettering, 80 min. @ 620° 25 min. 1000 °  $H_2$  Burn Oxidation **Define Base Regions** Boron Implant, 3×10<sup>13</sup>/cm<sup>2</sup> @ 25 Kev 10 min. 1000 ° H<sub>2</sub> Burn Oxidation **Define Emitter Regions** As Implant,  $1 \times 10^{15}$ /cm<sup>2</sup> @ 25 Kev #2-8 : 10 min. 900 °  $H_2$  Burn Oxidation Define Poly Windows Poly Deposition, 8 min. @ 620° As Implant, #2,3,7 : 1×10<sup>15</sup> @ 25 Kev #4,5,8 : 3×10<sup>15</sup> @ 25 Kev **Poly Definition** 10 min. 800-1000 ° H<sub>2</sub> Burn Oxidation #0,1-5,7,8 : Define Contacts Metallization(Perkin-Elmer), RF sputter Al-Si Presputter 10 min., Sputter Al 30 min.

#### Best Results Obtained

Figure 27b. Wafer Set V, good Poly Contacted and Control Devices.

#### Wafer set V Results

Wafer set V resulted in good substrate (control) devices and good polysilicon contacted devices. The average the peak betas, leakage currents, ideality factors, and breakdown voltages were all very reasonable. Preliminary results of wafer set are tabulated as shown in Figure 27b. Wafers labeled V2, V3, and V5 are listed.

The data in Figure 28 can be interpreted as follows:

- 1. The "wafer lot" is series "V", the wafer number is "V3"; "V3-ii-36" means from V3 quadrant "ii" on the wafer and a 36 micron by 36 micron emitter devices in the package.

- 2. The type of device is "sub" for the control or metal contacted BJT, while the polysilicon contacted emitter is called "1con" or "con1".

- 3. Each device has a label; i.e. "con1 12" is the 12th device in the array of polysilicon contacted devices. Therefore "V3-ii-36-con1-12" is from wafer set V, wafer 3, 2nd quadrant, a 36  $\mu \times 36 \mu$  device, and polysilicon contacted emitter.

- 4. The complete testing data is enclosed for 18  $\mu \times 18 \mu$  sub; 18  $\mu \times 18 \mu$  1con; 36  $\mu \times 36 \mu$  sub; and 36  $\mu \times 36 \mu$  1con devices.

- 5. The data was obtained on a HP 4145A Semiconductor Parameter analyzer. Analysis of the data was with a computer program to take slopes, projections, maximum values, etc. Both the emitter base and the collector base junctions are measured, with IS as the forward biased extrapolated coefficient;  $\eta(\text{eta})$  is the slope from ideal; res is the emitter or collector series resistances; Vebo is the E-B breakdown voltage, lebo is the measured reverse bias leakage current; Vcbo is the C-B breakdown voltage, lcbo is the measured reverse bias leakage current; Vceo is the C-E base open breakdown; Max beta is the peak beta, etc.

Figure 29 through Figure 33 are the statistical data on the devices tested. Figure 29 has all the statistical data on wafer "V2" for the 36  $\mu \times 36 \mu$  1con and substrate devices. Note that for the 36  $\mu$  by 36  $\mu$  devices the ratio of the beta polycontacted/metal contacted is about 2.278 for the average peak betas. The squares are the 25% and 75% marks of the data and the solid line is the median. The tightness of the betas for the control devices is better than that of the polycontacted devices.

Figure 30 illustrates a comparison of wafer V3 for the 18  $\mu \times 18 \mu$  and 36  $\mu \times 36 \mu$  devices, while Figure 31 lists the statistical data for the 18  $\mu \times 18 \mu$  transistors. For the 18  $\mu \times 18 \mu$  devices the ratio of the beta poly-contacted/metal contacted is about 1.715 for the average peak betas. Figure 32 shows that for the 36  $\mu$  by 36  $\mu$  devices the ratio of the beta poly-contacted is about 2.997 for the average peak betas. Figure 33 illustrates a comparison of wafer V5 for the 18  $\mu \times 18 \mu$  and 36  $\mu \times 36 \mu$  devices, while Figure 34 lists the statistical data for the 18  $\mu \times \mu$  transistors. For the 18  $\mu \times \mu$  devices the ratio of the beta poly-contacted/metal contacted is about 1.771 for the average peak betas. Figure 35 shows that for the 36  $\mu$  by 36  $\mu$  devices the ratio of the beta poly-contacted is about 2.566 for the average peak betas.

Figures 36 and 37 are a result of combining all the data from wafers V2, V3, and V5. Clearly the poly-contacted devices show a beta enhancement over the sub devices. All devices have identical processing on each wafer. The 36  $\mu$ m emitter structures show better beta enhancement results because the ratio of the area to perimeter is larger. Wafer V3 had a 1000 C° poly anneal and wafer V5 had a 900 C° anneal. The results show that the 1000 C° anneal has produced a better set of poly contacted emitter devices. Figure 38 lists the "run sheet" for wafer V3.

base/emitter

base/collector

| · · · ·           | e fa se en el | · · · ·  |       | 1.1.1.1.1.1.1 |          |         | · · · · |       |                |                                         | 1       |                 |     |

|-------------------|---------------|----------|-------|---------------|----------|---------|---------|-------|----------------|-----------------------------------------|---------|-----------------|-----|

|                   | Is            | eta      | res   | Veb0          | Ieb0     | Is      | eta     | res   | Vcb0           | Icb0                                    | max     | Vce0            | 2   |

|                   | Amps          |          | kohms | @1uA          | Amps     | Amps    |         | kohms | @1uA           | Amps                                    | beta    | @1mA            |     |

| v3-ii-18c- sub 1  | 1.5e-15       | 1.08     | 0.2   | 8.40          | 2.90e-12 | 5.1e-15 | 1.07    | 0.3   | 51.00          | 1.77e-10                                | 70.1    | 51.22           |     |

| v3-ii-18c-sub2    | 2.7e-11       | 2.00     | 0.1   | 0.20          | 1.57e-05 | 9.4e-15 | 1.08    | 0.3   | 17.40          | 5.64e-08                                | 15.6    | 51.22           |     |

| v3-ii-18-sub3     | 2.3e-15       | 1.10     | 0.2   | 8.40          | 2.28e-11 | 5.0e-14 | 1.20    | 0.3   | 53.00          | 4.19e-08                                | 71.1    | -53.66          |     |

| v3-ii-18-sub4     | 1.7e-15       | 1.08     |       | 8.60          | 2.03e-11 | 6.6e-15 | 1.08    | 0.3   | 51.00          | 1.16e-11                                | 10000.0 | -51.22          |     |

| v3-ii-18c-sub6    | 1.2e-15       | 1.07     | 0.2   | 8.40          | 7.00e-12 | 4.7e-15 | 1.06    | 0.3   | 50.40          | 1.39e-11                                | 72.9    | 49.76           |     |

| v3-ii-18c-sub8    | 1.3e-15       | 1.07     | 0.2   | 8.40          | 5.40e-12 | 4.9e-15 | 1.06    | 0.3   | 51.00          | 1.60e-11                                | 70.9    | 51.22           |     |

| v3-ii-18-sub9     | 1.9e-15       | 1.09     | 0.2   | 8.00          | 3.05e-11 | 7.4e-15 | 1.08    | 0.3   | 53.00          | 1.36e-11                                | 74.2    | -5 <b>3.6</b> 6 |     |

| v3-ii-18-sub10    | 1.8e-15       | 1.08     | 0.2   | 8.40          | 2.71e-11 | 6.8e-15 | 1.07    | 0.3   | 53.00          | 2.71e-08                                | 74.7    | -53.66          |     |

| v3-ii-18-sub11    | 1.6e-15       | 1.08     | 0.2   | 8.60          | 2.91e-11 | 6.2e-15 | 1.07    | 0.6   | 52.00          | 1.46e-11                                | 1       | -56.10          |     |

| v3-ii-18c-sub12   | 1.4e-15       | 1.08     | 0.2   | 8.50          | 8.10e-12 | 5.0e-15 | 1.06    | 0.3   | 52.20          | 1.59e-09                                | 70.9    | 52.68           |     |

| v3-iii-18c-sub11  | 1.7e-15       | 1.08     | 0.2   | 8.80          | 5.20e-12 | 5.3e-15 | 1.06    | 0.3   | 51.60          | 1.82e-11                                | 74.1    | 51.22           |     |

| v3-iii-18c-sub12  | 1.4e-15       | 1.07     | 0.2   | 8.70          | 4.65e-12 | 5.2e-15 | 1.06    | 0.3   | 51.00          | 1.13e-09                                | 76.9    | 51.22           |     |

| v3-iv-18c-sub2    | 1.6e-15       | 1.08     | 0.2   | 8.40          | 5.00e-14 | 6.2e-15 | 1.07    | 0.3   | 50.40          | 1.46e-11                                | 82.5    | 51.22           |     |

| v3-iv-18c-sub5    | 1.7e-15       | 1.08     | 0.2   | 8.60          | 7.35e-12 | 6.7e-15 | 1.07    | 0.3   | 49.80          | 1.25e-11                                | 77.6    | 49.76           |     |

| v3-iv-18c-sub11   | 2.1e-15       | 1.09     | 0.2   | 8.60          | 5.25e-12 | 7.1e-15 | 1.07    | 0.3   | 51.00          | 1.21e-11                                | 76.3    | 51.22           | •   |

| v3-iv-18c-sub12   | 2.4e-15       | 1.09     | 0.2   | 8.60          | 1.60e-12 | 7.5e-15 | 1.08    | 0.3   | 51.00          | 1.37e-11                                | 79.8    | 51.22           |     |

| v3-ii-18-1con1    | 2.0e-15       | 1.11     | 0.6   | 7.40          | 6.69e-11 | 6.9e-15 | 1.08    | 0.3   | 53.00          | 2.44e-08                                | 136.2   | -53.66          |     |

| v3-ii-18c-1con2   | 3.8e-15       | 1.12     | 0.5   | 5.90          | 1.76e-11 | 1.9e-07 | 2.32    | 0.5   | 1.20           | 8.56e-05                                | 10000.0 | 4.39            |     |

| v3-ii-18-1con3    | 1.5e-15       | 1.10     | 0.5   | 7.40          | 5.76e-11 | 5.4e-15 | 1.06    | 0.3   | 31.00          | 5.60e-11                                | 148.6   | -31.71          |     |

| v3-ii-18c-1con4   | 1.4e-15       | 1.09     | 0.5   | 7.30          | 4.05e-12 | 4.8e-15 | 1.06    | 0.3   | 31.20          | 8.09e-09                                | 135.4   | 49.76           |     |

| v3-ii-18-1con5    | 4.1e-15       | $1,\!15$ | 0.5   | 7.40          | 2.88e-11 | 7.4e-15 | 1.07    | 0.3   | 52.00          | 1.48e-11                                | 122.3   | -51.22          |     |

| v3-ii-18c-1con6   | 1.3e-15       | 1.09     | 0.6   | 7.10          | 3.35e-12 | 4.6e-15 | 1.06    | 0.3   | 52.20          | 1.36e-11                                | 127.3   | 52.68           |     |

| v3-ii-18c-1con7   | 1.5e-15       | 1.10     | 0.6   | 7.30          | 6.20e-12 | 5.0e-15 | 1.06    | 0.3   | 51.60          | 6.65e-12                                | 124.7   | 51.22           |     |

| v3-ii-18c-1con8   | 1.5e-15       | 1.09     | 0.7   | 7.20          | 4.20e-12 | 5.1e-15 | 1.06    | 0.3   | 49.20          | 7.90e-12                                | 131.8   | 49.76           |     |

| v3-ii-18-1con9    | 1.9e-15       | 1.10     | 0.7   | 7.40          | 4.61e-11 | 8.6e-14 | 1.21    | 0.3   | 53.00          | 1.30e-11                                | 116.1   | -53.66          |     |

| v3-ii-18-1con10   | 2.0e-15       | 1.11     | 0.8   | 7.40          | 4.69e-11 | 6.8e-15 | 1.07    | 0.3   | 53.00          | 1.18e-11                                | 114.5   | -53.66          |     |

| v3-ii-18c-1con11  | 1.4e-09       | 1.59     | 1.8   | 2.80          | 3.27e-07 | 4.8e-15 | 1.05    | 0.3   | 51.00          | 1.51e-11                                | 13.9    | 52.68           |     |

| v3-ii-18c-1con12  | 1.1e-14       | 1.20     | 1.2   | 7.30          | 3.01e-09 | 1.4e-14 | 1.12    | 0.3   | 15.00          | 4.23e-07                                | 70.5    | 30.73           |     |

| v3-iii-18c-1con1  | 1.5e-15       | 1.09     | 0.9   | 7.30          | 5.10e-12 | 6.3e-15 | 1.07    | 0.3   | 50.40          | 1.35e-11                                | 123.9   | 51.22           | ÷., |

| v3-iii-18c-1con2  | 1.2e-15       | 1.08     | 0.9   | 7.30          | 6.60e-12 | 5.5e-15 | 1.06    | 0.3   | 49.80          | 8.76e-10                                | 121.0   | 49.76           |     |

| v3-iii-18c-1con5  | 1.3e-15       | 1.08     | 1.0   | 7.40          | 6.40e-12 | 6.1e-15 | 1.06    | 0.3   | 50.40          | 1.30e-11                                | 109.4   | 51.22           |     |

| v3-iii-18c-1con8  | 1.2e-15       | 1.08     | 0.9   | 7.30          | 6.75e-12 | 5.9e-15 | 1.06    | 0.3   | 48.60          | 8.80e-12                                | 125.9   | 49.76           |     |

| v3-iii-18c-1con11 | 1.5e-15       | 1.09     | 0.8   | 7.40          | 6.40e-12 | 5.9e-15 | 1.06    | 0.3   | 47.40          | 7.20e-12                                | 126.3   | 48.29           |     |