## Purdue University Purdue e-Pubs

**Open Access Dissertations**

Theses and Dissertations

January 2016

# Programming models, compilers, and runtime systems for accelerator computing

Amit Sabne *Purdue University*

Follow this and additional works at: https://docs.lib.purdue.edu/open\_access\_dissertations

#### **Recommended** Citation

Sabne, Amit, "Programming models, compilers, and runtime systems for accelerator computing" (2016). *Open Access Dissertations*. 1396. https://docs.lib.purdue.edu/open\_access\_dissertations/1396

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

# PURDUE UNIVERSITY GRADUATE SCHOOL Thesis/Dissertation Acceptance

This is to certify that the thesis/dissertation prepared

By Amit Sabne

Entitled Programming Models, Compilers, and Runtime Systems for Accelerator Computing

For the degree of \_\_\_\_\_ Doctor of Philosophy

Is approved by the final examining committee:

RUDY EIGENMANN

MILIND KULKARNI

ANAND RAGHUNATHAN

#### SAMUEL P. MIDKIFF

To the best of my knowledge and as understood by the student in the Thesis/Dissertation Agreement, Publication Delay, and Certification/Disclaimer (Graduate School Form 32), this thesis/dissertation adheres to the provisions of Purdue University's "Policy on Integrity in Research" and the use of copyrighted material.

#### RUDY EIGENMANN

| A | Approved | l by | <sup>v</sup> Major | Professor(s | :): |  |

|---|----------|------|--------------------|-------------|-----|--|

|   |          |      |                    |             |     |  |

|   |          |      |                    |             |     |  |

|   |          |      |                    |             |     |  |

|   |          |      |                    |             |     |  |

| Approved by: V. Balakrishnan | 07/21/2016 |

|------------------------------|------------|

|                              |            |

Head of the Department Graduate Program

Date

# PROGRAMMING MODELS, COMPILERS, AND RUNTIME SYSTEMS FOR ACCELERATOR COMPUTING

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Amit J. Sabne

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

August 2016

Purdue University

West Lafayette, Indiana

Dedicated to Ramprasad Joshi who cultivated my inquisitiveness

#### ACKNOWLEDGMENTS

First and foremost, I thank my advisor, Prof. Rudolf Eigenmann, whose unconditional support made this dissertation possible. His remarkable patience and flexibility helped me navigate through the process so much so I barely realized that he was physically away for half the duration. I admire his willingness to provide me complete independence in my research and his wisdom that got me out of dead ends from time to time.

Many people kept me motivated through the PhD process. I thank my committee members Prof. Samuel Midkiff, Prof. Anand Raghunathan, and Prof. Milind Kulkarni for the inspiring interactions. I thank Prof. Charles Bouman, Xiao Wang, and Jordan Kisner for their help through the MBIR project. I am grateful to Prof. T. N. Vijaykumar for his insightful comments in the HeteroDoop project. My present and former labmates have been a useful bunch to brainstorm with. I thank them all: Putt Sakdhnagool, Okwan Kwon, Fahed Jubair, Hansang Bae, Aurangzeb, and Tsung-Tai Yeh. I am grateful to my collaborator-turned-mentors, Prof. Jeffrey Vetter and Seyong Lee from the Oak Ridge National Laboratory for their valuable guidance.

The PhD process required a lot of personal support too. I thank my parents, my sister, and Kanak, my girlfriend, to have shown unwavering faith in me and to have sacrificed a lot over the years. I was fortunate to have been roommates with my old friends from the undergraduate years: Rohan Gandhi, Neeraj Gadgil, and Saikumar Reddy. I thank all my friends – the list is too long to be mentioned – for their immense support.

I am grateful to the J. N. Tata Endowment for awarding me the scholarship for graduate studies.

Finally, I must thank the faculty and staff of the ECE department, as well as Purdue University, to have offered me the PhD opportunity and to have made my stay here a joyful ride.

## TABLE OF CONTENTS

|    |      |        |                                                                                | Page |

|----|------|--------|--------------------------------------------------------------------------------|------|

| LI | ST O | F TAB  | LES                                                                            | ix   |

| LI | ST O | F FIGU | URES                                                                           | x    |

| Al | BSTR | ACT    |                                                                                | xiv  |

| 1  |      |        | OF COMPILER OPTIMIZATIONS IN<br>TO CUDA TRANSLATION                            | 1    |

|    | 1.1  | Introd | luction                                                                        | 1    |

|    | 1.2  | Overv  | iew of OpenMPC System                                                          | 3    |

|    |      | 1.2.1  | Optimization options                                                           | 3    |

|    |      | 1.2.2  | Improving the OpenMPC Tuning System                                            | 5    |

|    | 1.3  | Modif  | ied IE (MIE) Algorithm for OpenMPC                                             | 9    |

|    |      | 1.3.1  | Iterative Elimination                                                          | 9    |

|    |      | 1.3.2  | Grouping of different Optimization Options                                     | 10   |

|    |      | 1.3.3  | MIE Running Strategy                                                           | 12   |

|    | 1.4  | Perfor | mance Analysis                                                                 | 13   |

|    |      | 1.4.1  | Setup                                                                          | 13   |

|    |      | 1.4.2  | Performance Comparison Between Pruned Exhaustive and<br>Modified IE Algorithms | 13   |

|    |      | 1.4.3  | Impact of Individual Optimization Options                                      | 14   |

|    | 1.5  | Chapt  | er Takeaways                                                                   | 17   |

| 2  |      |        | LARGE-DATA COMPUTATIONS ON MULTI-GPU ACCEL-                                    | 19   |

|    | 2.1  |        | luction                                                                        | 19   |

|    | 2.2  | Prelin | ninaries                                                                       | 22   |

|    |      | 2.2.1  | GPUs and CUDA                                                                  | 22   |

|    |      | 2.2.2  | OpenMPC                                                                        | 23   |

# Page

vi

|   | 2.3 | COSP    | - An Enabler Technique                                      | 24 |

|---|-----|---------|-------------------------------------------------------------|----|

|   |     | 2.3.1   | Catering to Arbitrary Device Memory Sizes                   | 24 |

|   |     | 2.3.2   | COSP Through a Code Example                                 | 27 |

|   | 2.4 | Pipelin | ning                                                        | 29 |

|   |     | 2.4.1   | Achievable Speedup from Pipelining                          | 30 |

|   |     | 2.4.2   | Compiler Organization                                       | 32 |

|   |     | 2.4.3   | Generating Pipelined Code                                   | 33 |

|   |     | 2.4.4   | Multi-GPU Code Generation                                   | 37 |

|   | 2.5 | Adapt   | ive Runtime Tuning System                                   | 38 |

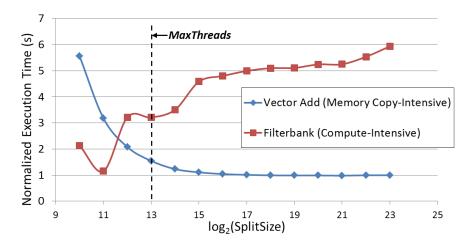

|   |     | 2.5.1   | Performance Variation with SplitSize                        | 38 |

|   |     | 2.5.2   | Adaptive Runtime Tuning Algorithm                           | 41 |

|   |     | 2.5.3   | Compiler Support for Tuning                                 | 44 |

|   | 2.6 | Evalua  | ation                                                       | 45 |

|   |     | 2.6.1   | System Scalability                                          | 46 |

|   |     | 2.6.2   | Tuning System Performance                                   | 48 |

|   |     | 2.6.3   | Overall Performance Comparison                              | 50 |

|   | 2.7 | Relate  | d Work                                                      | 50 |

|   | 2.8 | Chapt   | er Takeaways                                                | 53 |

| 3 |     |         | OOP : A MAPREDUCE PROGRAMMING SYSTEM FOR AC-<br>OR CLUSTERS | 54 |

|   | 3.1 |         | uction                                                      | 54 |

|   | 3.2 |         | ninaries                                                    | 58 |

|   | 0.2 | 3.2.1   | CUDA Architecture and Programming                           | 58 |

|   |     | 3.2.2   | MapReduce and Hadoop                                        | 59 |

|   | 3.3 |         | Doop Directives                                             | 61 |

|   | 0.0 | 3.3.1   | HeteroDoop Directives with an Example                       | 61 |

|   |     | 3.3.2   | Clauses for Memory and Thread Attributes                    | 64 |

|   | 3.4 |         | iler                                                        | 66 |

|   | ა.4 | Comp    | Щеι                                                         | 00 |

# Page

|   |                                                                                          | 3.4.1                                                                                               | Map Kernel Generation                                          | 68                                                                                                                           |

|---|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                          | 3.4.2                                                                                               | Combine Kernel Generation                                      | 71                                                                                                                           |

|   |                                                                                          | 3.4.3                                                                                               | Host Code for Offloading                                       | 74                                                                                                                           |

|   | 3.5                                                                                      | Overa                                                                                               | ll Execution and Runtime System                                | 75                                                                                                                           |

|   |                                                                                          | 3.5.1                                                                                               | Overall Execution                                              | 76                                                                                                                           |

|   |                                                                                          | 3.5.2                                                                                               | Assisting GPU Execution                                        | 77                                                                                                                           |

|   |                                                                                          | 3.5.3                                                                                               | Implementing MapReduce Semantics                               | 78                                                                                                                           |

|   | 3.6                                                                                      | Tail S                                                                                              | cheduling                                                      | 79                                                                                                                           |

|   |                                                                                          | 3.6.1                                                                                               | GPU-First Execution vs Tail Scheduling                         | 81                                                                                                                           |

|   | 3.7                                                                                      | Evalua                                                                                              | ation                                                          | 83                                                                                                                           |

|   |                                                                                          | 3.7.1                                                                                               | Benchmarks                                                     | 83                                                                                                                           |

|   |                                                                                          | 3.7.2                                                                                               | Cluster Setups                                                 | 85                                                                                                                           |

|   |                                                                                          | 3.7.3                                                                                               | Overall Improvements                                           | 88                                                                                                                           |

|   |                                                                                          | 3.7.4                                                                                               | Detailed Analysis                                              | 88                                                                                                                           |

|   |                                                                                          |                                                                                                     |                                                                |                                                                                                                              |

|   | 3.8                                                                                      | Relate                                                                                              | ed Work                                                        | 92                                                                                                                           |

|   | 3.8<br>3.9                                                                               |                                                                                                     | ed Work                                                        | 92<br>94                                                                                                                     |

| 4 | 3.9<br>FOR                                                                               | Chapt                                                                                               | er Takeaways                                                   |                                                                                                                              |

| 4 | 3.9<br>FOR                                                                               | Chapt<br>MALIZ<br>PLOSIC                                                                            | er Takeaways                                                   | 94                                                                                                                           |

| 4 | 3.9<br>FOR<br>EXP                                                                        | Chapt<br>CMALIZ<br>PLOSIC<br>Introd                                                                 | er Takeaways<br>ZED CONTROL FLOW STRUCTURING WITHOUT CODE<br>N | 94<br>96                                                                                                                     |

| 4 | 3.9<br>FOR<br>EXP<br>4.1                                                                 | Chapt<br>MALIZ<br>PLOSIC<br>Introd<br>Prelin                                                        | er Takeaways                                                   | 94<br>96<br>96                                                                                                               |

| 4 | <ul><li>3.9</li><li>FOR</li><li>EXP</li><li>4.1</li><li>4.2</li></ul>                    | Chapt<br>Chapt<br>PLOSIC<br>Introd<br>Prelin<br>Analy                                               | er Takeaways                                                   | 94<br>96<br>96<br>101                                                                                                        |

| 4 | <ul> <li>3.9</li> <li>FOR</li> <li>EXP</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> </ul> | Chapt<br>Chapt<br>PLOSIC<br>Introd<br>Prelin<br>Analy                                               | er Takeaways                                                   | 94<br>96<br>96<br>101<br>104                                                                                                 |

| 4 | <ul> <li>3.9</li> <li>FOR</li> <li>EXP</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> </ul> | Chapt<br>Chapt<br>COSIC<br>Introd<br>Prelin<br>Analy<br>Struct                                      | er Takeaways                                                   | 94<br>96<br>96<br>101<br>104<br>116                                                                                          |

| 4 | <ul> <li>3.9</li> <li>FOR</li> <li>EXP</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> </ul> | Chapt<br>Chapt<br>COSIC<br>Introd<br>Prelin<br>Analy<br>Struct<br>4.4.1                             | er Takeaways                                                   | 94<br>96<br>96<br>101<br>104<br>116<br>117                                                                                   |

| 4 | <ul> <li>3.9</li> <li>FOR</li> <li>EXP</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> </ul> | Chapt<br>Chapt<br>COSIC<br>Introd<br>Prelin<br>Analy<br>Struct<br>4.4.1<br>4.4.2                    | er Takeaways                                                   | <ul> <li>94</li> <li>96</li> <li>96</li> <li>101</li> <li>104</li> <li>116</li> <li>117</li> <li>120</li> </ul>              |

| 4 | <ul> <li>3.9</li> <li>FOR</li> <li>EXP</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> </ul> | Chapt<br>MALIZ<br>PLOSIC<br>Introd<br>Prelin<br>Analy<br>Struct<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4 | er Takeaways                                                   | <ul> <li>94</li> <li>96</li> <li>96</li> <li>101</li> <li>104</li> <li>116</li> <li>117</li> <li>120</li> <li>124</li> </ul> |

|    |      |          |                                                                       | Page |

|----|------|----------|-----------------------------------------------------------------------|------|

|    |      | 4.5.2    | Structuring Algorithm                                                 | 132  |

|    |      | 4.5.3    | Termination Proof and Time Complexity of the Structuring<br>Algorithm | 133  |

|    | 4.6  | Avoidi   | ing Exponential Blowup                                                | 135  |

|    |      | 4.6.1    | Removing Irreducibility with Node Splitting                           | 135  |

|    |      | 4.6.2    | How Does the Structuring Algorithm Avoid Exponential<br>Blowup?       | 137  |

|    | 4.7  | Relate   | ed work                                                               | 138  |

|    | 4.8  | Exper    | iments                                                                | 139  |

|    |      | 4.8.1    | Setup                                                                 | 140  |

|    |      | 4.8.2    | Code Size Expansion on Random CFGs                                    | 140  |

|    |      | 4.8.3    | Unstructuredness in Compiler-generated CFGs                           | 141  |

|    |      | 4.8.4    | Obfuscation by Irreducibility Insertion                               | 142  |

|    |      | 4.8.5    | Case Study on a GPU Program                                           | 146  |

|    | 4.9  | Chapt    | er Takeaways                                                          | 147  |

| 5  | Cone | clusions | and Future Work                                                       | 148  |

| RF | EFER | ENCES    | S                                                                     | 150  |

| VI | TA   |          |                                                                       | 162  |

## LIST OF TABLES

| Tabl | le                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1  | Optimization options in OpenMPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6    |

| 1.2  | Variations on GPU Programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7    |

| 1.3  | Grouping of OpenMPC Options for Tuning (MemTR = Memory Transfer<br>Optimization, Comp = Computation Optimization). Options in paran-<br>thesis imply multi-values options                                                                                                                                                                                                                                                                                                                                                                                                                 | 11   |

| 1.4  | Tuning Time Comparison of Pruned Exhaustive Vs. Modified IE Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 16   |

| 2.1  | Scalability of the <i>COSP</i> and Pipelining Mechanism : We compare the execution times of hand-written CUDA, baseline OpenMPC and compute split, pipelined OpenMPC programs. The ideal speedup is calculated using Eq. 2.2. In the table, '***' represent failure of the code due to larger-than-<br>allowed grid sizes used. '' represent code failure due to out-of-memory data size errors. Scalability of our approach can be gauged as arbitrarily large problems with out-of-card data sizes can be run and the speedup achieved for any large data size remains almost constant. | 46   |

| 3.1  | HeteroDoop Directives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 65   |

| 3.2  | Description of the Benchmarks Used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 84   |

| 3.3  | Description of the Benchmarks Used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 84   |

| 3.4  | Cluster Setups Used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 86   |

| 4.1  | Unstructuredness of CFGs in NAS Benchmarks: Even the functions with structured source code can have unstructuredness in the compiler front-end generated CFG. Optimized CFGs are more likely to possess unstructuredness.                                                                                                                                                                                                                                                                                                                                                                 | 142  |

## LIST OF FIGURES

| Figu | ire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

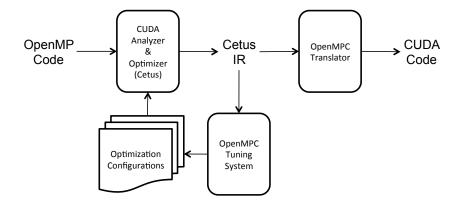

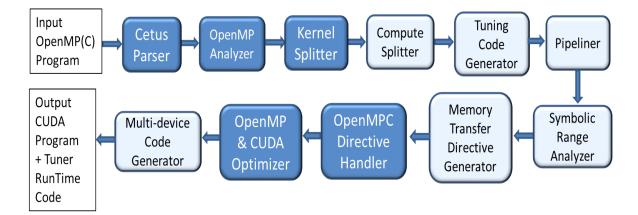

| 1.1  | OpenMPC workflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3    |

| 1.2  | OpenMPC translation example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4    |

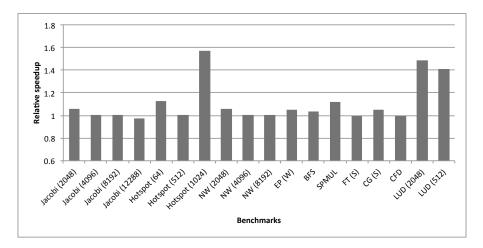

| 1.3  | Program Speedups of Modified IE relative to Pruned Exhaustive Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14   |

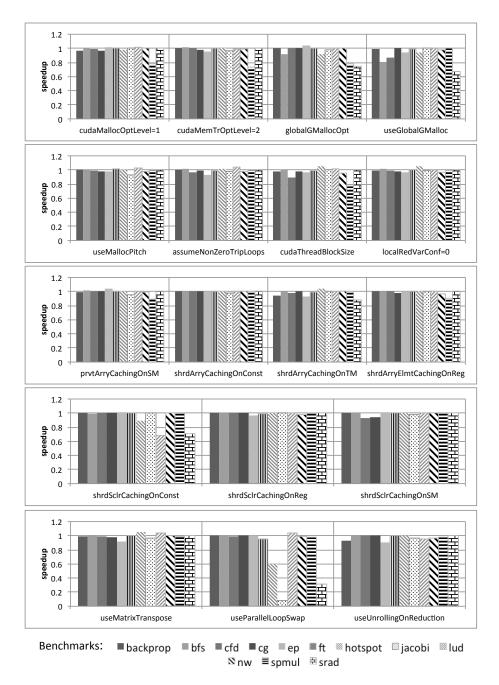

| 1.4  | Individual impacts of the 18 optimizations. Bars show normalized per-<br>formance of the benchmarks after disabling the selected optimization. A<br>large drop in performance indicates high impact.                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15   |

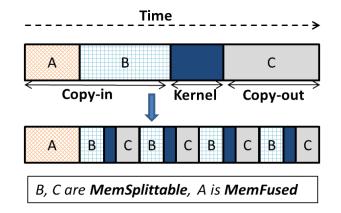

| 2.1  | COSP - MemSplittable data can be split since only a part of them is required per chunk of computation, MemFused is the part of the data accessed by every chunk.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25   |

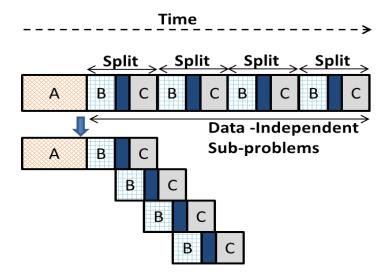

| 2.2  | Pipelining Opportunity Generated by <i>COSP</i> : Individual Splits are independent; they can be pipelined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30   |

| 2.3  | Overall System Flow : Darker boxes indicate the base OpenMPC passes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32   |

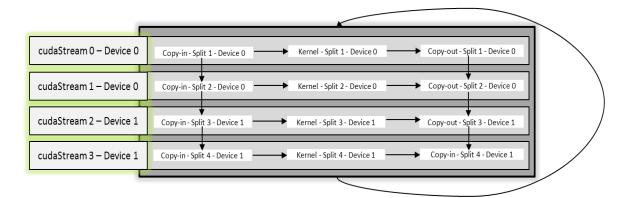

| 2.4  | System Strategy to generate and run programs on Multiple Devices - In this case, the number is 2. Straight arrows depict dependences, the curved arrow represents Split loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35   |

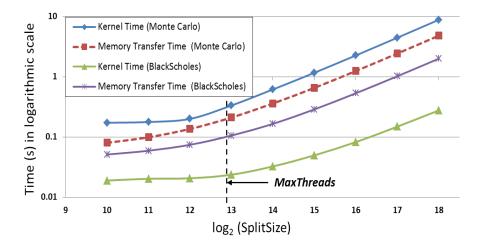

| 2.5  | Performance Variation with SplitSize : Performance is higher for smaller SplitSizes for compute-intensive benchmarks, while for memory copy-<br>intensive ones, performance is higher for larger SplitSizes. <i>MaxThreads</i> is the maximum number of threads that can co-exist on the GPU                                                                                                                                                                                                                                                                                                                                                             | 40   |

| 2.6  | Kernel execution and Memory copy times per Split for different SplitSizes.<br>Monte Carlo is compute-intensive; Black Scholes is memory copy-intensive.<br>Experiments were run on Tesla M2090.                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40   |

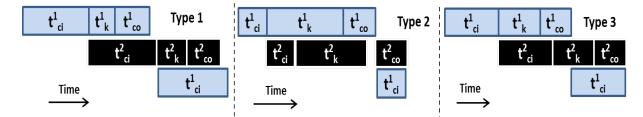

| 2.7  | Possible Overlap Types for GPUs with Distinct Copy-in and Copy-out<br>Engines : $t_{ci}$ is the copy-in time, $t_{co}$ is the copy-out time and $t_k$ is the kernel<br>execution time. Number in the superscript represents the <i>cudaStream</i> .<br>Type 1 is the highly memory copy-intensive type with $t_{ci} > t_{co} + t_k$ . Note<br>that $t_{ci}$ and $t_{co}$ are interchangeable. Type 2 is highly compute-intensive,<br>with $t_k > t_{ci} + t_{co}$ . Type 3 is neither ( $t_{ci} > t_k > t_{co} \& t_k + t_{co} > t_{ci}$ ).<br>Note that shown is one of the many cases of different program patterns<br>that can fit in <i>Type 3</i> . | 41   |

## Figure

| xi |  |

|----|--|

|    |  |

| Figu | re                                                                                                                                                                                                                                                             | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

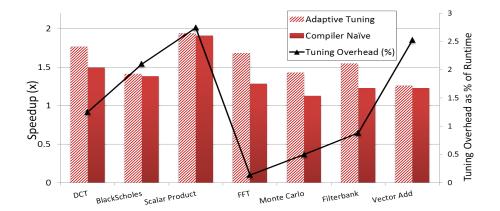

| 2.8  | Performance of Adaptive Runtime Tuning System : Speedups are with<br>respect to the OpenMPC non-pipelined baseline. Higher performance of<br>the tuned program versions over a naive pipelining approach emphasize<br>the necessity of tuning                  | 48   |

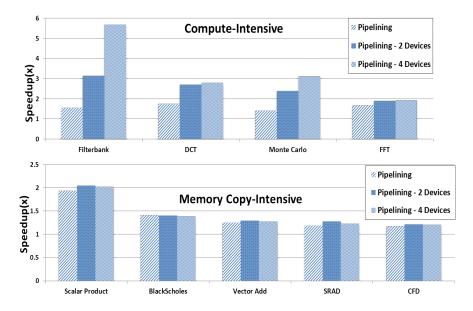

| 2.9  | Speedup over the Baseline OpenMPC Generated Codes (without pipelin-<br>ing) : Compute-intensive applications show good scalability with multiple<br>GPUs. Memory copy-intensive programs scale poorly with multiple GPUs<br>since PCIe bus forms a bottleneck. | 49   |

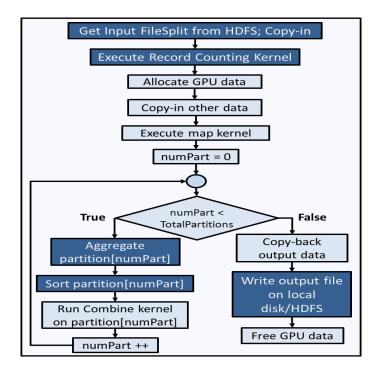

| 3.1  | Flowchart for the driver code on the host CPU : Dark boxes indicate functions provided by the runtime system                                                                                                                                                   | 75   |

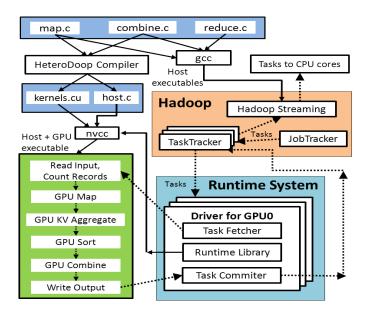

| 3.2  | Execution Scheme of HeteroDoop : Dashed arrows represent the execution flow; solid arrows represent the compilation flow                                                                                                                                       | 76   |

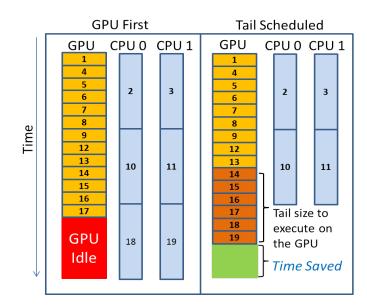

| 3.3  | Key Idea of Tail Scheduling                                                                                                                                                                                                                                    | 80   |

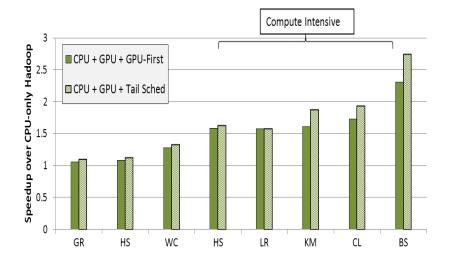

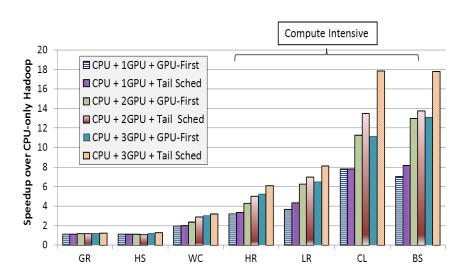

| 3.4  | Performance gains of HeteroDoop normalized to CPU-only Hadoop on<br>Cluster1                                                                                                                                                                                   | 86   |

| 3.5  | Performance gains of HeteroDoop normalized to CPU-only Hadoop on<br>Cluster2                                                                                                                                                                                   | 87   |

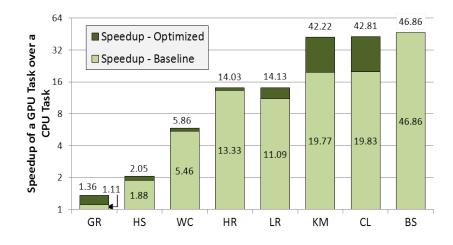

| 3.6  | Speedup of a single GPU task over a CPU task : Optimizations have high impact on three benchmarks                                                                                                                                                              | 89   |

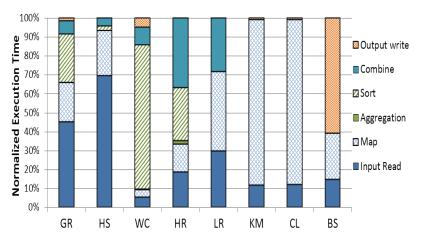

| 3.7  | Execution time breakdown of a GPU task                                                                                                                                                                                                                         | 89   |

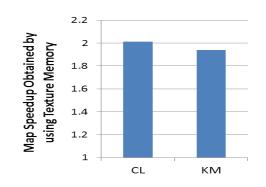

| 3.8  | Effects of using Texture Memory                                                                                                                                                                                                                                | 89   |

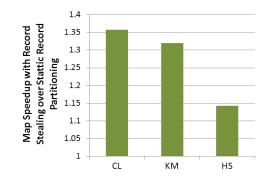

| 3.9  | Effects of Record Stealing on map kernels                                                                                                                                                                                                                      | 90   |

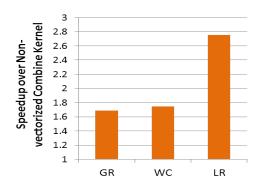

| 3.10 | Effects of Vectorized Read-Write on combine kernels                                                                                                                                                                                                            | 90   |

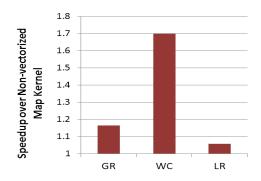

| 3.11 | Effects of Vectorized Read-Write on map kernels                                                                                                                                                                                                                | 91   |

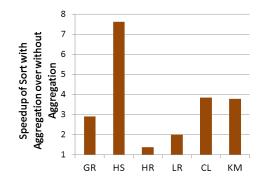

| 3.12 | Effects of KV Pair Aggregation on sort kernels                                                                                                                                                                                                                 | 91   |

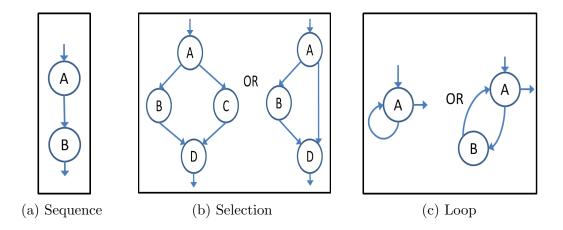

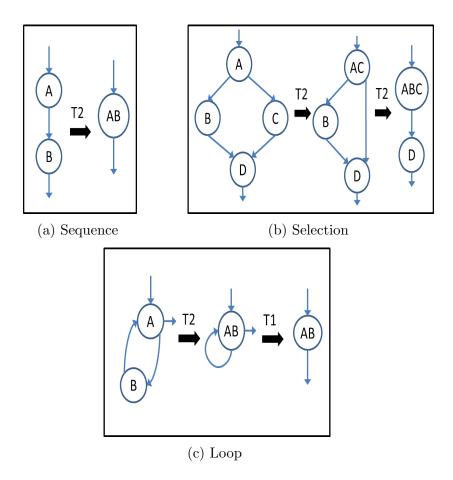

| 4.1  | Base Structured Patterns                                                                                                                                                                                                                                       | 97   |

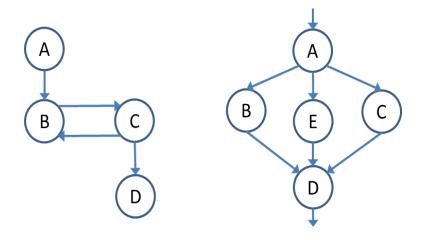

| 4.2  | Are these CFGs structured? The base patterns in Fig. 4.1 fail to answer.                                                                                                                                                                                       | 98   |

| 4.3  | Example of an irreducible CFG                                                                                                                                                                                                                                  | 103  |

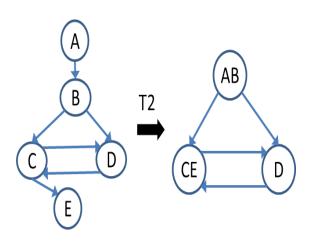

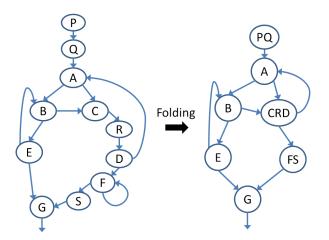

| 4.4  | Maximal folding                                                                                                                                                                                                                                                | 105  |

| 4.5  | Reducibility of base patterns                                                                                                                                                                                                                                  | 108  |

| 4.6  | Combinations of PR-PDC pairs for the maximally folded CFG in Fig. 4.4                                                                                                                                                                                          | 110  |

# Figure

| lre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

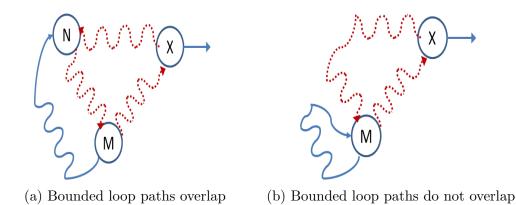

| Bounded loop path $(\vec{P})$ has a bounded loop condition node (M) : $\vec{P}$ is represented by dotted lines                                                                                                                                                                                                                                                                                                                                                                                                                  | 112                         |

| Bounded loop path $(\vec{P})$ has no condition nodes : $\vec{P}$ is represented by dotted lines                                                                                                                                                                                                                                                                                                                                                                                                                                 | 113                         |

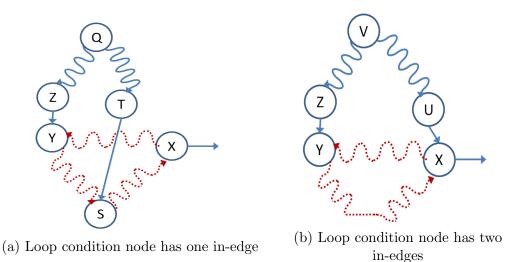

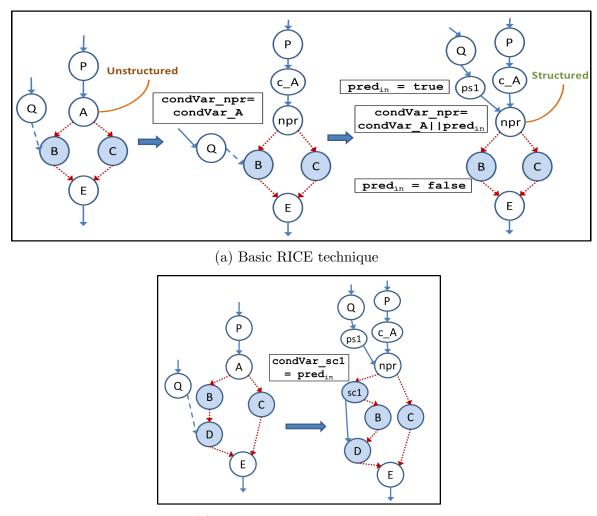

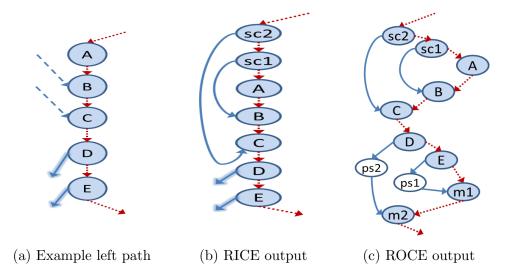

| RICE Transformation: Dotted edges and darkened nodes belong to left-/right paths. Dashed edge is an ICE                                                                                                                                                                                                                                                                                                                                                                                                                         | 115                         |

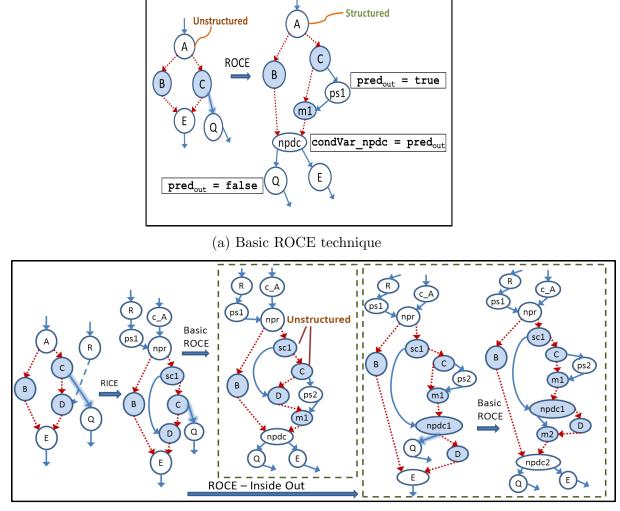

| ROCE Transformation: Dotted edges and darkened nodes belong to left-/right paths. Dashed edge is an ICE, shadowed edge is an OCE. Nodes named sc* are <i>short-channel</i> nodes, m* are <i>merge</i> nodes, and ps* are <i>predSetter</i> nodes                                                                                                                                                                                                                                                                                | 119                         |

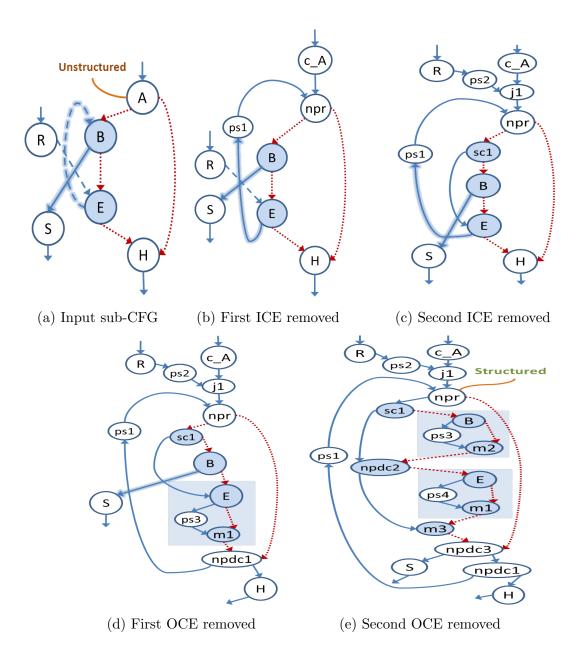

| Example of RICE and ROCE transformations: $A-H$ is the PR-PDC pair.<br>Dashed edges are ICEs, shadowed edges are OCEs. Dotted edges and<br>darkened nodes belong to the left/right paths. Nodes named j* are join<br>nodes, sc* are <i>short-channel</i> nodes, m* are <i>merge</i> nodes, and ps* are<br><i>predSetter</i> nodes. Shaded boxes indicate structured regions. After RICE<br>and ROCE, the region between the first and last edges of the left path<br>become SESE, making <i>npr</i> a structured condition node | 121                         |

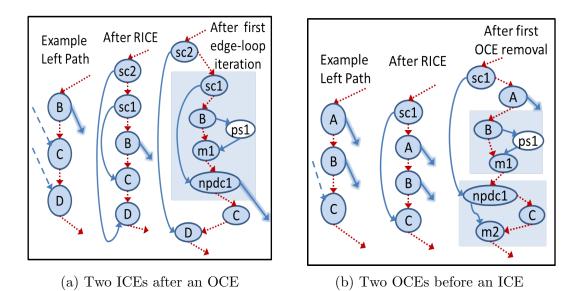

| Ensuring structuredness of all condition nodes on the left path when there is no crossing, i.,e., no OCE source is followed by an ICE sink: Dashed edges are ICEs, shadowed edges are OCEs. Dotted edges and darkened nodes belong to the left path. Nodes named sc* are <i>short-channel</i> nodes, m* are <i>merge</i> nodes, and ps* are <i>predSetter</i> nodes.                                                                                                                                                            | 127                         |

| Ensuring structuredness of all condition nodes on the left path when there is crossing, i.e., one or more OCE sources are followed by one or more ICE sinks: Dashed edges are ICEs, shadowed edges are OCEs. Dotted edges and darkened nodes belong to the left path. Nodes named sc* are <i>short-channel</i> nodes, m* are <i>merge</i> nodes, and ps* are <i>predSetter</i> nodes. Shaded boxes indicate structured regions.                                                                                                 | 128                         |

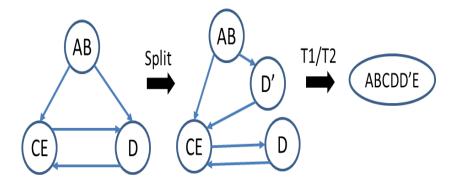

| Node Splitting: D' is a copy of D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 136                         |

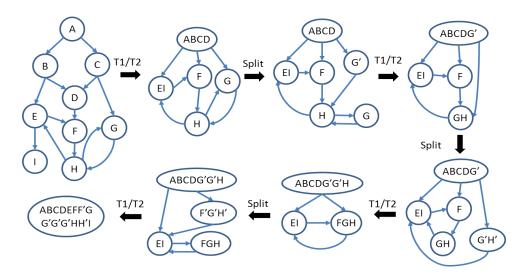

| Blowup caused by Node Splitting: Four copies of G, two copies each of F and H                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 136                         |

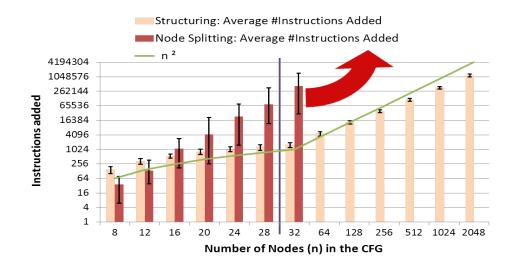

| of the X-axis to a logarithmic scale. Node Splitting generated CFGs are much larger. The size of 32-node CFGs after Node Splitting can be larger than the size of 1024-node structured CFGs. Node Splitting did not finish                                                                                                                                                                                                                                                                                                      | 140                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 143                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | represented by dotted lines |

| Figu | re                                                                                                                                                                                                  | Page |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

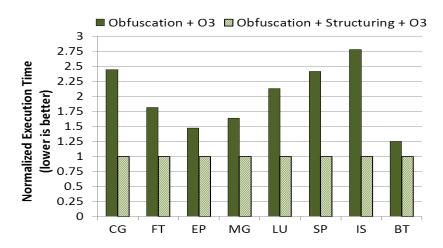

| 4.18 | Measuring analyzability of obfuscated CFGs achieved by structuring: The structured versions run significantly faster (1.92x geometric mean) compared to the unstructured (irreducible) counterparts | 144  |

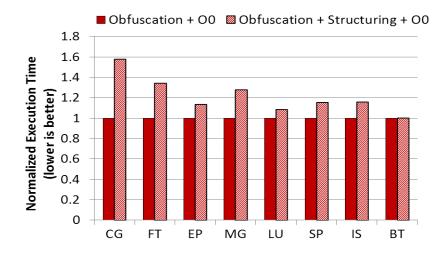

| 4.19 | Measuring overheads introduced by structuring: Structuring causes an overhead of 20% (geometric mean).                                                                                              | 145  |

#### ABSTRACT

Sabne, Amit J. PhD, Purdue University, August 2016. Programming Models, Compilers, and Runtime Systems for Accelerator Computing. Major Professor: Rudolf Eigenmann.

The last decade has seen a growing trend in the use of accelerators for highperformance computing. Accelerators are computationally powerful, massively parallel co-processors. Examples of accelerators include NVIDIA CUDA GPUs [1], AMD GCN GPUs [2], Intel Xeon Phi [3] (Many Core Processors), and Cell Broadband Engine [4]. Accelerators gain most of their performance through massive parallelism. A key challenge hindering the widespread use of accelerators is their programmability. The architectural complexity of these accelerators necessitates explicitly parallel programming models and creates a multitude of tuning avenues that must be explored to obtain high performance. This thesis proposal offers improved programming models, compilation techniques, and runtime systems to make accelerator programming easy, while bettering/retaining the performance.

In this abstract, we first briefly describe some of these accelerator architectures. Due to the massive parallelism, accelerators typically rely on explicitly parallel programming models, which we describe next. Lastly, the abstract provides an overview of open issues in accelerator programming, and the contributions made by this thesis to address them.

#### Accelerator Architectures

Graphical Processing Units (GPUs) were the first accelerator architectures to have received widespread attention. The advances in GPU technologies led to their instruction set to resemble the ones of CPUs, creating an opportunity for generalpurpose computations on GPUs [5]. A primary motivation for using GPUs for generalpurpose computation was the massive parallelism imbibed in them. GPUs work in an SIMD fashion, where thousands of threads can co-exist on the chip. GPU architectures comprise many light-weight cores, which are computationally much less powerful than the CPU cores. However, due to a large number of such cores, the achievable throughput was much higher than the CPU.

This throughput-oriented paradigm also gave birth to other accelerator architectures, such as Cell Broadband Engine and Intel Xeon Phi processors. These architectures were immediately adopted by the high-performance computing community and many supercomputers started to gain a high percentage of their computational power through the accelerators.

Typical high-performing accelerators are connected as coprocessors to the host CPU in the system, through a PCIe bus. The main memory of the accelerator is separate from the CPU. Further, the accelerator architectures possess specialized memory spaces that can be used to boost the program performance.

#### **Programming Accelerator Architectures**

The architectural distinctions of accelerators necessitate specialized programming models. First, to utilize the massive parallelism, explicitly parallel programming models, such as CUDA [1] and OpenCL [6] are necessary. In order to obtain acceleration, the programmer must identify the compute-intensive, parallel code regions and offload them on to the accelerator as *kernels*. Secondly, since accelerators have discrete memories, input data must be copied from the CPU memory into the accelerator, and vice-versa for the output data. These data transfers need to be handled by the programmer. Both CUDA and OpenCL offer necessary APIs for data transfers. Recently, there have been attempts to unify the CPU-accelerator memory spaces. Although such mechanisms improve accelerator programmability, they suffer on the performance, owing to page-level data handling. For HPC uses, programmers still manually perform the data transfers. Lastly, these architectures have unique memory hierarchies. CUDA, which is specific to NVIDIA GPUs, provides explicit functionalities to utilize on-chip memories, such as shared, texture and constant memories. It also offers architecture- specific functions for using vector units, performing warpoperations etc.

Despite the availability of CUDA and OpenCL, programming accelerator architectures remains difficult and error prone, owing to the complexity of these models. Programmers need to rewrite their applications to make use of the accelerators. To obtain better programmability, researchers created more user-friendly, high-level programming models, such as OpenMPC [7] and hiCUDA [8]. The former offers an OpenMP to CUDA translation system with additional, CUDA-specific directives added to OpenMP. The latter presents directives to be placed on a serial program, and a compiler that translates the annotated program into a CUDA program. Such high-level programming models have now been standardized. OpenACC [9] is the first such OpenMP-like programming standard for accelerators. Commercial compilers [10–12] are presently available for OpenACC. Recently published OpenMP 4.0 [13] extends the OpenMP standard to accelerators.

#### Thesis Contributions

While the high-level programming models offer better programmability, programmers still face several issues. We highlight such open issues below, and briefly summarize our contributions to address them.

• **Program tuning** : Several factors affect the program performance in accelerator programs. These factors include compiler optimizations (e.g. parallel loop interchange, data transfer reduction) and user specifications (e.g. number of threads to use, CPU-accelerator synchronization) [14–16]. Due to the presence of a large number of these factors, achieving the best performance requires tuning, which may be performed by an automatic tuning system, or manually by the programmer. In Chapter 1, we evaluate the effects of compiler

optimizations on OpenMP to CUDA translation. This work is built on top of the OpenMPC [7] system, which comprises an auto-translator from OpenMP to CUDA. OpenMPC offers many compiler optimizations and an auto-tuning system for the same. This auto-tuner performs a pruned-exhaustive search among the possible program configurations. Chapter 1 will present a more advanced tuning approach that reduces the search time-complexity to a polynomial time, and finds better program configurations than the pruned-exhaustive search approach. With this new tuning method, we analyze the performance effects of each compiler optimization.

- Limited accelerator memory sizes : Accelerators typically use nonvirtualized memories. Therefore, the programmer must ensure that the data size used by the problem fits inside the main memory. Otherwise, the programmer must carry out manual computation blocking so that the data fits within the accelerator memory. The available automatic solutions, such as zero-copy memory, or unified virtual memory [1], require excessive CPU-GPU communication while the kernel is in flight, lowering the performance. Chapter 2 addresses this issue of limited memory spaces on accelerators. It presents a novel compiler technique, called *Computation Splitting* or *COSP* [17] that automatically splits the computation so as to make the problem fit in the accelerator memory, without lowering the performance.

- Multi-GPU scaling : Many supercomputers comprise of nodes containing multiple GPUs. The previous solutions to exploit all GPUs of a node required manual computation partitioning [18, 19]. There existed one automatic approach that provides a single device image for all GPUs [20]. However, the computation size in such an approach is restricted by the combined memory of all the GPUs. The COSP technique in Chapter 2 generates data-independent subproblems. The chapter describes how these subproblems can be mapped to multiple GPUs attached to a node, overcoming the memory size barrier.

- Computation-communication overlap : As the input data must be copied in the accelerator memory before the computation, and the output data must be copied out from the accelerator memory to the CPU memory, an opportunity arises to overlap this communication with the kernel computations. Programmers must manually obtain this overlapping behaviour. Chapter 2 will present an automatic mechanism to perform such pipelining and a runtime tuning mechanism to obtain a high performing pipeline stage size. This is in contrast to previous approaches [21–24] where pipelining was exploited on the GPU to hide device memory latency by copying data into the on-chip programmer-managed cache first.

- Accelerator clusters : MapReduce is a popular programming framework for distributed computing. However, when it comes to accelerator clusters, available systems either use CPUs [25–28], or GPUs [29–31]. Since CPUs perform better on IO-intensive applications, while GPUs perform better on the compute-intensive ones, a need of a framework that uses both CPUs and GPUs arises to cater to all possible workloads. Chapter 3 will present HeteroDoop, a MapReduce programming system that exploits both CPUs and GPUs in a cluster. HeteroDoop [32] programs require simpler modifications to already available CPU-only MapReduce programs, unlike other GPU-MapReduce frameworks that require explicit parallelization or custom APIs [30, 33, 34].

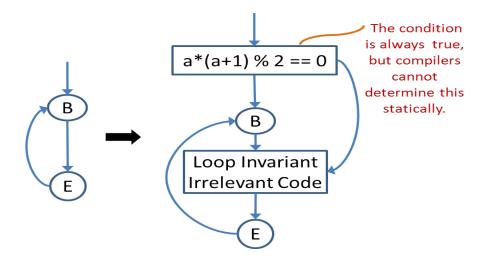

- Control flow divergence : The SIMD execution model employed by accelerators mandates the set of threads/lanes in the SIMD to execute the same instruction. If the threads encounter a branch wherein some threads take the **if** while others take the **else** path, then the execution of these two divergent outcomes gets serialized. The lockstep execution can only resume once the immediate post-dominator (IPDOM) of the divergent branch is reached. Such divergence can worsen the program performance under the presence of "unstructured" control flow [35]. Unfortunately, there is little formalization

available on what unstructured control flow means. Chapter 4 will formalize the notion of structured control flow graphs. The chapter will also present an unstructured-to-structured conversion algorithm which eliminates the exponential code expansion possible in previous approaches [36–40]. Our control flow structuring approach improves divergent code execution on SIMD units, to which no software solution was previously available [35].

# 1. EFFECTS OF COMPILER OPTIMIZATIONS IN OPENMP TO CUDA TRANSLATION

#### 1.1 Introduction

OpenMP is an established standard in parallel programming and is of particular interest for today's and future multicores. There is a large and growing code base, the standard is widely understood and is well documented, and there exists a multitude of compilers and supporting tools. These features are of paramount importance to the programmer. They help reduce the difficulty and the cost of developing parallel software significantly.

The number of new parallel languages that have been proposed in even just the past two decades is massive. The question of cost versus benefit arises with every such proposal. Unfortunately, few quantitative analyses are available that would allow one to find out if the same objective could have been achieved with an existing language standard and what are costs and benefits of new versus old, in terms of performance and productivity. Obviously, any new language will start from zero in building a code base, compilers, tools, and programming experience.

A new language development has emerged in the context of new graphics processing units, or accelerators. These devices offer promising avenues towards low-energy, highly parallel computation for a class of parallel applications. Among the proposed programming models are CUDA and OpenCL, both of which allow the programmer to access architecture-specific features. These architecture-specific interfaces, however, significantly depart from the parallel programming semantics offered by standards, such as OpenMP. The cost/benefit question arises anew.

Previous work has addressed this cost/benefit question [41]. This work provided quantitative comparisons of hand-written CUDA programs versus equivalent programs written in OpenMP and translated to CUDA. Using an automatic translator and tuning system, called OpenMPC, we were able to achieve performance results that came close to hand-coded CUDA on a large set of benchmarks. The contribution of the present chapter is to address three open issues of that work.

- The previous work provided overall performance numbers. The breakdown into individual techniques was not yet available. In this chapter, we quantify the contributions of each individual technique. Of particular interest in this analysis is also the importance of CUDA-specific OpenMP extensions, which are generated automatically in the OpenMPC system.

- A key component of the OpenMPC is its tuning system, which empirically searches through a large space of optimization variants and tries to find the best. The initial OpenMPC system used an inefficient exhaustive search mechanism. In this work, we use an improved *Iterative Elimination (IE)* [42] based tuning system that significantly reduces the tuning time.

- A problem faced by all empirical tuning systems is the variability of execution times, even for the same program executed repeatedly on the same platform in single-user setup. This effect makes it difficult to correctly measure the impact of an optimization technique. A common approach is to average over multiple runs, increasing tuning time. We have developed a new method that identifies optimizations that are vulnerable to runtime variations and uses increased measuring time only for those.

The remainder of the chapter is organized as follows. Section 1.2 describes Open-MPC and its available optimization options. It also identifies opportunities for improvement in the present OpenMPC tuning system. Section 1.3 explains our tuning mechanism for finding the best tuning options. Individual performance analysis is shown in Section 1.4. Section 4.9 presents the takeaways from this chapter.

Figure 1.1.: OpenMPC workflow

#### 1.2 Overview of OpenMPC System

OpenMPC [41] is a programming framework that generates CUDA programs from OpenMP programs. The framework includes an extended OpenMP programming interface, a source-to-source translator, and an automatic tuning system. The programming interface extends OpenMP with a new set of directives and environment variables (henceforth referred to as CUDA extensions<sup>1</sup>) for controlling CUDA-related parameters and optimizations. OpenMP translates standard OpenMP programs by applying a set of program transformations and by inserting CUDA extensions. Open-MPC includes an empirical tuning system that automatically generates, prunes, and searches the optimization space and determines the best combination of optimizations. Fig. 1.1 shows the workflow of the OpenMPC translator. Fig. 1.2 displays a small example of the OpenMPC translated CUDA code for Jacobi benchmark.

#### **1.2.1** Optimization options

There are 18 optimization options available in OpenMPC, grouped into 4 categories: (1) Program environment configuration, (2) Data caching strategy, (3) Data offloading optimizations, and (4) Code transformation. Table 1.1 shows all optimiza-

<sup>&</sup>lt;sup>1</sup>Our CUDA extensions are not meant to be a proposal for extending the OpenMP standard. They represent a research framework for exploring questions such as those addressed in this chapter.

Listing 1.1: Source code in OpenMP

Listing 1.2: Resulting CUDA kernel from OpenMPC translation

```

_global___ void kernel(...){

1

\mathbf{2}

3

int _bid = (blockIdx.x+(blockIdx.y*gridDim.x));

int _gtid = (threadIdx.x+(_bid*blockDim.x));

4

5

tid = (\_gtid+1);

6

7

if (tid<=SIZE) {</pre>

8

for (i=1; i<=SIZE; i ++ ) {</pre>

9

a[i][j] = (b[i-1][tid] + b[i+1][tid] +

10

b[i][tid-1] + b[i][tid+1] )/4.0F;

11

}

12

}

13 }

```

Figure 1.2.: OpenMPC translation example

tion options in OpenMPC that are considered for individual optimization analysis. The first three groups are supported by our CUDA extensions. The fourth group is applied through source-to-source transformation in the OpenMPC compiler.

#### 1.2.2 Improving the OpenMPC Tuning System

To analyze the effects of individual tuning options, we make use of the OpenMPC system, which allows us to implement the method in [43]: Using the highest-optimized program variant as a baseline, this method iteratively switches off one optimization at a time, to measure its effect in terms of the slowdown incurred. To this end, we have identified a number of open issues in OpenMPC, which we address in the present work.

#### Advanced Optimization Space Navigation:

The goal of an empirical tuning system is to generate a set of optimizations that yield best performance. In OpenMPC, 18 optimizations are available as compiler flags. Finding the best combination from these flags is non-trivial, because each optimization can improve or worsen the performance of a program, depending upon its characteristic and depending on other present optimizations.

The initial OpenMPC system uses simple exhaustive search to navigate the space of optimization variants. This space can be very large (for n on-off optimization options, the size is  $2^n$ ). OpenMPC reduces this space using aggressive tuning heuristics, which we refer to as pruned exponential search (PE). PE does the program analysis to prune the tuning space by removing the inapplicable or non-beneficial tuning options for the particular program. It then runs exhaustive search over the remaining tuning options. However, two issues remain: The resulting search space can still be large (which was acceptable for obtaining the original research results [41], but can be too

| Program Environment Configuration |                                                |

|-----------------------------------|------------------------------------------------|

| Compiler Flags                    | Description                                    |

| cudaThreadBlockSize=N             | Set the default CUDA thread block size         |

| assumeNonZeroTripLoops            | Assume that all loops have non-zero iterations |

## Table 1.1.: Optimization options in OpenMPC

# Data Caching Strategy

| Compiler Flags           | Description                                          |

|--------------------------|------------------------------------------------------|

| shrdSclrCachingOnReg     | Cache shared scalar variables onto GPU register      |

| shrdArryElmtCachingOnReg | Cache shared array elements onto GPU register        |

| shrdSclrCachingOnSM      | Cache shared scalar variables onto GPU shared mem-   |

|                          | ory                                                  |

| prvtArryCachingOnSM      | Cache private array variables onto GPU shared mem-   |

|                          | ory                                                  |

| shrdArryCachingOnTM      | Cache 1-dimensional, R/O shared array variables onto |

|                          | GPU texture memory                                   |

| shrdSclrCachingOnConst   | Cache R/O shared scalar variables onto GPU constant  |

|                          | memory                                               |

| shrdArryCachingOnConst   | Cache R/O shared array variables onto GPU constant   |

|                          | memory                                               |

### Data Offloading Optimization

| Compiler Flags       | Description                                              |  |

|----------------------|----------------------------------------------------------|--|

| useMallocPitch       | Use cudaMallocPitch() for 2-dimensional arrays           |  |

| useGlobalGMalloc     | Allocate GPU variables as global variables               |  |

|                      | which provides more scope for reducing memory transfers  |  |

| globalGMallocOpt     | Apply CUDA malloc optimization for globally allocated    |  |

|                      | GPU variables                                            |  |

| cudaMallocOptLevel=N | Set CUDA malloc optimization level for locally allocated |  |

|                      | GPU variables                                            |  |

| cudaMemTrOptLevel=N  | Set CUDA CPU-GPU memory transfer optimization level      |  |

# Code Transformation

| Compiler Flags          | Description                                      |

|-------------------------|--------------------------------------------------|

| localRedVarConf=N       | Configure how local reduction variables are gen- |

|                         | erated for array-type variables                  |

| useMatrixTranspose      | Apply Matrix Transpose optimization              |

| useParallelLoopSwap     | Apply Parallel Loop Swap optimization            |

| useUnrollingOnReduction | Apply Loop Unrolling for in-block reduction      |

| Benchmark      | Relative Standard Deviation  | Relative Standard Deviation | Ratio |

|----------------|------------------------------|-----------------------------|-------|

|                | for Memory Transfer Time (A) | for Computation Time (B)    | (A/B) |

| NW (8192)      | 0.2395                       | 0.0128                      | 18.71 |

| Jacobi (12288) | 0.7394                       | 0.0001                      | 7394  |

| CG (W)         | 0.2562                       | 0.0706                      | 3.63  |

| FT(W)          | 0.1521                       | 0.0112                      | 13.58 |

Table 1.2.: Variations on GPU Programs

long for end users). In addition, sometimes the aggressive pruning heuristics may eliminate the best optimization combination.

#### Runtime Variations – A Key Problem of Auto-Tuning Systems:

In computer systems, unpredictable system variations during program execution are usual. They arise due to OS overheads, other running processes, or underlying hardware operations. Although these variations do not affect the correctness of the program, they can impact its execution time. We define this type of variation as *runtime variation*. Although runtime variation does not disrupt program execution, in auto-tuning system, runtime variation can be problematic. Since the auto-tuning systems improves the program based on execution time, the variation can cause some beneficial optimizations to be removed from the tuning result and vice versa.

One of the significant observations made during our study was the fact that most of the variations on GPU programs are due to the variations in memory transfer times. Since GPU and CPU do not share a common address space, memory transfers form an essential part of GPU programs. GPUs are generally connected to the CPU using a PCIe bus, thereby leading to a variability in the memory transfer times. Table 1.2 compares the relative standard deviation in computation time and the memory transfer time. Relative standard deviation is a percentage of the ratio of standard deviation to the mean of the sample. It acts as an indicator as of how the variations relate to the average. From Table 1.2, we can see that the relative standard deviations in memory transfer can be as much as 7000 times the relative standard deviations in computation time.

To alleviate runtime variations, one can average execution times across multiple runs. However, multiple executions can increase the tuning time significantly. The PE algorithm does not take runtime variations into consideration, and therefore is more prone to erroneous final option combinations on GPU programs.

#### **Objectives of this Work:**

Our goal is to determine the impact of individual optimization techniques in the OpenMP to CUDA translator. To this end, we use the improved OpenMPC translation and tuning system, which can find the best combination of optimization techniques for each program. In doing so, it also reports the performance difference made by individual optimizations. We proceed as follows.

- We modify a previously described *Iterative Elimination (IE)* [42] tuning algorithm to make it applicable to GPU programs.

- We describe a generic tuning methodology to deal with memory transfer time based variations of GPU applications.

- With the best tuning option combination generated by the above tuning system, we analyze the impact of each tuning option or compiler flag.

The next section presents the new tuning algorithm. Section 1.4 presents results obtained using this methodology.

#### **1.3** Modified IE (MIE) Algorithm for OpenMPC

To address the issues presented in Section 1.2.2, we propose a *Modified IE (MIE)* algorithm, which is a tuning algorithm based on *Iterative Elimination (IE)* [42]. In this section, we briefly describe IE and then present our MIE algorithm.

#### **1.3.1** Iterative Elimination

The IE algorithm is shown in Algorithm 1. IE begins by switching on all optimization options, and then iteratively measures their effect by switching off one tuning option at a time. Next, it removes the one with the most negative effect. The process repeats until all remaining optimizations show non-negative effects. The complexity of IE is  $O(n^2)$ , compared to  $O(2^n)$  of the *PE* algorithm.

| Algorithm 1: Iterative Elimination Algorithm                                           |  |  |

|----------------------------------------------------------------------------------------|--|--|

| <b>Input</b> : $n =$ Number of Tuning Options $(F_1, F_2, \dots, F_n)$                 |  |  |