### Purdue University Purdue e-Pubs

**Open Access Dissertations**

Theses and Dissertations

January 2016

# DESIGN, COMPACT MODELING AND CHARACTERIZATION OF NANOSCALE DEVICES

Yanfei Shen Purdue University

Follow this and additional works at: https://docs.lib.purdue.edu/open\_access\_dissertations

### **Recommended** Citation

Shen, Yanfei, "DESIGN, COMPACT MODELING AND CHARACTERIZATION OF NANOSCALE DEVICES" (2016). *Open Access Dissertations*. 1373. https://docs.lib.purdue.edu/open\_access\_dissertations/1373

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

### PURDUE UNIVERSITY GRADUATE SCHOOL Thesis/Dissertation Acceptance

This is to certify that the thesis/dissertation prepared

### By YANFEI SHEN

Entitled DESIGN, COMPACT MODELING AND CHARACTERIZATION OF NANOSCALE DEVICES

For the degree of Doctor of Philosophy

Is approved by the final examining committee:

SAEED MOHAMMADI

Co-chair

CHEN YANG

Co-chair

LUIS M. KRUCZENSKI

KENNETH P. RITCHIE

To the best of my knowledge and as understood by the student in the Thesis/Dissertation Agreement, Publication Delay, and Certification Disclaimer (Graduate School Form 32), this thesis/dissertation adheres to the provisions of Purdue University's "Policy of Integrity in Research" and the use of copyright material.

Approved by Major Professor(s): <u>SAEED MOHAMMADI</u>

Approved by: \_\_\_\_\_ FINLEY

11/29/2016

Head of the Departmental Graduate Program

# DESIGN, COMPACT MODELING AND CHARACTERIZATION OF

### NANOSCALE DEVICES

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Yanfei Shen

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

December 2016

Purdue University

West Lafayette, Indiana

#### ACKNOWLEDGEMENTS

First of all, I would like to thank my advisor, Professor Saeed Mohammadi, for his guidance during my research work. During my years at Purdue, he has offered my many valuable suggestions and ideas, without which this thesis would not have been possible.

I would also like to thank my committee members Professor Chen Yang, Professor Martin Krucszenski, and Professor Kenneth Ritchie for their time and sitting on my committee, Professor Gabor Csathy for sitting on my preliminary exam committee.

This thesis would not have been possible without the help and support from my colleagues and friends. I would like to express my special thanks to Noah Opondo, Hossein Pajouhi, Scott Calvert, Jie Cui, Shabnam Ghotbi for their help and advice. I would like to appreciate my friends for their support and feedback, Sultan Helmi, Yingheng Tang, Hengying Shan and many others.

Finally, I would like to thank my family. Special gratitude to my parents for their encouragement and continuous support. I would also like to express my appreciation to my brother, his wife and their son, Yuhang for their support during these years.

### TABLE OF CONTENTS

|                                                        | Page   |

|--------------------------------------------------------|--------|

| LIST OF TABLES                                         | vi     |

| LIST OF FIGURES                                        | vii    |

| LIST OF ABBREVIATIONS                                  | xiii   |

| ABSTRACT                                               | XV     |

| CHAPTER 1. INTRODUCTION                                | 1      |

| 1.1 Introduction                                       | 1      |

| 1.2 Compact Modeling of 45nm CMOS SOI Transistors      | 4      |

| 1.3 Cold Cathode Technology                            | 9      |

| 1.4 Nano-Electro-Mechanical (NEM) Systems              |        |

| CHAPTER 2. COMPACT MODELING OF 45NM CMOS SOI TRANSISTO | ORS 14 |

| 2.1 Introduction                                       | 14     |

| 2.2 Virtual Source (VS) Based DC Modeling              |        |

| 2.3 Nonlinear RF Modeling                              |        |

| 2.3.1 Equivalent Circuit Based RF Model                |        |

| 2.3.2 Extrinsic Parameter Extraction                   |        |

| 2.3.3 Intrinsic Parameter Extraction                   |        |

| 2.3.4 S-parameter Simulation                           |        |

| 2.4 Noise Behavior of nm-Scale Transistors             |        |

| 2.5 Model Validation                                   |        |

| 2.6 Conclusion                                         |        |

| CHAPTER 3. COLD CATHODE TECHNOLOGY                     |        |

| 3.1 Introduction                                       |        |

| 3.2 Physics                                            |        |

|                                                           | Page |

|-----------------------------------------------------------|------|

| 3.3 Failure Mechanisms                                    | 55   |

| 3.3.1 Thermal Stability                                   | 55   |

| 3.3.2 Ion Bombardment                                     | 58   |

| 3.4 Silicon Nanowire Field Emitter Arrays                 | 59   |

| 3.4.1 Simulation                                          | 59   |

| 3.4.2 Design and Fabrication                              | 61   |

| 3.4.3 Device Characterization                             | 65   |

| 3.5 Conclusion                                            | 70   |

| CHAPTER 4. NANO-ELECTRO-MECHANICAL SYSTEMS                | 72   |

| 4.1 Introduction                                          | 72   |

| 4.2 CMOS NEMS Resonator Characterization                  | 72   |

| 4.2.1 Metal Grid Plate NEMS Resonator                     | 72   |

| 4.2.2 H-shape Resonator                                   | 74   |

| 4.3 Compact Modeling of Double-Clamped Silicon Resonators | 76   |

| 4.3.1 Experimentation and Characterization                | 76   |

| 4.3.2 Mechanical Equation of Motion                       | 77   |

| 4.3.3 Forcing Model                                       | 77   |

| 4.3.4 Capacitance Modulation                              | 78   |

| 4.3.5 Piezoresistive Effect                               | 78   |

| 4.3.6 Equivalent Circuit Representation                   | 80   |

| 4.3.7 Simulation                                          | 81   |

| 4.3.7.1 Single-tone excitation                            | 82   |

| 4.3.7.2 Multi tone simulation                             | 82   |

| 4.4 Conclusion                                            | 83   |

| CHAPTER 5. FUTURE WORK                                    | 85   |

| 5.1 Process Design Kit (PDK)                              | 85   |

| 5.2 High Frequency Nano-Vacuum Tube Devices               | 86   |

| 5.3 Future Nano-Electromechanical Sensing Systems         | 88   |

| LIST OF REFERENCES                                        | 91   |

|     | P | age  |

|-----|---|------|

| VIT | A | . 98 |

### LIST OF TABLES

| Table                                                                        | Page         |

|------------------------------------------------------------------------------|--------------|

| 2.1. Extracted VS Parameters                                                 |              |

| 2.2. Extracted extrinsic parameter values for different sizes of transistors |              |

| 3.1. A comparison among the old vacuum tube technology, the mod              | lern CMOS    |

| technology and the new proposed vacuum tube technology                       | 53           |

| 3.2. A comparison of field emission measurement results between the device   | in this work |

| with other published works.                                                  | 68           |

| 4.1. Coefficients – Dimensional Form [86]                                    | 79           |

### LIST OF FIGURES

| Figure Page                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------|

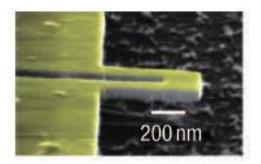

| 1.1. A single crystal SiC epilayer cantilever for mass sensor [1]                                                        |

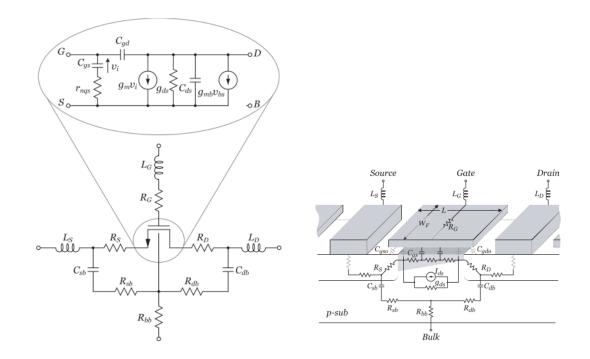

| 1.2. Equivalent circuit model of modern NMOS transistor [8]                                                              |

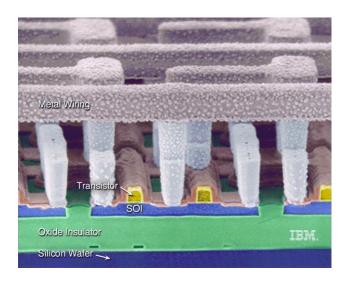

| 1.3. A SEM image from IBM of one finger of CMOS SOI transistor [20]7                                                     |

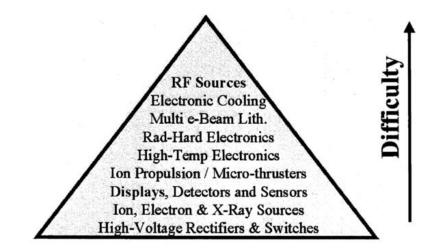

| 1.4. Difficulty level of various applications of field emitters[36] 10                                                   |

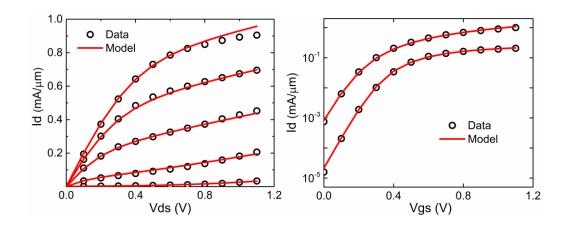

| 2.1. Accuracy of the developed VS model with self-heating effect (red curves) vs.                                        |

| measured DC data (open symbols) for two DC characteristics: (a) Drain current vs                                         |

| drain-source voltage ( $I_d$ - $V_{ds}$ characteristics), when gate-source voltage $V_{gs}$ varies                       |

| from 0.2 V to 1.0 V in steps of 0.2 V; (b) Drain current vs. gate-source voltage                                         |

| (transfer characteristics) when $V_{ds} = 0.1$ V (lower currents) and $V_{ds} = 1.1$ V (higher                           |

| currents))                                                                                                               |

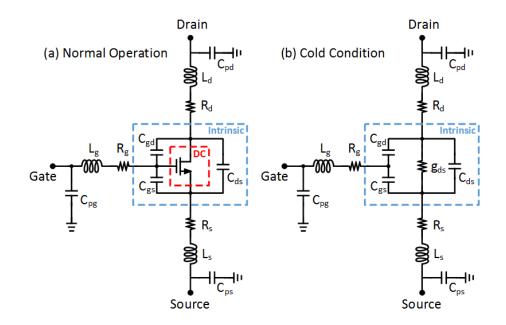

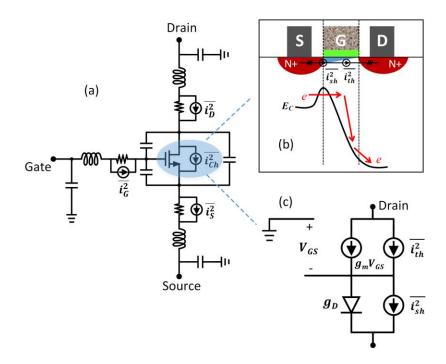

| 2.2. Nonlinear equivalent circuit model of NMOS transistors under (a) normal operation                                   |

| and (b) cold bias condition. The DC characteristics is given by VS model (inside the                                     |

| red box). Elements inside the blue box are denoted as intrinsic elements whereas                                         |

| those outside of the box are extrinsic elements                                                                          |

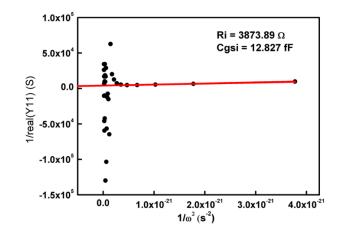

| 2.3. Linear fitting of $1/\text{real}(Y_{11})$ to $1/\omega^2$ at low frequency region to extract $R_i$ and $C_{gsi}$ 29 |

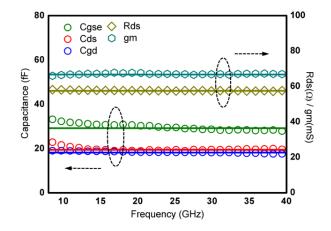

| 2.4. Frequency dependence of the extracted intrinsic elements, $C_{gse}$ , $C_{ds}$ , $C_{gd}$ , $R_{ds}$ , and $g_m$    |

| for a 42 $\mu$ m transistor biased at $V_{gs} = 0.9$ V, $V_{ds} = 0.9$ V                                                 |

- 2.6. Intrinsic capacitances as functions of transistor width at  $V_{gs} = 0.9$  V and  $V_{ds} = 0.9$  V. 30

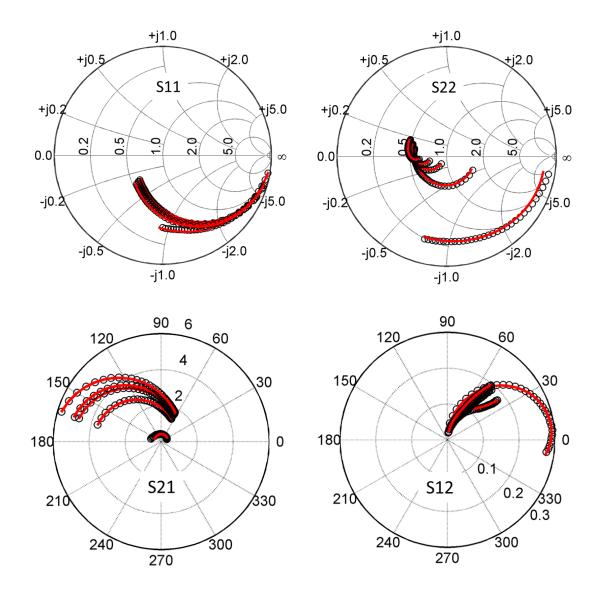

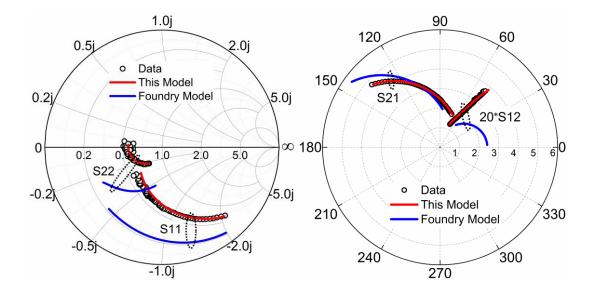

- 2.8. Comparisons of measured (open symbol) and simulated (solid line) S-parameters for different  $V_{ds}$  (0.0V, 0.3V, 0.6V, 0.9V, 1.2V) and  $V_{gs} = 1.2V$  for 84µm transistor.... 33

- 2.9. Comparisons of measured (open symbol) and simulated (solid line) S-Parameters for different  $V_{gs}$  (0.0V, 0.3V, 0.6V, 0.9V, 1.2V) and  $V_{ds}$  = 1.2V for 84µm transistor.... 34

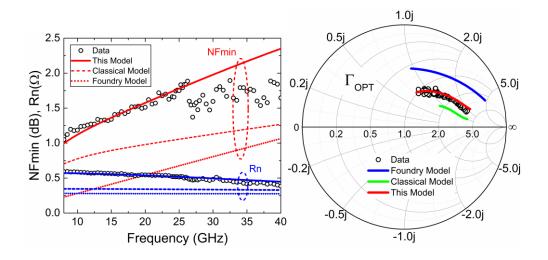

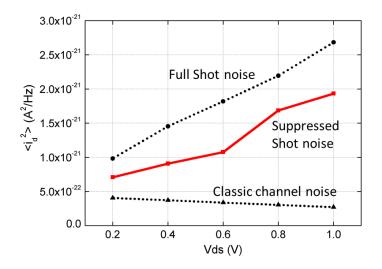

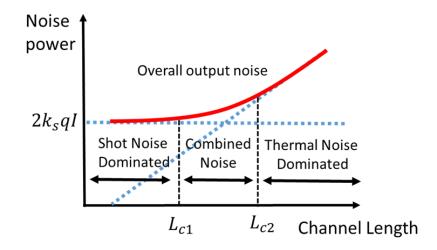

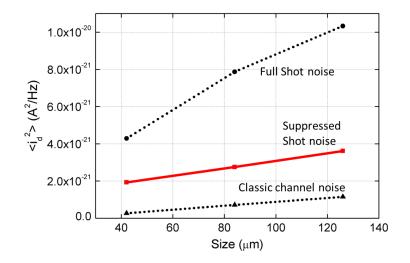

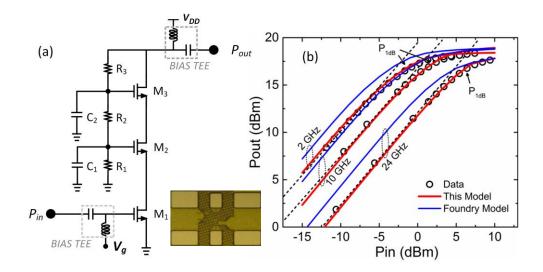

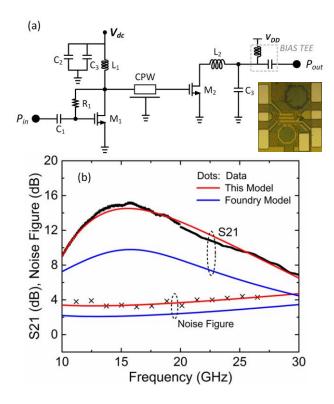

2.12. Measured (open symbols) and simulated (lines) noise parameters with three different noise models: (a)  $NF_{min}$  and  $R_n$  as functions of frequency and (b)  $\Gamma_{OPT}$ plotted on a Smith impedance chart for an NMOS transistor with a width of 84 µm at bias  $V_{gs} = 0.5$  V and  $V_{ds} = 1$  V. Note that, the mismatch in NF<sub>min</sub> at frequencies between 26 and 40 GHz is due to the measurement issues as it appears in all the 2.13. Comparisons of different channel noise models as a function of  $V_{ds}$ ,  $V_{gs}$  is kept at 2.14. Relation between shot noise, thermal noise with the overall output noise as a 2.15. Comparison of different channel noise models for transistors of different sizes, bias 2.16. (a) The circuit schematic of a triple-stack power amplifier cell. All transistors are 126 µm wide. (b) The comparison among measured and simulated output powers of the triple-stack power cell at three different frequencies: 2 GHz, 10 GHz, 24 GHz. 45 2.17. (a) The circuit schematic of a two-stage microwave LNA. The first stage uses a 126  $\mu$ m wide transistor while the second stage has an 84  $\mu$ m wide transistor. (b) The comparison between measured and simulated S21 and Noise Figure of the LNA (50  $\Omega$  source impedance) vs. frequency. Noise data was only available up to 26.5 GHz.

Page

| Figu | Page                                                                                  |

|------|---------------------------------------------------------------------------------------|

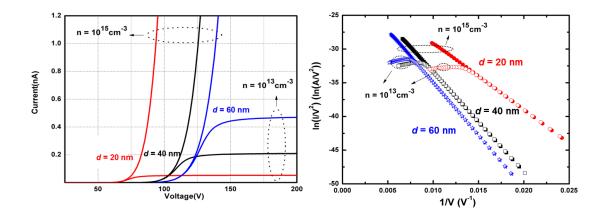

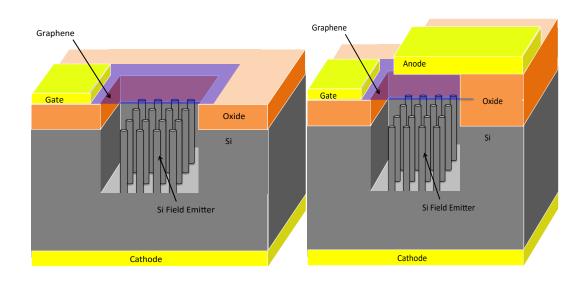

| 3.2. | The proposed silicon FEAs as a vacuum transistor                                      |

| 3.3. | (Left) Field emission characteristics of a single silicon nanowire with different     |

|      | diameters and doping densities demonstrating current regulation. (Right) the          |

|      | corresponding FN plot                                                                 |

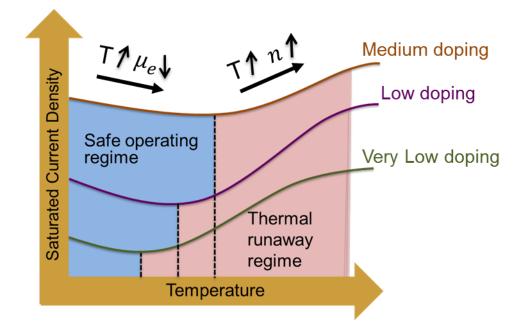

| 3.4  | FEAs saturated current density as a function of temperature for different doping      |

|      | levels. Safe Operating Area (SOA, blue region) is where the current density           |

|      | negatively depends on the temperature while Thermal runaway area is where current     |

|      | density positively depends on temperature                                             |

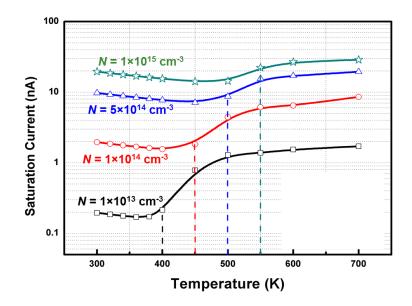

| 3.5. | Simulation result of saturation current as a function of temperature for different    |

|      | carrier concentrations                                                                |

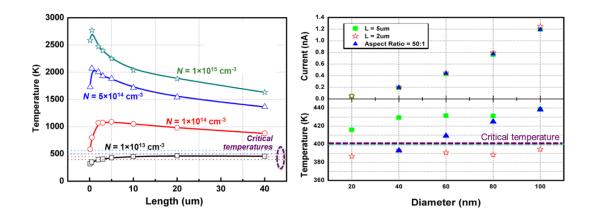

| 3.6. | (Left) Temperature as a result of operating silicon nanowire field emitters under     |

|      | saturation regime as a function of nanowire length. Dashed lines show the critical    |

|      | temperatures for different doping densities. (Right) Temperature (bottom) as a result |

|      | of operating silicon nanowire field emitters under saturation regime as a function of |

|      | diameter and the corresponding current single nanowire (top)                          |

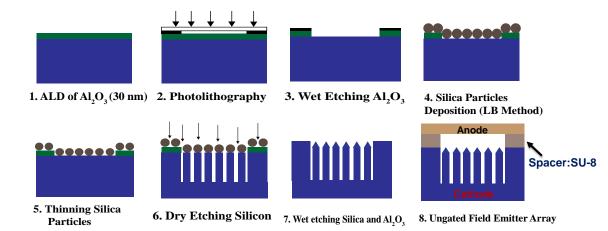

| 3.7. | The fabrication process of silicon FEAs                                               |

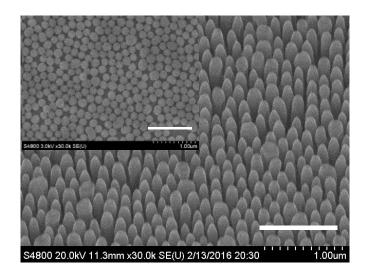

| 3.8. | An SEM image of the silicon FEA. The inset is an SEM image of silica particles        |

|      | deposited on top of silicon wafer by LB process. The white bars are 1µm in length.    |

|      |                                                                                       |

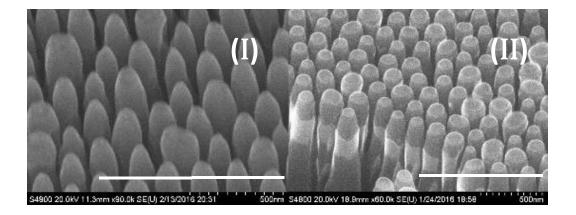

| 3.9. | Two SEM images of silicon FEA with different tip curvatures. Type (I) sample was      |

|      | achieved by using 30s thinning time of silica particles while Type (II) was thinned   |

|      | for 15s. The white bars are 1µm in length                                             |

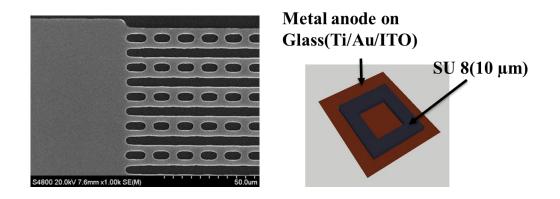

| 3.10. (Left) The fabricated Nickel/Aluminum pattern on top of wafer used as the gate in        |

|------------------------------------------------------------------------------------------------|

| three-terminal silicon FEAs. (Right) The metal anode of the three-terminal FEAs                |

| with a 10 $\mu$ m SU 8 acting as a spacer between the gate and anode                           |

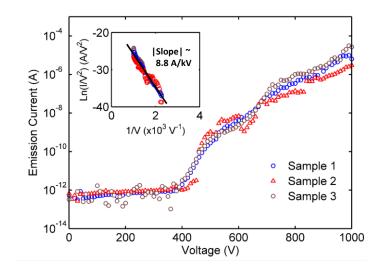

| 3.11. Measurement result of ungated two-terminal silicon FEA for different samples. The        |

| inset is the corresponding FN plot. The solid line is fit to the data. All three are Type      |

| (I) samples in Figure 3.967                                                                    |

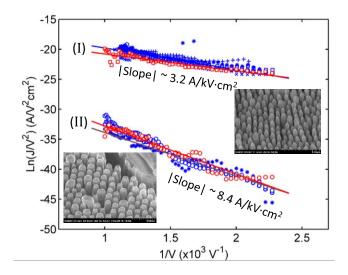

| 3.12. FN plots of various silicon FEAs. The solid lines are fit to the data. Type (I) and (II) |

| curves correspond to samples in Figure 3.9, respectively                                       |

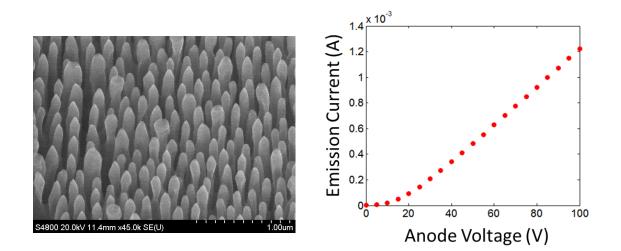

| 3.13. (Left) An SEM image of silicon FEAs with tips thinned further to 50 nm in                |

| diameter on average. (Right) The measured IV characteristics with a 10 $\mu m$ SU-8            |

| spacer showing an improved turn-on voltage of 20 V and a current density of 1.6                |

| A/cm <sup>2</sup> at 8 V/µm                                                                    |

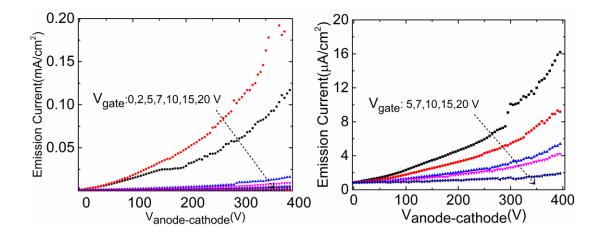

| 3.14. The measured IV characteristics of the gated three-terminal FEAs. The right figure       |

| is a zoom-in of the left figure with gate voltages of 0 V and 2 V omitted69                    |

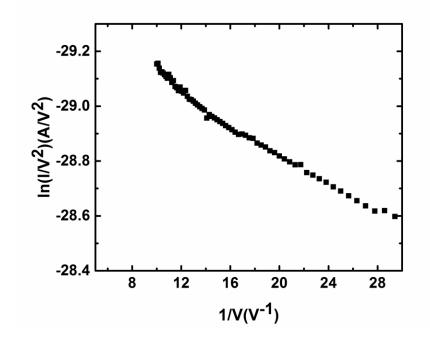

| 3.15. FN plot of the measured IV characteristics of the gated three-terminal FEAs 70           |

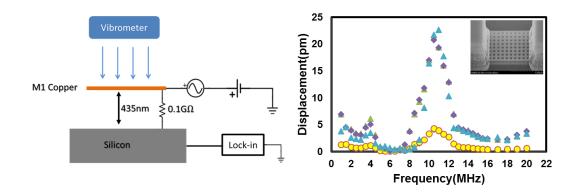

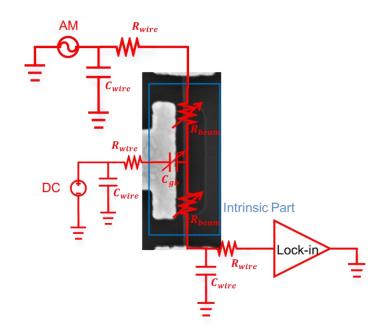

| 4.1. (Left) The testing scheme of post-processed metal grid mechanical resonator. (Right)      |

| DLV optical measurement result of the metal grid resonator. Different symbols are              |

| results with different AC and DC excitation configurations. (Inset) An SEM of the              |

| resonator with dimensions: $5.396 \mu m \times 4.82 \mu m \times 136 nm$                       |

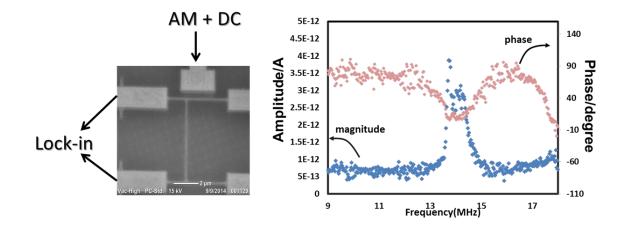

| 4.2. (Left) An SEM image of the H-shape resonator and the testing scheme. AM:                  |

| amplitude modulated signal, Lock-in: lock-in amplifier. (Right) The corresponding              |

| measured frequency response74                                                                  |

Page

| Figure   Page                                                                             |

|-------------------------------------------------------------------------------------------|

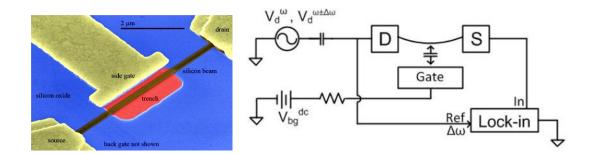

| 4.3. (Left) An SEM picture of a representative silicon resonator [84]. (Right) Diagram of |

| the measurement setup [85]75                                                              |

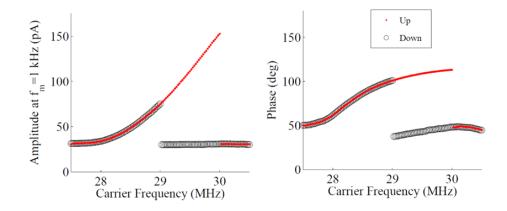

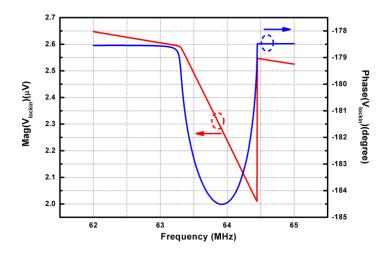

| 4.4. Measured magnitude (left) and phase (right) frequency response of the double-        |

| clamped silicon resonator [86]76                                                          |

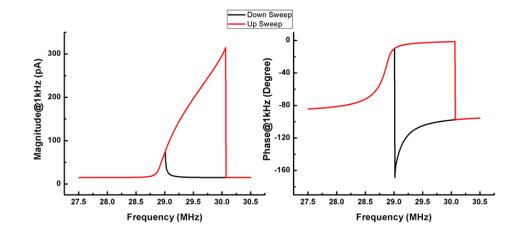

| 4.5. Equivalent circuit representation of the beam and measurement setup                  |

| 4.6. Frequency response of the beam driven by a single-tone excitation. Red line is the   |

| magnitude. Blue line is the phase                                                         |

| 4.7. Frequency response of the beam under an amplitude modulation excitation.             |

| Frequency response of magnitude (left) and phase (right) of the output current at         |

| modulated frequency 1kHz. Red curves are the response when the carrier frequency          |

| is up-swept while the black curves is down-swept                                          |

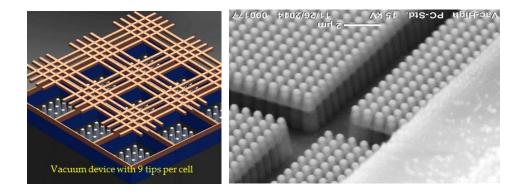

| 5.1. Vacuum transistors implemented on the GlobalFoundries 45 nm CMOS SOI                 |

| platform (left) and an SEM image of the device after post-processed to release the        |

| silicon emitters (right)                                                                  |

| 5.2. Implementation of silicon FEAs with transparent monolayer graphene gate before       |

| placing anode (left) and after adding anode (right)                                       |

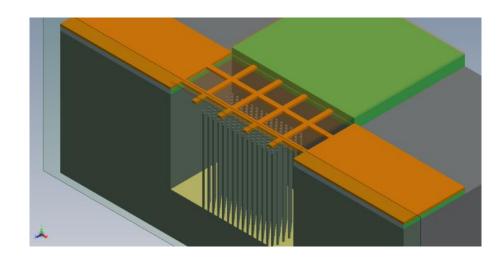

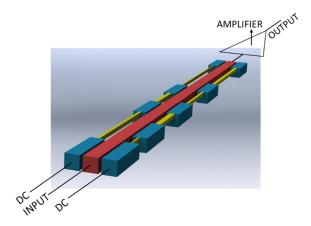

| 5.3. A diagram showing the transmission line resonators with testing scheme. The yellow   |

| parts are the resonators with different dimensions. The red line is the input line for    |

| the amplifiers. The blue boxes are the anchors for the resonators                         |

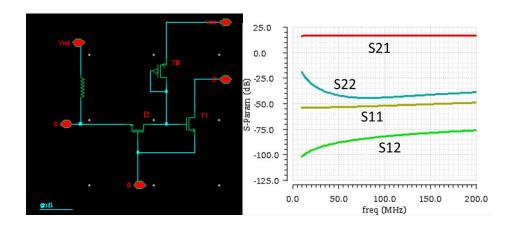

| 5.4. Circuit schematic of an output amplifier for the nano-resontors (left) and simulated |

| S-parameters of the amplifier (right)                                                     |

## LIST OF ABBREVIATIONS

| FE           | Field Emission                          |

|--------------|-----------------------------------------|

| FEA          | Finite Element Analysis                 |

| KCL          | Kirchhoff's Current Law                 |

| KVL          | Kirchhoff's Voltage Law                 |

| FEA          | Field Emitter Array                     |

| FN tunneling | Fowler-Nordheim Tunneling               |

| SOA          | Safe Operating Area                     |

| FBSOA        | Forward Bias Safe Operating Area        |

| LB technique | Langmuir-Blodgett Technique             |

| TCAD         | Technology Computer-Aided Design        |

| SEM          | Scanning Electron Microscope            |

| ALD          | Atomic Layer Deposition                 |

| RIE          | Reactive Ion Etching                    |

| DRIE         | Deep Reactive Ion Etching               |

| BOE          | Buffered Oxide Etch                     |

| CMP          | Chemical-Mechanical Planarization       |

| HF           | Hydrogen Fluoride                       |

| CMOS         | Complementary Metal Oxide Semiconductor |

| SOI         | Silicon on Insulator                              |

|-------------|---------------------------------------------------|

| BOX         | Buried Oxide                                      |

| MOSFET      | Metal Oxide Semiconductor Field Effect Transistor |

| NMOS        | N-channel MOSFET                                  |

| BSIM        | Berkeley Short-channel IGFET Model                |

| DIBL        | Drain Induced Barrier Lowering                    |

| RF          | Radio Frequency                                   |

| NVT         | Nano-Vacuum Tube                                  |

| IC          | Integrated Circuit                                |

| VS          | Virtual Source                                    |

| GSG         | Ground-Signal-Ground                              |

| S-parameter | Scattering Parameter                              |

| Y-parameter | Admittance Parameter                              |

| Z-parameter | Impedance Parameter                               |

| NF          | Noise Figure                                      |

| PSD         | Power Spectral Density                            |

| M/NEMS      | Micro/Nanoelectromechanical Systems               |

| DLV         | Doppler Laser Vibrometer                          |

| AM          | Amplitude Modulation                              |

### ABSTRACT

Shen, Yanfei. Ph.D., Purdue University, December 2016. Design, Compact Modeling and Characterization of Nanoscale Devices. Major Professor: Saeed Mohammadi.

Electronic device modeling is a crucial step in the advancement of modern nanotechnology and is gaining more and more interest. Nanoscale complementary metal oxide semiconductor (CMOS) transistors, being the backbone of the electronic industry, are pushed to below 10 nm dimensions using novel manufacturing techniques including extreme lithography. As their dimensions are pushed into such unprecedented limits, their behavior is still captured using models that are decades old. Among many other proposed nanoscale devices, silicon vacuum electron devices are regaining attention due to their presumed advantages in operating at very high power, high speed and under harsh environment, where CMOS cannot compete. Another type of devices that have the potential to complement CMOS transistors are nano-electromechanical systems (NEMS), with potential applications in filters, stable frequency sources, non-volatile memories and reconfigurable and neuromorphic electronics.

In this work, a compact scalable nonlinear RF MOSFET model for NMOS transistors in a standard 45nm CMOS SOI technology is presented. This model employs a simple nonlinear core known as the Virtual Source (VS) model and adds parasitic elements around it to accurately simulate the RF performance of NMOS transistors up to 40GHz. The traditional long-channel thermal noise model is replaced by a combined shot-thermal noise model for the first time to accurately predict the noise behavior of these short-channel transistors up to 40GHz. The model parameters are extracted from DC, S-parameter and noise measurements across different bias conditions and for different device dimensions to achieve a scalable nonlinear model.

In addition to CMOS modeling, silicon nanowire field emitter arrays, which yield large current densities with high reliability and low turn-on voltages are designed, and implemented. An electro-thermal simulation is performed to obtain the parameters that optimize the device performance. The silicon emitter arrays are fabricated using a self-assembled technique for the first time. Silicon nanowire FEAs fabricated with this technique are dense (~75% fill factor), highly repeatable and reproducible, and low-cost. An ungated two-terminal device and a gated vacuum transistor are fabricated in this technology and are characterized.

Various CMOS integrated NEMS resonators are fabricated and characterized. A compact model for double-clamped CMOS Silicon on Insulator (SOI) NEMS devices is constructed and implemented. The model covers both linear and nonlinear characteristics of nanoscale single gated and double gated resonators made of silicon beam of different sizes and gaps. This model can also capture the hardening or softening effects, Duffing-type response and hysteresis responses, that are observed in such devices.

### CHAPTER 1. INTRODUCTION

### 1.1 Introduction

For novel nanoscale devices, integration with CMOS is an essential step that facilitates such advanced devices to transition from research-grade technology into the consumer market. There are generally two paths to design CMOS integrated devices. One way is to fabricate the devices first and then try to make them CMOS compatible. The other way is to design devices directly on a CMOS chip. Once the devices are made CMOS compactible, they can benefit from enormous infrastructure available for CMOS electronic manufacturing and can quickly gain high reliability and low cost status available in CMOS, leading to their good commercial prospective. After devices are ready for commercial use, there is a second complication that needs to be addressed. In an integrated circuit, there are sometimes millions or even billions of devices with different sizes and operating conditions. These devices have different parameters, which lead to different electrical performance. The decision in what type of device to use and what parameters may provide optimal performance can be addressed by device modeling. There are basically two types of device models; The FEA (finite element analysis) based models utilized in TCAD device simulation, suitable for process as well as single device level simulation to predict different real-world physical effects such as heat, vibration,

flow, EM wave, etc. They utilize the very fundamental physics principles, ranging from the very general, like Maxwell Equations or Bernoulli's Principle to the very specialized functions, such as Fowler-Nordheim tunneling equation for field emission tunneling. They employ the boundary conditions, which are set by a user, divide the whole geometry into smaller meshes and solve the physics based equations consistently for all meshes. The finer the meshes are, the more accurate the simulation is, and the more time it will take to run the simulation. Typically, this type of simulation is very computational intensive. So only a single device or a few very simple devices are acceptable at a fair accuracy if the simulation runs on a single computing platform. A few commercialized simulators are Synopsis Sentaurus TCAD, COMSOL Multiphysics, Ansys HFSS and so on. Circuit simulations, which usually composed of a dozen to millions of sophisticated electrical devices, sources, passive components, however, cannot rely on TCAD simulations as they are very inefficient in solving such a big problem. Therefore, a socalled compact model for each of the devices is needed to speed up the simulation with a reasonable accuracy.

Compact model is the bridge between devices and circuits. While partially physics based, most compact models utilize a set of empirical or semi-empirical mathematical equations to describe the device characteristics for circuit simulators. The compact model takes in the terminal input and generates terminal output information, which is based on the electrical behavior of the device, but can be extended to other characteristics such as mechanical motion, stress and heat. A simple example is an ideal resistor with resistance *R*. A simple mathematical function to describe the behavior would be I = V/R, where *I* is the current in the resistor when a voltage *V* is applied. The compact model takes in the terminal voltage of the resistor (V) and output the current flowing through it (I). The device behavior described by compact model could be multi-domain correlated. For example, in a simple micro-cantilever as shown in Figure 1.1, mechanical domain and electrical domain are combined. The deflection of the micro-cantilever will induce the resistance change in the beam, which could be sensed by electrical instrument. If a gate is present, the electrical force between the gate and cantilever will drive the beam and the beam deflection will change the capacitance, which will further change the electrical forcing between the two. Therefore, a good compact model is able to take in the terminal information, combine the inherent dynamics to predict electrical or mechanical behavior accurately.

Figure 1.1. A single crystal SiC epilayer cantilever for mass sensor [1]

As modern nano-scale devices are becoming more and more sophisticated as the dimensions are getting smaller, compact models are becoming more complex since a number of physics-based phenomena need to be considered. Modern state-of-the-art MOSFET compact models usually have several hundred of parameters to take care of

various physical effects, such as short-channel effect, narrow-width effect, channel length modulation, drain-induced barrier lowering (DIBL), etc.[2].

After the compact model is developed, the circuit simulator takes all the compact models for each of the elements and the inter-connection information to solve the circuit equations iteratively using Newton-Raphson or a similar method. The circuit equations are Kirchhoff's Voltage Law (KCL) and Kirchhoff's Current Law (KVL). A good compact model needs to have the following properties,

- (1) Accurate for a wide range of parameters

- (2) Physics based

- (3) Computationally simple

- (4) Smooth enough: continuous, differentiable, even second order differentiable

Finally, a compact model needs to have good parameter initializations and limits to ensure convergence in a circuit simulation.

### 1.2 Compact Modeling of 45nm CMOS SOI Transistors

A comprehensive deep submicron MOSFET model that captures DC, RF and noise characteristics of transistors is of great importance for circuit designers and several such models have already been fully or partially developed [3]–[7]. Modern mainstream transistor compact models are composite type models, which take an accurate DC core model to describe the drain current characteristic and a terminal charge model for low frequency analog simulations. In order to predict high frequency (HF) behavior, an equivalent circuit is constructed and various technology-related parasitic elements are

added around the DC core model. These parasitic elements are extracted from experimental data for different geometries and biases.

Figure 1.2 is a typical example of modern transistor model. The bottom circuit in the left figure is the equivalent circuit model, which consists of a core transistor model, taking care of the drain current information and intrinsic parasitic elements, such as the overlapping capacitances,  $C_{gs}$ ,  $C_{gd}$ ,  $C_{ds}$ , output conductance  $g_{ds}$ , etc. and several peripheral extrinsic parasitic elements (both resistive and inductive) such as  $L_G$ ,  $R_G$ ,  $L_S$ ,  $R_S$ ,  $R_D$ ,  $L_D$ , etc., which cannot be neglected at high frequency operation.

Figure 1.2. Equivalent circuit model of modern NMOS transistor [8]

The origins of the various parasitics in a single finger layout of a CMOS transistor is also shown Figure 1.2. Almost all mainstream MOSFET models provide the core part of the model as shown in the top left figure of Figure 1.2, while semiconductor manufacturing foundries characterize their own external parasitics for their own technology and add them to these core models to achieve a complete non-linear transistor model.

Most current state-of-the-art transistor models are equivalent circuit based as discussed above. The differences are in the approaches that they employ to describe the DC model and charge model. In particular, how much physical phenomena are captured in the model may vary. Most of the models were intended for digital and low frequency applications so they often fail to capture the RF behavior accurately. With more attention towards the wireless communication market, the model vendors are forced to extend their models for HF applications. The widely used transistor models such as BSIM, and Phillips MOS Model have been shown to accurately predict the drain current behavior for deep submicron devices [3][4]. However, they usually employ hundreds of parameters to achieve such accuracy, which makes the parameter extraction process very tedious. Yet they fail to accurately capture the RF and noise behavior of modern sub-100-nm CMOS transistors. The new surface-potential-based PSP model formerly developed at the Pennsylvania State University and Philips (now at Arizona State University and NXP Semiconductors Research) has been supported by the Compact Modeling Council (now Compact Model Coalition in Si2) as the next standard model. It is a combined product of MOS Model 11 [4] and SP [9], both of which are based on charges calculated from surface potential [2]. The virtual source (VS) model has its advantage in reducing the number of parameters down to below twenty, while maintaining the accuracy of predicting non-linearity at DC, especially for short channel transistors, where semiballistic transport takes place [6][10]. The model, however, is still in infancy with

unproven accuracy for non-linear RF behavior and no apparent advantages in prediction of the noise behavior at high frequencies.

Various work on MOSFET small signal modeling has been reported [11]–[14]. For many RF applications such as RF power amplifiers, mixers, and oscillators, however, the capability of the model to predict the large signal and intermodulation distortions is important. Several work on MOSFET nonlinear model has also been reported [15]–[19].

Figure 1.3. A SEM image from IBM of one finger of CMOS SOI transistor [20]

Nevertheless, few deal with nonlinear RF modeling of MOSFETs with channel lengths below 65 nm and also on silicon-on-insulator (SOI) technology. CMOS SOI technology usually offers 20-35% better performance compared to its bulk CMOS counterparts [21], because of the elimination of junction capacitances and substrate loss. Also for power applications, the presence of the Buried Oxide (BOX) layer helps the device to sustain larger voltage swing, which may lead to high output power. Figure 1.3 is a SEM image of one finger of a CMOS SOI transistor. Only a few work has been devoted to CMOS SOI transistor modeling [13], [22]–[24]. Most are either dealing with small-signal models or are purely empirical based. Large signal circuit design has been purely relying on the models provided by semiconductor manufacturing foundries, which are developed for digital and low-frequency analog circuits, and lack the accuracy to predict RF and microwave behavior.

Accurate MOSFET noise model requires deep understanding of device physics and accurate noise source identification. Most existing MOSFET noise models are thermalnoise based, which consider the noise originated from the finite channel resistance, induced gate noise, correlation between gate and channel noise and various parasitic resistances [25]–[29]. Reference [30] adds the source-bulk junction and drain-bulk junction shot noise to the channel thermal noise. The latter two noise sources, under normal biasing condition of the transistor, are very small, as these junctions are reversed biased. Classical long channel thermal noise model is not able to fully capture the noise for nanoscale transistors, especially when the channel length scales down to below 100 nm. Compromises have been made to fit the need, however, not only does the classical long channel model fail to capture the fundamental physics, but also, as the device channel length scales down further, the model requires even more revisions. Lastly, reference [31] proposed that for short channel MOSFETs, the shot noise induced by the random nature of electron injection from the source through the potential barrier into the channel dominates the drain current noise compared to the thermal channel noise induced by electron random scattering in the channel. This model, unfortunately, has not been tested and verified.

In summary, an accurate CMOS SOI transistor modeling will require the model to have the following properties:

- (1) Physics based accurate drain current model

- (2) Accurate HF small signal and large signal model

- (3) Accurate nonlinear and intermodulation distortion

- (4) Scalability and bias dependence

- (5) Accurate HF noise prediction

In this thesis, a comprehensive NMOS transistor model that covers drain current, high frequency nonlinear behavior, and a new combined shot-thermal noise is presented in the following sections.

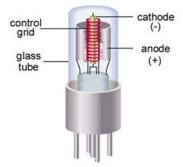

#### 1.3 Cold Cathode Technology

Cold cathode field emission has numerous vacuum microelectronic applications including plasma displays [32], electron guns for high power microwave sources [33], spacecraft neutralizer [34], scanning electron microscopes and so on. The mechanism for electron emission from a surface by applying a large electric field is called field emission. Recently, a field emission based vacuum channel MOSFET has been reported [35]. Figure 1.4 lists the applications of field emitters and the corresponding difficulty levels. Thermionic emission demands active cooling, a problem that has hindered the integration of thermionic electron guns into microsystems. In comparison to thermionic emission, field emission requires no cooling, thus may be suitable for integrated circuit applications. For a cold cathode to emit electrons, a substantially large electric field is often required to overcome the work function of the material used. To reduce the voltage

required between the two electrodes, sharp tips are usually used in almost all field emission applications. Tremendous amount of work has been devoted to conical shape field emitter arrays, known as Spindt arrays, for which the top sharp tip reduces the required voltage level and the large body would be able to provide sufficient amount of electrons and also helps to cool the device at the same time [34][36]. The problem associated with this type of devices is, however, the non-uniformity in tip sharpness due to fabrication variations. Typically, sharper tips are turned on earlier and conduct more current under the same bias, when compared to dull tips. This phenomenon leads to more heat generation for sharper tips, which in turn, causes them to burn easily. In order to mitigate the non-uniformity in tip current for longevity, a large feedback resistor, which acts as a current regulator, has been added in series with the emitter [37].

Figure 1.4. Difficulty level of various applications of field emitters[36]

This approach is not promising since the total emission current is limited to a fairly low number of field emitters as they continue to burn while their current is shifted to other tips. A silicon pillar structure made with a low-doped semiconductor to achieve uniformity of emission current has been previously proposed [38]. Moreover, different materials are used as electron source, including carbon nanotubes (CNTs) [39]-[42], zinc oxide (ZnO) [43], and silicon carbide (SiC) [44]. The problem with all these implementations is that not only are they are still early stage research projects and far from integration, but also they have no current control mechanism, which may cause the device to fail rapidly. In this thesis, a field emitter electron source with vertical silicon nanowire array structure is proposed that addresses the problems of previous work. By taking advantage of current saturation mechanism in high aspect ratio semiconductor structure, the emission current can be readily limited and uniformity of emission is expected. Also, by reducing the doping level, the saturation voltage can be lowered to a few tens of volts for sharp tips and small gaps. A comprehensive device TCAD simulation has been conducted to achieve the optimal parameters for the design of the nanoscale electron field emitter. Two main failure mechanisms have been considered: thermal runaway and ion bombardment. Approaches to avoid both mechanisms are evaluated [34]. By utilizing the Langmuir-Blodgett (LB) experiment, a self-assembled mechanism to achieve low-cost and high density field emitters has been established. In this technique, instead of using electron beam lithography, a single compact layer of silica particles is deposited and used as a mask for etching of silicon nanowires. This way of fabrication yields a very dense array of nanowires, which will lead to high current density at a very reduced cost. Moreover, a new packaging process is proposed. Details of simulation, optimization and fabrication of these devices are discussed in Chapter 3.

#### 1.4 Nano-Electro-Mechanical (NEM) Systems

Micro/Nanoelectromechanical systems (M/NEMS) are gaining great momentum and interest for a variety of applications such as extremely high sensitivity mass sensors [1], mechanical switches [45], mechanical memories[46], tunable filters [47] and oscillators [48]. One reason is the maturity of fabrication and their commercialization. Consequently, several MEMS devices have been used in our daily lives, such as accelerometers and pressure sensors in cars, different type of sensors in phones, etc. [49]. The other reason is that they possess an inherently high quality factors and can provide narrow bandwidth operation compared to their electrical counterparts. Moreover, mechanical devices, when scaled down to nanometer dimensions are usually more energy efficient, which is a good advantage for mobile computing. Most commercialized mechanical devices are MEMS devices. When compared to their micro-scale counterparts, the nano-scale mechanical devices offer even better performance in most cases and are more sensitive if used as a sensor. The main problem is that they suffer from process variations and are still considered research-grade devices. The other challenge is that these nano-scale devices are difficult to integrate reliably because mechanical parts are more fragile as dimensions shrink down. Also, nano-scale devices are more challenging to characterize as the output signal is usually very weak and various damping sources such as surface effects may become more prominent.

Regarding NEMS devices, two different goals are pursued in this thesis. One is to design CMOS-compatible NEMS devices based on already commercialized CMOS technologies. These NEMS devices are then post-processed using a simple microfabrication technology in the cleanroom to release the mechanical parts. These devices are then characterized with various methods for different purposes. Barniol group has done some pioneering work for CMOS-compatible MEMS device mostly based on  $0.35 \,\mu\text{m}$  and  $0.13 \,\mu\text{m}$  CMOS technologies and has proven the concept [50]–[54]. A more advanced technology, namely GlobalFoundries 45 nm CMOS SOI technology, has been used to pursue alternative designs for different applications. Further details are illustrated in Chapter 4.

The other goal of pursuing NEMS technology is to construct a system-level compact model for nano-scale NEMS resonators. Not only does the model capture the mechanical behavior of the device, it also accounts for the detailed coupling between the mechanical and electrical behavior of the system. Furthermore, it takes into account the various parasitic elements, which are important for these nano-scale devices. Chapter 4 provides further details on this subject.

### CHAPTER 2. COMPACT MODELING OF 45NM CMOS SOI TRANSISTORS

#### 2.1 Introduction

Nanoscale CMOS technology is an excellent platform for implementing single-chip systems because of its low manufacturing cost and integration capability with digital circuits [55]. Cutoff frequency  $f_T$  and maximum oscillation frequency  $f_{MAX}$  of advanced nanoscale Metal Oxide Semiconductor Field Effect Transistor (MOSFET) have surpassed 200 GHz mark, enabling microwave and mm-wave circuit operation [56]. Implementing microwave and mm-wave circuits with first time success remains elusive due to limited accuracy of the available device models on conductive Si substrates. Accordingly, comprehensive deep sub-100 nm MOSFET models that accurately capture DC, RF (including nonlinear) and noise characteristics of transistors are of great demand. Device modeling requires the knowledge and expertise in several distinct areas including mathematical modeling, device physics, high frequency and microwave measurement, electro-thermal analysis, noise analysis, programming, and statistics. Several MOSFET models have already been fully or partially developed [3]-[6]. The widely used BSIM model employs hundreds of parameter - many of them empirical - to capture linear and nonlinear RF and noise behavior of modern submicron MOSFET devices. Extraction of so many parameters is cumbersome and has led to the development of many BSIM models with insufficient accuracy. The surface potential based Phillips MOS Model

utilizes fewer empirical parameters compared to BSIM model. With over 200 parameters to be extracted, however, the model development is still an enormous challenge given the short time to market for advanced CMOS technologies. Another MOSFET model is the so-called virtual source (VS) model, which uses about ten parameters to describe the nonlinear DC performance of short-channel transistors. This model assumes a semi-ballistic transport mechanism inside nanoscale channels of MOSFETs, leading to a good modeling accuracy [6][10]. The VS model, however, has to be supplemented with bias and geometry dependent parasitic resistances, capacitances, and inductances to become suitable for deployment at high frequencies. To date, the VS model, however, is still unproven for predicting the nonlinear RF to mm-wave behavior of MOSFETs. Furthermore, it has no apparent advantage in predicting the noise behavior of nanoscale MOSFETs at high frequencies over other available MOSFET models.

Compared to nonlinear DC modeling, the nonlinear RF modeling of transistors is more challenging due to bias and geometry dependence of some of the parasitic elements in the RF model. Small-signal modeling is a shortcut in developing RF models and helps capturing the high frequency behavior of transistors under small-signal excitation and under a particular bias condition with good accuracy. Various MOSFET small-signal models have been reported [11]–[14]. The main drawbacks in utilizing small-signal models are that the model cannot capture device nonlinearity and is only valid for particular device geometries and at particular bias conditions under small-signal excitation. Thus, the small-signal model fails to predict the large-signal behavior of RF power amplifiers, mixers, and oscillators, where device bias and gain may change under applied RF signal and device nonlinearity. Furthermore, even for low-power RF circuits such as low noise amplifiers, weak nonlinearities including third order intermodulation distortions cannot be envisaged by the small-signal model. Several MOSFET nonlinear RF models have been reported [15]–[19]. Nevertheless, few deal with nonlinear RF modeling of MOSFETs with channel lengths below 65 nm and none addresses the intricacies of CMOS SOI modeling. To date, RF to mm-wave circuit designers have been mostly relying on digital models provided by semiconductor manufacturing foundries, which are mainly developed for digital and relatively low frequency analog circuit applications. These models have insufficient accuracy to predict RF and microwave behavior of linear and nonlinear devices and circuits.

MOSFET noise modeling requires a good understanding of device physics in order to identify various noise sources across the device. Most existing MOSFET noise models are based completely upon thermal noise. Such models presume that the noise originates from several thermal noise sources including a finite channel resistance, induced gate noise correlated to the channel noise, and various parasitic resistances [25]–[29]. The induced gate noise is introduced to explain the extra gate noise of MOSFETs at high frequencies as the device dimensions scale down. The induced noise model is incorporated more or less in the same manner among van der Ziel long-channel model, the BSIM 6 model, and Phillips MOS 11 model [3][4][58]. They share the same noise topology, in which, two correlated noise sources, i.e. the channel noise (the current noise flowing from the drain to the source terminal) and the induced gate noise (the current noise flowing from the gate to the source terminal), are incorporated [4][25][59]. Several other modifications to the classical long-channel noise model have been introduced.

Reference [30] adds the source-bulk junction and drain-bulk junction shot noise to the channel thermal noise in an attempt to capture the extra noise seen in sub-micron MOSFETs. Moreover, for noise, high frequency and high power applications, the distributed gate resistance effect of multi-finger MOSFETs has been introduced. Due to difficulty in its implementation, instead of using a lumped RC model, this effect has been most commonly modeled by a lumped gate resistor with a modified empirical resistance value [60][61][62]. The distributed gate resistance depends on the MOSFET layout and can be avoided if short transistor finger widths are employed in multi-finger RF transistor structures.

Despite all the modification made to the classical long-channel thermal noise model of MOSFETs, it still fails to fully capture the noise of nanoscale transistors, especially when the channel length scales down below 100 nm. On the other hand, for ultra short-channel MOSFETs with ballistic transport, it has been proposed that shot noise induced by the random nature of electron injection from the source contact through the potential barrier and into the channel dominates the drain current noise [31]. Therefore, the thermal channel noise induced by the random thermal motion of electrons in the channel of transistors operating in ballistic transport regime can be ignored. While this shot noise model fits the noise behavior of ultra short-channel MOSFETs investigated by device simulation, the model is not experimentally verified as no comparison to measured noise data has been provided [28]. Additionally, current sub-100 nm MOSFETs are still semiballistic transport devices and the aforementioned shot noise model is not expected to completely capture their noise behavior. It only seems logical that a combined shot-thermal channel noise model, which would integrate the classical long-channel noise

model and the shot-channel noise model together be utilized to accurately predict the noise behavior of the semi-ballistic transport devices.

### 2.2 Virtual Source (VS) Based DC Modeling

Since the explosion of mobile communication and computing, CMOS SOI technology has been in the forefront of technology platforms for applications such as microprocessors, embedded DRAM, transceivers and low-power devices [21]. Compared to its bulk CMOS counterpart, CMOS SOI provides between 20% to 35% performance gain or reduced power dissipation. The technology has been widely used in RF circuit design due to its low power dissipation, improved RF isolation, transistor stacking capability and the possibility of utilizing high resistivity and low-loss substrates [63][64]. The reasons for the performance gain of CMOS SOI devices over conventional bulk CMOS devices are: (i) significant reduction of transistor and passive element areal capacitances, (ii) reduced transistor short channel effects (SCE), (iii) improved transistor subthreshold slope, and (*iv*) the capability of using high resistivity substrate to reduce the losses and improve the self-resonance frequency of passive components. There are two types of SOI devices, namely, partially-depleted (PD) SOI and fully depleted (FD) SOI. In FD-SOI, the device layer thickness is smaller than the depletion thickness of source and drain contacts, leading to fully depleted body at threshold. There is no possibility of employing a body contact to the transistor in these devices and they behave similar to bulk CMOS devices, *i.e.* no kink effect (sudden increase in the output conductance for large drain-source voltage  $V_{ds}$ ) is observed. One of the main drawbacks of FD-SOI technology is its large-scale manufacturability, especially at sub-100 nm nodes. It has been proven difficult to control the parameters responsible for device depletion thickness

to guarantee that the body is depleted under all biasing conditions across all device dimensions. PD-SOI, on the other hand, has a device layer thickness at least twice larger than the maximum depletion thickness, leading to the formation of a neutral region beneath the depletion region. Compared to the bulk CMOS and their FD-SOI counterparts, PD-SOI MOSFETs exhibit anomalous behavior such as kink effect, and reduction of threshold voltage  $V_T$  with an increase of  $V_{ds}$  for devices without substrate contacts (floating body configuration) [63]. The VS model employed in this work is developed for PD-SOI CMOS transistors, but currently does not capture kink effect. Additionally, several other mechanisms including breakdown mechanisms (source-drain reach-through, source-drain breakdown and gate oxide breakdown), low-frequency noise, lifetime and statistical variations of various device parameters are not employed at this time. While all these mechanisms are important and will be implemented in future modeling efforts, the current model is proven to have excellent accuracy for these 45 nm NMOS transistors, as long as the applied gate-source voltage  $V_{gs}$  and drain-source voltage  $V_{ds}$  remain below the safe transistor operating voltage in this technology ( $V_{safe} = 1.2$  V). Note that although the VS model was originally developed for bulk MOSFETs, it has been applied to GaN HEMTs and Carbon Nanotube FETs with good accuracies, achieved by tweaking DC model parameters [65][66]. Through matching with measured data, it has been shown that the VS model is very robust in predicting the DC characteristics of NMOS transistors with different widths investigated in this work.

As the channel length becomes comparable to the electron mean free path in the channel, the classical drift-diffusion transport model fails [10]. Under this condition, MOS transistors feature semi-ballistic transport in the channel, where the classical drift-

diffusion based transport model fails [10]. By employing only a few physical parameters, the virtual source VS model is able to capture the output characteristics of modern short channel CMOS devices to a good accuracy. In the VS model, the normalized drain current is calculated as the product of the channel charge density ( $Q_{x0}$ ) and the virtual source velocity ( $v_{x0}$ ) at the top of the energy barrier at the source [6], where the gradual channel approximation applies [6].

$$\frac{I_d}{W} = Q_i(x_o) \cdot v_{x_o} \cdot F_{sat}$$

(2.1)

where  $F_{sat} = \frac{V_{ds}/V_{dsat}}{\left(1 + \left(\frac{V_{ds}}{V_{dsat}}\right)^{\beta}\right)^{1/\beta}}$ . The channel charge density is given by an empirical

function given by

$$Q_i(x_o) = nC_{in\nu}\phi_t \ln\left(1 + \exp\left(\frac{V'_{GS} - (V_T - \alpha\phi_t F_f)}{n\phi_t}\right)\right)$$

(2.2)

where *n* is subthreshold coefficient,  $V'_{GS}$  is series resistance corrected voltage between gate and source and  $\alpha$  is a fitting parameter.  $V_T$  is DIBL corrected threshold voltage.  $F_f$  is inversion function given by

$$F_f = \frac{1}{1 + \exp\left(\frac{V'_{GS} - (V_T - \alpha\phi_t/2)}{\alpha\phi_t}\right)}$$

(2.3)

Figure 2.1. illustrates the VS model fit into the measured data. An excellent fit for  $I_d$ - $V_{ds}$  curves is observed.

The VS model has ten input parameters: gate capacitance under strong inversion  $C_{inv}$ , threshold voltage  $V_T$ , subthreshold swing SS, drain-induced barrier lowering parameter *DIBL*, series contact resistances  $R_s$  and  $R_d$ , effective channel length  $L_{eff}$ , carrier low-field effective mobility  $\mu$ , carrier velocity  $v_{x_o}$  at the virtual source  $x_o$ , and two fitting parameters  $\alpha$ ,  $\beta$ . Details of extraction of these parameters are provided in [6]. In short, the gate capacitance and effective channel length are extracted from the foundry design manual. Series contact resistances, threshold voltage, *DIBL*, *SS*, carrier mobility, and carrier velocity at the VS are extracted from the measured data. Empirically,  $\alpha$  is set to be 3.5 while  $\beta$  is set to be 1.8 for NMOS transistors. The VS parameter values for the NMOS transistors investigated in this work are extracted from the dc behavior and are listed in Table 2.1.

| Parameters                   | NMOS  | Notes                               |

|------------------------------|-------|-------------------------------------|

| $L_g$ (nm)                   | 40    | Channel length                      |

| Lov                          | 12    | Total overlap channel length        |

| $C_g (\mu F/cm^2)$           | 2.625 | Gate capacitance                    |

| $R_s(\Omega \cdot \mu m)$    | 153   | Series contact resistance           |

| DIBL (mV/V)                  | 156   | Drain-induced barrier lowering      |

| SS (mV/dec)                  | 97    | Subthreshold swing                  |

| $v_{xo}$ (cm/s)              | 9.1e6 | Electron velocity at virtual source |

| $\mu$ (cm <sup>2</sup> /V·s) | 144   | Mobility                            |

| α                            | 3.5   | Fitting parameter                   |

| β                            | 1.8   | Fitting parameter                   |

Table 2.1. Extracted VS Parameters

Compared to its bulk counterpart, CMOS SOI devices present a relatively low thermal conductivity to the substrate due to a thin yet considerable buried oxide layer with low thermal conductivity under the active region. For RF transistors operating under high DC and/or RF powers, the temperature in the active region rises considerably. Higher temperature in the channel leads to higher scattering, higher noise and device

performance deterioration. In order to capture this phenomenon, a self-heating module is added to the VS model as described below.

$$\Delta T = \frac{R_{ih}}{\tau} \int_0^\tau V_{ds} I_{ds} dt, \quad T_{junc} = T_{amb} + \Delta T$$

(2.4)

$$v_{x} = v_{x_{o}}(1 - \eta \Delta T), \quad \mu = \frac{\mu_{o}}{1 + \theta \frac{\Delta T}{T_{amb}}}, \quad (2.5)$$

where both  $\theta$  and  $\eta$  are fitting parameters.  $\tau$  is the period of the RF signal or the interval over which the heat dissipation is calculated and *dt* is an infinitesimal time increment.  $T_{amb}$  is the ambient temperature and  $T_{junc}$  is the elevated junction temperature due to selfheating. Parameters  $v_{xo}$  and  $\mu_o$  are the initial VS velocity and carrier mobility at ambient temperature.  $R_{th}$  is the thermal resistance, assumed to be constant with modest temperature changes and may be calculated according to [67],

$$R_{th} = \frac{1}{2W} \left( \frac{t_{box}}{k_{ox} k_d t_{si}} \right)^{\frac{1}{2}}$$

(2.6)

where *W* is the transistor width,  $t_{box}$  is the thickness of buried oxide,  $t_{si}$  is the silicon body thickness,  $k_{ox}$  and  $k_d$  are the silicon dioxide and source/drain (n+ silicon) thermal conductivities, respectively. Note that thermal capacitance, which is a measure of how quickly the device warms up or cools down when power increases or decreases is not modeled. The above self-heating model takes into account virtual source velocity and mobility degradations due to the temperature rise  $\Delta T$  caused by the self-dissipated power according to (2.5).

An accurate DC model is the very foundation of the high frequency nonlinear transistor model. It not only requires to have an accurate prediction of the drain current, but also both transconductance and output conductance must be modeled with good

accuracies in order to predict both linear and nonlinear high frequency behavior of the transistor.

Figure 2.1. Accuracy of the developed VS model with self-heating effect (red curves) vs. measured DC data (open symbols) for two DC characteristics: (a) Drain current vs drainsource voltage ( $I_d$ - $V_{ds}$  characteristics), when gate-source voltage  $V_{gs}$  varies from 0.2 V to 1.0 V in steps of 0.2 V; (b) Drain current vs. gate-source voltage (transfer characteristics) when  $V_{ds} = 0.1$  V (lower currents) and  $V_{ds} = 1.1$  V (higher currents)).

#### 2.3 Nonlinear RF Modeling

## 2.3.1 Equivalent Circuit Based RF Model

A simple equivalent circuit based MOSFET RF model has been developed for MOSFET transistors in this technology as shown in Figure 2.2 (a). It consists of the core nonlinear VS model with included self-heating, intrinsic parasitic capacitances  $C_{gs}$ ,  $C_{gd}$ ,  $C_{ds}$  (enclosed by the blue box in Figure 2.2) and extrinsic parasitic elements ( $C_{pg}$ ,  $C_{pd}$ ,  $L_{g}$ ,  $R_{g}$ ,  $L_{d}$ ,  $R_{d}$ ,  $L_{s}$ ,  $R_{s}$ ) originated from interconnections, vertical interconnects (VIAs), RF pads and transistor layout parasitics. All these parasitic elements have been extracted from the measured S-parameter data. The measured transistors have multi-finger layout with 1 µm finger width and 40 nm effective finger length and number of fingers ranging from 42 to 336. The S-parameters were measured up to 40 GHz using Keysight E8361A PNA with INFINITI GSG RF probes. Moreover, the open de-embedding patterns were measured and used to eliminate the parasitic parallel capacitances associated with the pads ( $C_{pg}$ ,  $C_{pd}$ ). Note that, unlike the small-signal equivalent circuit model, this model is built upon a physics based DC model, rather than empirical transconductance and output conductance extracted from measured S-Parameter data.

Figure 2.2. Nonlinear equivalent circuit model of NMOS transistors under (a) normal operation and (b) cold bias condition. The DC characteristics is given by VS model (inside the red box). Elements inside the blue box are denoted as intrinsic elements whereas those outside of the box are extrinsic elements.

## 2.3.2 Extrinsic Parameter Extraction

Most extrinsic elements (with the exception of  $R_g$ ,  $R_d$  and  $R_s$  in Fig. 2.2 (a)) originate from the intermediate metal layers and the pads of MOSFET test structures and should not be taken into account when developing the nonlinear scalable RF model. The extrinsic parameters are bias independent but are functions of pad and interconnect geometries and their metallization structure. The extrinsic parasitic elements should be accurately extracted in order to obtain accurately extracted intrinsic parasitic elements discussed in the following section. The gate and drain parallel capacitances are extracted from an open de-embedding pattern that is fabricated on the same chip. Next, extrinsic parasitic inductances and resistances are extracted. Various extraction techniques have been developed for different technologies [12]-[14], [68]. Among them, techniques presented in [12] and [13] have been found to be most effective for this short-channel CMOS SOI technology. Under cold bias condition ( $V_{ds} = 0$  V and  $I_{ds} = 0$  A), the transistor operates in the linear regime and the equivalent circuit of the transistor simplifies to the one shown in Fig. 2.2 (b). During the extraction of extrinsic parameters, reference [13] utilized the fact that channel conductance in the linear regime is proportional to the overdrive voltage  $(V_{gs} - V_t)$  and this assumption has been verified for the NMOS transistors investigated in this work. By utilizing Z-parameters and equations developed in [13], all series parasitic elements may be extracted with a simple linear regression. The extracted extrinsic parameters are shown in Table 2.2.

| Width<br>(µm)              | 42    | 84    | 168   | 336   |  |

|----------------------------|-------|-------|-------|-------|--|

| $C_{pg}$ (fF)              | 13.65 |       |       |       |  |

| $C_{pd}$ (fF)              | 12.11 |       |       |       |  |

| $L_g$ (pH)                 | 32.13 | 30.33 | 35.32 | 35.41 |  |

| $L_d$ (pH)                 | 32.24 | 23.37 | 31.55 | 35.72 |  |

| $L_{s}$ (pH)               | 45.22 | 41.26 | 39.76 | 38.40 |  |

| $R_{g}\left( \Omega ight)$ | 25.78 | 14.15 | 5.9   | 2.95  |  |

| $R_{d}\left(\Omega ight)$  | 2.62  | 2.47  | 2.01  | 2.08  |  |

| $R_{s}\left( \Omega ight)$ | 0.36  | 0.34  | 0.69  | 0.85  |  |

Table 2.2. Extracted extrinsic parameter values for different sizes of transistors

# 2.3.3 Intrinsic Parameter Extraction

The intrinsic parameters were extracted from intrinsic Y-parameters, which can be obtained from the measured S-parameter by performing the following steps,

(1) converting the measured S-parameter (pads included) to extrinsic Y-parameter  $(Y^{ext})$ ;

(2) subtracting extrinsic parallel capacitances from extrinsic Y-parameter  $(Y^{ext})$  to obtain intermediate Y-parameter (Y');

$$[Y'] = [Y^{ext}] - \begin{bmatrix} j\omega C_{pg} & 0\\ 0 & j\omega C_{pd} \end{bmatrix}$$

(3) converting the intermediate Y-parameter (Y') to intermediate Z-parameter (Z')

(4) subtracting extrinsic series resistances and inductances from the intermediate Zparameter (Z') to obtain intrinsic Z-parameter ( $Z^{int}$ )

$$[Z^{int}] = [Z'] - \begin{bmatrix} R_g + R_s + j\omega L_g + j\omega L_s & R_s + j\omega L_s \\ R_s + j\omega L_s & R_d + R_s + j\omega L_d + j\omega L_s \end{bmatrix}$$

(5) converting intrinsic Z-parameter  $(Z^{int})$  to intrinsic Y-parameter  $(Y^{int})$ .

With the intrinsic Y-parameter ( $Y^{int}$ ), the intrinsic elements can be extracted according the following equations:

$$C_{ge} = -\frac{imag(Y_{12}^{int})}{\omega}$$

$$C_{gs} = \frac{imag(Y_{11}^{int} + Y_{12}^{int})}{\omega}$$

$$C_{ds} = \frac{imag(Y_{22}^{int} + Y_{12}^{int})}{\omega}$$

$$R_{ds} = \frac{1}{real(Y_{21}^{int})}$$

$$g_m = real(Y_{21}^{int})$$

$C_{gsi}$  and  $R_i$  were extracted from the intrinsic  $Y_{11}^{int}$  as

$$Y_{11}^{int} = j\omega \left( C_{gse} + C_{gd} + \frac{C_{gsi}}{1 + \omega^2 R_i^2 C_{gsi}^2} \right) + \frac{\omega^2 R_i C_{gsi}^2}{1 + \omega^2 R_i^2 C_{gsi}^2}$$

(2.7)

Thus,  $C_{gsi}$  and  $R_i$  were extracted from linear fitting of the following equation at low frequency as shown in Figure 2.3.

$$\frac{1}{real(Y_{11}^{int})} = R_i + \frac{1}{R_i C_{gsi}^2} \cdot \frac{1}{\omega^2}$$

(2.8)

Figure 2.4 depicts extracted intrinsic elements *vs*. frequency for a 42  $\mu$ m wide transistor (42 fingers with finger width of 1  $\mu$ m and effective finger length of 40 nm) biased at gate-source voltage  $V_{gs} = 0.9$  V, and drain-source voltage  $V_{ds} = 0.9$  V following the above extraction procedures. The fact that these intrinsic elements are constant over a broad frequency range of interest indicates the physical accuracy of the model. The same extraction technique has been applied to transistors with different sizes (84  $\mu$ m, 168  $\mu$ m,

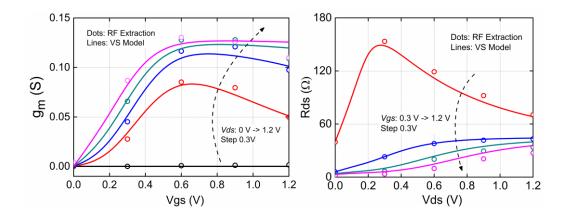

and 336  $\mu$ m wide NMOS transistors with 84, 168, and 336 fingers, respectively, each with finger width of 1 µm and effective finger length of 40 nm) under different biasing combinations.  $V_{gs}$  is varied from 0 V to 1.2 V in steps of 0.3 V and  $V_{ds}$  is varied from 0 V to 1.2 V, also in steps of 0.3 V. The extracted intrinsic parameters  $g_m$  and  $R_{ds}$  are compared with  $dI_{ds}/dV_{gs}$  and the reciprocal of  $dI_{ds}/dV_{ds}$  from the nonlinear VS model and tossed out in favor of the nonlinear and scalable VS model. In Figure 2.5 (a), the extracted intrinsic transconductance  $g_m$  (open circles) of an 84 µm wide transistor is compared with  $dI_{ds}/dV_{gs}$  from the VS model (solid curves) as functions of gate-source voltage  $V_{gs}$ , when drain-source voltage  $V_{ds}$  is a parameter. Similarly, in Figure 2.5 (b), the output resistance  $R_{ds}$  (open circles) of an 84 µm wide transistor is compared with the reciprocal of  $dI_{ds}/dV_{ds}$  from the VS model (solid curves) as functions of drain-source voltage  $V_{ds}$ , when gate-source voltage  $V_{gs}$  is a parameter. Similar observations are made for other transistor sizes. Therefore, the two comparisons show close match between the transconductance and output resistance and their respective VS values, which is an indication of VS model accuracy.

Figure 2.3. Linear fitting of  $1/\text{real}(Y_{11})$  to  $1/\omega^2$  at low frequency region to extract  $R_i$  and  $C_{gsi}$

Figure 2.4. Frequency dependence of the extracted intrinsic elements,  $C_{gse}$ ,  $C_{ds}$ ,  $C_{gd}$ ,  $R_{ds}$ , and  $g_m$  for a 42 $\mu m$  transistor biased at  $V_{gs} = 0.9$ V,  $V_{ds} = 0.9$ V

Figure 2.5. Accuracy of the VS model demonstrated by comparison to the extracted intrinsic parameters: (a)  $g_m$  and (b)  $R_{ds}$  for different bias conditions for an 84 µm wide transistor. Extracted intrinsic parameters  $g_m$  and  $R_{ds}$  are tossed out in favor of the scalable VS model.

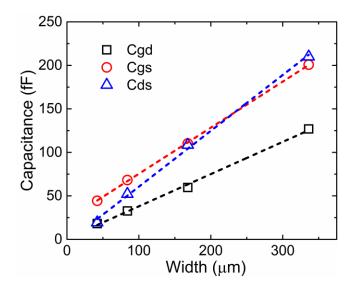

Figure 2.6. Intrinsic capacitances as functions of transistor width at  $V_{gs} = 0.9$  V and  $V_{ds} = 0.9$  V.

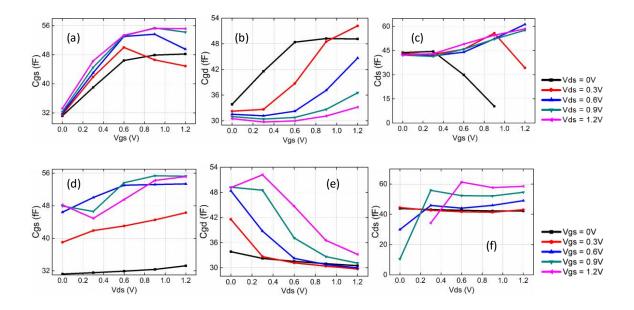

Figure 2.7. Bias dependence of extracted intrinsic elements (a)(d)  $C_{gs}$ , (b)(e)  $C_{gd}$ , and (c)(f)  $C_{ds}$  as functions of drain-source voltage  $V_{ds}$  and gate-source voltage  $V_{gs}$  for an 84  $\mu$ m wide transistor.

Scalability is an essential part of a compact transistor model as it enables circuit designers to optimize the circuit performance by choosing the optimal transistor size. Figure 2.6 depicts the scalability of the extracted intrinsic capacitances  $C_{gs}$ ,  $C_{gd}$ , and  $C_{ds}$  for transistor widths ranging from 42 µm to 336 µm. As these parasitic capacitances are mostly the overlapping and fringing capacitances among different terminals, they have linear dependences on the transistor width. An empirical approach has been taken to model the size dependency (scalability) of the three intrinsic parasitic capacitances. Six fitting parameters (the slope and the Y-axis intersection of each curve in Figure 2.6) have been extracted. Intrinsic elements for transistors with other sizes not measured here are extrapolated from these values. Figure 2.7 shows the gate-source and drain-source bias dependence of the three intrinsic capacitances ( $C_{gs}$ ,  $C_{gd}$  and  $C_{ds}$ ) for an 84 µm wide

transistor. In Figure 2.7 (a)-(c), the drain-source voltage is a parameter whereas the gatesource voltage is swept and in Figure 2.7 (d)-(f), the gate-source voltage is a parameter while the drain-source voltage is swept. Again, similar trends are observed for transistors with different width.

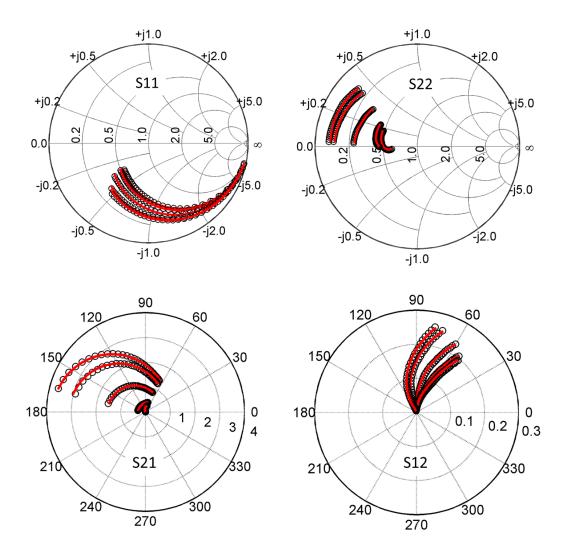

### 2.3.4 S-parameter Simulation

The developed MOSFET scalable model is put to a simple verification test. The Sparameters of an 84 µm NMOS transistor combined with extrinsic parasitic elements that represent interconnect test structure and the pads are calculated using Cadence SpectreRF and compared with the measured S-parameter values for the same transistor under different bias conditions. Figure 2.8 shows such comparison when gate-source voltage is fixed, while drain-source voltage is varied ( $V_{gs} = 1.2 \text{ V}$ ,  $V_{ds} = 0 \text{ V}$ , 0.3 V, 0.6 V, 0.9 V, 1.2 V). Figure 2.9 depicts the comparison for a fixed drain-source voltage, while gatesource voltage is varied ( $V_{ds} = 1.2 \text{ V}$ ,  $V_{gs} = 0 \text{ V}$ , 0.3 V, 0.6 V, 0.9 V, 1.2 V). An excellent match among measured and simulated S-parameter values up to 40 GHz and for all biasing conditions is observed. Moreover, similar trends are observed for other transistor sizes, demonstrating the accuracy of the scalable nonlinear model to predict the smallsignal RF performance of transistors with different sizes.

Figure 2.8. Comparisons of measured (open symbol) and simulated (solid line) S-parameters for different  $V_{ds}$  (0.0V, 0.3V, 0.6V, 0.9V, 1.2V) and  $V_{gs} = 1.2$ V for 84µm transistor.

Figure 2.9. Comparisons of measured (open symbol) and simulated (solid line) S-Parameters for different  $V_{gs}$  (0.0V, 0.3V, 0.6V, 0.9V, 1.2V) and  $V_{ds} = 1.2$ V for 84µm transistor.

# 2.4 Noise Behavior of nm-Scale Transistors

The next step in the model development is to add noise capability to the existing nonlinear model. According to classical high frequency noise models, the noise sources

in a MOS transistor originate from thermal noise associated with access resistances and channel resistance as shown in Figure 2.10 (a)  $(\overline{i_D^2}, \overline{i_G^2}, \overline{i_S^2}, \text{ and } \overline{i_{Ch}})$ . The thermal noise of physical resistors within the transistor can be described by a current noise source in parallel with the resistor *R* with a noise power spectral density  $4kT\Delta f/R$ . The absolute temperature *T* is set to the junction temperature of the device according to the self-heating module of the nonlinear transistor model. For  $\overline{i_G^2}$ , in addition to the thermal gate noise stemmed from the physical gate resistance, an induced gate noise is introduced to the classical model of sub-micron MOSFETs with very thin gate oxide to capture the noise due to the coupling between the potential fluctuations in the channel and the overlaying gate through gate-oxide capacitance [58]. On the other hand, for channel thermal noise, while some circuit simulators such as SPICE use the model  $\overline{i_{Ch}^2} = 4\gamma k_B T g_m$  (where  $g_m$  is the transconductance at the DC operating point, not valid for the linear region), the most widely used channel noise model is the one derived by van der Ziel given by,

$$\overline{I_d^2} = 4\gamma k_B T g_0 \tag{2.9}$$

where  $g_0$  is the output conductance at  $V_{ds} = 0$  V (linear region).  $\gamma$  is the so-called channel noise parameter and is equal to 2/3 in saturation and 1 in linear region for long channel devices [25]. This noise model describes the noise behavior of long-channel transistors well. The model, however, tends to underestimate the channel noise for short-channel transistors [69]. In an attempt to explain the excess noise of short-channel transistors, the

Figure 2.10. (a) Equivalent noise circuit model of a MOSFET with various noise sources.(b) The inset depicts the noise mechanisms in the channel for short-channel MOSFETs.(c) Circuit diagram of the combined channel noise model.

excess noise has been attributed to the elevated electron temperature at the drain [70]. Unfortunately, the electron temperature based noise model is shown to be in contradiction with simulation results [71]. On the other hand, the existing long-channel noise model has been adopted by most model developers through assigning a larger channel noise parameter  $\gamma$  that is no longer constant and changes with both bias and device dimensions to accommodate larger than expected noise of short-channel MOSFETs. While such a modification is convenient, it does not capture the noise of the short-channel device accurately, especially as the drain-source voltage or the lattice temperature of the device changes. Extraction of such empirical parameter  $\gamma$  to fit to all measured noise data is also very challenging.

Reference [31] points out that classical thermal channel noise model is based on driftdiffusion transport theory, which fails to predict the transport behavior of short-channel devices with ballistic transport. Therefore, in [31] the channel noise has been attributed to the shot noise induced by random injections of electrons from the source terminal to the channel, whereas the thermal noise in the channel has been completely eliminated. The current noise spectral density of the channel has been described by  $2k_sqI$  following the shot noise model in vacuum tubes (which are ballistic devices). According to the model, as the injection of electrons alter the field near the source in the space-charge region, the probability for the following electron injection is reduced, leading to the introduction of a shot noise suppression factor  $k_s$  ( $k_s < 1$ ). The shot noise model of short-channel MOSFET with the assumption of ballistic transport has been compared with device simulation data. Unfortunately, to the best of authors' knowledge, no verification of the noise model with measured noise performance has been provided since.

The shot noise model is built upon the ballistic transport theory, in which the electrons, after tunneling into the channel, are pumped into the drain immediately without any scattering. Given the doping density of the channel of NMOS transistors in this 45 nm CMOS SOI technology, the electron mean free path is roughly 7 nm [72]. Therefore, each electron encounters, on average, 5-6 scattering events in the channel before arriving at the drain (Effective channel length is 40 nm). This assumption ignores the fact that the transport occurs at Si-SiO<sub>2</sub> interface, which may impact the number of scattering events experienced by each electron. Therefore, it is only logical to devise a MOSFET noise model for such semi-ballistic devices that has contributions from both thermal and shot

noise. Therefore, the effective channel noise spectral density can be described through the following equation,

$$\overline{i_{Ch}^2} = \overline{i_{sh}^2} + \overline{i_{th}^2}$$

(2.10)