## Purdue University Purdue e-Pubs

**Open Access Dissertations**

Theses and Dissertations

January 2015

# From Process to Circuits: New Perspectives to Solar Cell Design

Elif Selin Mungan Purdue University

Follow this and additional works at: https://docs.lib.purdue.edu/open\_access\_dissertations

#### **Recommended** Citation

Mungan, Elif Selin, "From Process to Circuits: New Perspectives to Solar Cell Design" (2015). *Open Access Dissertations*. 1356. https://docs.lib.purdue.edu/open\_access\_dissertations/1356

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

# PURDUE UNIVERSITY GRADUATE SCHOOL Thesis/Dissertation Acceptance

This is to certify that the thesis/dissertation prepared

By Elif Mungan

Entitled From Process to Circuits: New Perspectives to Solar Cell Design

For the degree of \_\_\_\_\_ Doctor of Philosophy

Is approved by the final examining committee:

KAUSHIK ROY, Co-Chair

MUHAMMAD A. ALAM, Co-Chair

BYUNGHOO JUNG

JEFFERY L. GRAY

To the best of my knowledge and as understood by the student in the Thesis/Dissertation Agreement, Publication Delay, and Certification/Disclaimer (Graduate School Form 32), this thesis/dissertation adheres to the provisions of Purdue University's "Policy on Integrity in Research" and the use of copyrighted material.

KAUSHIK ROY, Co-Chair

| Approved by Major Professor(s): |  |

|---------------------------------|--|

|                                 |  |

|                                 |  |

| Approved by: Michael R. Melloch | 03/02/2015 |

|---------------------------------|------------|

|                                 |            |

Head of the Department Graduate Program

Date

## FROM PROCESS TO CIRCUITS: NEW PERSPECTIVES TO SOLAR CELL DESIGN

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Elif Selin Mungan

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

May 2015

Purdue University

West Lafayette, Indiana

To my dearest coauthor in life, without whom this PhD wouldn't be possible.

# TABLE OF CONTENTS

| Page |

|------|

|------|

| LIST OF TABLES                                                                                                 |

|----------------------------------------------------------------------------------------------------------------|

| LIST OF FIGURES vi                                                                                             |

| ABSTRACTxii                                                                                                    |

| 1. INTRODUCTION 1                                                                                              |

| 1.1. The Need for a Green Energy Source: Photovoltaics 1                                                       |

| 1.2. Fundamentals of Photovoltaics                                                                             |

| 1.2.1. Photovoltaic Effect                                                                                     |

| 1.2.2. Solar Cell Configurations and Band Diagrams                                                             |

| 1.2.3. Carrier Transport in Solar Cells                                                                        |

| 1.2.4. Figure of Merits and Compact Model                                                                      |

| <ol> <li>2. EFFECTS OF PROCESS CONDITIONS ON THE EFFICIENCY OF<br/>CHALCOGENIDE SOLAR CELLS</li></ol>          |

| 2.1.1. Polysilicon Solar Cells                                                                                 |

| 2.1.2. Polycrystalline CIGS Solar Cells 10                                                                     |

| 2.1.3. Polycrystalline CdTe Solar Cells 12                                                                     |

| 2.2. Grain Boundaries                                                                                          |

| 2.2.1. Grain Size Measurement Techniques and Distribution                                                      |

| 2.2.2. Effects of Grain Boundaries on Device Performance                                                       |

| 2.3. Effects of Na on the Efficiency of CIGS Solar Cells                                                       |

| 2.3.1. Simulation Framework192.3.2. Analysis of Possible Improvement Mechanisms212.3.3. Discussion28           |

| 2.4. Effects of Deposition Pressure on the Efficiency of Close Space<br>Sublimation Deposited CdTe Solar Cells |

iv

| 2.4.1. Change in Grain Size Distribution and Performance Variation                                                                                                    | . 29         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Technology from Process to Module Design                                                                                                                              | . 35         |

| 3. MODELING AND CO-OPTIMIZATION OF POLYCRYSTALLINE SILICON<br>SOLAR CELLS AND POWER CONDITIONING CIRCUITRY FOR ENERGY<br>SCAVENGING APPLICATIONS                      | . 50         |

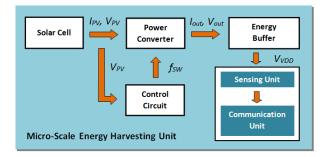

| 3.1. Micro-scale Energy Scavenging Concept                                                                                                                            | . 50         |

| 3.2. Thin Film Transistor Modeling                                                                                                                                    | . 52         |

| 3.3. Thin Film Transistor Process Compatible Polysilicon Solar Cell Model                                                                                             | . 56         |

| <ul> <li>3.3.1. Optimization of the Single-crystalline Structure</li></ul>                                                                                            | . 59<br>. 62 |

| 3.4. Effects of Process Parameters on Device, Circuit and System Levels in a Polysilicon Based Energy Scavenging System                                               | . 65         |

| <ul><li>3.4.1. Process Parameters</li><li>3.4.2. Effects of Process Parameters on the Performance of Thin Film</li></ul>                                              | . 66         |

| Transistors                                                                                                                                                           |              |

| 3.4.3. Effects of Process Parameters on the Performance of Solar Cells                                                                                                |              |

| <ul><li>3.4.4. Effects of Process Parameters on the Power Conditioning Circuit</li><li>3.4.5. Effects of Process Parameters on the Energy Scavenging System</li></ul> |              |

| 3.4.6. Looking Across Design Levels                                                                                                                                   |              |

| 4. SUMMARY                                                                                                                                                            | . 90         |

| LIST OF REFERENCES                                                                                                                                                    | . 91         |

| VITA                                                                                                                                                                  | 100          |

| PUBLICATIONS                                                                                                                                                          | 101          |

# LIST OF TABLES

| Table                                                                                                                                                                                        | age |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 Parameters used to model GB trapped charge density $(N_T)$ [a] and surface recombination velocity $(s_R)$ [b] with different trap models [34]. Copyright $\bigcirc$ by IEEE <sup>9</sup> | 20  |

| 2.2 Material Model Simulation Parameters. Copyright © by IEEE                                                                                                                                | 41  |

| 3.1 The effects of light trapping mechanisms on the 100 nm-thick solar cell [91].<br>Copyright © by IEEE                                                                                     | 58  |

| 3.2 Performance metrics for different doping concentrations [91]. Copyright © by IEEE                                                                                                        | 59  |

| 3.3 Impact of trap density $(N_T)$ on the polycrystalline cell performance [91] . Copyright $©$ by IEEE                                                                                      | 60  |

| 3.4 Efficiency of the proposed TFT process compatible solar cell [91]. Copyright © by IEEE                                                                                                   | 63  |

| 3.5 TFT Device Simulation Parameters                                                                                                                                                         | 67  |

| 3.6 V <sub>TH</sub> Values Used for TFTs in Circuit Simulations                                                                                                                              | 69  |

| 3.7 Parameters used to model the solar cell of micro-scale energy scavenging system                                                                                                          | 72  |

| 3.8 Processes used to determine the impact of process parameters on the performance of the micro-scale energy scavenging system.                                                             | 84  |

# LIST OF FIGURES

| Figure Page                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

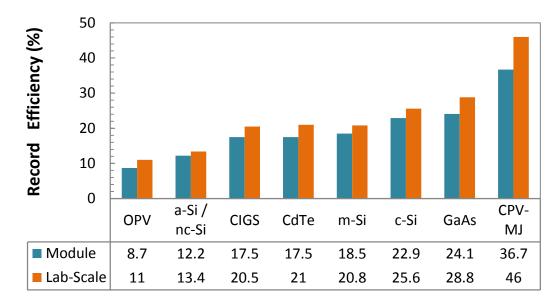

| 1.1 Best lab-scale cell (orange) and typical module level (blue) efficiencies for various solar cell technologies as of 2015. (Data is courtesy of Green et al. [6]) 2                                                   |

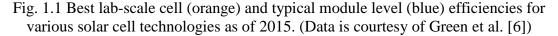

| 1.2 The band diagrams of p and n-type materials before and after they form a homojunction                                                                                                                                |

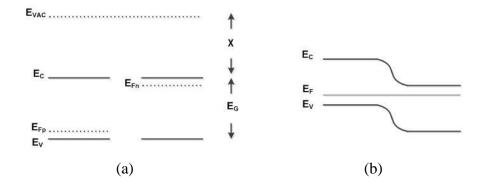

| 1.3 The band diagrams of p and n-type materials before and after they form: a Type I heterojunction (a, b) and a Type II heterojunction (c, d)                                                                           |

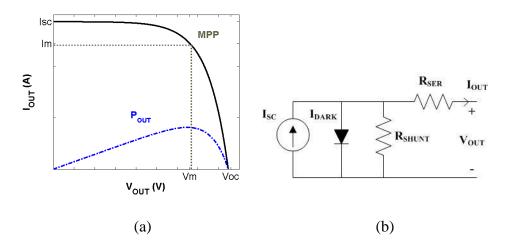

| 1.4 Current-voltage and power-voltage characteristics (a) and the compact model (b) of a solar cell                                                                                                                      |

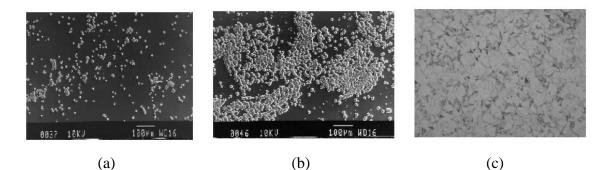

| <ul><li>2.1 Nucleation (a) and growth (b) process of polycrystalline Si fabricated with atmospheric pressure CVD. Grains would be seen as in (c) under a microscope [17]. Copyright © by John Wiley &amp; Sons</li></ul> |

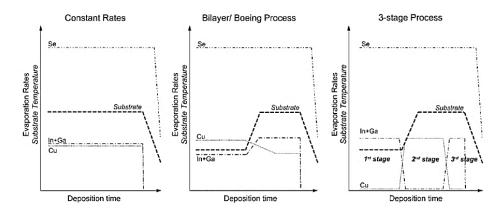

| 2.2 Three variations of co-evaporation process used for CIGS solar cells [19].<br>Copyright © by John Wiley & Sons                                                                                                       |

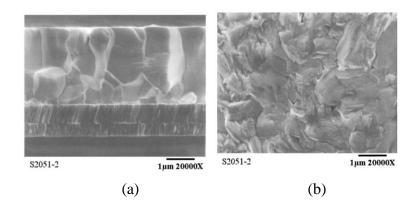

| <ul><li>2.3 Cross-section (a) and top view (b) of the CIGS sample fabricated with 3-stage process [20]. Copyright © by John Wiley &amp; Sons</li></ul>                                                                   |

| 2.4 Deposition setup for close space sublimation (CSS) process [21]. Copyright © by<br>John Wiley & Sons                                                                                                                 |

| 2.5 The cross-section of CdTe samples fabricated with CSS process. Before and after CdCl <sub>2</sub> treatment [22]. Copyright © by John Wiley & Sons                                                                   |

| 2.6 Grain boundaries as planar defects [23]. Copyright © by John Wiley & Sons 13                                                                                                                                         |

| 2.7 The change in the GB size distribution tail over time [26]. Copyright © by Elsevier                                                                                                                                  |

Page

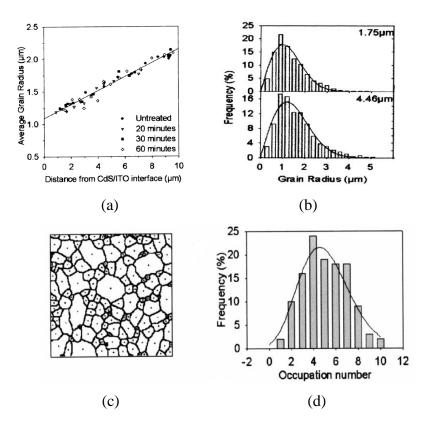

| 2.8 7 | The average grain size of <i>CSS</i> CdTe films with respect to measurement depth (a) and the grain size distributions of the films at two different depths (b). An illustrative top-view image of CdTe film (c) and the distribution for the number of grain centroids in a given area (d) [27]. Copyright © by Elsevier |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.9 ] | The band diagram of a negatively charged GB in an n-type semiconductor [29].<br>Copyright © by IEEE                                                                                                                                                                                                                       |

| 2.10  | Experimentally observed changes in CIGS due to Na diffused from the substrate: (A) Increased carrier density, (B) Ga segregation and (C) Change in crystal orientation [34]. Copyright © by IEEE                                                                                                                          |

| 2.11  | Single-crystalline (a) and polycrystalline (b) structures used in the simulations.<br>(c) SEM image of the CIGS solar cell in 2.3.a [34]. Copyright © by IEEE <sup>9</sup> 19                                                                                                                                             |

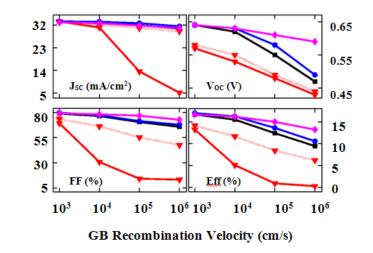

| 2.12  | Performance of a polycrystalline CIGS solar cell with respect to GB recombination velocity ( $s_R$ ) and GB model [34]. Copyright © by IEEE <sup>9</sup> 22                                                                                                                                                               |

| 2.13  | Energy band diagrams and recombination rates at GBs modeled with: (a) Donor-like traps with no valence band discontinuity (b) Neutral traps within a valence band shifted region [34]. Copyright © by IEEE <sup>9</sup>                                                                                                   |

| 2.14  | Energy band diagram of the double graded single-crystalline CIGS solar cell [34]. Copyright © by IEEE <sup>9</sup>                                                                                                                                                                                                        |

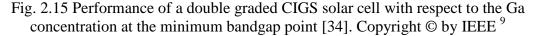

| 2.15  | Performance of a double graded CIGS solar cell with respect to the Ga concentration at the minimum bandgap point [34]. Copyright © by IEEE <sup>9</sup>                                                                                                                                                                   |

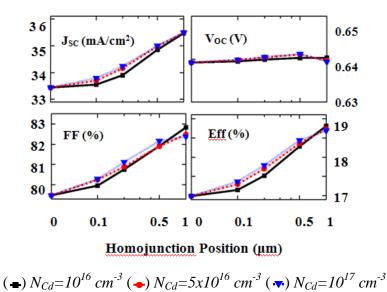

| 2.16  | Performance of CIGS solar cell with respect to homojunction position and doping density ( $N_{Cd}$ ) of the Cd diffused n-type CIGS layer [34]. Copyright © by IEEE <sup>9</sup>                                                                                                                                          |

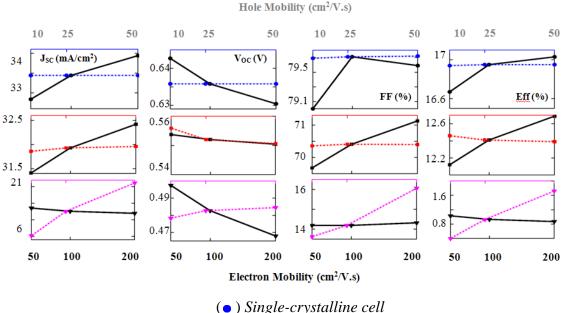

| 2.17  | Performance of CIGS solar cell with respect to electron mobility (solid black lines) and hole mobility (dashed colored lines) [34]. Copyright © by IEEE <sup>9</sup> 27                                                                                                                                                   |

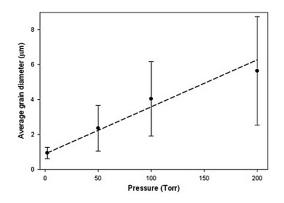

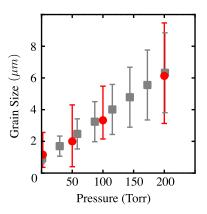

| 2.18  | Relation between the average GrS of a CSS-deposited CdTe thin film and the deposition pressure [51]. Copyright © by Elsevier                                                                                                                                                                                              |

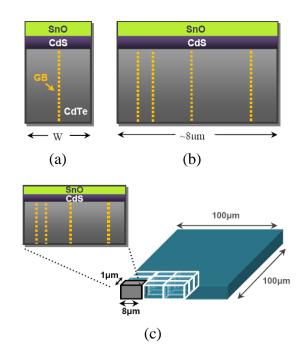

| 2.19  | Structures used to model the micron-scale solar cell [with uniform GrS (a) and random GrS (b)] and millimeter-scale cell (c) [53]. Copyright © by IEEE                                                                                                                                                                    |

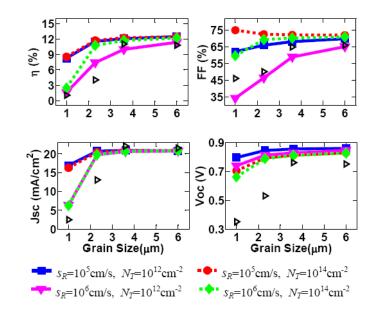

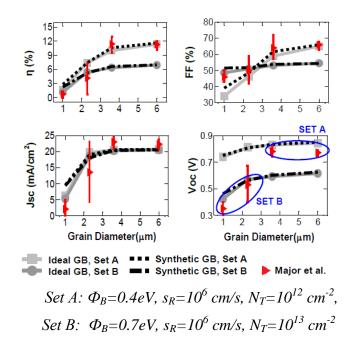

| 2.20  | Performance of simulated micron-scale cells with different GB recombination velocities ( $s_R$ ) and GB trap densities ( $N_T$ ). [" $\triangleright$ " indicates the data from Major et al. in [51]] [53]. Copyright © by IEEE                                                                                           |

# Figure

| Page |

|------|

|------|

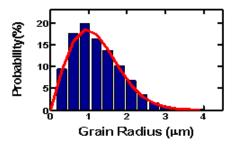

| 2.21 | The grain size distribution of the randomly generated structures used to simulate the variation in cell efficiency (blue bars) and the fitting distribution from [27] (red line) [53]. [Data is courtesy of Cousins et al.] Copyright © by IEEE                                |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

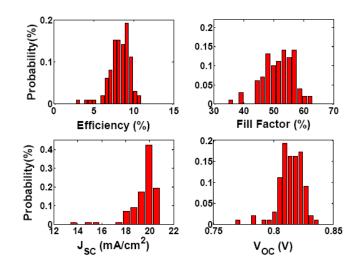

| 2.22 | The variation results from $\mu$ -scale TCAD simulations [53]. Copyright © by IEEE                                                                                                                                                                                             |

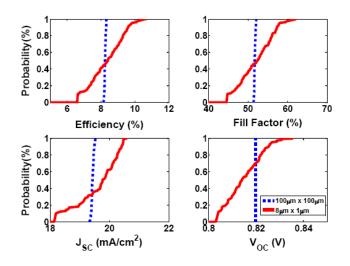

| 2.23 | The empirical cumulative distribution functions of the Monte Carlo simulation results for micron-scale and millimeter-scale CSS CdTe cells [53]. Copyright © by IEEE                                                                                                           |

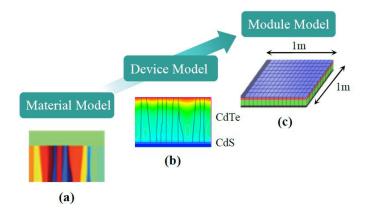

| 2.24 | Setup of hierarchical end-to-end model of CSS CdTe solar cell technology [58].<br>Copyright © by IEEE                                                                                                                                                                          |

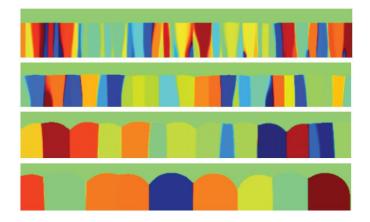

| 2.25 | 50 $\mu$ m x 6 $\mu$ m CSS CdTe thin films deposited under different chamber pressures [Top to bottom: 2, 50, 100 and 200 Torr] [58]. Copyright © by IEEE 41                                                                                                                   |

| 2.26 | CSS-CdTe grain size as a function of chamber pressure (simulation data: ●, experimental data from Major et al. in [51]: ■) [58]. Copyright © by IEEE                                                                                                                           |

| 2.27 | Device structure with synthetic GBs for CSS CdTe solar cells deposited under 2<br>Torr pressure. [Device dimensions are 10 $\mu$ m x 6 $\mu$ m] [58]. Copyright © by<br>IEEE                                                                                                   |

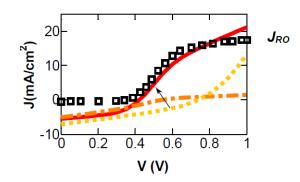

| 2.28 | Dependency of light J-V curve and the roll-over current $(J_{RO})$ of CSS CdTe solar cells on back contact barrier $(\Phi_B)$ and GB trap density $(N_T)$ . (Experimental data courtesy of Major et al. [51]) [s <sub>R</sub> =10 <sup>6</sup> cm/s] [58]. Copyright © by IEEE |

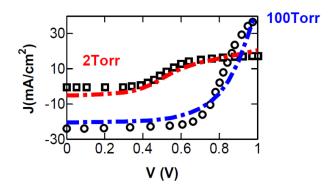

| 2.29 | Reconstruction of light J-V curves of CSS CdTe solar cells deposited under 2<br>Torr and 100 Torr pressures. (Simulation results: (dash-dotted lines),<br>experimental data: $(\Box, \circ)$ courtesy of Major et al. [51]) [58]. Copyright © by<br>IEEE                       |

| 2.30 | Performance metrics of CSS CdTe Solar Cells modeled with ideal GBs (solid lines) and synthetic GBs (dashed lines) versus experimental data (Courtesy of Major et al. [51]). [58]. Copyright © by IEEE                                                                          |

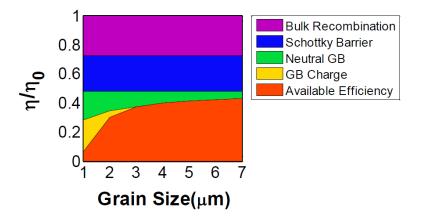

| 2.31 | Breakdown of loss mechanisms observed in polycrystalline CSS CdTe solar cells. (The results are normalized with respect to efficiency of an ideal cell $(\eta_0)$ ) [58]. Copyright © by IEEE                                                                                  |

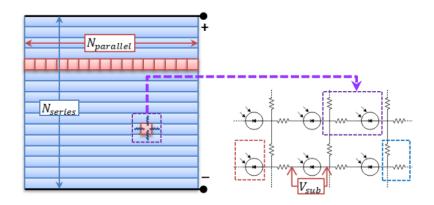

| 2.32 | Module model configuration and its equivalent circuit representation [58].<br>Copyright © by IEEE                                                                                                                                                                              |

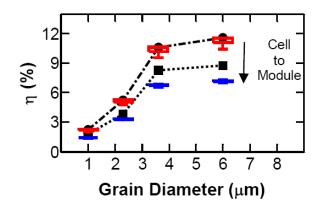

# Figure

| 2.33 Change in the efficiency of CSS CdTe solar cell as the cell size is changed from lab-scale (1 cm <sup>2</sup> ) to module-scale (0.65 m <sup>2</sup> ) [58]. Copyright © by IEEE                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1 Building blocks of a wireless sensor node powered by scavenged solar energy 51                                                                                                                                    |

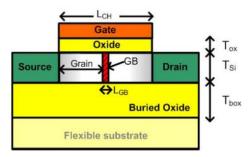

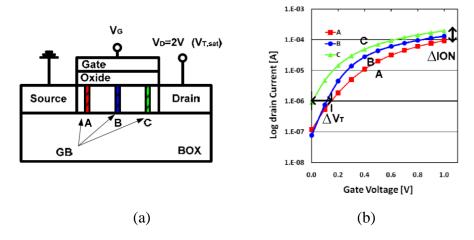

| 3.2 The device structure of the modeled TFT [83]. Copyright © by IEEE                                                                                                                                                 |

| 3.3 2D TFT device structure with a GB at different locations in the channel (a) and the corresponding Id-Vg curves (b) [83]. Copyright © by IEEE                                                                      |

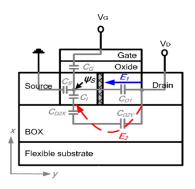

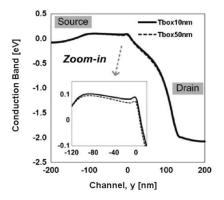

| 3.4 Capacitive network that determines the energy barrier between source and the channel [83]. Copyright © by IEEE                                                                                                    |

| 3.5 Reduction in DIBL effect for thicker BOX thickness ( $T_{BOX}$ ) observed at the conduction band diagram of the proposed TFT ( $V_{GS} = 1$ V and $V_{DS} = 2$ V [84]). Copyright © by IEEE                       |

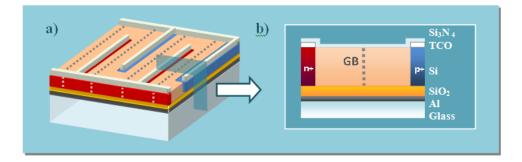

| 3.6 The top view (a) and cross section (b) of the proposed polycrystalline Si solar cell structure                                                                                                                    |

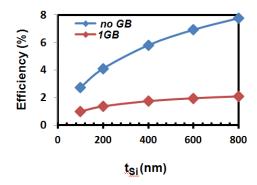

| 3.7 Dependence of cell efficiency on device thickness for a single–crystalline cell (no GB) and a cell with a single GB (1GB) [91]. Copyright © by IEEE 60                                                            |

| 3.8 Change in the performance metrics of the proposed solar cell with respect to the position of a single GB [The results are normalized with respect to the minimum value for that metric] [91]. Copyright © by IEEE |

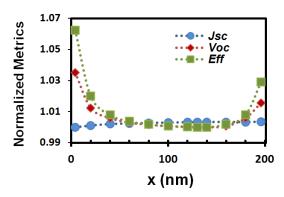

| 3.9 The open circuit voltage (V <sub>OC</sub> ) and efficiency of a 1 cm <sup>2</sup> polycrystalline Si solar cell with respect to the average grain size [91]. Copyright © by IEEE                                  |

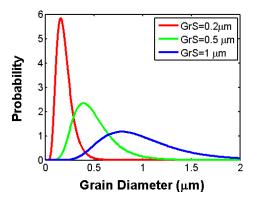

| 3.10 Lognormal grain size (GrS) distributions of processes with different average<br>GrSs                                                                                                                             |

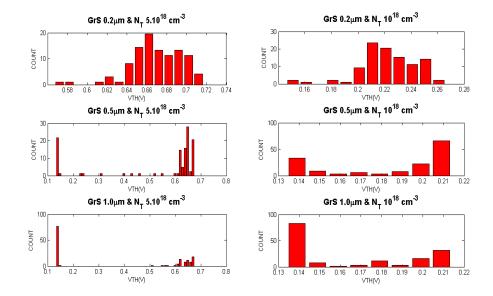

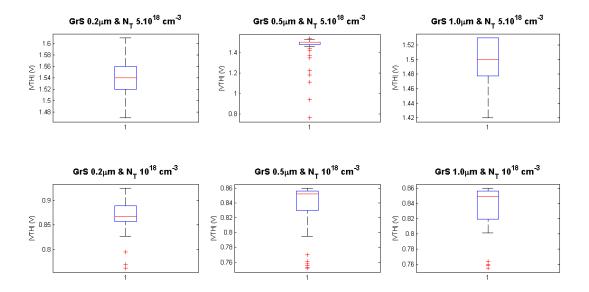

| 3.11 Threshold voltage (V <sub>TH</sub> ) distribution of nTFTs for different trap densities (N <sub>T</sub> s) and grain sizes (GrSs)                                                                                |

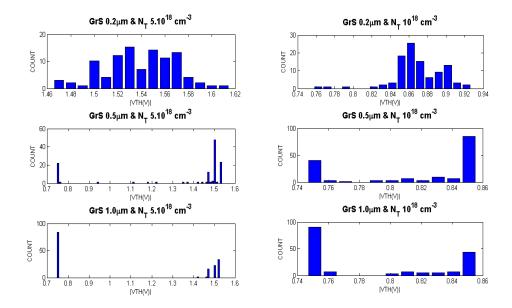

| 3.12 Threshold voltage (V <sub>TH</sub> ) distribution of pTFTs for different trap density (N <sub>T</sub> s) and grain sizes (GrSs)                                                                                  |

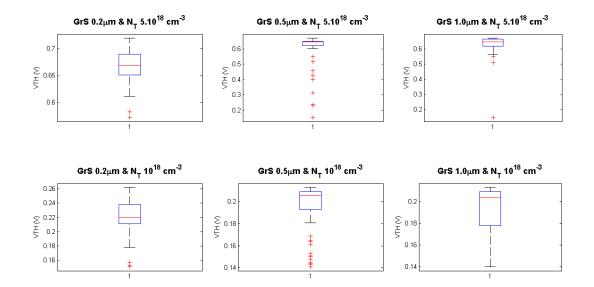

| 3.13 Boxplot of threshold voltages for nTFTs with different trap densities (N <sub>T</sub> s) and grain sizes (GrSs)                                                                                                  |

| 3.14 Boxplot of threshold voltages for pTFTs with different trap densities (N <sub>T</sub> s) and grain sizes (GrSs)                                                                                                  |

Page

# Figure

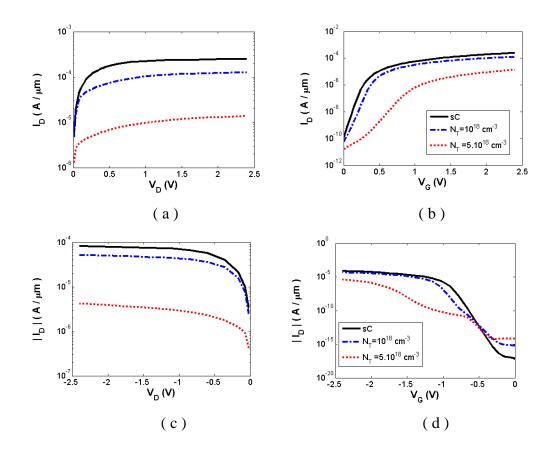

| 3.15 | Id-Vd ( Vg =2.4V) and Id-Vg curves ( Vd =2.4V) of nTFT (a-b) and pTFT (c-d) [source is grounded]                                                                                                                                                                                          | 71 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

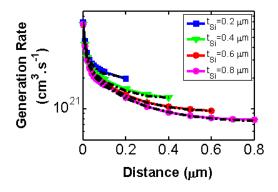

| 3.16 | Generation profiles for the proposed device obtained with the empirical model (colored solid lines) and numerical model (black dashed lines) [97]. Copyright © by ACM                                                                                                                     | 73 |

| 3.17 | Comparison between 1D MATLAB model and 2D Sentaurus results for the proposed solar cell for the cases when there is no GB (sC), 1 GB at $W_{SC}/4$ distance away from the n+ region (1GB) and 2 GBs placed $W_{SC}/4$ distance away from the n+ and p+ regions (2GB) [ $W_{SC}$ =200 nm ] | 74 |

| 3.18 | Width dependency of the proposed solar cell's efficiency for different lifetimes and cases when there is no GB (sC) and 1 GB at $W_{SC}/4$ distance away from the n+ region (1GB) [T <sub>Si</sub> =0.8 µm]                                                                               | 75 |

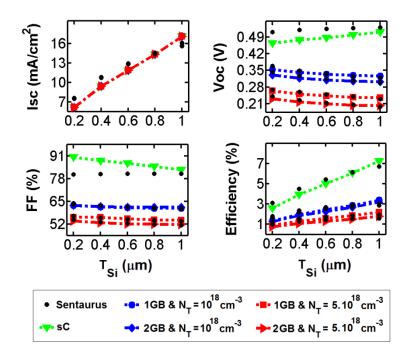

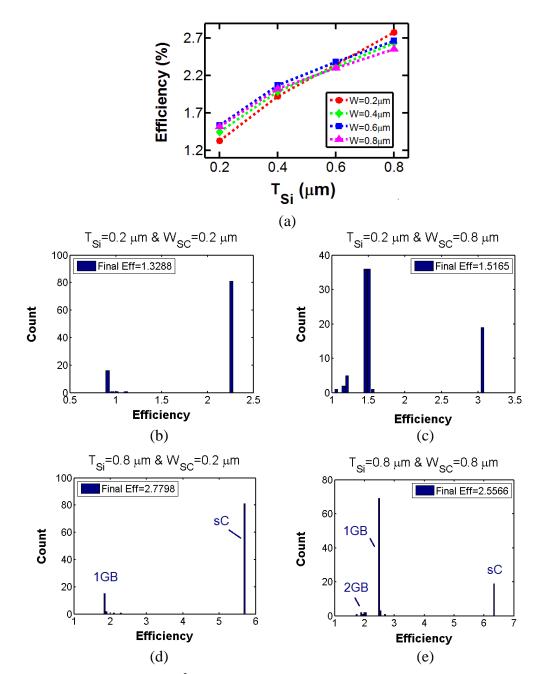

| 3.19 | Efficiency of a 1 cm <sup>2</sup> solar cell (a) and efficiency distributions for its unit cells (b-e) for different $W_{SC}s$ and $T_{Si}s$ [N <sub>T</sub> =5.10 <sup>18</sup> cm <sup>-3</sup> , average GrS=1µm]                                                                      | 76 |

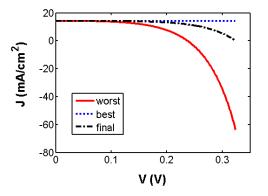

| 3.20 | J-V curves under illumination for best and worst unit cells and the final 1 cm <sup>2</sup> cell. [W <sub>SC</sub> =0.2 $\mu$ m, T <sub>Si</sub> =0.8 $\mu$ m, average GrS=1 $\mu$ m]                                                                                                     | 77 |

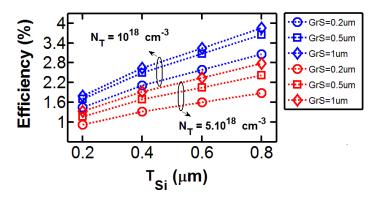

| 3.21 | Impact of GrS and $N_Ts$ on the efficiency of the proposed 1 $cm^2$ solar cell. $[W_{SC}{=}0.2~\mu m].$                                                                                                                                                                                   | 77 |

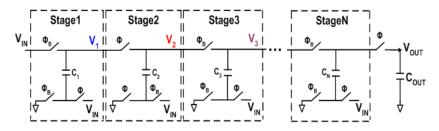

| 3.22 | N-stage linear charge pump with gate control [97]. Copyright © by IEEE                                                                                                                                                                                                                    | 78 |

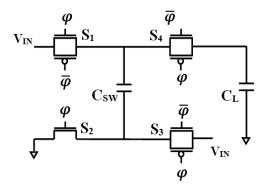

| 3.23 | Single stage charge pump topology                                                                                                                                                                                                                                                         | 79 |

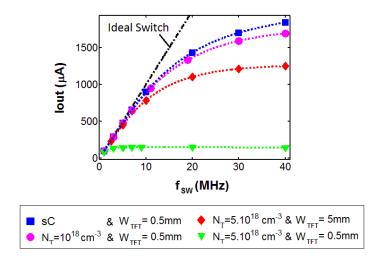

| 3.24 | Output of a single stage linear charge pump for different TFT models                                                                                                                                                                                                                      | 80 |

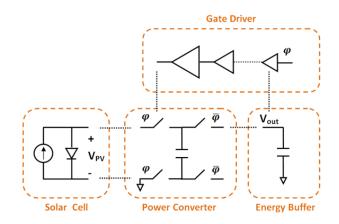

| 3.25 | Schematic of the energy scavenging system                                                                                                                                                                                                                                                 | 82 |

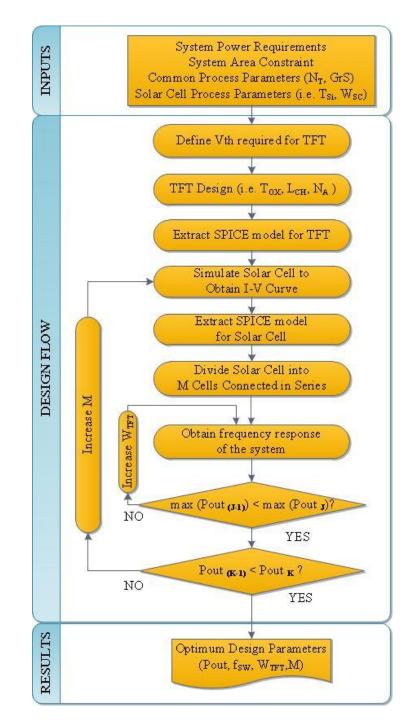

| 3.26 | Micro-scale energy scavenging system design flow                                                                                                                                                                                                                                          | 83 |

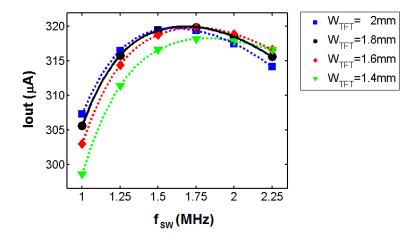

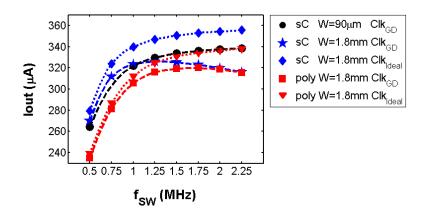

| 3.27 | System net output current for different W <sub>TFT</sub> s fabricated with the "Worst" process. [M=7]                                                                                                                                                                                     | 84 |

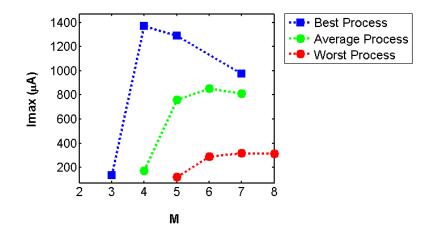

| 3.28 | Best possible output current $(I_{MAX})$ of the energy scavenging system with respect to M for different processes                                                                                                                                                                        | 85 |

| 3.29 | System performance improvement due to increase in the GrS and change in the TFT model from polycrystalline (poly) to single-crystalline (sC) [Clock is provided from a gate driver (Clk <sub>GD</sub> ) or an ideal voltage source (Clk <sub>Ideal</sub> )]                               | 87 |

xi

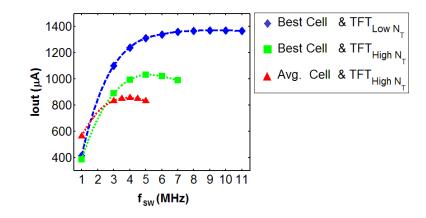

| 3.30 Improvement in system performance due to the increase in $N_T$ of the "Average | "  |

|-------------------------------------------------------------------------------------|----|

| process                                                                             | 88 |

#### ABSTRACT

Mungan, Elif Selin. Ph.D., Purdue University, May 2015. From Process to Circuits: New Perspectives to Solar Cell Design. Major Professors: Kaushik Roy and Muhammad Ashraful Alam.

As the demand for cheap and clean energy sources increased over the last two decades, solar cells have proven to be strong candidates against the fossil fuels. From an economic perspective, in order to replace fossil fuels, it is required to reduce the cost of solar cells. This can be achieved by depositing thinner absorber layers under low process temperatures, yet these efforts lead to poorer efficiency values. Addressing such tradeoffs and providing solutions to this problem have been the main objectives of this study.

In this research, we have approached the aforementioned problem from two distinct approaches. The first one is to look at the correlation between the fabrication conditions and the performance of the cell, while the second one is to investigate the interaction between the solar cell and the power conditioning circuitry. Following our first approach, we started from the deposition conditions of thin films and addressed their effects on the efficiency of the solar cells made out of these films. Using numerical simulations, we were able to identify the effect of various changes in the copper indium gallium diselenide (CIGS) and CdTe solar cells due to deposition conditions. Within the context of our second approach, we demonstrated that the performance of a polycrystalline Si based energy scavenging system can be improved, provided that the optimization for the solar cell and the power conditioning circuitry is done simultaneously. Finally, these approaches were combined to study the effects of process conditions on the device, circuit and system levels.

### **1. INTRODUCTION**

#### 1.1. The Need for a Green Energy Source: Photovoltaics

Since the early  $20^{\text{th}}$  century, the amount of CO<sub>2</sub> released to the atmosphere increased as a byproduct of industrialization process all over the world. This excess CO<sub>2</sub> led to the greenhouse effect, which increased the surface temperature of Earth. With the increase in the fossil fuel consumption, the increase in surface temperature has taken a steeper slope in the last 50 years [1]. This alarming fact underlined the need for alternative energy resources with no or minimum carbon footprint. In addition, fossil fuels are limited resources and the increasing demand for oil reduces the energy independency of the nations while causing conflicts all over the world. From the possible options, sun is the most promising candidate to replace the fossil fuels given the fact that only 0.4% of US land covered with solar cells would be enough to generate the nation's energy demand [2]. Yet, in order to replace fossil fuels, the cost of the generated electricity should be low as well. Even though the solar module prices dropped 57% in the last 10 years [3], the levelized cost of solar energy (\$/kWh) is still higher than that of fossil fuels [4].

As the first and widely used photovoltaic (PV) technology, single-crystalline Si (c-Si) solar cells generally employ high temperature processes and thick Si layers (~400 $\mu$ m) to absorb the whole spectrum of sunlight [5]. In order to reduce the cost of a solar cell, one can reduce the amount of material used or the process temperature during the fabrication. The first approach led to thin film solar cells, which required highly absorptive materials such as CIGS and CdTe to collect all of available the photons. On the other hand, the second approach affected the crystallinity of the materials and led to usage of amorphous, microcrystalline and polycrystalline materials. Although they might not be single-crystalline, thin film solar cells demonstrated efficiency values comparable

to that of c-Si technology as shown in Fig. 1.1. Yet, to compete with a mature technology like c-Si, a deep understanding of these materials is required. Therefore, the focus in this research has been the mechanisms limiting the efficiencies of thin film solar cells, specifically solar cells made out of polycrystalline Si (poly-Si), CdTe and CIGS.

Organic PV (OPV), amorphous and nanocrystalline Si tandem cells (a-Si/n-Si),copper indium gallium diselenide (CIGS), multicrystalline Si (mc-Si), single-crystalline Si (c-Si), and concentrator PV (CPV) with multi-junctions (MJs)

#### **1.2. Fundamentals of Photovoltaics**

#### 1.2.1. Photovoltaic Effect

The solar cells make use of the photovoltaic effect to convert the sun's energy to electricity. The photons coming onto a semiconductor excites an electron from the valence band to the conduction band, leaving a hole behind. Thus, an electron-hole pair is generated which can be collected at contacts in the presence of an electric field. Yet, all photons in the sun's spectrum might not be collected. In order for a photon to excite an electron, it should have energy larger than the bandgap of the absorber material which limits the efficiency of a solar cell. For instance, photons with energies smaller than 1.1eV cannot be collected with a single c-Si cell. In addition, the conduction band minima ( $E_C$ ) and the valence band maxima ( $E_V$ ) of Si do not have the same momentum which makes Si an indirect bandgap material. Because of this bandgap structure, the excitation of an electron from valence band requires the presence of a phonon to occur. Therefore, this event is less likely to happen in Si compared to the direct bandgap materials with aligned  $E_C$  and  $E_V$  such as CIGS and CdTe.

#### 1.2.2. Solar Cell Configurations and Band Diagrams

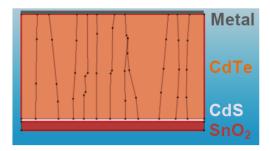

The electric field required to collect the generated electron-hole pairs in a solar cell is generally provided by the built-in voltage of a pn or p-i-n junction. Depending on the electron affinities of materials forming the junction ( $\chi$ s), a homojunction or a heterojunction can form. For instance, polycrystalline Si solar cells are homojunctions (see Fig. 1.2) while CdTe and CIGS solar cells are preferred to be heterojunctions. Since CdTe and CIGS materials are generally p-type materials and are hard to dope, they are coupled with n-type CdS layers which create the heterojunction. In this study, the CIGS solar cells are assumed to be Type I heterojunctions with fully overlapping bandgaps and a positive conduction band offset ( $\Delta E_C$ ) (see Fig. 1.3.b), whereas the CdTe solar cells are assumed to be Type II heterojunctions with staggered bandgaps and a negative  $\Delta E_C$  (see Fig. 1.3.d).

Fig. 1.2 The band diagrams of p and n-type materials before and after they form a homojunction

Fig. 1.3 The band diagrams of p and n-type materials before and after they form: a Type I heterojunction (a, b) and a Type II heterojunction (c, d)

#### 1.2.3. Carrier Transport in Solar Cells

In a polycrystalline homojunction pn diode, the relationship between the charges in a device and the electric field is given by the Poisson equation:

$$\nabla (\epsilon \nabla \varphi) = -q(p - n + N_D + N_A) - \rho_{Trap}$$

(1.1)

where  $\varepsilon$  is electrical permittivity,  $\varphi$  is electrostatic potential, p, n, N<sub>D</sub>, N<sub>A</sub> are densities of holes, electrons, ionized donors and acceptors, and  $\rho_{Trap}$  is the charges at the traps within the device. In non-equilibrium conditions (under bias and/or illumination), the quasi Fermi levels for electrons and holes (F<sub>n</sub>, F<sub>p</sub>) split in the bandgap and determine the carrier densities as:

$$n = n_i e^{(F_n - E_i)/kT} \tag{1.2}$$

$$p = n_i e^{(E_i - F_p)/kT} \tag{1.3}$$

where  $n_i$ ,  $E_i$  and k are the intrinsic carrier density, intrinsic Fermi level and Boltzmann constant. The diode current can be determined from the slope of  $F_n$  and  $F_p$  which gives the following transport equations for electrons:

$$J_n = \mu_n \mathbf{n} \nabla F_n \tag{1.4}$$

$$= q\mu_n n \nabla \varphi + q D_n \nabla n \tag{1.5}$$

where q,  $\mu_n$  and  $D_n$  are the charge, mobility and diffusion constant of electrons. The Equation (1.4) can be extended to be Equation (1.5) in which the carrier transport is described by two competing processes, namely, drift and diffusion mechanisms consecutively. Similar expressions can also be written for hole current density:

$$J_p = q\mu_p p \nabla \Phi_p \tag{1.6}$$

$$= q\mu_p p \nabla \varphi - q D_p \nabla p \tag{1.7}$$

The change in the number of carriers in a diode over time is given by the following continuity equations:

$$\frac{dn}{dt} = \frac{1}{q} \nabla J_n - R_n + G_n \tag{1.8}$$

$$\frac{dp}{dt} = \frac{1}{q} \nabla J_p - R_p + G_p \tag{1.9}$$

where R and G terms stand for recombination and generation rates within the diode. The R term can contain multiple recombination mechanisms. For indirect bandgap materials such as c-Si, Auger recombination mechanisms dominate while it is the radiative recombination mechanism for direct bandgap materials like GaAs [7]. On the other hand, the efficiencies of polycrystalline solar cells are limited by the Shockley-Read-Hall recombination (SRH) occurring at their defective regions or surfaces [8]. In steady state, dn/dt term in Eq. (1.8) becomes zero which leads to the equation for the DC condition.

It should be noted that these sets of equations are valid for homojunctions. Attention should be paid while dealing with heterojunctions since modifications are required to accommodate the change in the  $\epsilon$  value and the abrupt potential change from one material to another [9].

#### **1.2.4. Figure of Merits and Compact Model**

The transport equations set in Section 1.2.3 can be solved to determine the current of a pn diode in dark ( $I_{dark}$ ) and it can be superposed with the generated current under illumination at short circuit conditions ( $I_{Light}$ ) to obtain the I-V characteristics of a solar cell. If the series resistance is negligible, the I-V characteristic in the first quadrant is given by:

$$I = I_{Light} - I_{Dark} \tag{1.10}$$

$$= I_{Light} - I_0(e^{qV/nkT} - 1)$$

(1.11)

where  $I_0$  is the reverse saturation current n is the ideality factor of the diode and V is the applied voltage at the output of the solar cell. A sample I-V curve of a solar cell under illumination is illustrated in Fig. 1.4.a. This I-V curve can be modeled with the compact model shown in Fig. 1.4.b. The model employs a current source to indicate the light generation in the device. A diode in reverse polarity to the current source stands for the  $I_{dark}$ . In addition, this model indicates two parasitic resistances within the device. The first of those is the series resistance ( $R_{ser}$ ) that is due to the resistance of the material between front contacts, the sheet resistance of contacts or recombination in the bulk of the absorber. The second resistance, shunt resistance ( $R_{sh}$ ), indicates the low resistance paths that might have formed between front and back contacts during the deposition. Both resistances are undesired for a high efficiency solar cell since they reduce amount of power delivered to the load. If these parasitic effects are included, Equation (1.11) would become [10]:

$$I = I_{Light} - I_0 \left( e^{\frac{q(V+IR_{Ser})}{nkT}} - 1 \right) - \frac{V+IR_{Ser}}{R_{Sh}}$$

(1.12)

Although this compact model and the related superposition principle holds for thick c-Si solar cells, it generally is not a good fit for thin film solar cells since recombination modeled in  $I_{dark}$  gets strongly coupled with generation mechanism and becomes voltage dependent [11].

Fig. 1.4 Current-voltage and power-voltage characteristics (a) and the compact model (b) of a solar cell.

The performance of a solar cell is determined by four figure of merits shown in Fig. 1.4.a, namely, short circuit current ( $I_{SC}$ ), open circuit voltage ( $V_{OC}$ ), fill factor (FF) and efficiency ( $\eta$ ). The first of these terms,  $I_{SC}$ , indicates the current of the diode at short circuit condition (V=0) under illumination. Since  $I_{dark}$  goes to 0 at V=0,  $I_{SC}$  is found to be equivalent to  $I_{Light}$  from the superposition method in Equation (1.11). If the carrier collection occurs mainly diffusively,  $I_{SC}$  would be given by:

$$I_{SC} = qG(L_e + L_p) \tag{1.13}$$

where Le and  $L_p$  are the diffusion lengths of electrons and holes.

The second figure of merit,  $V_{OC}$ , is the voltage applied on the solar cell for which the  $I_{Light}$  is equal to the  $I_{dark}$  and thus the net current is 0. If the net current (I) is equated to 0 in Equation (1.11),  $V_{OC}$  can be written as:

$$V_{OC} = \frac{nkT}{q} \ln\left(\frac{I_{SC}}{I_0}\right) + 1 \tag{1.14}$$

As it can be observed from Fig. 1.4.a, the power that can be extracted from a solar cell increases as V is increased. Once it reaches the maximum power point (MPP), the power declines due to lack of output current. This maximum point indicated by maximum point current and voltage  $(I_m, V_m)$  is the ideal biasing point of a solar cell and determines

the FF and  $\eta$ . FF indicates the importance of parasitic resistances and can be determined by the ratio :

$$FF = \frac{I_m V_m}{I_{SC} V_{OC}} \tag{1.15}$$

The final and most important figure of merit,  $\eta$ , indicates the efficiency of the solar cell while converting the incoming solar power (P<sub>S</sub>) to electrical power (P<sub>E</sub>).

$$\eta = \frac{P_E}{P_S} = \frac{I_m V_m}{P_S} = \frac{I_{SC} V_{OC} FF}{P_S}$$

(1.16)

In solar cell design, the main goal is to improve the efficiency of the device. To achieve this goal, one can improve the absorption via reducing the reflection on the front surface, introducing direct bandgap materials or higher carrier lifetimes to increase the carrier collection at short circuit condition and therefore the  $I_{SC}$ . If a higher  $V_{OC}$  is desired, one can work with larger bandgap materials that would create a larger built-in voltage. Yet, since the number of photons that can excite an electron in the semiconductor reduces as the bandgap increases, there is an optimum bandgap (~1.35eV for a single junction [12]). Reducing the  $R_{ser}$ , (by reducing the recombination in the bulk) or increasing  $R_{sh}$  (by introducing buffer layers that stop diffusion of metals during contact annealing) improves the FF and therefore the  $\eta$ .

## 2. EFFECTS OF PROCESS CONDITIONS ON THE EFFICIENCY OF CHALCOGENIDE SOLAR CELLS

#### 2.1. Process Technologies for Thin Film Polycrystalline Solar Cells

#### 2.1.1. Polysilicon Solar Cells

Due to its usage in integrated circuits, various fabrication processes have been studied for polycrystalline Si material. For fabrication of solar cells two different approaches can be taken in general. The first approach would be the deposition of the material in one step. As shown in Fig. 2.1, the direct deposition approach starts on a clean substrate. Later on, initial particles stick to the surface and start the nucleation process. Later on, the incoming particles stick to regions close to these nucleation centers. By the time the surface is filled, each nucleation center will have a crystal formed around them which are called as "grains". For this method, the control of the initial nucleation phase is critical since the size of the initial nuclei determines the size of the crystals inside the material. If the initial nuclei radius is too small, then the grains grow to be small too. On the other hand, if the initial nuclei are few and large in size, it will be harder to obtain a continuous film [13].

To avoid the problem of controlling the initial nucleation phase, a second approach can be taken in which the material is deposited on a high quality thin film called as the "seed". The seed layer can be made by laser annealing of an amorphous Si layer (Excimer laser annealing (ELA) [14], sequential lateral solidification (SLS) [15]) or by using metals to induce nucleation sites (metal induced lateral crystallization (MILC) [16]) which would lead to larger grain sizes (GrSs). These processes are widely used for thin film transistor (TFT) fabrication, yet they get less feasible with an increase in film thickness. Thus, for solar cell fabrication these processes are generally used to form the seed layer and the rest of deposition is done with another epitaxial method.

Fig. 2.1 Nucleation (a) and growth (b) process of polycrystalline Si fabricated with atmospheric pressure CVD. Grains would be seen as in (c) under a microscope [17]. Copyright © by John Wiley & Sons<sup>1</sup>

There is a wide range of epitaxial methods that can be used to deposit the bulk of the solar cell. From these methods, chemical vapor deposition (CVD) works well with the seeding approach. The deposition process for this method involves the chemical reactions between the different gases (precursors) and the surface at high temperatures (around 800 to 1200 C°). Generally silane (SiH<sub>4</sub>) precursor is used for polycrystalline Si deposition. A uniform film can be achieved using this method and when it is used with direct deposition approach, the microstructure in Fig. 2.1.c can be obtained.

#### 2.1.2. Polycrystalline CIGS Solar Cells

The highest efficiencies for CIGS solar cells are obtained with the co-evaporation process technology. In this technology, all elements in the compound are evaporated simultaneously. Three variations of this approach are illustrated in Fig. 2.2. The main difference between these processes is the change in the Cu flux and substrate temperature during the deposition. Bilayer and 3-stage processes make use of the fact that Cu rich process step provides larger GrSs. In [18], Cu<sub>x</sub>Se formation during growth is claimed to enlarge the grains and make the film more uniform. On the other hand in the bilayer process, the film is made Cu-rich at the first step and Cu-poor at the second. By doing this, excess  $Cu_x$ Se layer can be turned into CIGS and a relatively uniform Cu

<sup>&</sup>lt;sup>1</sup> From Poortmans & Arkhipov, <u>Thin Film Solar Cells Fabrication, Characterization and Applications</u>, 1st Edition. Copyright © 2006 by John Wiley & Sons, Inc. Reprinted by permission of John Wiley & Sons, Inc.

composition can be achieved throughout the device. In 3-stage process an initial Cu-poor layer is incorporated along with additional Ga grading which introduces a second bandgap grading in the device due to the change in the mole fraction of Ga in the film.

Fig. 2.2 Three variations of co-evaporation process used for CIGS solar cells [19]. Copyright © by John Wiley & Sons<sup>2</sup>

Fig. 2.3 Cross-section (a) and top view (b) of the CIGS sample fabricated with 3-stage process [20]. Copyright © by John Wiley & Sons<sup>3</sup>

<sup>&</sup>lt;sup>2</sup> From Romeo et al., <u>Development of Thin-film Cu(In,Ga)Se2 and CdTe Solar Cells</u>, Progress in Photovoltaics, Vol. 12, Iss. 2-3. Copyright © 2004 by John Wiley & Sons, Inc. Reprinted by permission of John Wiley & Sons, Inc.

<sup>&</sup>lt;sup>3</sup> From Ramanathan et al., <u>Properties of 19.2% Efficiency ZnO/CdS/CuInGaSe2 Thin-film Solar Cells</u>, Progress in Photovoltaics Vol. 11, Iss. 4. Copyright © 2003 by John Wiley & Sons, Inc. Reprinted by permission of John Wiley & Sons, Inc.

In Fig. 2.3, the microstructure of the CIGS films fabricated with 3-stage process indicate the high quality of the material. The sizes of the individual crystals are significantly larger (~um) compared to other process technologies.

#### 2.1.3. Polycrystalline CdTe Solar Cells

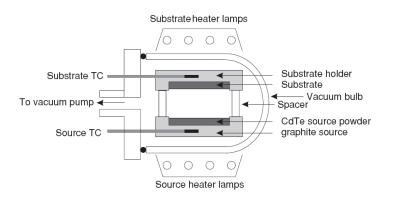

There are two variations of the same method that provide the highest efficiencies for CdTe solar cells [21]. The method is based on the evaporation of the substrate material (~600C), which can be CdTe compound or a stoichiometric mixture of Cd and Te onto a substrate that is spaced very close (mm to cm) to the source. If the chuck of the substrate is kept at a slightly lower temperature (~450C), the process is called close space sublimation (CSS). If the material transport is sustained by an inert gas, it is called as vapor transport deposition (VTD). An illustration of the deposition chamber for CSS is provided in Fig. 2.4 [21].

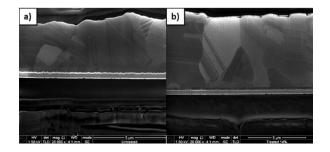

Another important aspect of the CdTe deposition is the post-treatment of samples with CdCl<sub>2</sub>. The samples are annealed at temperatures from 300 to 600 C° in Cl-O ambient and an increase in the GrS is observed as in Fig. 2.5 [22]. For samples fabricated at lower temperatures, this increase would be more dramatic.

Fig. 2.4 Deposition setup for close space sublimation (CSS) process [21]. Copyright © by John Wiley & Sons<sup>1</sup>

Fig. 2.5 The cross-section of CdTe samples fabricated with CSS process. Before and after CdCl<sub>2</sub> treatment [22]. Copyright © by John Wiley & Sons<sup>4</sup>

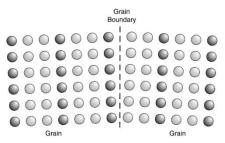

#### 2.2. Grain Boundaries

As their name indicates, polycrystalline materials have multiple crystalline sections called as "grains". Each of these grains has a different crystallographic orientation and the regions (generally planes) where these sections meet are called as grain boundaries (GBs) as shown in Fig. 2.6.

Fig. 2.6 Grain boundaries as planar defects [23]. Copyright © by John Wiley & Sons <sup>5</sup>

There are several ways that a GB can form. The simplest possibility is to have a grain that is rotated around an axis on a plane parallel to the GB plane. This type of GB is called as the tilt GB. On the other hand, if the rotation axis is perpendicular to the boundary plane, the twist GBs are formed.

<sup>&</sup>lt;sup>4</sup> From Major et al., <u>Focussed ion beam and field emission gun-scanning electron microscopy for the investigation of voiding and interface phenomena in thin-film solar cells</u>, in Progress in Photovoltaics, vol. 20, Iss. 7. Copyright © 2012 by John Wiley & Sons, Inc. Reprinted by permission of John Wiley & Sons, Inc.

<sup>&</sup>lt;sup>5</sup> From Tilley, <u>Extended Defects</u>, Defects in Solids. Copyright © 2008 by John Wiley & Sons, Inc. Reprinted by permission of John Wiley & Sons, Inc.

The misorientation between the grains is generally indicated with the rotation angle  $(\theta)$ . Depending on the value of  $\theta$ , the GBs are categorized to be low or high angle. In the case of a tilt GB, if the GB is low angle, it can be described as an array of edge dislocations which are the discontinuities in the crystal structure. The distance between the edge dislocations (D) is given by:

$$D = \frac{b}{2\sin(\theta/2)} \approx \frac{b}{\theta}$$

(2.1)

where b is the Burgers vector, which indicates the direction and magnitude of the misorientation. As  $\theta$  grows larger, D reduces such that the dislocations overlap and become indistinguishable for high angle GBs. The transition from low to high angles generally occur around  $\theta = \sim 15^{\circ}$  [24].

#### 2.2.1. Grain Size Measurement Techniques and Distribution

A polycrystalline material's quality is generally measured by its average GrS. Therefore, there are several ways to measure this figure of merit. The simplest method is lineal intercept technique [25], which includes drawing a line on the micrograph of the film and counting the number of grains that line intercepts ( $N_L$ ). The mean lineal intercept would be the average distance between GBs and would be expressed as:

$$\bar{l} = \frac{L}{N_L M} \tag{2.2}$$

where L is the length of the drawn line and M is the magnification magnitude. This procedure should be repeated for multiple lines to obtain a statistically sound value.

The second method is devised by American Society of Testing and Material (ASTM) which includes counting the number of grains in 1 inch<sup>2</sup> samples which are magnified at 100x. The number of grains (N) is converted to the standardized GrS number (n) using:

$$N = 2^{(n-1)} \tag{2.3}$$

Once n is found, the user can refer to the sample charts prepared by ASTM and determine the average GrS of the sample.

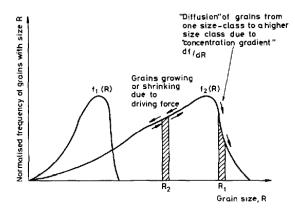

Besides average GrS, the distribution of the measured GrSs is an important data for polycrystalline materials. Based on this data, one can comment on the growth process and do performance variation analysis. Experimentally observed GrS distributions do generally have a tail which is due to the change in GrS and number during the film growth as shown in Fig. 2.7. Starting from the initial distribution at t=0 ( $f_1$ ) the distribution grows to be  $f_2$  over time and two simultaneous mechanisms in grain growth is illustrated in this figure. First, the grains in range  $R_1$  can grow due to a diffusion-like process given that there is a concentration gradient at the GB. On the other hand, the grains in range  $R_2$  can either increase or decrease due to a field dependent mechanism caused by a driving force such as the change in GB curvature [26].

Fig. 2.7 The change in the GB size distribution tail over time [26]. Copyright © by Elsevier <sup>6</sup>

Historically, the GB size distributions are fitted with lognormal distribution, yet it is not found to be a good fit universally. In [26], it is found that the two mechanisms mentioned above causes a distribution peak sharper than lognormal which is more in line with the experimental data.

Although the theoretical works are mainly done on single-element metals, the GrS distributions for alloys and compounds follow a similar trend and data are readily available for CdTe and CIGS materials [27] [28]. Fig. 2.8.a indicates an increase in the average GrS with CSS CdTe film thickness. The distributions of the GrSs observed from the top of the sample at two different film thicknesses are provided in Fig. 2.8.b. These distributions are found to be Rayleigh distributions [27].

<sup>&</sup>lt;sup>6</sup> Reprinted from <u>Acta Metallurgica</u>, Vol. 3, Iss. 3, Atkinson et al., Theories of Normal Grain Growth in Pure Single Phase Systems, Pages 469-491, Copyright (1988), with permission from Elsevier.

Fig. 2.8 The average grain size of *CSS* CdTe films with respect to measurement depth (a) and the grain size distributions of the films at two different depths (b). An illustrative top-view image of CdTe film (c) and the distribution for the number of grain centroids in a given area (d) [27]. Copyright © by Elsevier <sup>7</sup>

Instead of measuring the GrS, one can look into the number of grains in a given area. In Fig. 2.8.d, the distribution for the number of grain centroids in a given area is shown for the same CdTe sample. This distribution is fitted with a Poisson distribution indicating that the occurrence of grains in an area is a random-like process. The GrS distribution for CIGS reported in [28] differs from the CdTe sample discussed previously and follows a lognormal distribution. In addition, the deposition temperature is found to affect the distribution such that the mean GrS shifts to larger values at higher temperatures as the variation in GrS increases.

<sup>&</sup>lt;sup>7</sup> Reprinted from <u>Thin Solid Films</u>, Vol. 361-362, Cousins et al., Grain structure of CdTe in CSS-deposited CdTe/CdS solar cells, Pages 253-2571, Copyright (2000), with permission from Elsevier.

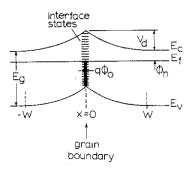

#### 2.2.2. Effects of Grain Boundaries on Device Performance

Since GBs are considered to be arrays of dislocations, they tend to trap free carriers. Based on the type of defects, these traps can be charged which changes the potential near the GB position. If the trap is acceptor-like, it would be neutral when unoccupied and it would be negatively charged when occupied by an electron. On the other hand, if the trap is donor-like, the unoccupied trap would be positively charged, while the occupied trap would be neutral. These traps are generally represented with an energy level in the bandgap and act as the recombination centers. In a real material, it is possible to have multiple traps with different energy levels. In that case, one can define a neutral energy level which indicates the net charge along that GB [29]. For instance for the band diagram in Fig. 2.9, the positively charged donor-like traps are compensated by negatively charged acceptor-like traps which resulted in a negative charge along the GB. To maintain the charge neutrality, the energy band at GB position bend upwards, leading to an energy barrier that limits the carrier transport in this n-type material. This barrier affects the subthreshold slope in TFTs, while its effects are rather complex in solar cells and will be discussed in the following sections.

Fig. 2.9 The band diagram of a negatively charged GB in an n-type semiconductor [29]. Copyright © by IEEE <sup>8</sup>

Although the atomic forces exist over the GBs, the atoms along them are loosely connected to each other. These unsatisfied bonds create a surface energy along the GB. For high angle GBs, this energy is higher. Due to this surface energy, GBs are

<sup>&</sup>lt;sup>8</sup> © 1977 IEEE. Reprinted with permission from Card et.al, Electronic Processes at Grain Boundaries in Polycrystalline Semiconductors Under Optical Illumination, IEEE Transactions on Electron Devices, 1977.

chemically more active than the bulk of the grains [30] which leads to the gettering of impurities along the GBs [31]. The dislocations on the GBs generally attract impurities like metals which might be useful in some cases. The passivating properties of Na along the GBs would be a good example. In [32] it is claimed that for polycrystalline CIGS, following the procedure in [32], Na acts as a catalyzer during the adsorption process of  $O_2$  which takes the place of the Se vacancies and passivates these defects. On the other hand, the Cu diffusion along the GBs from the back contact to the front of the device in a CdTe solar cell is found to be degrading the reliability of the product over time [33].

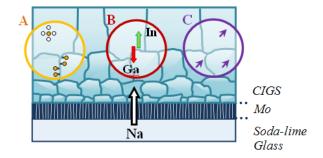

Fig. 2.10 Experimentally observed changes in CIGS due to Na diffused from the substrate: (A) Increased carrier density, (B) Ga segregation and (C) Change in crystal orientation [34]. Copyright © by IEEE <sup>9</sup>

#### 2.3. Effects of Na on the Efficiency of CIGS Solar Cells

As it is discussed in Section 1.1, CIGS and CdTe are promising materials for high performance thin film photovoltaics. Therefore in the following sections, CIGS and CdTe solar cells are going to be taken under investigation. Particularly for this section, the relationship between the CIGS cell performance with its Na content is going to be studied. It has been experimentally observed that Na diffusing from the soda-lime glass substrate causes an increase in the CIGS cell efficiency [35]. Yet, there is not a consensus on a mechanism that explains how Na affects the cell efficiency.

In literature, Na is observed to (a) increase the carrier density [36] [37], (b) cause segregation of Ga towards the Mo back contact [38] [39], (c) increase the number of

<sup>&</sup>lt;sup>9</sup> © 2013 IEEE. Reprinted with permission from Mungan et.al, Modeling the Effects of Na Incorporation on CIGS Solar Cells, IEEE Journal of Photovoltaics, 2013.

<112> oriented grains [40] [41] (see Fig. 2.10). Given that these observations can occur simultaneously in a real device, it would be hard to distinguish the effects of one from the others. Therefore, the numerical simulation framework in Section 2.3.1 is proposed to investigate each observation and their potential effects on the efficiency of the CIGS cell.

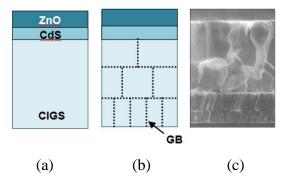

Fig. 2.11 Single-crystalline (a) and polycrystalline (b) structures used in the simulations. (c) SEM image of the CIGS solar cell in Fig. 2.3.a [34]. Copyright © by IEEE <sup>9</sup>

#### **2.3.1. Simulation Framework**

The simulation framework required to study the effects of Na incorporation is constructed in a commercial 2D/3D device simulator called Sentaurus [42]. Within this framework, TCAD models are developed for a single-crystalline and a polycrystalline CIGS solar cell as in Fig. 2.11. Both models are composed of CIGS, CdS and ZnO layers as the absorber, buffer and window layers respectively. Both devices are set to be 1  $\mu$ mwide, whereas the thickness of each aforementioned layer is 3  $\mu$ m, 50 nm and 200 nm respectively. The material parameters are adopted from [43]. For instance, the bandgap of CIGS is chosen to be 1.15eV and the affinity difference between CIGS and CdTe is assumed to be 0.3 eV. CIGS absorber is set to be p-type with a doping level of  $2x10^{16}$  cm<sup>-</sup> <sup>3</sup> and its bulk trap density is fixed to be  $10^{14}$  cm<sup>-3</sup>. The simulations are conducted under standard terrestrial solar spectrum (AM 1.5), whereas 5% and 80% reflectance are assumed at the front and back contacts of the device. The polycrystalline model is formed by placing GBs in the single-crystalline model. Idealized Manhattan geometry is employed to model the grains in the polycrystalline model in Fig. 2.11.b and the GrSs are enlarged towards the CdS layer to make the model similar to the SEM image of the reallife device in Fig. 2.11c [20].

Table 2.1 Parameters used to model GB trapped charge density ( $N_T$ ) [a] and surface recombination velocity ( $s_R$ ) [b] with different trap models [34]. Copyright  $\bigcirc$  by IEEE <sup>9</sup>

Trap energy level ( $E_T$ ), trap density at shallow and midgap energy levels ( $N_{TS}$  and  $N_{TM}$ ), capture cross section for electrons and holes ( $\sigma_e$ ,  $\sigma_h$ ), conduction and valence band edge energies ( $E_C$ ,  $E_V$ ).

|                       | E <sub>T</sub> (eV) | $N_{TS}$ (cm <sup>-2</sup> ) | $\sigma_{e}(cm^{2})$ | $\sigma_h(cm^2)$             |

|-----------------------|---------------------|------------------------------|----------------------|------------------------------|

| Neutral               | Midgap              | 0                            | 10 <sup>-18</sup>    | 10-18                        |

| Acceptor              | Ev+0.1              | $4.5 \times 10^{11}$         | 10 <sup>-18</sup>    | 10 <sup>-18</sup>            |

| Donor                 | Ec-0.2              | $4.5 \times 10^{11}$         | 10 <sup>-18</sup>    | 10 <sup>-18</sup>            |

|                       |                     | [a]                          |                      |                              |

| s <sub>R</sub> (cm/s) | E <sub>T</sub> (eV) | $N_{TM}$ (cm <sup>-2</sup> ) | $\sigma_e(cm^2)$     | $\sigma_{\rm h}({\rm cm}^2)$ |

| $10^3 - 10^6$         | Midgap              | $10^4 - 10^7$                | 10-8                 | 10 <sup>-8</sup>             |

|                       |                     | [b]                          |                      |                              |

The GBs are modeled with defective interfaces. Following Ref. [43], four possible trap types are considered to model those defects: (a) neutral traps, (b) acceptor-like traps, (c) donor-like traps with no valence band discontinuity, and (d) neutral traps in a valence band shifted region. For charged traps, recombination velocity ( $s_R$ ) and trapped charge density ( $N_T$ ) of a GB is studied independently from each other.  $s_R$  is considered to be determined by midgap trap states with large capture cross-sections ( $\sigma$ ), whereas  $N_T$  is controlled by the shallower trap states with small  $\sigma$ s. The last trap type mentioned above is considered to be due to the Cu depletion around the GB region [44]. Therefore, it is modeled with a 20 nm-wide region around a neutral GB and only the valence band energy ( $E_V$ ) of the material in this region is shifted down by 0.2 eV. As in Table 2.1, the trap density of shallow traps ( $N_{TS}$ ) is chosen to be 4.5x10<sup>11</sup> cm<sup>-2</sup> since it is the worst case scenario for a device with the parameters selected in this section.  $N_{TS}$  values higher than

$4.5 \times 10^{11}$  cm<sup>-2</sup> create a highly inverted region around the GB that limits the number of holes and therefore the recombination at the GB [43].

$\sigma$  for electrons and holes ( $\sigma_{e,} \sigma_{h}$ ) at shallow traps are assumed to be  $10^{-18}$  cm<sup>-2</sup> so that they create an energy barrier at the GB but do not contribute to the carrier recombination ( $s_{R} < 10$  cm/s). On the contrary,  $10^{-8}$  cm<sup>-2</sup> is used for  $\sigma_{e,}$  and  $\sigma_{h}$  of midgap traps and their trap density ( $N_{TM}$ ) is varied to keep  $s_{R}$  between  $10^{3}$ - $10^{6}$  cm/s. This reduction in trap density towards the midgap is considered to be a valid assumption since it is observed to be common for various materials [45].

#### 2.3.2. Analysis of Possible Improvement Mechanisms

In this subsection, the aforementioned changes in the CIGS absorber layer with Na incorporation are going to be replicated in the simulation environment and their effects on the CIGS cell performance is going to be investigated independently.

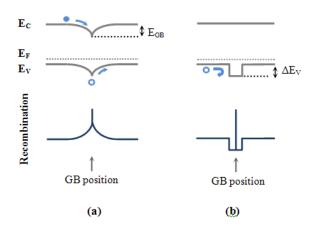

#### 2.3.2.1. Observation 1: Increase in the Carrier Density

As the first observation to be studied, the increase in the carrier density is replicated in the simulation environment using the polycrystalline structure in Fig. 2.11.b. The performance of this structure is evaluated for various GB models and  $s_Rs$  to explore how much GB passivation can improve the cell performance. As the results in Fig. 2.12 indicate, the degradation in the cell performance is worst for GBs with donor-like traps with no discontinuity in the valence band (solid red line with triangles). This observation can be explained by the downward band bending at the GB position as shown in in Fig. 2.13.a. Due to the positive charges at the GB in a p-type CIGS, a downward band bending ( $E_{GB}$ <0) that attracts minority carriers (electrons) occurs in the device. As more minority carriers are attracted to the GB, electron and hole concentrations get closer to each other and SRH recombination at the GB is increased. This increase in the GB recombination is found to cause a significant reduction in performance metrics (short circuit current density ( $J_{SC}$ ),  $V_{OC}$ , FF and efficiency) as shown in Fig. 2.12.

(◆) Neutral trap in a valence band shifted region (△E<sub>V</sub>=0.2eV)

(◆) Acceptor-like traps

(◆) Neutral traps

(◆) Donor-like traps with N<sub>TS</sub> = 4x10<sup>11</sup> cm<sup>-2</sup>

(◆) Donor-like traps with N<sub>TS</sub> = 4.5x10<sup>11</sup> cm<sup>-2</sup>

Fig. 2.12 Performance of a polycrystalline CIGS solar cell with respect to GB recombination velocity (s<sub>R</sub>) and GB model [34]. Copyright © by IEEE <sup>9</sup>

Since there is no band bending for neutral GBs, the GB recombination remains low and performance degradation with  $s_R$  is subtle (black squares in Fig. 2.12). As for the GBs with acceptor-like traps (blue circles in Fig. 2.12), the GB is charged negatively which leads to an upward band bending ( $E_{GB}>0$ ). Therefore, the minority carriers are repelled from the GB and the recombination at the GBs is minimized. Finally, for the GBs modeled with neutral traps in a valence band shifted region (magenta diamonds in Fig. 2.12), the band diagram looks like Fig. 2.13.b. The holes are repelled from the region due to the barrier at the valence band, whereas electrons are not affected. Provided that the shift in the valence band ( $\Delta E_V$ ) is large enough, the region around the GB can be inverted to the extent that the recombination is limited by the number of holes at the GB. The  $\Delta E_V$  due to Cu depletion in CIGS can go up to 0.4 eV [44]. The results for this type GBs in Fig. 2.12 are obtained for a  $\Delta E_V$  of 0.2 eV which is found to be large enough to reduce the GB recombination significantly. The results in Fig. 2.12 can be used to estimate a possible improvement in CIGS cell performance due to GB passivation. For instance, if the trap type at a GB with an  $s_R$  of  $10^5$  cm/s changes from donor-like traps to neutral traps, its efficiency can improve by ~11%. On the other hand, if the N<sub>TS</sub> of donor-like traps at the GB is low, the improvement margin would be lower as well. For this purpose, results for a second N<sub>TS</sub> are provided Fig. 2.12 (dotted red line with triangles). If the N<sub>TS</sub> was  $4x10^{11}$  cm<sup>-2</sup>, the improvement margin would have reduced to 4%. From a different perspective, only the midgap trap states could be passivated which would reduce the  $s_R$ . If GB  $s_R$  is improved from  $10^6$  cm/s to  $10^3$  cm/s, the efficiency of a device whose GBs are modeled with donor-like traps and N<sub>TS</sub> =  $4.5x10^{11}$  cm<sup>-2</sup> (solid red line with triangles in Fig. 2.12) can improve by ~13%. Note that, in this analysis  $s_R$  and N<sub>T</sub> are isolated from each other. Yet, an annealing process might reduce the trap densities related to both  $s_R$  and N<sub>T</sub> which would further improve the efficiency.

Fig. 2.13 Energy band diagrams and recombination rates at GBs modeled with: (a) Donor-like traps with no valence band discontinuity (b) Neutral traps within a valence band shifted region [34]. Copyright © by IEEE <sup>9</sup>

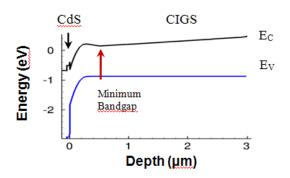

## 2.3.2.2. Observation 2: Change in Ga Distribution

As the second change in the CIGS material properties with Na incorporation, Ga segregation towards the Mo back contact is investigated in this subsection. In the presence of Na, the interdiffusion between Ga and In decreases and Ga diffuses towards

the back of the device. Since Ga concentration ([Ga]) determines the bandgap of CIGS, this leads to the double graded band diagram in Fig. 2.14 [38], [39]. To explore the impact of this change, the mole fraction of Ga within the single-crystalline and polycrystalline CIGS cell structures in Fig. 2.11.a and Fig. 2.11.b is graded. For ease of comparison,  $N_{TS}=4x10^{11}$  cm<sup>-2</sup> is used in this part of the study. The optical material parameters and dependence of the CIGS bandgap on [Ga] is taken from [46] and [47].The  $E_V$  of CIGS is kept fixed and the change in the bandgap is reflected only to electron affinity. [Ga]/[Ga+In] ratio is set to be 0.3 and 0.5 at the CdS/CIGS and CIGS/Mo interfaces respectively [20]. Afterwards, the ratio is varied at 500 nm away from the CdS/CIGS junction (minimum bandgap point in Fig. 2.14). The formula of the CIGS is assumed to be CuIn<sub>(1-x)</sub>Ga<sub>x</sub>Se for this analysis.

Fig. 2.14 Energy band diagram of the double graded single-crystalline CIGS solar cell [34]. Copyright © by IEEE <sup>9</sup>

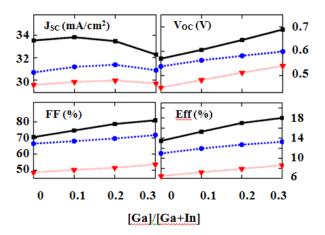

As shown in Fig. 2.15, the performance of both single-crystalline and polycrystalline cells are found to be reduced as the Ga mole fraction (and therefore the bandgap) is reduced at the minimum bandgap point. The reduction in Ga leads to smaller effective bandgap for CIGS (thus reduces the  $V_{OC}$ ) and increases the absorption (thus increases the J<sub>SC</sub>) of the cell. The reduction in  $V_{OC}$  is found to be more pronounced which causes the reduction in the efficiency. In polycrystalline cells, the  $V_{OC}$  is already suppressed by the GB recombination. Hence, the reduction in efficiency with the reduction in [Ga]/[Ga+In] is subtle for the polycrystalline structures. If existence of Na reduces [Ga]/[Ga+In] from 0.3 to 0.2 as in [20], the efficiency is expected to be reduced by 1% for single-crystalline

cell. For a polycrystalline cell, this reduction would be 0.58% or 0.71%, if its GBs are modeled with neutral traps or donor-like traps respectively.

(→) Single-crystalline

(→) Polycrystalline with neutral traps

(▼) Polycrystalline with donor-like traps & N<sub>TS</sub>=4x10<sup>11</sup> cm<sup>-2</sup>

#### 2.3.2.3. Observation 3: Change in Crystal Orientation

The increase in the number of <112> oriented grains with Na incorporation [40] [41] can affect the CIGS in two different ways: (a) the Cd diffusion from the CdS layer into CIGS is reduced for <112> oriented grains [48], (b) crystalline order and therefore the mobility of CIGS might increase. In the following subsections, the effects of these two methods on the performance of the CIGS solar cell are explored.

# 2.3.2.3.1 Reduced Cd Doping from CdS Layer

To observe the effect of Cd diffusion into the CIGS layer, an n-type CIGS layer is created between the n-type CdS and p-type CIGS layers while keeping the cell thickness fixed. Afterwards, the performance of the single-crystalline CIGS cell is monitored for different Cd doping depths and concentrations. The results in Fig. 2.16 demonstrate an increase in  $J_{SC}$  and FF due to the improved electric field introduced by the homojunction in CIGS layer. Given that the efficiency of the CIGS cell increases with Cd doping and

<112> oriented grains allow less Cd diffusion, the CIGS cell would suffer from an efficiency loss due to Na incorporation. Fortunately, this loss would be around 0.5% since a typical homojunction depth is around 80 nm [49].

Fig. 2.16 Performance of CIGS solar cell with respect to homojunction position and doping density ( $N_{Cd}$ ) of the Cd diffused n-type CIGS layer [34]. Copyright © by IEEE <sup>9</sup>

## 2.3.2.3.2 Increase in the mobility

As a possible consequence of the increase in the <112> oriented grains, the mobility of the CIGS layer might increase with Na incorporation. To investigate the extent of improvement that can be obtained with higher mobility values, mobility values for electrons ( $\mu_e$ ) and holes ( $\mu_p$ ) are varied for both single-crystalline and polycrystalline CIGS models. Two models are considered for the GBs of the polycrystalline structure: (a) neutral traps and (b) donor-like traps with N<sub>TS</sub>=4.5x10<sup>11</sup> cm<sup>-2</sup>. In both cases, the GB s<sub>R</sub> is fixed to be 10<sup>5</sup> cm/s and the results of this analysis are reported in Fig. 2.17.

As the results in Fig. 2.17 show, effect of  $\mu_p$  on the efficiency of a single-crystalline cell (first row in Fig. 2.17) is minimal since the absorber length is already shorter than the diffusion length for holes. On the other hand, when the mobility of the minority carriers ( $\mu_e$ ) is increased, an increase in carrier collection, J<sub>SC</sub> and efficiency is observed. When neutral GBs are implemented in the device structure (second row in Fig. 2.17), the

efficiency trend remained similar. A slight reduction in  $V_{OC}$  is observed as  $\mu_p$  is increased. This change in trend is found to be due to an increase in hole density and therefore an increase in recombination at the inverted GB in the depletion region. The reduction in  $V_{OC}$  is found to be more prominent for higher  $s_Rs$ .

(●) Single-crystalline cell

(■) Polycrystalline cell with neutral traps

(▼) Polycrystalline cell with donor-like traps & N<sub>TS</sub>=4.5x10<sup>11</sup> cm<sup>-2</sup>

Fig. 2.17 Performance of CIGS solar cell with respect to electron mobility (solid black lines) and hole mobility (dashed colored lines) [34]. Copyright © by IEEE <sup>9</sup>

Once donor-like traps with the  $N_{TS}$  of  $4.5 \times 10^{11}$  cm<sup>-2</sup> are placed into the GB (third row in Fig. 2.17) instead of neutral traps, the trend is found to be reversed. For this GB model, the holes are repelled from the GB, whereas the electrons are attracted to it (see Fig. 2.13.a). Hence, when  $\mu_p$  is increased, hole concentration decreases at already inverted GB regions. This mechanism further reduces the GB recombination and improves  $J_{SC}$  along with the efficiency. On the other hand, increasing  $\mu_e$  increases the electron concentration at the GB, causing higher GB recombination and lower efficiency.

Overall, the change in performance metrics with respect to the mobility values is found to be very small. The maximum amount of improvement in efficiency is found to be limited to 1.44% for a realistic improvement in the mobility values. That is why change in crystal observation is considered to be not the dominant cause for the increase in CIGS cell efficiency with Na incorporation.