# Purdue University Purdue e-Pubs

**Open Access Dissertations**

Theses and Dissertations

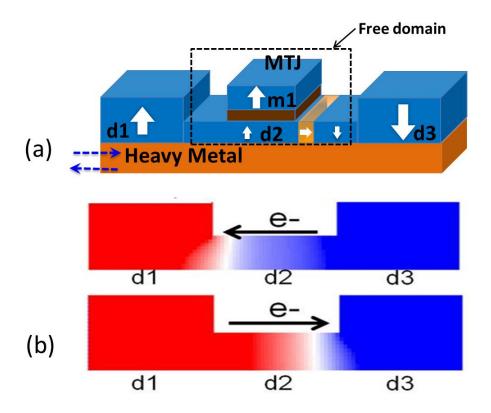

January 2015

# BOOLEAN AND BRAIN-INSPIRED COMPUTING USING SPIN-TRANSFER TORQUE DEVICES

Deliang Fan *Purdue University*

Follow this and additional works at: https://docs.lib.purdue.edu/open access dissertations

#### Recommended Citation

Fan, Deliang, "BOOLEAN AND BRAIN-INSPIRED COMPUTING USING SPIN-TRANSFER TORQUE DEVICES" (2015). Open Access Dissertations. 1186.

https://docs.lib.purdue.edu/open\_access\_dissertations/1186

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

### PURDUE UNIVERSITY GRADUATE SCHOOL Thesis/Dissertation Acceptance

This is to certify that the thesis/dissertation prepared

| By DELIANG FAN                                                                                                                                                                                                                                                                              |               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Entitled<br>BOOLEAN AND BRAIN-INSPIRED COMPUTING USING SPIN-TRANSFER TORQUE                                                                                                                                                                                                                 | DEVICES       |

|                                                                                                                                                                                                                                                                                             |               |

|                                                                                                                                                                                                                                                                                             |               |

| For the degree of Doctor of Philosophy                                                                                                                                                                                                                                                      |               |

|                                                                                                                                                                                                                                                                                             |               |

| Is approved by the final examining committee:                                                                                                                                                                                                                                               |               |

| KAUSHIK ROY                                                                                                                                                                                                                                                                                 |               |

| Chair                                                                                                                                                                                                                                                                                       |               |

| ANAND RAGHUNATHAN                                                                                                                                                                                                                                                                           |               |

| BYUNGHOO JUNG                                                                                                                                                                                                                                                                               |               |

| VIJAY RAGHUNATHAN                                                                                                                                                                                                                                                                           |               |

|                                                                                                                                                                                                                                                                                             |               |

|                                                                                                                                                                                                                                                                                             |               |

| To the best of my knowledge and as understood by the student in the Thesis Agreement, Publication Delay, and Certification Disclaimer (Graduate Schothis thesis/dissertation adheres to the provisions of Purdue University's "Po Integrity in Research" and the use of copyright material. | ool Form 32), |

| Approved by Major Professor(s): KAUSHIK ROY                                                                                                                                                                                                                                                 |               |

|                                                                                                                                                                                                                                                                                             |               |

| Approved by: MICHAEL R. MELLOCH                                                                                                                                                                                                                                                             | 7/17/2015     |

| Head of the Departmental Graduate Program                                                                                                                                                                                                                                                   | Date          |

# BOOLEAN AND BRAIN-INSPIRED COMPUTING USING SPIN-TRANSFER TORQUE DEVICES

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Deliang Fan

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

August 2015

Purdue University

West Lafayette, Indiana

| 11 |  |

|----|--|

|    |  |

Dedicated to my family and friends for their endless love and selfless support

#### **ACKNOWLEDGMENTS**

First and foremost, I would like to express my sincere gratitude to my Ph.D. advisor, Prof. Kaushik Roy. His exceptional guidance, constant support and encouragement are pivotal in making this dissertation possible. I would never forget the words he told me-"You will never know if you don't try", which inspired me during my hard times. I sincerely thank him, not only for teaching me to be a qualified research scientist, but also for guiding me to be a man who can face the challenges with courage and confidence.

I would also like to thank my advisory committee members, Prof. Anand Raghunathan, Prof. Byunghoo Jung, and Prof. Vijay Raghunathan, for their constructive advice and feedback to improve the quality of my doctoral research and dissertation.

I am thankful to the former Nanoelectronic Research Lab (NRL) members for their valuable discussion and inspiration: Dr. Mrigank Sharad, Dr. Xuanyao Fong, Dr. Chao Lu, Dr. Harsha Choday, Dr. Chih-Hsiang Ho, Dr. Charles Augustine and Dr. Sumeet Gupta. Special thanks to Dr. Mrigank Sharad for being an exceptional mentor, collaborators and good friend since the time I started my doctoral program.

I sincerely thank my other colleagues and collaborators from NRL and Embedded System Lab (ESL) for their technical discussion, contribution and support: Karthik Yogendra, Supriyo Maji, Yong Shim, Abhronil Sengupta, Yusung Kim, Minsuk Koo, Yeongkyo Seo and all other NRL & ESL members.

Last but not the least, I would like to express my gratitude to my parents - Tianlu Fan & Tuansi Liu, my relatives and my girlfriend - Zhao Cui for their endless love and selfless support.

## TABLE OF CONTENTS

|                                                                           | Page |

|---------------------------------------------------------------------------|------|

| LIST OF TABLES                                                            | vi   |

| LIST OF FIGURES                                                           | vii  |

| ABSTRACT                                                                  | xiii |

| 1. INTRODUCTION                                                           | 1    |

| 1.1. Introduction                                                         | 1    |

| 1.2. Spin Devices                                                         | 1    |

| 1.2.1. Magnet Switching Energy                                            | 2    |

| 1.2.2. Magnetic Field Switching                                           |      |

| 1.2.3. Spin-Transfer Torque Switching                                     |      |

| 1.3. Organization                                                         | 7    |

| 2. SPIN-TRANSFER TORQUE DEVICES                                           | 10   |

| 2.1. Vertical Spin Valve                                                  | 10   |

| 2.2. Lateral Spin Valve                                                   | 14   |

| 2.3. Magnetic Domain Wall Strip                                           | 17   |

| 2.4. Spin-Orbit Torque                                                    | 19   |

| 2.5. Summary                                                              | 21   |

| 3. BOOLEAN LOGIC DESIGN: SPIN-MEMRISTOR THRESHOLD LOGIC                   | 22   |

| 3.1. Introduction                                                         | 22   |

| 3.2. Design of TLG First Stage using Memristive Cross-bar Array           | 23   |

| 3.2.1. Multi-level MCA                                                    | 24   |

| 3.2.2. Threshold Logic Computing using MCA                                | 26   |

| 3.3. TLG Second Stage Design using Spintronic Threshold Device            | 28   |

| 3.4. Design of SMTL Array                                                 | 32   |

| 3.5. Optimal Pipelining and Partitioning of SMTL Arrays for Logic Mapping | 36   |

| 3.5.1. Pipelining Optimization                                            | 36   |

| 3.5.2. Partition and Interconnects                                        | 38   |

| 3.6. Simulation and Synthesis Algorithm                                   | 41   |

| 3.7. Performance and Prospects                                            | 45   |

| 3.8. Summary                                                              | 49   |

| 4. BRAIN-INSPIRED COMPUTING: HIERARCHICAL TEMPORAL MEMORY                 |      |

| BASED ON SPIN-NEURON AND RESISTIVE MEMORY                                 | 50   |

|              |                                                                | Page |

|--------------|----------------------------------------------------------------|------|

|              | action                                                         |      |

|              | Algorithm and Architecture                                     |      |

|              | TM Architecture and Training                                   |      |

| 4.2.2. H     | TM Inference                                                   | 57   |

| 4.2.3. H     | TM Design Specification                                        | 59   |

| 4.3. Comp    | uting with memristive cross-bar array                          | 61   |

| 4.4. Spin-N  | Neuron with heavy metal layer                                  | 62   |

| 4.5. Design  | n of HTM Computing Block using Spin-Neuron and MCA             | 66   |

| 4.5.1. Sp    | atial and Temporal Pooler Design                               | 67   |

|              | TM Hardware Mapping Using Spin-MCA Based Pattern Matching      | 7.4  |

|              | Architecture                                                   |      |

|              | mance of Proposed HTM Hardware                                 |      |

|              | ary                                                            |      |

|              | ANSFER TORQUE BASED SOFT-LIMITING NON-LINEAR NEU               |      |

|              | action                                                         |      |

| =            | sed Spin-Transfer Torque based Soft-limiting Non-linear Neuron |      |

|              | stive Cross-bar Array Synapses                                 |      |

|              | Hardware Using STT-SNN and MCA                                 |      |

|              | ation & Performance Results                                    |      |

|              | ary                                                            | 102  |

|              | SPIRED COMPUTING USING COUPLED SPIN TORQUE                     | 100  |

|              | TOR ARRAY                                                      |      |

|              | action                                                         |      |

| •            | Forque Oscillators                                             |      |

|              | erminal STO                                                    |      |

| -            | in Hall Effect STO                                             |      |

|              | Coupling Mechanisms                                            |      |

|              | agnetic coupling                                               |      |

|              | ectrical Coupling                                              |      |

|              | ection Locking                                                 |      |

| 6.4. Injecti | on Locked SHE-STO Cluster                                      | 122  |

|              | ative Computing Using Injection Locked SHE-STO Cluster         |      |

| 6.6. CMOS    | S Interface Circuits and System Performance                    | 130  |

| 6.6.1. CN    | MOS Interface Circuits Design                                  | 130  |

| 6.6.2. Sy    | stem Performance and Variation Analysis of SHE-STO based AM    | 136  |

| 6.7. Summ    | ary                                                            | 140  |

| 7. SUMMAR    | YY                                                             | 141  |

| LIST OF RE   | FERENCES                                                       | 143  |

| VITA         |                                                                | 161  |

## LIST OF TABLES

| Table                                                         | Page |

|---------------------------------------------------------------|------|

| 3.1 STD device parameters                                     | 29   |

| 3.2 SMTL Design Parameters.                                   | 49   |

| 4.1 HTM Design Parameters                                     | 80   |

| 5.1 STT-SNN Device Parameters used in Simulation              | 87   |

| 5.2 Number of Neurons for Different Neuron Transfer Functions | 98   |

| 6.1 SHE-STO Device parameters used in simulation              | 111  |

| 6.2 Comparison of power consumption for 2T-STO and SHE-STO    | 112  |

| 6.3 CMOS interface circuit simulation results                 | 136  |

| 6.4 Energy analysis of associative module                     | 137  |

## LIST OF FIGURES

| Figure Pag                                                                                                                                                                                                                                              | e |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 1.1 Nano-magnet with uniaxial anisotropy and corresponding energy landscape                                                                                                                                                                             | 2 |

| 1.2 (a) Two orthogonal wires generate two orthogonal fields HHARD and HEASY (b) magnetic field generation using current carrying wire                                                                                                                   | 4 |

| 1.3 Slonczewski torque and field-like torque on the nano-magnet due to the flowing of spin-polarized current                                                                                                                                            | 5 |

| 2.1 Physical structure of a vertical spin value and its two states, corresponding to low and high resistance state                                                                                                                                      | 1 |

| 2.2 Physical structure of MTJ and its band structure of parallel and anti-parallel configurations                                                                                                                                                       | 3 |

| 2.3 Physical structure of a lateral spin valve of local and non – local measurements that has been made to experimentally observe magneto-resistance effect and pure spin-current generation.                                                           | 6 |

| 2.4 Typical domain wall structure (a) in-plane magnetic anisotropy transverse head-to-head transverse DW (b) IMA vortex DW, (c) perpendicular magnetic anisotropy nanowire with Neel DW, and (d) PMA Bloch DW                                           | 8 |

| 2.5 Charge current applied in non-magnetic heavy metal with strong spin-orbit coupling is converted to pure spin current due to spin hall effect                                                                                                        | 9 |

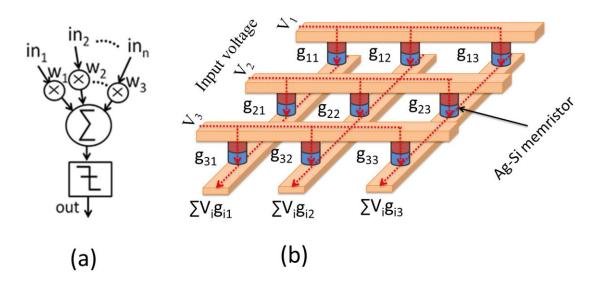

| 3.1 (a) A Schematic representation of a threshold logic gate (TLG), (b) memristive cross-bar array                                                                                                                                                      | 4 |

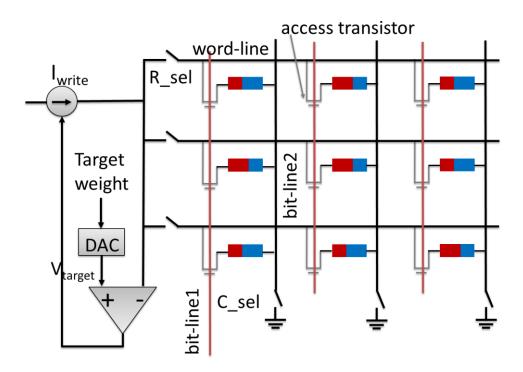

| 3.2 A resistive memory array with multi-level programming periphery                                                                                                                                                                                     | 5 |

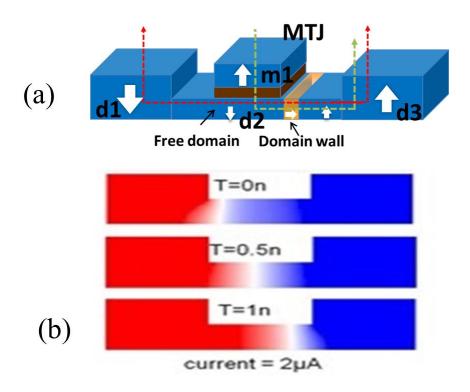

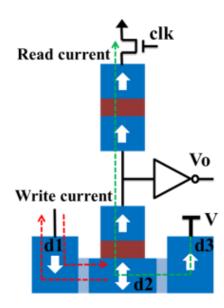

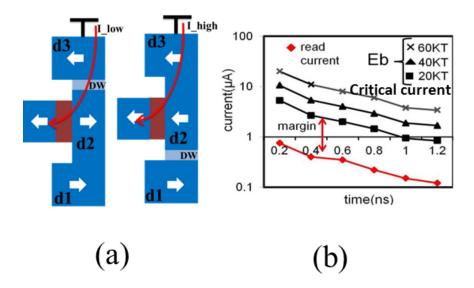

| 3.3 (a) Device structure for Spintronic Threshold Device (b) Transient micro-magnetic simulation plots. Read color represents the 'down spin' corresponding to d1. Blue color represents the 'up spin' in d3. White color is the magnetic domain wall 2 | 8 |

| 3.4 STD state sense circuit                                                                                                                                                                                                                             | 0 |

| 3.5 (a) read current for different d2 state (b) read current margin to critical current 3                                                                                                                                                               | 1 |

| Figure                                                                                                                                                                                                                                                                                              | Page |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

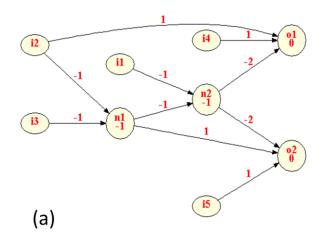

| 3.6 (a) synthesized ISCAS85 benchmark C17 threshold logic network. (b) synthesized ISCAS85 benchmark-C432 (27-channel interrupt controller) threshold logic network.                                                                                                                                | 32   |

| 3.7 Circuit of one single threshold logic stage using MCA and STD                                                                                                                                                                                                                                   | 34   |

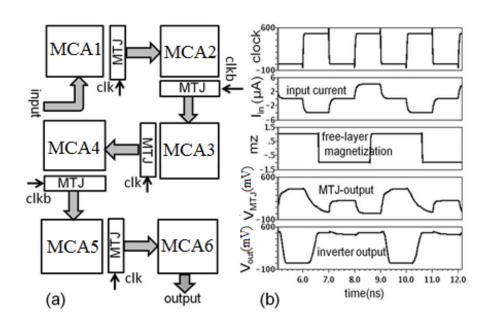

| 3.8 (a) 2-phase pipelined MCA blocks for large-scale logic design, (b) transient simulation plots for a single TLG.                                                                                                                                                                                 | 35   |

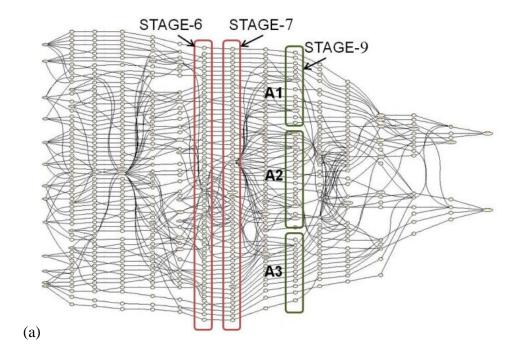

| 3.9 synthesized C432 pipelined threshold logic network. (a) Fully pipelined architecture (b) two TLG stages combined with one pipeline stage                                                                                                                                                        | 37   |

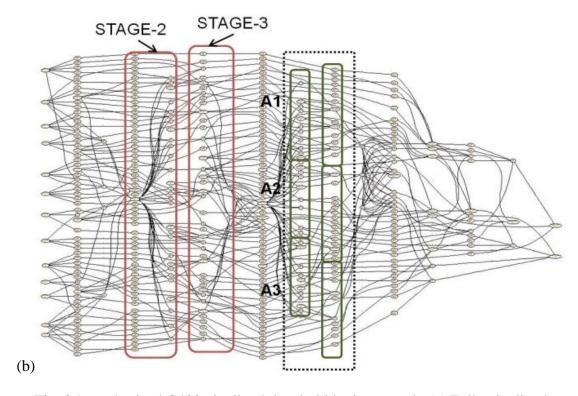

| 3.10 : (a) Power consumption of different pipeline configurations (b) tradeoff between power and area. 'Power_MCA_5uA' represents the power of memristocross-bar array when the DTCS current is 5uA. 'Power_det' is the power of detection module including MTJ-voltage divider, clock and inverter |      |

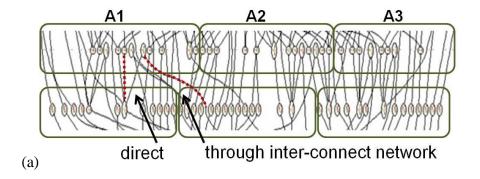

| 3.11 (a) Enlarged green square part of Fig. 3.9b (b) SMTL network partition architecture                                                                                                                                                                                                            | 40   |

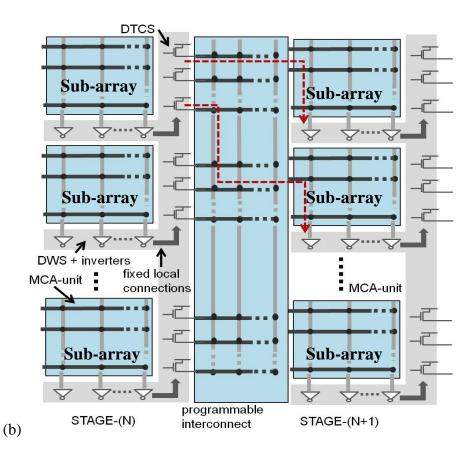

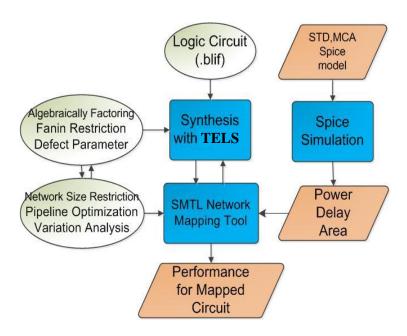

| 3.12 Relationship between (a) power, (b) area and sub-array dimension, (larger dimension implies lower number of sub-arrays needed)                                                                                                                                                                 | 41   |

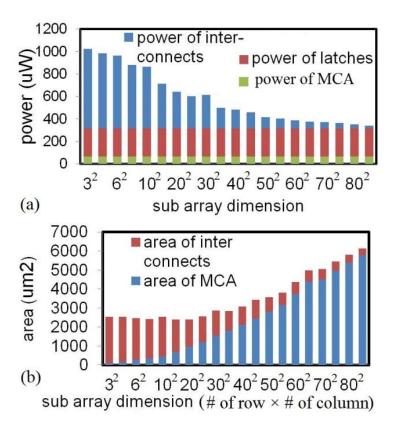

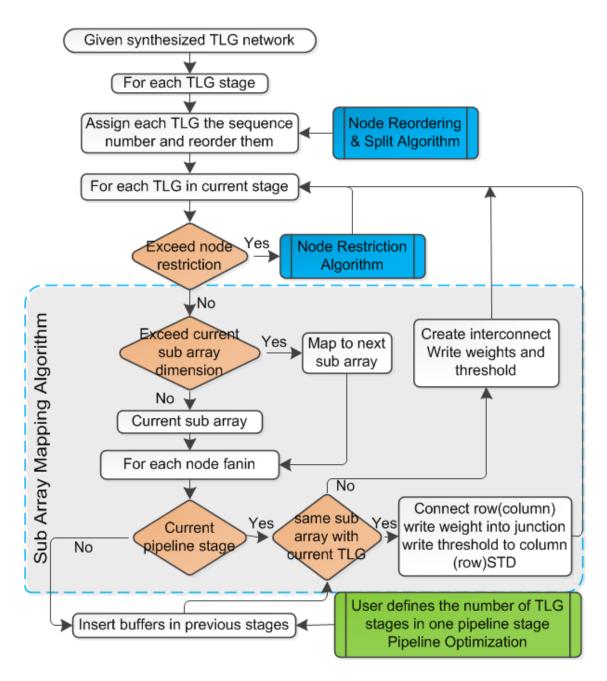

| 3.13 Proposed design methodology                                                                                                                                                                                                                                                                    | 42   |

| 3.14 SMTL network mapping algorithm                                                                                                                                                                                                                                                                 | 43   |

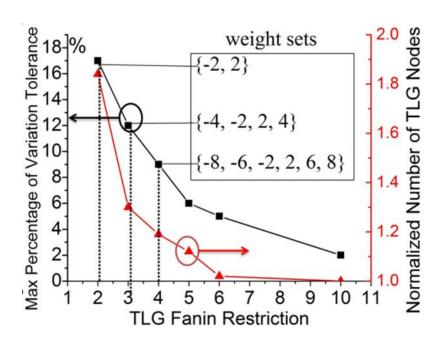

| 3.15 the relationship between variation tolerance, TLG fan-in restriction and number of TLGs                                                                                                                                                                                                        | 44   |

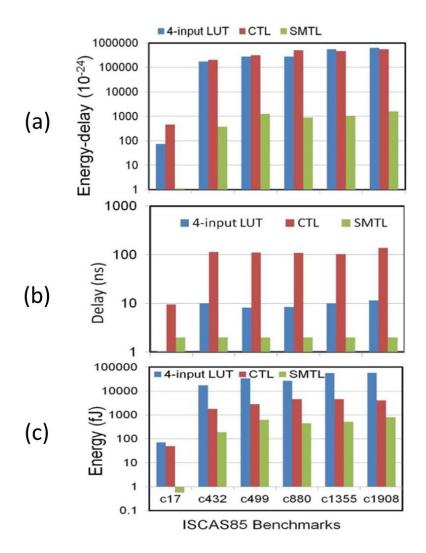

| 3.16 (a) Energy-delay product, (b) delay and (c) computation energy of SMTL compared with 4-input LUT based FPGA [73] and CTL [73] for ISCAS85 benchmarks.                                                                                                                                          | 47   |

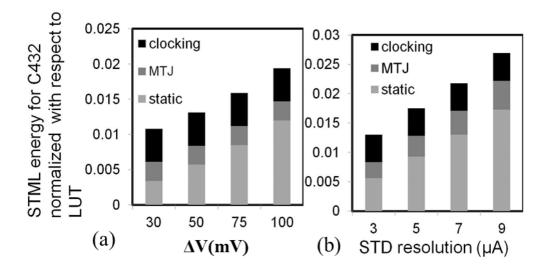

| 3.17 SMTL energy for C432 normalized with respect to 4-input LUT for the case of (a) increasing ΔV, (b) increasing STD threshold for a fixed ΔV of 50mV; LUT delay is ~10ns                                                                                                                         | 48   |

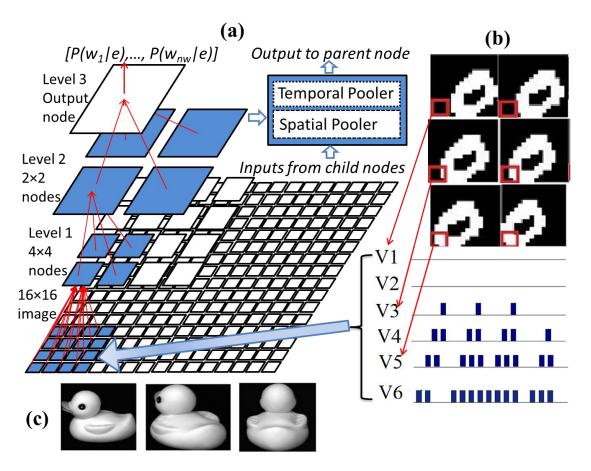

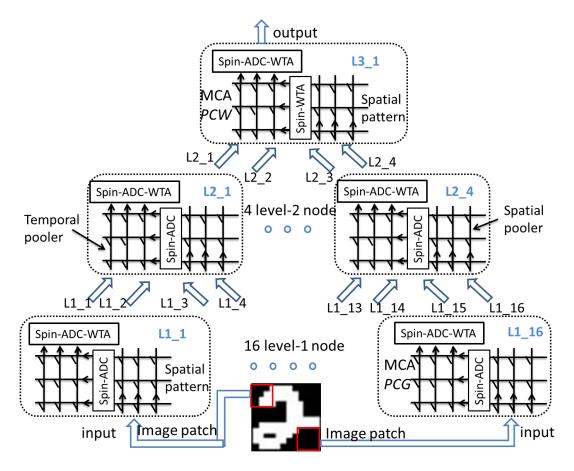

| 4.1 (a) A three-level HTM architecture designed to work with 16×16 pixel images (b) HTM Training Sequence generated by zigzag scan and part of the training sequence of the highlighted lower left node in level 1 (c) snap-shots of a moving duck.                                                 | 53   |

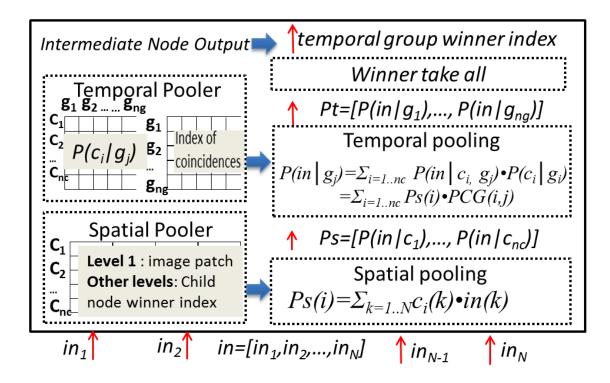

| 4.2 HTM-node structure and the associated inference-steps                                                                                                                                                                                                                                           | 57   |

| Figure                                                                                                                                                                                                                                                                                                                                                                                | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

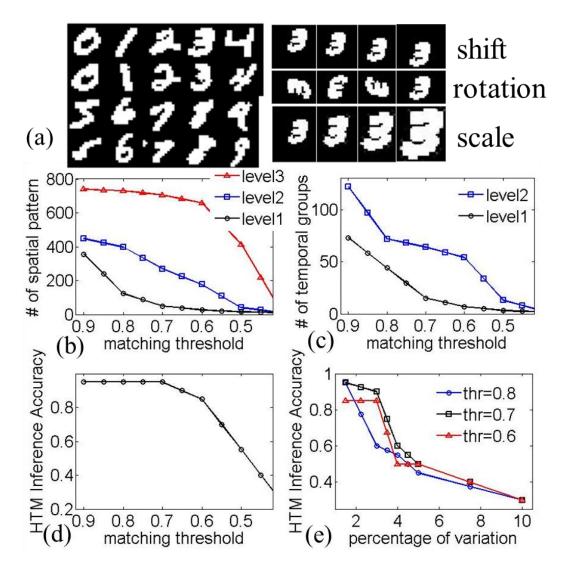

| 4.3 (a) 20 image samples in MNIST benchmark and the shift, rotation and scale variations. (b) Numbers of spatial patterns in each node vs. matching threshold. (c) Numbers of temporal groups in each node vs. matching threshold. (d) HTM inference accuracy vs. matching threshold. (e) HTM inference accuracy vs. percentage-variation in the elements of spatial-temporal memory. | 60   |

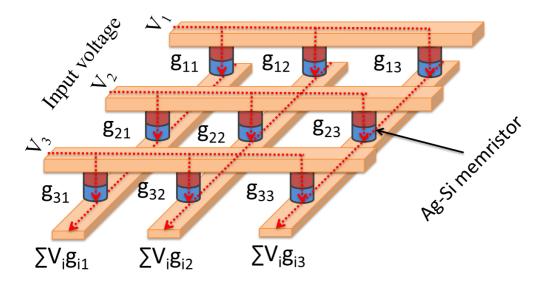

| 4.4 Correlation evaluation between input vector and stored vectors using a memristive cross-bar array                                                                                                                                                                                                                                                                                 | 61   |

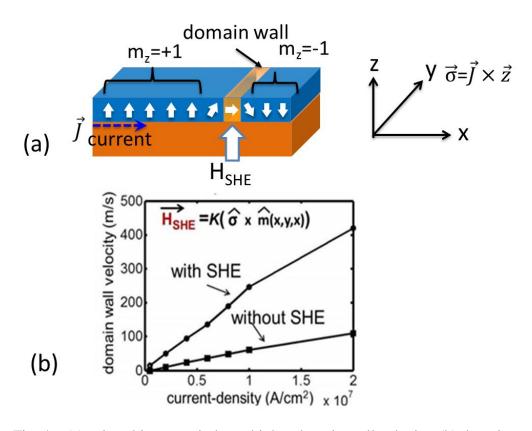

| 4.5 (a) Spin-neuron with heavy metal layer, (b) micro-magnetic simulation of domain wall motion with applied current along spin hall metal layer [114]                                                                                                                                                                                                                                | 63   |

| 4.6 (a) spin orbit torque induces higher domain wall velocity, (b) domain wall velocity vs. applied current density with and without SHE                                                                                                                                                                                                                                              | 64   |

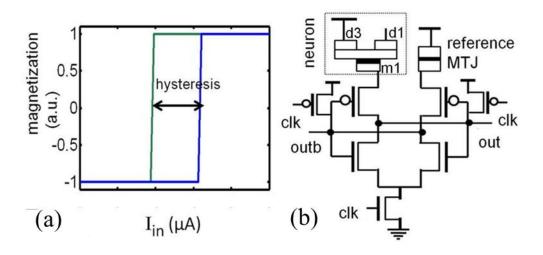

| 4.7 (a) transfer characteristics of the spin-neuron with spin hall metal layer (Eb=20KT), (b) dynamic CMOS latch to sense spin-neuron state                                                                                                                                                                                                                                           | 65   |

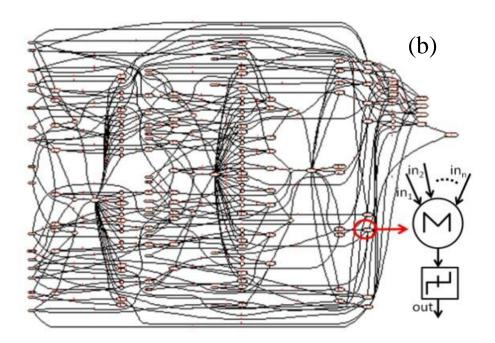

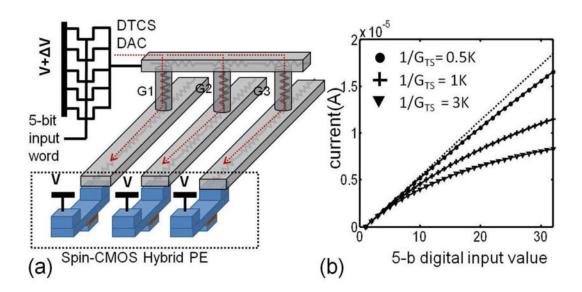

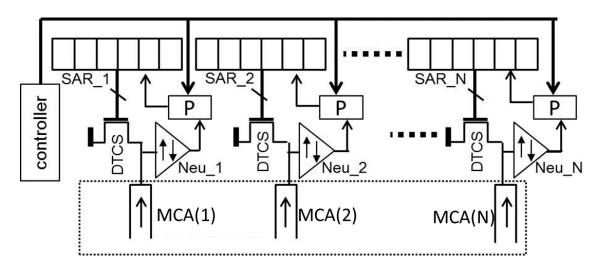

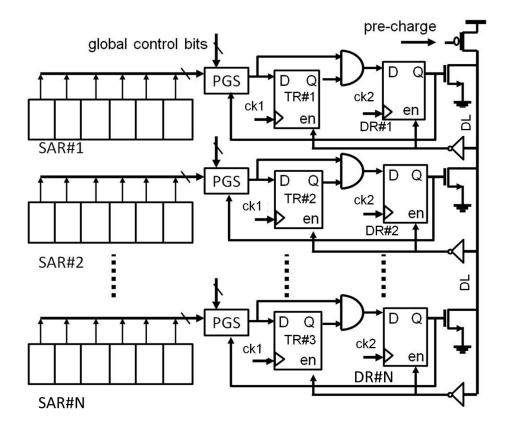

| <ul><li>4.8 (a) DTCS DAC provides inputs to MCA, while spin-CMOS hybrid PE takes the MCA outputs (heavy metal layer is not shown for simplicity)</li><li>(b) DTCS DAC non-linearity with different GTS [83]</li></ul>                                                                                                                                                                 | 68   |

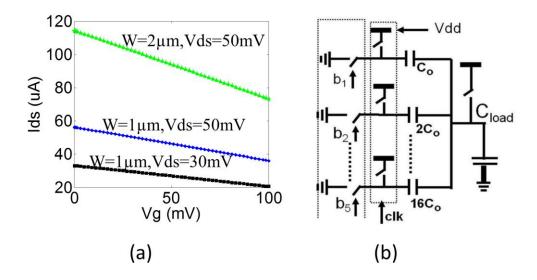

| 4.9 (a) near-linear drain-current (Id) vs. gate voltage (Vg) with different Vdd and $\Delta V$ (b) compact switched capacitor DAC scheme [83]                                                                                                                                                                                                                                         | 69   |

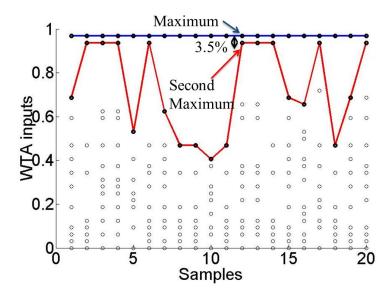

| 4.10 the normalized MCA column outputs (WTA inputs) for different image samples, showing isolation between the best and second best match                                                                                                                                                                                                                                             | 71   |

| 4.11 Spin-neuron based SAR ADC circuit diagram [83]                                                                                                                                                                                                                                                                                                                                   | 72   |

| 4.12 WTA circuit diagram [83]                                                                                                                                                                                                                                                                                                                                                         | 73   |

| 4.13 HTM hardware mapping using spin-MCA based pattern matching network architecture                                                                                                                                                                                                                                                                                                  | 75   |

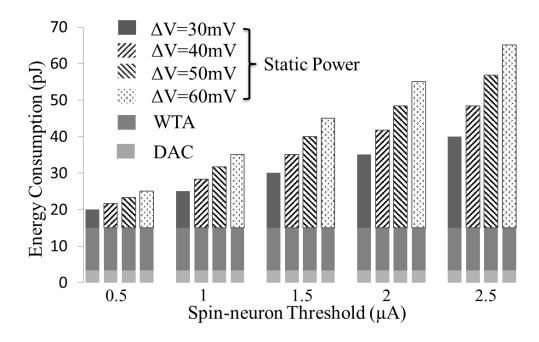

| 4.14 Energy consumption of a single HTM node (level 2) for different values of spin-neuron threshold and $\Delta V$                                                                                                                                                                                                                                                                   | 76   |

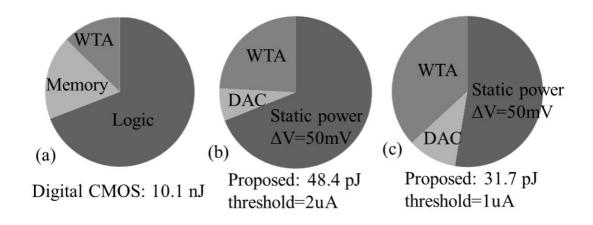

| 4.15 Distribution of energy dissipation for a single HTM node design (level 2 node) (a) fully digital CMOS design, (b) Spin-MCA based design with 2 μA spin-neuron threshold, (c) Spin-MCA based design with 1 μA spin-neuron threshold ('WTA' in the pie chart includes both the ADC and WTA circuit )                                                                               | 77   |

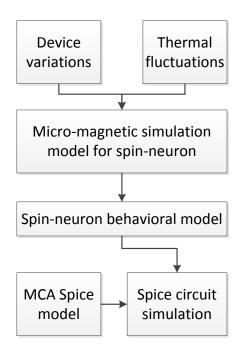

| 4.16 simulation framework used in this work                                                                                                                                                                                                                                                                                                                                           | 79   |

| Figure                                                                                                                                                                                                                                                                                                                                              | ge             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

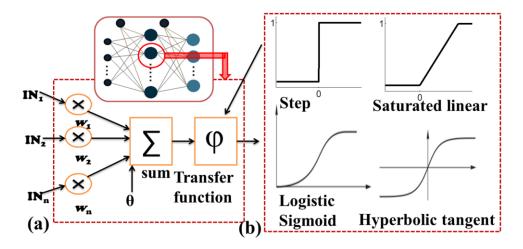

| 5.1 (a) artificial neuron: it takes weighted sum of n inputs and passes the result through an transfer/activation function (b) four representative transfer (activation) functions                                                                                                                                                                  | 33             |

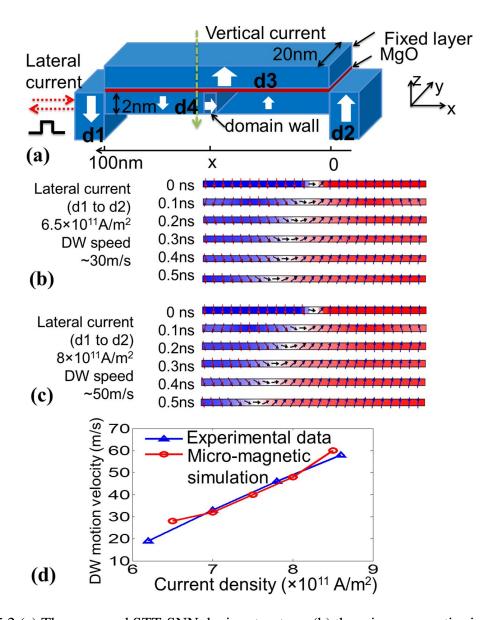

| 5.2 (a) The proposed STT-SNN device structure, (b) the micro-magnetic simulation of free layer DW motion when the injected lateral current density is $6.5\times10^{11}~\text{A/m}^2$ and (c) $8\times10^{11}~\text{A/m}^2$ , (d) simulated DW motion velocity vs. current density, showing a good match with experimental data reported in [126] 8 | 36             |

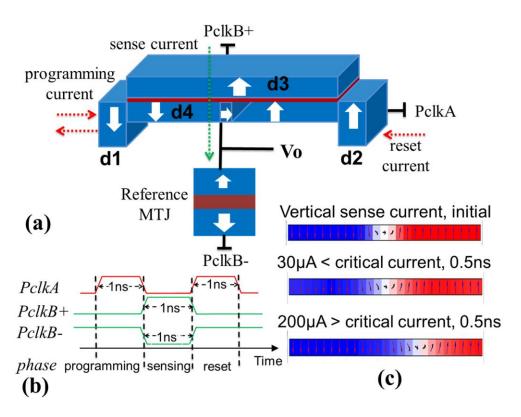

| 5.3 (a) The programming and sensing circuit of the proposed STT-SNN, (b) the clocked power supply waveforms, (c) the micro-magnetic simulation of STT-SNN free layer with different vertical sense currents                                                                                                                                         | 39             |

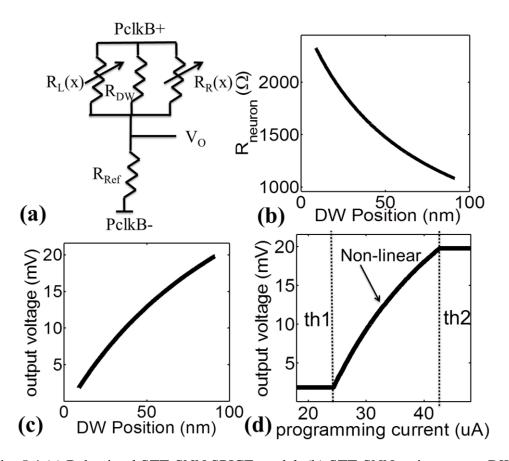

| 5.4 (a) Behavioral STT-SNN SPICE model, (b) STT-SNN resistance vs. DW positions, (c) output voltage vs. DW positions, (d) output voltage vs. programming current. Note, the positive current direction is defined from d1 to d2. Clock cycle is 1ns.                                                                                                | 91             |

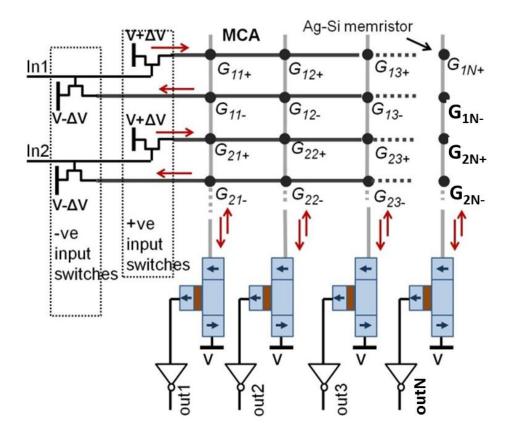

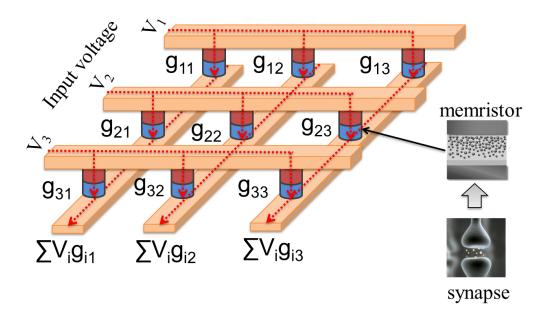

| 5.5 (a) Memristor crossbar array used for evaluating the weighted sum of inputs for ANN                                                                                                                                                                                                                                                             | €              |

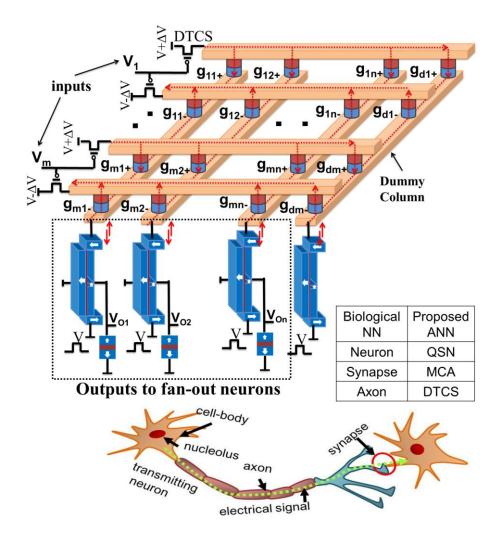

| 5.6 The proposed ANN hardware design using DTCS-axon, MCA-synapse, and STT-SNN                                                                                                                                                                                                                                                                      | €              |

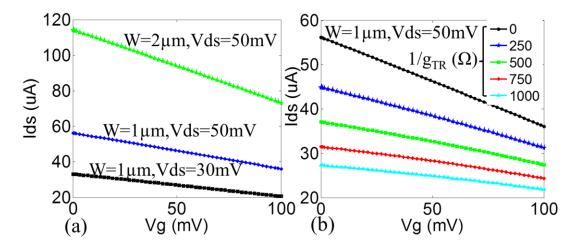

| 5.7 (a) DTCS Ids vs. Vg for different width and Vds (b) non-linearity characteristics of DTCS transistor due to drain terminal memristor load                                                                                                                                                                                                       | ∂6             |

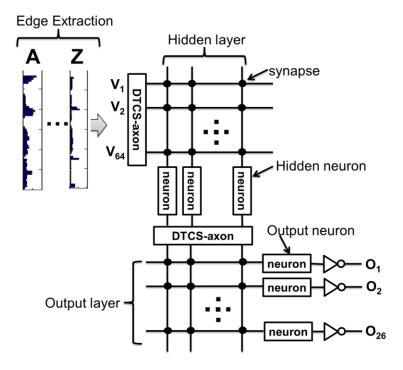

| 5.8 Alphabet feature vectors and two-layer feed-forward ANN architecture. Note, the hardware implementation of each layer can be seen in Fig. 5.6                                                                                                                                                                                                   | <del>)</del> 7 |

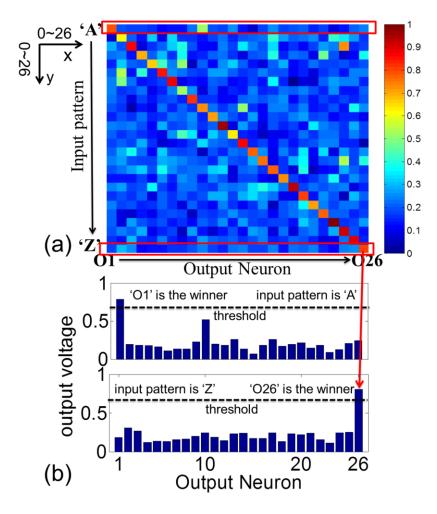

| 5.9 (a) Normalized 26 output neurons' voltages for 26 test input patterns. Note that, pixel (i, j) indicates ith output neuron voltage for jth input pattern. (b) The 26 output neurons' voltages when the input patterns are 'A' and 'Z'                                                                                                           | 99             |

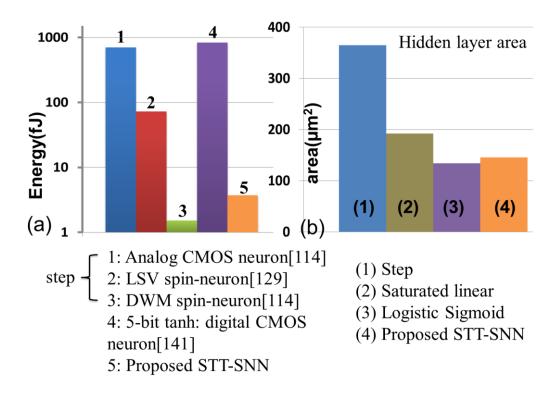

| 5.10 (a) Energy for different single neuron implementations, (b) hidden layer area based on different neuron transfer functions                                                                                                                                                                                                                     | )0             |

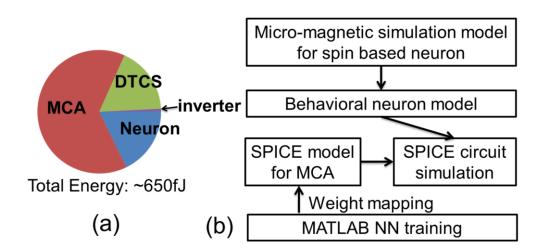

| 5.11 (a) Energy analysis of the proposed ANN hardware for character recognition benchmark, (b) simulation framework                                                                                                                                                                                                                                 | )1             |

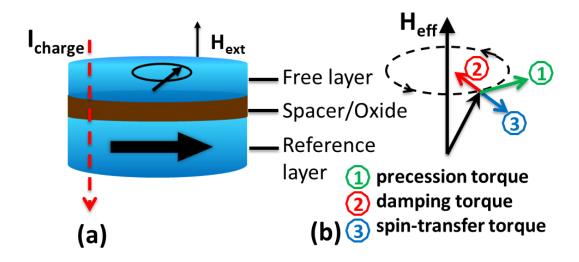

| 6.1 (a) 2-terminal STO device structure, (b) different torque terms acting in the free layer                                                                                                                                                                                                                                                        | )5             |

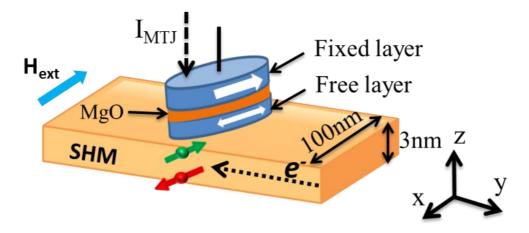

| 6.2 SHE-STO device structure. Spin accumulation at the top and bottom surface of SHM due to SHE. Hext is the applied external magnetic field                                                                                                                                                                                                        | )7             |

| Figure                                                                                                                                                                                                                                                                                                                          | e |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

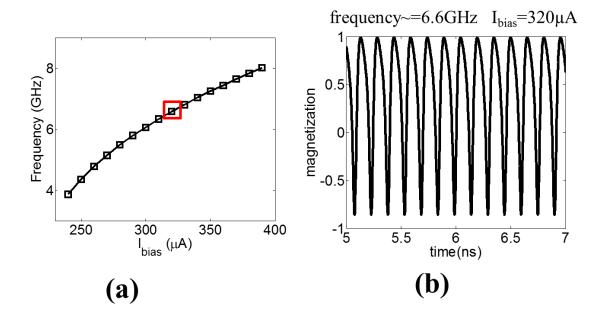

| 6.3 (a) SHE-STO output frequency vs. Ibias, (b) transient simulation of SHE-STO free layer oscillation when Ibias=320μA                                                                                                                                                                                                         | 9 |

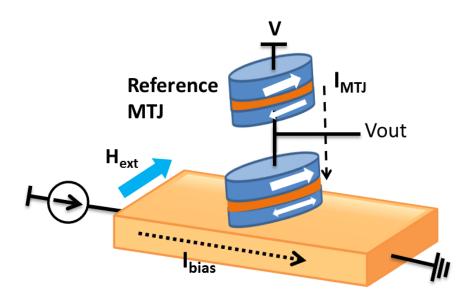

| 6.4 SHE-STO biasing and sensing circuit                                                                                                                                                                                                                                                                                         | 0 |

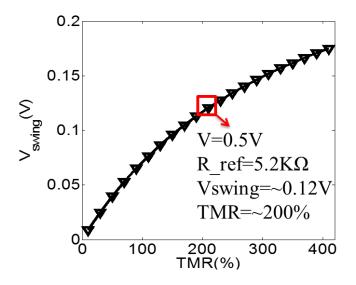

| 6.5 peak-to-peak output voltage swing vs. different TMR                                                                                                                                                                                                                                                                         | 1 |

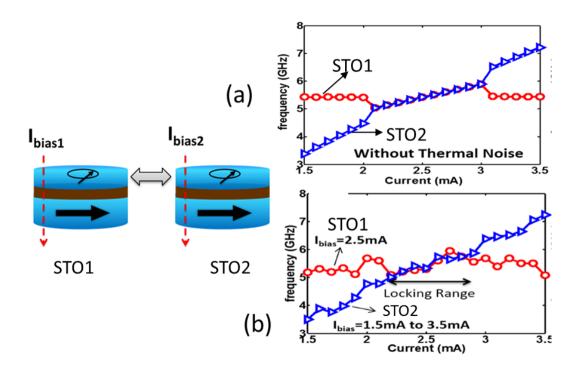

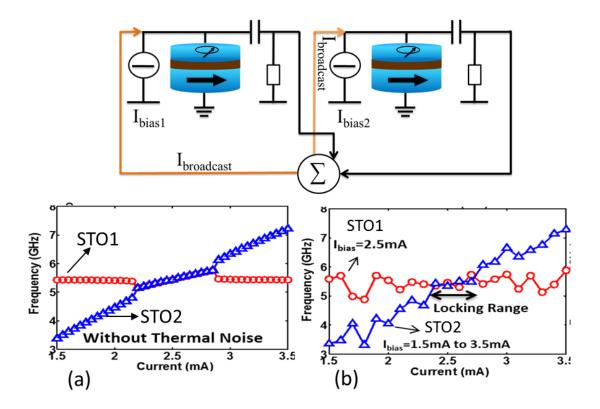

| 6.6 STO frequency vs. DC bias currents in magnetic coupling (a) without thermal noise, (b) with thermal noise (temperature, 300K)                                                                                                                                                                                               | 5 |

| 6.7 STO frequency vs. DC bias currents in electrical coupling (a) without thermal noise, (b) with thermal noise                                                                                                                                                                                                                 | 7 |

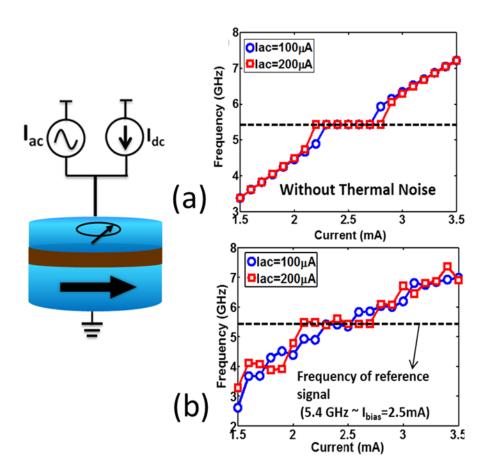

| 6.8 STO frequency vs. DC bias currents in current injection locking mechanism (a) without thermal noise, (b) with thermal noise                                                                                                                                                                                                 | 8 |

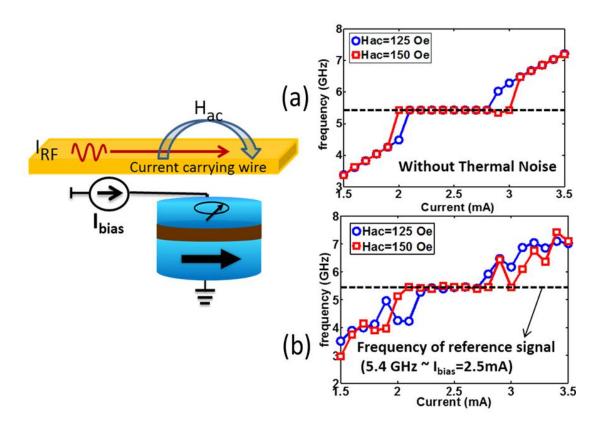

| 6.9 STO frequency vs. DC bias currents in field injection locking mechanism (a) without thermal noise, (b) with thermal noise                                                                                                                                                                                                   | 0 |

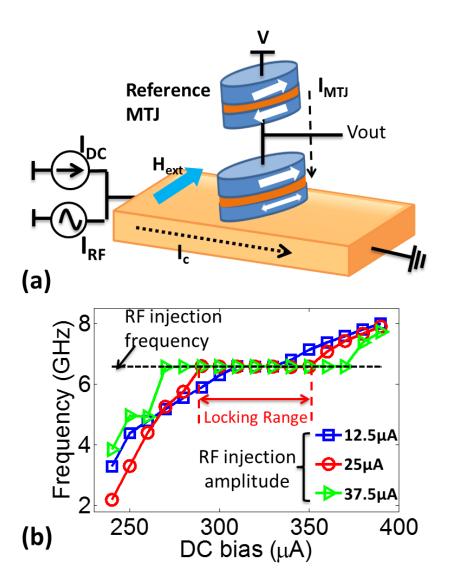

| 6.10 (a) SHE-STO locked to an external microwave current, (b) SHE-STO frequency vs. different RF current amplitude, showing SHE-STO locks to external RF signal and DC locking range increases with higher RF amplitude                                                                                                         | 2 |

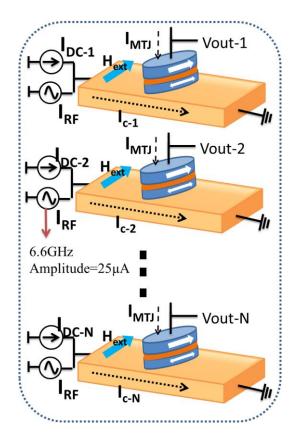

| 6.11 N-number of SHE-STOs can be locked to a common external RF signal 124                                                                                                                                                                                                                                                      | 4 |

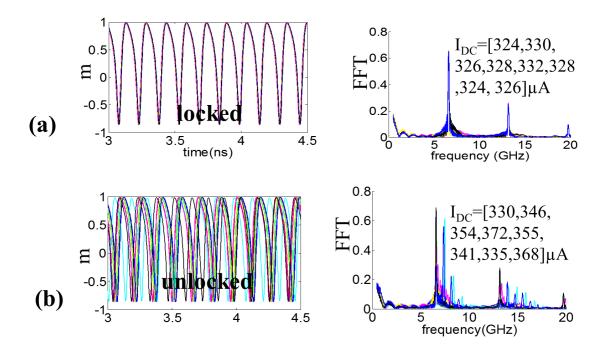

| 6.12 transient waveforms and FFT of 8 SHE-STOs when they are (a) locked or (b) unlocked with different SHE-STO DC biases                                                                                                                                                                                                        | 5 |

| 6.13 transient plots for 8 injection locked SHE-STOs (a) without parameter variations and thermal noise, (b) with parameter variations and thermal noise when RF amplitude is 12.5μA, (c) 25μA, (d) 37.5μA. Note: the DC inputs of each SHE-STO are [330, 346, 354, 372, 355, 341, 335, 368]μA, external RF frequency is 6.6GHz | 6 |

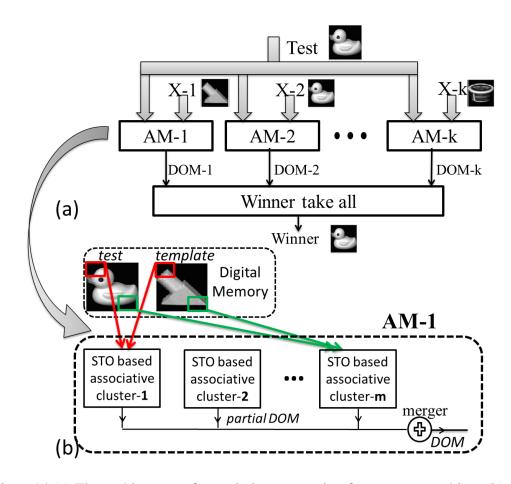

| 6.14 (a) The architecture of associative computing for pattern matching, (b) the architecture of individual associative module design                                                                                                                                                                                           | 7 |

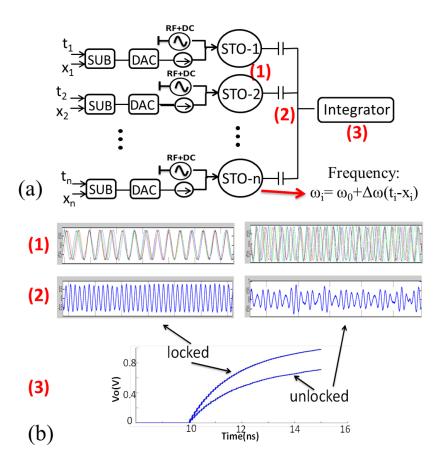

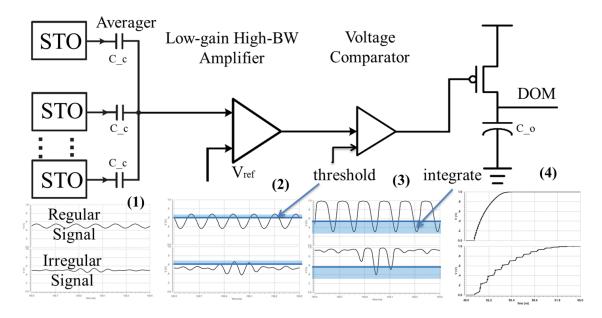

| 6.15 (a) Circuit blocks of STO based associative cluster (b) transient simulation waveform of (1) STO outputs (2) capacitive addition outputs (3) integrator outputs                                                                                                                                                            | 8 |

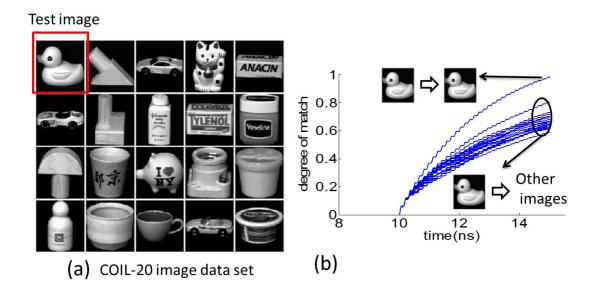

| 6.16 (a) COIL-20 image data set [118] used in simulation: pixel values corresponding to the individual images were stored as 1-D analog templates, (b) merger outputs for a particular test (duck) image compared with all the other template images 129                                                                        | 9 |

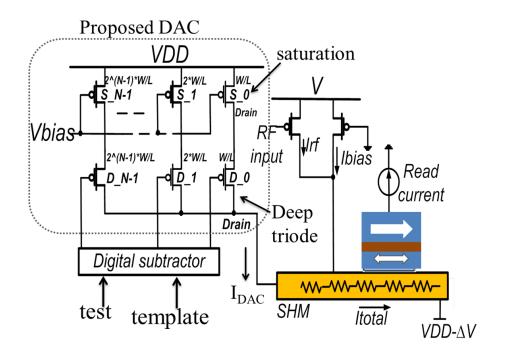

| 6.17 Proposed DAC circuit for SHE-STO                                                                                                                                                                                                                                                                                           | 1 |

| Figure                                                                                                                                                                                                                                                                                                                                      | Page  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 6.18 Integrator circuit design and the transient waveforms. Note, regular signal corresponds to locked case. Irregular signal corresponds to unlocked case                                                                                                                                                                                  | 132   |

| 6.19 (a) Analog merger circuit, (b) Simulation results                                                                                                                                                                                                                                                                                      | . 134 |

| 6.20 (a) Normalized outputs of SHE-STO based AM for all 20 patterns shown in Fig. 6.16a. Note that, pixel (i, j) indicates the SHE-STO AM output when ith pattern compared with jth pattern (b) detection margin for all 20 patterns. Pattern #3, 6 and 19 are shown in the right. Note that detection margin= (DOM(1st)-DOM(2nd))/DOM(1st) | 138   |

| 6.21 transient AM output (a) without variation, (b) Monte-Carlo simulation on interface circuits, device parameters and thermal noise. Note that, only the best match and second best match outputs are shown for simplicity. Blue line is the best match, and red line is the second best match.                                           | 140   |

#### **ABSTRACT**

Fan, Deliang. Ph.D., Purdue University, August 2015. Boolean and Brain-Inspired Computing Using Spin-Transfer Torque Devices. Major Professor: Kaushik Roy.

Several completely new approaches (such as spintronic, carbon nanotube, graphene, TFETs, etc.) to information processing and data storage technologies are emerging to address the time frame beyond current Complementary Metal-Oxide-Semiconductor (CMOS) roadmap. The high speed magnetization switching of a nano-magnet due to current induced spin-transfer torque (STT) have been demonstrated in recent experiments. Such STT devices can be explored in compact, low power memory and logic design. In order to truly leverage STT devices based computing, researchers require a re-think of circuit, architecture, and computing model, since the STT devices are unlikely to be drop-in replacements for CMOS. The potential of STT devices based computing will be best realized by considering new computing models that are inherently suited to the characteristics of STT devices, and new applications that are enabled by their unique capabilities, thereby attaining performance that CMOS cannot achieve. The goal of this research is to conduct synergistic exploration in architecture, circuit and device levels for Boolean and brain-inspired computing using nanoscale STT devices. Specifically, we first show that the non-volatile STT devices can be used in designing configurable Boolean logic blocks. We propose a spin-memristor threshold logic (SMTL) gate design, where memristive cross-bar array is used to perform current mode summation of binary inputs and the low power current mode spintronic threshold device carries out the energy efficient threshold operation. Next, for brain-inspired computing, we have exploited different spin-transfer torque device structures that can implement the hard-limiting and soft-limiting artificial neuron transfer functions respectively. We apply

such STT based neuron (or 'spin-neuron') in various neural network architectures, such as hierarchical temporal memory and feed-forward neural network, for performing "human-like" cognitive computing, which show more than two orders of lower energy consumption compared to state of the art CMOS implementation. Finally, we show the dynamics of injection locked Spin Hall Effect Spin-Torque Oscillator (SHE-STO) cluster can be exploited as a robust multi-dimensional distance metric for associative computing, image/ video analysis, etc. Our simulation results show that the proposed system architecture with injection locked SHE-STOs and the associated CMOS interface circuits can be suitable for robust and energy efficient associative computing and pattern matching.

#### 1. INTRODUCTION

#### 1.1. Introduction

The scaling of Complementary Metal-Oxide Semiconductor (CMOS) transistors brings a lot of issues, such as short channel effect, large leakage current and so on. Considerable research efforts has started in earnest to explore new devices that can potentially replace CMOS. Several completely new approaches (such as spintronic [1]-[7], TFETs [8][9], etc.) to information processing and data storage technologies are emerging to address the time frame beyond current CMOS roadmap. These emerging devices have unique characteristics that set them apart from traditional MOS transistors. In order to attain performance that CMOS cannot achieve, new computing models that are uniquely suited to the characteristics of these emerging devices are required to be explored.

Recently, it was experimentally demonstrated that the spin polarized currents can switch nano-scale magnets due to spin-transfer torque (STT) [4][5]. Compared with CMOS transistors, STT devices have the characteristics of non-volatility, zero current leakage and high integration density, which make them promising candidates for designing compact, low power memory and Boolean logic [13]-[24]. It is well accepted that STT devices are suitable in on-chip memory design, while the suitability of spin-transfer torque devices for logic applications is debatable [24]. In this dissertation, we focus on a wider perspective on the application of STT devices involving exploring combination of spin and charge devices and searching for computation models enabled by their unique capabilities.

#### 1.2. Spin Devices

Every atom is composed of a nucleus and one or more electrons, where electrons are orbiting around the nucleus. Thus electron has an orbital angular momentum. However,

the experimental evidence suggests that an electron has an intrinsic angular momentum, which comes from the spin of the electron. Electrons with unidirectional electron spin moment results in magnet with non-zero moment, or in other words, electron is a magnet. Some atoms, such as Fe<sup>2+</sup>, Co<sup>3+</sup>, Mn<sup>2+</sup>, have oxidation states with incomplete electronic sub-shells, occurring in the 3d shells of the transition elements. These elements can produce magnetic moments. The electron spin can be manipulated using external magnetic field or spin-transfer torque effect [1][2]. In the following subsections, we will discuss the magnet switching energy and the above two magnet switching mechanisms.

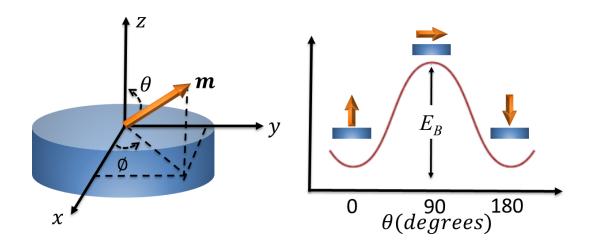

Fig. 1.1 Nano-magnet with uniaxial anisotropy and corresponding energy landscape

#### 1.2.1. Magnet Switching Energy

In a nano-magnet, up-spin (0°) and down-spin (180°), as shown in Fig. 1.1, are used to denote two stable states. The anisotropy barrier is introduced to stabilize the magnetic moment along one direction as illustrated in Fig. 1.1. The information can be encoded as nano-magnet magnetization directions. Note that, nano-magnets can be used as non-volatile bi-stable elements due to the fact that the anisotropy barrier exists without the need for an external power supply. The information retention time ( $T_{rt}$ ) of a nano-magnet is expressed as follow:

$$T_{rt} = T_0 \exp(\frac{K_u V}{K_B T}) \tag{1.1}$$

where,  $T_0$  denotes the characteristic time,  $K_u$  is the magnetic anisotropy, V represents the nano-magnet volume,  $K_B$  is the Boltzmann's constant and T is the temperature in Kelvin [27]. Typically, around ten years of retention time can be achieved when the energy barrier ( $E_B = K_u V$ ) is around  $40K_B T$ .

#### 1.2.2. Magnetic Field Switching

One way of manipulating the magnetization direction of a nano-magnet is using an external magnetic field generated by a current-carrying wire. The minimum magnetic field required to switch the magnet is called *critical magnetic field* ( $H_c$ ), which can be expressed as:

$$H_c = 2\frac{K_u}{M_s} \tag{1.2}$$

where, Ms denotes saturation magnetization. For example, if we want to switch the magnet from up-spin (0°) to down-spin (180°), in general, there are two scenarios to switch the magnet using external magnetic field. In the first scenario, a critical magnetic field ( $H_c$ ) is first applied perpendicular (90°) to the easy-axis, namely along the hard-axis. Then a small bias field ( $H_{bias}$ ), which can be ~10% $H_c$ , is applied along the easy-axis (180°). When the 90°  $H_c$  magnetic field is removed, the magnet can be switched from up-spin (0°) to down-spin (180°).

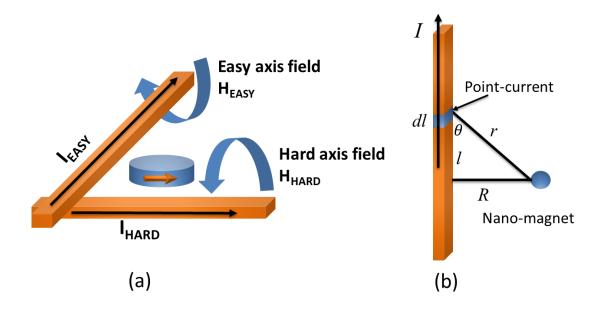

The layout of two orthogonal wires generating two orthogonal fields are shown in Fig. 1.2a. The relationship between the current and the generated magnetic field can be described by Biot-Savart law:

$$B = I \frac{\mu_0}{4\pi} \int \frac{dl \sin \theta}{r^2} \tag{1.3}$$

where, as shown in Fig. 1.2b, I is the current flowing through the wire, l is the distance from the point-current element to the closest point of the wire to the nanomagnet, r is the distance from the point-current element to the nanomagnet.

Fig. 1.2 (a) Two orthogonal wires generate two orthogonal fields  $H_{HARD}$  and  $H_{EASY}(b)$  magnetic field generation using current carrying wire

In the second scenario of magnetic switching, the critical magnetic field is directly applied along the easy-axis (180°). Compared to the first scenario, it only requires one magnetic field. However, the nano-magnet switching time is slower than that of first scenario. In both scenarios, the magnetic field is not localized and is energy inefficient. In addition, the magnetic field switching method is also not scalable for applications that require high density of on-chip nano-magnets.

### 1.2.3. Spin-Transfer Torque Switching

A more efficient way to switch a nano-magnet involves exploiting the current induced spin-transfer torque effect as we will describe next.

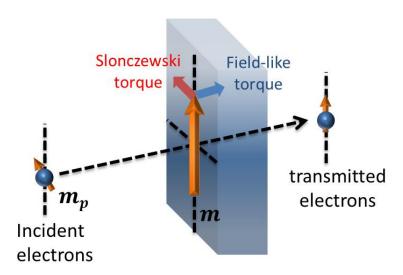

Fig. 1.3 Slonczewski torque and field-like torque on the nano-magnet due to the flowing of spin-polarized current

The behavior of the magnetization of the nano-magnet can be modeled using the Landau-Lifshitz-Gilbert equation with other terms describing the interaction between spin current and nano-magnets [1][2][23]:

$$\frac{d\mathbf{m}}{dt} = -|\gamma|\mathbf{m} \times \mathbf{H}_{eff} + \alpha \mathbf{m} \times \frac{d\mathbf{m}}{dt} + \mathcal{T}$$

(1.4)

where m is a unit vector pointing to the magnetization direction of nano-magnet,  $\gamma$  is the gyromagnetic ratio,  $H_{eff}$  denotes the effective magnetic field, and  $\alpha$  is the Gilbert damping factor.  $\tau$  represents the current induced torques that we will describe in details in this subsection.

$$\boldsymbol{H}_{eff} = \boldsymbol{H}_{ani} + \boldsymbol{H}_{exch} + \boldsymbol{H}_{ext} + \boldsymbol{H}_{M} + \boldsymbol{H}_{noise}$$

(1.5)

The first term in equation-1.4 describes the magnetization *precession* resulting from effective magnetic field, which may include anisotropy field ( $H_{ani}$ ), exchange magnetic field ( $H_{exch}$ ), external magnetic field ( $H_{ext}$ ), magneto-static field ( $H_{M}$ ) and thermal noise term ( $H_{noise}$ ), as shown in equation-1.5 [115]. Anisotropy field comes from the anisotropy effect observed in ferromagnetic bodies resulting from the lattice structure and the particular symmetries in certain crystals. The *easy directions* in this dissertation are certain energetically favorable directions in a given magnetic materials without external

magnetic field. The exchange field arises from the exchange phenomenon (i.e. ferromagnetism and anti-ferromagnetism) observed in a large magnet composed of many smaller ferromagnetic particles. Unlike the exchange fields coming from the nearest neighbor coupling between magnetic particles, the magneto-static field (i.e. demagnetizing field) represents the long range coupling. It comes from the fact that the magnetic particle in a ferromagnetic body can be affected by the magnetic fields generated from the rest of the magnetic particles. Thermal effects are modeled using a stochastic Gaussian magnetic field,  $H_{noise}=(H_{noise-x}, H_{noise-z})$ . The mean of this Gaussian distribution is zero, while the standard deviation is  $\sqrt{2\alpha K_B T/\gamma M_s V \Delta t}$  [127], where  $K_B$  is Boltzmann's constant, T is temperature in Kelvin,  $M_s$  is the saturation magnetization, V is the volume of free layer and  $\Delta t$  is the time step used in solving LLG equation.

The second term, called *Gilbert damping* term, describes the nonlinear spin relaxation phenomenon due to spin-orbit coupling [147]. It represents the damping rate at which m reaches equilibrium.

In general, the last term  $\tau$  represents current induced torques that take Slonczewski (i.e. spin-transfer torque) term and field-like term as shown in Fig. 1.3. Spin-transfer torque effect was theoretically predicted by Slonczewski1 [1] and Berger [2]. It comes from the interaction between spin current and a nano-magnet. Since a nano-magnet has unequal up-spin and down-spin density of states, the currents flowing through a nano-magnet is spin-polarized. Thus, a nano-magnet can act as a spin-polarizer whose direction is determined by the magnetization. The non-collinear spin-polarized electrons experience an exchange field trying to align the electron spins in the same direction of the nano-magnet, when they flow through the nano-magnet. This exchange field is the same field that aligns all the spins in the nano-magnet. Correspondingly, due to angular momentum conservation, the nano-magnet also experience a torque of equal magnitude but opposite sign at the same time. This torque is called *spin-transfer torque* (STT), which can be employed to switch the magnetization. It can be expressed as follows:

$$\tau_{STT} = -\frac{\gamma \hbar}{2eM \, V} \, \boldsymbol{m} \times (\boldsymbol{m} \times \boldsymbol{I}_s) \tag{1.6}$$

where,  $\hbar$  is the Plank's constant, e is the electron charge,  $M_s$  denotes the saturation magnetization of the magnet, and V represents the volume of the magnet. The spin current  $(I_s)$  is determined by the device geometry and materials combination, which will be described in the next chapter.

Generally, a field-like torque is also generated in asymmetric layered systems shown as follows:

$$\tau_{fl} = -\frac{\gamma \hbar}{2eM_s V} \beta m \times I_s \tag{1.7}$$

where,  $\beta$  is the ratio of this field-like torque strength to the Slonczewski torque. The magnitude of these two torques is dependent on the material and the device structures. Note that, for giant-magneto resistance (GMR) devices, the field like term is typically negligible as transverse spins dephase rapidly [184]. While for tunneling magneto resistance (TMR) devices, besides the in-plan torque predicted by Slonczewski, this field-like (out of plane) torque is proven significant in modeling the dynamics of magnet [187].

Following the recent discoveries of various physical phenomena involved in the current induced switching of nano-magnets, there have been various devices based on spin-transfer torque for memory and logic applications. In next chapter, we will discuss various spin-transfer torque devices that are employed in our research.

#### 1.3. Organization

This dissertation conducts synergistic exploration in architecture, circuit and device levels for Boolean and brain-inspired computing using spin-transfer torque devices. Compared with state of the art CMOS designs, the spin based Boolean threshold logic design and brain-inspired computing can achieve ultra-low energy consumption. The remaining part of this dissertation is organized as follows.

Chapter 2 reviews several spin-transfer torque devices, including vertical spin value, lateral spin valve, magnetic domain wall strip and spin-orbit torque devices. The associated underlying physical phenomena in these STT devices are also described in this chapter.

Chapter 3 explores the spin based Boolean computation in threshold logic design. Memristive cross-bar array is employed to perform current mode summation of binary inputs in the proposed spin-memristor threshold logic gate design. The low power, current mode spintronic threshold device is used to carry out the energy efficient threshold operation. Compared with state of the art CMOS threshold logic design, the proposed spin-memristor threshold logic achieves around two orders of magnitude lower energy consumption.

In chapter 4, we propose an energy efficient hardware mapping of a novel brain-inspired computing scheme - Hierarchical temporal memory (HTM) that tries to mimic the computing in cerebral neocortex. In HTM design, ultra-low power, magneto metallic hard-limiting spin-neurons combined with memristive cross-bar array (MCA) are explored in the dot product based pattern matching, which is the core computing block in HTM hardware. Such a direct mapping of the core-computing primitive of the cortical computing system can be very attractive for large-scale and energy efficient design.

In chapter 5, we present a spin-transfer torque (STT) device based on Domain Wall Motion (DWM) magnetic strip that can efficiently implement a Soft-limiting Non-linear Neuron (SNN) operating at ultra-low supply voltage and current. In contrast to previous spin-based neurons that can only realize hard-limiting (i.e. step function) transfer functions, the proposed STT-SNN displays a continuous resistance change with varying input current, and can therefore be employed to implement a soft-limiting neuron transfer function. We also present an artificial neural network (ANN) hardware design employing the proposed STT-SNNs and MCA as synapses. The ultra-low voltage operation of the magneto metallic STT-SNN enables the programmable MCA-synapses, computing analog domain weighted summation of input voltages, to also operate at ultra-low voltage. We modeled the STT-SNN using micro-magnetic simulation and evaluated them using a feed-forward ANN for character recognition. Comparisons with analog and digital CMOS neurons show that STT-SNNs can achieve more than two orders of magnitude lower energy consumption.

Chapter 6 shows that the dynamics of injection locked Spin Hall Effect Spin-Torque Oscillator (SHE-STO) cluster can be exploited as a robust primitive computational operator for associative computing. A cluster of SHE-STOs can be locked to a common frequency and phase with an injected AC current signal. DC inputs to each STO from

external stimuli can conditionally unlock some of them. Based on the input DC signal, the degree of synchronization of the SHE-STO cluster is detected by CMOS interface circuitry. The degree of synchronization can be used for associative computing/matching. We present a numerical simulation model of SHE-STO devices based on Landau-Lifshitz-Gilbert (LLG) equation with spin-transfer torque (STT) term and Spin Hall Effect (SHE). The model is then used to analyze the frequency and phase locking properties of injection locked SHE-STO cluster. Results show that associative computing based on the injection locked SHE-STO cluster can be energy efficient and relatively immune to device parameter variations and thermal noise.

Finally, the concluding remarks are available in chapter 7. Spin-transfer torque devices are unlikely to be drop-in replacements for CMOS. They may be integrated with CMOS and other charge based devices to model energy efficient computing systems. The proposed new computing models in Boolean and brain-inspired computing are inherently suited to the characteristics of STT devices, thereby attaining performance that CMOS cannot achieve.

### 2. SPIN-TRANSFER TORQUE DEVICES

In this chapter, we review several spin-transfer torque devices, including vertical spin value, lateral spin valve, magnetic domain wall strip and spin-orbit torque devices. The associated underlying physical phenomena in these STT devices are also described in this chapter. In the latter chapters of this dissertation, the fundamental STT devices described in this chapter will be employed as the building blocks in Boolean and brain-inspired computing.

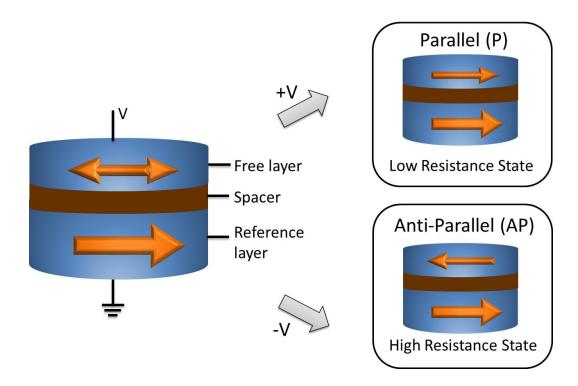

#### 2.1. Vertical Spin Valve

The device structure of vertical spin valve is shown in Fig. 2.1. It consists of a fixed ferromagnetic layer (reference layer), a free ferromagnetic layer (free layer) and a spacer in between. Historically, this device structure is used as a sensor by exploiting the resistance dependence on the magnetic orientation in the vertical spin valve. In 1975, Julliere [6] discovered Tunneling Magneto-Resistance (TMR) effect when the spacer between two ferromagnetic layers is insulator. In such TMR vertical spin valve device, the resistance is higher when the magnetization of two ferromagnetic layers are antiparallel compared to the resistance of parallel magnetization configuration. The magnetoresistance (MR) ratio defined as  $\Delta G/G_{AP}$  in percentage is used to characterize vertical spin value, where  $\Delta G$  is the difference of the conductance between parallel (P) configuration and anti-parallel (AP) configuration and  $G_{AP}$  is conductance of AP configuration. In Julliere's work [6], MR is ~14% in a Fe/GeO/Co vertical spin valve at  $T=\sim 4.2K$  (T is the temperature). In 1988, Fert and Grunberg [7][29] discovered the similar resistance dependence on the magnetic orientation in a vertical spin valve with a metallic spacer, which is called *Giant Magneto-Resistance* (GMR). In Fert's work [7], a vertical spin valve with Fe/Cr super lattices structure can achieve MR ratio ~80% at T =  $\sim 4.2K$ . After these pioneering works, more works on GMR and TMR effects has been developed [10]-[12], [30]-[34].

When the spin-polarized electrons travel through the vertical spin valve with metallic spacer, the spin scattering effect causes the GMR effect. Specifically, electrons experience little scattering and can pass through the vertical spin valve easily when the device is in parallel magnetization orientations. While for anti-parallel configuration, electrons experience more spin scattering when passing through the vertical spin valve. It makes electrons difficult to pass through the device. Thus, the conductance of parallel configuration is higher than that of anti-parallel configuration.

Fig. 2.1 Physical structure of a vertical spin value and its two states, corresponding to low and high resistance state

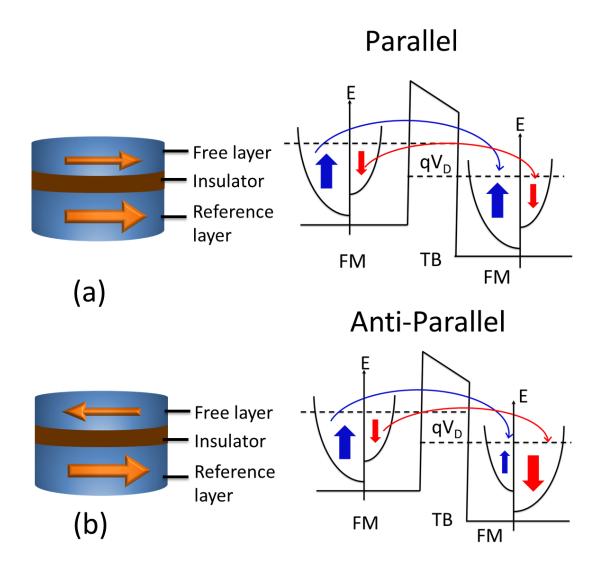

A Magnetic Tunnel Junction (MTJ), as shown in Fig. 2.2, consists of two nanomagnets separated by an insulator. The band structures of parallel MTJ and anti-parallel MTJ are shown in Fig. 2.2a and Fig. 2.2b, respectively. In MTJ, the ferromagnetic layer

acts as polarizer of electron spin. The TMR effect in an MTJ can be explained by the *spin filtering effect*, where the tunneling probability of electrons across the tunnel barrier depends on the relative magnetization of the reference and free ferromagnetic layers [6], [10]-[12]. As shown in Fig. 2.2, the electrons can only tunnel into the sub-band of the same spin orientation in the absence of spin-flip processes. For example, in the MTJ parallel configuration shown in Fig. 2.2a, the sub-bands of two ferromagnetic layers (FM) are well matched, namely the number of filled and empty electronic states for each spin are well matched. On the other hand, the sub-bands of anti-parallel MTJ is not matched. Thus, larger number of electrons can tunnel through the parallel MTJ than anti-parallel MTJ, leading to a larger tunneling conductance of parallel MTJ than anti-parallel MTJ.

Fig. 2.2 Physical structure of MTJ and its band structure of parallel and anti-parallel configurations

The MTJ tunneling conductance can be expressed as:

$$G(\theta) = \frac{1}{2}(G_P + G_{AP}) + \frac{1}{2}(G_P - G_{AP})\cos\theta$$

(2.1)

where  $\theta$  is the relative angle of two ferromagnetic layers,  $G_{AP}$  and  $G_P$  are the antiparallel ( $\theta$ =180°) and parallel ( $\theta$ =0°) MTJ conductance, respectively. Then the TMR ratio is defined as:

$$TMR \ Ratio = \frac{G_P - G_{AP}}{G_{AP}}$$

(2.2)

Typically, the spin filtering effect enhances the MR ratios of MTJ, which makes it much higher than those of GMR based vertical spin valves. Furthermore, the MTJ resistance difference between P and AP configurations are much higher than that of GMR based vertical spin valve due to the employment of insulator as spacer.

So far, we have discussed that the vertical spin valve can be easily used as a sensor to detect the magnetic state of a nano-magnet by exploiting the GMR or TMR effects. However, for memory and logic applications, manipulation of the magnetic state is also necessary. Next, we will discuss how to manipulate the magnetization of the free layer in the vertical spin valve using current induced spin-transfer torque as we described in the previous subsection.

Since the electron spins get polarized flowing through the FM layer, they exert spintransfer torque on the FM layer magnetization. For the reference layer, the magnetization is strongly pinned so that STT is negligible. While for the free layer, the STT can switch the magnetization direction or drive the magnetization into a sustained oscillation based on the orientation of the magnetization and the spin current polarization. Thus, the spin current generated by the vertical spin valve can be expressed as:

$$I_s = \eta I m_p \tag{2.3}$$

Where  $I_s$  is the spin-polarized current, I is the charge current,  $m_p$  is the FM layer magnetization direction and  $\eta$  indicates the ratio of charge current magnitude to spin-polarized current magnitude. The magnitude of  $\eta$  may depend on the voltage across vertical spin valve, m and  $m_p$  [185]. Note that, MTJ is more efficient at generating spin-polarized current than GMR based vertical spin valve due to the spin filtering effect.

#### 2.2. Lateral Spin Valve

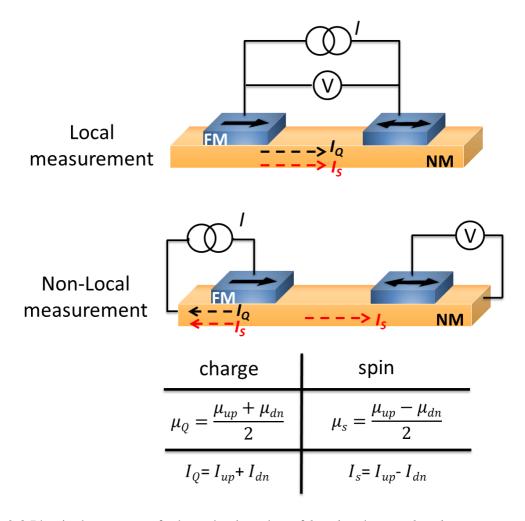

Fig. 2.3 shows the physical structure of lateral spin valve (LSV) with local and non-local measurements [35]-[39]. LSV consists of two ferromagnetic contacts (FM) deposited on a non-magnetic (NM) channel. As shown in Fig. 2.3, there are two ways to measure the magneto-resistance effect in LSV, namely local and non-local measurements. For local measurement, it is similar to a vertical spin valve with a structure of

FM/NM/FM. Thus the magneto-resistance effect is also observed [35]. For non-local measurement of lateral spin valve, authors in [36][37] discovered that voltage on the FM detector contact can be modulated by current injection through the FM injector contact. It depends on the current injection and the distance between the injector and the detector.

In the non-local measurement, though a current is injected through the FM injector contact, this current does not flow through the FM detector contact or the NM channel underlying the detector contact. The electron transport spin drift diffusion model can be used to explain LSV non-local effect [41]. Firstly, the FM injector spin-polarizes the injected electrons. As a result, the number of spins with same magnetization direction as FM injector is larger than that of opposite spins in the underlying non-magnetic channel. This imbalance of spins leads to non-equilibrium spin accumulation, thus a spin voltage in the NM. Note that, the spin voltage is the defined as the *electrochemical potential* (ECP) difference between the *up-spin potential* ( $\mu_{up}$ ) and *down-spin potential* ( $\mu_{dn}$ ). Due to the spin voltage across the non-magnetic channel, one type of spins flow in one direction ( $I_{up}$ ), while the other type of spins flow in the opposite direction ( $I_{dn}$ ). As shown in Fig. 2.3, the charge current is defined as  $I_Q=I_{up}+I_{dn}$  and the spin current is defined as  $I_S=I_{up}-I_{dn}$ . Since  $I_{up}$  and  $I_{dn}$  have the same magnitude, but opposite directions, the charge current in the non-magnetic channel is zero and the spin current is non-zero.

Fig. 2.3 Physical structure of a lateral spin valve of local and non-local measurements that has been made to experimentally observe magneto-resistance effect and pure spin-current generation.

Typically, the spin current generation efficiency in lateral spin valve is mainly limited by two factors: spin injection efficiency at the FM injector contact and the spin flip length in the NM channel. The spin injection efficiency at FM/NM interface can be improved by inserting a tunnel barrier between FM and NM, as shown experimentally in [37]. In the non-magnetic channel, the spin current decays exponentially because of the spin flip processes, leading to reduced magnitude of spin current to the FM detector contact. Several research works [35]-[38], [42][43] have investigated different NM channel materials with different spin flip lengths ( $\lambda_{sf}$ ) for implementing energy efficient

lateral spin valves. The pure spin current generation efficiency can be improved by exploring LSV material combinations. In this non-local LSV experiment [44], the non-local spin current was proven large enough to switch the magnetization of the FM detector. Therefore, by measuring the magnetization of FM detector contact, we can detect the non-local spin current in the LSV. Based on non-local LSV, "all-spin" based computation was proposed in [21].

#### 2.3. Magnetic Domain Wall Strip

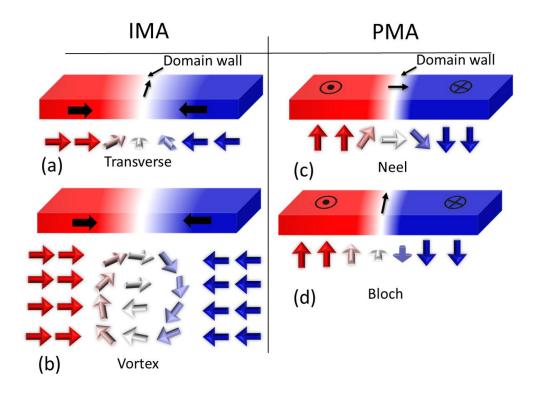

So far, the spin current we have discussed are generated by injecting current through a spin valve and the exerted STT is used to manipulate another nano-magnet. Besides spin valve structure, it has been experimentally shown that the spin current can also be generated in a magnetic domain wall strip. Fig. 2.4 shows a ferromagnetic wire, called magnetic domain wall stripe (DWS), with a nanowire-like geometry and opposite magnetization at its two ends. The magnetization transition region along the DWS from one direction to the opposite direction is called *domain wall* (DW), whose structure and size are dependent on the DWS geometry and material properties.

Fig. 2.4 shows several typical DW structures in a DWS [45][46], [189]-[193]. When the shape anisotropy dominates in materials such as Permalloy, NiFe or Py, the magnetic domains lie along the wire axis (in-plan magnetic anisotropy, IMA). The domain wall in such materials can be either transverse or vortex type. In a thin and narrow magnetic nano-strip, a transverse DW is typically formed. While, the vortex domain wall occurs when the magnetic nano-strip is relatively wider and thicker [189][190]. As shown in the right column of Fig. 2.4, the DWS has a strong perpendicular magnetic anisotropy (PMA, such as Co/Ni magnetic multilayers), where the magnetic domains are magnetized in the out-of-plane directions. A Neel type DW usually occurs in a narrower PMA DWS, while a Bloch type DW typically forms in a wider PMA DWS. Typically, the probabilities of left-handed and right-handed rotations of the DW are equal. However, an additional Dzyaloshinskii-Moriya interaction (DMI) [191][192] can favor and stabilize a particular DW configuration [45][46][193] in the presence of broken inversion symmetry.

Fig. 2.4 Typical domain wall structure (a) in-plane magnetic anisotropy transverse head-to-head transverse DW (b) IMA vortex DW, (c) perpendicular magnetic anisotropy nanowire with Neel DW, and (d) PMA Bloch DW.

An external magnetic field can be used to move domain walls in magnetic nano-wire. However, similar to the switching of magnetization in spin valves due to current induced STT, a more energy efficient way to induce domain wall motion is applying an electrical current along the domain wall strip [40][46], [77]-[80]. When electrons flow through a fixed domain in the DWS, they become spin-polarized. The spin-polarized electrons exert spin-transfer torque on the magnetic moments in and around the domain wall region. If the applied current density is above the *critical current density*, the exerted STT can overcome the pinning force, leading to steady domain wall motion (DWM). The critical current density is defined as the minimum current density applied along DWS to induce a steady DWM. Its magnitude is proportional to hard-axis anisotropy and the domain wall length. Earlier current induced domain wall motion experiments are based on IMA ferromagnetic nanowires with the critical current density in the order of ~10<sup>8</sup>A/cm<sup>2</sup>.

Several issues, such as excessive Joule heating and reliability concerns, may accompany this relative high current density. In order to reduce the critical current density of DWM, a scaled PMA DWS is used in [126]. The hard-axis anisotropy of a PMA device reduces with lower device thickness and becomes much smaller than that of an IMA device. Moreover, the DW length in a PMA DWS is in general smaller than that in an IMA DWS. Therefore, a scaled PMA magnetic nano-strip can achieve much lower critical current density to induce steady DWM, leading to smaller power consumption.

#### 2.4. Spin-Orbit Torque

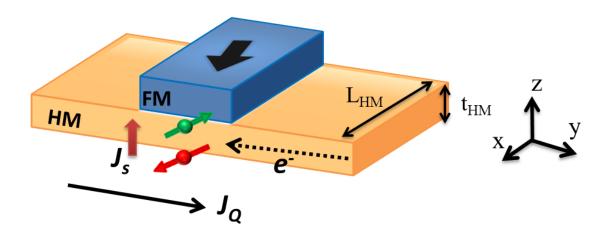

In spin valve or DWS, the spin current is generated by passing charge current through a FM or spin polarizer. In these cases, the efficiency of generating spin current from charge current is limited by the polarization efficiency of the FM. Recent experiments show that spin current can be generated more efficiently through spin-orbit interaction (SOI) [50]. Later on, current induced SOI was experimentally demonstrated in I/FM/HM structure (I: Insulator, FM: Ferro-magnet, and HM: non-magnetic heavy metal) and applied in efficient magnetization switching [48]-[55], domain wall motion [45]-[47], [56], and spin-torque oscillations [49][57][58].

Fig. 2.5 Charge current applied in non-magnetic heavy metal with strong spin-orbit coupling is converted to pure spin current due to spin Hall effect

The observed phenomenon can be explained by either Rashba effect [47][60] or Spin Hall Effect [61]. Rashba effect arises from the broken structural inversion symmetry in a material system [47][60]. This structural inversion asymmetry first produces an electrical potential along the asymmetry direction. When electrons travel through this electrical potential, they experience an effective magnetic field. This magnetic field induces spin polarization of electrons based on the magnetic momentum. Therefore, a pure spin current can be generated. The other explanation of the observed phenomenon is based on Spin Hall Effect (SHE) [61]. Referring to Fig. 2.5, when electrons flow through a non-magnetic heavy metal (HM) (in  $\pm y$  direction) with strong spin-orbit coupling, opposite electron spins accumulate on the opposite surfaces of HM. Thus, a pure spin current ( $I_s$ ) in the  $\pm z$  direction is generated, which exerts a spin-transfer torque on the adjacent FM. The STT will switch the magnetization or drive the FM into steady oscillation. The relationship between the generated spin current ( $I_s$ ) and the applied charge current ( $I_0$ ) can be expressed as follows:

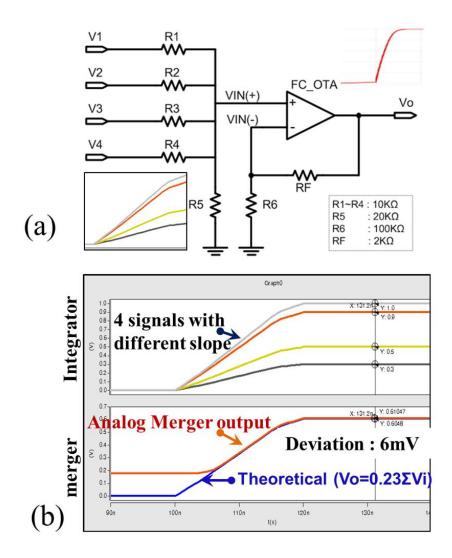

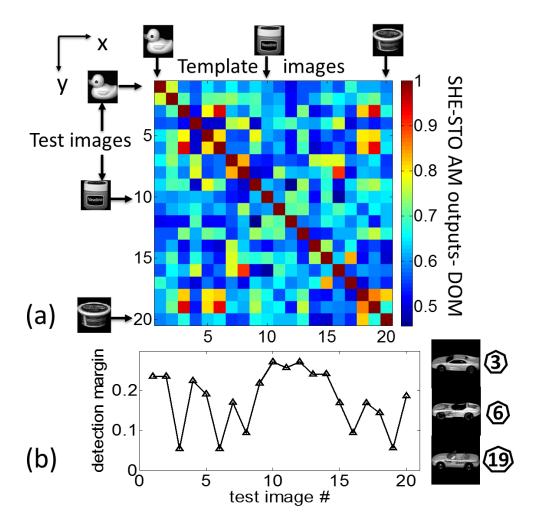

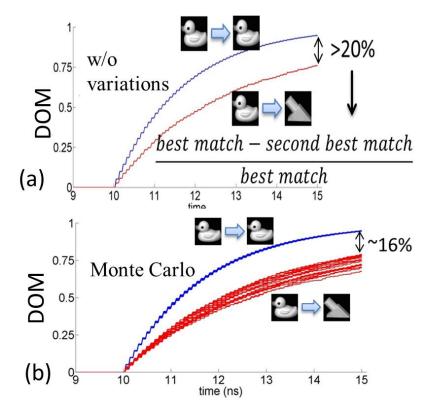

$$\boldsymbol{I}_{s} = \frac{A_{FM}}{A_{SH}} \, \theta_{SH} (\boldsymbol{\sigma} \times \boldsymbol{I}_{Q}) \tag{2.4}$$