# Utah State University DigitalCommons@USU

All Graduate Theses and Dissertations

**Graduate Studies**

5-1974

# Asynchronous Logic Design with Flip-Flop Constraints

David Franklin Cox Utah State University

Follow this and additional works at: https://digitalcommons.usu.edu/etd

Part of the Electrical and Computer Engineering Commons

### **Recommended Citation**

Cox, David Franklin, "Asynchronous Logic Design with Flip-Flop Constraints" (1974). *All Graduate Theses and Dissertations*. 6956. https://digitalcommons.usu.edu/etd/6956

This Dissertation is brought to you for free and open access by the Graduate Studies at DigitalCommons@USU. It has been accepted for inclusion in All Graduate Theses and Dissertations by an authorized administrator of DigitalCommons@USU. For more information, please contact digitalcommons@usu.edu.

### ASYNCHRONOUS LOGIC DESIGN WITH

## FLIP-FLOP CONSTRAINTS

### by

### David Franklin Cox

# A dissertation submitted in partial fulfillment of the requirements for the degree

of

### DOCTOR OF PHILOSOPHY

in

Electrical Engineering

Approved:

UTAH STATE UNIVERSITY Logan, Utah

### ABSTRACT

Asynchronous Logic Design with Flip-Flop Constraints

David Franklin Cox, Doctor of Philosophy Utah State University, 1974

Major Professor: Ronald L. Thurgood, Ph.D. Department: Electrical Engineering

Some techniques are presented to permit the implementation of asynchronous sequential circuits using standard flip-flops. An algorithm is presented for the RS flipflop, and it is shown that any flow table may be realized using the algorithm (the flow table is assumed to be realizable using standard logic gates). The approach is shown to be directly applicable to synchronous circuits, and transition flip-flops (JK, D, and T) are analyzed using the ideas developed. Constraints are derived for the flow tables to meet to be realizable using transition flipflops in asynchronous situations, and upper and lower bounds on the number of transition flip-flops required to implement a given flow table are stated.

(121 pages)

х

by

# ASYNCHRONOUS LOGIC DESIGN WITH

•

. -.

## FLIP-FLOP CONSTRAINTS

by

### David Franklin Cox

# A dissertation submitted in partial fulfillment of the requirements for the degree

of

### DOCTOR OF PHILOSOPHY

in

# Electrical Engineering

Approved:

UTAH STATE UNIVERSITY Logan, Utah

#### ACKNOWLEDGMENTS

With sincere appreciation, I would like to thank Dr. Ronald Thurgood for his encouragement and help, and for being both advisor and friend during the preparation of this thesis.

I would also like to thank Dr. Alvin Despain for his inspiring discussions of pertinent points and critical review of the final paper. A special note of thanks go to Dr. Glen Smerage, Dr. William Jones, and Professor William Fletcher for their support. I am very grateful to Dr. Michael Windham of the Math department for taking the time to serve on my committee, and for providing a sympathetic ear in times of need.

Finally, to my wife, Chris, for her patience in typing the rough and final drafts, and to my children, Shaun and Kelli, I extend a husband's and father's gratitude for the sacrifices they have made.

David Franklin Cox

# TABLE OF CONTENTS

|                                                                                             | Page                                         |

|---------------------------------------------------------------------------------------------|----------------------------------------------|

| CHAPTER I INTRODUCTION                                                                      | 1                                            |

| Combinational and sequential systems<br>Synchronous and asynchronous sequential systems     | 1<br>2                                       |

| CHAPTER II CLASSICAL ASYNCHRONOUS LOGIC DESIGN                                              | 4                                            |

| Asynchronous problem formulation                                                            | 4<br>7<br>12<br>15                           |

| CHAPTER III HAZARDS AND RACES                                                               | 18                                           |

| Logic delays                                                                                | 18<br>21<br>22<br>24                         |

| CHAPTER IV BISTABLE ASYNCHRONOUS SUBSYSTEMS                                                 | 28                                           |

| Flip-flop types                                                                             | 28<br>29<br>30<br>31                         |

| CHAPTER V AN ALGORITHM FOR DESIGNING ASYNCHRONOUS SEQUENTIAL CIRCUITS USING RS FLIP-FLOPS . | 33                                           |

| Characteristic map equation                                                                 | 33<br>36<br>41                               |

| CHAPTER VI AN APPLICATION OF THE MAP-METHOD TO<br>SYNCHRONOUS CIRCUITS                      | 42                                           |

| Problems in synchronous design                                                              | 42<br>43<br>46<br>48<br>49<br>50<br>50<br>52 |

# TABLE OF CONTENTS (continued)

|                                                                             |                    |   |                       | Page                                                                                         |

|-----------------------------------------------------------------------------|--------------------|---|-----------------------|----------------------------------------------------------------------------------------------|

| RS flip-flop                                                                | •<br>•<br>•        | • | •                     | 53<br>53<br>53<br>53<br>54<br>54                                                             |

| CHAPTER VII AN APPLICATION OF THE MAP-METHOD TRANSITION FLIP-FLOPS          |                    |   |                       | 56                                                                                           |

| Types of transition flip-flops<br>Clocked JK flip-flop                      | p-f1<br>JK<br>ze a |   | ·<br>·<br>·<br>·<br>· | 56<br>59<br>61<br>63<br>65<br>68<br>70<br>71<br>73<br>74<br>76<br>77<br>80<br>82<br>86<br>88 |

| CHAPTER VIII SUMMARY AND CONCLUSIONS                                        |                    |   |                       | 91                                                                                           |

| Summary                                                                     |                    | • |                       | 91<br>92                                                                                     |

| BIBLIOGRAPHY                                                                |                    |   |                       | 94                                                                                           |

| APPENDIXES                                                                  |                    |   |                       | 99                                                                                           |

| Appendix A Flow Table Reduction<br>Appendix B Column Transition Constraints | •                  | • | •                     | 100<br>104                                                                                   |

| VITA                                                                        | 0                  | • |                       | 111                                                                                          |

iv

# LIST OF FIGURES

| Figur | e                                      |       | Page |

|-------|----------------------------------------|-------|------|

| 1.    | Flow table form                        |       | 5    |

| 2.    | Normal fundamental mode primitive flow | table | 7    |

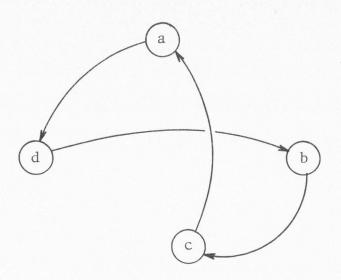

| 3.    | State diagram                          |       | 7    |

| 4.    | Pair chart for flow table of Figure 2  |       | 9    |

| 5.    | Minimized flow table                   |       | 12   |

| 6.    | Minimized state diagram                |       | 13   |

| 7.    | Necessary adjacencies                  |       | 14   |

| 8.    | Flow table with "transition" state .   |       | 15   |

| 9.    | Flow matrix                            |       | 15   |

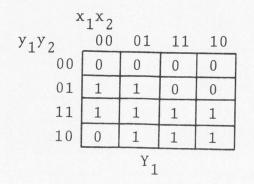

| 10.   | Karnaugh map for $Y_1$                 |       | 16   |

| 11.   | Karnaugh map for $Y_2$                 |       | 16   |

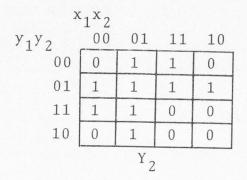

| 12.   | Partial Z-map                          |       | 16   |

| 13.   | Complete Z-map                         |       | 17   |

| 14.   | Critical race condition                |       | 19   |

| 15.   | Hazard situation                       |       | 19   |

| 16.   | Static "1" hazard for change in z      |       | 20   |

| 17.   | Functional hazard situation            |       | 21   |

| 18.   | Essential hazard condition             |       | 22   |

| 19.   | Nonessential hazard condition          |       | 23   |

| 20.   | Flow table derived from Figure 9       |       | 24   |

| 21.   | State and output maps for example of   |       |      |

|       | Chapter II                             |       | 26   |

v

| Figur | e                                                                                    | Page |

|-------|--------------------------------------------------------------------------------------|------|

| 22.   | Circuit diagram for example problem                                                  | 27   |

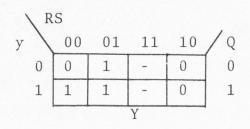

| 23.   | RS flip-flop flow table                                                              | 29   |

| 24.   | RS flip-flop flow matrix and output map                                              | 30   |

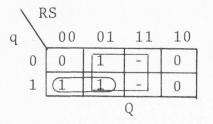

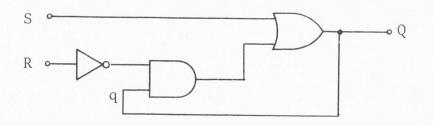

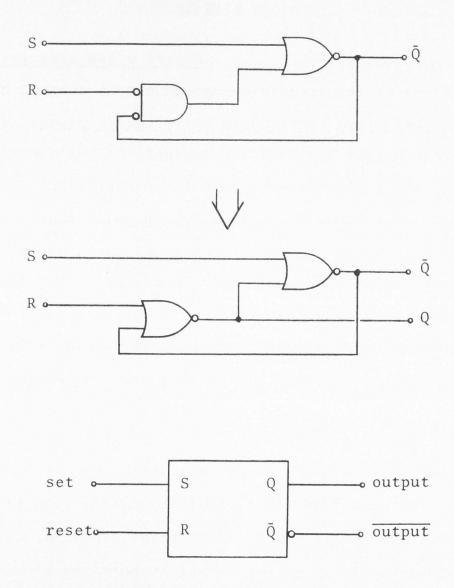

| 25.   | RS flip-flop circuit diagram                                                         | 31   |

| 26.   | RS NOR flip-flop and symbol                                                          | 32   |

| 27.   | State and output maps of Figure 21                                                   | 35   |

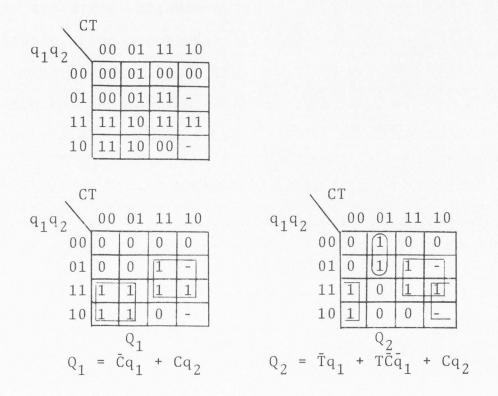

| 28.   | Characteristic map equation for $Q_1$                                                | 36   |

| 29.   | Complete specification for $Q_1$ excitation                                          | 38   |

| 30.   | Complete specification for ${\rm Q}_2$ excitation $% {\rm Q}_2$ .                    | 39   |

| 31.   | Flip-flop excitation expressions                                                     | 40   |

| 32.   | Sequential circuit with RS flip-flops                                                | 40   |

| 33.   | D flip-flop symbol, characteristic map, and                                          |      |

|       | characteristic equation                                                              | 44   |

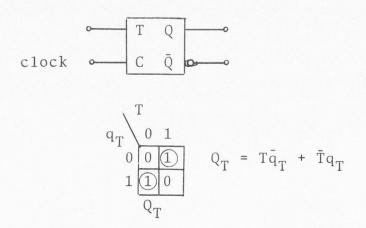

| 34.   | T flip-flop symbol, characteristic map, and                                          |      |

|       | characteristic equation                                                              | 44   |

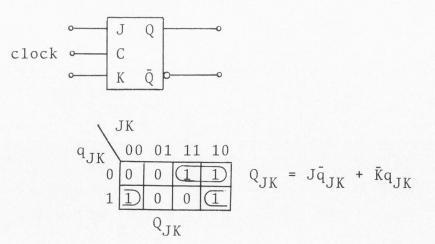

| 35.   | JK flip-flop symbol, characteristic map, and characteristic equation                 | 44   |

| 36.   |                                                                                      | 44   |

| 50.   | RST flip-flop symbol, characteristic map,<br>characteristic equation, and constraint |      |

|       | equations                                                                            | 45   |

| 37.   | Flow table for synchronous design                                                    | 46   |

| 38.   | Flow matrix for synchronous problem                                                  | 47   |

| 39.   | State maps for synchronous problem                                                   | 47   |

| 40.   | Input excitation maps for realization with                                           |      |

|       | D flip-flops                                                                         | 48   |

| Figur | e                                                                                  | Page |

|-------|------------------------------------------------------------------------------------|------|

| 41.   | Realization expression for T flip-flops                                            | 49   |

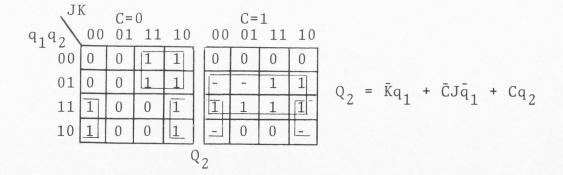

| 42.   | Realization expressions for JK flip-flops                                          | 50   |

| 43.   | Realization expressions for RST flip-flops                                         | 51   |

| 44.   | Clocked JK flip-flop primitive flow table and                                      |      |

|       | merged flow table                                                                  | 57   |

| 45.   | Clocked JK characteristic equations and maps .                                     | 58   |

| 46.   | Map equations with static constraints for JK flip-flop                             | 59   |

| 47.   | Possible "next state" entries in JK realizable                                     |      |

|       | flow table                                                                         | 62   |

| 48.   | Acceptable vertical transitions for JK flip-                                       |      |

|       | flop                                                                               | 62   |

| 49.   | Three-variable flow table column and ${\rm Q}^{}_3$ map $% {\rm Q}^{}_3$ .         | 64   |

| 50.   | Four-variable map column                                                           | 65   |

| 51.   | $Q_1 Q_2$ and $Q_3 Q_4$ maps with entry constraints and required column equalities | 67   |

| 52.   | Primitive and merged flow tables for D flip-                                       |      |

|       | flop                                                                               | 68   |

| 53.   | Flow matrix and characteristic equations for                                       |      |

|       | D flip-flop                                                                        | 69   |

| 54.   | Static state constraints on D flip-flop                                            | 70   |

| 55.   | Acceptable vertical transitions for D flip-                                        |      |

|       | flop                                                                               | 71   |

| 56.   | Clocked T flip-flop primitive flow table and merged flow table                     | 71   |

| 57.   | Clocked T flip-flop flow matrix and                                                |      |

|       | characteristic equations                                                           | 72   |

| Figur | e                                                                           | Page |

|-------|-----------------------------------------------------------------------------|------|

| 58.   | Clocked T flip-flop state constraints                                       | 72   |

| 59.   | Clocked T flip-flop acceptable vertical transitions                         | 73   |

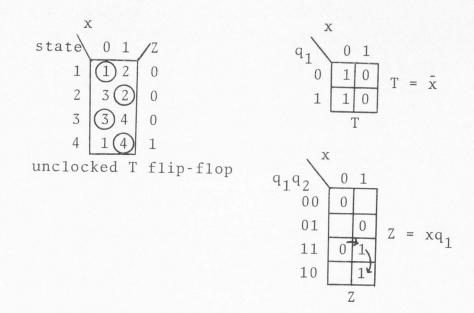

| 60.   | Unclocked T flip-flop flow table, flow matrix, and characteristic equations | 74   |

| 61    |                                                                             |      |

| 61.   | Unclocked T static state constraints                                        | 75   |

| 62.   | Unclocked T flip-flop acceptable states and transitions                     | 76   |

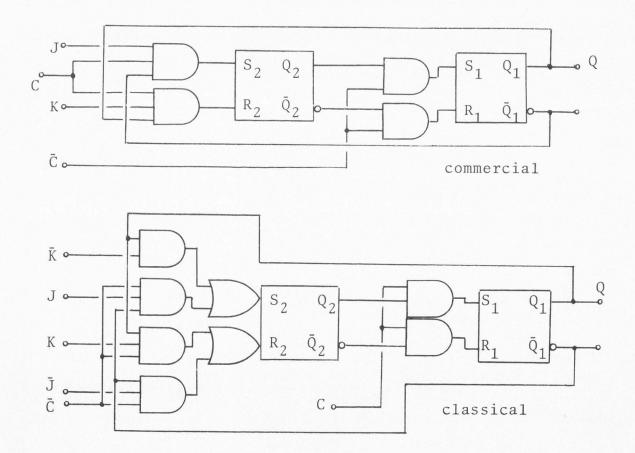

| 63.   | Commercial "one's-catching" and classical JK                                |      |

|       | realizations                                                                | 77   |

| 64.   | "One's-catching" JK flip-flop functional                                    | 70   |

| 65    | descriptives                                                                | 79   |

| 65.   | Generation of an RS flip-flop from a transition flip-flop                   | 81   |

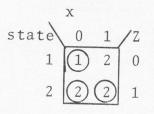

| 66.   | Simple two-state flow table                                                 | 83   |

| 67.   | Acceptable flow tables                                                      | 83   |

| 68.   | Flow matrices and input maps for JK and clocked                             |      |

|       | T flip-flops                                                                | 84   |

| 69.   | Flow matrices and input maps for D and unclocked T flip-flops               | 85   |

| 70.   | Four-state system implemented with one                                      | 00   |

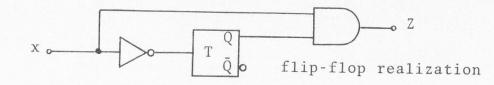

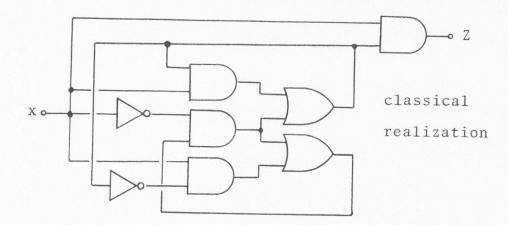

| 70.   | unclocked T flip-flop                                                       | 86   |

| 71.   | Schematic comparison of flip-flop and classical                             |      |

|       | realizations                                                                | 87   |

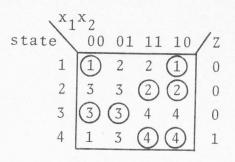

| 72.   | Reproduction of Figure 20                                                   | 88   |

| 73.   | Example problem of Chapter II realized with T                               |      |

|       | flip-flops                                                                  | 89   |

| F | igur | e                                              | Page |

|---|------|------------------------------------------------|------|

|   | 74.  | Transition-realizable flow table expansion for |      |

|   |      | flow table of Figure 72                        | 90   |

|   | 75.  | Example of merging process                     | 102  |

#### ABSTRACT

Asynchronous Logic Design with Flip-Flop Constraints

by

David Franklin Cox, Doctor of Philosophy Utah State University, 1974

Major Professor: Ronald L. Thurgood, Ph.D. Department: Electrical Engineering

Some techniques are presented to permit the implementation of asynchronous sequential circuits using standard flip-flops. An algorithm is presented for the RS flipflop, and it is shown that any flow table may be realized using the algorithm (the flow table is assumed to be realizable using standard logic gates). The approach is shown to be directly applicable to synchronous circuits, and transition flip-flops (JK, D, and T) are analyzed using the ideas developed. Constraints are derived for the flow tables to meet to be realizable using transition flipflops in asynchronous situations, and upper and lower bounds on the number of transition flip-flops required to implement a given flow table are stated.

(121 pages)

#### CHAPTER I

#### INTRODUCTION

### Combinational and sequential systems

The realm of basic logic design is usually broken into two major divisions. The first is normally called "combinational" logic design and consists of a set of input variables  $I_1$ ,  $I_2$ , ...  $I_n$ , a set of output variables  $O_1$ ,  $O_2$ , ...  $O_m$ , and a mapping f from the input variables to the output variables wherein the combinational design objective is to physically implement a logic device that is isomorphic to the mapping function f relating two sets of physically realizable logic variables. i.e.

(a) I = {I<sub>i</sub> | i = 1, 2, ... n},

(b) 0 = {0<sub>j</sub> | j = 1, 2, ... m},

(c) f : I

$$\rightarrow$$

0.

At any instant of time for a given input  $I_k$ , a unique output  $O_a$  can be accurately predicted.

The second major division of logic design is sequential logic design. Sequential circuits have inputs and outputs, but also require positing internal "states" to adequately describe them. Briefly, a sequential circuit (or machine) can be described as having the following properties (Hartmanis and Stearns, 1966):

1. A finite set of inputs that may be applied to the circuit in a sequential order.

2. A finite set of internal states in which the circuit may be in.

3. The next state of the circuit is determined by the present circuit state and the present input.

4. A finite set of outputs that are determined by the combination of circuit state and input.

The above properties can be concisely stated as follows:

(a) S is a finite nonempty set of states;

(b) I is a finite nonempty set of inputs;

(c) 0 is a finite nonempty set of outputs;

(d) N : S X I  $\rightarrow$  S is called the next state function;

(e)  $Z : S X I \rightarrow 0$  is called the output function.

It should be noted that the output function involves both the input and the state of the circuit. Sequential circuits that have this property are called "Mealy" circuits. If the output is a function of the circuit state only, the circuit is called a "Moore" circuit.

### Synchronous and asynchronous sequential systems

Sequential circuits can be subdivided into what are called "synchronous" and "asynchronous" sequential circuits. Synchronous sequential circuits are sequential circuits whose events are constrained to occur only at specified instances of time, and are usually controlled by a device that provides "clock" pulses. The clock pulses need not be evenly spaced in time but must be spaced far enough apart so that all transient circuit action has vanished at the time the next clock pulse occurs.

Asynchronous sequential circuits do not have a "clocking" constraint on them and their circuit action commenses from the time an input changes (assuming the circuit has started in a stable state) and stops only when it can achieve a state coexistent with the new input (known as a "stable" state). In this report some current methods used in asynchronous logic design will be outlined, and an algorithm will be presented wherein the asynchronous design can be implemented using standard set-reset flip-flops. A less formal method will be given for the transition-type flip-flops, and an application to synchronous sequential circuits will be outlined.

#### CHAPTER II

4

### CLASSICAL ASYNCHRONOUS LOGIC DESIGN

### Asynchronous problem formulation

D. A. Huffman presented a method for designing an asynchronous circuit from problem specifications in 1954. His method basically consists of reducing the problem statement to a flow table from which the state function, N, can be derived after some flow table manipulation (Huffman, 1954).

It is assumed that the inputs are known, and a certain sequence of inputs is to give a specified output sequence. The flow table is then constructed from the problem statement in the following form:

1. The columns of the flow table are unique to a given input

2. The rows of the flow table are unique to a given state.

3. If the intersection of the input column and state row is to indicate a stable condition in the circuit, then the entry in that position is given the label of the row that it is in, and circled to indicate that it is stable.

4. If a column-row intersection is unstable, the entry in that position is labeled according to the row it is to move to (the new state).

5. If a "don't care" condition arises, or an impossible

input condition is evident, then a dash is entered into the column-row intersection.

It should be clear that the entries in the flow table merely indicate the next state the circuit is to move into from a given input/state condition; i.e. the flow table is a tabular representation of the "next state" function N. See Figure 1 for the flow table form.

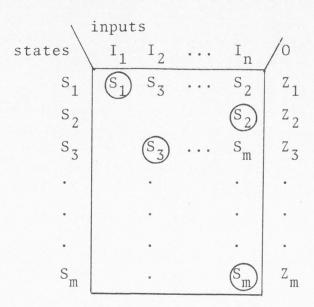

Figure 1. Flow table form.

If the flow table is constructed such that there is only one stable state per row, the table is called a primitive flow table. The output can be listed alongside each stateentry in the table, or it can be listed along the right side of the table as shown in Figure 1 if the table is primitive. If the outputs for transient states are known, they can be put in with the states shown. Usually these transient state outputs are left until later, however. An example (from Unger, 1969) will now be given to illustrate the procedure. A sequential circuit is to have two inputs,  $x_1$  and  $x_2$ , and one output, Z. Z is to go on when  $x_1$  goes on only if  $x_2$  was on during the previous "off" time of  $x_1$ .  $x_2$  is allowed to come on and go off during the "off" time of  $x_1$  as well as come on and stay on until after  $x_1$  goes on. Z is to go off when  $x_1$  goes off and wait for the sequence of events to reoccur.

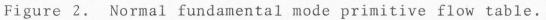

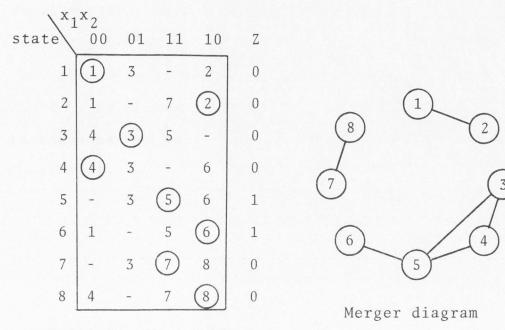

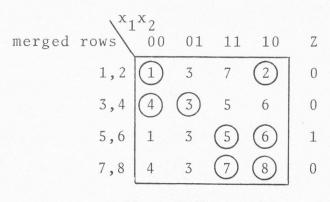

The primitive flow table is constructed from the statement of the problem by assuming an initial input and output condition. It will be convenient here to start with inputs and output set to zero. Figure 2 shows the completed primitive flow table. We will assume that simultaneous input changes do not occur (which simplifies Unger's problem). When only single input changes occur the operation is known as "normal mode", and when the inputs are allowed to change only when the system is in a stable state, the operation is "fundamental mode". Hence, Figure 2 is a normal fundamental mode primitive flow table. Dashes are placed in forbidden input transition spaces to indicate the "don't care" condition. A state diagram is shown in Figure 3, and is equivalent to the flow table but may provide a more intuitive interface between the word statement of the problem and the flow table.

Figure 3. State diagram.

# State reduction

The next step in the synthesis procedure is to try to reduce the number of states. This will generally (but not

always) reduce the gate-count of the final circuit. The method, bacically, is to compare pairs of rows and see if any combination of input changes will lead to the same state. If such is the case, then the two compared states are called "equivalent" and further comparisons can be made to see if all input changes take the rows to the same or equivalent states. The process is continued until all the states (rows) have been placed into equivalence classes. This effectively partitions the set of states into nonintersecting sets, the union of which consists of the initial primitive set of states. Each equivalence class will then represent one state in the final circuit.

The logical behavior of the sequential circuit will not be modified by eliminating redundant states. The method of Paull and Unger (1959) will be used (an alternate method is given in Appendix A). The state reduction consists of eliminating all incompatible pairs of states. To define "compatible" we have to first define "cover".

Definition: A state  $S_a$  of a flow table A is said to cover state  $S_b$  of flow table B if, for any finite input sequence, the output from A when started in  $S_a$  is identical to the output from B when started in  $S_b$  whenever the B output is specified.

Definition: Two states of a flow table are compatible if they are both covered by some row of a flow table A. A set of states of a flow table that are covered by a single

state of some flow table is called a compatible set, or a compatible.

A convenient way to check for incompatibles is by constructing a pair chart as shown in Figure 4. If two states that are assumed to be equivalent have different next state entries in one (or more) of their columns then the compatibility of the first two states implies the compatibility of the two different state entries in that column.

The states are now compared pair-wise and if an output incompatibility is noted, an "x" is placed in the pair intersection square. If no output incompatibility exists, then implied pairs are written in the square. If neither of the above occur, then the square is left blank.

|        | 1 |      |      |      |      |      |   |   |

|--------|---|------|------|------|------|------|---|---|

|        |   | 2    |      |      |      |      |   |   |

| 14     | x | 14 x |      |      |      |      |   |   |

|        | x | 57 x | 3    |      |      |      |   |   |

| 26     | x | 14 x |      |      |      |      |   |   |

|        | x | 26 x |      | 4    | _    |      |   |   |

| х      | х | x x  | x x  | x x  |      |      |   |   |

|        |   |      |      |      | 5    |      |   |   |

| x      | x | x x  | x x  | x x  |      |      |   |   |

|        |   |      |      |      |      | 6    |   |   |

| 28     | x | 28 x | 57 x | 68 x | 68 x | 57 x |   |   |

|        | x | x    | x    | x    | x    | 68 x | 7 |   |

| <br>14 | x | 14 x | 57 x | 68 x | 57 x | 14 x |   |   |

| 28     | x | x    | x    | x    | 68 x | 57 x |   |   |

|        |   |      |      |      |      |      |   | 1 |

Figure 4. Pair chart for flow table of Figure 2.

9

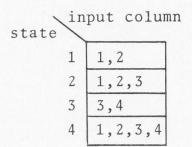

The chart is then filled in as follows: (Note that states 5 and 6 have outputs of "1" and the other states all have outputs of "0"). All combinations that have incompatible outputs have an "x" placed in them. Pairs that imply other pairs have the other pairs written in the box. After all pairs are entered, a check for incompatibles is made. A start is made from one of the output incompatible squares. Assume we start from square 15. Since it is output incompatible, we place an "x" in the square. We check all other squares for entries of "15" and if we find one, an "x" is placed within the square in which it is found and the square is considered to be an incompatible. This process is continued until no more x's can be entered. When the search for the entry of incompatible pairs in other squares is completed, a second "x" is placed in the original incompatible pair's square (15) to indicate that the square need not be referenced again. When the table is complete, the compatibles can be grouped so as to minimize the total number of states. The rules for checking the pair chart are as follows:

1. Start the compatible list (c-list) with the compatible pairs in the first column from the right having at least one entry without an x in it.

2. Move to the left, column by column. Let  $S_i$  be the set consisting of all non-x entries in column i. Take the intersection of  $S_i$  with current c-list. If the

intersection has more than one member, add the set consisting of i appended to the intersection. Delete duplicate entries and entries that are contained in other entries. Add pairs consisting of i and any members of  $S_i$  that did not appear in any of the intersections.

3. The final c-list plus those states not yet included in the c-list comprise the final groupings of states, and are called maximum compatibles.

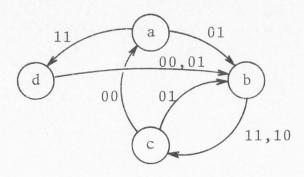

The pair chart of Figure 4 yields the following:

| Start:       | с = | {78} |     |     |     |

|--------------|-----|------|-----|-----|-----|

| $S_6 = \phi$ | c = | {78} |     |     |     |

| $S_{5} = 6$  | c = | {78, | 56} |     |     |

| $S_4 = \phi$ | с = | {78, | 56} |     |     |

| $S_3 = 4$    | с = | {78, | 56, | 34} |     |

| $S_2 = \phi$ | с = | {78, | 56, | 34} |     |

| $S_{1} = 2$  | с = | {78, | 56, | 34, | 12} |

All states are included in the final c-list, hence the final c-list is

$c = \{78, 56, 34, 12\}.$

Now we choose compatibles from the c-list such that every row of the original table is covered by at least one of the compatibles, and the set is "closed" in the sense that any set of rows implied by any compatible in the set is a subset of at least one compatible of the set. It is obvious that each element of the c-list is required to completely cover the original table so we have to use each maximum compatible. The final flow table then looks like Figure 5.

| \ X.  | $1^{\mathbf{x}}2$ |     |     |     |    |

|-------|-------------------|-----|-----|-----|----|

| state | 00                | 01  | 11  | 10  |    |

| a     | a,0               | b   | d   | a,0 | 12 |

| b     | b,0               | b,0 | С   | С   | 34 |

| с     | a                 | b   | c,1 | c,1 | 56 |

| d     | b                 | b   | d,0 | d,0 | 78 |

Figure 5. Minimized flow table.

The states are listed as letters so as not to be confused with the original state numbers (which are given on the right). The output is listed for each stable state.

### State code assignment

The next step in the synthesis procedure is the state assignment. Each state is assigned a binary valued code such that the internal state transitions are not dependent on the binary values of the state variables. If more than one state variable is required to change for a given transition, then inherently unequal delays in the circuit make it virtually impossible for the two states to change value simultaneously. Such a condition is called a race and will be discussed later in this report. In most cases, then, what is needed is essentially a gray-code assignment for the states. Adjacent states are coded so that only one state variable changes per transition (adjacent states are states connected with a transition arrow on the state diagram, if one were drawn). Starting with the flow table of Figure 5, we can draw a state diagram for the four states and assign binary values to the states so that each transition involves only a change in one state variable. Since there are only four states, the minimum number of state variables required for a unique code is two. Figure 6 shows the state diagram for the flow table of Figure 5.

Figure 6. Minimized state diagram.

The state diagram of Figure 6 cannot be gray-coded with only two state variables as it's drawn. An extra state variable could be added to bring the total possible number of states to eight. This would give four extra states to use in which transitions could pass through one or more states before settling in the final state, and would give some flexibility to the state assignment. A Liu (1963) or Tracey (1966) assignment could also be made, but will not be commented on here.

An alternate method would be to note the availability of extra "b's" in column "01" of Figure 5. For an input

of "01" every state has state "b" as its transition objective. It is possible in this case to have the transition pass through one or more of the other states before settling at state "b". Figure 7 shows the necessary adjacencies (those determined from columns other than "01"). The transition from "a" to "b" is seen to have been removed, and can be routed through state "d". The modified flow table is shown in Figure 8. Note that total state a-01

Figure 7. Necessary adjacencies.

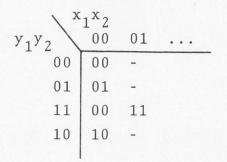

has been changed from "b" to "d". Since the output, Z, is constant for a given state, it is noted on the right of the flow table (it should be remembered that transition states do not, as yet, have specified outputs). Binary values for the states can now be assigned as follows:

a ←00; d ←01; b ←11; c ←10.

| \ x   | $L^{\mathbf{x}}_{2}$ |    |    |    |    |

|-------|----------------------|----|----|----|----|

| state | 00                   | 01 | 11 | 10 | /2 |

| а     | а                    | d  | d  | a  | 0  |

| Ъ     | b                    | b  | с  | с  | 0  |

| с     | а                    | b  | с  | с  | 1  |

| d     | b                    | b  | d  | d  | 0  |

Figure 8. Flow table with "transition" state.

The state assignment can be modified (permuted)--the important point is that each entry must be adjacent to the one above and below it ("a" and "c" are adjacent).

The flow matrix (binary values assigned to the states) can now be drawn as shown in Figure 9. The state values are placed in "Karnaugh" order to facilitate the construction of the state maps.

| $\backslash^{x_1}$ | x <sub>2</sub> |    |    |    |    |

|--------------------|----------------|----|----|----|----|

| y1y2               | 00             | 01 | 11 | 10 | /Z |

| 00                 | 00             | 01 | 01 | 00 | 0  |

| 01                 | 11             | 11 | 01 | 01 | 0  |

| 11                 | 11             | 11 | 10 | 10 | 0  |

| 10                 | 00             | 11 | 10 | 10 | 1  |

Figure 9. Flow matrix.

### State and output maps

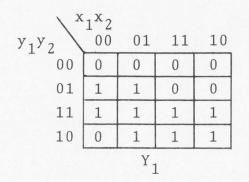

The state variable maps are simply maps taken from the flow matrix with one entry-variable shown. The maps are shown in Figures 10 and 11.

Figure 10. Karnaugh map for Y<sub>1</sub>.

| $y_1y_2$ | 1 <sup>x</sup> 2<br>00 | 01 | 11 | 10 |

|----------|------------------------|----|----|----|

| 00       | 0                      | 1  | 1  | 0  |

| 01       | 1                      | 1  | 1  | 1  |

| 11       | 1                      | 1  | 0  | 0  |

| 10       | 0                      | 1  | 0  | 0  |

Figure 11. Karnaugh map for Y<sub>2</sub>.

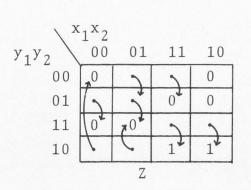

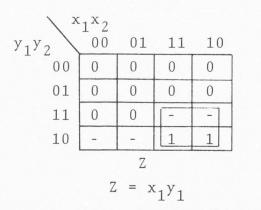

The output map, or Z-map, is taken from the flow matrix with entries placed only in the stable state positions. It is shown in Figure 12. Transition arrows are indicated to show beginning and end points for the transitions. Since

### Figure 12. Partial Z-map.

the output (Z) is the same for indicated entries on a given row, only verticle transitions need to be indicated.

The transition entries can be derived as follows:

A "O" initial to "O" final entry should have a

"O" in the transition position(s).

2. A "O" initial to "1" final entry (or vice-versa) may have a "O", "1", or "-" ("don't care") entry in the transition position(s). Usually a "-" is preferred for later flexibility in deriving the boolean expressions.

3. A "1" initial to "1" final entry should have a

"1" in the transition position(s).

The reason for the above constraints is to prevent unnecessary "glitches" on the output. The complete Zmap is shown in Figure 13.

| X                             | $1^{\mathbf{X}}_{00}$ |    |    |    |

|-------------------------------|-----------------------|----|----|----|

| y <sub>1</sub> y <sub>2</sub> | 00                    | 01 | 11 | 10 |

| 00                            | 0                     | 0  | 0  | 0  |

| 01                            | 0                     | 0  | 0  | 0  |

| 11                            | 0                     | 0  |    | -  |

| 10                            | -                     | -  | 1  | 1  |

|                               |                       | Z  |    |    |

Figure 13. Complete Z-map.

From the above maps the expressions for the states and output can be written. The next chapter describes subtleties to be aware of when going from the map to the boolean expressions (and hence to the circuit realization).

### CHAPTER III

### HAZARDS AND RACES

#### Logic delays

Inherent in any physical implementation of a digital circuit are logic delays. In combinational circuits these delays may not bother the circuit function but in sequential circuits random delays play funny tricks.

It was mentioned earlier that races should be avoided in asynchronous sequential design because critical races may lead to improper circuit action. An example of this is shown in Figure 14. If the input changes from  $x_1x_2y_1y_2 = 0111$ to  $x_1x_2y_1y_2 = 0011$  the state is unstable and tries to go to  $x_1x_2y_1y_2 = 0000$ . Since both state variables are unstable  $(y_1 \text{ and } y_2)$  they will both try to change to "0" simultaneously. The probability that  $y_1$  and  $y_2$  will both switch simultaneously is virtually zero, and hence the circuit may end up in state 01 or 10, depending on which state variable switched first. The proper state assignment is one way of alleviating the critical race problem, and cycling through other states going to the same final state is another way.

A more subtle problem in sequential circuits due to random delays is the existence of combinational hazards. Each state variable is essentially generated through

Figure 14. Critical race condition.

combinational logic, and any stray hazard pulses may cause the circuit to jump into the wrong state.

A "0" static hazard occurs when a single input change takes the output function from a "0" to a "0" and a momentary "1" may occur on the output at the time of the input change. A "1" static hazard is similar except for output polarity.

The reason for a hazard existing is illustrated in Figure 15. If adjacent implicants are not covered by a common cover, then the possibility of a hazard pulse occurring is present.

| \ × | сy |     |              |     |

|-----|----|-----|--------------|-----|

| z 🔪 | 00 | 01  | 11           | 10  |

| 0   |    | 1   | 1            |     |

| 1   |    |     | (1)          | ·1) |

|     | F  | = y | 7 <u>2</u> + | XZ  |

Figure 15. Hazard situation.

If the input goes from xyz = 110 to xyz = 111, the map function F can be expressed as  $xy\overline{z} + xyz$ , x = y = 1.

Note that only one variable is changing (due to the fact that only adjacent changes are assumed). With the variables assuming their respective values we have

```

F = xy(z + \overline{z})= z + \overline{z}.

```

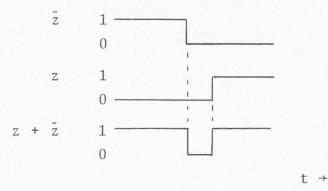

The common boolean reduction for the above situation is "1", but if z is generated from  $\overline{z}$  through an inverter, there will be some delay after  $\overline{z}$  switches from "1" to "0" before z switches from "0" to "1". This will give rise to a static "1" hazard as shown in Figure 16.

Figure 16. Static "1" hazard for change in z.

A dynamic hazard occurs when a single variable input change causes the output to change three times when normally only a single output change would be expected. The cause of the dynamic hazard is due to different signal paths reaching the output with different delays. A thorough treatment of hazards can be found in Unger (1969).

A fix for the static hazards is to include a common cover for all adjacent implicants. This would add the

term "xy" for the example of Figure 15. The function would then be

$F = y\overline{z} + xz + xy.$

For the stated transition it would reduce to

```

F = \bar{z} + z + 1

= 1.

```

Hence no "0" pulse would occur. If all static hazards are fixed in this manner then the single-input-change dynamic hazards will have been corrected also (Unger 1969).

### Multiple input change problems

For multiple input changes higher order hazards may occur with the output oscillating on and off two or more times before settling down. A hazard of this type, called a functional hazard, may occur due to the function implemented and not from the method of forming the combinational logic. An example of this is shown in Figure 17. An input change from xy = 00 to xy = 11 should cause the

$$\begin{array}{c} x \\ y & 0 & 1 \\ 0 & 1 & 0 \\ 1 & 0 & 1 \\ F &= \bar{x}\bar{y} + xy \end{array}$$

Figure 17. Functional hazard situation.

output, F, to remain at "1". However, due to unequal internal delays in the logic (the "AND" gate realizing

xy may have a smaller delay time than the "AND" gate realizing xy) F would in reality put out a small "O" pulse. There is no known way to inhibit multiple-inputchange hazards.

### Essential hazards

Up to now, only combinational hazards due to inputs have been mentioned. Asynchronous sequential circuits have special problems due to arbitrary delays inherent in the feedback, or state, variables in conjunction with the delays in the input variables. Figure 18 shows a possible hazard situation with a single-input-change

Figure 18. Essential hazard condition.

constraint (only the two columns with the changing input are shown). The flow table has two input columns and three rows shown. If the initial state is assumed to be 1-a, the position is stable. If the input is then changed to "b", the circuit that realizes the flow table may have some of its state variables see changes in other state variables before the first state variables see the input change. In this case the initial movement on the table will be vertical instead of horizontal. For the input change in Figure 18 the initial transition may be from 1-a to 2-a instead of 1-a to 1-b. From 2-a the circuit is taken to 3-a and thence to 3-b when the input change is finally sensed. From there it goes to n-b. This is not the 2-b destination originally designed for. The above aberration is called an "essential hazard" and can be checked for in a flow table in the following manner: For some initial total state and an input variable x, if three changes in x take the system to a state different from the state that only one change in x takes it to (assuming both sequences start in the same total state), then an essential hazard exists. The only solution for an essential hazard is to insert delay elements in the state variable feedback paths to insure that input changes are seen by the system before the state variable changes are sensed.

A related hazard condition called a "nonessential hazard" (or d-trio) is shown in Figure 19. Starting in

Figure 19. Nonessential hazard condition.

total state 1-a, three consecutive input changes of the same variable (only one shown in Figure 19) take the system to the same total state that only one input change would,

but it is possible to cycle through state 3 if the state variable changes were sensed first. The static behavior of the system would be correct, but a possible output transient may occur if the output for state 3-a is different from the outputs for 1-a and 2-b. Some of the transient problems for the output were mentioned in conjunction with the Z-map of Chapter II.

### Synthesis of example problem

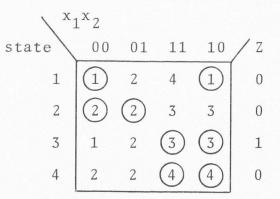

With the above race and hazard conditions in mind we can review the example problem of Chapter II and specify the circuit realization. The flow table is redrawn in Figure 20. (The flow table is redrawn from Figure 9 with the states numbered for easy reference).

| × 2   | $x_1 x_2$ |    |    |    | ,   |

|-------|-----------|----|----|----|-----|

| state | 00        | 01 | 11 | 10 | / Z |

| 1     | 1         | 2  | 2  | 1  | 0   |

| 2     | 3         | 3  | 2  | 2  | 0   |

| 3     | 3         | 3  | 4  | 4  | 0   |

| 4     | 1         | 3  | 4  | 4  | 1   |

Figure 20. Flow table derived from Figure 9.

A check for essential hazards shows that the condition exists for the 1-00 to 1-11 transition, the 2-11 to 2-00 transition, the 2-10 to 2-00 transition, the 3-00 to 3-11 transition, the 3-00 to 3-10 transition, and the 4-11 to 4-00 transition. There are two single-input-change

essential hazards (2-10 to 2-00 and 3-00 to 3-10) so care must be taken to insure that the state variable changes are sensed after the input change. This may necessitate the addition of delays in the feedback paths.

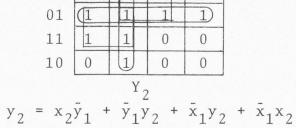

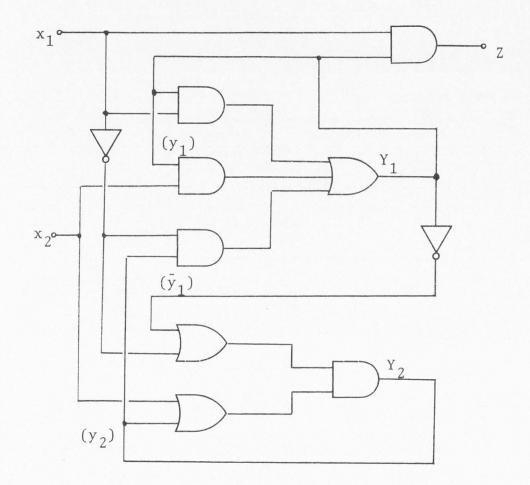

Boolean expressions can be derived from the Y-maps and Z-map as indicated in Figure 21. Note that the Y-map adjacencies are covered. If hazard pulses occur on the state variable outputs, the system would think it was in an entirely different state and improper circuit action could ensue. The Z-map adjacencies (none in this case) may be covered if transient output pulses are not desired.

It might be noted that a simpler expression could be written for  $Y_2$  by covering the "0's",

i.e.  $Y_2 = (x_2 + y_2) (\bar{x}_1 + \bar{y}_1)$ . The above expression could also be derived by factoring the "1's" cover expression. The circuit realization is shown in Figure 22.

This completes the classical synthesis procedure. Enough of the procedure has been presented to give an idea of the methods and problems of asynchronous logic design, and the next four chapters will be concerned with flipflops and their application to synchronous and asynchronous logic design.

Figure 21. State and output maps for example of Chapter II.

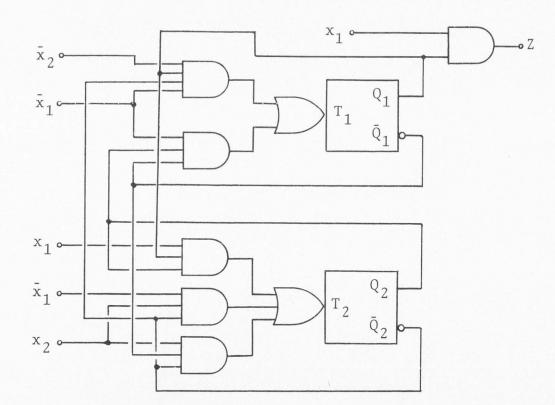

Figure 22. Circuit diagram for example problem.

### CHAPTER IV

### BISTABLE ASYNCHRONOUS SUBSYSTEMS

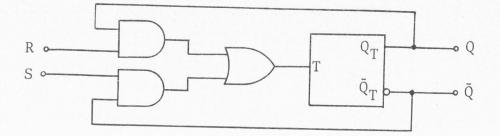

## Flip-flop types

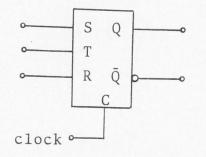

In synchronous sequential design, by far the majority of synthesis techniques involve clocked flip-flops. The four major types of flip-flops are the RS (Reset-Set), D (Data, or Delay), JK (it is unknown what J and K stand for), and T (Toggle). Sometimes the RS and T flip-flops are combined into one device with the R, S, and T inputs and called an RST flip-flop. The purpose of a flip-flop is to store a bit of information when a specified event occurs on one or more of the inputs (the bit could be a "0" or a "1"). The different types of flip-flops are categorized by the input sequencing required to store the required bit of information. The output of all flip-flops is labeled Q, and if its inverse is also available it is labeled  $\overline{Q}$ .

The RS flip-flop can be completely characterized through level logic inputs without positing internal states other than the output state. The D, JK, and T flip-flops are essentially transition flip-flops and require additional internal state variables to be accurately characterized using the Huffman method of asynchronous analysis. For this reason the present chapter will be concerned with the RS flip-flop only, and its application in the synthesis of asynchronous sequential logic circuits. Transition flip-flops will be treated in Chapters VI and VII.

# RS flip-flop

The basic RS flip-flop has two inputs and one output. The inputs are labeled "Set" and "Reset", and the output is labeled "Q". Assume an initial state of "O" for Q, S, and R. If S and R remain at "O", then Q will also remain at "O". If R goes to "1" (with S remaining at "O"), Q will remain at "O". If S goes to "1" (with R remaining at "O") or oscillates between "O" and "1", Q will go to and remain at "1". With S set at "O", if R now goes to "1", then Q will go to "O" and remain there until R = 0 and S = 1 again (which repeats the process). If both S and R go to "1" at the same time, then the circuit action is undefined.

The RS flip-flop can now be described by a flow table as shown in Figure 23. Since the circuit operation was so

Figure 23. RS flip-flop flow table.

simple, the primitive flow table was bypassed and all entries were entered by inspection. Due to the fact that the output (Q) is different for each row, a merge (or simplification) of the rows is not possible. The flow table has a minimum number of rows as shown.

The flow matrix and state (Y) map are shown in Figure 24. Note that Q = y, so that the state could be labeled Q if desired. Since there is only one state, the flow matrix and Y-map are the same.

Figure 24. RS flip-flop flow matrix and output map.

### Characteristic equation

The "characteristic equation" for the RS flip-flop can be taken from the output map of Figure 24. If the constraint that R and S cannot be "1" simultaneously is added, we have

```

Q = S + \bar{R}qSR = 0.

```

"Q" is the next state function defined by R, S, and q. "q" is the present state (or output) of the flip-flop and equals Q for static conditions. If an input change causes

an output transition then q will eventually assume the value Q defined by the characteristic equation. "q" may be thought of as being the system state variable. The second equation (SR = 0) is a constraint to be met by the designer and not a functional relationship of the flip-flop.

### Logic realization of RS flip-flop

A possible circuit diagram for the RS flip-flop is shown in Figure 25. A more common configuration is shown in Figure 26. The evolution from Figure 25 should be evident.

Figure 25. RS flip-flop circuit diagram.

An inverter may be placed on the output if Q is desired, or it may be noted that the point labeled "Q" in Figure 26 is actually the inverse of  $\overline{Q}$  for all acceptable inputs.

However the RS flip-flop is realized physically, the diagrammatical symbol used for it in this report will be as shown in Figure 26.

Figure 26. RS NOR flip-flop and symbol.

### CHAPTER V

# AN ALGORITHM FOR DESIGNING ASYNCHRONOUS SEQUENTIAL CIRCUITS USING RS FLIP-FLOPS

### Characteristic map equation

In Chapter II the Huffman synthesis method (with the Paull-Unger minimization method) was presented and it was shown how to generate the Karnaugh maps defining the state variables in terms of themselves and the inputs. In this chapter a method will be given wherein the state variables are realized by RS flip-flops, and the Set and Reset inputs of the RS flip-flops will be functions of the flip-flop outputs (states) and the system inputs. The original state variable maps will be the starting point from which the maps defining the Set and Reset inputs to the flip-flops are generated.

Since the flip-flop is to represent the state variable, its next state function (or characteristic equation) must somehow be related to the Y-map that generates the state variable which the flip-flop is to replace. If we think of the variables of the characteristic equation as functions of other variables, then it is an easy step to go to maps to represent those functions. The characteristic equation is

$Q_i = S_i + \bar{R}_i q_i$ ,

where i represents the  $i\frac{th}{t}$  state variable.  $Q_i$ ,  $S_i$  and  $\bar{R}_i$ will be functions of the system inputs, I, and the flipflop outputs (or state variables)  $Q_i$ . i.e.

$Q_{i} : Q X I \rightarrow Q$  $S_{i} : Q X I \rightarrow S$  $R_{i} : Q X I \rightarrow R.$

${\bf q}_{\bf i}$  is one of the independent variables and hence is not a function of the other independent variables. Note that

$I = \{x_1 x_2 \dots x_n | x_i = 0, 1; i = 1, 2, \dots n\}$  $Q = \{q_1 q_2 \dots q_m | q_j = 0, 1; j = 1, 2, \dots m\}.$

Since the Karnaugh map is essentially a graphical representation of the functional relationship, we can replace the symbols in the characteristic equation with the appropriate Karnaugh map. The Boolean operators are valid if we assume that the operations take place between corresponding minterms of the maps, and the map variables are identical and in the same position on each map (Caldwell, 1958).

The example of Chapters II and III will be used to illustrate the method. The state and output maps of Figure 21 are reproduced in Figure 27 for reference. The state variables  $(y_1 \text{ and } y_2)$  will be relabeled  $q_1$  and  $q_2$ with the next state variables  $(Y_1 \text{ and } Y_2)$  changed to  $Q_1$ and  $Q_2$ .

Figure 27. State and output maps of Figure 21.

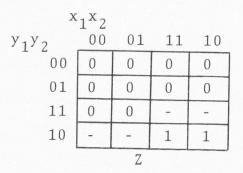

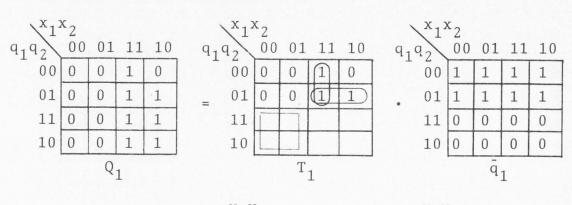

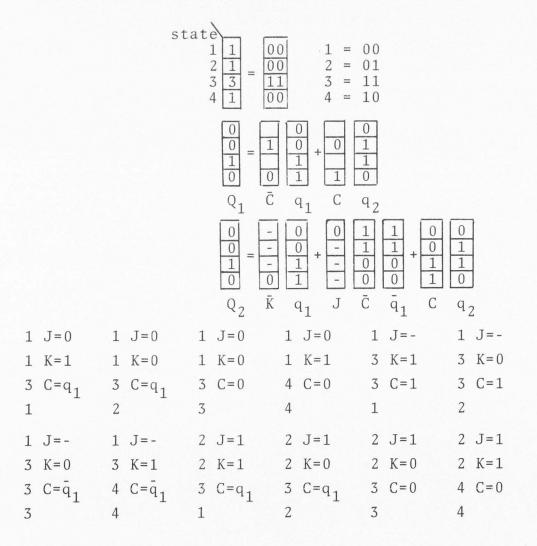

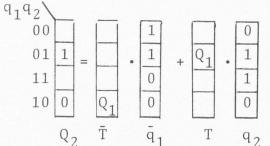

The characteristic equation is then written with maps replacing the functional symbology as shown in Figure 28. Each map must be a function of the same variables  $(x_1, x_2, q_1, q_2)$  as stated previously, and the variables must be in the same position on each map for the boolean operators between the maps to be valid.

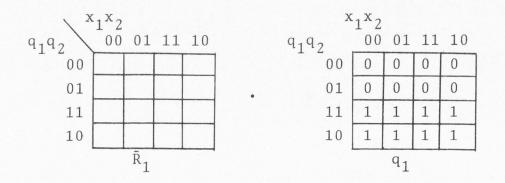

Figure 28. Characteristic map equation for  $Q_1$ .

# Selecting the minterm entries

The  $Q_1$  map is identical to the  $Y_1$  map derived from the classical synthesis, and the  $q_1$  map simply shows that  $q_1$  is identical to itself. This provides the starting point for filling in the  $S_1$  and  $\bar{R}_1$  maps. The procedure is outlined as follows:

1. Place "0's" in each minterm position of  $S_1$  where a "0" occurs in the equivalent minterm of  $Q_1$ .

2. Place "0's" in each minterm position of  $\bar{R}_1$  where q<sub>1</sub> = 1 occurs and where a "0" occurs in the equivalent minterm of Q<sub>1</sub>.

3. Place a "-" ("don't care") in each minterm position of  $\bar{R}_1$  where  $q_1 = 0$  occurs and where a "0" occurs in the equivalent minterm of  $Q_1$ .

4. Place a "1" in each minterm position of  $S_1$  where  $q_1 = 0$  occurs and where a "1" occurs in the equivalent minterm position of  $Q_1$ .

5. Place a "1" in each minterm position of  $\bar{R}_1$  where  $q_1 = 0$  occurs and where a "1" occurs in the equivalent minterm position of  $Q_1$ .

6. Place a "-" in each minterm position of  $S_1$  where  $q_1 = 1$  occurs and where a "1" occurs in the equivalent minterm position of  $Q_1$ .

7. Place a "1" in each minterm position of  $\bar{R}_1$  where q<sub>1</sub> = 1 occurs and where a "1" occurs in the equivalent minterm position of Q<sub>1</sub>.

8. If a "-" occurs in the  $Q_1$  map, then a "+" (a "don't care" with caution) is placed in the corresponding minterms of  $S_1$  and  $\bar{R}_1$ . When the final coverings are placed to derive the expressions from the maps it should be noted that the choice of  $S_1 = 1$  and  $\bar{R}_1 = 0$  is <u>not allowed</u>. All other combinations are permitted (i.e.  $S_1 = 1$ ,  $\bar{R}_1 = 1$ ;  $S_1 = 0$ ,  $R_1 = 1$ , etc.). Note that a "-" does not occur in  $Q_1$  for this example.

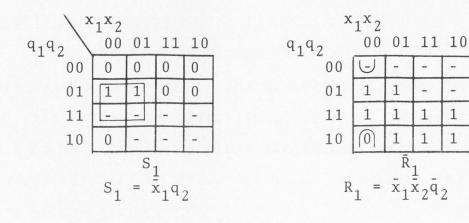

The above procedure has accounted for the SR = 0 constraint, and the algorithm uniquely specifies the S and  $\bar{R}$  map entries for a fully specified Q map. Figure 29 shows the completed S<sub>1</sub> and  $\bar{R}_1$  maps (using the algorithm) of Figure 28.

Figure 29. Complete specification for  $Q_1$  excitation.

10

1

1

q1

1

1

1

1

R<sub>1</sub>

1

10

0

A quick check could be made of the S and  $\bar{R}$  maps to insure that the minterm positions of S that have a "1" or "-" entry correspond only to "1" entries in the respective minterm positions of  $\bar{R}$ .

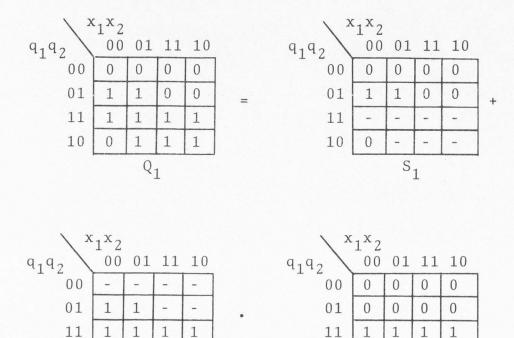

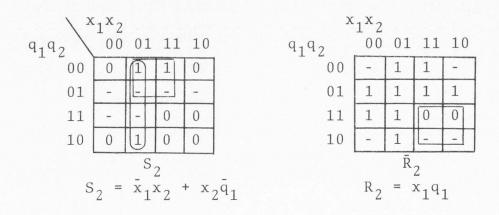

The Set and Reset maps of  $Q_2$  are similarly derived, and are shown in Figure 30. Expressions for  $S_1$ ,  $R_1$ ,  $S_2$ , and  $R_2$  can now be written as shown in Figure 31. The R expressions are found from the "0" terms of the  $\bar{R}$  maps.

Figure 30. Complete specification for  $Q_2$  excitation.

The circuit diagram can be drawn once the excitation functions are derived, and is shown in Figure 32. Inputs are indicated on the left to simplify the circuit schematic. The output function is the same as derived in Chapter II (Figure 21) with  $q_1$  substituted for  $y_1$ :

# $Z = x_1 q_1.$

The map procedure can be extended to cover any number of state variables, but the maps become unwieldy to work with for seven or more variables. The entries are specified for any number of variables, however, since the procedure given only deals with minterms and is not changed by the map size.

Figure 31. Flip-flop excitation expressions.

Figure 32. Sequential circuit with RS flip-flops.

-

-

1

### Algorithm statement

Using the example given, an extension to the general case should be obvious. The algorithm is given for the set and reset maps of a given state variable. Reference need only be made to the original excitation maps, but the entire map equality can be drawn (as shown in Figures 28, 29, or 30) as a memory aid.

Given the excitation map for state variable  $Q_i$ , the  $S_i$  and  $R_i$  maps are derived as follows:

$\begin{array}{rcl} Q_{i} &=& 0\,, \ q_{i} &=& 0\,; & S_{i} &=& 0\,; & R_{i} &=& -\,. \\ & & q_{i} &=& 1\,; & S_{i} &=& 0\,; & R_{i} &=& 1\,. \\ Q_{i} &=& 1\,, \ q_{i} &=& 0\,; & S_{i} &=& 1\,; & R_{i} &=& 1\,. \\ & & q_{i} &=& 1\,; & S_{i} &=& -\,; & R_{i} &=& 0\,. \end{array}$   $\begin{array}{rcl} Q_{i} &=& -\,, & a\,11\,\,q_{i}\,; & S_{i} &=& +\,; & R_{i} &=& +\,. \end{array}$

The  $S_i$  and  $R_i$  maps are covered in the standard fashion with a caution on the "+". A "+" is considered equivalent to a "-" ("don't care"), but with the restriction that the  $S_i$  and  $R_i$  maps cannot have a "+" in corresponding minterm positions both grouped in a "1's" grouping (i.e., they both cannot be used as "1's" for a given  $S_i$  and  $R_i$  realization). Static hazard conditions should be eliminated to insure smooth state transitions since static "0" hazards could cause an inadvertent set or reset. If one of the flip-flops changed its state at the wrong time, an improper state transition would occur, and proper action as defined by the flow table could not be achieved in most cases.

# CHAPTER VI AN APPLICATION OF THE MAP-METHOD TO SYNCHRONOUS CIRCUITS

### Problems in synchronous design

If the technique presented in Chapter V is tried for asynchronous design using T or D flip-flops, a problem arises (the unclocked JK flip-flop is excluded due to the improbability of simultaneous J and K transitions occuring, hence it reduces to an RS flip-flop). In describing the T and D flip-flops more than two states are required to adequately describe their total operation using logic levels as excitations. This means that a set of equations is required to describe the circuit action-hence more than one state variable is needed.

For the RS flip-flop only two states were required to describe the circuit operation, and hence only one state variable was needed. As it turned out the RS flipflop output represented the state variable, and so was accessible. Where more than one state variable is required the relationship between them has to be maintained in the state assignment for the flow table to be achieved. Such is the case for only a small fraction of possible flow tables. This problem will be discussed in Chapter VII.

### Synchronous analysis

In synchronous sequential design the presence of a "clock" signal supresses the requirement for positing extra states for a complete description of the D, T, or JK flip-flops, and the method of Chapter V can be used effectively to produce maps for the inputs of the state flip-flops. Note that it is possible for the JK flipflop to be used in synchronous design problems since the initiating signal transition occurs only on the "clock" input. The other flip-flop inputs are assumed to be at a definite logic level when the clock transition occurs (flip-flop action may occur on positive-going or negativegoing clock transitions, depending on how the flip-flop is constructed. In this report excitation is assumed to occur on the positive-going edge of the clock).

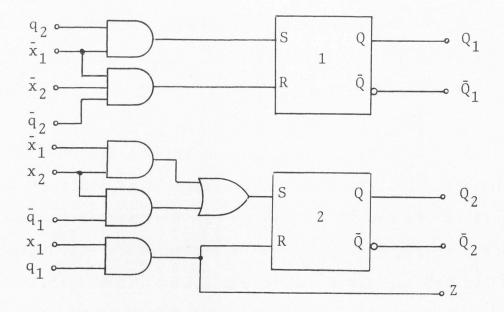

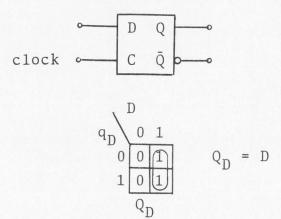

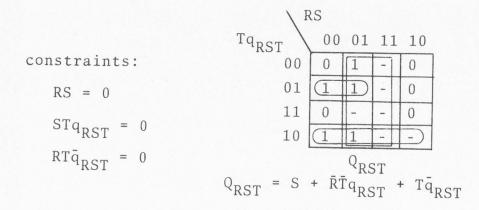

The characteristic map, characteristic equation, and symbol are shown in Figures 33-36 for D, T, JK, and RST flip-flops. The RST flip-flop is included for completeness. Note that the clocked RS flip-flop would have the same characteristic equation and map-generation algorithm as described in Chapter V. In generating the RST characteristic map the technique of Marcus (1969) was used. Each minterm entry of the respective map indicates what the flip-flop output will be upon the occurrence of a positivegoing transition on the clock input lead.

Figure 33. D flip-flop symbol, characteristic map, and characteristic equation.

Figure 34. T flip-flop symbol, characteristic map, and characteristic equation.

Figure 35. JK flip-flop symbol, characteristic map, and characteristic equation.

Figure 36. RST flip-flop symbol, characteristic map, characteristic equation, and constraint equations.

Only the RST flip-flop is seen to have constraints on its inputs. When realizing the R, S, and T input maps these constraints have to be accounted for.

The problem statement of a synchronous sequential circuit is similar to the asynchronous case, but the race and hazard problems need not be accounted for in the synchronous problem. A state diagram or flow table is constructed and a state reduction is attempted as in the asynchronous case. The state assignment can be taken as the minimum number of state variables to uniquely code each state. All destination state transitions are taken

in one step since the clock essentially constrains the circuit activity to occur at discrete points in time, and all feedback paths (from flip-flop output to flip-flop input) are nonfunctional at points in time other than when the positive-going clock transition occurs. From the transition matrix (flow table with states coded) the state maps are drawn, and these are then used to generate the flip-flop input maps as determined from the characteristic equation.

### Example

An example will be given to illustrate the procedure. The minimized flow table of Figure 5 is redrawn (with the states numbered) as shown in Figure 37. Since races are

Figure 37. Flow table for synchronous design.

not a problem in synchronous design, cycles need not be introduced for proper circuit operation. All transitions are direct, as previously mentioned.

The states are assigned a binary code in a fashion (generally) to realize the output function (Z) in the

simplest way. In this case (Figure 37) the output is coincident with state (3) only, so access will be required to both state variables (only two state variables are required to uniquely realize four states). The flow matrix is shown in Figure 38.

| $\backslash^{x_1}$ | x <sub>2</sub> |    |    |    |

|--------------------|----------------|----|----|----|

| 9192               | 00             | 01 | 11 | 10 |

| 00                 | 00             | 01 | 10 | 00 |

| 01                 | 01             | 01 | 11 | 11 |

| 11                 | 00             | 01 | 11 | 11 |

| 10                 | 01             | 01 | 10 | 10 |

Figure 38. Flow matrix for synchronous problem.

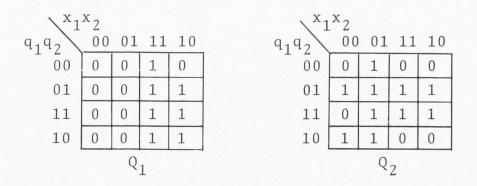

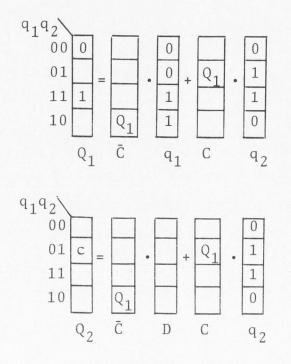

The state maps can be drawn as shown in Figure 39. The state map is then used in the characteristic equation of whichever flip-flop (or combination thereof) is desired to implement the total system. If all flip-flops are available, each state map can be tried with all of the characteristic equations to see which one would give the cheapest realization in combinational logic.

Figure 39. State maps for synchronous problem.

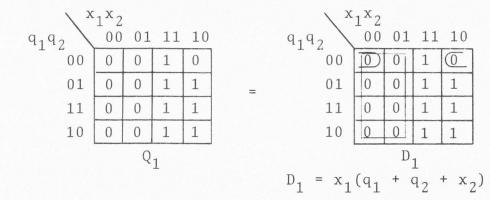

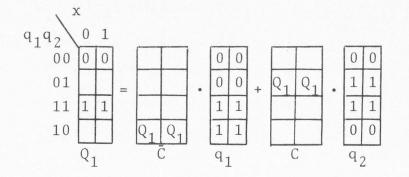

### D realization

To realize the states with D flip-flops it is necessary to refer to the characteristic equation of the D flipflop. Figure 40 shows the generation of the inputs for  $D_1$  and  $D_2$ . It is seen that the input maps are simply the state maps. This may mean a lack of ability to generate "don't care" conditions from specified conditions of the state maps, which could provide a means of further simplification. However, the single input may make up for the lack of flexibility.

$Q_D = D$

# Figure 40. Input excitation maps for realization with D flip-flops.

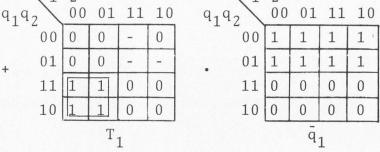

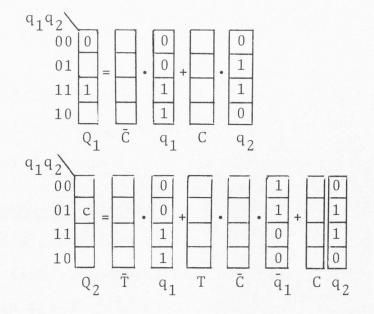

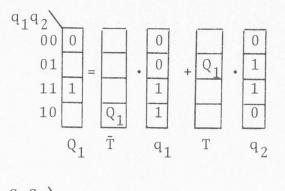

### T realization

The realization using T flip-flops is shown in Figure 41. A fully specified state map generates a fully specified T-map as in the D flip-flop case. Only the generation of  $Q_1$  is shown for brevity. It should be

$Q_T = T\bar{q}_T + \bar{T}q_T$

Figure 41. Realization expressions for T flip-flops.

evident that the T-map is identical to the Q-map where q = 0, and is the inverse of Q where q = 1.  $T_1$  and  $\bar{T}_1$  are filled in only where they contribute to  $Q_1$  to clarify the process.

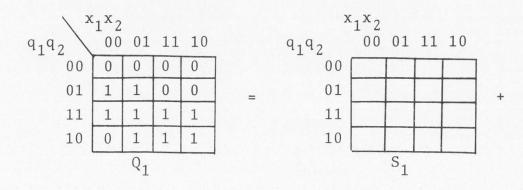

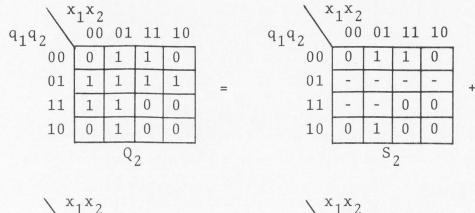

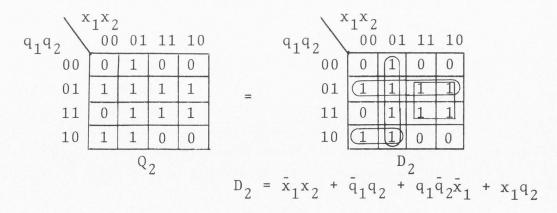

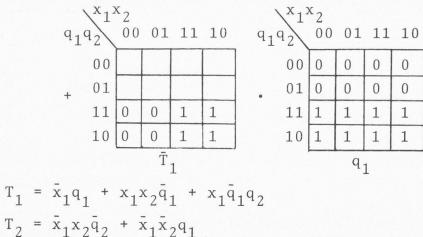

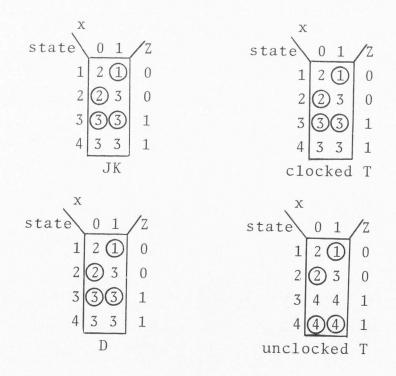

#### JK realization

The JK realization expressions are given in Figure 42, along with the map equality for  $Q_1$ . The JK flip-flop is seen to be similar to the T flip-flop with the exception that half of the J and K maps consist of don't cares, which may eliminate some of the combinational logic altogether (as in the generation of  $K_1$ ).

$Q_{JK} = J\bar{q}_{JK} + \bar{K}q_{JK}$

| $\setminus^{x_1}$ | $\setminus x_1 x_2$ |    |    |    |                  |    | $\chi_1^{x_2}$ |    |    |    |  |     | ×12 | <sup>c</sup> 2 |    |    |    |

|-------------------|---------------------|----|----|----|------------------|----|----------------|----|----|----|--|-----|-----|----------------|----|----|----|

| 9192              | 00                  | 01 | 11 | 10 | . q <sub>1</sub> | q2 | 00             | 01 | 11 | 10 |  | 910 | 42  | 00             | 01 | 11 | 10 |

| 00                | 0                   | 0  | 1  | 0  |                  | 00 | 0              | 0  | 1  | 0  |  | -   | 00  | 1              | 1  | 1  | 1  |

| 01                | 0                   | 0  | 1  | 1  | =                | 01 | 0              | 0  | 1  | 1  |  |     | 01  | 1              | 1  | 1  | 1  |

| 11                | 0                   | 0  | 1  | 1  |                  | 11 | -              | -  | -  | _  |  |     | 11  | 0              | 0  | 0  | 0  |

| 10                | 0                   | 0  | 1  | 1  |                  | 10 | -              | -  | -  | -  |  |     | 10  | 0              | 0  | 0  | 0  |

|                   |                     | Q  | 1  |    |                  |    |                | J  | 1  |    |  |     |     |                | ą  | 1  |    |

Figure 42. Realization expressions for JK flip-flops.

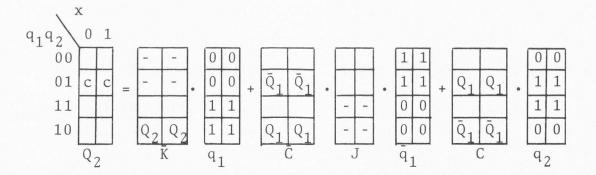

### RST realization

The RST flip-flop is the last flip-flop to be looked at in the synchronous sequential example. The realization expressions are given in Figure 43. Filling out the S, R, and T-maps is complicated by the fact that the three

+

Figure 43. Realization expressions for RST flip-flop.

constraints must also be met. The best way to fill out the maps is to fill in the required minterm entries that give the required equality, and then check T and  $\overline{T}$  for proper matching before further filling in to meet the constraints. Initially "0's" can be filled in the S<sub>1</sub>map where Q<sub>1</sub> = 0, and in the T<sub>1</sub>-map where Q<sub>1</sub> = 0 and q<sub>1</sub> = 0. The "0's" in T<sub>1</sub> where q<sub>1</sub> = 0 go into "1's" in  $\overline{T}_1$  where q<sub>1</sub> = 0. The corresponding minterms of  $\overline{R}_1$ can be filled in with "-'s". For minterms where Q<sub>1</sub> = 0 and q<sub>1</sub> = 1, place "1's" in T<sub>1</sub> and "-'s" in  $\overline{R}_1$  (or "-'s" in T<sub>1</sub> and "0's" in  $\overline{R}_1$ ). Note that there is a choice that may be made, thereby making the R, S, and T-maps nonunique for fully specified Q-maps.

Where  $Q_1$  had "1's", and  $q_1 = 0$ , set  $S_1 = 1$ ,  $\bar{R}_1 = 1$ , and  $\bar{T}_1 = -$  (or  $S_1 = -$ ,  $\bar{R}_1 = 1$ ,  $\bar{T}_1 = 0$ ). For  $Q_1 = 1$  and  $q_1 = 1$ , set  $S_1 = -$ ,  $\bar{R}_1 = 1$ , and  $\bar{T}_1 = 1$ . Another choice may be made here. The entries could be placed side by side in the maps so that when the final covers are placed, the optimum choice can be made.

The availability of multiple minterm entry selections is due to the fact that there are two complete flip-flops combined into one. Each separate flip-flop is capable of setting or resetting the combined flip-flop, hence more than one choice is available in certain situations.

# Summary for sequential flip-flops

The previous algorithms for determining the input equations for specified types of flip-flops is summarized

as follows. The RS flip-flop is equivalent to the asynchronous case and the RS algorithm is taken from Chapter V.

### RS flip-flop

The characteristic and constraint equations are:  $Q = S + \bar{R}q$ , RS = 0; where Q represents entries in the "next state" map, and q represents the "present state" variable.

Q = 0: (a) S = 0 in all corresponding minterms. (b) q = 0: R = -. (c) q = 1: R = 1. Q = 1: (a) q = 0: S = 1, R = 0. (b) q = 1: S = -, R = 0.

# D flip-flop

The characteristic equation is: Q = D. The input maps are identical to the state variable maps.

### <u>T</u> flip-flop

The characteristic equation is:  $Q = T\bar{q} + \bar{T}q$ . Q = 0: (a) q = 0: T = 0. (b) q = 1: T = 1. Q = 1: (a) q = 0: T = 1. (b) q = 1: T = 0.

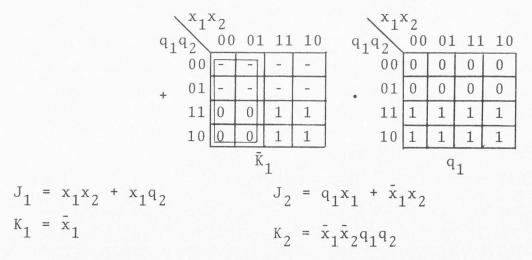

### JK flip-flop

The characteristic equation is:  $Q = J\bar{q} + \bar{K}q$ . It should be obvious that this is similar to the T flip-flop with the "T" function being shared by "J" and "K".

| Q | = | 0: | (a) | q | = | 0: | J | = | 0,  | K | = |    |  |

|---|---|----|-----|---|---|----|---|---|-----|---|---|----|--|

|   |   |    | (b) | q | = | 1: | J | = | -,  | K | = | 1. |  |

| Q | = | 1: | (a) | q | = | 0: | J | = | 1,  | K | = |    |  |

|   |   |    | (b) | q | = | 1: | J | = | - , | K | = | 0. |  |

### RST flip-flop

The characteristic and constraint equations are:  $Q = S + \overline{RTq} + T\overline{q}$ , RS = 0, STq = 0, and  $RT\overline{q} = 0$ . Q = 0: (a) S = 0 in all corresponding minterms. (b) q = 0: T = 0, R = -. (c) q = 1: T = -, R = 1; or T = 1, R = -. Q = 1: (a) q = 0: S = -, R = 0, T = 1; or S = 1, R = 0, T = -. (b) q = 1: S = -, R = 0, T = 0.

### "Don't care" conditions

If "don't cares" occur in the state maps, they are inserted in the corresponding minterm positions of the T, D, and JK input maps. The RS and RST input maps should have a "+" inserted in the corresponding minterm positions, and final covers placed so as not to contradict the constraint equations as was done for the RS flip-flop in Chapter V.

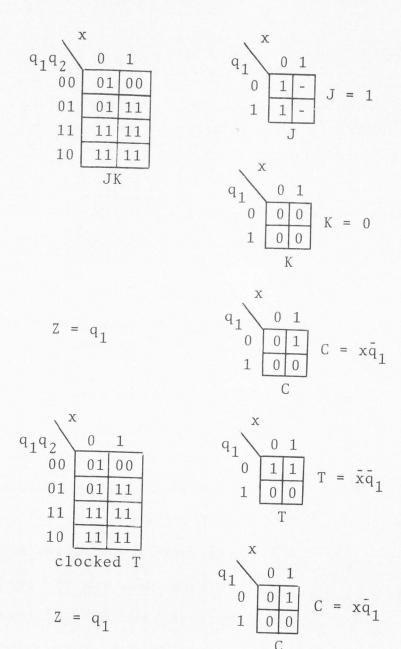

Each minterm position can be considered separately for a choice of which entry algorithm is desired (if a choice is available). In this way a more optimum map may be achieved in terms of the minimum number of logic gates required in the final implementation. The best way to do this is to draw out the maps in the characteristic equation and observe how each entry is being placed. Previous entries can be altered as the form of the map takes shape.

### CHAPTER VII

# AN APPLICATION OF THE MAP METHOD TO TRANSITION FLIP-FLOPS

## Types of transition flip-flops

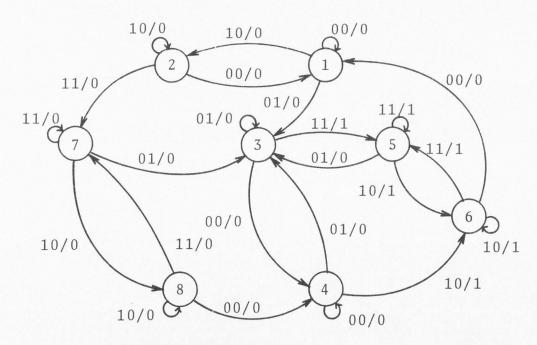

It was mentioned in Chapter IV that transition flipflops required more than one state variable to adequately describe them using the Huffman approach. In this chapter the clocked JK, "one's-catching" JK, D, T, and unclocked T flip-flops will be analyzed and their use in realizing asynchronous flow matrices will be described. The method will consist of modifying a given flow table into a form that is realizable using the selected transition flipflop.

# Clocked JK flip-flop

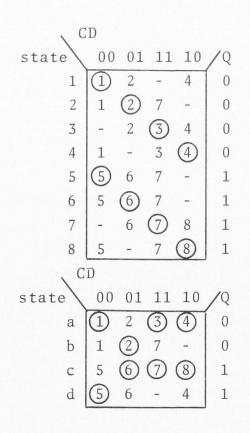

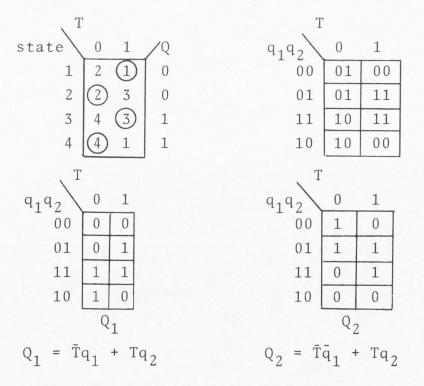

The clocked JK flip-flop to be analyzed is the same one used in Chapter VI. Its flow table and reduction are shown in Figure 44. The table is set up with the enabling clock transition ("0" to "1") dividing the flow table into two vertical halves. Since circuit action occurs only during the clock transition, this facilitates filling out the flow table. Note that the table is normal only with respect to the clock transitions. The state reduction was chosen with "don't cares" to give simpler characteristic expressions.

| CJ    | K                |      |      |      |      |      |      |      |    |

|-------|------------------|------|------|------|------|------|------|------|----|

| state | 000              | 001  | 011  | 010  | 100  | 101  | 111  | 110  | /Q |

| 1     | 1                | 2    | 3    | 4    | 5    | -    | -    | -    | 0  |

| 2     | 1                | 2    | 3    | 4    | -    | 6    | -    | -    | 0  |

| 3     | 1                | 2    | 3    | 4    | -    | -    | 15   | -    | 0  |

| 4     | 1                | 2    | 3    | 4    | -    | -    | -    | 16   | 0  |

| 5     | 1                | -    | -    | -    | 5    | 6    | 7    | 8    | 0  |

| 6     | -                | 2    | -    | -    | 5    | 6    | 7    | 8    | 0  |

| 7     | -                | -    | 3    | -    | 5    | 6    | 7    | 8    | 0  |

| 8     | -                | -    | -    | 4    | 5    | 6    | 7    | 8    | 0  |

| 9     | 9                | 10   | 11   | 12   | 13   | -    | -    | -    | 1  |

| 10    | 9                | 10   | 11   | 12   | -    | 6    | -    | -    | 1  |

| 11    | 9                | 10   | 11   | 12   | -    | -    | 7    | -    | 1  |

| 12    | 9                | 10   | 11   | 12   | -    | -    | -    | 16   | 1  |

| 13    | 9                | -    | -    | -    | 13   | 14   | 15   | 16   | 1  |

| 14    | -                | 10   | -    | -    | 13   | 14)  | 15   | 16   | 1  |

| 15    | -                | -    | 11   | -    | 13   | 14   | 15   | 16   | 1  |

| 16    | -                | -    | -    | 12   | 13   | 14   | 15   | 16   | 1  |

| 、 CJ  | K                |      |      |      |      |      |      |      |    |

|       | 000              | 001  | 011  | 010  | 100  | 101  | 111  | 110  | 10 |

| a     | $\overline{(1)}$ | (2)  | 3    | 4    | (5)  | (6)  | (7)  | (8)  | 0  |

| b     | 1                | 2    | (3)  | (4)  | -    | -    | 15   | 16   | 0  |

| c     | 9                | 10   | 11   | (12) | (13) | (14) | (15) | (16) | 1  |

| d     | 9                | (10) | (11) | 12   | -    | 6    | 7    | -    | 1  |

| - [   |                  | 0    | 0    |      |      |      |      |      |    |

Figure 44. Clocked JK flip-flop primitive flow table and merged flow table.

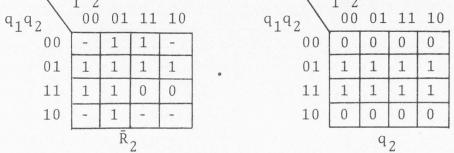

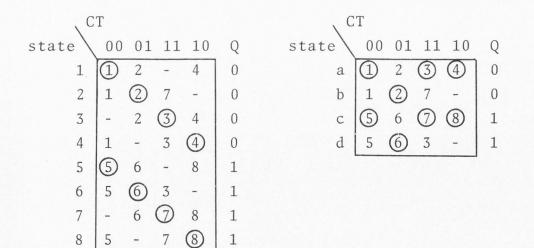

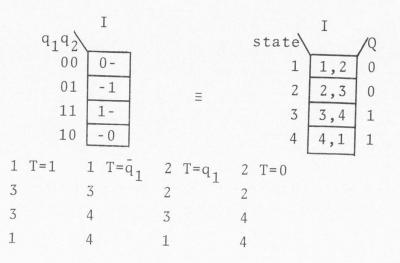

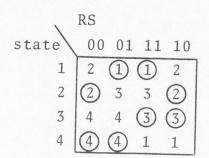

The state assignment and state maps are shown in Figure 45. The characteristic equation consists of two equations. This means that in certain cases a pair of states in a flow matrix may be realized with one flipflop. It will be seen that such is the case, and the conditions under which this is possible will be discussed.

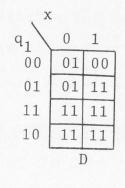

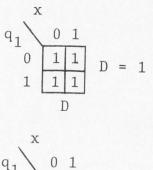

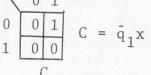

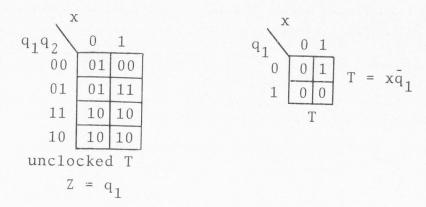

| 00 001 | 011                                                         | 010                                                                                               |                                                                                                                              | 100                                                                                                                          | 101                                                                                                                                                          | 111                                                                                                                                                                                          | 110                                                                                                                                                                                                                           | 10                                                                                                                                                          |