## University of Massachusetts Amherst

# ScholarWorks@UMass Amherst

**Doctoral Dissertations**

**Dissertations and Theses**

July 2019

# A Discrete-Time Technique for Linearity Enhancement of **Wideband Receivers**

Mohammad Ghadiri Sadrabadi University of Massachusetts Amherst

Follow this and additional works at: https://scholarworks.umass.edu/dissertations\_2

Part of the Electrical and Electronics Commons, and the Signal Processing Commons

#### **Recommended Citation**

Ghadiri Sadrabadi, Mohammad, "A Discrete-Time Technique for Linearity Enhancement of Wideband Receivers" (2019). Doctoral Dissertations. 1545.

https://scholarworks.umass.edu/dissertations\_2/1545

This Open Access Dissertation is brought to you for free and open access by the Dissertations and Theses at ScholarWorks@UMass Amherst. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

# A DISCRETE-TIME TECHNIQUE FOR LINEARITY ENHANCEMENT OF WIDEBAND RECEIVERS

A Dissertation Presented

by

MOHAMMAD GHADIRI-SADRABADI

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2019

Electrical and Computer Engineering

© Copyright by Mohammad Ghadiri-Sadrabadi 2019 All Rights Reserved

# A DISCRETE-TIME TECHNIQUE FOR LINEARITY ENHANCEMENT OF WIDEBAND RECEIVERS

### A Dissertation Presented

by

## MOHAMMAD GHADIRI-SADRABADI

| Approved as to style and content by | <b>7:</b> |                |            |  |

|-------------------------------------|-----------|----------------|------------|--|

|                                     |           |                |            |  |

| Joseph C. Bardin, Chair             |           | -              |            |  |

|                                     |           |                |            |  |

| Robert W. Jackson, Member           |           | -              |            |  |

|                                     |           |                |            |  |

| Dennis L. Goeckel, Member           |           |                |            |  |

|                                     |           | -              |            |  |

| Grant Wilson, Member                |           |                |            |  |

|                                     |           |                |            |  |

|                                     | C. V. Ho  | ollot, Departi | nent Chair |  |

Electrical and Computer Engineering

## **DEDICATION**

To my parents, Fatemeh and Ahmad, who dedicated their lives to their children's success, my two inspirational sisters, Fereshteh and Saeedeh, and my wife, my friend, and my colleague, Shirin.

### ACKNOWLEDGMENTS

I wish to thank Prof. Bardin, for his great mentorship throughout the past seven years. I had the privilege to work with him during my PhD and Master studies and learned a lot from him.

I wan to thank the committee members Prof. Jackson, Prof. Goeckel, and Prof. Wilson, for their valuable feedback regarding this dissertation. In addition, I want to thank Prof. Duarte and Dian Mo for valuable discussions regarding this research.

I had the privilege of working with some amazing people at the RF Nano electronics group at University of Massachusetts Amherst for the past seven years. I shared a lot of the burden of working as a graduate student with them and without their help and support, I would have not been able to go through this phase of my life. Being away from my family in a different country, they became my family. For this, I am grateful to P. Ravindran, A.H. Coskun, M.Yogeesh, A. Subarmanian, M. Ayata, S.W. Chang, M. Conte, S. Montazeri, W.T.Wong, R. Kwende, M. Hosseini, Z. Zou, and S. Das.

This research would not have been possible if it was not for the help of the staff at electrical and computer engineering department at University of Massachusetts Amherst. For that I want to thank M. McCulloch, J. Pease, B. Barnett, and F. Caron.

I want to acknowledge the tax payers in my home country, Iran, who enabled me to get high quality public education and graduate college debt free. For that I will always be indebted to them. I also want to thank all the amazing people that I have met in the United States who accepted me in their community and made this country to feel like home.

### ABSTRACT

# A DISCRETE-TIME TECHNIQUE FOR LINEARITY ENHANCEMENT OF WIDEBAND RECEIVERS

#### MAY 2019

MOHAMMAD GHADIRI-SADRABADI

B.Sc., UNIVERSITY OF TEHRAN

M.Sc., UNIVERSITY OF MASSACHUSETTS AMHERST

Ph.D., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Joseph C. Bardin

A new signal processing technique is introduced to enhance the linearity performance of wideband radio frequency (RF) receivers. The proposed technique combines the advancements in mixer first architectures with a library of binary sequences as local oscillator signals to enable wide instantaneous bandwidth and high linearity for the RF receiver. To do so, N-bit pseudo-random-binary-sequences (PRBS) are used as local oscillator signals. The RF input signal is multiplied with the PRBS at the mixer and then averaged over the full sequence. This in effect reduces the amplitude of the signal and improves the overall linearity of the system. In order to enable full reconstruction of the input signal N channels are used with each employing a shifted version of a PRBS.

The effect of the proposed technique on different aspects of the system performance such as noise and linearity is discussed. In addition, the effect of nonidealities

A prototype integrated circuit (IC) is implemented in 130 nm CMOS technology to demonstrate the feasibility of the proposed technique. The design procedure of each circuit block is described and simulation results are used to evaluate the performance. The device is fabricated and characterized using a custom data acquisition system. Measurement results show good agreement with the expected values from simulation and analytical analysis.

Calibration techniques are introduced to minimize the effect of DC offsets, gain mismatches, and timing skews. Modifications to the implemented CMOS circuit are proposed to enable such calibrations and further enhance the overall performance of the system. The requirements for the precision of calibration techniques are derived and used to find the specifications of circuit block that are designed to enable these techniques. Calibration of DC offsets along with gain mismatches is carried out for the fabricated IC and results are shown. A digitally assisted technique is proposed to enable the calibration of timing skews. In addition, a review of additional implementation shortcomings that can affect the system performance are reviewed. Finally, a conclusion of the dissertation is presented along with potential future work for further enhancement of the system performance.

# TABLE OF CONTENTS

|            |                         | Page                                                                                             |

|------------|-------------------------|--------------------------------------------------------------------------------------------------|

| ACKN       | OWLI                    | ${f EDGMENTS}$ ${f v}$                                                                           |

| ABST       | RACT                    | vi                                                                                               |

| LIST (     | OF TA                   | BLES                                                                                             |

| LIST (     | OF FIG                  | GURES xii                                                                                        |

| CHAP       | TER                     |                                                                                                  |

| 1. INT     | rodi                    | UCTION                                                                                           |

| 1.1<br>1.2 |                         | Data Rate Communication Systems       2         enges Associated with Wideband Receivers       5 |

|            | 1.2.1<br>1.2.2          | Sensitivity and dynamic range of RF receivers                                                    |

| 1.3<br>1.4 |                         | Of-The-Art High Dynamic Range Wideband Receivers                                                 |

| 2. TH      | E PRO                   | POSED DISCRETE-TIME TECHNIQUE 17                                                                 |

| 2.1        | Discre                  | te-Time Signal-Processing Technique                                                              |

|            | 2.1.1<br>2.1.2<br>2.1.3 | Matrix Representation20Signal Reconstruction21Baseband Signal24                                  |

| 2.2        | Overa                   | ll System Linearity and Noise Performance                                                        |

|            | 2.2.1<br>2.2.2          | Linearity       26         Noise       31                                                        |

|            |                         | 2.2.2.1 Sampling Jitter                                                                          |

|           | 2.3                    | Summary                                                           | 38  |

|-----------|------------------------|-------------------------------------------------------------------|-----|

| 3.        |                        | FECT OF SYSTEMATIC ERRORS ON OVERALL                              |     |

|           | 1                      | PERFORMANCE                                                       | 39  |

|           | 3.1                    | DC Offset Errors                                                  | 40  |

|           | 3.2                    | Gain Mismatch                                                     |     |

|           | 3.3                    | Timing Skew                                                       | 45  |

|           | 3.4                    | Similarities of Mismatch Errors to Those of Time-Interleaved ADCs | 18  |

|           | 3.5                    | Summary                                                           |     |

|           |                        | V                                                                 |     |

| 4.        |                        | OS IMPLEMENTATION OF THE PROPOSED                                 |     |

|           | 1                      | ARCHITECTURE                                                      | 50  |

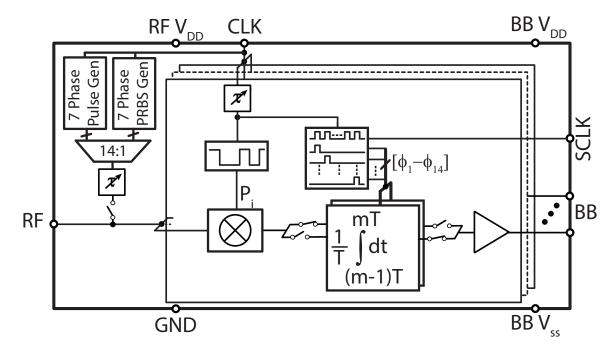

|           | 4.1                    | System Implementation                                             | 51  |

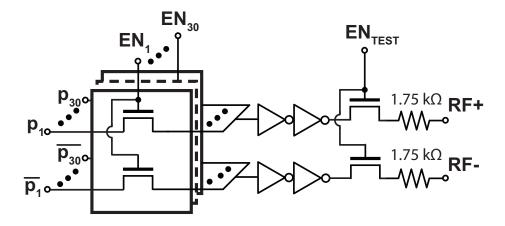

|           |                        | 4.1.1 Discrete-Time Signal Processing Block                       | 51  |

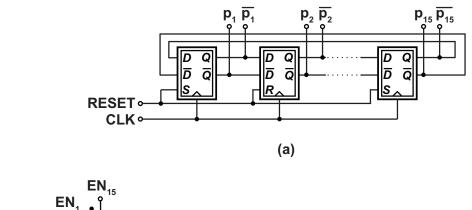

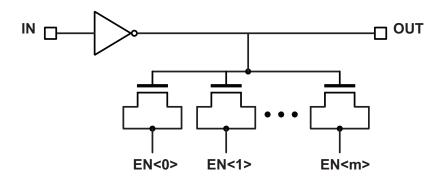

|           |                        | 4.1.2 Digital Control Signal Generation                           |     |

|           |                        | 4.1.3 Baseband Amplifier Design                                   | 60  |

|           | 4.2                    | Summary                                                           | 65  |

| <b>5.</b> | ME                     | ASUREMENT RESULTS OF THE PROTOTYPE IC                             | 67  |

|           | 5.1                    | PCB Design                                                        | 67  |

|           | 5.2                    | Custom Data Collection Board Design                               |     |

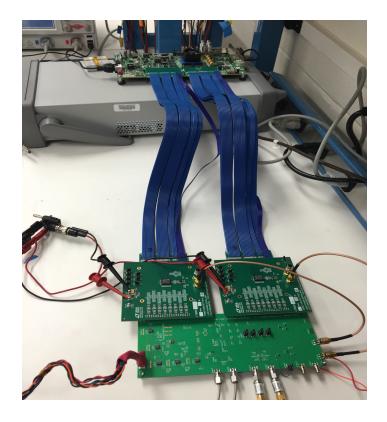

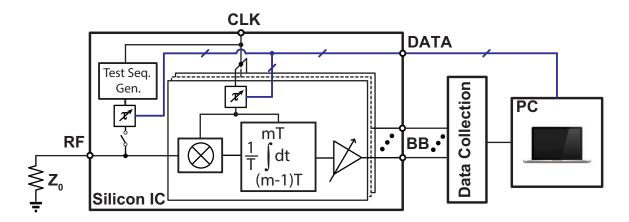

|           | 5.3                    | Complete Measurement Setup                                        |     |

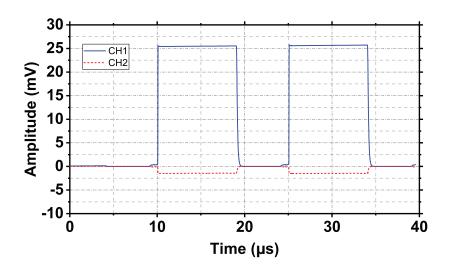

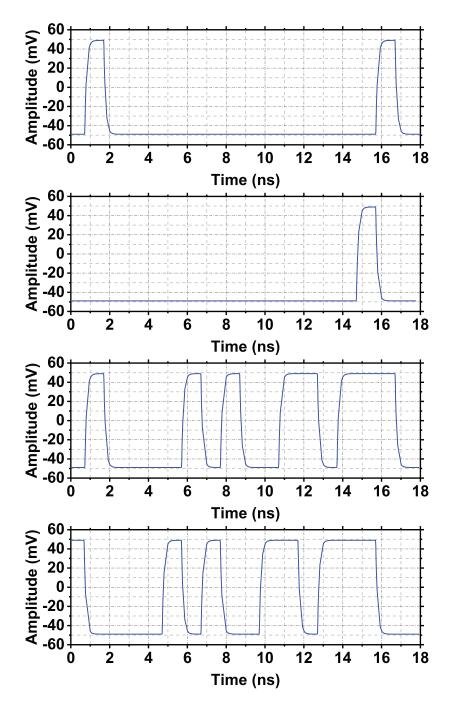

|           | 5.4                    | Time Domain Measurements                                          |     |

|           | 5.5                    | Summary                                                           | 91  |

| 6.        | $\mathbf{C}\mathbf{A}$ | LIBRATION OF MISMATCH EFFECTS                                     | 92  |

|           | 6.1                    | Calibration of DC Offset and Gain Mismatch Error                  | 93  |

|           |                        | 6.1.1 Calibration of DC Offset Mismatches                         | 03  |

|           |                        | 6.1.2 Calibration of Gain Mismatches                              |     |

|           |                        | 6.1.3 Calibration of Timing Mismatches                            |     |

|           | 6.2                    | DC offset and Matrix Calibration for the CMOS Implementation      | 97  |

|           |                        | -                                                                 |     |

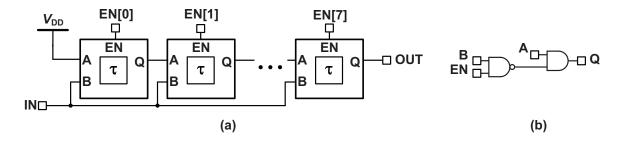

|           |                        | 6.2.1 Circuit Implementation of the Test Sequence Generator       | 98  |

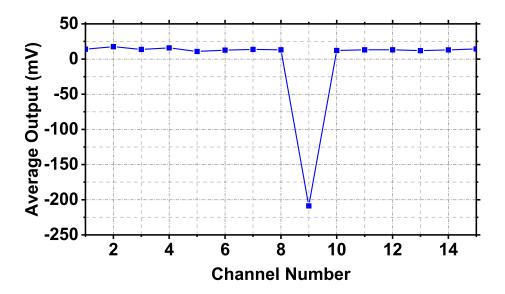

|           | 6.3                    | Calibration Measurements                                          | 100 |

|           | 6.4                    | Proposed Circuit Modifications for System Performance Enhancement | 107 |

|           |                        | 1.000.000.000.000.000.000.000.000.000.0                           |     |

|              |       | 6.4.1   | Timing Delay Generator Block                                     | 110 |

|--------------|-------|---------|------------------------------------------------------------------|-----|

|              | 6.5   | Test Se | equence Generation Circuitry                                     | 111 |

|              |       | 6.5.1   | Calibration of Timing Mismatches Using the Proposed Delay Blocks | 11/ |

|              |       | 6.5.2   | Other Mechanisms of Timing Skew                                  |     |

|              | 6.6   | Summ    | ary                                                              | 120 |

| 7.           | COI   | NCLU    | SION AND FUTURE WORK                                             | 122 |

|              | 7.1   | Future  | e Work                                                           | 123 |

| $\mathbf{A}$ | PPEI  | NDICE   | $\mathbf{E}\mathbf{S}$                                           |     |

|              |       |         | ΓΙΕS OF PRBS AND MATRIX OF PRBSS                                 |     |

|              |       |         | CODES USED FOR DATA PROCESSING                                   |     |

| C.           | . BLC | OCK D   | DIAGRAMS OF THE SIMULINK MODEL 1                                 | 135 |

| Bl           | IBLI  | OGRA    | PHY 1                                                            | 142 |

# LIST OF TABLES

| Table | Page                                                                                                                     |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| 1.1   | Examples of frequency bands used for 2G,3G and 4G applications 3                                                         |

| 1.2   | Example of wideband receivers with no off-chip filtering                                                                 |

| 5.1   | Comparison table                                                                                                         |

| A.1   | Different number of storage elements in a LFSR with the corresponding PRBS length one possible characteristic polynomial |

## LIST OF FIGURES

| Figure | Page                                                                                                                                                                                                         |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1    | Conceptual schematic diagram of a traditional multi-carrier multi-mode cellular modem4                                                                                                                       |

| 1.2    | Illustration of (a) dynamic range definition and (b) spurious free dynamic range (SFDR) definition                                                                                                           |

| 1.3    | An example of a blocker filtering scheme that incorporates the power of a large blocker to tune a notch filter for providing rejection 8                                                                     |

| 1.4    | An example of a wideband receiver where polyphase filtering is used for channelizing RF band                                                                                                                 |

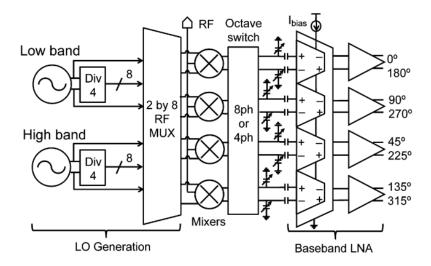

| 1.5    | Schematic diagram of the multiphase passive mixer phase receiver for low power and high linearity applications                                                                                               |

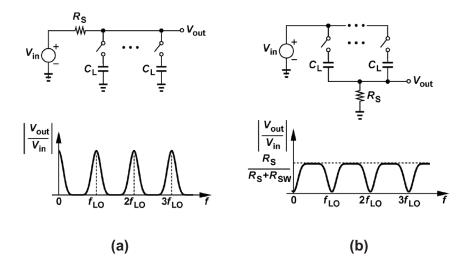

| 1.6    | Example of N-path filters used to implement (a) bandpass response and (b) notch response                                                                                                                     |

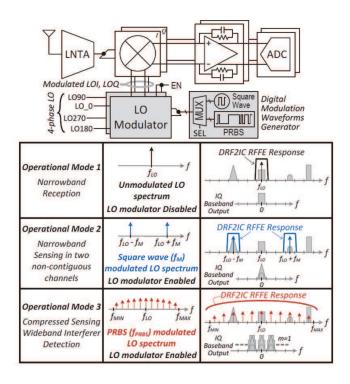

| 1.7    | System diagram of a wideband compressive sensing based receiver with blocker rejection                                                                                                                       |

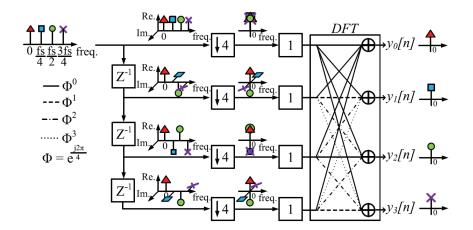

| 1.8    | Operating principle of the polyphase-FFT filter                                                                                                                                                              |

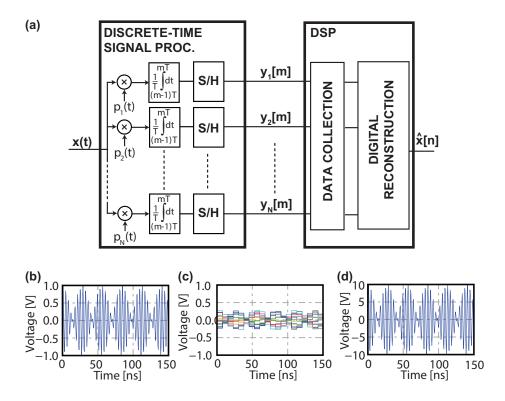

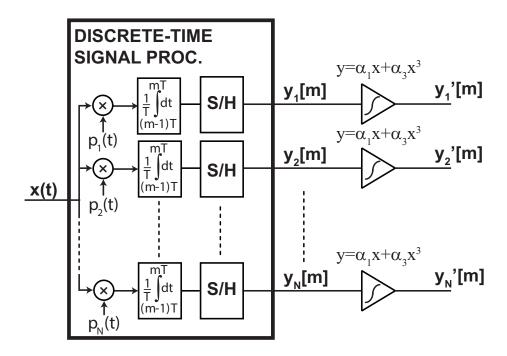

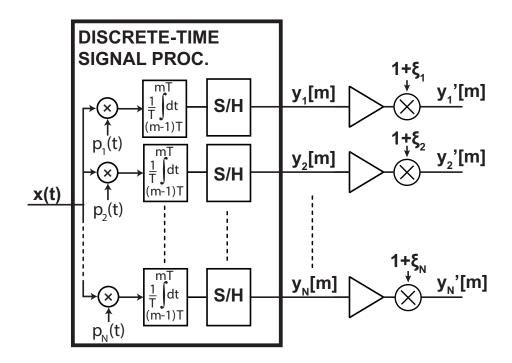

| 2.1    | Schematic diagram of the proposed discrete-time signal-processing technique along with the digital signal processing block required for collection of samples and reconstruction of the sampled input signal |

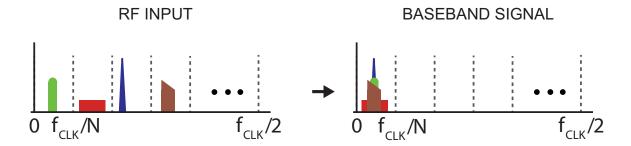

| 2.2    | Spectrum folding due to sub-sampling of the input signal and reduced bandwidth at each baseband output                                                                                                       |

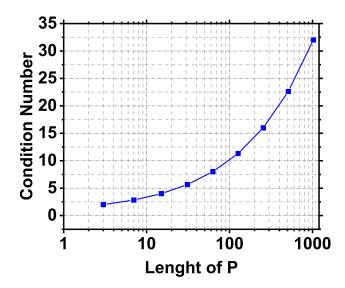

| 2.3    | Condition number of P for different lengths                                                                                                                                                                  |

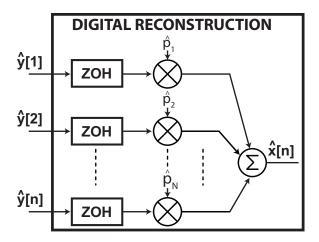

| 2.4    | Conceptual block diagram demonstrating reconstruction procedure                                                                                                                                              |

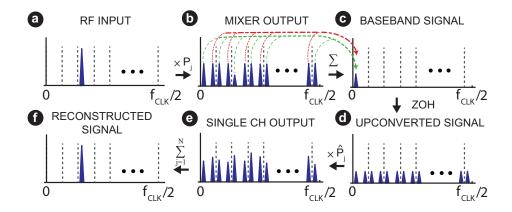

| 2.5  | Single-sided frequency spectrum at different steps. Steps (b)-(e) represent only one of the channels                                                                                                                                                                                 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

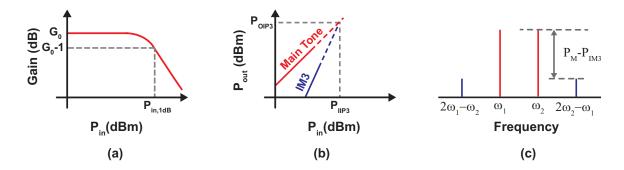

| 2.6  | (a) Compression of gain due to increase in input signal power. The input power that causes 1dB reduction is called 1dB compression point (P1dB). (b) The input power at which the extrapolated IM3 tone and main tone signal would have equal output power.(c) IIP3 calculation test |

| 2.7  | Inclusion of the third order nonlinearity in the top level system. All amplifiers are assumed to exhibit the same nonlinearity properties                                                                                                                                            |

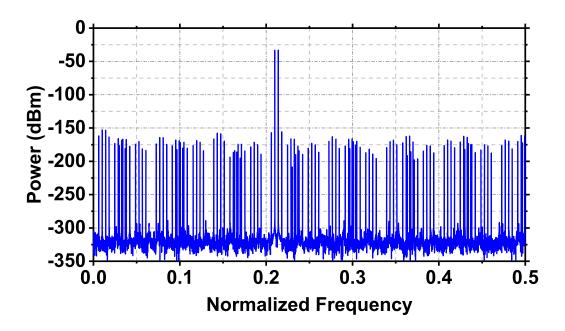

| 2.8  | An example spectrum of a reconstructed two tone signal with third-order nonlinearity at baseband. For these simulation $\alpha_1=1$ and $\alpha_3=0.1$ . These numbers correspond to a gain of 0 dB and IIP3 of approximately 40 dBm into a 1 $\Omega$ termination                   |

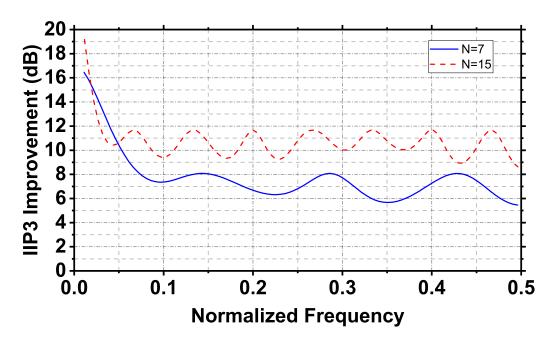

| 2.9  | Simulation results of system IIP3 improvement over that of each channel for PRBS lengths of N=7 and N=15                                                                                                                                                                             |

| 2.10 | Top level diagram of the receiver system including noise sources referred to the input of the baseband amplifier for each channel                                                                                                                                                    |

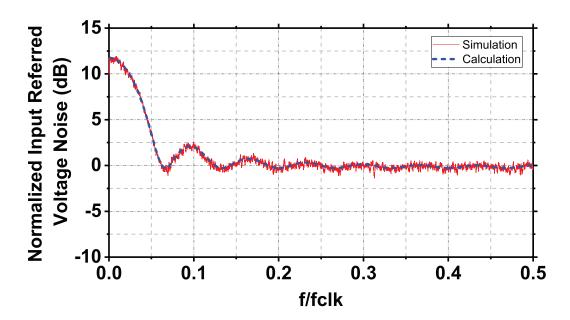

| 2.11 | Comparison of simulated noise from Matlab Simulink model for N=15 and results of (2.27)                                                                                                                                                                                              |

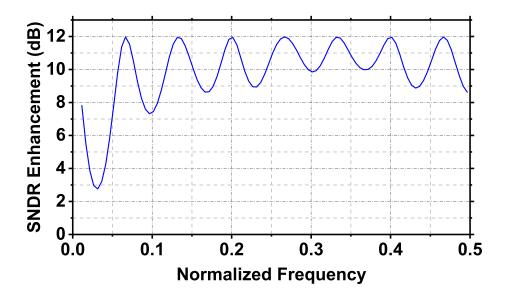

| 2.12 | Overall SNDR enhancement of the system over frequency for N=15                                                                                                                                                                                                                       |

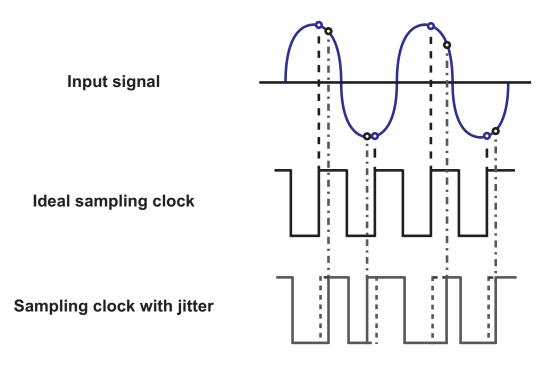

| 2.13 | Effect of clock jitter on sampling signals                                                                                                                                                                                                                                           |

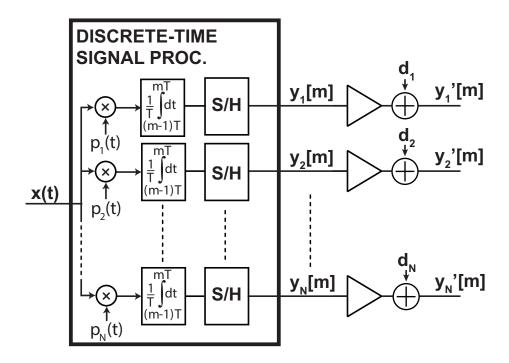

| 2.14 | (a) Phase noise of the oscillator adds a skirt to the frequency spectrum of the clock signal, (b) The noise skirt of a blocker signal corrupting the spectrum of a message signal                                                                                                    |

| 3.1  | Top level diagram of the system including the dc offsets modeled as additive errors to the signal at the output of amplifiers                                                                                                                                                        |

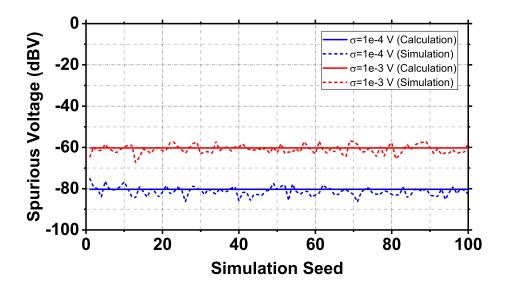

| 3.2  | Monte Carlo simulation results of DC offset induced spurious content along the average value predicted by (3.4)                                                                                                                                                                      |

| 3.3  | Top level diagram of the system including the effect of gain mismatch errors                                                                                                                                                                                                         |

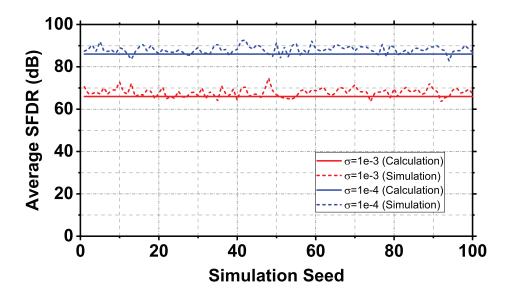

| 3.4 | Monte Carlo simulation results of SFDR values due to gain mismatch induced spurious tones versus predicted results by (3.10)                                                                                                                                                                                           |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

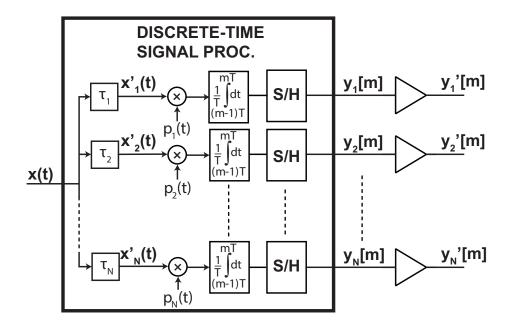

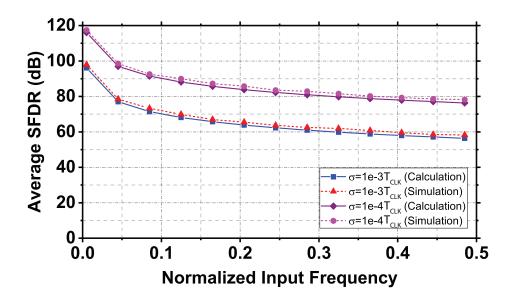

| 3.5 | Top level diagram demonstrating the effect of timing skew between channels which can be modeled as a different delay for the input signal to each individual channel                                                                                                                                                   |

| 3.6 | Simulation results of the effect of timing skew on expected value of the overall system SFDR versus input frequency                                                                                                                                                                                                    |

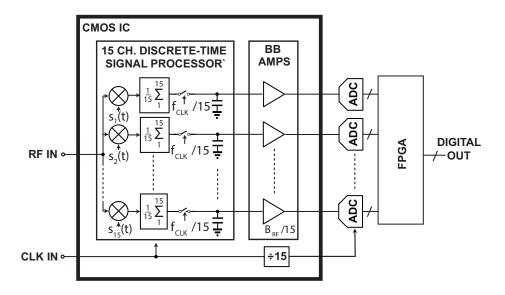

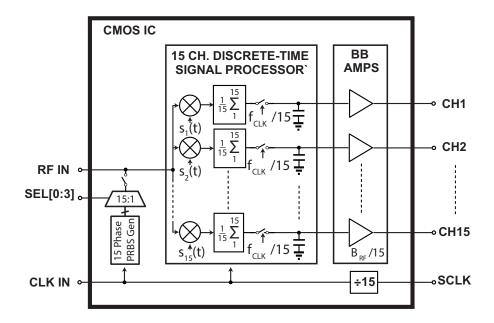

| 4.1 | Top level schematic diagram of the 15 channel prototype CMOS  IC                                                                                                                                                                                                                                                       |

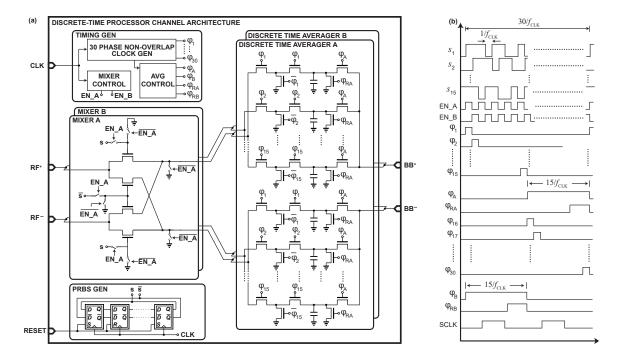

| 4.2 | (a) Simplified schematic diagram of a single channel of the front-end discrete-time signal processor. (b) Timing diagram. The signal SCLK shown in the timing diagram is generated globally and used to drive off-chip ADCs                                                                                            |

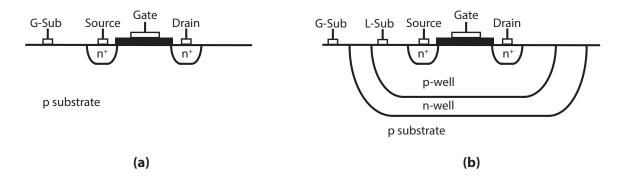

| 4.3 | Schematic diagram of the cross section of (a) a regular n-FET device and (b) a triple-well n-FET device                                                                                                                                                                                                                |

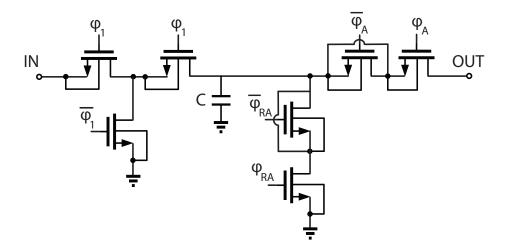

| 4.4 | Detailed schematic diagram of the switched-capacitor circuit including the dummy transistors to reduce charge injection effects                                                                                                                                                                                        |

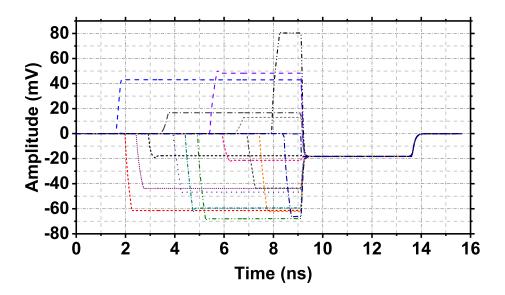

| 4.5 | Cadence transient simulation of the switched-capacitor circuit demonstrating the sampling and averaging operation of the discrete time signal processing block. Dashed lines show the voltage on each individual sampling capacitor and the solid line shows the voltage at the input node of the baseband amplifier56 |

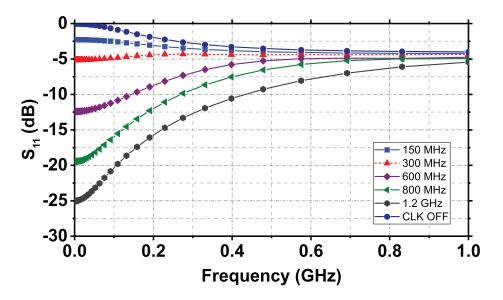

| 4.6 | Simulated input reflection coefficient for a variety of clock frequencies                                                                                                                                                                                                                                              |

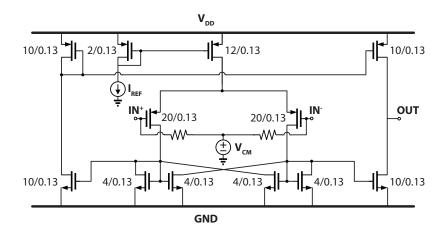

| 4.7 | Schematic diagram of the LVDS to LVCMOS converter. Off-chip series ac coupling capacitors are required to isolate the bias circuit. For this design $V_{\rm CM}=0.6{\rm V},V_{\rm DD}=1.2{\rm V},{\rm and}I_{\rm REF}=250$ uA                                                                                          |

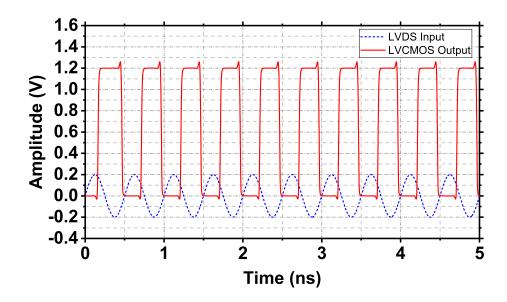

| 4.8 | Simulation results of the LVDS to CMOS converter for clock frequency of 2 GHz                                                                                                                                                                                                                                          |

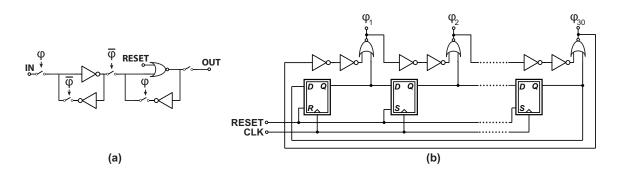

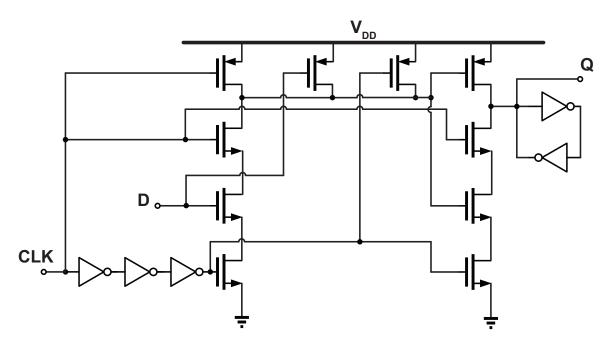

| 4.9 | Simplified schematic diagram of the (a) D flip-flop circuit and (b) non-overlapping phase generator                                                                                                                                                                                                                    |

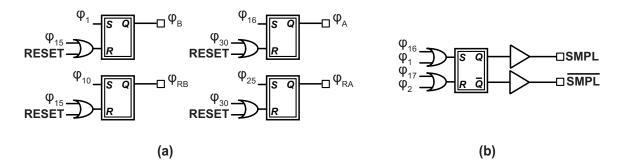

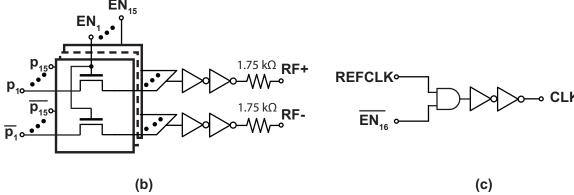

| 4.10 | Schematic diagram of (a) the control signals generator and (b) the ADC reference clock generator                                                                                                                                                                                                                                              |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

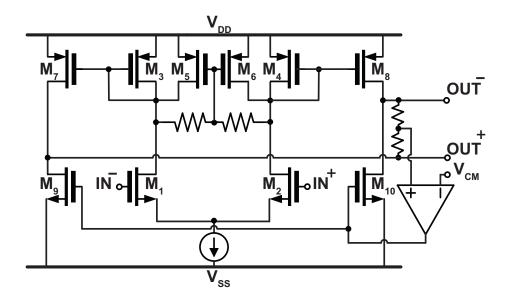

| 4.11 | Simplified schematic diagram of the baseband amplifier including the common-mode feedback loop to set the output DC voltage61                                                                                                                                                                                                                 |

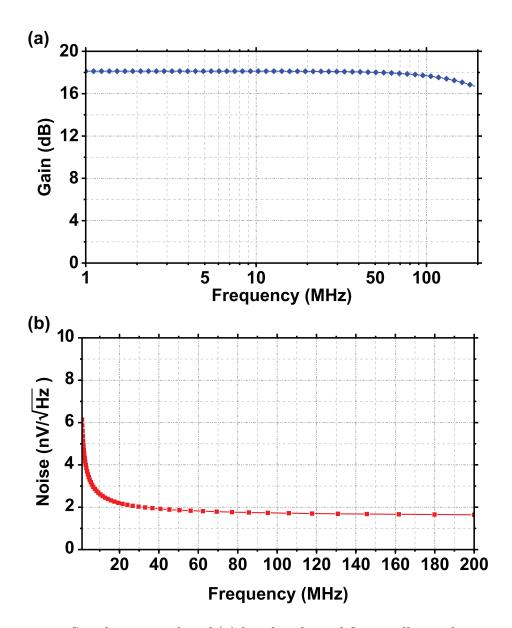

| 4.12 | Simulation results of (a) baseband amplifier small signal gain and (b) noise                                                                                                                                                                                                                                                                  |

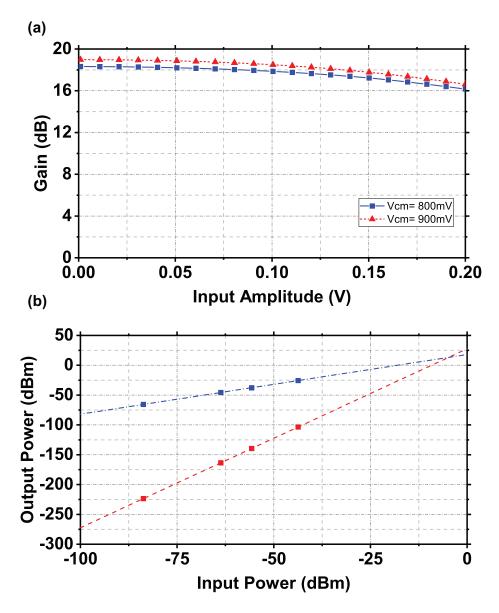

| 4.13 | Simulation results of (a) the baseband amplifier gain compression for two output common mode voltages of $800\mathrm{mV}$ and $900\mathrm{m}$ and (b) the baseband amplifier IIP3 for $V_{cm}$ of $900\mathrm{mV}$                                                                                                                            |

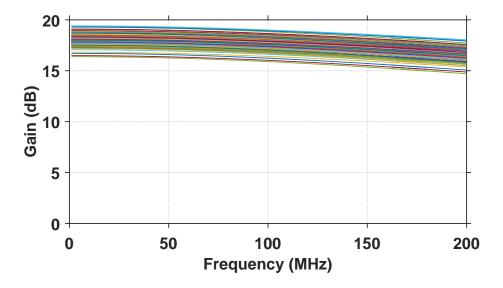

| 4.14 | Monte Carlo simulation results of the baseband amplifier frequency response over 100 runs. Results include both process and mismatch variations                                                                                                                                                                                               |

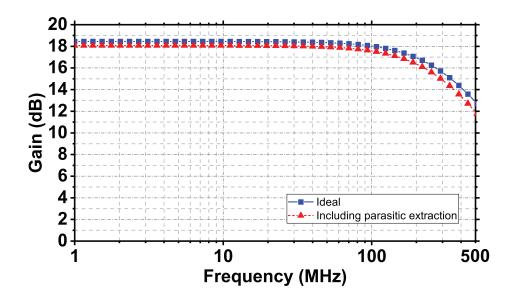

| 4.15 | Comparison of the simulation results for ideal schematic versus the layout parasitic extracted circuit                                                                                                                                                                                                                                        |

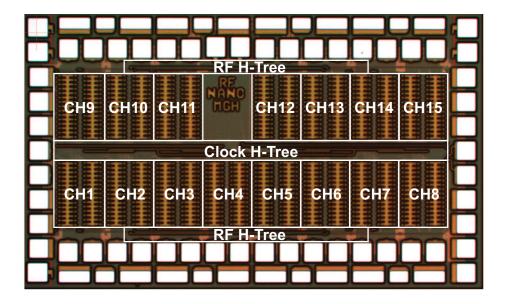

| 5.1  | Die photo of the fabricated IC in Global Foundries BiCMOS8HP technology                                                                                                                                                                                                                                                                       |

| 5.2  | Block diagram of the PCB designed for testing of the prototype IC                                                                                                                                                                                                                                                                             |

| 5.3  | Bottom side of the PCB. The lines for all channels are matched to less than 0.1% to ensure matched phasing                                                                                                                                                                                                                                    |

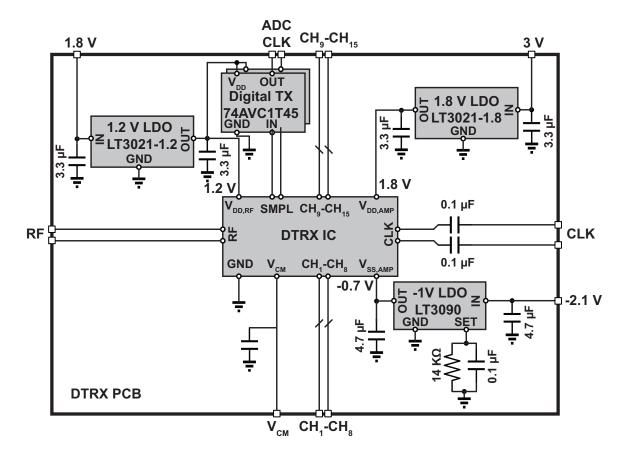

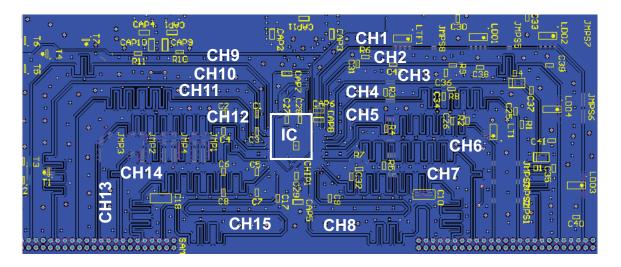

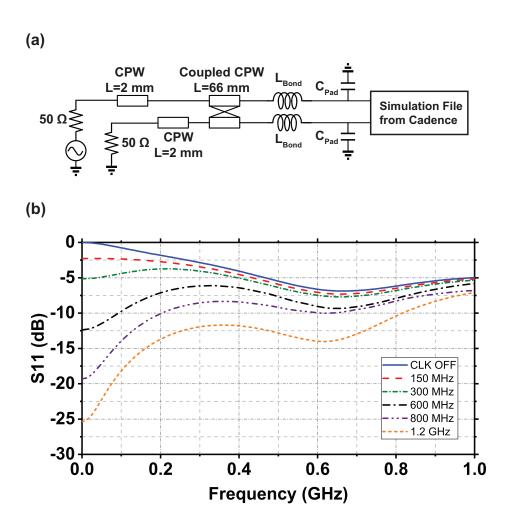

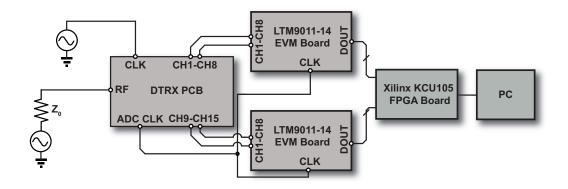

| 5.4  | (a) Block diagram of the simulation setup in Microwave Office using the extracted S-parameter files from Cadence. For this simulation a bond wire inductance of 0.5 nH and a pad capacitance of 0.1 pF was assumed.(b) $S_{11}$ simulation results of the system for different clock frequencies including effect of PCB traces on RF lines71 |

| 5.5  | Block diagram of the measurement setup employing two LTM9011-14 ADC EVM boards and a Xilinx KCU105 FPGA board                                                                                                                                                                                                                                 |

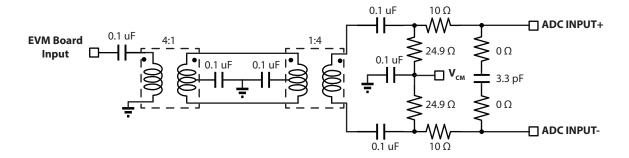

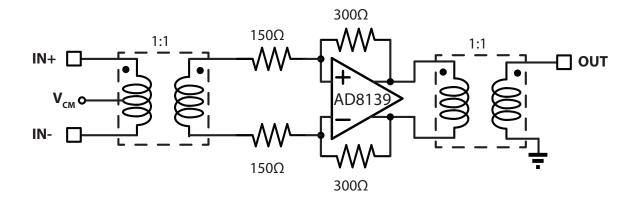

| 5.6  | The schematic diagram of the ADS5249 EVM board input circuitry                                                                                                                                                                                                                                                                                |

| 5.7  | Schematic diagram of the single channel of the adapter board                                                                                                                                                                                                                                                                                  |

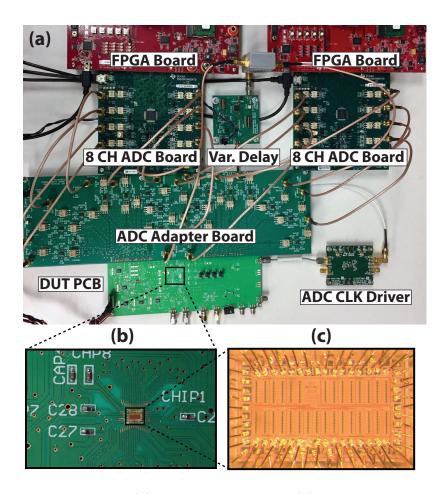

| 5.8  | Photograph of (a) Measurement setup,(b) assembled PCB, and (c) the wire-bonded chip                                                                                                                                                                                                                                                           |

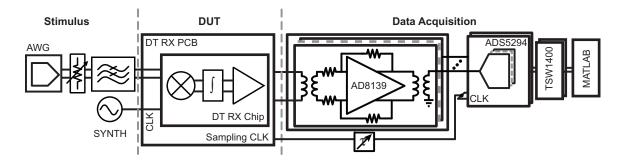

| 5.9  | Schematic diagram of the complete measurement setup                                                                                                                                                                                                                                                                                                                             |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

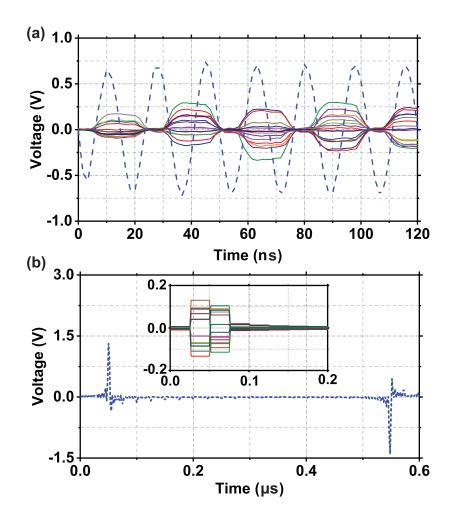

| 5.10 | (a) Reconstructed waveform for a 58 MHz sinusoidal input (dashed blue line) along with oscilloscope measurements of the 15 ADC inputs. (b) Reconstructed waveform for the case in which the input is excited using a pulse waveform. The inset contains the fifteen digitized baseband outputs over the time period where the pulse was active.Reproduced from [38] © IEEE 2018 |

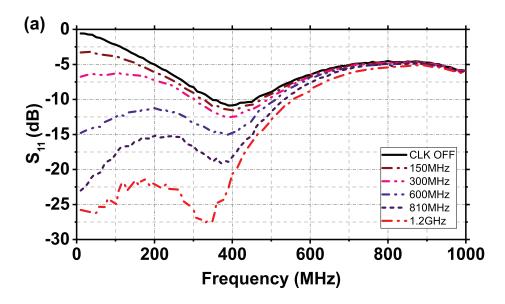

| 5.11 | Differential mode input reflection coefficient. The measurement reference plane is at the PCB input. Reproduced from [38]©IEEE 2018                                                                                                                                                                                                                                             |

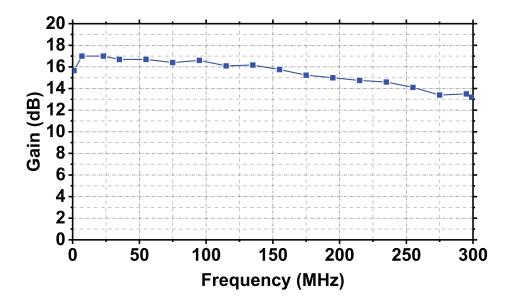

| 5.12 | Conversion gain of the receiver over frequency                                                                                                                                                                                                                                                                                                                                  |

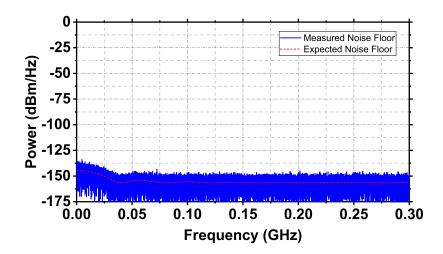

| 5.13 | Input referred noise floor of the receiver versus the expected noise floor based on simulation results and aliasing factor at the ADC input                                                                                                                                                                                                                                     |

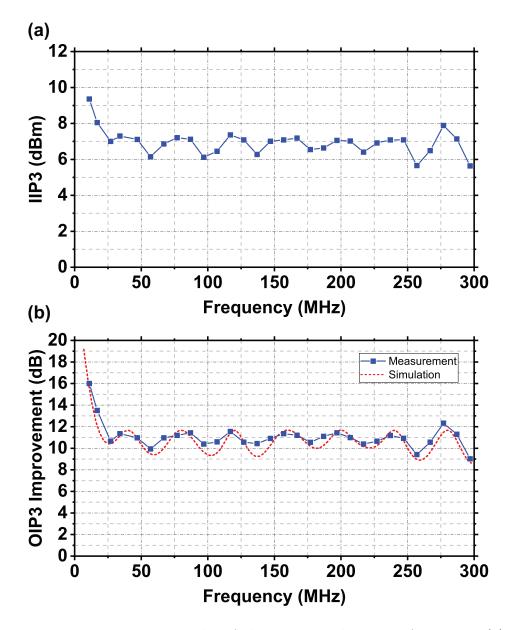

| 5.14 | Measurement results of the intermodulation performance                                                                                                                                                                                                                                                                                                                          |

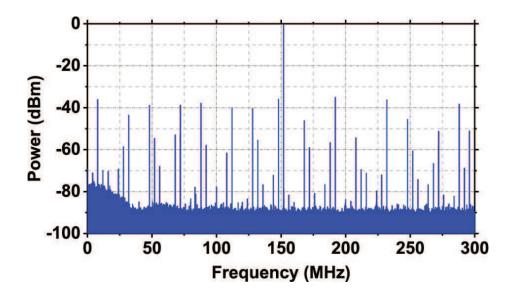

| 5.15 | Spectrum of the reconstructed waveform for a 152 MHz CW tone. All spurious tones above -70 dBm were verified to be at frequencies predicted by analysis in Chapter 3                                                                                                                                                                                                            |

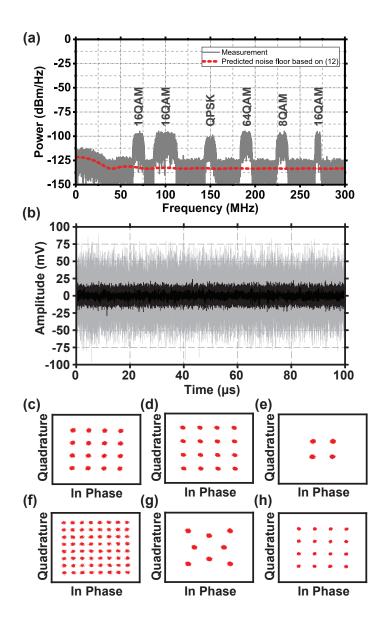

| 5.16 | Example of wideband operation of the system85                                                                                                                                                                                                                                                                                                                                   |

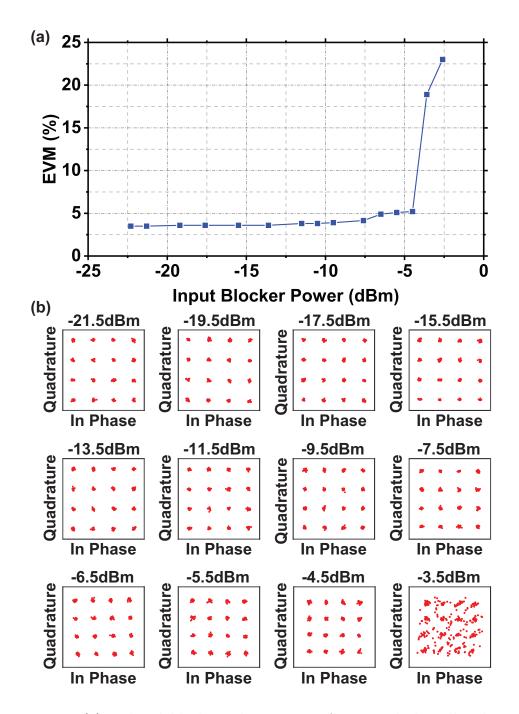

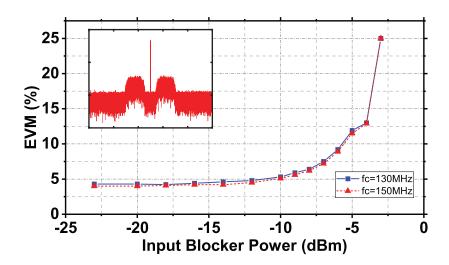

| 5.17 | In-band blocker tolerance test for a single broadband message signal                                                                                                                                                                                                                                                                                                            |

| 5.18 | In-band blocker tolerance test for two broadband message signals 88                                                                                                                                                                                                                                                                                                             |

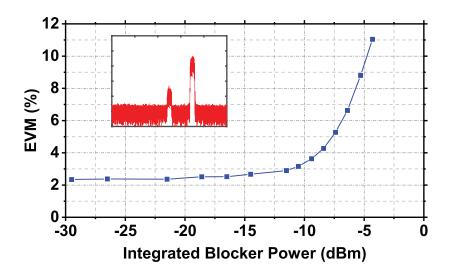

| 5.19 | Broadband blocker tolerance test                                                                                                                                                                                                                                                                                                                                                |

| 6.1  | Schematic diagram of the CMOS IC including the additional PRBS generator block at the RF input for matrix calibration                                                                                                                                                                                                                                                           |

| 6.2  | Schematic diagram of (a) 15 phase PRBS generator , (b) the 15 to 1 multiplexer, and (c) clock gating for disabling the PRBS generator during normal operation of the system                                                                                                                                                                                                     |

| 6.3  | Cadence transient simulation results of the signal at the baseband amplifier input for two sample channels with a PRBS sequence connected to the RF input. The input PRBS test signal phase is chosen to be in-phase with channel 1                                                                                                                                             |

| 6.4  | Measurement setup used for calibration measurements                                                                                                                                                                                                                                                                                                                 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.5  | Measurement results of the average output value at different channels for a single phase of the PRBS test generator                                                                                                                                                                                                                                                 |

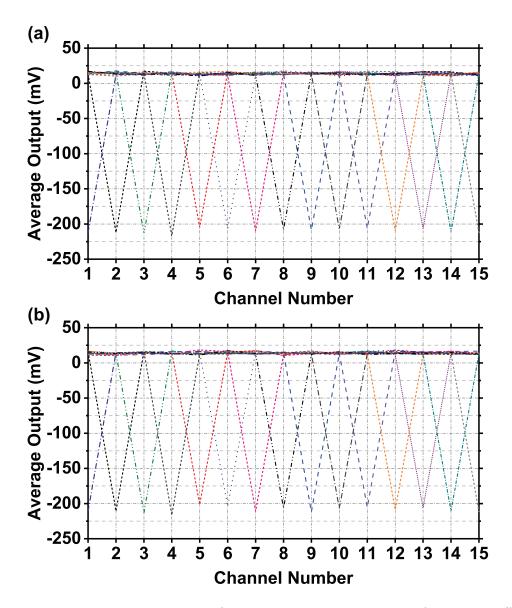

| 6.6  | Measurement results of the average channel output for all 15 different phases of the PRBS corresponding to (a) capacitor bank 1 and (b) capacitor bank 2                                                                                                                                                                                                            |

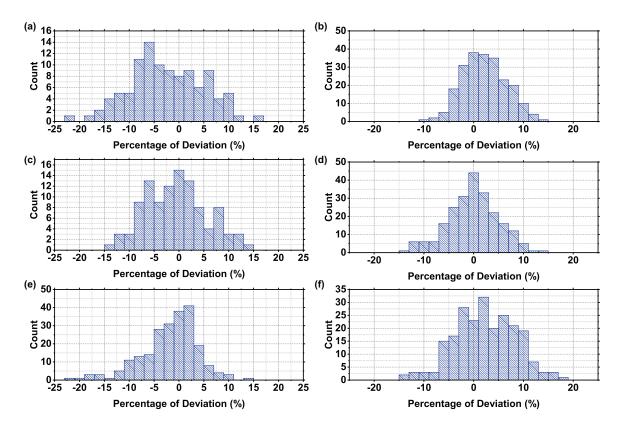

| 6.7  | Histogram of difference of individual elements of chip # 1 between (a) $\bf P$ and $\bf P_{m,1}$ , (c) $\bf P$ and $\bf P_{m,2}$ , and (e) $\bf P_{m,1}$ and $\bf P_{m,2}$ , and the histogram of the difference of individual elements of chip # 2 between (b) $\bf P$ and $\bf P_{m,1}$ , (b) $\bf P$ and $\bf P_{m,2}$ , and (f) $\bf P_{m,1}$ and $\bf P_{m,2}$ |

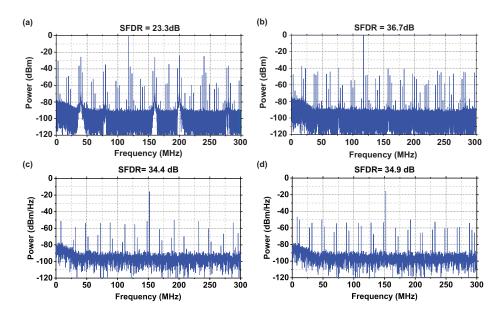

| 6.8  | Spectrum of the reconstructed signal for a 117 MHz sine wave signal for chip # 1 using (a) the ideal matrix and (b) calibrated matrices, and the Spectrum of the reconstructed signal for a 152 MHz sine wave signal for chip # 2 using (c) the ideal matrix and (d) the calibrated matrices                                                                        |

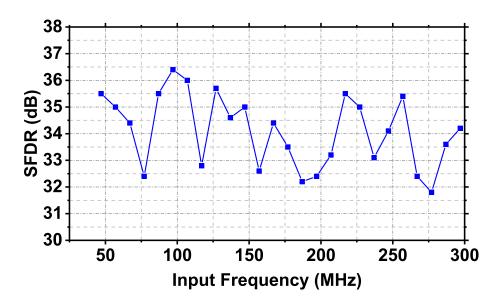

| 6.9  | SFDR performance of the IC #2 over RF input frequency 107                                                                                                                                                                                                                                                                                                           |

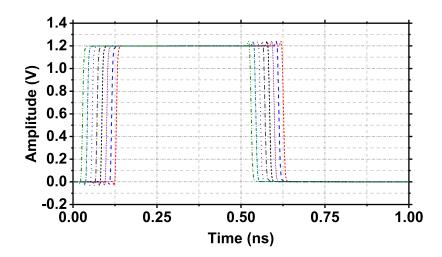

| 6.10 | Monte Carlo simulation results of a minimum sized inverter output for a pulse input. 200 simulation seeds are run and a maximum delay mismatch of 6 ps is observed. The inverter is loaded with the same inverter                                                                                                                                                   |

| 6.11 | Top level schematic diagram of the implemented CMOS circuit in 65nm Technology                                                                                                                                                                                                                                                                                      |

| 6.12 | Schematic diagram of (a) the full 8 element delay generator and (b) the individual delay cell                                                                                                                                                                                                                                                                       |

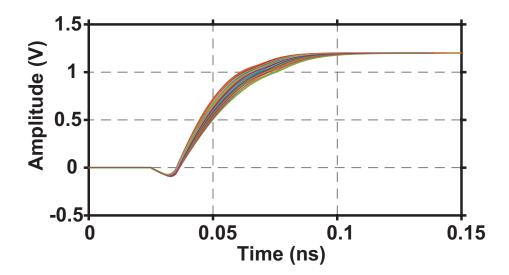

| 6.13 | Transient simulation results of the delay generator block for a impulse input signal over different delay settings                                                                                                                                                                                                                                                  |

| 6.14 | Alternative programmable delay generator for finer resolution delays                                                                                                                                                                                                                                                                                                |

| 6.15 | Schematic diagram of the 30-1 multiplexer employed at the output of the test sequence generator block                                                                                                                                                                                                                                                               |

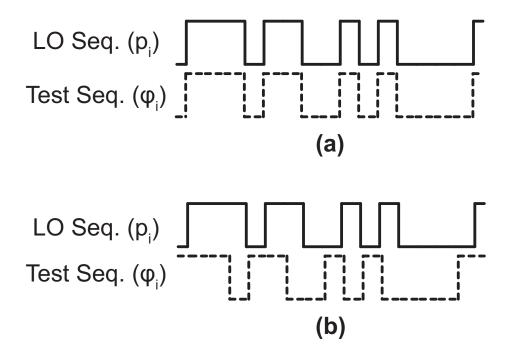

| 0.10 | generator block when (a) $\phi_1$ of the pulse generator, (b) $\phi_3$ , and (c) first phase of the PRBS, are selected                                                                                     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.17 | Closed loop system employed for calibration of timing skews among channels                                                                                                                                 |

| 6.18 | Timing diagram of the test sequence at the input of channel 1 along with the LO sequence of Channel 1 for (a) when no delay and (b) a non-zero delay, between the two sequences                            |

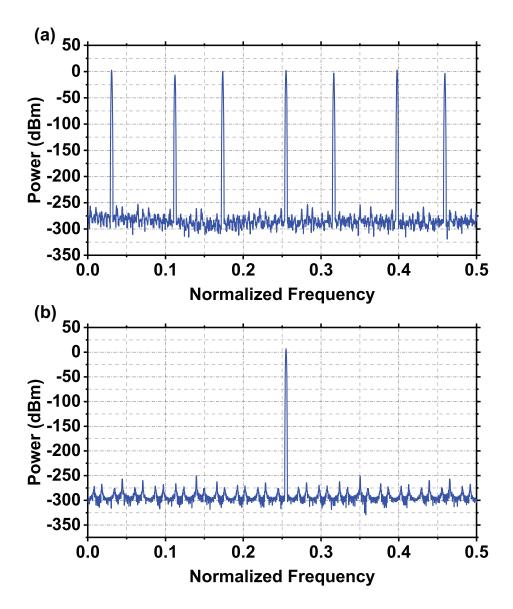

| 6.19 | Matlab simulation result for the spectrum of the reconstructed signal for a sine wave input at 255 MHz for (a) a system with random timing skew among four channels, (b) after calibration of timing skews |

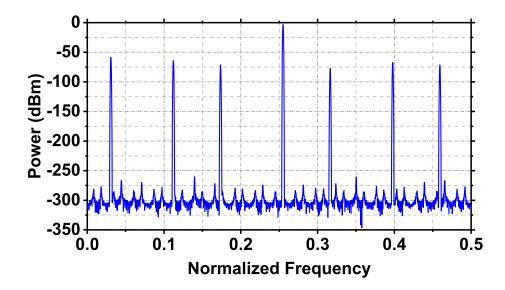

| 6.20 | Matlab simulation result for the spectrum of the reconstructed signal for a sine wave input after calibration of the timing skews with the presence of gain mismatches among channels                      |

| 7.1  | Schematic diagram of the hybrid lath flip-flop circuit used to increase the operating speed of the system                                                                                                  |

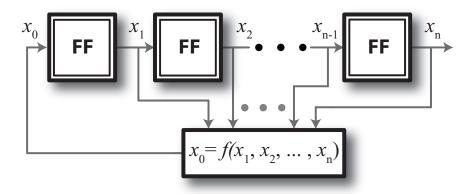

| A.1  | A schematic diagram of an n-bit LFSR                                                                                                                                                                       |

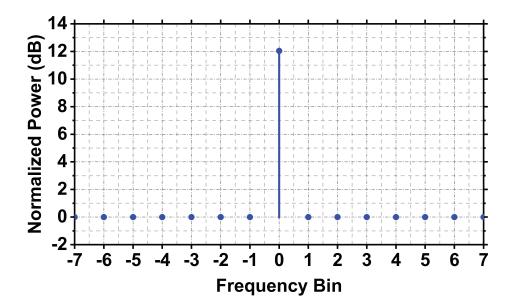

| A.2  | The spectrum of the inverse PRBS normalized to the power at non-zero frequency bins                                                                                                                        |

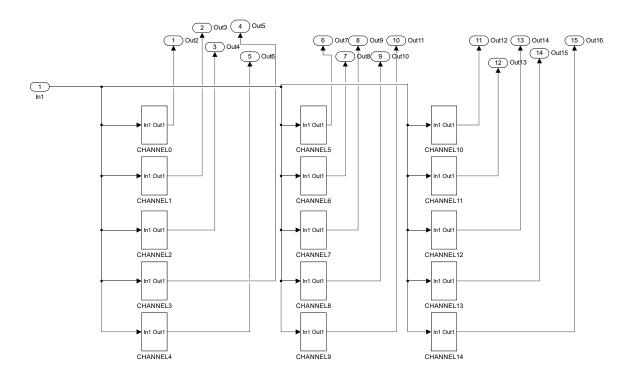

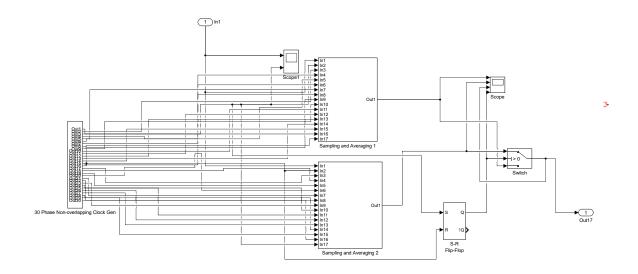

| C.1  | Top level diagram of the Simulink model for the 15 channel system. 136                                                                                                                                     |

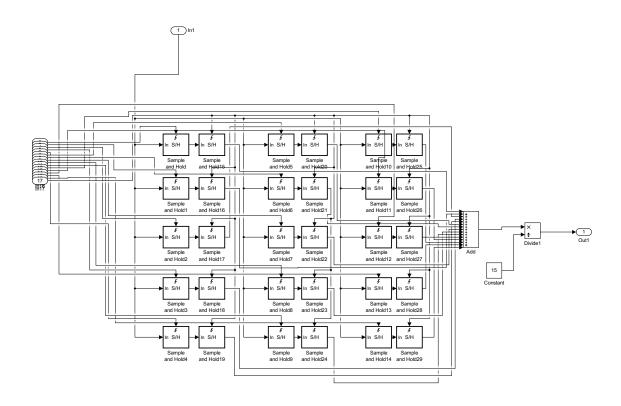

| C.2  | Schematic diagram of each channel                                                                                                                                                                          |

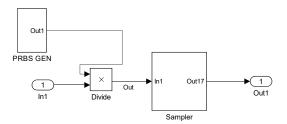

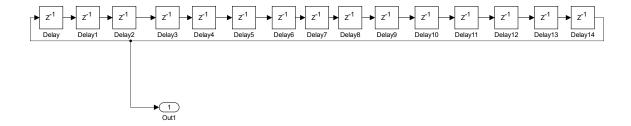

| C.3  | Schematic diagram of the PRBS generator. The initial value of delay elements for each channel was set based on the PRBS                                                                                    |

| C.4  | Schematic diagram of the sampler                                                                                                                                                                           |

| C.5  | Schematic diagram of the 30 phase non-overlapping clock generator.  The initial value for all delay elements is set to 0 except the last element for which it is set to 1                                  |

| C.6  | Schematic diagram of the sampling and averaging block                                                                                                                                                      |

## CHAPTER 1

### INTRODUCTION

This dissertation is focused on the development of a novel discrete-time technique to enhance the linearity of wideband radio frequency (RF) receivers. The effect of the proposed technique on different RF receiver performance metrics is studied and discussed. The dissertation is organized as follows:

- 1. Motivation and current state-of-the-art wideband receivers (Chapter

- 1)— The recent growing demand for wideband receivers is discussed and some of the challenges associated with these systems are described. Some examples of available techniques to mitigate these challenges are reviewed and their advantages and shortcoming are discussed.

- 2. **Theory** (Chapters 2, 3)— The discrete-time RF signal-processing technique is introduced and a matrix representation of the overall system is described to further demonstrate the operating principles of the proposed technique. Using both analytical and numerical solutions, the effect of the proposed technique on different aspects of the receiver performance is studied. In addition, the effect of nonidealities that would arise with system implementation on silicon integrated circuit (IC) is studied.

- 3. Implementation (Chapter 4)— The implementation of a prototype CMOS IC to evaluate the performance of the proposed technique is presented. Different design considerations for the implementation are discussed. Computer aided simulations are used to evaluate the performance of the design.

- 4. Measurement Results and Discussion (Chapter 5)— The measurement results of the fabricated IC in 130nm CMOS technology are reported. The measurement setup and the reconstruction procedure are described in detail and limitations on performance due to the setup are discussed. The basic operation of the system is evaluated with time domain measurements. Then several measurement results are used to evaluate linearity and noise performance of the system. It will be shown that nonidealities in the system limit the spurious free dynamic range (SFDR) of the system and appropriate techniques are required to reduce their effect.

- 5. Calibration Techniques to Enhance System Performance (Chapter 6)—

Several techniques that can be used to reduce the effect of mismatches are proposed. The circuit implementation of these techniques is also presented.

Some of these techniques are implemented on the CMOS IC of Chapter 4 and measurement results are shown to discuss the effect of calibration.

## 1.1 High Data Rate Communication Systems

As technology becomes more integrated with every aspect of daily life, more and more electronic devices are used that require wireless connection. New applications such as internet-of-things (IoT), smart cars and wearable electronics are expected to increase the number of wireless connected devices to more than 1000 times the current number by the year 2020 [1]. This large increase in the number of users along with already limited frequency spectrum has become a big challenge in development of the next generation of communication devices such as fifth generation mobile networks (5G).

In addition to larger number of users, higher data rates required for many of new applications, such as high resolution video streaming, has created significant demand for communication systems with wider instantaneous bandwidth. One early example

**Table 1.1.** Examples of frequency bands used for 2G,3G and 4G applications. Reproduced from [2] ©IEEE 2013. The narrowband nature of all bands should be noted.

| Band               | Uplink (MHz) | Downlink (MHz) | Signal Bandwidth (MHz) |

|--------------------|--------------|----------------|------------------------|

| $700 \mathrm{MHz}$ | 746–763      | 776-793        | 1.25–10                |

| AWS                | 1710 – 1755  | 2110 – 2155    | 2.5 – 15               |

| IMT Extension      | 2500 – 2570  | 2620 – 2690    | 2.5 – 20               |

| GSM 900            | 880 – 915    | 925 – 960      | 1.25 - 5               |

| UMTS Core          | 1920 – 1980  | 2110 – 2170    | 5–10                   |

| GSM 1800           | 1710 - 1785  | 1805 – 1880    | 1.25 – 5               |

| PCS 1900           | 1850 – 1910  | 1930 – 1990    | 1.25 - 5               |

| Cellular 850       | 824-849      | 869-894        | 1.25 - 5               |

| Digital Dividend   | 470 – 854    | 470 - 854      | 1.25 – 20              |

that can highlight the importance of wideband signal operation in recent years is the allocation of frequency band between 3.1-10.6 GHz by FCC for the unlicensed use of ultra-wideband (UWB) in 2002 [3]. Ultra-wideband is defined as signals with bandwidth larger than 500 MHz. This at the time was the largest allocation of spectrum by FCC in history which illustrates the preceived importance of growing wideband applications in the past decade [4]. Since then, wideband orthogonal frequency division multiplexing (OFDM) systems that operate in the allocated band have provided data rates of 53.3-480 Mbps [5]. These data rates along with predicted data rates of 100Mbps predicted for 5G [6] applications when compared to those of traditional cellular standard (shown in Table 1.1), show significant shift towards higher bandwidth systems.

As a result, future generanios of wireless devices face two major challenges: the increased number of users in the already dense spectrum spaces and the higher data transfer rates. The capacity of a communication channel (C) with a fixed bandwidth (B) and signal to noise ratio (SNR) performance can be found using the Shannon-Hartley theorem as

$$C = B\log_2(1 + SNR). \tag{1.1}$$

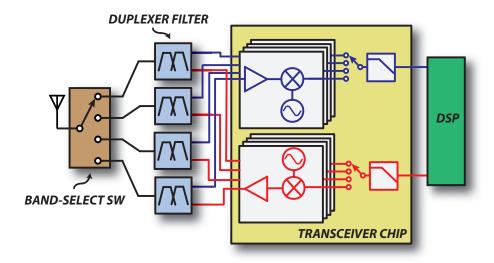

**Figure 1.1.** Conceptual schematic diagram of a traditional multi-carrier multi-mode cellular modem.

Thus the signal capacity an be significantly enhanced for wider channel bandwidths. Several proposals have been introduced to address this issue such as the use of higher unallocated frequency bands, such as mm-Wave frequency range, and more efficient communication channels. The former has gained a lot of attention specially for the prospect of 5G where multiple mm-wave bands have been considered as potential candidates [6]. The latter is focused on addressing the issue of low utilization of already allocated frequency spectrum. One way of increasing utilization is to employ cognitive radios that scan the spectrum and exploit any unused frequency band [7]. Another technique is to employ carrier aggregation (CA) which uses two or more adjacent (intra-band) or none-adjacent (inter-band) channels for the transmission of wideband data [8–10].

Traditional wireless communication systems are designed to transmit and receive in specific frequency bands that are limited in bandwidth. An example of such systems is current cellphone devices. These devices use multiple off-chip duplexers that are each tuned to a specific carrier frequency to eliminate unwanted signals out of the band of interest. A conceptual example of such system is illustrated in Fig. 1.1. However, development of advanced communication systems, such as cognitive radios, requires the ability to communicate over a wide frequency range. The large number of duplexers and switches to enable such operation using traditional systems increases the loss and form factor of these devices beyond what is acceptable for current devices [11]. An alternative approach is to use advanced wireless devices such as software-defined-radios (SDR) that, unlike the traditional receivers, are capable of receiving multiple channels and multiple standards by adapting themselves [12–14]. Such systems require receivers that operate with large bandwidths and a processing block that controls the receiver. There are several challenges that are associated with such wideband devices that will be discussed next.

## 1.2 Challenges Associated with Wideband Receivers

At each instance of time many different signals that differ in frequency, bandwidth and power occupy different portions of the frequency spectrum received by a given device. In addition, the spectral content significantly changes from location to location. Thus the desired message signal for a specific communication device may be accompanied by large blocker signals with small frequency offsets. Hence, a wideband receiver that does not incorporate off-chip high quality factor (Q) filtering would be susceptible to large blocker signals. These large blocker signals can be from other users or even from the transmitter path of the same device. This puts stringent requirements on the receiver dynamic range. Prior to further discussion of challenges associated with these requirements, some fundamental concepts of radio frequency (RF) receivers will be reviewed.

### 1.2.1 Sensitivity and dynamic range of RF receivers

Two of the main performance metrics of a RF receiver are the noise performance and linearity. There are several metrics set by each communication standard that

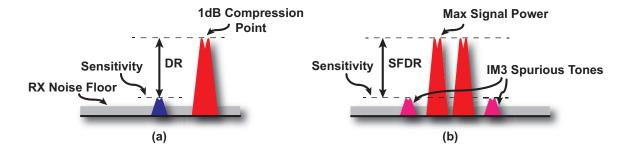

**Figure 1.2.** Illustration of (a) dynamic range definition and (b) spurious free dynamic range (SFDR) definition [15].

define the required performance of a receiver. These metric specifications are derived based on several factors such as neighboring channels, self interference and modulation scheme. Two of the general specifications that are used to quantify the desired receiver performance are dynamic range and sensitivity.

Sensitivity can be defined as the lowest signal power that can be received with the desired signal-to-noise-ratio [15]. For a system operating at room temperature (300 K) and connected to a 50  $\Omega$  antenna, the sensitivity ( $S_n$ ) in dBm can be written as

$$S_{\rm n}(dBm) = -174({\rm dBm/Hz}) + NF(dB) + SNR(dB) + 10\log_{10}(BW)(dBHz), (1.2)$$

where -174 dBm/Hz is the noise floor due to the receiver thermal noise, NF is the noise figure of the receiver in dB, SNR is the desired signal to noise ratio in dB desired for a particular modulation and coding scheme, and BW is the bandwidth of the receiver in Hz.

Simply put, the dynamic range is defined as the difference between the power of the largest input signal that can be received with tolerable distortion and the sensitivity level. There are two definitions of dynamic range that are typically used in RF designs. The first one is simply called the dynamic range (DR) which is the difference between the 1 dB compression point and the sensitivity level (as illustrated

in Fig. 1.2(a)). The second one is called the spurious-free-dynamic-range (SFDR) and is defined as the difference between sensitivity level and the power of the largest input signal that can be received before any spurious tones due to non-linearity raise above the sensitivity level (as illustrated in Fig. 1.2(b)). Throughout this document the latter definition is used for SFDR.

Depending on the communication standard used, specifications for these metrics may become challenging to meet for wideband receivers with no upfront filtering. For instance the GSM standard requires the receiver to withstand a 0 dBm blocker at 20 MHz offset while maintaining -99 dBm sensitivity level at 200 kHz bandwidth [16]. This requires the receiver to achieve a dynamic range of close to 100 dB. Traditional devices, such as the one showed in Fig. 1.1, employed the rejection provided by offchip filters (duplexers) to relax this requirement. For every dB of blocker rejection provided by the filter, the dynamic range requirement on the receiver chain is relaxed by 1 dB. However, for a wideband receiver system that does not incorporate any offchip filtering the full dynamic range requirement should be met. This has been the topic of significant research in recent years and many different approaches have been developed and demonstrated to address this issue. Next, some of these approaches are introduced and reviewed.

# 1.2.2 Methods for Implementing High Dynamic Range Wideband Receivers

Efforts to address the issue of large required dynamic range of receivers can be generally divided into two categories. The first is to focus on mimicking the filter response of off-chip components with on-chip filtering techniques. Second is to develop new techniques to enhance the dynamic range of wideband receivers to meet the stringent requirements.

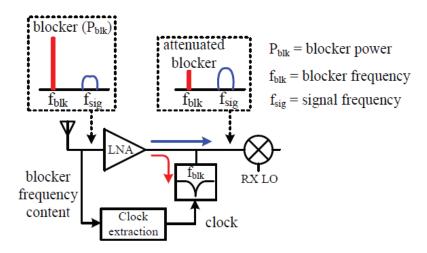

**Figure 1.3.** An example of a blocker filtering scheme that incorporates the power of a large blocker to tune a notch filter for providing rejection. Reproduced from [17] ©IEEE 2016.

The first approach mainly focuses on developing programmable filtering in order to relax the required dynamic range due to out-of-band blockers by creating narroband responses [11,16–25]. An example of such systems is shown in Fig. 1.3. These approaches have been proved highly effective in achieving similar levels of out-of-band rejection to those of traditional receivers. However, they are only effective for signals with small fractional instantaneous bandwidth with all having fractional bandwidths less 15% and mostly less than 1%. This is due to the inherent narrowband response created by the filtering implemented in these receivers. Although these techniques address some of the new applications such as carrier aggregation where narrowband signals are used with programmable center frequencies, they fail to address the need for high data rate communications where signal bandwidths of greater that 100 MHz are required.

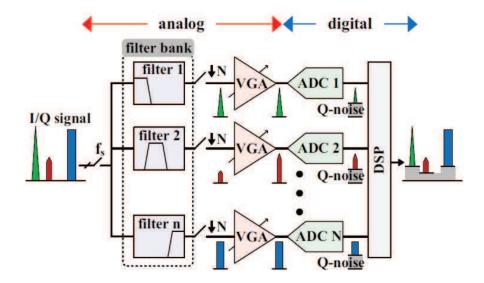

The second approach has focused on enhancing the in-band dynamic range of receivers through different techniques to avoid narrow-band responses and accommodate wide-instantaneous bandwidths [5, 26, 27]. The block diagram of an example of such receivers is shown in Fig. 1.4. One of the challenges that these approaches face, other

**Figure 1.4.** An example of a wideband receiver where polyphase filtering is used for channelizing RF band. Reproduced from [26] ©IEEE 2017.

than large dynamic range, is the high speed analog-to-digital converter required for sampling at such high rates. In the system shown in Fig.1.4, the requirement on ADC performance is realized by downsampling the signal at each channel. While a simple high-speed ADC could be potentially used for direct sampling of the RF signal, it has been proven difficult to achieve the required DR at reasonable power consumption [26]. Next, some examples of techniques implemented for both approaches are discussed.

# 1.3 State-Of-The-Art High Dynamic Range Wideband Receivers

In this section a review of current state-of-the-art high dynamic range receivers is presented. Several techniques have been demonstrated to enhance the linearity of individual blocks in the receiver chain such as LNA and mixer but the focus of this section is on the system level approaches proposed to enhance the overall dynamic range. Some of these techniques include passive mixer first [28], N-path filters [11,16,

Figure 1.5. Schematic diagram of the multiphase passive mixer phase receiver for low power and high linearity applications. Reproduced from [28] ©IEEE 2013.

21,25],  $\Delta-\Sigma$  techniques [18], blocker detection [5,17,24,29,30], RF channelization [26] and RF sampling ADCs [31]. Some of these techniques will be discussed here.

• Mixer first receivers— Traditionally, low noise amplifiers (LNA) have been used as the first block of the receiver chain to provide sufficient gain and low noise performance. However, recent advancements in CMOS technology have enabled the use of passive mixers connected directly to the antenna. One advantage of this approach is the high linearity and wideband operation of these devices [28]. An example of a passive mixer first receiver is the work reported in [28], where a multiphase local oscillator (LO) is used to achieve low noise and sufficient out-of-band linearity. The block diagram of the receiver is shown in Fig. 1.5. The multiphase LO is mainly used to implement harmonic rejection mixing (HRM) which allows for rejection of LO harmonics by correctly weighting different LO phases. This is crucial since any blocker signal at harmonics of the LO would be downconverted to the same baseband frequency [28, 32, 33].

**Figure 1.6.** Example of N-path filters used to implement (a) bandpass response and (b) notch response. Reproduced from [16] ©IEEE 2014.

- N-path filters— One of the most promising approaches to mimic the filtering response of off-chip filters is the use of N-path filters [34]. These filters usually employ multiple parallel branches of switched-capacitor combinations that are controlled with non-overlapping clocks. The passband shape is set by the number of phases and the center frequency of the filter can be tuned effectively without degrading the Q [35]. Fig. 1.3 shows simple N-path filters used to create bandpass and notch filters. As reported in [35] these filters can achieve out-of-band rejections of up to 60 dB. As a result there has been significant research devoted to the use of these filters for eliminating the need of off-chip filters. However these architectures fail to address the need for wide instantaneous bandwidth and the challenge of high in-band linearity.

- Blocker detection and rejection—Another approach that has been proven effective, is to employ the knowledge of a blocker to effectively reject it. In [5,17] the blocker signal is detected through an auxiliary path and then used to tune an N-path notch filter and reject the blocker at the output of the LNA. An

**Figure 1.7.** System diagram of a wideband compressive sensing based receiver with blocker rejection. Reproduced from [29] ©IEEE 2017.

innovative approach is presented in [30], where an auxiliary path parallel to the main RX path is implented with lower gain to enable detection of any possible nonlinearity. If any nonlinearity is detected, this information is used in digital domain to linearize the signal received from the main path. In [24, 29] compressive sensing techniques are used for detection of any large blockers across the band and then digital techniques such as sequence design and LO modulation are used to reject the band where blocker exists(as demonstrated in Fig. 1.7). These methods have been able to achieve large instantaneous bandwidths of up to 1 GHz. However, they are limited in the number of blockers and their bandwidth.

• RF channelization— An approach presented in [26] employs polyphase FFT filtering to create bandpass filter responses and hence channelize the entire frequency band. The operation principle of the PFFT is demonstrated in Fig. 1.8.

**Figure 1.8.** Operating principle of the polyphase-FFT. Reproduced from [26] ©IEEE 2017.

In this work a four channel implementation is used which divides the entire spectrum into four effective bands. While this implementation achieves large in-band linearity for each band, the noise performance of the system is high which is due to the complete passive implementation of the system. In addition, any in-band blockers pass through the system and can compress the corresponding channel.

• RF Sampling ADCs—As discussed previously, direct sampling of RF signals with an ADC and achieving the required DR has proved to be power inefficient. However, techniques such as time-interleaving have helped achieving higher effective data rates while employing ADCs with lower sampling frequencies [36]. While these ADCs can achieve data rates of higher than 12 GS/s [37], their low effective number of bits (ENOB) limits their use as a direct RF sampling receiver. As an instance the work reported in [37] achieves a 5-bit resolution which corresponds to an effective noise figure of approximately 46 dB. This is much higher than the requirement for most wireless standard which usually require the receiver noise figure to be less than 10 dB. An alternative approach is to use a broadband LNA prior to the ADC to enhance the sensitivity of the overall

**Table 1.2.** Example of wideband receivers with no off-chip filtering

| Reference | Technique                 | Wide/Narrow<br>Inst. BW | In/Out-of-Band<br>Linearity | Maximum No. of<br>Blockers rejected |

|-----------|---------------------------|-------------------------|-----------------------------|-------------------------------------|

| [28]      | Mixer first               | NB                      | OB                          | unlimited                           |

| [32]      | Mixer first               | NB                      | OB                          | unlimited                           |

| [35]      | Active N-path filter      | NB                      | OB                          | unlimited                           |

| [25]      | Passive N-path filter     | NB                      | OB                          | unlimited                           |

| [16]      | Passive N-path filter     | NB                      | OB                          | unlimited                           |

| [11]      | Active N-path filter      | NB                      | OB                          | unlimited                           |

| [17]      | Blocker detect+N-path     | WB                      | OB                          | limited                             |

| [5]       | Blocker detect+N-path     | WB                      | OB                          | limited                             |

| [30]      | Blocker detect+dig. proc. | NB                      | IB                          | unlimited                           |

| [29]      | Blocker detect+ CS.       | WB                      | IB                          | limited                             |

| [24]      | Blocker detect+CS         | WB                      | IB                          | limited                             |

| [26]      | RF Channelization         | WB                      | OB                          | unlimited                           |

| [31]      | WB LNA+ RF ADC            | WB                      | IB                          | unlimited                           |

receiver as presented in [31]. In this work a BiCMOS wideband LNA is used in front of a CMOS 2.7 GS/s ADC. While achieving good SFDR performance the use of two separate integrated circuits implemented in different technologies makes this approach unsuitable for highly integrated devices.

Table 1.2 presents example of state-of-the-art wideband receivers with no off-chip filtering along with the main technique used, the effective instantaneous bandwidth, high in-band or out-of-band linearity, and the fundamental number of blockers that can be rejected. It can be seen that very few efforts have addressed the need for high in-band linearity for wide instantaneous bandwidth receivers with presence of multiple blockers.

Based on the discussion presented here the need for new receiver architectures that enable wider instantaneous bandwidths and better in-band blocker tolerance is evident. In this dissertation a new analog technique will be introduced which focuses on achieving wide instantaneous bandwidth along with high in-band linearity.

## 1.4 Contributions of this Work

The work reported in this dissertation provides several contributions to the field of radio frequency integrated circuits. These contributions include:

- Introduction of a new technique that combines the benefits of mixer first receivers with library of pseudo random binary sequences to enhance linearity of wideband RF receivers. A detailed analysis on the effect of the proposed technique on system noise and linearity performance is presented to highlight the effectiveness of the proposed method. In addition, the effect of systematic errors due to non-ideal implementation on system performance are discussed and evaluated.

- To evaluate the effectiveness of the proposed technique a CMOS integrated circuit implementation of the system is presented. The design procedure for passive mixers, switched-capacitor block, and baseband amplifiers required for system implementation are each discussed in detail. A custom built data collection system is use for measurements of the fabricated IC. In addition, calibration techniques are introduced to enhance the overall performance of the implemented systems. Circuit implementation of the proposed calibration schemes are presented. Some of the techniques are implemented on-chip and evaluated through measurement results.

The work reported in this dissertation has resulted in a filed US patent for the original idea and a peer reviewed journal paper that presents the main idea along with measurement results of the implemented IC [38].

List of publications during the PhD studies:

• S. Pi, M. Ghadiri-Sadrabadi, J.C. Bardin, and Q. Xia, Nanoscale memristive radiofrequency switches. Nature Communications 6, 7519 (2015).

- S. Pi, M. Ghadiri-Sadrabadi, J. C. Bardin, and Q. Xia, "Memristors as radiofrequency switches," 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, 2016, pp. 377-380.

- M. Ghadiri-Sadrabadi and J. C. Bardin, "A Discrete-Time RF Signal-Processing

Technique for Blocker-Tolerant Receivers With Wide Instantaneous Bandwidth,"

in IEEE Transactions on Circuits and Systems I: Regular Papers. doi: 10.1109/TCSI.2018.2842

## CHAPTER 2

## THE PROPOSED DISCRETE-TIME TECHNIQUE

In this chapter, a novel RF discrete-time signal-processing technique for linearity enhancement of wideband RF receivers is introduced. A multi-channel receiver architecture is presented to implement the proposed technique. Fundamentals of system operation are discussed in both time and frequency domain. In this technique, linearity advantages of mixer first architectures are combined with properties of pseudo-random binary sequences as local oscillator signals to achieve high linearity. A matrix representation is introduced to simplify the understanding of the system operation. In addition, analytical and numerical approaches are used for the analysis of linearity and noise performance of the overall system.

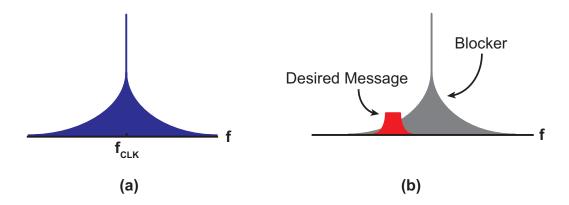

## 2.1 Discrete-Time Signal-Processing Technique

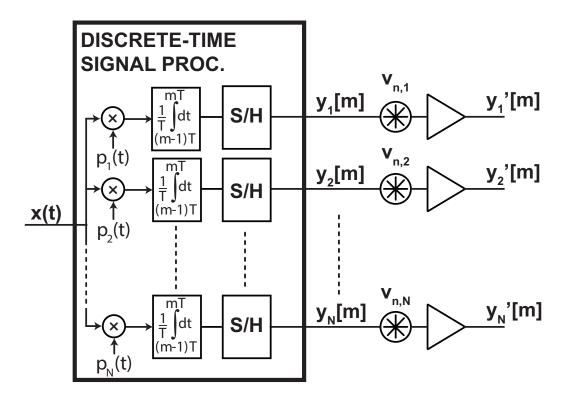

A top level block diagram of the proposed architecture is shown in Fig. 2.1(a). A multi-channel system is used where each channel multiplies the RF input signal (x(t)) with a shifted version of a pseudo-random-bit-sequence (PRBS)  $(P_i)$ . A review of PRBS properties is presented in Appendix A. The resulting signal is then averaged over a full period of the PRBS and then sampled, generating  $y_i[m]$ . These samples are updated after each period of the PRBS which results in  $y_i$  signals to be N times slower than the rate of PRBS signals. This, effectively decimates the input signal rate to a lower frequency of  $f_{\rm BB} = f_{\rm s/N}$ . Fig. 2.1(b)-(d) shows the time domain signals at different stages of the system for an example input signal. The lower speed of

Figure 2.1. (a) Schematic diagram of the proposed discrete-time signal-processing technique along with the digital signal processing block required for collection of samples and reconstruction of the sampled input signal. Example of a signal at (b) input, (c) baseband channels output, and (d) reconstructed output. Reproduced from [38]©IEEE 2018

the baseband signals  $(y_i)$  compared to that of the input signal (x(t)) can be seen in Fig. 2.1(c).

The reduction of bandwidth at each channel causes the full RF spectrum to fold back to only a fraction of the bandwidth. This would violate the Nyquist criteria and can result in corruption and loss of data as demonstrated in Fig. 2.2. This is due to the fact that each N set of RF samples result in only one baseband sample at each channel. As a result, for the full reconstruction of the input signal, N separate channels are required that each provide a unique data sample at baseband. This can be achieved by employing sufficiently uncorrelated signals multiplied with RF input signal at each channel. Such signals can form a vector basis for the projection of the input signal [39].

Figure 2.2. Spectrum folding due to sub-sampling of the input signal and reduced bandwidth at each baseband output

As discussed in the Appendix A, shifted versions of the same PRBS are approximately orthogonal to each other. This implies that the multiplication of the input signal with each shifted version of the PRBS provides unique baseband samples at each channel. This property along with the simplicity of PRBS implementation on an integrated circuit is the main motivation for employing these signals in the proposed architecture of Fig. 2.1(a).

The minimal correlation between the generated baseband samples enables close to full reconstruction of the input signal from those. As such, a means of signal processing is required after baseband to enable such reconstruction by the use of these samples. This is performed in digital domain as shown in Fig. 2.1(a) and will be discussed in detail in the next section.

The multiplication of the input signal with a PRBS results in a set of noise-like samples over one period of the sequence. During the integration process, these noise-like samples add in power domain. Hence, the averaging process reduces the average voltage at baseband by a factor of  $\approx 1/\sqrt{N}$ . If  $p_{\rm i}$  signals were true random signals, these samples would be fully uncorrelated and the average amplitude reduction would be exactly  $1/\sqrt{N}$ . However, since the PRBS basis used in the proposed system is not fully orthogonal, on average, the reduction in baseband amplitudes is expected to be slightly less than 1/sqrtN.

The proposed architecture in Fig.2.1 provides several advantages in the implementation of the receiver system. First, the RF section of the receiver can be implemented using all passive circuits which generally provide better linearity performance and consume less power compared to their active counterparts. In addition, the active part of the circuit can be moved to the baseband where higher linearity can be achieved with less power consumption. Second, the reduction of signal amplitude at baseband relaxes the linearity requirement of each baseband circuit by  $\approx 10 \log_{10}(N)$ . Both of these advantages suggest that significant linearity enhancement can be achieved through the proposed architecture.

In the next section, a matrix representation of the architecture proposed in Fig. 2.1 will be introduced. This will simplify the understanding of the operational principle of the system.

#### 2.1.1 Matrix Representation

Over a single frame of operation<sup>1</sup>, the full system can be modeled as

$$\mathbf{y} = \mathbf{P}\mathbf{x},\tag{2.1}$$

where  $\mathbf{P}$  is a normalized  $N \times N$  PRBS matrix as defined in Appendix A,  $\mathbf{x}$  is the vector of N RF samples and  $\mathbf{y}$  is the vector of corresponding baseband samples at channel outputs. Each row of the matrix corresponds to the  $\mathbf{p}_i$  at each channel in Fig. 2.1. Therefore, each row of the  $\mathbf{P}$  is a shifted version of a normalized PRBS and the matrix possesses all properties of the PRBS matrix as discussed in the Appendix A. An example of such a matrix for a seven channel system employing seven-bit PRBSs can be given as

$<sup>^{1}\</sup>mathrm{Each}$  frame is the set of N RF samples that result in one baseband sample at each channel at each output

$$P = \begin{bmatrix} -0.14 & -0.14 & -0.14 & 0.14 & 0.14 & -0.14 & 0.14 \\ 0.14 & -0.14 & -0.14 & -0.14 & 0.14 & 1 & -1 \\ -0.14 & 0.14 & -0.14 & -0.14 & -0.14 & 0.14 & 0.14 \\ 0.14 & -0.14 & 0.14 & -0.14 & -0.14 & -0.14 & 0.14 \\ 0.14 & 0.14 & -0.14 & 0.14 & -0.14 & -0.14 & -0.14 \\ -0.14 & 0.14 & 0.14 & -0.14 & 0.14 & -0.14 & -0.14 \\ -0.14 & -0.14 & 0.14 & 0.14 & -0.14 & 0.14 & -0.14 \end{bmatrix}.$$

(2.2)

Properties of such matrices have been studied in depth in [40].

#### 2.1.2 Signal Reconstruction

From (2.1) it is clear that the reconstruction of the sampled input signal  $(\mathbf{x})$  can be carried out by

$$\hat{\mathbf{x}} = \mathbf{P}^{-1}\mathbf{y}.\tag{2.3}$$