#### University of Massachusetts Amherst

### ScholarWorks@UMass Amherst

**Doctoral Dissertations**

Dissertations and Theses

November 2017

# Formal Analysis of Arithmetic Circuits using Computer Algebra -Verification, Abstraction and Reverse Engineering

**CUNXI YU** ECE, University of Massachusetts Amherst

Follow this and additional works at: https://scholarworks.umass.edu/dissertations\_2

Part of the Computer Engineering Commons, and the VLSI and Circuits, Embedded and Hardware

**Systems Commons**

#### **Recommended Citation**

YU, CUNXI, "Formal Analysis of Arithmetic Circuits using Computer Algebra - Verification, Abstraction and Reverse Engineering" (2017). Doctoral Dissertations. 1142.

https://scholarworks.umass.edu/dissertations\_2/1142

This Open Access Dissertation is brought to you for free and open access by the Dissertations and Theses at ScholarWorks@UMass Amherst. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

# FORMAL ANALYSIS OF ARITHMETIC CIRCUITS USING COMPUTER ALGEBRA

- VERIFICATION, ABSTRACTION AND REVERSE ENGINEERING

A Dissertation Presented

by

CUNXI YU

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

September 2017

Electrical and Computer Engineering

© Copyright by Cunxi Yu 2017 All Rights Reserved

# FORMAL ANALYSIS OF ARITHMETIC CIRCUITS USING COMPUTER ALGEBRA

### - VERIFICATION, ABSTRACTION AND REVERSE ENGINEERING

A Dissertation Presented by CUNXI YU

| Approved as to style and content by: |                                        |  |

|--------------------------------------|----------------------------------------|--|

|                                      |                                        |  |

| Maciej Ciesielski, Chair             |                                        |  |

|                                      |                                        |  |

| George S. Avrunin, Member            |                                        |  |

|                                      |                                        |  |

| Daniel Holcomb, Member               |                                        |  |

|                                      |                                        |  |

| Sandip Kundu, Member                 |                                        |  |

|                                      |                                        |  |

|                                      | Christopher V. Hollot, Department Head |  |

Electrical and Computer Engineering

#### **ABSTRACT**

# FORMAL ANALYSIS OF ARITHMETIC CIRCUITS USING COMPUTER ALGEBRA

- VERIFICATION, ABSTRACTION AND REVERSE ENGINEERING

#### SEPTEMBER 2017

#### CUNXI YU

B.Sc., ZHEJIANG UNIVERSITY CITY COLLEGE

Ph.D., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Maciej Ciesielski

Despite a considerable progress in verification and abstraction of random and control logic, advances in formal verification of arithmetic designs have been lagging. This can be attributed mostly to the difficulty in an efficient modeling of arithmetic circuits and datapaths without resorting to computationally expensive Boolean methods, such as Binary Decision Diagrams (BDDs) and Boolean Satisfiability (SAT), that require, bit-blasting, i.e., flattening the design to a bit-level netlist. Approaches that rely on computer algebra and Satisfiability Modulo Theories (SMT) methods are either too abstract to handle the bit-level nature of arithmetic designs or require solving computationally expensive decision or satisfiability problems.

The work proposed in this thesis aims at overcoming the limitations of analyzing arithmetic circuits, specifically at the post-synthesized phase. It addresses the verification, abstraction and reverse engineering problems of arithmetic circuits at

iv

an algebraic level, treating an arithmetic circuit and its specification as a properly constructed algebraic system. The proposed technique solves these problems by function extraction, i.e., by deriving arithmetic function computed by the circuit from its low-level circuit implementation using computer algebraic rewriting technique. The proposed techniques work on large integer arithmetic circuits and finite field arithmetic circuits, up to 512-bit wide containing millions of logic gates.

## TABLE OF CONTENTS

|              |                          |                                                    | $\mathbf{P}_{i}$                                                                                                        | age           |

|--------------|--------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------|

| $\mathbf{A}$ | BST:                     | RACT                                               | -<br>-                                                                                                                  | . <b>iv</b>   |

| LI           | ST (                     | OF TA                                              | ABLES                                                                                                                   | . x           |

|              |                          |                                                    |                                                                                                                         |               |

| LI           | ST (                     | OF FIG                                             | GURES                                                                                                                   | xii           |

| Cl           | HAP                      | TER                                                |                                                                                                                         |               |

| 1.           | INT                      | rod'                                               | UCTION                                                                                                                  | . 1           |

|              | 1.1<br>1.2               |                                                    | ware Verification                                                                                                       |               |

|              |                          | 1.2.1<br>1.2.2<br>1.2.3<br>1.2.4<br>1.2.5<br>1.2.6 | Equivalence Checking  Model Checking  Theorem Proving  Symbolic Simulation  Reverse Engineering  Overview of the thesis | 8<br>9<br>.10 |

| 2.           | BA                       | CKGF                                               | ROUND                                                                                                                   | 13            |

|              | 2.1<br>2.2<br>2.3<br>2.4 | SAT a                                              | nical Diagrams and SMT solvers tural Minimization outer Algebra Approaches                                              | . 14          |

| 3.           |                          | _                                                  | L VERIFICATION OF INTEGER ARITHMETIC UITS USING FUNCTION EXTRACTION                                                     | 25            |

|              | 3.1<br>3.2               |                                                    | duction                                                                                                                 |               |

|              |                          | 3.2.1<br>3.2.2                                     | Algebraic Model                                                                                                         |               |

|    |                                              | 3.2.3<br>3.2.4                                                                    |                                                                                                   | es of Computed Input Signature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                         |

|----|----------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|    | 3.3                                          | Exper                                                                             | imental R                                                                                         | tesults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 41                      |

|    |                                              | 3.3.1                                                                             | Compari                                                                                           | ison with SAT and SMT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 41                      |

|    |                                              |                                                                                   | 3.3.1.1<br>3.3.1.2                                                                                | SAT comparison:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |

|    |                                              | 3.3.2                                                                             | Limitati                                                                                          | ons and Proposed Solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45                      |

|    |                                              |                                                                                   | 3.3.2.1<br>3.3.2.2<br>3.3.2.3                                                                     | Circuit Boundaries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 46                      |

|    | 3.4                                          | Verific                                                                           | cation of I                                                                                       | Datapaths - A Case Study                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 47                      |

|    |                                              | 3.4.1<br>3.4.2<br>3.4.3                                                           | Bit-level                                                                                         | vel Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54                      |

|    | 3.5                                          | Concl                                                                             | usions                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56                      |

|    | 0.0                                          |                                                                                   |                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |

| 4. | CO                                           |                                                                                   |                                                                                                   | GEBRA BASED VERIFICATION WITH POLYNOMIALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 59                      |

| 4. | CO                                           | REDU<br>Introd<br>Previo                                                          | NDANT<br>uction<br>ous Work                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59                      |

| 4. | 4.1<br>4.2                                   | REDU<br>Introd<br>Previo                                                          | NDANT Auction bus Work hinaries Vanishin                                                          | POLYNOMIALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 59<br>60<br>61          |

| 4. | 4.1<br>4.2                                   | Introd<br>Previo<br>Prelin<br>4.3.1<br>4.3.2                                      | NDANT auction ous Work ninaries Vanishin Don't-ca                                                 | r POLYNOMIALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 59<br>61<br>63          |

| 4. | 4.1<br>4.2<br>4.3                            | Introd<br>Previo<br>Prelin<br>4.3.1<br>4.3.2                                      | NDANT Auction bus Work hinaries Vanishin Don't-ca ntial Verif                                     | re Polynomials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 59<br>61<br>63<br>65    |

| 4. | 4.1<br>4.2<br>4.3                            | Introd<br>Previo<br>Prelin<br>4.3.1<br>4.3.2<br>Seque<br>4.4.1<br>4.4.2<br>Exper  | NDANT Auction bus Work hinaries Vanishin Don't-ca ntial Verif Multiply Serial So imental R        | POLYNOMIALS  In Polynomials  I | 59 61 63 65 67 67 69    |

|    | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>AD | Introde Previous Previous Prelim 4.3.1 4.3.2 Seque 4.4.1 4.4.2 Exper Conclus VANC | NDANT Auction bus Work hinaries Vanishin Don't-ca htial Verif Multiply Serial Sc imental R usions | POLYNOMIALS  In Polynomials  I | 59 61 63 65 67 67 67 67 |

|    |                   | 5.2.1<br>5.2.2          | Boolean Network                                         |     |

|----|-------------------|-------------------------|---------------------------------------------------------|-----|

|    | 5.3               | Appro                   | oach                                                    | 79  |

|    |                   | 5.3.1<br>5.3.2          | Outline of the Approach                                 |     |

|    | 5.4<br>5.5        |                         | usion                                                   |     |

| 6. |                   |                         | AIC SPECTRUM - A NEW CANONICAL ESENTATION OF ARITHMETIC | 87  |

|    | 6.1<br>6.2<br>6.3 | Relate                  | luctioned Work                                          | 89  |

|    |                   | 6.3.1<br>6.3.2<br>6.3.3 | Uniqueness of Algebraic Spectrum                        | 97  |

|    | 6.4<br>6.5<br>6.6 | Result                  | omial-Time Spectrum Extraction                          | 104 |

| 7. |                   |                         | ANALYSIS OF FINITE FIELD ARITHMETIC                     | 107 |

|    | 7.1<br>7.2        |                         | luctionround                                            |     |

|    |                   | 7.2.1<br>7.2.2          | Galois Field Multiplication                             |     |

|    | 7.3               | Parall                  | el Extraction in Galois Field                           | 112 |

|    |                   | 7.3.1<br>7.3.2<br>7.3.3 | Computer Algebraic model                                | 113 |

|    | 7.4               | Revers                  | se Engineering in Galois Field                          | 120 |

|    |                   | 7.4.1<br>7.4.2<br>7.4.3 | Output encoding determination                           | 122 |

| 7.5   | Result | ts       |                                               |

|-------|--------|----------|-----------------------------------------------|

|       | 7.5.1  | Parallel | Verification of $GF(2^m)$ Multipliers         |

|       |        |          | Design and Verification cost depend on $P(x)$ |

|       | 7.5.2  | Reverse  | Engineering of $GF(2^m)$ Multipliers          |

| 7.6   | Concl  | usion    |                                               |

| BIBLI | OGR.A  | APHY     |                                               |

# LIST OF TABLES

| Table | Page                                                                                                                                                                                                                                               |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1   | 2-bit multiplier intermedia expression size of two substitution sequence                                                                                                                                                                           |

| 3.2   | $N_1, N_2$ are the numbers of nodes before and after $fraig - v$ in $ABC$ ; $N_3, N_4$ are the numbers of clauses before and after simplification by [12]                                                                                          |

| 3.3   | CPU time and memory results of 256-bit (Operands $A$ and $B$ ) arithmetic circuits. (TO = timeout after 3600 sec; MO = memory out of 8 GB)                                                                                                         |

| 3.4   | Results for a synthesized multiplier; comparison with [32], SAT, SMT, and commercial tools (TO = timeout after 3600 sec; UD = undecided; MO = memory out of 8 GB). *ABC was unable to synthesize the 512-bit CSA multiplier due to memory limit 45 |

| 3.5   | CPU time and memory results using TDS and Function Extraction                                                                                                                                                                                      |

| 4.1   | Verification results for GF(2 <sup>256</sup> ) Adder, MAC, and Add-shift Multipliers71                                                                                                                                                             |

| 4.2   | Effect of Vanishing and Don't Care Polynomials for MAC (MO = Memory out of 8 GB)                                                                                                                                                                   |

| 4.3   | Effect of Vanishing and Don't Care Polynomials for Serial Squarer (MO = Memory out of 8 GB)                                                                                                                                                        |

| 4.4   | Sequential Squarer results: comparison with SAT and SMT (TO = Time_out after 3600 sec)                                                                                                                                                             |

| 5.1   | Results of applying AIG-based algebraic rewriting to pre- and post-synthesized CSA multipliers compared to functional extraction presented in Chapter 3. *t(s) is the runtime in seconds.  *mem is the memory usage in mb                          |

| 5.2 | Results of applying AIG-based algebraic rewriting to post-synthesized complex arithmetic circuits compared to functional extraction presented in Chapter 3. *MO = Memory out of 8 GB85                                        |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.1 | Results of extracting the specification of pre- and post-synthesized CSA multipliers compared to functional extraction presented in [31]. $*t(s)$ is the runtime in seconds. $*mem$ is the memory usage in mb                 |

| 6.2 | Results of extracting the specification of the post-synthesized complex arithmetic circuits compared to functional extraction presented in [31]. $*MO = $ Memory out of 8 GB                                                  |

| 6.3 | Runtime of extracting the specification of the radix-4 Booth multiplier. $*MO = $ Memory out of 8GB                                                                                                                           |

| 6.4 | Evaluation of word-level abstraction using algebraic spectrum. Multiplications in $F_1$ and $F_2$ are implemented using CSA-multiplier. $F_3$ uses radix-4 Booth-multiplier                                                   |

| 7.1 | Results of verifying Mastrovito multipliers using our parallel approach. $T$ is the number of threads. $MO$ =Memory out of 32 GB. $TO$ =Time out of 12 hours. (* $T$ =1 shows the maximum memory usage of a single thread.)   |

| 7.2 | Results of verifying $Montgomery$ multipliers using our parallel approach. $T$ is the number of threads. $TO$ =Time out of 12 hours. $MO$ =Memory out of 32 GB. (* $T$ =1 shows the maximum memory usage of a single thread.) |

| 7.3 | Runtime and memory usage of synthesized $Mastrovito$ and $Montgomery$ multipliers $(T=20)$                                                                                                                                    |

| 7.4 | Results of reverse engineering synthesized and technology mapped  Mastrovito and Montgomery multipliers  133                                                                                                                  |

## LIST OF FIGURES

| re Pa                                                                                                                                                                                                                             | igure | Page |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|

| 1 Typical industrial IC design flow                                                                                                                                                                                               | 1.1   | 3    |

| 2 Combinational equivalence checking model                                                                                                                                                                                        | 1.2   | 5    |

| 3 Sequential equivalence checking model                                                                                                                                                                                           | 1.3   | 6    |

| A gate-level circuit implementing 2-input AND function with inputs $a$ and $b$                                                                                                                                                    | 1.4   |      |

| 5 Proving the function of output z in Figure 1.4 is AND(a,b) using theorem proving                                                                                                                                                | 1.5   | 10   |

| Canonical diagrams - Ordered Binary Decision Diagrams (OBDD); a) Gate-level design with output z; b) Gate-level design with output z'. c) The truth table of z and z'; d) BDDs of z and z' are identical with same variable order | 2.1   | it   |

| 2 Reduced ordered binary decision diagrams of 4-bit multiplication                                                                                                                                                                | 2.2   | 15   |

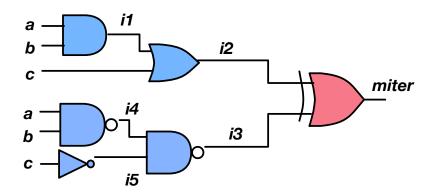

| 3 Example of equivalence checking using SAT solver using a Boolean miter                                                                                                                                                          | 2.3   | 16   |

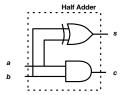

| 4 Half adder design with input $a$ and $b$ . $s$ is the sum function and $c$ is the carry function                                                                                                                                | 2.4   |      |

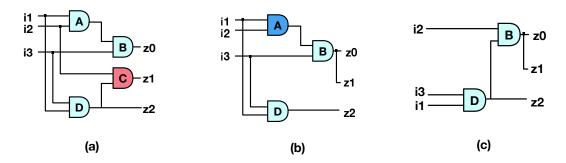

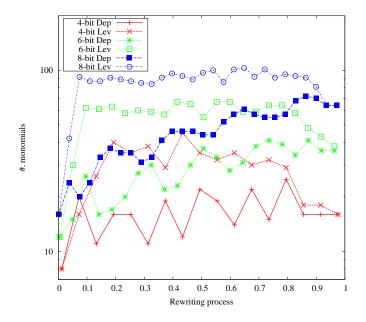

| 5 Example of logic minimization. a) Original circuit; b) Circuit with gates B and C are merged; c) Circuit with gates A and D are merged                                                                                          | 2.5   | 19   |

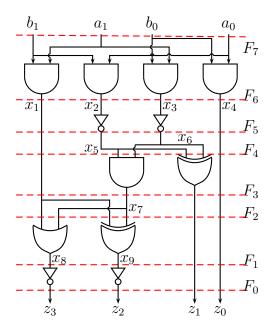

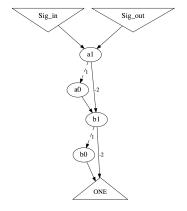

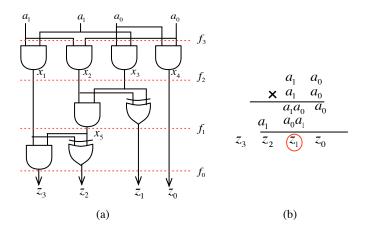

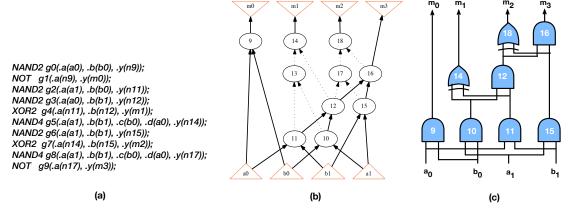

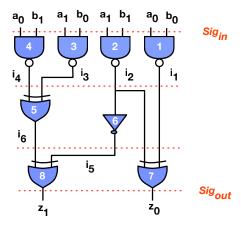

| 1 Verifying a 2-bit signed multiplier: Gate-level circuit with output signature $Sig_{out} = -8z_3 + 4z_2 + 2z_1 + z_0$                                                                                                           | 3.1   | 28   |

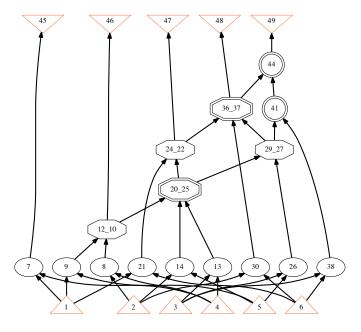

| 2 Two substitution orders for an unsigned 2-bit multiplier                                                                                                                                                                        | 3.2   | 30   |

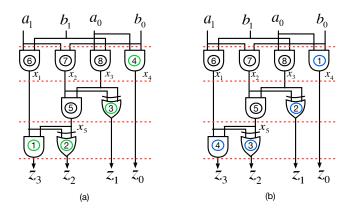

| 3 Substitution order analysis using 4-bit, 6-bit, and 8-bit multiplier.  *Dep is dependency; Lev is levelization                                                                                                                  | 3.3   | 32   |

| 3.4  | Parallel prefix adder, hybrid model                                                                                                                                         |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

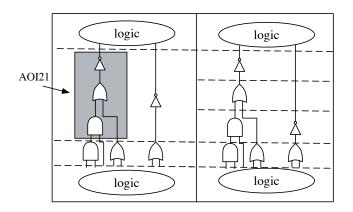

| 3.5  | Expanding complex gates for cut rewriting                                                                                                                                   |

| 3.6  | Proof that $x_5x_8$ evaluates to 0 using both, the computer algebraic and Boolean methods                                                                                   |

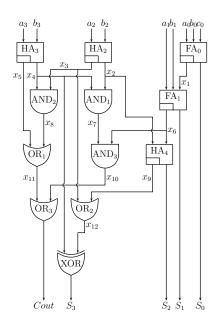

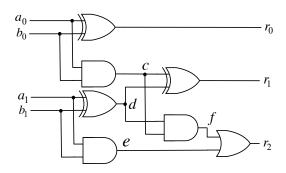

| 3.7  | 2-bit gate-level adder. $R = r_0 + 2r_1 + 4r_2$ , $A = a_0 + 2a_1$ , $B = b_0 + b_1$ . $R = A + B$                                                                          |

| 3.8  | Arithmetic function of a 2-bit multiplier extracted from the circuit using TED in normal factored form: $Sig_{in} = (-2a_1 + a_0)(-2b_1 + b_0).$                            |

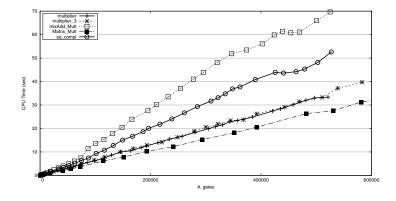

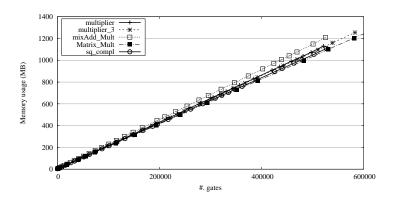

| 3.9  | Verifying combinational arithmetic circuits: CPU time                                                                                                                       |

| 3.10 | Verifying combinational arithmetic circuits: Memory usage 45                                                                                                                |

| 3.11 | Comparing rewriting of the expression $Sig_{out}$ vs individual output bits for a 4-bit multiplier                                                                          |

| 3.12 | Synthesis impacts on function extraction                                                                                                                                    |

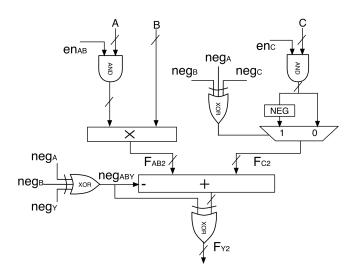

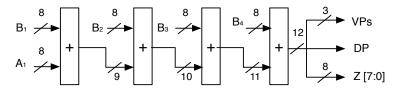

| 3.13 | Integer ALU - initial RTL design                                                                                                                                            |

| 3.14 | Integer ALU - final RTL design                                                                                                                                              |

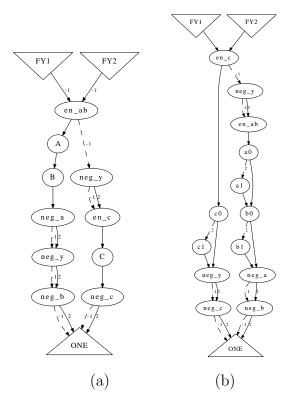

| 3.15 | TED representation: (a) word-level model; (b) bit-level model 52                                                                                                            |

| 3.16 | Modeling of the word-level XOR                                                                                                                                              |

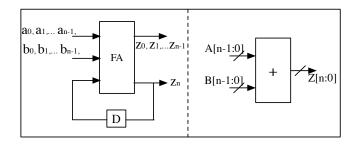

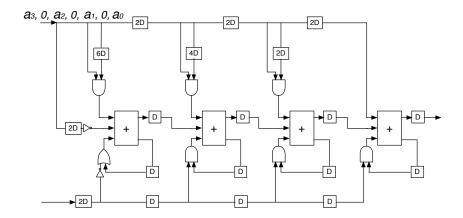

| 4.1  | Sequential <i>n</i> -bit adder, $Z = A + B$                                                                                                                                 |

| 4.2  | 2-bit combinational squarer circuit. a) Gate-level netlist; b) arithmetic squaring structure                                                                                |

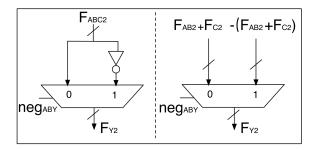

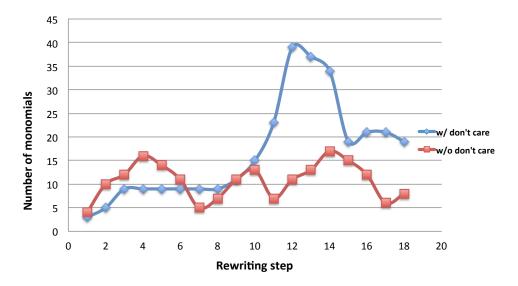

| 4.3  | Compare the size of internal expressions with, without $don't$ care polynomial $x_3$                                                                                        |

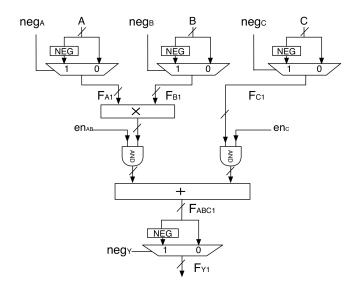

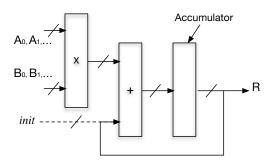

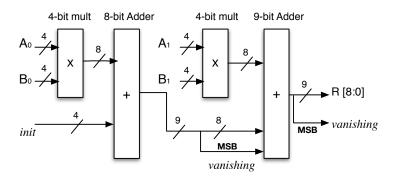

| 4.4  | Original MAC circuit: $R = \sum_{i} A_i \cdot B_i + C_0 \cdot \dots \cdot $ |

| 4.5  | MAC circuit unrolled over two cycles                                                                                                                                        |

| 4.6  | A 4-bit Serial Squarer                                                                                                                                                      |

| 4.7 | Unrolled 4-bit Serial Squarer                                                                                                                                                                                                     |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

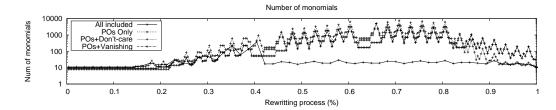

| 4.8 | Evaluation of Don't Care and Vanishing polynomials on a 4-bit serial squarer                                                                                                                                                      |

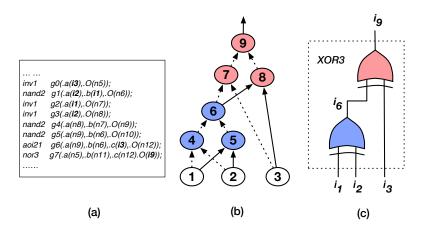

| 5.1 | Representing circuits as AIGs. a) Post-synthesized XOR3 gate-level netlist. b) AIG of the synthesized XOR3 gate-level netlist. (c) The extracted two XOR2 functions (nodes 6 and 9) and one XOR3 function (node 9)                |

| 5.2 | (a) AIG representation of a post-synthesized 2-bit multiplier gate-level netlist; (b) The AIG of the 2-bit multiplier shown in Figure 5.2(a); (c) Detected unobserved functions from the AIG and the correspondences to AIG nodes |

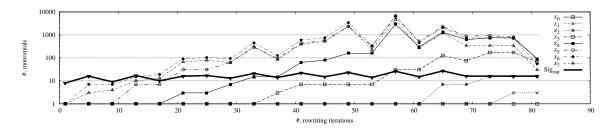

| 5.3 | Detecting $\{MAJ3\text{-}XOR3\}$ pairs of a 3-bit post-synthesized CSA-multiplier with MSB $z_5$ deleted                                                                                                                          |

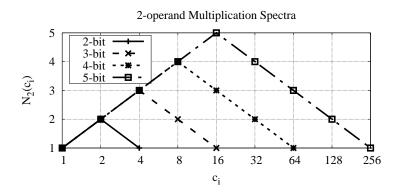

| 6.1 | The spectra of 2-bit, 3-bit, 4-bit and 5-bit two-operand multiplication                                                                                                                                                           |

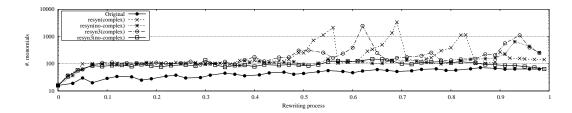

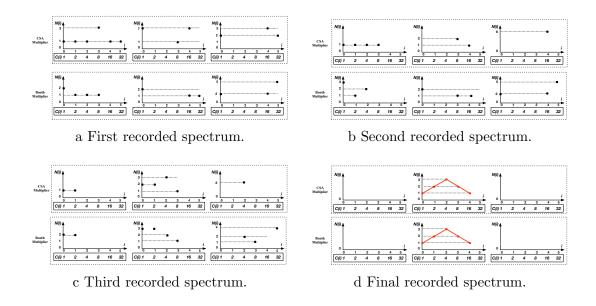

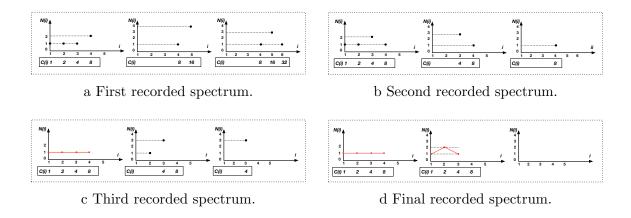

| 6.2 | Spectra of a 3-bit Booth-multiplier and CSA-multiplier of the four recorded expressions                                                                                                                                           |

| 6.3 | Spectra of a 2-bit MAC of the four recorded expressions                                                                                                                                                                           |

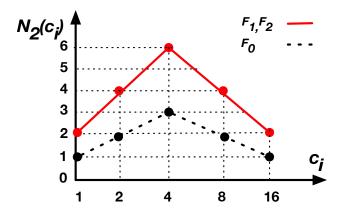

| 6.4 | Spectra of $F_1=A \times (B+C)$ , $F_2=A \times B+A \times C$ , and $F_3=A \times B$ . A,B, and C are 3-bit unsigned words                                                                                                        |

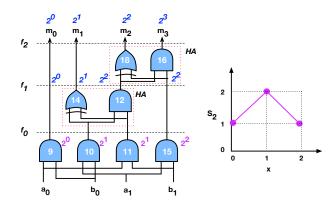

| 6.5 | Extracting the function of 2-bit multiplier using spectral method without algebraic rewriting                                                                                                                                     |

| 7.1 | Two multiplications in $GF(2^4)$ constructed using $P(x)_1 = x^4 + x^3 + 1$ and $P(x)_2 = x^4 + x + 1$                                                                                                                            |

| 7.2 | Extracted algebraic expressions of the four output bits of a $GF(2^4)$ multiplier. $P(x)=x^4+x+1$                                                                                                                                 |

| 7.3 | The gate-level netlist of post-synthesized and mapped 2-bit multiplier over $GF(2^2)$ . The irreducible polynomial $P(x) = x^2 + x + 1$ 115                                                                                       |

| 7.4 | Function extraction of a 2-bit $GF$ multiplier shown in Figure 7.3 using backward rewiring from PO to PI                                                                                                                          |

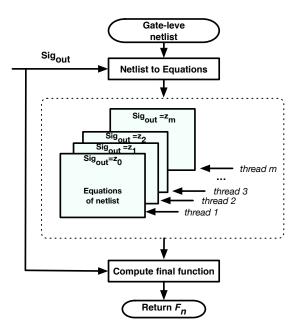

| 7.5 | Overview of the parallel extraction framework                                                                                                                                                                                     |

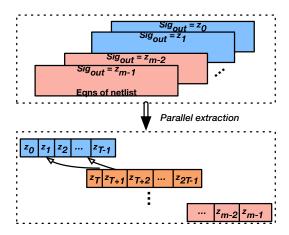

| 7.6  | Step3: parallel extraction of a $GF(2^m)$ multiplier with number of threads $T$                                                                  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.7  | Extracting the algebraic expression of $z_0$ and $z_1$ separately in Figure 7.4                                                                  |

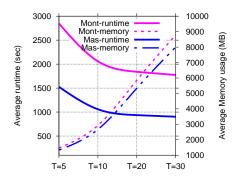

| 7.8  | Runtime and memory usage of our parallel verification approach as a function of number of threads $T$                                            |

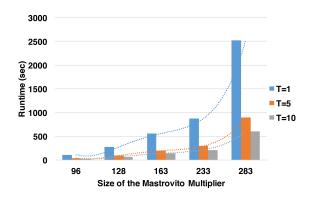

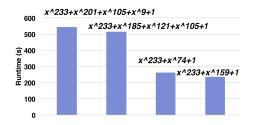

| 7.9  | Sing thread runtime analysis using Mastrovito multipliers                                                                                        |

| 7.10 | Result of reverse engineering $GF(2^{233})$ Mastrovito multipliers that are implemented using different $P(x)$                                   |

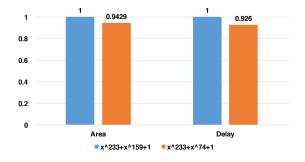

| 7.11 | Evaluation of the design cost using GF( $2^233$ ) Mastrovito multipliers with irreducible polynomials $x^{233}+x^{159}+1$ and $x^{233}+x^{74}+1$ |

#### CHAPTER 1

#### INTRODUCTION

With an almost unmanageable increase in the size and complexity of ICs and SoCs, hardware design analysis has become a dominating factor of the overall design flow [44]. Hardware verification is one of the essential procedures in the design flow that checks whether the actual hardware implementation has the correct specification. Specifically, verifying arithmetic computation units are particularly difficult due to the "bit blasting" issue, i.e., flattening the design specification into to a bit-level. The importance of arithmetic verification problem grows with an increased use of arithmetic modules in embedded systems to perform computation-intensive tasks for multimedia, signal processing, and cryptography applications.

Formal verification techniques can benefit greatly from abstractions of the functionality of the circuits being verified. Abstraction reduces the complexity of analysis of the design and may provide a hierarchical view of the register transfer level (RTL), which could be applied to system-level verification. Word-level abstraction specifically focuses on extracting a word-level representation of the function implemented by a gate-level design. For example, for an n-bit gate-level multiplier, the word-level function can be extracted as Z = AB. We can see that as the datapath size of the multiplier grows, the bit-level representation increases exponentially, while the word-level abstraction does not change. However, formal techniques for abstraction in gate-level design are challenging. The abstraction problems are even harder than the verification problem since there are no clear boundaries of the arithmetic functions in the design.

This thesis aims at overcoming the limitations of analyzing large arithmetic circuits, especially of the post-synthesized circuits. The approach proposed here addresses the verification, abstraction and reverse engineering problems in the algebraic domain, in which both the implementation and the specification of the arithmetic circuit are represented as pseudo-Boolean polynomials in respective variables (circuit signals). It solves the verification problem by extracting an arithmetic function computed by the circuit directly from its gate-level circuit implementation using computer algebraic methods, called function extraction or algebraic rewriting. This rewriting technique transforms the polynomial representing an encoding of the primary outputs (called the output signature) into a polynomial at the primary inputs (called the input signature). The computed arithmetic function can be used to verify the circuit against the given specification (i.e., the expected function of the design), or to decipher the function performed by the circuit. In the case of an incorrectly implemented function, this method will generate a counterexample (bug trace).

Regarding abstraction, a new canonical representation of arithmetic functions, called algebraic spectrum, is introduced in this thesis. Algebraic spectrum refers the coefficient distribution of the polynomial expressions that are computed using the rewriting technique. We prove that the coefficients distribution of arithmetic function is unique depending on the arithmetic operations. Finally, the verification and reverse engineering problems of Finite Field Arithmetic circuits are explored. For the finite field arithmetics, the main contributions include:

- 1) computer algebraic method is approved to be applied for parallel verification over  $GF(2^m)$ .

- 2) the approach of analyzing the irreducible polynomials of finite field arithmetic is proposed.

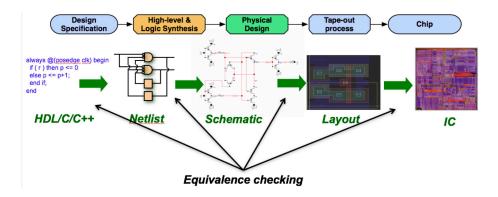

Figure 1.1: Typical industrial IC design flow.

• 3) the complete reverse engineering framework of finite field arithmetic is developed.

#### 1.1 Hardware Verification

The importance and difficulty of arithmetic circuit verification can be illustrated by the famous FDIV bug in Intel's Pentium processor in 1995, which cost Intel \$475 million. This bug was not covered by the one trillion simulation vectors used for this processor [27]. Verification is a critical problem in the chip industry since the cost of hardware verification is claimed to be 70 percent of the overall hardware design effort. Although the engineers and researchers invest a lot in hardware verification, it is still challenging as the design complexity increases. The recent verification industry study presented by Foster [44] showed that the average verification time in the last ten years is around 60% (57% in 2014) over the entire chip design period. In this survey, it also shows that there are more than 50% designs requires more than 60% project time in verification only. Most of those designs contain large arithmetic units.

Hardware verification is a process of checking the correctness of the fabricated hardware compared to the specification. However, it is impossible to directly check if the fabricated hardware matches the original specification. Typically, hardware verification is conducted step-by-step during the design flow. Hence, there are many hardware verification techniques developed that apply on different representations of hardwares, such as verification of HDL, gate-level netlist, schematic netlist, and so on. The design flow typically starts with a high-level specification using hardware description language (HDL) or C/C++. This specification is then compiled into a register-transfer-level (RTL) description, which is further optimized by high-level synthesis and logic synthesis techniques and translated into a corresponding netlist representation. The logic-level netlist is then translated to a physical layout during placement and routing synthesis.

Typically, equivalence checking has been applied at each step to check the equivalence before and after each optimization or transformation step in the design flow. There are many verification techniques that apply to different representations of hardware, such as HDL code, gate-level netlist, layout, etc. This thesis focuses on gate-level implementation of arithmetic circuits. Traditional approaches to verifying arithmetic circuits are based on simulation or emulation, but exhaustive simulation is not applicable to the large modern designs. Theorem proving approaches require verification experts to manually guide the systems to complete the proof. Thus, to automatically verify arithmetic circuits, many formal techniques have been developed to handle large practical circuits. However, few formal techniques are applicable to large gate-level arithmetic circuits. Those contemporary formal methods that could be applied to arithmetic circuits verification are reviewed in Chapter 2. The limitations of those formal methods for verifying arithmetic circuits are studied in the Chapter 3.

#### 1.2 Verification Techniques

#### 1.2.1 Equivalence Checking

In recent years, many CAD vendors have offered equivalence checking tools for design verification. Equivalence checking (EC) is one of the most widely used formal techniques in the verification of digital circuits. Depending on the type of the target circuits, i.e. sequential circuits or combinational circuits, equivalence checking can be classified in two types: sequential equivalence checking (SEC) and combinational equivalence checking (CEC).

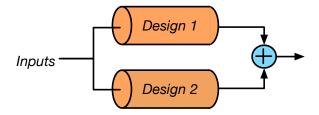

Figure 1.2: Combinational equivalence checking model.

The Combinational Equivalence Checking (CEC) model is shown in Figure 1.2. Let Design1 be the design to be verified, and Design2 be the reference design. The specification of the reference design is the expected specification of Design1. Given identical inputs to Design1 and Design2, a miter is built by XORing the corresponding output bits of these two designs and connecting to a wide OR gate. If the functions represented by the two designs are identical for all input patterns, then miter always evaluates to 0 (Boolean false) for any input pattern. In this case, the two designs are proved to be equivalent. Otherwise, these two designs are not equivalent.

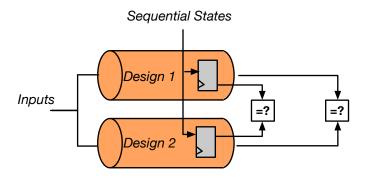

The Sequential Equivalence Checking (SEC) model is shown in Figure 1.3. SEC checks if the corresponding outputs are equivalent for any state of the two circuits with identical initial states. The proof of correctness of two sequential circuits requires a complete state-space traversal, which is one of the bottlenecks of sequential

Figure 1.3: Sequential equivalence checking model.

equivalence checking. The complexity of sequential equivalence checking could be significantly increased by synthesis process, such as retiming technique [120].

The most straightforward technique to prove or disprove the equivalence using EC model is exhaustive simulation. It is obvious that exhaust simulation is not possible for design with a large number of input bits. And, random simulation does not provide complete proof of the equivalence because of the coverage problem. Further, formal verification methods are heavily investigated to address the equivalence checking problem. The most promising formal techniques for solving equivalence checking problem include canonical diagrams, satisfiability and computer algebra methods.

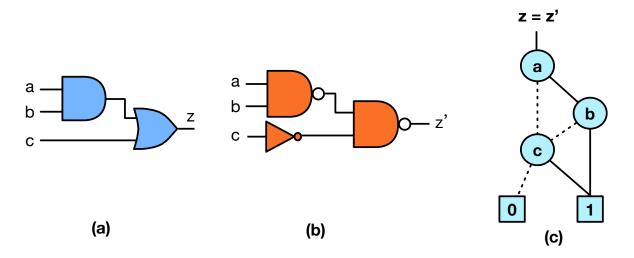

Reduced Ordered Binary Decision Diagrams (OBDDs) [20], provide the efficient method for equivalence checking for combinational and sequential circuits [5]. OBDDs are canonical representation with a fixed variable ordering. Hence, equivalence checking problem can be addressed by comparing the OBDDs of two designs. If two OBDDs are identical, two designs are functional equivalent. However, the size of the BDDs explodes for large designs. Specifically, it becomes large for the arithmetic circuits. For example, for integer multiplication, it has been shown that an n-bit multiplication requires a  $O(n^3)$  size OBDD [24].

Due to the limitation of the BDDs, many techniques have been developed to reduce the complexity of equivalence checking. Goldberg et. al [47] presented a simple framework for SAT-based CEC and reported results on an ISCAS-85 benchmarks. Paruthi et. al [88] proposed an idea that is based on a tight integration of a structural satisfiability (SAT) solver, BDD sweeping, and random simulation. In this work, the integral application of the SAT solver significantly enhances the capacity and efficiency of BDD sweeping and extends its suitability for mis-comparing designs. Further, the random simulation algorithm works on the graph that represents the netlist and thus runs more efficiently. Mishchenko et. al [76] presented an And-Inv-Graph (AIG) data structure that is the *state-of-the-art* technique for logic reduction and synthesis. The *Functional-reduced AIG* (FRAIG) is able to efficiently reduced the logic complexity [78] which has been implemented in the ABC system [80]. However, all these techniques are not applicable to large arithmetic circuits, such as Galois field multipliers and integer multipliers [31][72].

With significant research efforts spent on formal methods, formal verification for hardware that combines heuristic methods, such as checking structure similarity, becomes more and more popular. The similarity between the two circuits is exploited to identify the equivalences between internal nodes of the two circuits being checked for equivalence [63]. For example, the partial list of equivalence checkers are Formality (from Synopsys), Design Verifyer (from Chrysalis) and Verity (from IBM) [64]. Similarly, identifying structural similarities for sequential equivalence checking is also explored [120]. These tools perform logic equivalence checking of two circuits based structural analysis and BDD techniques. Similarly to other verification techniques, these equivalence checking techniques are limited by the memory explosion problem for arithmetic circuits. Recently, IBM Formal Verification team showed that their tools could automatically verify the floating point division (FDIV) unit using their SixthSense formal engine [62].

#### 1.2.2 Model Checking

Model checking performs verification by exhaustively checking whether a state-transition graph (STGs) satisfies a given property [36]. In this approach, a circuit is described as a state machine with transitions to describe the circuit behavior. The specifications to be checked are described as properties that the machine should or should not satisfy. Model checking is limited by the *state-space explosion problem*. The state explosion problem refers to the fact that the number of states is exponential in the number of Boolean variables. Explicit state model checkers are based on graph-traversal of the model states, and must keep track of the visited states. However, this is infeasible due to the large size of the modern designs.