# Schemes and Applications for Binding Hardware and Software in Computing Devices

**Robert Philip Lee**

Thesis submitted to Royal Holloway, University of London for the degree of Doctor of Philosophy in Information Security.

2018

# Declaration

These doctoral studies were conducted under the supervision of Professor Konstantinos Markantonakis.

The work presented in this thesis is the result of original research I conducted, in collaboration with others, whilst enrolled in the School of Mathematics and Information Security as a candidate for the degree of Doctor of Philosophy. This work has not been submitted for any other degree or award in any other university or educational establishment.

> Robert Lee Date

## Acknowledgements

Firstly, I would like to thank Prof. Kostas Markantonakis for his support and supervision throughout my PhD. Without his direction, support and ability (if not eagerness) to tell me his honest opinions then I'd have never produced this thesis. Similarly, I must also thank Raja Naeem Akram for his invaluable inputs to my research and for being so welcoming whenever I turned up at his office without warning.

Next, I must thank the Information Security Group, the Centre for Doctoral Training in Cyber Security and the Smart Card and IoT Security Centre. Thank you to the management committee who gave me the opportunity to pursue this PhD and thank you to my fellow students who made the experience so much fun. My thanks go especially to Andreas, Christian, Greg, Jonathan, Pip, Rachel, Sam, Thalia and Thyla who's friendship so blessed my time at RHUL.

To Adam, Rose, Steve, Steve, Steve, Mary, Claire, Sophie, Stuart, Reuben and all at St Liz - thank you for your friendship, company and for providing that essential tether to the "real world".

My family are also due their share of thanks for this thesis. Thank you to all of you but especially to my father, David, and my brother, Stuart, for your support, encouragement and advice.

And finally, a mountain of thanks are due to Ela, who during the course of this PhD has been the most amazing girlfriend, the most amazing fiancée and now the most amazing wife that anyone could ask for. Thank you for your love, for your support and for taking me away from work when I needed the breaks and for encouraging me back to my desk when I was convinced I needed more breaks from my corrections. I couldn't have done this without you, thank you.

## **Publications**

A number of papers from this work have been presented and published at international, peer-reviewed conferences. The published papers include:

- R. P. Lee, K. Markantonakis, and R. N. Akram. Binding hardware and software to prevent firmware modification and device counterfeiting. In J. Zhou and J. López, editors, *Proceedings of the 2nd ACM International Workshop on Cyber-Physical System* Security, CPSS@AsiaCCS, Xi'an, China, May 30, 2016, pages 70–81. ACM, 2016

- C. Shepherd, G. Arfaoui, I. Gurulian, R. P. Lee, K. Markantonakis, R. N. Akram, D. Sauveron, and E. Conchon. Secure and trusted execution: Past, present, and future - A critical review in the context of the internet of things and cyber-physical systems. In 2016 IEEE Trustcom/BigDataSE/ISPA, Tianjin, China, August 23-26, 2016, pages 168–177. IEEE, 2016

- R. P. Lee, K. Markantonakis, and R. N. Akram. Provisioning software with hardwaresoftware binding. In *Proceedings of the 12th International Conference on Availability*, *Reliability and Security, Reggio Calabria, Italy, August 29 - September 01, 2017*, pages 49:1–49:9. ACM, 2017

- R. P. Lee, K. Markantonakis, and R. N. Akram. Ensuring secure application execution and platform-specific execution in embedded devices. ACM Transactions on Embedded Computing Systems, 18(3):26:1–26:21, Apr. 2019

## Abstract

The Internet of Things (IoT) is considered one of the most significant computing trends of the 21<sup>st</sup> century so far, causing the number of deployed computing devices to increase dramatically. However, the frequency and severity of attacks against computer systems is increasing with attacks such as Stuxnet and Mirai. This thesis is concerned with securing computing devices by creating bonds between hardware and software to ensure deployed devices only execute the software they are intended to and vice versa. This prevents counterfeiting, device tampering and other attacks.

This thesis presents three studies into binding hardware and software. These concern creating secure dependencies between the hardware and software of computing devices. Specifically, this thesis considers mutual dependencies created by bidirectional bonds between hardware and software. The first study defines hardware-software bonds, the problem space and proposes the first bidirectional scheme for binding hardware and software together. The scheme is implemented using an FPGA and analysed for security and performance.

The second case considers the deployment of binding schemes. This is considered in a smart city environment by first studying and modelling the security architecture of the problem. Two security models are proposed with associated software provisioning protocols. All the proposals are formally analysed using Tamarin Prover and implemented for Raspberry Pi and laptop computer.

The third study combines hardware-software binding with another problem in cyber security - Secure Application Execution. The two problems are compared and set of requirements for simultaneously achieving both is defined. A binding scheme is proposed solving the expanded problem and a prototype Secure Execution Processor equipped with the scheme is presented and analysed.

Finally, the thesis concludes by summarising the research presented and highlighting potential areas for future work in binding hardware and software together.

# Contents

| 1        | Intr | oduction            |                       |              | 12     |

|----------|------|---------------------|-----------------------|--------------|--------|

|          | 1.1  | The Computing La    | andscape              |              | <br>13 |

|          | 1.2  | Contributions       |                       |              | <br>14 |

|          | 1.3  | Thesis Structure    |                       |              | <br>15 |

| <b>2</b> | Bac  | kground             |                       |              | 17     |

|          | 2.1  | Embedded System     | s and Smart Cards .   |              | <br>18 |

|          |      | 2.1.1 Embedded      | Systems               |              | <br>18 |

|          |      | 2.1.2 Smart Card    | ls                    |              | <br>19 |

|          | 2.2  | Field Programmab    | le Gate Arrays        |              | <br>21 |

|          | 2.3  | Physically Unclone  | able Functions        |              | <br>22 |

|          |      | 2.3.1 PUF Exam      | ples                  |              | <br>24 |

|          |      | 2.3.2 PUF Uses      |                       |              | <br>26 |

|          | 2.4  | Binding Hardware    | and Software          |              | <br>27 |

|          |      | 2.4.1 Application   | Binding               |              | <br>28 |

|          |      | 2.4.2 Algorithm     | Binding               |              | <br>29 |

|          |      | 2.4.3 Bond Direc    | tionality             |              | <br>30 |

|          | 2.5  | Secure Application  | Execution             |              | <br>32 |

|          |      | 2.5.1 Proposals f   | or Securing Applicati | on Execution | <br>32 |

|          | 2.6  | Spectre and Meltd   | own                   |              | <br>35 |

|          | 2.7  | Formal Analysis .   |                       |              | <br>36 |

| 3        | Bin  | ding Hardware aı    | nd Software           |              | 38     |

|          | 3.1  | Introduction        |                       |              | <br>39 |

|          |      | 3.1.1 Contributio   | ons                   |              | <br>40 |

|          |      | 3.1.2 Structure     |                       |              | <br>40 |

|          | 3.2  | Problem Description | on                    |              | <br>41 |

|          |      | 3.2.1 Notation .    |                       |              | <br>41 |

|   |                 | 3.2.2  | Problem Scenarios                                                                              | 41 |

|---|-----------------|--------|------------------------------------------------------------------------------------------------|----|

|   |                 | 3.2.3  | Attacker Model                                                                                 | 42 |

|   |                 | 3.2.4  | Assumptions                                                                                    | 43 |

|   |                 | 3.2.5  | Design Requirements                                                                            | 43 |

|   | 3.3             | Relate | d Work                                                                                         | 45 |

|   |                 | 3.3.1  | Anti-counterfeiting measures                                                                   | 45 |

|   |                 | 3.3.2  | Hardware Intrinsic Security                                                                    | 47 |

|   | 3.4             | Propos | sed Solution                                                                                   | 50 |

|   |                 | 3.4.1  | Design Overview                                                                                | 50 |

|   |                 | 3.4.2  | Securing Mutable Data                                                                          | 52 |

|   |                 | 3.4.3  | Choice of Function $F$                                                                         | 53 |

|   |                 | 3.4.4  | Implementation Considerations $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 55 |

|   |                 | 3.4.5  | Solution Analysis                                                                              | 56 |

|   |                 | 3.4.6  | Security Evaluation                                                                            | 57 |

|   | 3.5             | Impler | nentation                                                                                      | 58 |

|   |                 | 3.5.1  | Development Platform                                                                           | 59 |

|   |                 | 3.5.2  | Demonstration Application                                                                      | 60 |

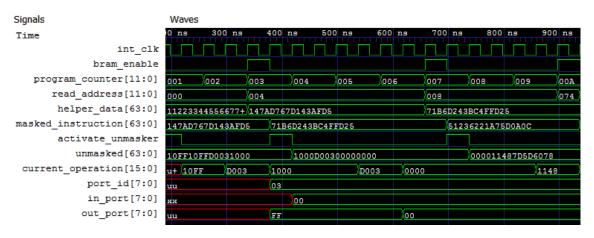

|   |                 | 3.5.3  | Unmasking Unit                                                                                 | 61 |

|   |                 | 3.5.4  | Performance Analysis                                                                           | 65 |

|   |                 | 3.5.5  | Security Analysis                                                                              | 66 |

|   | 3.6             | Conclu | usion                                                                                          | 68 |

| 4 | $\mathbf{Inst}$ | alling | and Updating Software with Hardware-Software Binding                                           | 69 |

|   | 4.1             | Introd | uction                                                                                         | 70 |

|   |                 | 4.1.1  | Contributions                                                                                  | 71 |

|   |                 | 4.1.2  | Structure                                                                                      | 71 |

|   | 4.2             | Proble | m Description                                                                                  | 72 |

|   |                 | 4.2.1  | Entities and Motivations                                                                       | 72 |

|   |                 | 4.2.2  | Attacker Model                                                                                 | 73 |

|   |                 | 4.2.3  | Protocol Requirements                                                                          | 74 |

|   | 4.3             | Model  | s for Software Provisioning                                                                    | 75 |

|   |                 | 4.3.1  | Device-centric Software Provisioning                                                           | 76 |

|   |                 | 4.3.2  | Authority-centric Software Provisioning                                                        | 78 |

|   | 4.4             | Relate | d Work                                                                                         | 80 |

|   |                 | 4.4.1  | Binding Hardware and Software                                                                  | 80 |

|   |     | 4.4.2 | MULTOS                                                                                                                                                 |

|---|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 4.4.3 | Global Platform $\ldots \ldots \ldots$ |

|   | 4.5 | Propo | sed Solution $\ldots \ldots 84$                             |

|   |     | 4.5.1 | Overview of Solution                                                                                                                                   |

|   |     | 4.5.2 | Device-centric Software Provisioning                                                                                                                   |

|   |     | 4.5.3 | Authority-centric Software Provisioning                                                                                                                |

|   | 4.6 | Analy | sis                                                                                                                                                    |

|   |     | 4.6.1 | Description of Protocol Models                                                                                                                         |

|   |     | 4.6.2 | Scope of Mechanical Analysis                                                                                                                           |

|   |     | 4.6.3 | Modelling Assumptions Required                                                                                                                         |

|   |     | 4.6.4 | Results of Analysis                                                                                                                                    |

|   |     | 4.6.5 | Further Observations                                                                                                                                   |

|   | 4.7 | Concl | usion                                                                                                                                                  |

| 5 | Sec | uring | Application Execution and Binding Hardware and Software 93                                                                                             |

| 0 | 5.1 | 0     | luction                                                                                                                                                |

|   | 0.1 | 5.1.1 | Contributions                                                                                                                                          |

|   |     | 5.1.2 | Chapter Structure                                                                                                                                      |

|   | 5.2 |       | em Description                                                                                                                                         |

|   |     | 5.2.1 | Platform Specific Execution                                                                                                                            |

|   |     | 5.2.2 | Secure Application Execution                                                                                                                           |

|   |     | 5.2.3 | Attacker Model                                                                                                                                         |

|   |     | 5.2.4 | Requirements                                                                                                                                           |

|   | 5.3 |       | ed Work                                                                                                                                                |

|   |     | 5.3.1 | Platform Specific Execution                                                                                                                            |

|   |     | 5.3.2 | Secure Application Execution                                                                                                                           |

|   | 5.4 | Propo | sed Solution                                                                                                                                           |

|   |     | 5.4.1 | Protecting Sequential Transitions                                                                                                                      |

|   |     | 5.4.2 | Protecting Instruction-Dependent Transitions                                                                                                           |

|   |     | 5.4.3 | Securing Instruction-Independent Transitions                                                                                                           |

|   | 5.5 | Imple | mentation $\ldots$                                                    |

|   |     | 5.5.1 | Design Decisions                                                                                                                                       |

|   |     | 5.5.2 | Assembler                                                                                                                                              |

|   |     | 5.5.3 | Hardware                                                                                                                                               |

|   | 5.6 | Analy | sis                                                                                                                                                    |

#### CONTENTS

|              |                | 5.6.1   | Requirements Analysis                                       | . 119  |

|--------------|----------------|---------|-------------------------------------------------------------|--------|

|              |                | 5.6.2   | Implementation Analysis                                     | . 120  |

|              | 5.7            | Conclu  | usion                                                       | . 121  |

| 6            | Con            | clusio  | n                                                           | 123    |

|              | 6.1            | Summ    | ary and Conclusions                                         | . 124  |

|              | 6.2            | Future  | e Work                                                      | . 125  |

| A            | $\mathbf{Sim}$ | ple Bi  | nding Scheme Test Application Code                          | 126    |

| в            | Tan            | arin I  | Model for Device-Centric Provisioning                       | 128    |

| С            | Tan            | arin I  | Model for Authority-Centric Provisioning                    | 136    |

| D            | Tan            | narin N | Iodel for Authority-Centric Provisioning with Pre-Shared Ke | eys148 |

| $\mathbf{E}$ | Secu           | ıre-Ex  | ecution Processor Test Application Code                     | 161    |

| Bi           | bliog          | raphy   |                                                             | 163    |

# **List of Figures**

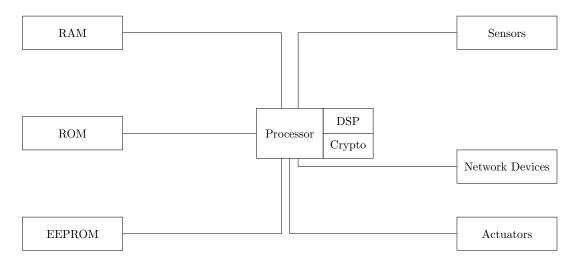

| 2.1 | Embedded systems may be built using a combination of many components.                                                 | 19 |

|-----|-----------------------------------------------------------------------------------------------------------------------|----|

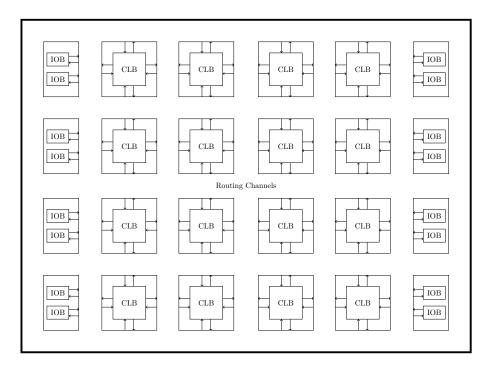

| 2.2 | An FPGA consists of programmable logic elements and IO connections to                                                 |    |

|     | other devices                                                                                                         | 22 |

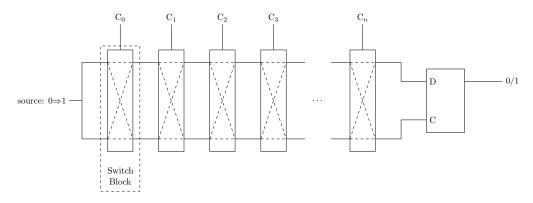

| 2.3 | An arbiter Physically Uncloneable Function (PUF) may include a source,                                                |    |

|     | a number of multiplexer switch blocks and a D flip-flop acting as an arbiter.                                         | 25 |

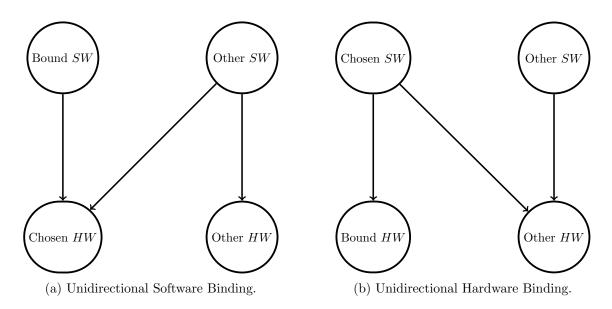

| 2.4 | Unidirectional binding only restricts one of hardware or software. When                                               |    |

|     | only the software is bound, it is restricted to only the hardware it is bonded                                        |    |

|     | to whereas the hardware is unrestricted and may execute other software.                                               |    |

|     | The same applies in reverse when only the hardware is bound, the hardware                                             |    |

|     | is restricted but the software chosen for the hardware is not. Edges between                                          |    |

|     | software and hardware indicate permitted installations                                                                | 31 |

| 2.5 | Bidirectional binding of hardware and software ensures bound elements                                                 |    |

|     | cannot be moved onto other devices or installed with alternative software.                                            |    |

|     | Edges indicate an allowed installation of software onto hardware                                                      | 31 |

| 2.6 | Code designed to improve program security is exploited by Spectre. Exam-                                              |    |

|     | ple code copied from [64].                                                                                            | 36 |

| 3.1 | Hardware block diagram of the typical embedded system considered in this                                              |    |

|     | work. The grey area indicates the "safe zone" impenetrable by attackers. $% \left( {{{\bf{x}}_{{\rm{s}}}}} \right)$ . | 44 |

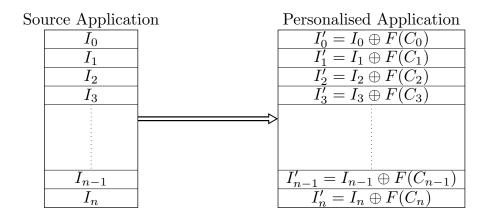

| 3.2 | The transformation of source memory content into a personalised application                                           | 51 |

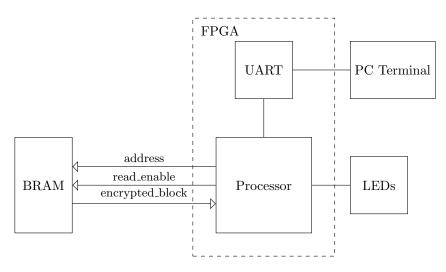

| 3.3 | Diagram of implemented system                                                                                         | 60 |

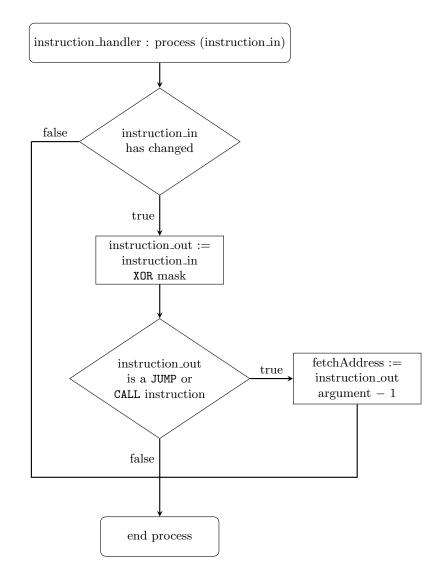

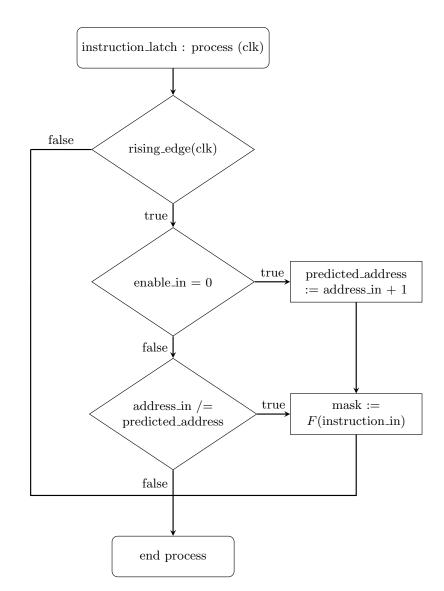

| 3.4 | A flowchart of the instruction_in handling of the Unmasking Unit. $\ldots$ .                                          | 63 |

| 3.5 | A flowchart of the calculation of the instruction mask values                                                         | 64 |

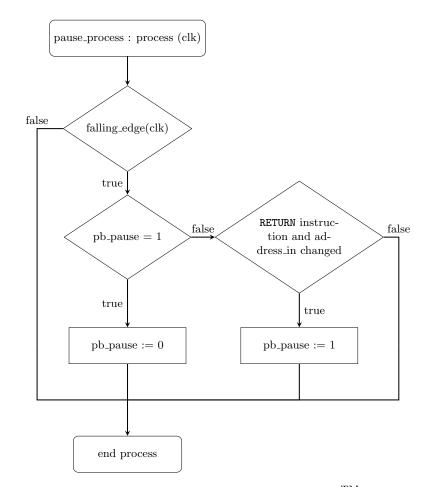

| 3.6 | A flowchart of the operation of the PicoBlaze $^{\rm TM}$ pause process                                               | 65 |

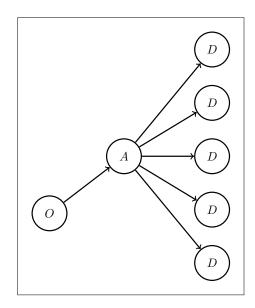

| 4.1 | Device-centric application provisioning only requires connection between                                              |    |

|     | Operator $(O)$ and Device $(D)$ , however this requires prior trust between $D$                                       |    |

|     | and Authority $(A)$ and between A and O                                                                               | 77 |

#### LIST OF FIGURES

| 4.2 | The Application-Relay model allows an Authority to monitor application                                             |

|-----|--------------------------------------------------------------------------------------------------------------------|

|     | provisioning from $O$ to $D$                                                                                       |

| 4.3 | Application-Broadcast model considers the situation in which $O$ is loading                                        |

|     | a large number of Devices with a single application                                                                |

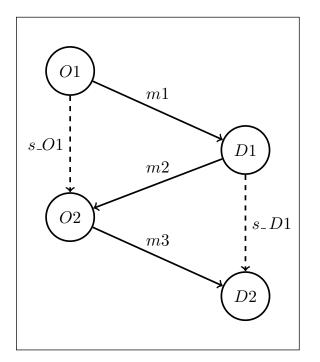

| 4.4 | Modelling Device-centric application provisioning requires a state machine                                         |

|     | of four states with five connections                                                                               |

| 5.1 | Legitimate executions follow each instruction in a control path such as the                                        |

|     | ticked instructions, illegitimate executions skip instructions such as the path $% \left( \frac{1}{2} \right) = 0$ |

|     | avoiding the JUMP NZ, 6 that is marked by crosses                                                                  |

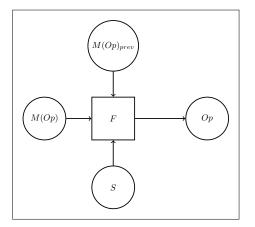

| 5.2 | The binding scheme from Chapter 3 uses a secret, $S$ , and the previous,                                           |

|     | masked instruction, $M(Op)_{prev}$ , to unmask $M(Op)$ and reveal $Op$ for exe-                                    |

|     | cution                                                                                                             |

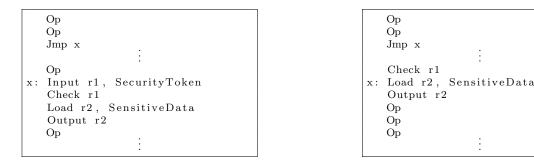

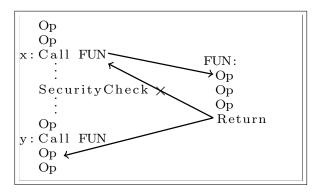

| 5.3 | When protected by only simple hardware-software binding, the code snippet                                          |

|     | on the left can be modified to leak sensitive data by moving code into a                                           |

|     | location reached by a JUMP operation                                                                               |

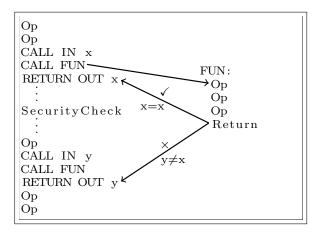

| 5.4 | Changing return addresses can be used to skip security critical instructions. 108                                  |

| 5.5 | The extra operations added to the instruction set secure the ${\tt RETURN}$ after                                  |

|     | execution of re-used function code                                                                                 |

| 5.6 | The prototype included serial and LED outputs to demonstrate correct                                               |

|     | execution                                                                                                          |

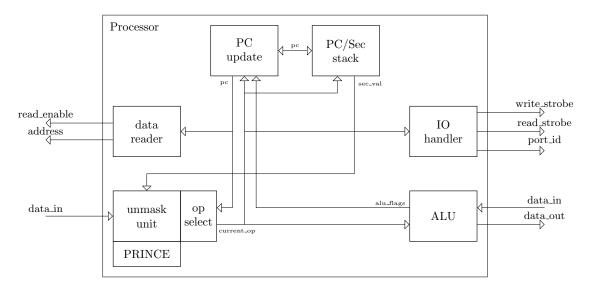

| 5.7 | The Secure-Execution Processor consists of six main elements                                                       |

| 5.8 | The Secure-Execution Processor updates each signal according to a strict                                           |

|     | schedule                                                                                                           |

# **List of Tables**

| 4.1 | Protocol Notation                                                                    |

|-----|--------------------------------------------------------------------------------------|

| 4.2 | Device-centric Software Provisioning                                                 |

| 4.3 | Authority-centric Software Provisioning (with Public-Key Cryptography) $.$ 87        |

| 4.4 | Authority-centric Software Provisioning (with Pre-Shared Keys) 87                    |

|     |                                                                                      |

| 5.1 | Lightweight block ciphers implemented by Maene and Verbauwhede in [78]. 113          |

| 5.2 | Only the instructions needed for the test application were implemented and           |

|     | thus some common instructions are missing                                            |

| 5.3 | Sequential transitions require less memory accesses than unconditional ${\tt JUMPs}$ |

|     | which require less than conditional JUMPs                                            |

## Introduction

#### Contents

| 1.1 | The Computing Landscape | 13 |

|-----|-------------------------|----|

| 1.2 | Contributions           | 14 |

| 1.3 | Thesis Structure        | 15 |

This chapter introduces the thesis by describing the context and need for the research undertaken. Firstly, the landscape of computer systems and recent trends in computing are described. Recent attacks are described as well as some consequences of security breaches to argue the need for better security in computer systems. The chapter finishes by listing the main research contributions of this work and by describing the structure of the document.

## 1.1 The Computing Landscape

The number of computing devices in the world is growing at an increasing rate and there are now more devices connected to the internet than people on the Earth [120, 18]. Computing power continues to increase, and the number of places it is used expands [102]. One area experiencing the biggest expansion is embedded computing [111]. The Internet of Things (IoT) concept is causing embedded systems to be included into more and more devices including (but not limited to) cars, aeroplanes, industrial control systems, fridges, light bulbs and utility meters [66, 87].

The IoT has many advantages; smart meters can help people to save money by monitoring their energy consumption [103], healthcare processes can be improved using IoT solutions [92] and connected cars may make the roads safer [50]. Furthermore, as well as practical value, the IoT has great monetary value with some estimating the market to be worth \$457B or more in 2020 [25, 99].

However, as the deployment of computer systems increases, the number of attacks against them grows; 2017 saw many high profile attacks in which personal data or national infrastructure were targeted [95]. These attacks caused disruption, financial damage and reputation damage to businesses and governments [95]. Overall, the security software company Symantec observed a 600% increase in attacks against IoT systems in 2017 [114].

However, the consequences of insecure IoT devices can be much significant than damage to revenue or reputation. In 2014, Genesis Toys released "My Friend Cayla", a doll containing an embedded system to allow it to talk to children [40]. In 2015, researchers from Pen Test Partners discovered the insecurity of the dolls developer options made it possible to change the dolls behaviour. This allowed the researchers to force the doll to swear at children (which should not have been possible) or to eavesdrop on conversations held around the doll [94]. The existence of the latter modification caused the toy to be declared as "illegal espionage apparatus" and to be banned in Germany [96].

Another recent attack on computing devices is the Stuxnet malware deployed to sabotage Iranian nuclear power stations. The malware would interfere with plant centrifuges to cause premature wear and damage the Industrial Control System. By disabling legitimate code, the malware was able to run the attack code needed to target the centrifuges [69]. Thirdly, Mirai is a malware that caused significant disruption to a number of internet services including Spotify, Twitter and PayPal [115]. It spread by searching for devices with default login credentials still accepted. Once the malware connected to an open device it would spread itself to the new device to add another bot to the botnet [26]. The final result was a botnet capable of performing 620 Gbps Distributed Denial of Service (DDoS) attacks against targets selected via the command and control system running the malware [115].

These attacks show that more efforts are needed to secure computing devices and systems. There are many approaches to securing computer systems, however one approach is to ensure devices are only running correct, legitimate and trusted software. If this goal were achieved, the attacks described previously would all be thwarted as malicious code would not be executable on the devices as it would be neither legitimate nor trusted and it's behaviour incorrect for the devices.

One way of ensuring that only the correct software can execute on a device is to bind the hardware and software of computing devices together. If an application must be bound to a device to execute and only trustworthy parties may bind software then many attacks, such as those described, are prevented [67, 110, 10]. This thesis is focussed on the development and use of schemes for binding hardware and software in computing devices.

## 1.2 Contributions

The main research contributions of this thesis are:

- Expanding the definition of binding hardware and software to include directionality (Chapter 3).

- Proposing and implementing the first bidirectional scheme to bind hardware and software together (Chapter 3).

- Analysing software provisioning in smart city environments and proposing three models to fit the setting (Chapter 4).

- Proposing, formally analysing and implementing three protocols to provisioning soft-

ware in a smart city environment (Chapter 4).

- Combining the problem of binding hardware and software with securing application execution to better model security threats facing embedded devices (Chapter 5).

- Proposing and implementing a scheme to guarantee secure and platform specific application execution in embedded devices (Chapter 5).

## 1.3 Thesis Structure

This thesis is organised in six chapters starting with an introduction to embedded systems and the need for their security.

Chapter 2 introduces the research topics relevant to this work. The background chapter does not exhaustively list all relevant work but describes each of the problems, technologies and techniques used in the later chapters of this document. As such, the chapter defines the problems as considered in this work and provides the information needed to understand the tools and technologies used.

Chapter 3 describes the first hardware-software binding scheme proposed in this work. We argue that previously developed schemes are insufficient and a bidirectional method of binding hardware and software is needed. A scheme is proposed to meet the elicited requirements. The viability of the scheme is demonstrated by a proof-of-concept implementation.

In Chapter 4, we consider how the scheme proposed in Chapter 3 could be used in a real-world environment. This study focusses on how to install and update software when hardware-software binding is used. Considering the case study of a smart city, several models were developed to consider the different software installation models that might apply. Protocols meeting the elicited requirements were proposed, implemented and formally analysed using Tamarin Prover.

Chapter 5 also builds on Chapter 3 by expanding the problem considered to include ensuring correct application execution. An analysis of securing application execution led to a new, transition-based approach to Secure Application Execution (SAE). By combining the Chapter 3 scheme with ideas from the SAE literature a new binding scheme was proposed to ensure correct and platform specific application execution. The expanded scheme was implemented as a soft-core processor devloped and tested on a Field Programmable Gate Array (FPGA).

Finally, Chapter 6 concludes this thesis by summarising the work presented and describing potential directions for future work in the area.

## Background

#### Contents

| <b>2.1</b> | Embedded Systems and Smart Cards     |

|------------|--------------------------------------|

| 2.2        | Field Programmable Gate Arrays    21 |

| 2.3        | Physically Unclonable Functions      |

| 2.4        | Binding Hardware and Software        |

| <b>2.5</b> | Secure Application Execution         |

| 2.6        | Spectre and Meltdown 35              |

| 2.7        | Formal Analysis                      |

This chapter introduces the relevant background material to this work. Early sections describe the main technologies associated with the research presented in later chapters of this thesis. Schemes are proposed for embedded system or smart card (Section 2.1) use, prototyped using FPGAs (Section 2.2) and including PUFs (Section 2.3). Background research presented concerns binding hardware and software (Section 2.4), the focus of this work. However, later chapters include other topics including secure application execution and formal analysis, described in Sections 2.5 and 2.7. Two recent, significant attacks on processor technologies, Spectre and Meltdown, are included for completeness in Section 2.6.

## 2.1 Embedded Systems and Smart Cards

Embedded systems and smart cards are the most prevalent types of computing devices in the world [120, 52]. Both have become a significant part of modern life; and are the subject of academic and industrial interest. This section defines both types of device and how they are considered in this document.

#### 2.1.1 Embedded Systems

This thesis proposes multiple schemes for securing embedded systems. Embedded systems are defined by P. Marwedel as "information processing systems embedded into enclosing products" [88]. They are included in various settings including: cars, home electronics and Smart City infrastructure. In many of these, the presence of the computer is not obvious due to the difference of the form factor from "traditional" computers. This has led to embedded systems also being called *disappearing computers* [88]. Other titles given to the spreading of embedded systems include: *ubiquitous computing* [122], *pervasive computing* [105] and the Internet of Things (IoT) [11, 9].

Regardless of labels, embedded computing is concerned with the deployment of embedded systems. These are small, low power devices deployed for particular tasks. A general purpose processor or microcontroller may be included, but the device is deployed for a specific purpose. Some controllers operate washing machines, others network hardware or motor vehicles. The common feature is the devices are small, low-powered, and computing resources are often limited [88].

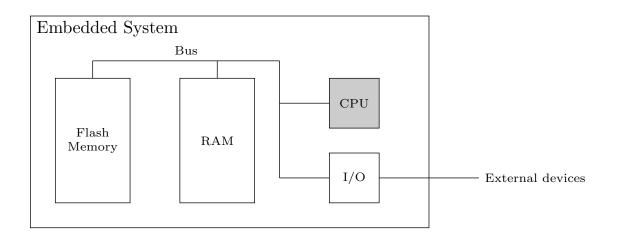

Embedded systems are complete systems deployed for a purpose, comprised of a number of elements [107]. Typically, an embedded system features a processor or microcontroller, this may include specialist hardware such as a cryptographic co-processor or Digital Signal Processor (DSP). Storage, such as flash memory, Read-Only Memory (ROM) or Electronically-Erasable Read-Only Memory (EEPROM) is included to store software and other data needed. Finally, some Input/Output (IO) devices may be attached to the system; these could be sensors to record information or actuators for interacting with the environment. In some cases, network capability is included allowing the device to communicate with other devices or servers. A diagram of an embedded system and the elements

Figure 2.1: Embedded systems may be built using a combination of many components.

that may be included is included in Figure 2.1.

The diagram in Figure 2.1 demonstrates many of the possible components that may be included in an embedded system as considered in this thesis. We assume they will include a processor, some long-term storage and Input/Output devices such as sensors or actuators. Some may also include a cryptographic co-processor or digital signal processor. However, embedded systems in this work will always include a processor, storage and some means of interacting with the world.

#### 2.1.2 Smart Cards

As well as applying to embedded systems, the schemes proposed in this thesis may apply to securing smart cards. Smart cards are small computing devices integrated into standardised forms used to add security to a transaction or communication. They are equipped with unique IDs, secure storage, security algorithms and tamper-resistance technologies to prevent forgery or duplication. Devices sometimes described as smart cards are magnetic stripe cards, these are cards without processors and equipped with magnetic stripes. However, these cards offer no security and are incapable of processing so are not considered in the definition of smart cards in this work. The most common forms of smart cards are the 86mm×54mm form factor of credit and debit cards and the smaller (25mm×15mm to 12.3mm×8.8mm) mobile phone SIM card forms. Like embedded systems (Section 2.1.1), smart cards are deployed as application specific devices. Common uses of smart cards include: payments, transport ticketing, mobile telephony, physical

access control and identification [90].

Smart card communications, structures and security mechanisms are carefully standardised. While there are many details covered, the sections on application protection and secure application installation are the details significant to this work. There are several standards and standardisation bodies involved in smart cards. The main organisations and bodies are ISO, GlobalPlatform and MULTOS [90].

The International Organisation for Standardisation (ISO) is the main creator of smart card standards. Four main standards cover smart cards: ISO 7816, ISO 14443, ISO 15693 and ISO 7501 [57, 56, 53, 54]. ISO 7816 covers most details of smart cards including sizes, interfaces, file structures, executable commands and cryptographic services [57]. Closeproximity contactless cards are described by ISO 14443, whereas ISO 15693 describes longer range "vicinity cards" [56, 53]. Smart cards also feature in ISO 7501, although it primarily concerns machine-readable travel documents and smart cards are only covered in that context [54]. However, while these cover many important details, the most relevant standards to this thesis are those from GlobalPlatform and the MULTOS consortium covering secure mechanisms for installing and managing applications.

GlobalPlatform, like ISO, is another standardisation group producing standards for smart card behaviour [42]. GlobalPlatform standards are also applied to securing connected cars and IoT devices [43]. The GlobalPlatform card specification is more application and security focussed than ISO standards and does not describe form factors or interfaces. However, it does cover how applications may be securely installed and the architecture ensuring GlobalPlatform compliant card trustworthiness. Application management is included in the GlobalPlatform specification with cryptographic means for ensuring software installation and verification [42]. This is significant as secure installation and management of applications is critical to securing computing devices.

Finally, MULTOS is an operating system for multi-application smart cards developed by the MULTOS consortium [85]. Like GlobalPlatform, MULTOS is designed for security and enabling multiple applications to be securely installed to a single card. MULTOS has been included in various devices including smart cards, ID cards, passports and ticketing [83]. Security is a major focus of MULTOS and cryptographic methods are included to secure communication between MULTOS devices, Issuers and Application Providers. MULTOS provides methods for secure software installation and updating [85]. These methods of securely distributing applications to remote devices can help secure cards against rogue applications. In MULTOS, security is maintained by certificates issued to each software before it may be installed [85].

## 2.2 Field Programmable Gate Arrays

FPGAs are reprogrammable hardware devices configurable for many different purposes including prototyping, computation and digital audioprocessing. A typical FPGA includes a two-dimensional array of configurable blocks, similar to a Programmable Array Logic (PAL) chip, but more complex and with a different development process. PALs required expert programming based on intimate knowledge of the architecture, FPGAs are programmed using powerful Computer Aided Design (CAD) software. Instead of a precise gate-level design, a designer uses Hardware Description Language (HDL) to describe required behaviour and the tools decide how to produce working circuits [49].

FPGAs are commonly used in prototyping circuit designs. Their re-programmable nature allows a design to be tested in real silicon without fabrication. However, FPGAs are also used in cases when a bespoke circuit is needed but a bespoke Integrated Circuit (IC) is not cost-effective. In these cases an FPGA provides the required functionality while minimising production cost [49].

Rapid prototyping is the main use of FPGAs in this thesis. In later chapters, two FPGA implementations are described demonstrating schemes proposed in this work. This approach allows a scheme to be demonstrated with real circuits rather than in theoretical models or simulations [49].

Many FPGAs, such as those produced by Xilinx Inc. and used in this work, consist of an array of programmable blocks programmed to create a circuit. Blocks include two components: a logical component and a routing component. The logical component receives block inputs and performs a function on some, all or none of the inputs. In Xilinx devices, the logical component is a Lookup Table (LUT) indexed by the inputs, allowing any boolean function. The result of the logic component is then routed to nearby blocks, as determined by the CAD tool. This logical structure allows for any possible boolean

Figure 2.2: An FPGA consists of programmable logic elements and IO connections to other devices.

functions of the block inputs to be programmed into a block. A complicated equation or a simple one will each require the same number of resources and give the same performance [49].

In addition to programmable logic blocks, FPGAs contain IO blocks to allow the FPGA to interface with other components and devices [49]. For example, the Xilinx Spartan-6 FPGA evaluation board used in this thesis includes UART, ethernet and headers for other I/O devices [124].

A diagram of this typical FPGA structure can be found in Figure 2.2. For clarity, the wiring between blocks is omitted, however, in many FPGAs, each block has the ability to connect to any other block in the FPGA [108].

## 2.3 Physically Unclonable Functions

Physically Uncloneable Functions (PUFs) as considered in recent literature were introduced in 2002 by Gassend et al. as Silicon Physical Random Functions [39]. A PUF can be considered a hardware biometric or as a fingerprint of an object [79]. Attempts had been made to exploit unclonable characteristics of physical devices before 2002 [14]. However, Gassend et al. were the first to propose silicon circuits with unclonable properties [39]. Since the work of Gassend et al. however, there have been many PUF designs proposed including: SRAM PUFs [45], Ring Oscillator PUFs [112], Arbiter PUFs [70] and FPGA specific designs [6, 68, 82]. This work considers PUFs as designs implemented in silicon integrated circuits.

We consider a PUF to be a circuit where two implementations do not exhibit precisely the same behaviour. PUFs provide device-specific output based on inputs received, giving similar (up to a small error rate) responses to repeated challenges and different responses to different challenges [79]. In 2010, Maes and Verbauwhede defined PUFs as *physical challenge-response procedures* [81]. They denoted PUF functionality by:  $\Pi : \mathcal{X} \to \mathcal{Y} :$  $\Pi(x) = y$ , where  $\Pi$  is the PUF instance,  $\mathcal{X}$  and  $\mathcal{Y}$  the input and output spaces in which the input x and output y are defined. Maes and Verbauwhede also listed seven properties defining PUFs. These properties state a PUF must be: Evaluatable, Unique, Reproducible, Unclonable, Unpredictable, One-way and Tamper evident [81]. These properties from Maes and Verbauwhede in [81] will now be described.

- Evaluatable: with the PUF,  $\Pi$  and an input, x, it should be easy to calculate  $y = \Pi(x)$ . This requires that the PUF must be usable in polynomial time [81].

- Unique: each PUF output,  $\Pi(x)$ , should provide some information about the physical entity that contains  $\Pi$ . Each PUF should produce outputs so that given a number of them, they should uniquely identify the entity containing  $\Pi$  [81].

- Reproducible: every time a PUF output, y = Π(x) is computed it should be approximately unchanged, subject to a small error rate. PUFs exploit random characteristics that are often susceptible to noise. However, outputs should be approximately repeatable for the PUF to be useful [81].

- Unclonable: a critical property, it declares that given a PUF, Π, it should be hard to construct a procedure, Γ ≠ Π s.t. ∀x : Γ(x) ≈ Π(x) within a small error rate [81]. Maes and Verbauwhede explicitly emphasise that Γ is a procedure and need not be a hardware function. This is drawn from their defining two types of cloning: mathematical cloning and physical cloning. Mathematical cloning requires an attacker to create a function, f, copying the behaviour of Π subject to error. Whereas, physical

cloning involves creating an alternative physical entity containing a PUF,  $\Pi'$  where  $\Pi' \neq \Pi$ , mimicking  $\Pi$  for all input challenges, subject to error [81].

- Unpredicatable: this requires that given a set Q = (x<sub>i</sub>, y<sub>i</sub> = Π(x<sub>i</sub>)) and an x<sub>c</sub>, s.t. x<sub>c</sub> ∉ Q, the attacker is unable to predict y<sub>c</sub> s.t. y<sub>c</sub> = Π(x<sub>c</sub>). Maes and Verbauwhede connect this property with mathematical uncloneability as follows. If a PUF is predictable, it is possible to create a mathematical clone of the PUF and violate the Unclonability property of the PUF [81].

- One-way: this property is inherited from traditional cryptographic definitions and requires that given a y and a  $\Pi$ , it is hard to find an x s.t.  $\Pi(x) = y$  [81]. This property adds little to the others listed; Maes and Verbauwhede admit to including it only because early PUF literature considered PUFs as physical one-way functions.

- Tamper evident: finally, this property requires that if the physical entity containing a PUF, Π, is interfered with, it will transform Π into a Π' s.t., with a high probability, ∃x ∈ X : Π(x) ≠ Π'(x) excluding error, where (X) is the set of all possible inputs, x [81]. This property is used in many schemes proposed that use PUFs and it relied upon for security by ensuring any attackers attempting to tamper with the device will cause a lasting, and noticeable, impact.

In this work, we assume PUFs behave perfectly and have an error rate of 0%. This means that for a given PUF instance, the same input will always yield the same output. We also assume outputs of PUF instances are high entropy, perfectly unpredictable and unclonable. We assume the PUF is one-way and tamper evident and that we are able to access it efficiently.

#### 2.3.1 PUF Examples

One common PUF design is the SRAM PUF; a simple design using an unmodified SRAM to provide device-unique outputs. A PUF provides an output, in the case of SRAM PUFs the device-specific output is the initial state of the chip. This is usable as a PUF because when an SRAM powers up, the memory cells initialise as either 0s or 1s with bias. The initial value is not set by design but by variations in the cells from the manufacturing process. The SRAM PUF is queried by performing a memory lookup and receiving the

Figure 2.3: An arbiter PUF may include a source, a number of multiplexer switch blocks and a D flip-flop acting as an arbiter.

result of that lookup. This type of PUF has a limited number of challenge/response pairs, so it is classified as a "weak PUF". Note: the term weak does not refer to the security of the design but the number of distinct responses it can provide [45].

Alternatively, there are "strong PUFs" providing a large (exponential) number of challengeresponse pairs. One strong PUF is the arbiter PUF, these require dedicated circuits to provide a PUF output by comparing signal transmission delay between wires of equal length. Theoretically, the wires should exhibit equal delay, however, due to production variations this is not true in reality. In practice, a single source connected to two wires is changed from low to high, the signal travels down the wires to the arbiter which returns a 0 or 1 depending on which signal arrived first. One potential arbiter is a D-type flip-flop with the two wires connected to the data and clock lines. Whichever is set first will determine if a 0 or 1 is output from the flip-flop. A simple arbiter PUF consists of 2N multiplexers connected in two lines from source to arbiter. The path used from source to arbiter is determined by the N-bit input challenge passed bitwise to each pair of multiplexers, when the bit is 1, the wires are crossed over, otherwise they are unchanged. A diagram of an arbiter PUF is shown in Figure 2.3. Due to the input provided to the circuit, an arbiter PUF has  $2^N$  challenge-response pairs making it a strong PUF, even though different challenges are correlated [70, 59].

#### 2.3.1.1 PUF Security

The previous subsection described two different PUF designs to demonstrate examples of how authors have attempted to implement the theoretical model described at the start of this section. One common theme in PUF research however, is the difficulty in creating designs that successfully meet the Unclonablility and Unpredictability properties. A main work studying the security of different PUF designs was published in 2012 by Katzenbeisser et al. [59].

Some recent attacks on PUF designs have made use of machine learning to model the PUF and violate the Unpredictability and Unclonability of designs. Recent works include attacks against Bistable Ring PUFs by Ganji et al. in 2016 [38] and Becker's attack against XOR Arbiter PUFs in 2015 [15].

Other attacks have used less conventional methods to compromise the properties of PUF designs. These include the characterisation attack on Arbiter PUFs demonstrated by Tajik et al. in 2014 that modelled instances using photonic emission analysis [116] and Helfmeier et al. who used Focussed Ion Beam circuit editing to clone an SRAM PUF [48].

#### 2.3.2 PUF Uses

Due to providing device-specific, random outputs, PUFs are an attractive security primitive to designers. Three main applications of PUFs arising in academic literature are: authentication, key generation and preventing counterfeiting.

Strong PUFs offer a set of challenge-response pairs, leading several authors to include them in authentication systems. Like biometrics for humans, a PUF is something a device is and not merely information it knows. Therefore, due to the Uniqueness property identified by Maes and Verbauwhede, a PUF can be used to identify devices uniquely. The authentication system would be intialised by the PUF-equipped device registering a number of challenge-response pairs with the identifier. When the device wishes to identify itself, the identifier would provide it one or more challenges. The device would respond with the PUF response and if these match, the identifier can confirm the identity of the device. If a PUF is Unique, it provides information about the device with each PUF-response. Furthermore, if the PUF is Unpredictable, Unclonable and one-way the identifier can be confident no other PUF, function, or entity would be able to correctly respond to the provided challenges [81]. Examples of PUF-based authentication schemes are found in [104, 89]. PUFs can also provide a device-specific sources of randomness for generating key material. This application mainly relies on the Uniqueness and Reproducibility properties. If a PUF is Unique, the outputs it produces contain information about the identity of the device containing the PUF. This ensures keys generated by the device will exist uniquely for that device. Furthermore, if the outputs are Reproducible, the device need not store key material - the PUF will reproduce keys when required [81]. Many PUF-based key generation schemes exist such as those of Paral and Devadas [97] and Liu et al. [75].

However, PUFs are significant in this thesis due to the intrinsic, device-specific randomness they offer by design. As such, schemes to prevent counterfeiting have been proposed by authors such as Simpson and Schaumont [110] and Guajardo et al. [45]. In their schemes, the authors proposed mechanisms by which hardware and software developers can combine products without exposing their Intellectual Property (IP) to the other party. PUF provided keys ensure IP elements can be decrypted by the target device only and no others devices [110, 45]. In these cases, the properties needed of the PUF are it being Unique, Reproducible, Unclonable and Unpredictable. These ensure the only devices with access to the protected IP are the devices for which use is authorised.

### 2.4 Binding Hardware and Software

Binding hardware and software is a little studied area of information security with three works comprising most of the literature in the area [67, 110, 10]. The major work in the area is a 2003 patent by Krasinski and Rosner proposing a scheme for binding copy protection software to devices to prevent copyright infringement [67]. In academia the most significant papers are by Simpson and Schaumont in 2006 [110] and a later work by Atallah et al. in 2008 [10].

In this thesis, binding hardware and software concerns combining the two elements together. The bond ensures a secure dependency between hardware and software that prevents correct operation if the entities are separated. Software cannot be moved, or copied, from one hardware to another as the removal of the bound hardware will prevent correct execution. For the bound system to correctly function it requires the presence of both correct the hardware and the correct software for the hardware [67, 110, 10]. The bond between hardware and software proposed in previous literature can be divided into two categories: application binding schemes and algorithm binding schemes. This section includes algorithm binding for completeness however the research in this thesis only explores application binding and "Hardware-software binding" and related terms are used to refer to application binding schemes only.

#### 2.4.1 Application Binding

As stated, binding hardware and software concerns securely combining hardware and software together. Application binding creates this bond by attaching an application, or IP, to a specific hardware instance. The schemes proposed by Krasinski and Rosner and also by Simpson and Schaumont are both application binding schemes [67, 110]. In both works, the authors use application binding to provide copy protection by ensuring the bound software cannot be removed from the hardware [67, 110].

Krasinski and Rosner proposed using device specific information to bind copy protection software, required for accessing secured media, to a particular device. Therefore, instead of binding the (much larger) media to the device, the authors could bind just the decoding application to the device. Efforts to move the protected content and thwart the copy protection are prevented because the decoding software is bound to the device using a device-specific key [67].

Similarly, Simpson and Schaumont use a PUF (Section 2.3) to bind third-party IP to the particular FPGA (Section 2.2) that will be hosting it [110]. Their scheme allows system developers to authenticate IP from developers and for IP developers to restrict their technology to authenticated parties. Simpson-Schaumont binding relies on encrypting hardware blocks using device-specific keys derived from PUF outputs. As the key is device-specific, it is not possible for a malicious party to attack the scheme and discover the IP. Simpson and Schaumont use a Trusted Third Party (TTP) to share key information between system and IP developers. Devices enroll keys with the TTP and these are shared securely with the IP developer who encrypts their product knowing that only the intended device may decrypt it. One issue with this scheme is it relies on all developers being honest and not leaking protected IP after decryption. However, a more serious flaw is that, as the scheme is only designed to protect the IP, it offers no protection for the FPGA system against malicious IP or IP added by attackers [110].

#### 2.4.2 Algorithm Binding

Algorithm binding is an alternative method of binding hardware and software. We define it as hardware-software binding using device specific information to bind the software at an algorithm level. This differs from the schemes described in the previous subsection; whereas they take the application and attach it to the device entirely, an algorithm binding scheme ties correct output of the computation to the particular hardware device. The first, published, algorithm binding scheme was proposed in 2008 by Atallah et al. [10].

Atallah et al. also proposed a scheme binding software to a hardware instance to prevent it being transplanted to a different device. The attacks they considered were of software being ran in a virtual environment replicating the behaviour of correct hardware. The authors proposed using hardware-software binding for copy protection and also for securing battlefield applications where rehosting by enemies is a national security threat. Like the Simpson-Schaumont scheme, the Atallah et al. scheme includes a PUF. However, where Simpson and Schaumont proposed binding through device specific encryption, Atallah et al. integrate a PUF result into correct application execution by including a device specific value into the computation. This ensures applications only produce correct answers if they have access to the hardware they are intended to be executed on. Due to the properties of PUFs (Section 2.3), attacks virtualising or emulating hardware are prevented because the virtual PUF will be unable to produce the correct value for the algorithm [10].

The example application Atallah et al. described binding was an implementation of RSA encryption<sup>1</sup>. However, where the encryption was split into two encryptions: one under a modified key and a second using a PUF output,  $R_i$ . The modified key is calculated by multiplying the original key, e, by the inverse of the PUF output<sup>2</sup>,  $R_i^{-1}$  to calculate  $R'_i$ . The modified encryption algorithm is then computed in two stages [10]:

<sup>&</sup>lt;sup>1</sup>However, it would apply to RSA decryption too.

<sup>&</sup>lt;sup>2</sup>Given p and q, calculating the inverse of  $R_i$  is straightforward.

$$\mathsf{Enc}_{R'_i}(m) = m^{R'_i} \mod n$$

$$\mathsf{Enc}_e(m) = \mathsf{Enc}_{R'_i}(m)^{R_i} \mod n = m^{eR_i^{-1}R_i} \mod n = m^e \mod n$$

$$= c.$$

This method ensures that only hardware in possession of the correct PUF can successfully compute the RSA encryption. Therefore, the Atallah et al. scheme creates a secure bond attaching software to a hardware instance at the algorithm level [10]. However, as with the application binding schemes, the Atallah et al. scheme only binds software to hardware. Therefore, it provides no protection to devices from malicious software or from software modification.

#### 2.4.3 Bond Directionality

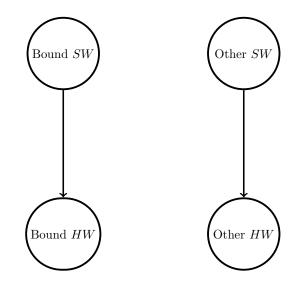

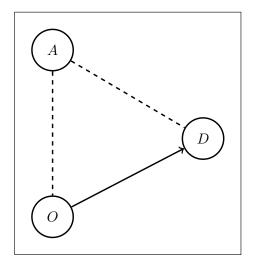

A significant concept in binding hardware and software together is "directionality". In this work, the term "directionality" defines a goal of a hardware-software bond. There are two different directionalities of hardware-software bonds: unidirectionality and bidirectionality. Unidirectional bonds tie one element (hardware or software) to the other element (software or hardware). The previous schemes by Krasinski-Rosner [67], Simpson and Schaumont [110] and Atallah et al. [10], described in this section create unidirectional bonds; the software (or algorithm or IP) is bound to the hardware it is intended for. Unidirectional binding is illustrated in Figure 2.4 where an arrow indicates where a software installation is permitted.

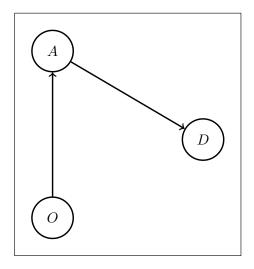

The alternative to unidirectional bonds is bidirectional hardware-software binding where bonds securely connect both elements together. With a bidirectional scheme, a piece of hardware only executes software bound to it *and* software only executes on the hardware it is bound to. The permitted installation combinations of software and hardware when bidirectional-software binding is used are shown in Figure 2.5.

Figure 2.4: Unidirectional binding only restricts one of hardware or software. When only the software is bound, it is restricted to only the hardware it is bonded to whereas the hardware is unrestricted and may execute other software. The same applies in reverse when only the hardware is bound, the hardware is restricted but the software chosen for the hardware is not. Edges between software and hardware indicate permitted installations.

Figure 2.5: Bidirectional binding of hardware and software ensures bound elements cannot be moved onto other devices or installed with alternative software. Edges indicate an allowed installation of software onto hardware.

### 2.5 Secure Application Execution

Secure Application Execution (SAE) concerns ensuring software runs correctly; following a legitimate path through the application without illegitimately avoiding any instructions or functions. A major work in this area is the 2002 paper by Kiriansky et al. who sought to prevent attacks by only allowing legitimate behaviour. Previous works prevented attacks exploiting particular vulnerabilities whereas Kiriansky et al. sought to prevent unauthorised behaviour rather than attacks [62]. Kiriansky et al. did not formally define SAE, instead considering broadly defined exploits comprising three features: a vulnerability exploited, a program address overwritten and some malicious code executed. Their scheme prevents any attacks from executing malicious code after exploiting any vulnerability to divert execution [62]. This is the definition of a Secure Application Execution scheme used in this work.

Similar to Secure Application Execution is Control-Flow Integrity (CFI). While SAE is a goal, CFI is a security property defined by Abadi et al. in 2005 [1]. Ensuring CFI guarantees program execution has followed a legitimate control-flow, or path, through the application. A legitimate execution path starts at the beginning of the application and runs every instruction in the path in sequence through the application until reaching the end. A legitimate sequence may not run all instructions or run instructions in series. Control-flow instructions may be in the sequence diverting execution to reused code or avoiding code not in the current path. Control-flow instructions are those transfering execution to remote instructions and include: JUMP, CALL and RETURN instructions and their conditional variants [1, 2].

This work uses the Kiriansky et al. and Abadi et al. definitions of Secure Application Execution and Control-Flow Integrity as securing the execution of an application to legitimate paths through the application, preventing all others [62, 1, 2].

### 2.5.1 Proposals for Securing Application Execution

Many schemes have been proposed to securely ensure program execution. This section describes the two main types of SAE schemes: software-based and hardware-based schemes. The schemes described are designed to prevent unauthorised behaviour by ensuring SAE.

#### 2.5.1.1 Software-Based Control-Flow Integrity Enforcement

The first software-based scheme is program shepherding, published in 2002, by Kiriansky et al. Program shepherding protects against threats with three techniques: restricting code origins, restricting control transfers and un-circumventable sandboxing. These properties are connected; sandboxing is used to defend the first two techniques securing execution [62].

Program shepherding is a security framework allowing different security levels to be set according to a security policy. In their paper, Kiriansky et al. provided a table detailing different program features and security options for each sorted from least to most restrictive. For example, a non-restrictive policy may allow any indirect call, a maximally restrictive policy may allow none [62].

Kiriansky et al. implemented their scheme by extending an interpreter to allow real-time execution monitoring. When tested, their implementation protected against several known vulnerabilities [62].

Another software-based scheme is inlined CFI enforcement proposed by Abadi et al. in 2005, it is an attack-agnostic method of protecting execution. CFI enforcement limits execution to the Control-Flow Graph (CFG) determined by the software developer [1, 2]. A CFG is a map showing all possible correct paths when executing the program. CFGs can be generated from application binaries, several methods have been proposed (e.g. [23, 117, 61]) but the precise method used is out of the scope of this work.

The CFG considers a program as a set of nodes and transitions. Each transition is the result of a control-flow instruction and each node represents a basic block. Basic blocks are groups of one or more instructions, executed in series, in which only the final instruction may be a control-flow instruction.

Abadi et al. implemented inlined CFI enforcement by labelling each control-flow instruction and their destinations. A control-flow instruction is only permitted if the attached label matches the label of the destination. This prevents attacks transferring control flow to arbitrary locations. The authors implemented their proposal as a tool to rewrite x86 binaries to include the proposed checks. The implementation prevented "jump-to-libc" attacks on tested binaries, but not those manipulating the program to improperly launch other software [1, 2].

#### 2.5.1.2 Hardware-Based CFI Enforcement

Several authors have proposed methods of securing application execution using hardware rather than software extensions. These provide the same level of CFI but with a reduced performance penalty as protections are included in device architecture. One significant hardware-based scheme was proposed by Arora et al. in 2005; using a hardware monitor to ensure execution security. Like Kiriansky et al., Arora et al. proposed a flexible primitive tailorable to the granularity of execution security available. They proposed three security measures of increasing resolution: inter-procedural control-flow, intra-procedural controlflow and integrity of the instructions executed [8].

Inter-procedural control-flow secures flow between different functions of the application. Intra-procedural control-flow checks every control-flow transfer in the application, between basic blocks and function calls. Finally, a running hash computation ensures integrity of instructions executed. The hash values calculated on groups of instructions are compared against stored, precomputed values to ensure correct instructions have been executed [8].

Arora et al. simulated an implementation of their of their proposal to test its performance using SimpleScalar and the PISA architectural simulation toolset [8]. Inter-procedural control-flow checks are facilitated by tables storing function start and return addresses and a finite state machine checking call and return validity. A basic block table was added to check intra-procedural control-flow by tracking control flow within functions. Finally, an instruction buffer and hash engine verify instruction integrity by computing hash values of basic blocks during execution. These values are compared with a column in the basic block table containing expected values. These measures ensure secure application execution at the three levels of granularity proposed [8].

Another hardware-based control flow integrity architecture is SOFIA, proposed by Clercq et al. in 2016 [32], publishing an extended paper in 2017 [31]. Like Arora et al., the authors combined CFI and Software Integrity (SI) protections to ensure correct, unmodified instruction execution. SOFIA includes two main components, encryption and Message Authentication Codes (MACs). To ensure SAE, each instruction is encrypted using a random value, the Program Counter (PC) value of the previous instruction and the PC of the current instruction. This ensures each instruction is encrypted according to its position in the application control-flow, preventing instruction tampering. To ensure SI, as instructions execute they are combined in a runtime MAC compared to a precalculated value to ensure SI [32, 31].

## 2.6 Spectre and Meltdown

Spectre and Meltdown are two significant attacks on modern processors, published in 2018, exploiting optimisation techniques used to improve performance. Both attacks are based on one class of vulnerability and Meltdown is considered a variant of Spectre [64, 74]. The difference between the two is Spectre is effective against processors from Intel, AMD and ARM, whereas Meltdown only effects some Intel devices [64].

To increase performance, modern processors use techniques including branch prediction and speculative execution. These are used when a branch decision is dependent on a memory access. For example, in Figure 2.6,  $\mathbf{x}$  is compared to the **array\_size** stored in memory. In this case, while waiting for the result of the memory access, the processor predicts the boolean statement will be true and proceeds to execute the branch, this is a speculative execution. In this speculative execution the processor continues executing and when the memory access completes, it determines if the current state should be kept (the branch prediction was correct) or rolled back to the state at the branch (if the prediction was wrong). In the latter case execution follows the branch previously not taken requiring any changes from the speculative execution to be undone [64].

If a speculative execution is abandoned, the processor should undo all changes made to ensure correct execution of the other branch. However, in practice, the authors discovered processors detectably affecting the cache during speculative execution. This cache effect is a side channel that authors were able to develop code to exploit and use to leak information about memory contents [64].

In the example given in Figure 2.6, the attacker first trains the CPU to assume the conditional statement will most likely return true. Second, the cache is manipulated

```

if (x < array_size)

y = array2[array1[x] * 256];

```

Figure 2.6: Code designed to improve program security is exploited by Spectre. Example code copied from [64].

to exclude  $array\_size$ . Therefore, when executed, the code will start to perform the comparison and while waiting for the memory access to complete, it speculatively executes the if-true condition. The value x and the address of array1 are added and the content of that location read to discover the secret byte k. This k is used to form a memory access in array2. When  $array\_size$  is read from memory, the speculative execution is declared erroneous and the register states are rewound. However, the speculated read of array2 affects the cache by moving the value read into cache space. The attack is completed by testing the cache to determine the address accessed by the speculative read, the index accessed with the lowest latency is k [64].

These attacks have prompted the discovery of similar attacks on Intel SGX [21], virtual memory [47] and cryptographic key generation [4]. However, these cache-based sidechannel attacks are considered outside of the scope of this work and have been included for completeness only.

## 2.7 Formal Analysis

Formal analysis, also known as symbolic, automatic or mechanical analysis involves using software tools to analyse protocols. In formally analysing a protocol, a model of the protocol is used by the tool to reason about the scheme. From the model, analysis tools perform detailed analysis of the protocol and can find attacks missed by human analysis [28].

One difference between human and formal analysis is analysis tools usually consider all cryptographic primitives to be completely secure, this is called the Dolev-Yao model. In this model, the attacker can intercept all messages but not break any cryptographic functions. Analysis tools search for protocol logic flaws allowing attackers to violate security properties. This search is carried out differently in different tools. Some tools test common security features of protocols, others allow the user to define properties [28].

Many tools exist for protocol analysis including Casper FDR [76], Scyther [27] and Tamarin [91]. Different tools have different strengths and weaknesses studied by multiple authors [20, 28, 98]. However, the merits of different tools is not the focus of this research and will not be discussed in detail.

In this work, Tamarin prover ([91]) is used to analyse protocols. Like Scyther, Tamarin uses backwards search to explore the protocol space. Protocols are specified with multi-set rewriting rules and properties by guarded first-order logic. This tool was chosen due to its accurate modelling of Diffie-Hellman Key Exchange, a featured used in all protocols proposed. Furthermore, proving properties is greatly aided by the Tamrin interactive proof mode [91].

# **Binding Hardware and Software**

#### Contents

| 3.1        | Introduction           |

|------------|------------------------|

| 3.2        | Problem Description 41 |

| 3.3        | Related Work           |

| <b>3.4</b> | Proposed Solution      |

| 3.5        | Implementation         |

| <b>3.6</b> | Conclusion             |