# High-speed hybrid III-V-ON-SI vertical cavity lasers

**Topic**, Vladimir

Publication date: 2019

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

*Citation (APA):* Topic, V. (2019). High-speed hybrid III-V-ON-SI vertical cavity lasers. Technical University of Denmark.

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# HIGH-SPEED HYBRID III-V-ON-SI VERTICAL CAVITY LASERS

# Vladimir Topić

A thesis submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Department of Photonics Engineering Technical University of Denmark

February 2019

| Project period:          | March 2015 - February 2019                                                                                                                                                                                                   |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Project funding:         | Innovation Fund Denmark<br>HOT project (Grant No. 5106-00013B)                                                                                                                                                               |

| Main supervisor:         | Associate Professor Il-Sug Chung                                                                                                                                                                                             |

| Co-supervisor:           | Dr. Luisa Ottaviano                                                                                                                                                                                                          |

| Ph.D. defense date:      | 28 <sup>th</sup> May 2019                                                                                                                                                                                                    |

| Ph.D. defense committee: | <ul> <li>Associate Professor Kresten Yvind, Technical University of<br/>Denmark, Denmark</li> <li>Dr. Dan Birkedal, Alight Technologies, Denmark</li> <li>Ingénieur chercheur Badhise Ben Bakir, CEA-Leti, France</li> </ul> |

# Abstract

Vertical cavity lasers (VCLs) are the dominating laser type for the short-reach fiber optical links, with rising interest in employing them across the wider range of optical interconnects. From micrometer length links in silicon (Si) photonics to long distance fiber links in mega data centers, the VCLs lasing at long wavelengths could satisfy the rising requirements for the high power efficiency and modulation speed.

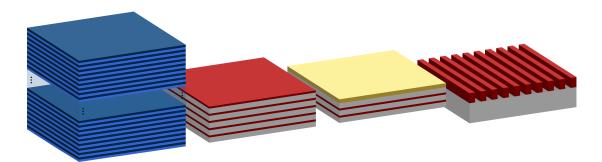

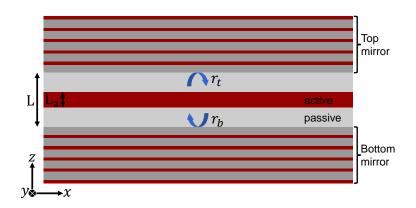

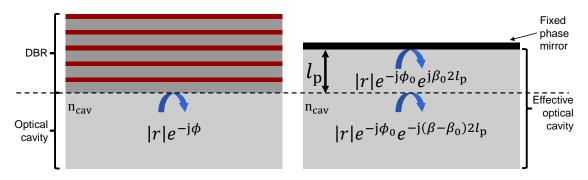

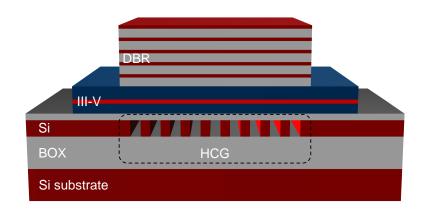

A novel design of hybrid III-V-on-Si VCLs is investigated in this thesis. It employs a highindex-contrast grating (HCG) as one mirror and dielectric distributed Bragg reflector (DBR) as second mirror to achieve very compact optical mode volume which results in potentially ultra-high intrinsic bandwidth. The aim of this work is the experimental demonstration of the electrically pumped VCLs based on this design.

The first part of this thesis deals with the design of the proposed lasers. The theoretical background of the HCG is given, focusing on its application as a compact broadband reflector. Basic theory of the dynamic properties of the laser and the optimization of the design for the high modulation speeds is explained. The key features of the electrically pumped design are discussed, focusing on minimizing the parasitic elements. The methods of achieving current confinement, using proton implantation and selective undercut etching, are investigated. The low-resistance ohmic contacts are optimized to avoid deep metal diffusion.

The complete fabrication of proposed laser design is discussed and presented in the second part of the thesis. The wafer bonding for integrating III-V layers onto a SOI wafer has been one of the main fabrication challenges. To solve it, the adhesive bonding method using ultra-thin polymer layers has been successfully implemented and optimized. The complete fabrication procedure for the hybrid VCLs has been developed using CMOS-compatible processes.

In the third part, the fabrication and characterization of several versions of VCLs is presented. Considerable efforts have been put in to demonstrate lasing; however, due to numerous fabrication obstacles this was not achieved. The first fabricated lasers showed no light emission due to issues with the epitaxy design. The poor wafer quality of the second epitaxy caused deviations during fabrication and low yield. The final fabricated design showed better properties, although the lasing was not reached due to too high threshold. The results of the experimental work are discussed focusing on prospects of optimizing the device design and fabrication to achieve successful demonstration of high-speed lasers.

# Resumé

Vertikale kavitetslasere (VKL) er den dominerende laser type når det kommer til kort-rækkevidde optiske forbindelser, med stigende interesse i anvendelse til en bred række af optiske forbindelseselementer. Fra mikrometerskala i silicium (Si) fotonik til fiberkoblinger over lange afstande i mega data centre, kan VKL lasere ved en lang bølgelængde indfri de stigende krav til høj ydeevne og modulationshastighed.

Et nyt design af hybrid III-V-på-Si VKL undersøges i denne afhandling. Den anvender et højt indekskontrast gitter (HKG) som det ene spejl og en dielektrisk distribueret Bragg reflektor (DBR) som det andet spejl til at opnå en meget kompakt optisk mode-volumen der resulterer i en potentiel ultra høj intrinsisk båndbredde. Målet for dette arbejde er at eksperimentelt demonstrere en elektrisk pumpet VKL baseret på dette design.

Den første del af afhandling gennemgår designet af foreslåede lasere. Den teoretiske baggrund for HKG gives, med fokus på dens anvendelse som en bredbåndsreflektor. Basal teori omkring de dynamiske egenskaber af lasere præsenteres og optimeringen af design for at opnå høj modulationshastighed gennemgås. Nøgleegenskaberne af et elektrisk pumpet design diskuteres med fokus på a minimere parasitære elementer. Metoderne til opnåelse af ladningsbærerindespærring ved brug af fotonimplantation og selektiv underskåret ætsning undersøges. De ohmiske kontakter med lav modstand optimeres for at undgå en dyb diffusion af metal.

Hele fabrikationsprocessen af det foreslåede laser design præsenteres og diskuteres i afhandlingens anden del. Waferbinding for at integrere III-V lag på en SOI wafer har været en af hovedudfordringerne i fabrikationen. For at løse denne udfordring er en klæbende bindingsmetode med brug af ultra tynde polymer lag blevet implementeret of optimeret. Hele fabrikationsprocessen for hybrid VKL er udviklet med CMOS kompatible processer.

I tredje del præsenteres fabrikationen og karakteriseringen af adskillige versioner af VKL. Betydelige bestræbelser har gået til at demonstrere lasing. Dette er imidlertid ikke opnået på grund af talrige fabrikationshindringer. De første fremstillede lasere viste ingen lysemission pga. problemer med epitaxidesignet. Den lave waferkvalitet ved den anden epitaxi medførte variationer underfabrikation og et lavt udbytte. Det endelige fabrikationsdesign viste bedre egenskaber men lasing ikke blev opnået på grund af en for højt tærskel. Resultaterne af det eksperimentelle arbejde diskuteres med fokus på udsigterne til at optimere enhedsdesignet og fabrikationen så højhastighedslasere succesfuldt kan demonstreres.

# Preface

This thesis is submitted to the Department of Photonics Engineering at Technical University of Denmark (DTU) for the partial fulfillment of the requirements for the degree of Doctor of Philosophy (Ph.D.). The work presented here is part of the Ph.D. project which was carried out in the Quantum and Laser Photonics group from March 15th, 2015 to February 14th 2019. The project has been supervised by main supervisor Assoc. Prof. Il-Sug Chung, and co-supervisor Dr. Luisa Ottaviano.

The Ph.D. project was mainly financed by the Department of Photonics Engineering at Technical University of Denmark (DTU) and Innovation Fund Denmark through the HOT project (Grant No. 5106-00013B).

# Acknowledgements

First and foremost, I would like to thank my supervisor Il-Sug Chung for giving me the opportunity to work on such an exciting and challenging project. I am grateful for his guidance, support, endless patience and inspiring perseverance. I would like to thank also my co-supervisor Luisa Ottaviano for sharing her expertise in cleanroom fabrication, as well as her understanding, support and friendship during difficult times.

A special thanks to Gyeong Cheol Park for being my unofficial mentor in cleanroom and for sharing his experience in characterization. Also, I am thankful to my teammate Sushil Tandukar, who worked side by side with me, for sharing all the ideas and experiences. Their involvement has been invaluable, and I wish to acknowledge their contribution in development of many fabrication processes used in this work. To Alireza Taghizadeh I thank for the discussions and sharing his knowledge on the theory behind this work. I would like to thank Kresten Yvind for helping me with characterization setup and for sharing his experience on laser physics and characterization.

Furthermore, I wish to thank all my colleagues in Quantum and Laser Photonics group and Nanophotonic Devices group for creating a fruitful and collaborative working atmosphere, all the constructive feedback, knowledge sharing and discussions, both inside and outside the cleanroom. Special thanks to Kristoffer Skaftved Mathiesen for help with the Danish translation of the abstract for this work. Additionally, I would also like to thank DTU Danchip staff for their expertise, help and support in the cleanroom.

I wish to acknowledge the Innovation Fund Denmark for funding the Ph.D. project, and the Otto Mønsteds Fond for economical support towards conference participation.

I will be forever grateful to my dear friends for always believing in me, pushing me further and being greatest inspiration in my life. A special thanks to my girlfriend for all the love, patience and encouragement in this difficult period. Last but not least, my deepest gratitude goes to my family for their continued encouragement throughout my life and for being there for me with unconditional love and support.

> Vladimir Topić DTU, Kongens Lyngby February 2019

# Contents

| RESUMÉ       iii         PREFACE       v         ACKNOWLEDGEMENTS       vii         CONTENTS       ix         1       INTRODUCTION       1         1.1.1       Motivation       1         1.1.2       Limits of electrical interconnects       2         1.1.3       Potential of optical interconnects       2         1.1.4       Silicon photonics       3         1.2       Lasers for silicon photonics       3         1.3       Recent progress of VCSELs       6         1.3.1       Short-wavelength VCSELs       6         1.3.2       Long-wavelength VCSELs       6         1.3.3       HOC and hybrid VCSELs       7         1.3.3       HOC and outline       10         1.4.1       Subject and contribution of the thesis       10         1.4.2       Structure of the thesis       11         2       THEORY AND OPTICAL DESIGN       13         2.1       High-index-contrast grating       13         2.2.1       Subwavelength gratings       14         2.2.2       High-index-contrast of HCGs       22         2.3       Mirrors for LW-VCSELS       23         2.3       Optical and ener                                                                                             | Aı | BSTRA | ACT                                   | i            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------|---------------------------------------|--------------|

| ACKNOWLEDGEMENTS       vii         CONTENTS       ix         1       INTRODUCTION       1         1.1.1       Optical interconnects       1         1.1.2       Limits of electrical interconnects       2         1.1.3       Potential of optical interconnects       2         1.1.4       Silicon photonics       3         1.2       Lasers for silicon photonics       3         1.3       Recent progress of VCSELs       6         1.3.1       Short-wavelength VCSELs       6         1.3.2       Long-wavelength VCSELs       6         1.3.3       HCG and hybrid VCSELs       7         1.3.3       HCG and hybrid VCSELs       8         1.4       Thesis contribution and outline       10         1.4.1       Subject and contribution of the thesis       10         1.4.2       Structure of the thesis       11         2       THEORY AND OPTICAL DESIGN       13         2.1       Introduction       13         2.2.1       Subwavelength gratings       14         2.2.2       HCG as a broadband reflector       17         2.3.3       Other applications of HCGs       22         2.3.1       Mirrors for LV-VCSELS                                                                   | Rı | ESUMI | É                                     | iii          |

| CONTENTS       ix         1 INTRODUCTION       1         1.1 Optical interconnects       1         1.1.1 Motivation       1         1.1.2 Limits of electrical interconnects       2         1.1.3 Potential of optical interconnects       2         1.1.4 Silicon photonics       3         1.2 Lasers for silicon photonics       3         1.3 Recent progress of VCSELs       6         1.3.1 Short-wavelength VCSELs       6         1.3.2 Long-wavelength VCSELs       7         1.3.3 HCG and hybrid VCSELs       8         1.4 Thesis contribution and outline       10         1.4.1 Subject and contribution of the thesis       10         1.4.2 Structure of the thesis       11         2 THEORY AND OPTICAL DESIGN       13         2.1 Introduction       13         2.2.1 Subwavelength gratings       14         2.2.2 HCG as a broadband reflector       17         2.3.3 Other applications of HCGs       22         2.3.1 Mirrors for LW-VCSELS       23         2.3.2 Phase and energy penetration depth       25         2.3.3 Comparison of TE and TM HCG designs       30         2.4.1 Intrinsic modulation response       33         2.4.2 Controlling the photon lifetime       37 | PI | REFAC | CE                                    | $\mathbf{v}$ |

| 1       INTRODUCTION       1         1.1       Optical interconnects       1         1.1.1       Motivation       1         1.1.2       Limits of electrical interconnects       2         1.1.3       Potential of optical interconnects       2         1.1.4       Silicon photonics       3         1.2       Lasers for silicon photonics       3         1.3       Recent progress of VCSELs       6         1.3.1       Short-wavelength VCSELs       6         1.3.2       Long-wavelength VCSELs       7         1.3.3       HCG and hybrid VCSELs       7         1.3.4       Thesis contribution and outline       10         1.4.1       Subject and contribution of the thesis       10         1.4.2       Structure of the thesis       11         2       THEORY AND OPTICAL DESIGN       13         2.1       Introduction       13         2.2.1       Subwavelength gratings       14         2.2.2       HCG as a broadband reflector       17         2.2.3       Other applications of HCGs       22         2.3.1       Mirrors for UN-VCSELS       23         2.3.2       Phase and energy penetration depth       25                                                                  | A  | CKNO  | WLEDGEMENTS                           | vii          |

| 1.1       Optical interconnects       1         1.1.1       Motivation       1         1.1.2       Limits of electrical interconnects       2         1.1.3       Potential of optical interconnects       2         1.1.4       Silicon photonics       3         1.2       Lasers for silicon photonics       3         1.3       Recent progress of VCSELs       6         1.3.1       Short-wavelength VCSELs       6         1.3.2       Long-wavelength VCSELs       7         1.3.3       HCG and hybrid VCSELs       8         1.4       Thesis contribution and outline       10         1.4.1       Subject and contribution of the thesis       10         1.4.1       Subject and contribution of the thesis       11         2       THEORY AND OPTICAL DESIGN       13         2.1       Introduction       13         2.2       HIgh-index-contrast grating       13         2.2.1       Subwavelength gratings       14         2.2.3       Other applications of HCGs       22         2.3       Mirrors for VCSELs       23         2.3.2       Phase and energy penetration depth       25         2.3.3       Comparison of TE and TM HCG designs<                                         | Co | ONTE  | NTS                                   | ix           |

| 1.1       Optical interconnects       1         1.1.1       Motivation       1         1.1.2       Limits of electrical interconnects       2         1.1.3       Potential of optical interconnects       2         1.1.4       Silicon photonics       3         1.2       Lasers for silicon photonics       3         1.3       Recent progress of VCSELs       6         1.3.1       Short-wavelength VCSELs       6         1.3.2       Long-wavelength VCSELs       7         1.3.3       HCG and hybrid VCSELs       8         1.4       Thesis contribution and outline       10         1.4.1       Subject and contribution of the thesis       10         1.4.1       Subject and contribution of the thesis       11         2       THEORY AND OPTICAL DESIGN       13         2.1       Introduction       13         2.2       High-index-contrast grating       13         2.2.1       Subwavelength gratings       14         2.2.3       Other applications of HCGs       22         2.3       Mirrors for VCSELs       23         2.3.2       Phase and energy penetration depth       25         2.3.3       Comparison of TE and TM HCG designs<                                         | 1  | Ιντι  | RODUCTION                             | 1            |

| 1.1.1       Motivation       1         1.1.2       Limits of electrical interconnects       2         1.1.3       Potential of optical interconnects       2         1.1.4       Silicon photonics       3         1.2       Lasers for silicon photonics       3         1.3       Recent progress of VCSELs       6         1.3.1       Short-wavelength VCSELs       6         1.3.2       Long-wavelength VCSELs       7         1.3.3       HCG and hybrid VCSELs       8         1.4       Thesis contribution and outline       10         1.4.1       Subject and contribution of the thesis       10         1.4.2       Structure of the thesis       11         2       THEORY AND OPTICAL DESIGN       13         2.1       Introduction       13         2.2.1       Subwavelength gratings       14         2.2.2       HCG as a broadband reflector       17         2.2.3       Other applications of HCGs       22         2.3       Mirrors for VCSELs       23         2.3.2       Phase and energy penetration depth       25         2.3.3       Comparison of TE and TM HCG designs       30         2.4       Designing a high-speed VCSEL                                              |    |       |                                       |              |

| 1.1.2       Limits of electrical interconnects       2         1.1.3       Potential of optical interconnects       2         1.1.4       Silicon photonics       3         1.2       Lasers for silicon photonics       3         1.3       Recent progress of VCSELs       6         1.3.1       Short-wavelength VCSELs       6         1.3.2       Long-wavelength VCSELs       7         1.3.3       HCG and hybrid VCSELs       7         1.3.3       HCG and hybrid VCSELs       8         1.4       Thesis contribution and outline       10         1.4.1       Subject and contribution of the thesis       10         1.4.2       Structure of the thesis       11         2       THEORY AND OPTICAL DESIGN       13         2.1       Introduction       13         2.2.1       Subwavelength gratings       14         2.2.2       HCG as a broadband reflector       17         2.2.3       Other applications of HCGs       22         2.3       Mirrors for UW-VCSELS       23         2.3.2       Phase and energy penetration depth       25         2.3.3       Comparison of TE and TM HCG designs       30         2.4       Designing a high-sp                                         |    | 1.1   | *                                     |              |

| 1.1.3       Potential of optical interconnects       2         1.1.4       Silicon photonics       3         1.2       Lasers for silicon photonics       3         1.3       Recent progress of VCSELs       6         1.3.1       Short-wavelength VCSELs       6         1.3.2       Long-wavelength VCSELs       7         1.3.3       HCG and hybrid VCSELs       7         1.3.4       Thesis contribution and outline       10         1.4.1       Subject and contribution of the thesis       10         1.4.2       Structure of the thesis       11         2       THEORY AND OPTICAL DESIGN       13         2.1       Introduction       13         2.2.1       Subwavelength gratings       14         2.2.2       HCG as a broadband reflector       17         2.3.3       Other applications of HCGs       22         2.3.1       Mirrors for LW-VCSELS       23         2.3.2       Phase and energy penetration depth       25         2.3.3       Comparison of TE and TM HCG designs       30         2.4.1       Intrinsic modulation response       33         2.4.2       Controlling the photon lifetime       37                                                                    |    |       |                                       |              |

| 1.1.4       Silicon photonics       3         1.2       Lasers for silicon photonics       3         1.3       Recent progress of VCSELs       6         1.3.1       Short-wavelength VCSELs       6         1.3.2       Long-wavelength VCSELs       6         1.3.3       HCG and hybrid VCSELs       7         1.3.3       HCG and outline       10         1.4.1       Subject and contribution of the thesis       10         1.4.2       Structure of the thesis       11         2       THEORY AND OPTICAL DESIGN       13         2.1       Introduction       13         2.2.1       Subwavelength gratings       14         2.2.2       HCG as a broadband reflector       17         2.2.3       Other applications of HCGs       22         2.3       Mirrors for UW-VCSELS       23         2.3.1       Mirrors for LW-VCSELS       23         2.3.2       Phase and energy penetration depth       25         2.3.3       Comparison of TE and TM HCG designs       30         2.4       Designing a high-speed VCSEL       33         2.4.1       Intrinsic modulation response       33         2.4.2       Controlling the photon lifetime                                                   |    |       |                                       |              |

| 1.2       Lasers for silicon photonics       3         1.3       Recent progress of VCSELs       6         1.3.1       Short-wavelength VCSELs       6         1.3.2       Long-wavelength VCSELs       7         1.3.3       HCG and hybrid VCSELs       7         1.3.3       HCG and hybrid VCSELs       8         1.4       Thesis contribution and outline       10         1.4.1       Subject and contribution of the thesis       10         1.4.2       Structure of the thesis       10         1.4.2       Structure of the thesis       11         2       THEORY AND OPTICAL DESIGN       13         2.1       Introduction       13         2.2.1       Subwavelength gratings       14         2.2.2       HCG as a broadband reflector       17         2.2.3       Other applications of HCGs       22         2.3       Mirrors for VCSELs       23         2.3.1       Mirrors for LW-VCSELS       23         2.3.2       Phase and energy penetration depth       25         2.3.3       Comparison of TE and TM HCG designs       30         2.4       Designing a high-speed VCSEL       33         2.4.1       Intrinsic modulation response <td></td> <td></td> <td></td> <td></td>    |    |       |                                       |              |

| 1.3       Recent progress of VCSELs       6         1.3.1       Short-wavelength VCSELs       6         1.3.2       Long-wavelength VCSELs       7         1.3.3       HCG and hybrid VCSELs       7         1.3.3       HCG and hybrid VCSELs       8         1.4       Thesis contribution and outline       10         1.4.1       Subject and contribution of the thesis       10         1.4.2       Structure of the thesis       10         1.4.2       Structure of the thesis       11         2       THEORY AND OPTICAL DESIGN       13         2.1       Introduction       13         2.2.1       Subwavelength gratings       14         2.2.2       HCG as a broadband reflector       17         2.2.3       Other applications of HCGs       22         2.3       Mirrors for VCSELs       23         2.3.1       Mirrors for LW-VCSELS       23         2.3.2       Phase and energy penetration depth       25         2.3.3       Comparison of TE and TM HCG designs       30         2.4       Designing a high-speed VCSEL       33         2.4.1       Intrinsic modulation response       33         2.4.2       Controlling the photon lifet                                         |    | 1.0   |                                       |              |

| 1.3.1       Short-wavelength VCSELs       6         1.3.2       Long-wavelength VCSELs       7         1.3.3       HCG and hybrid VCSELs       8         1.4       Thesis contribution and outline       10         1.4.1       Subject and contribution of the thesis       10         1.4.2       Structure of the thesis       10         1.4.2       Structure of the thesis       11         2       THEORY AND OPTICAL DESIGN       13         2.1       Introduction       13         2.2       High-index-contrast grating       13         2.2.1       Subwavelength gratings       14         2.2.2       HCG as a broadband reflector       17         2.3       Other applications of HCGs       22         2.3.1       Mirrors for VCSELs       23         2.3.2       Phase and energy penetration depth       25         2.3.3       Comparison of TE and TM HCG designs       30         2.4       Designing a high-speed VCSEL       33         2.4.1       Intrinsic modulation response       33         2.4.2       Controlling the photon lifetime       37                                                                                                                               |    |       |                                       |              |

| 1.3.2       Long-wavelength VCSELs       7         1.3.3       HCG and hybrid VCSELs       8         1.4       Thesis contribution and outline       10         1.4.1       Subject and contribution of the thesis       10         1.4.2       Structure of the thesis       10         1.4.2       Structure of the thesis       11         2       THEORY AND OPTICAL DESIGN       13         2.1       Introduction       13         2.2       High-index-contrast grating       13         2.2.1       Subwavelength gratings       14         2.2.2       HCG as a broadband reflector       17         2.2.3       Other applications of HCGs       22         2.3.1       Mirrors for VCSELs       23         2.3.2       Phase and energy penetration depth       25         2.3.3       Comparison of TE and TM HCG designs       30         2.4       Designing a high-speed VCSEL       33         2.4.1       Intrinsic modulation response       33         2.4.2       Controlling the photon lifetime       37                                                                                                                                                                                 |    | 1.3   | 1 0                                   |              |

| 1.3.3       HCG and hybrid VCSELs       8         1.4       Thesis contribution and outline       10         1.4.1       Subject and contribution of the thesis       10         1.4.2       Structure of the thesis       10         1.4.2       Structure of the thesis       11         2       THEORY AND OPTICAL DESIGN       13         2.1       Introduction       13         2.2       High-index-contrast grating       13         2.2.1       Subwavelength gratings       14         2.2.2       HCG as a broadband reflector       17         2.2.3       Other applications of HCGs       22         2.3.1       Mirrors for VCSELs       23         2.3.2       Phase and energy penetration depth       25         2.3.3       Comparison of TE and TM HCG designs       30         2.4       Designing a high-speed VCSEL       33         2.4.1       Intrinsic modulation response       33         2.4.2       Controlling the photon lifetime       37                                                                                                                                                                                                                                    |    |       | S S S S S S S S S S S S S S S S S S S |              |

| 1.4Thesis contribution and outline101.4.1Subject and contribution of the thesis101.4.2Structure of the thesis112THEORY AND OPTICAL DESIGN132.1Introduction132.2High-index-contrast grating132.2.1Subwavelength gratings142.2.2HCG as a broadband reflector172.2.3Other applications of HCGs222.3Mirrors for VCSELs232.3.1Mirrors for LW-VCSELS232.3.2Phase and energy penetration depth252.3.3Comparison of TE and TM HCG designs302.4Designing a high-speed VCSEL332.4.1Intrinsic modulation response332.4.2Controlling the photon lifetime37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |       |                                       | •            |

| 1.4.1Subject and contribution of the thesis101.4.2Structure of the thesis112THEORY AND OPTICAL DESIGN132.1Introduction132.2High-index-contrast grating132.2.1Subwavelength gratings142.2.2HCG as a broadband reflector172.2.3Other applications of HCGs222.3Mirrors for VCSELs222.3.1Mirrors for LW-VCSELS232.3.2Phase and energy penetration depth252.3.3Comparison of TE and TM HCG designs302.4Designing a high-speed VCSEL332.4.1Intrinsic modulation response332.4.2Controlling the photon lifetime37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |       |                                       |              |

| 1.4.2Structure of the thesis112THEORY AND OPTICAL DESIGN132.1Introduction132.2High-index-contrast grating132.2.1Subwavelength gratings142.2.2HCG as a broadband reflector172.2.3Other applications of HCGs222.3Mirrors for VCSELs222.3.1Mirrors for LW-VCSELS232.3.2Phase and energy penetration depth252.3.3Comparison of TE and TM HCG designs302.4Designing a high-speed VCSEL332.4.1Intrinsic modulation response332.4.2Controlling the photon lifetime37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 1.4   |                                       | -            |

| 2       THEORY AND OPTICAL DESIGN       13         2.1       Introduction       13         2.2       High-index-contrast grating       13         2.2.1       Subwavelength gratings       14         2.2.2       HCG as a broadband reflector       17         2.2.3       Other applications of HCGs       22         2.3       Mirrors for VCSELs       22         2.3.1       Mirrors for LW-VCSELS       23         2.3.2       Phase and energy penetration depth       25         2.3.3       Comparison of TE and TM HCG designs       30         2.4       Designing a high-speed VCSEL       33         2.4.1       Intrinsic modulation response       33         2.4.2       Controlling the photon lifetime       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |       |                                       | 10           |

| 2.1       Introduction       13         2.2       High-index-contrast grating       13         2.2.1       Subwavelength gratings       14         2.2.2       HCG as a broadband reflector       17         2.2.3       Other applications of HCGs       22         2.3       Mirrors for VCSELs       22         2.3.1       Mirrors for LW-VCSELS       23         2.3.2       Phase and energy penetration depth       25         2.3.3       Comparison of TE and TM HCG designs       30         2.4       Designing a high-speed VCSEL       33         2.4.1       Intrinsic modulation response       33         2.4.2       Controlling the photon lifetime       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |       | 1.4.2 Structure of the thesis         | 11           |

| 2.2High-index-contrast grating132.2.1Subwavelength gratings142.2.2HCG as a broadband reflector172.2.3Other applications of HCGs222.3Mirrors for VCSELs222.3.1Mirrors for LW-VCSELS232.3.2Phase and energy penetration depth252.3.3Comparison of TE and TM HCG designs302.4Designing a high-speed VCSEL332.4.1Intrinsic modulation response332.4.2Controlling the photon lifetime37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2  | THE   | CORY AND OPTICAL DESIGN               | 13           |

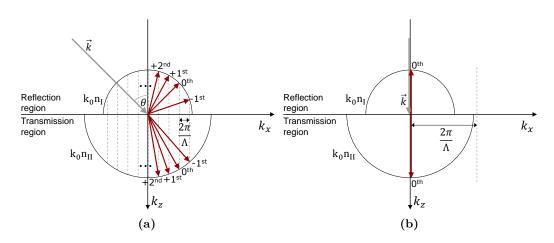

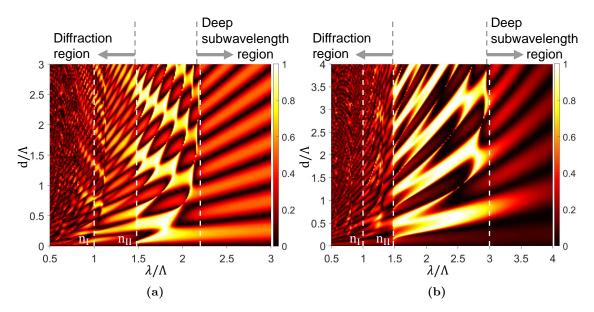

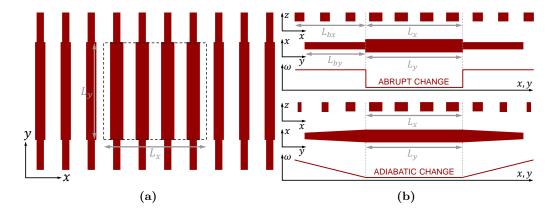

| 2.2.1Subwavelength gratings142.2.2HCG as a broadband reflector172.2.3Other applications of HCGs222.3Mirrors for VCSELs222.3.1Mirrors for LW-VCSELS232.3.2Phase and energy penetration depth252.3.3Comparison of TE and TM HCG designs302.4Designing a high-speed VCSEL332.4.1Intrinsic modulation response332.4.2Controlling the photon lifetime37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 2.1   | Introduction                          | 13           |

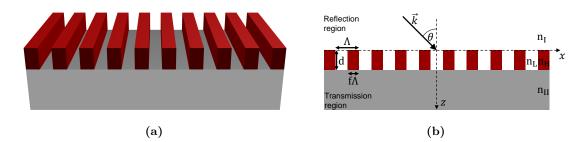

| 2.2.1Subwavelength gratings142.2.2HCG as a broadband reflector172.2.3Other applications of HCGs222.3Mirrors for VCSELs222.3.1Mirrors for LW-VCSELS232.3.2Phase and energy penetration depth252.3.3Comparison of TE and TM HCG designs302.4Designing a high-speed VCSEL332.4.1Intrinsic modulation response332.4.2Controlling the photon lifetime37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 2.2   | High-index-contrast grating           | 13           |

| 2.2.3 Other applications of HCGs222.3 Mirrors for VCSELs222.3.1 Mirrors for LW-VCSELS232.3.2 Phase and energy penetration depth252.3.3 Comparison of TE and TM HCG designs302.4 Designing a high-speed VCSEL332.4.1 Intrinsic modulation response332.4.2 Controlling the photon lifetime37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |       |                                       | 14           |

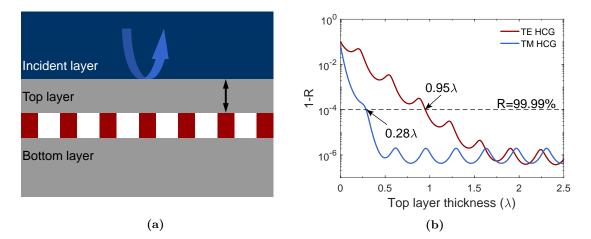

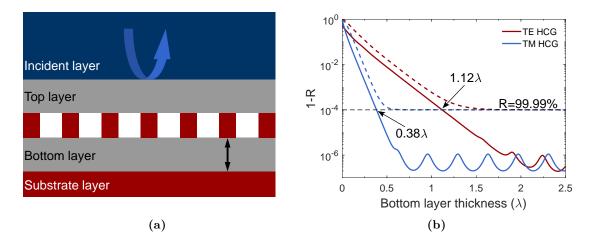

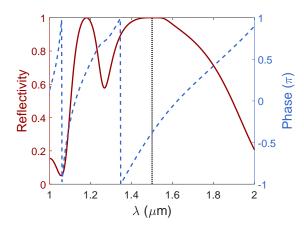

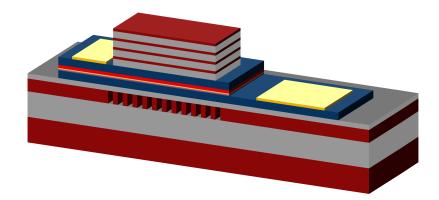

| 2.3 Mirrors for VCSELs       22         2.3.1 Mirrors for LW-VCSELS       23         2.3.2 Phase and energy penetration depth       25         2.3.3 Comparison of TE and TM HCG designs       30         2.4 Designing a high-speed VCSEL       33         2.4.1 Intrinsic modulation response       33         2.4.2 Controlling the photon lifetime       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       | 2.2.2 HCG as a broadband reflector    | 17           |

| 2.3.1Mirrors for LW-VCSELS232.3.2Phase and energy penetration depth252.3.3Comparison of TE and TM HCG designs302.4Designing a high-speed VCSEL332.4.1Intrinsic modulation response332.4.2Controlling the photon lifetime37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |       | 2.2.3 Other applications of HCGs      | 22           |

| 2.3.1Mirrors for LW-VCSELS232.3.2Phase and energy penetration depth252.3.3Comparison of TE and TM HCG designs302.4Designing a high-speed VCSEL332.4.1Intrinsic modulation response332.4.2Controlling the photon lifetime37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 2.3   | Mirrors for VCSELs                    | 22           |

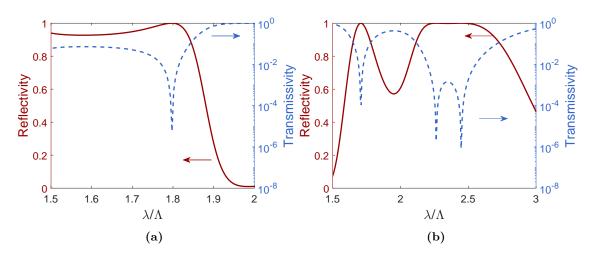

| 2.3.2Phase and energy penetration depth252.3.3Comparison of TE and TM HCG designs302.4Designing a high-speed VCSEL332.4.1Intrinsic modulation response332.4.2Controlling the photon lifetime37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | _     |                                       |              |

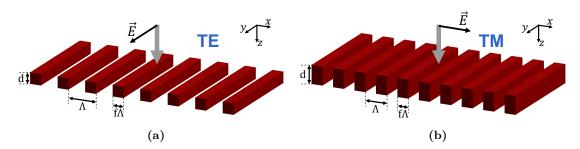

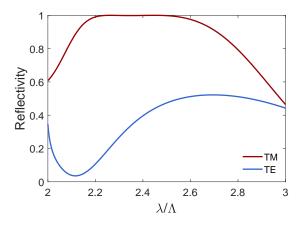

| 2.3.3       Comparison of TE and TM HCG designs       30         2.4       Designing a high-speed VCSEL       33         2.4.1       Intrinsic modulation response       33         2.4.2       Controlling the photon lifetime       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |       |                                       |              |

| 2.4 Designing a high-speed VCSEL       33         2.4.1 Intrinsic modulation response       33         2.4.2 Controlling the photon lifetime       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |       |                                       |              |

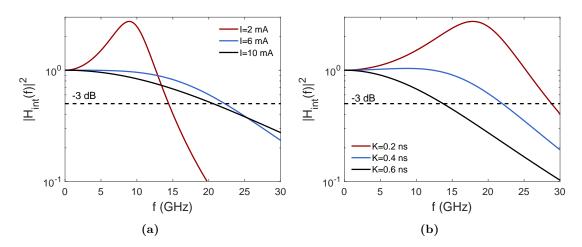

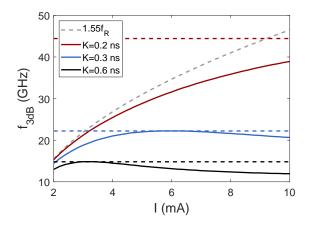

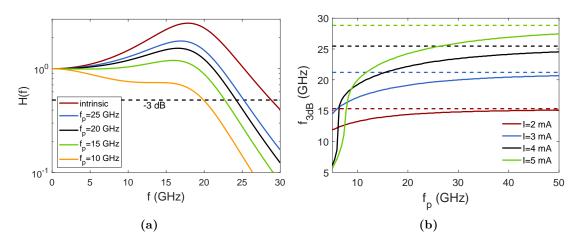

| 2.4.1Intrinsic modulation response332.4.2Controlling the photon lifetime37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 2.4   |                                       |              |

| 2.4.2 Controlling the photon lifetime                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 4.7   |                                       |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |                                       |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |                                       |              |

|   | 2.5 | 2.4.4       Chosen design       40         Summary       41         |  |  |  |  |  |  |  |

|---|-----|---------------------------------------------------------------------|--|--|--|--|--|--|--|

| 3 | Ele | ELECTRICAL PUMPING OF VCSELS 43                                     |  |  |  |  |  |  |  |

|   | 3.1 | Introduction                                                        |  |  |  |  |  |  |  |

|   | 3.2 | Electrical pumping for high-speed                                   |  |  |  |  |  |  |  |

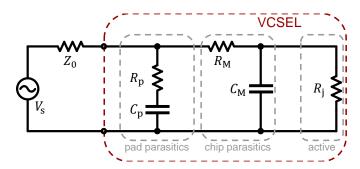

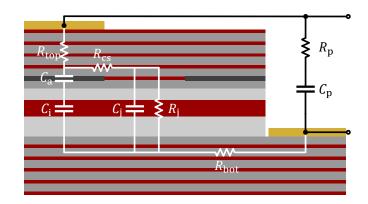

|   |     | 3.2.1 Extrinsic parasitic response                                  |  |  |  |  |  |  |  |

|   |     | 3.2.2 Parasitic elements                                            |  |  |  |  |  |  |  |

|   |     | 3.2.3 Tunnel junction                                               |  |  |  |  |  |  |  |

|   | 3.3 | Current confinement                                                 |  |  |  |  |  |  |  |

|   |     | 3.3.1 Current confinement methods                                   |  |  |  |  |  |  |  |

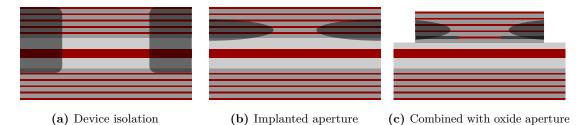

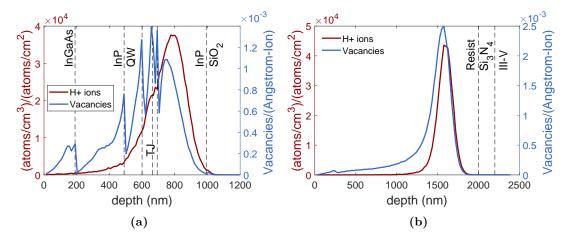

|   |     | 3.3.2 Ion implantation for current confinement                      |  |  |  |  |  |  |  |

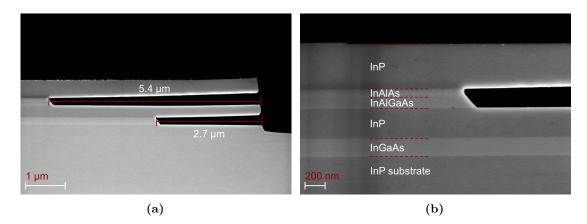

|   |     | 3.3.3 Undercut aperture                                             |  |  |  |  |  |  |  |

|   | 3.4 | Ohmic contacts for InP-based lasers                                 |  |  |  |  |  |  |  |

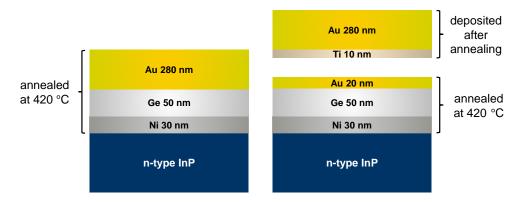

|   |     | 3.4.1 Ni/Ge/Au-based ohmic contact to $n$ -type InP                 |  |  |  |  |  |  |  |

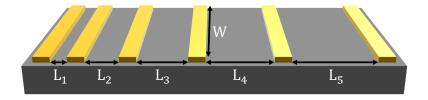

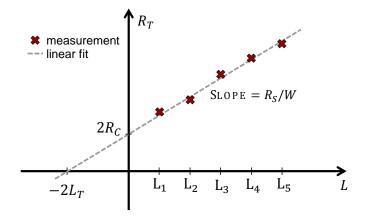

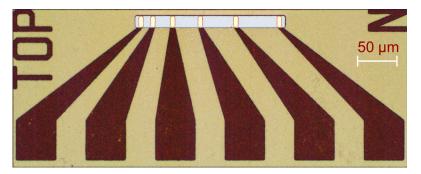

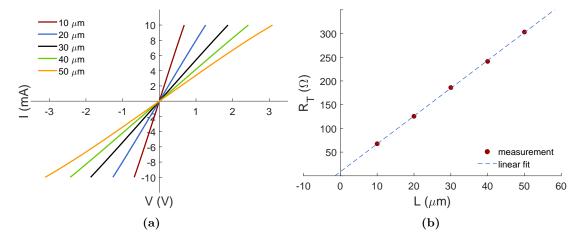

|   |     | 3.4.2 Transmission line method                                      |  |  |  |  |  |  |  |

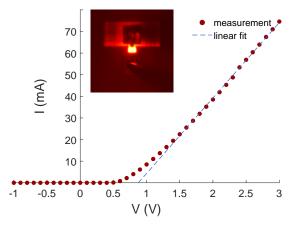

|   |     | 3.4.3 Ohmic contact testing                                         |  |  |  |  |  |  |  |

|   | 3.5 | Summary                                                             |  |  |  |  |  |  |  |

| 4 | D   |                                                                     |  |  |  |  |  |  |  |

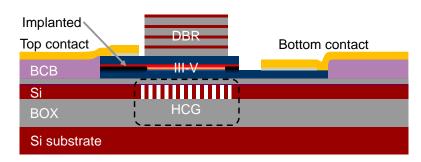

| 4 |     | VICE DESIGNS 59                                                     |  |  |  |  |  |  |  |

|   | 4.1 | Introduction                                                        |  |  |  |  |  |  |  |

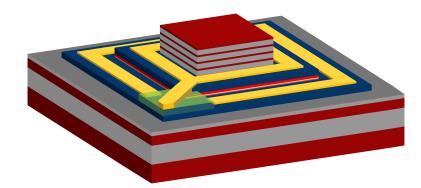

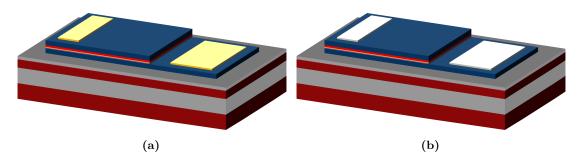

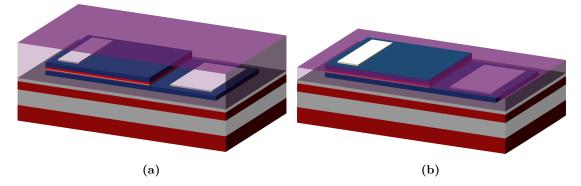

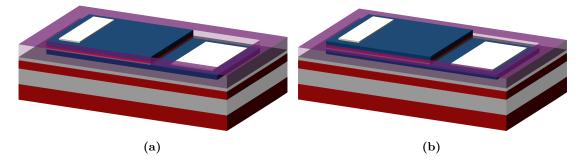

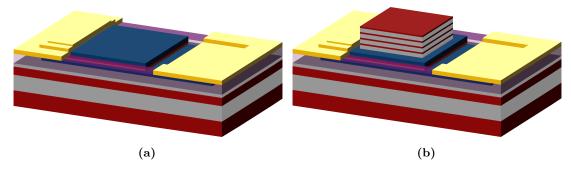

|   | 4.2 | Hybrid VCSEL design                                                 |  |  |  |  |  |  |  |

|   | 4.3 | Design versions                                                     |  |  |  |  |  |  |  |

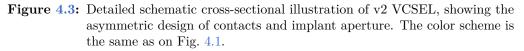

|   |     | 4.3.1       v1 VCSEL       61         4.3.2       v2 VCSEL       62 |  |  |  |  |  |  |  |

|   |     | 4.3.2       V2 VCSEL       62         4.3.3       V3 VCSEL       64 |  |  |  |  |  |  |  |

|   |     | 4.3.3 V3 VCSEL                                                      |  |  |  |  |  |  |  |

|   | 4.4 | Summary                                                             |  |  |  |  |  |  |  |

|   | 4.4 | Summary                                                             |  |  |  |  |  |  |  |

| 5 | WAI | FER BONDING OF III-V TO SOI 67                                      |  |  |  |  |  |  |  |

|   | 5.1 | Introduction                                                        |  |  |  |  |  |  |  |

|   | 5.2 | Direct wafer bonding method                                         |  |  |  |  |  |  |  |

|   |     | 5.2.1 Bonding mechanism                                             |  |  |  |  |  |  |  |

|   |     | 5.2.2 Oxygen plasma-assisted direct wafer bonding                   |  |  |  |  |  |  |  |

|   |     | 5.2.3 Cleaning and surface roughness requirement                    |  |  |  |  |  |  |  |

|   | 5.3 | Surface roughness issue                                             |  |  |  |  |  |  |  |

|   | 5.4 | BCB adhesive wafer bonding                                          |  |  |  |  |  |  |  |

|   |     | 5.4.1 Motivation                                                    |  |  |  |  |  |  |  |

|   |     | 5.4.2 Adhesive wafer bonding $\ldots$ 71                            |  |  |  |  |  |  |  |

|   |     | 5.4.3 Bonding using BCB polymer                                     |  |  |  |  |  |  |  |

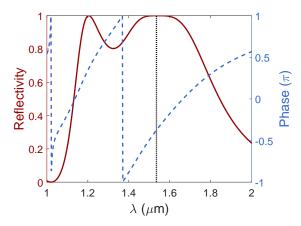

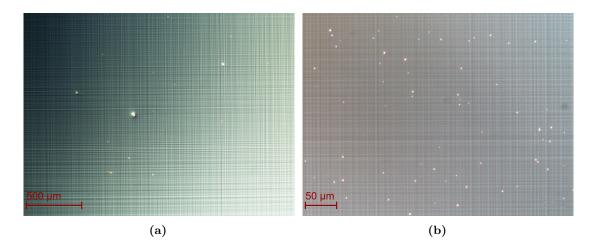

|   |     | 5.4.4 Bonding experiments                                           |  |  |  |  |  |  |  |

|   | 5.5 | Summary                                                             |  |  |  |  |  |  |  |

| 0 | T   |                                                                     |  |  |  |  |  |  |  |

| 6 |     | RICATION OF HYBRID VCSELS 81                                        |  |  |  |  |  |  |  |

|   | 6.1 | Introduction                                                        |  |  |  |  |  |  |  |

|   | 0.0 | 6.1.1 CMOS compatibility                                            |  |  |  |  |  |  |  |

|   | 6.2 | Process flow overview                                               |  |  |  |  |  |  |  |

|   |     | 6.2.1 Sample preparation                                            |  |  |  |  |  |  |  |

|   |     | 6.2.2 Fabrication steps                                             |  |  |  |  |  |  |  |

|   | 6.9 | 6.2.3 Summary and remarks                                           |  |  |  |  |  |  |  |

|   | 6.3 | Patterning the SOI                                                  |  |  |  |  |  |  |  |

|   |     | 6.3.1 Pattern                                                       |  |  |  |  |  |  |  |

|   |     | 6.3.2E-beam lithography916.3.3Si dry etching91                      |  |  |  |  |  |  |  |

|   |     | 6.3.3 Si dry etching                                                |  |  |  |  |  |  |  |

|   |                                           | 6.3.4 Grating bar width control                                                                              |

|---|-------------------------------------------|--------------------------------------------------------------------------------------------------------------|

|   | 6.4                                       | Bonding of samples and III-V substrate removal                                                               |

|   |                                           | 6.4.1 Preparation for bonding                                                                                |

|   |                                           | 6.4.2 Manual and mechanical bonding                                                                          |

|   |                                           | 6.4.3 InP substrate wet etch                                                                                 |

|   | 6.5                                       | UV Lithography and alignment                                                                                 |

|   |                                           | 6.5.1 Overview of photolithography processes                                                                 |

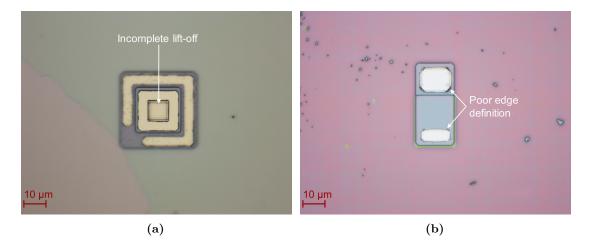

|   |                                           | 6.5.2 Pattern quality and resolution                                                                         |

|   | c c                                       | 6.5.3 Alignment marks and precision                                                                          |

|   | 6.6                                       | Mesa patterning                                                                                              |

|   |                                           | 6.6.1 Overview                                                                                               |

|   |                                           | 6.6.2       Hard mask and III-V dry etching       100         6.6.3       Removal of InGaAs layers       101 |

|   | 67                                        |                                                                                                              |

|   | $\begin{array}{c} 6.7 \\ 6.8 \end{array}$ | Proton implantation    102      Metallization for electrical contacts    102                                 |

|   | 0.0                                       | 6.8.1 E-beam evaporation and lift-off                                                                        |

|   |                                           | -                                                                                                            |

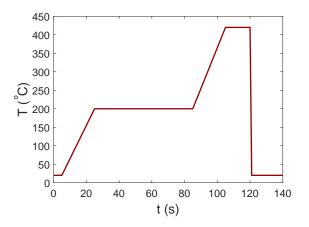

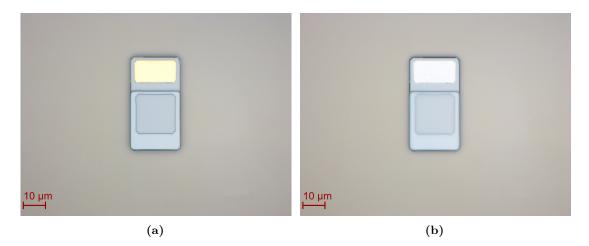

|   | 6.9                                       | 6.8.2Ohmic contact annealing103Planarization for contact pads105                                             |

|   | 0.9                                       | 6.9.1 Planarization with nitride                                                                             |

|   |                                           | 6.9.2       Planarization with BCB       105                                                                 |

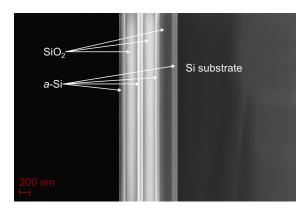

|   | 6 10                                      | DBR fabrication                                                                                              |

|   | 0.10                                      | 6.10.1 Deposition of SiO <sub>2</sub> and <i>a</i> -Si layers                                                |

|   |                                           | 6.10.2 DBR mesa etching                                                                                      |

|   | 6 11                                      | Remarks                                                                                                      |

|   | 0.11                                      |                                                                                                              |

| 7 | REST                                      | ULTS AND DISCUSSION 109                                                                                      |

|   | 7.1                                       | Introduction                                                                                                 |

|   | 7.2                                       | Characterization methods and setups                                                                          |

|   |                                           | 7.2.1 Electrical pumping method and setup 110                                                                |

|   |                                           | 7.2.2 Optical pumping method and setup                                                                       |

|   | 7.3                                       | v1 VCSEL results and discussion                                                                              |

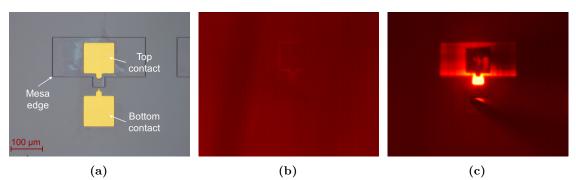

|   |                                           | 7.3.1 Fabrication results                                                                                    |

|   |                                           | 7.3.2 Characterization results                                                                               |

|   |                                           | 7.3.3 Discussion                                                                                             |

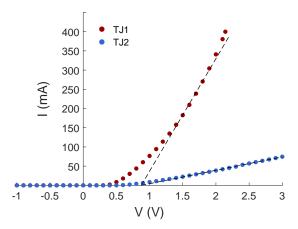

|   | 7.4                                       | Comparison of TJ epitaxies                                                                                   |

|   | 7.5                                       | v2 VCSEL results and discussion                                                                              |

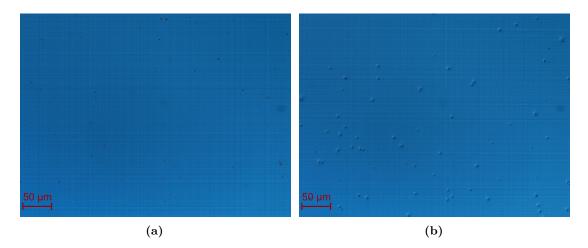

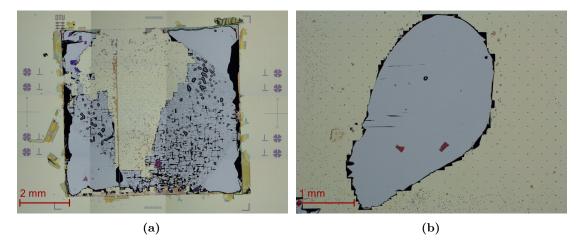

|   |                                           | 7.5.1 Fabrication results                                                                                    |

|   |                                           | 7.5.2 Characterization results                                                                               |

|   | 7.0                                       | 7.5.3 Discussion                                                                                             |

|   | 7.6                                       | v3 VCSEL results and discussion                                                                              |

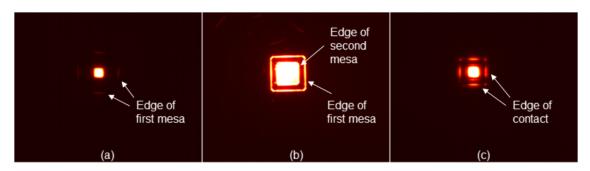

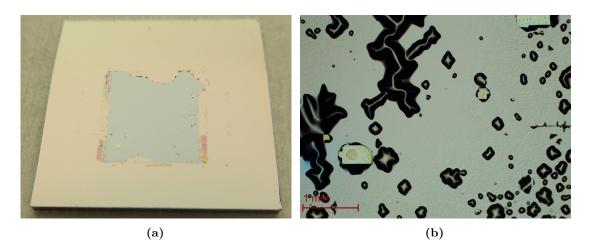

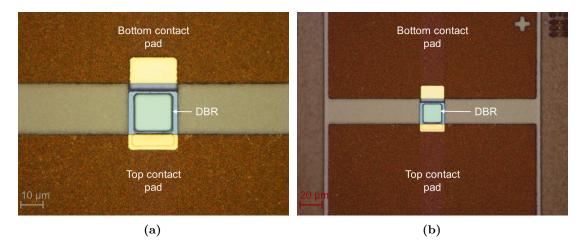

|   |                                           | 7.6.1 Fabrication results                                                                                    |

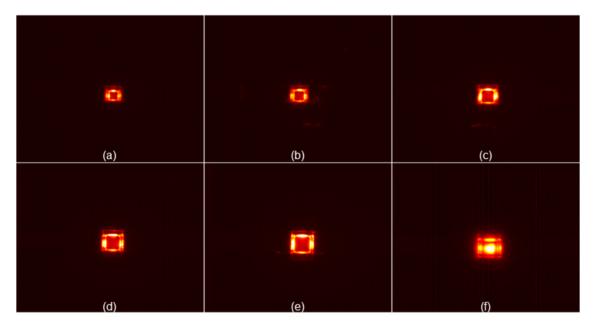

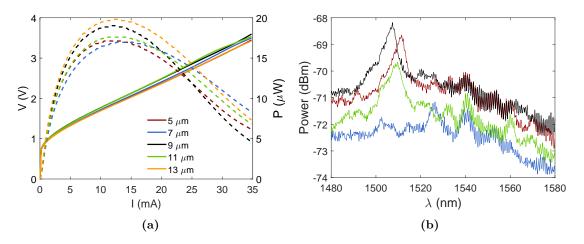

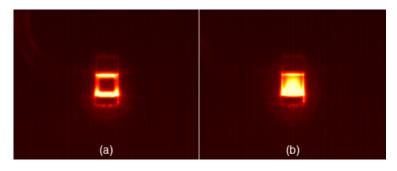

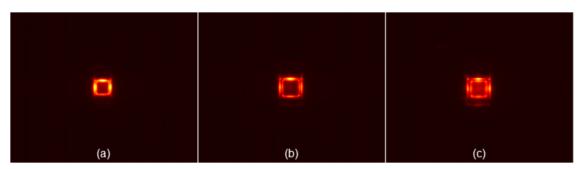

|   |                                           | 7.6.2 Characterization results                                                                               |

|   |                                           | 7.6.3 Discussion                                                                                             |

|   | 7.7                                       | v4 VCSEL results and discussion                                                                              |

|   |                                           |                                                                                                              |

|   |                                           |                                                                                                              |

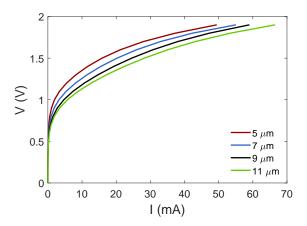

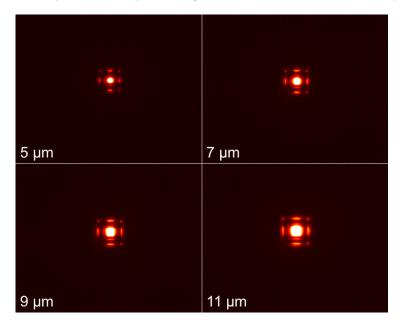

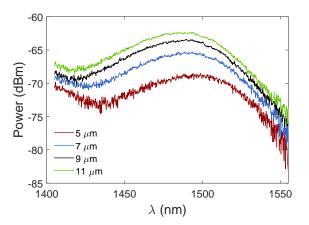

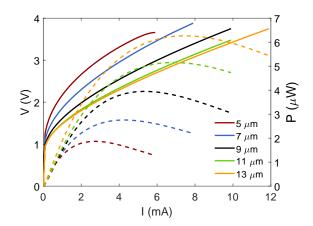

|   |                                           | 7.7.2 Characterization results                                                                               |

|   | 7 0                                       | 7.7.2Characterization results1317.7.3Discussion134                                                           |

|   | 7.8                                       | 7.7.2 Characterization results                                                                               |

| 8 |                                           | 7.7.2Characterization results1317.7.3Discussion134Summary and discussion135                                  |

| 8 |                                           | 7.7.2Characterization results1317.7.3Discussion134Summary and discussion135ICLUSION AND OUTLOOK137           |

| 8 | Con                                       | 7.7.2Characterization results1317.7.3Discussion134Summary and discussion135ICLUSION AND OUTLOOK137           |

| xii                        | Contents |

|----------------------------|----------|

| A FABRICATION PROCESS FLOW | 141      |

| LIST OF ACRONYMS           | 151      |

| Bibliography               | 153      |

# CHAPTER ]

# Introduction

In the recent years, data has become the most valuable resource in the world and the information is available to everybody all over the world. This has led to entire modern world's economy being based on information technology (IT). The top five largest companies in the world by market value by 2018 are all from IT sector, offering hardware and software that are now part of our everyday life, giving us access to all the information and enabling us to stay connected. Internet, online shopping, social networks, media streaming, cloud computing and storage are just a few examples of the services in use today that have caused the amount of data being transferred globally to increase by an exponential trend over the past few decades. New services, like the artificial intelligence, augmented reality and Internet of Things (IoT), that are already starting to spread, will push this trend even further in coming years. And the technology that enabled this kind of growth and, in a way, shaped the modern world is optical communications.

Development of the semiconductor diode lasers and the optical fibers were the milestones in communication technology that enabled us to use photons to transfer information across huge distances with high speed and low power consumption [1, 2]. Decades later, single frequency lasers, fiber optics, fast detectors, high frequency modulation, wavelength multiplexing, higher order modulation formats, etc. are used to carry petabytes of information from continent to continent. This technology was first employed to connect the continents, countries and cities and form long-haul global area networks (GANs) and wide area networks (WANs). Naturally, not long after, optical communication moved from long-haul backbones to the metropolitan area networks (MANs) and even local area networks (LANs), with fiber replacing copper cables at shorter and shorter distances [2]. Past decade has seen the need for optical communication technologies to be employed at even shorter distances between different parts of large electronic systems. Today, rack-to-rack (1 m to 100 m) and even board-to-board (50 cm to 100 cm) interconnects are commonly optical [3, 4]. In recent years, efforts have been focused on bringing optics to even shorter distances for chip-to-chip (1 cm to 50 cm) and even on-chip  $(100 \,\mu\text{m to } 1 \text{ cm})$  interconnects, but electrical interconnects still dominate all short-distance communications, especially on integrated circuit chips and on circuit boards [5].

# **1.1** Optical interconnects

### 1.1.1 Motivation

The unrelenting growth of data traffic has led to equally dramatic growth of data centers. Energy consumption of the biggest data centers today is comparable to a city of million people and in total, they eat up more than 3% if world's electricity, with projections that it could increase to 20% by 2025 [6]. The need to improve energy efficiency and reduce carbon footprint of data centers is obvious. With power usage effectiveness of modern data centers approaching close to theoretically perfect value [7], any future improvements will be minor and incremental. Therefore, further drastic improvement would have to come by improving the computing efficiency.

## **1.1.2** Limits of electrical interconnects

The drive to replace electrical interconnects is due to their fundamental physical limitations which pose a challenge for them to cope with the exponentially growing data traffic [5, 8]. For a long time, the strategy for improving the computing power was to increase the performance of a single computing unit. When the limits were reached, the strategy moved to increasing the number of the computing units, but then the efficiency and performance of the communication between computing units becomes a key factor that determines the performance of an entire computer system. In other words, now performance is dominated by the interconnection medium between chips rather than the devices at either end [9]. Apart from the limited bandwidth that can be reached, the biggest limitation of electrical interconnects is the energy consumption. Radio-frequency waves of electrical interconnects are guided using metal waveguides and wires. The increasing resistive loss in metals at high oscillation frequency dominates the propagation loss in electrical interconnects which limits their length and the density [3, 5]. The energy required for charging and discharging of electrical connections leads to losses in interconnects so significant that they account to as much as half of the total power consumption in computer units [3]. Furthermore, at high speed and density, the interconnects have issue with cross-talk and electromagnetic interference (EMI) through capacitive and inductive coupling [3].

#### **1.1.3** Potential of optical interconnects

Optics has potential to improve on all of these issues. Optical interconnects can offer much greater bandwidth, lower power consumption, and decrease interconnect delays [2]. Light is guided using dielectric waveguides that have very low loss, so an optical interconnect can be employed where long distance is the limiting factor for electrical interconnects. Interconnect density can be increased drastically considering that optical fibers and waveguides have much smaller dimensions and do not suffer from EMI and signal cross-talk. The density can be further multiplied by employing wavelength division multiplexing (WDM). This density benefit was the main driver for the introduction of optical interconnects at shorter distances [5]. However, as discussed above, energy consumption is becoming more and more critical issue, especially as the distance decreases, and total energy per bit of the link becomes the leading criterion. Optics can potentially be more energy efficient since it doesn't need to charge the line to operating voltage [3], but it is limited by the efficiency of transmitter and receiver.

In order for optical interconnects to become a viable alternative for future use at the shortest distances they need to meet some very strict energy targets [10]. The single most energy demanding part of the optical link is the device that converts the electrical signal to the optical one. Optical output device with sufficiently low energy per bit is the single largest technological challenge for realization chip-to-chip and on-chip optical interconnects. Semiconductor diode lasers have been the main optical output devices used in communications for a long time. However, as distances become shorter, the density of interconnects and the number of the transmission lines grows, which means that the fabrication costs of a single laser becomes a big factor in the total costs. Despite their potential, optical interconnects will replace electrical interconnects only when they have higher performance at lower cost and strong manufacturability in high volume.

Long distance optical links employ edge-emitting lasers at wavelengths around 1550 and 1310 nm, at which respectively minimum of absorption and dispersion in the optical fibers occur. However, these devices cannot meet the targeted low energy consumption, low cost and small footprint that are needed for short distance optical interconnects. Instead, the most used laser type in optical interconnects are vertical-cavity surface-emitting lasers (VCSELs). They can have many features that make them attractive, such as higher energy efficiency, high-speed modulation, single longitudinal mode operation, low fabrication cost, narrow circular beam for convenient fiber coupling, small footprint, possibility of forming two-dimensional arrays, wafer level testing, etc. [11]. VCSELs, operating in the short-wavelength spectral range ( $\lambda \sim 800 - 1000 \,\mathrm{nm}$ ), and multi-mode fiber (MMF) links are dominating the short-reach optical interconnects used in data centers and high-performance computing systems where links are shorter than 300 m in most cases. However,

as the new data rate standards increase from 10 Gb/s towards 100 Gb/s, modal and chromatic dispersion in the MMF reduces the reach from 300 m to only 100 m [12]. On the other hand, the data centers are growing in size. Newer mega data centers can span across huge areas and multiple buildings with links reaching kilometers in length, beyond the reach of short-wavelength VCSELs and MMFs. There is much interest in bringing the low cost and high energy efficiency of the VCSELs to longer wavelengths for high-speed links of over several kilometers with single-mode fibers (SMFs), not only for data centers and LANs but even for MANs and WANs [11, 13].

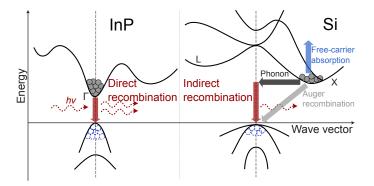

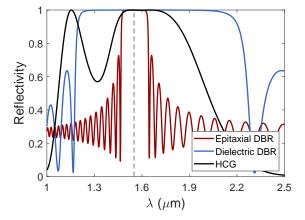

Short-wavelength VCSELs (SW-VCSELs) in use today, typically emitting around 850, 980, and 1100 nm, are based on well matured gallium arsenide (GaAs) technology, with oxide apertures for electrical and optical confinement, developed during the 1990s [14–16]. Long-wavelength VCSELs (LW-VCSELs), based on indium phosphide (InP) and emitting around 1310 and 1550 nm, have been much bigger challenge. Suffering from less mature fabrication technology, problems related to material quality and fundamental issues with device design, they could not keep up with SW-VCSELs [13]. For longer wavelengths energy bandgaps in active region are smaller, which leads to more dominant Auger non-radiative recombination, lowering the gain and causing poorer temperature performance. Main issue of InP-based VCSELs is realization of epitaxial distributed Bragg reflectors (DBRs) with high thermal conductivity, high reflectivity, and high electrical conductivity [17]. Typically used lattice-matched InGaAsP/InP epitaxial DBR has low refractive-index contrast ( $\Delta n \approx 0.2 - 0.3$ ), which means that large number of quarter-wavelength layers is needed for high reflection. Such thick mirrors have poor thermal conductivity, limiting the continuous-wave (CW) operation at high temperatures [18]. Only recently have the LW-VCSELs seen novel approaches that enabled significant progress in performance and commercialization.

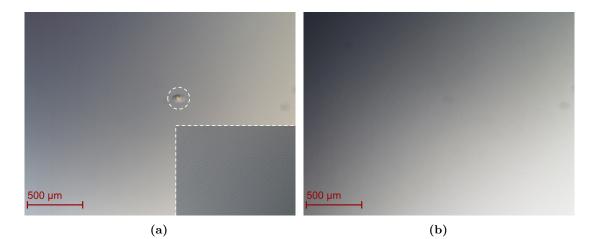

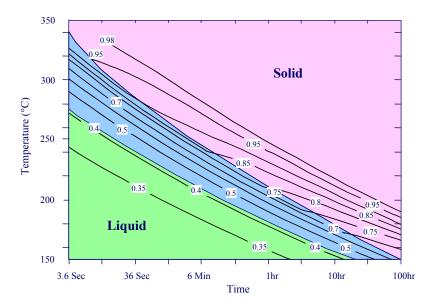

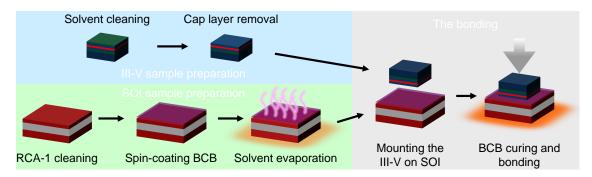

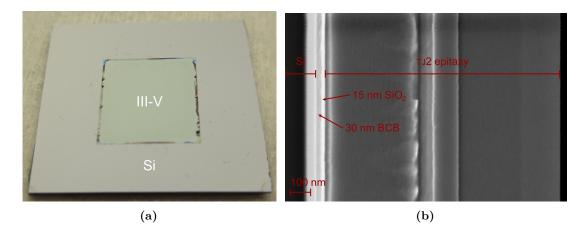

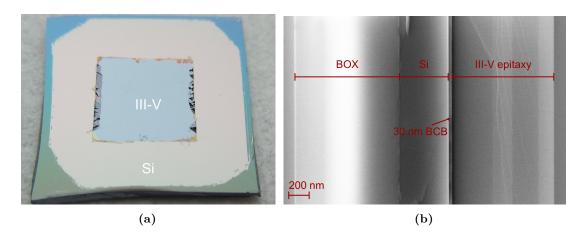

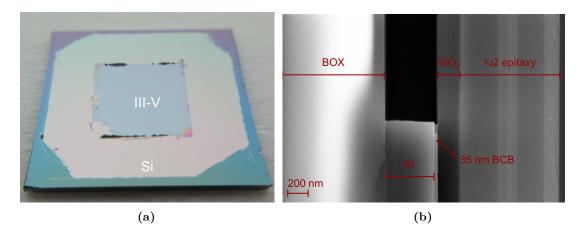

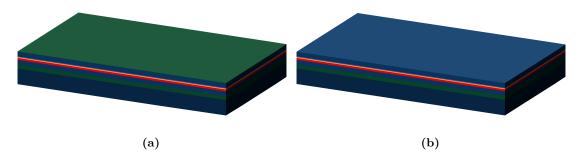

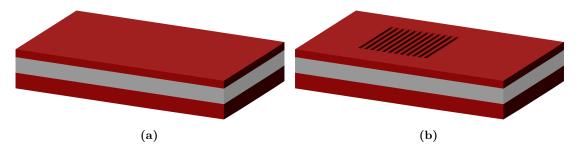

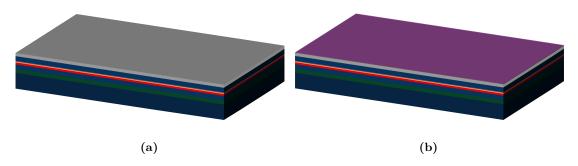

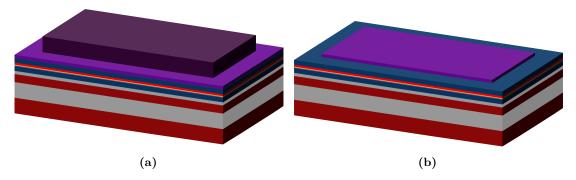

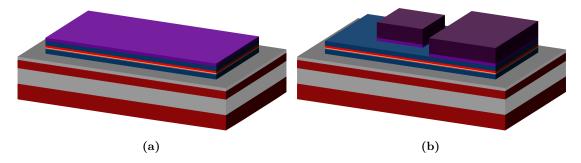

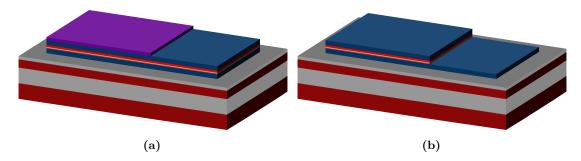

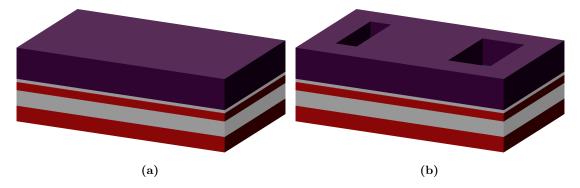

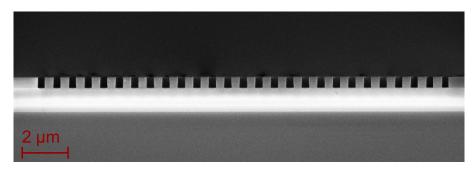

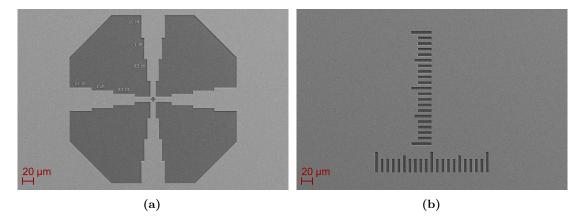

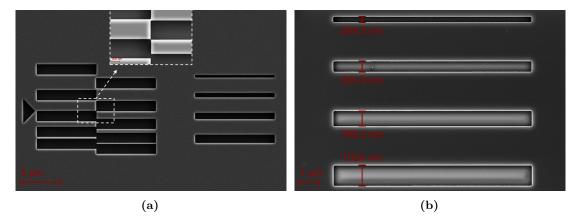

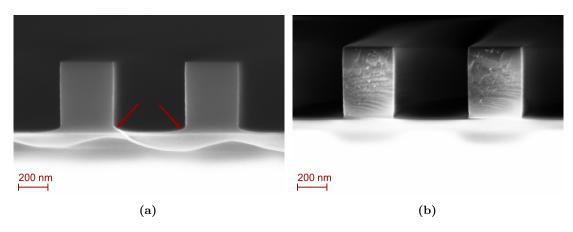

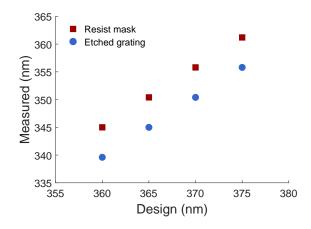

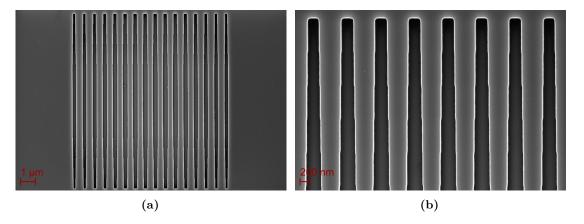

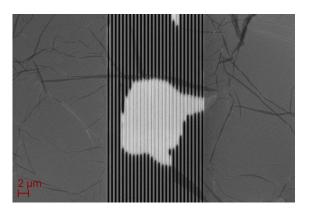

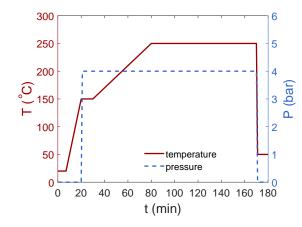

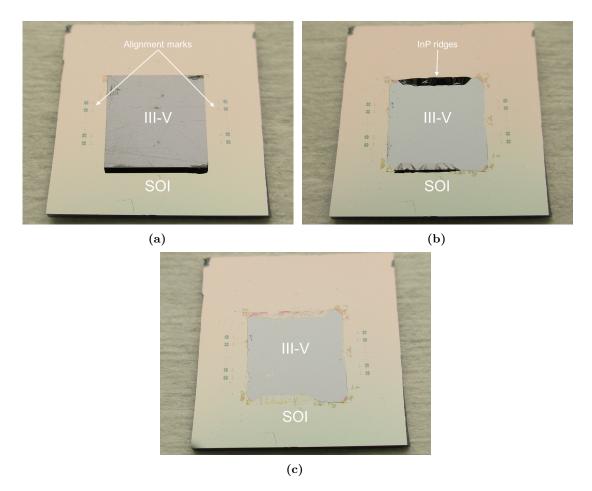

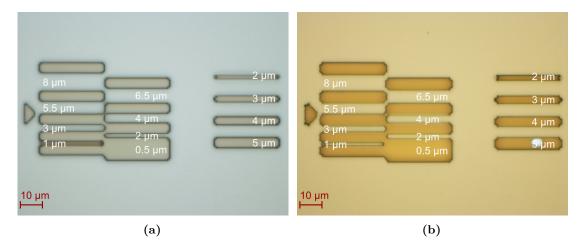

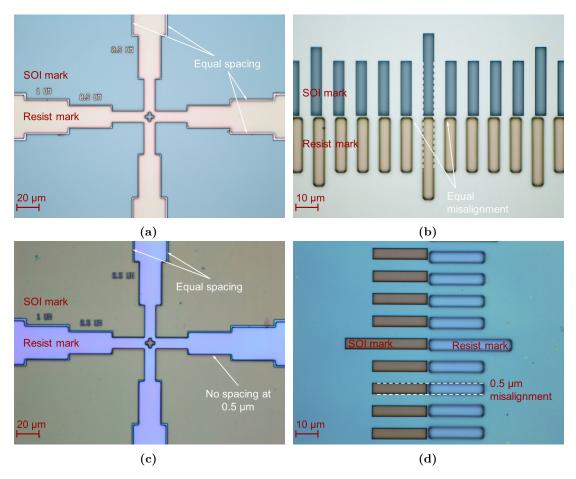

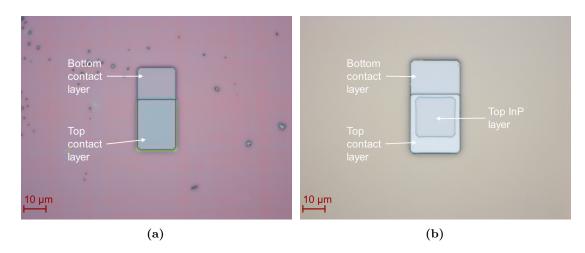

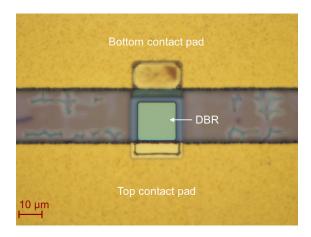

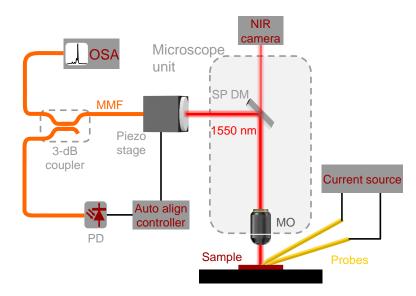

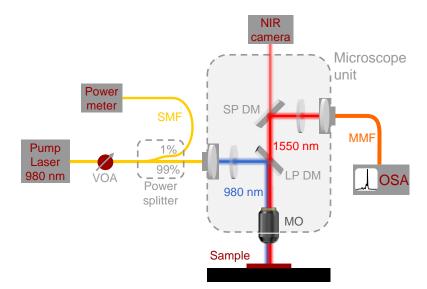

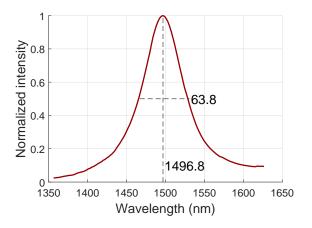

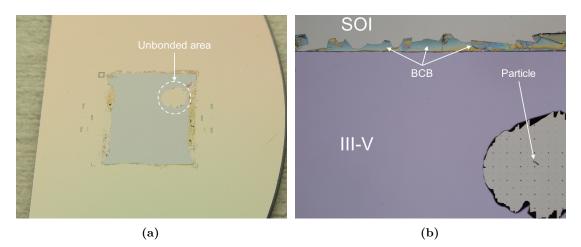

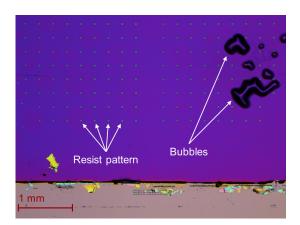

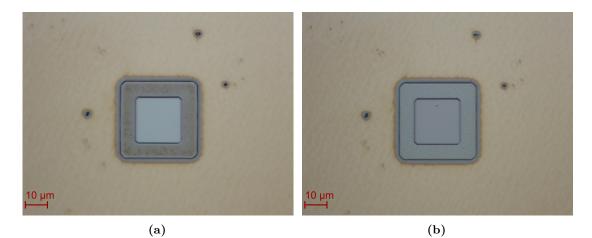

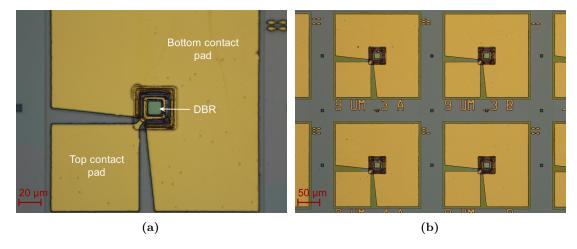

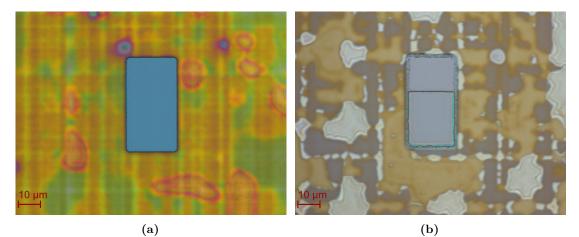

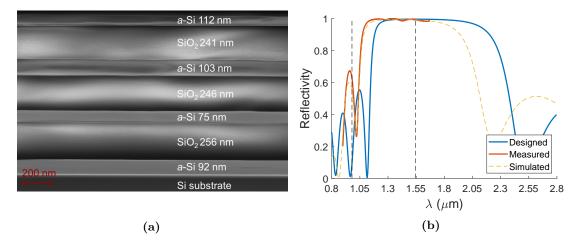

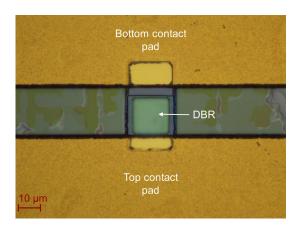

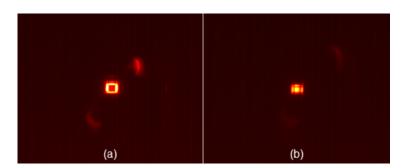

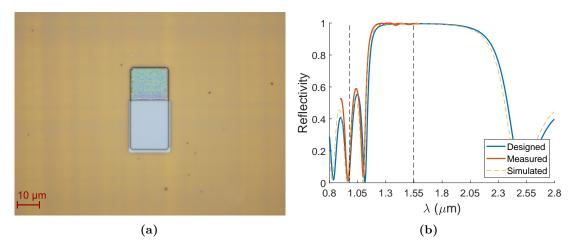

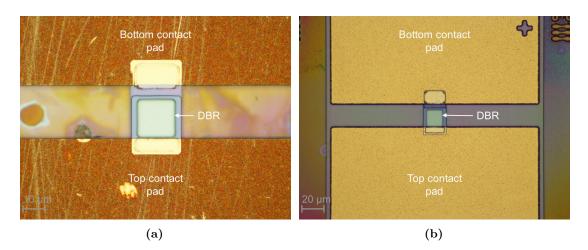

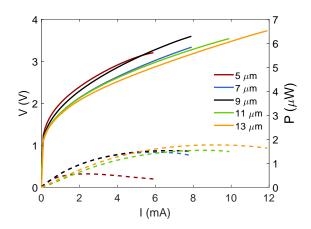

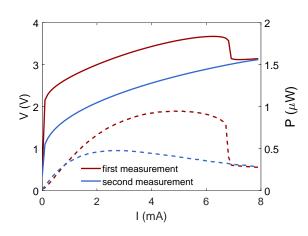

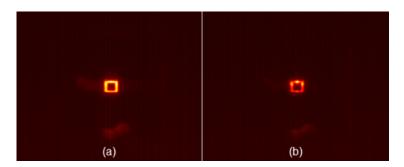

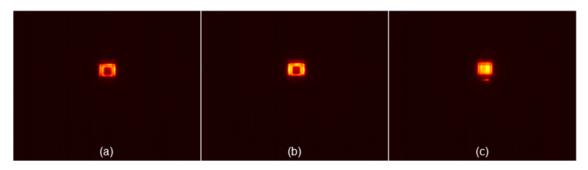

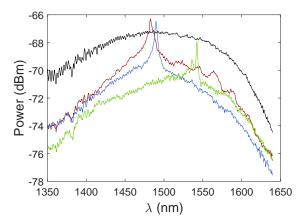

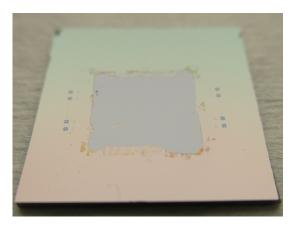

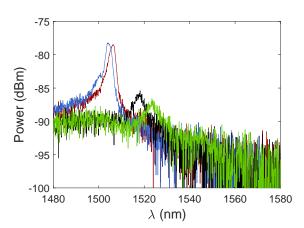

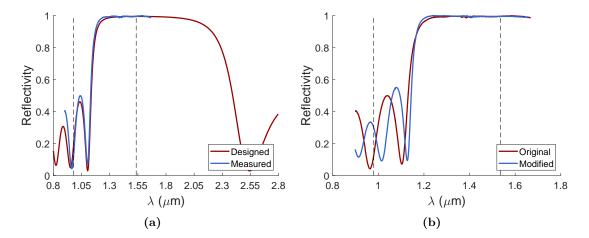

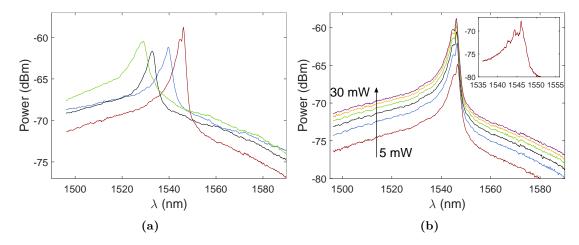

## 1.1.4 Silicon photonics