## COMPILER OPTIMIZATION EFFECTS ON REGISTER COLLISIONS

A Thesis

presented to

the Faculty of California Polytechnic State University,

San Luis Obispo

In Partial Fulfillment

of the Requirements for the Degree

Master of Science in Computer Science

by

Jonathan Tan

June 2018

## © 2018

# Jonathan Tan ALL RIGHTS RESERVED

## COMMITTEE MEMBERSHIP

| TITLE:            | Compiler Optimization Effects on Register |

|-------------------|-------------------------------------------|

|                   | Collisions                                |

|                   |                                           |

| AUTHOR:           | Jonathan Tan                              |

|                   |                                           |

| DATE SUBMITTED:   | June 2018                                 |

|                   |                                           |

|                   |                                           |

| COMMITTEE CHAIR:  | Aaron Keen, Ph.D.                         |

|                   | Professor of Computer Science             |

|                   |                                           |

|                   |                                           |

| COMMITTEE MEMBER: | Theresa Migler, Ph.D.                     |

|                   | Professor of Computer Science             |

|                   |                                           |

|                   |                                           |

| COMMITTEE MEMBER: | John Seng, Ph.D.                          |

|                   | Professor of Computer Science             |

#### ABSTRACT

## Compiler Optimization Effects on Register Collisions

## Jonathan Tan

We often want a compiler to generate executable code that runs as fast as possible. One consideration toward this goal is to keep values in fast registers to limit the number of slower memory accesses that occur. When there are not enough physical registers available for use, values are "spilled" to the runtime stack. The need for spills is discovered during register allocation wherein values in use are mapped to physical registers. One factor in the efficacy of register allocation is the number of values in use at one time (register collisions). Register collision is affected by compiler optimizations that take place before register allocation. Though the main purpose of compiler optimizations is to make the overall code better and faster, some optimizations can actually increase register collisions. This may force the register allocation process to spill. This thesis studies the effects of different compiler optimizations on register collisions.

## ACKNOWLEDGMENTS

Thanks to:

- My advisor, Aaron Keen, for guiding, encouraging, and mentoring me on the thesis and classes. Words cannot describe the impact you had on me.

- My committee members (John Seng and Theresa Migler) for taking time out of their busy schedules to help better my thesis.

- My many great professors that taught me so many invaluable lessons.

- My Dad, Mom, and Brother (Jeffrey Tan, Shirley Her, and Benjamin Tan) for taking care of me and calling me to check in and see how I am doing.

- My roomates (Andrew Kim, Michael Djaja, Dylan Sun, Pierson Yieh) for encouragement to push through the hard times and the great times.

- My entire EPIC family for the continued support and many great laughs and times throughout college.

## TABLE OF CONTENTS

|     |       | Pa                                                 | ge  |

|-----|-------|----------------------------------------------------|-----|

| LIS | ST O  | FIGURES                                            | iii |

| CF  | IAPT  | IR                                                 |     |

| 1   | Intro | luction                                            | 1   |

|     | 1.1   | Register Collisions                                | 1   |

|     | 1.2   | Optimizations                                      | 3   |

|     | 1.3   | Motivation                                         | 4   |

|     | 1.4   | Contributions                                      | 4   |

| 2   | Back  | round & Related Works                              | 5   |

|     | 2.1   | Control-Flow Graph                                 | 5   |

|     | 2.2   | Live Ranges                                        | 6   |

|     | 2.3   | Register Allocation                                | 8   |

|     |       | 2.3.1 Interference Graph                           | 9   |

|     |       | 2.3.2 Graph Coloring                               | 10  |

|     | 2.4   | Related Works                                      | 11  |

|     |       | 2.4.1 Heuristics                                   | 11  |

|     |       | 2.4.2 Graph Coloring Algorithm                     | 11  |

| 3   | Setu  | & Experimental Design                              | 13  |

|     | 3.1   | Clang and LLVM                                     | 13  |

|     | 3.2   | Aggregation                                        | 17  |

|     | 3.3   | Benchmarks                                         | 18  |

| 4   | Rest  | ts & Analysis                                      | 20  |

|     | 4.1   | Baseline Graph Anaylsis                            | 21  |

|     |       | 4.1.1 Average Register Collisions Across Functions | 21  |

|     |       | 4.1.2 Maximum Register Collisions Across Functions | 22  |

|     |       | 4.1.3 Register Collisions Across Registers         | 24  |

|     |       | 1.1.4 Stack Space                                  | 28  |

|     | 4.2   | All-Loops Configuration                            | 28  |

|     |       | 4.2.1 All-Loops Optimization On                    | 28  |

|       | 4.2.2  | All-Loops Optimization Off                       | 32 |

|-------|--------|--------------------------------------------------|----|

| 4.3   | Gener  | ral Observations                                 | 35 |

|       | 4.3.1  | Stack Space On Optimization                      | 36 |

|       | 4.3.2  | Stack Space Off Optimization                     | 40 |

| 4.4   | Doub   | le Optimizations                                 | 41 |

|       | 4.4.1  | All-Loops and Argpromotion Optimization          | 42 |

|       | 4.4.2  | Licm and All-loops Optimization                  | 45 |

|       | 4.4.3  | Licm and Argpromotion Optimization               | 50 |

| 4.5   | Thum   | b Architecture                                   | 52 |

|       | 4.5.1  | All-Loops Optimization                           | 52 |

|       | 4.5.2  | Jump-threading and Early-cse-memssa Optimization | 56 |

|       | 4.5.3  | Spills Between Architectures                     | 57 |

| 5 Fut | ure Wo | rks & Conclusion                                 | 61 |

| 5.1   | Futur  | e Works                                          | 61 |

|       | 5.1.1  | Subject Optimizations                            | 61 |

|       | 5.1.2  | Optimization Combinations                        | 61 |

|       | 5.1.3  | Register Allocator                               | 61 |

|       | 5.1.4  | Timings                                          | 62 |

|       | 5.1.5  | Architectures                                    | 62 |

| 5.2   | Concl  | usion                                            | 62 |

| BIBLI | OGRAF  | РНҮ                                              | 64 |

| APPE  | NDICES | S                                                |    |

| А     | -O3 C  | Optimization List                                | 67 |

| В     | ARM    | Double Optimization Numbers                      | 69 |

| С     | Regis  | ter Collision Graphs                             | 70 |

| D     | Doub   | le Optimizations Spill Count                     | 94 |

## LIST OF FIGURES

| Figure |                                                                                                                            | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------|------|

| 1.1    | Example of the loop-unrolling compiler optimization. Left side is original loop. Right side is with loop-unrolling applied | 2    |

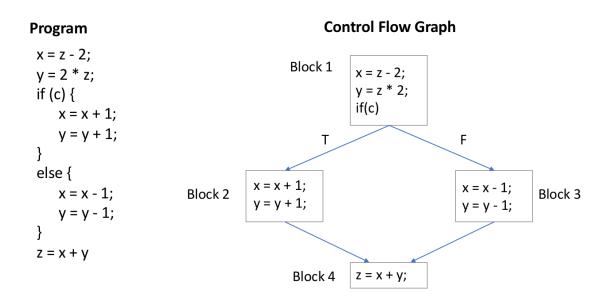

| 2.1    | Example of creating a CFG given a program                                                                                  | 6    |

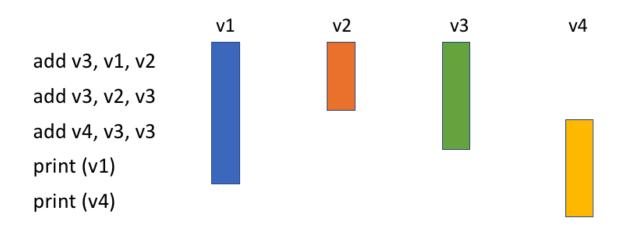

| 2.2    | Example of a live range with virtual registers                                                                             | 7    |

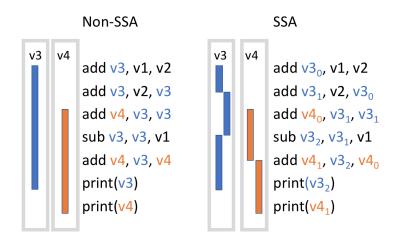

| 2.3    | Example of Non-SSA form when compared to SSA form                                                                          | 8    |

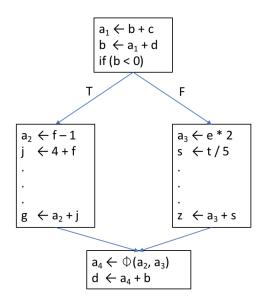

| 2.4    | Example of why SSA may be beneficial                                                                                       | 9    |

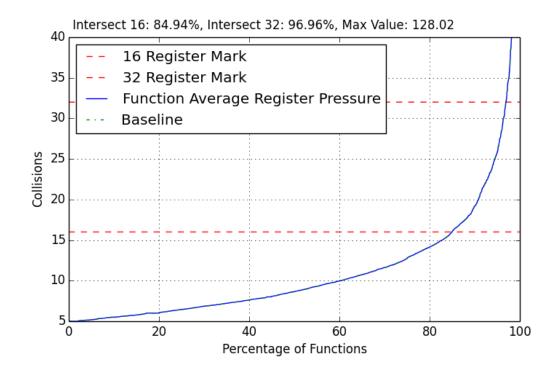

| 4.1    | Average Reg Collisions by Function, Baseline All Subject<br>Optimizations Off, No Minimum Register Collisions Threshold    | 21   |

| 4.2    | Average Reg Collisions by Function, Baseline All Subject<br>Optimizations On, No Minimum Register Collisions Threshold     | 22   |

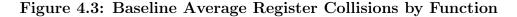

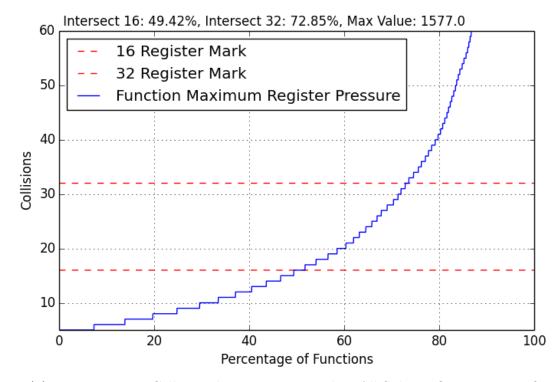

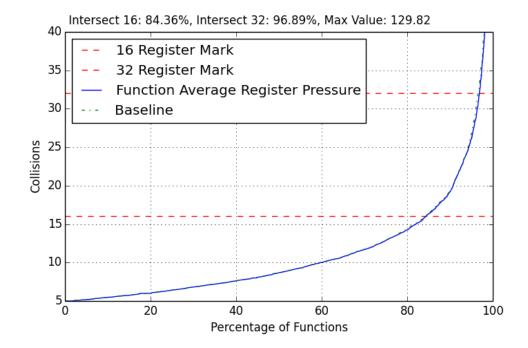

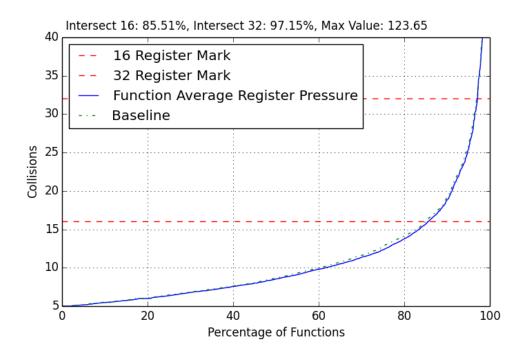

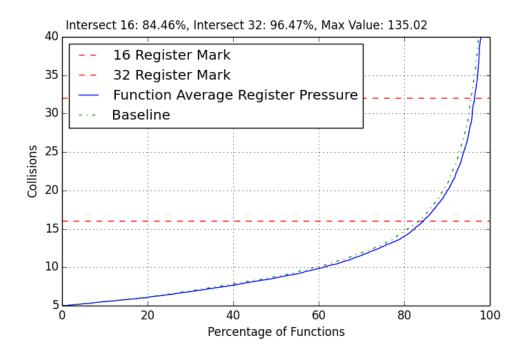

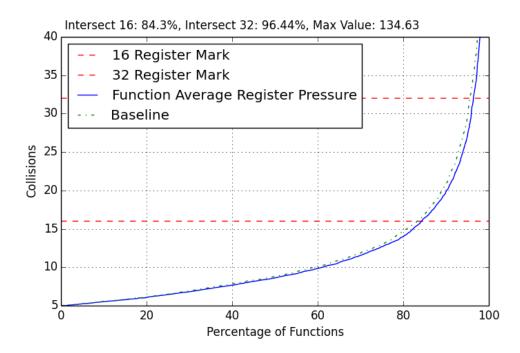

| 4.3    | Baseline Average Register Collisions by Function                                                                           | 23   |

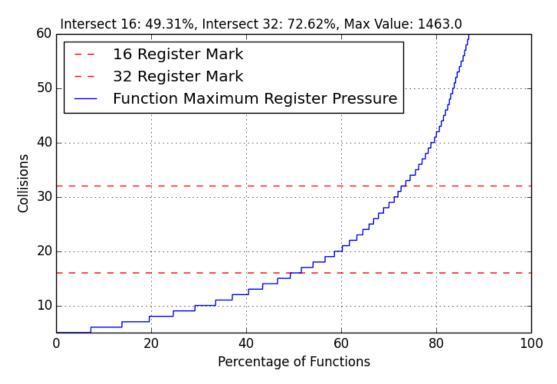

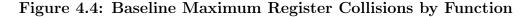

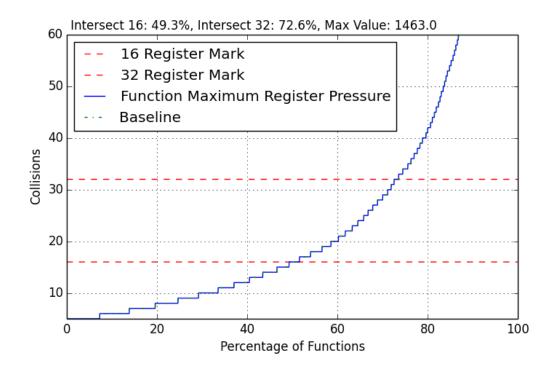

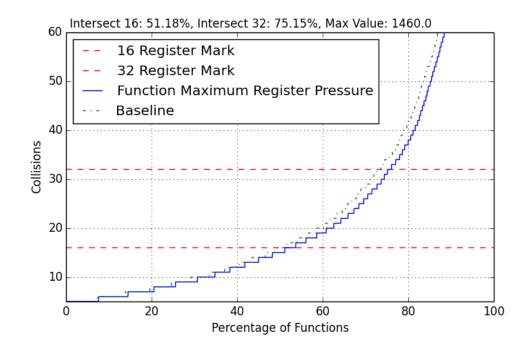

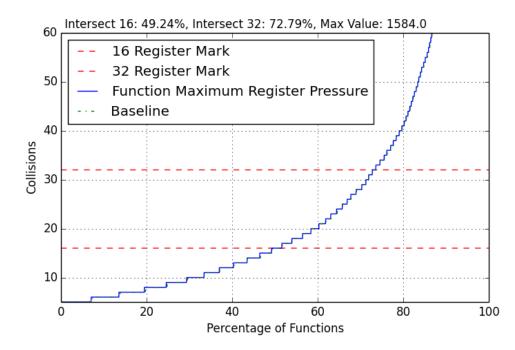

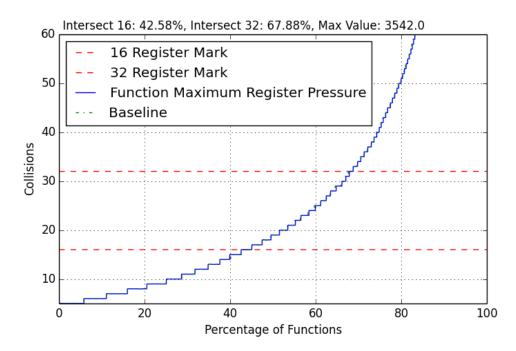

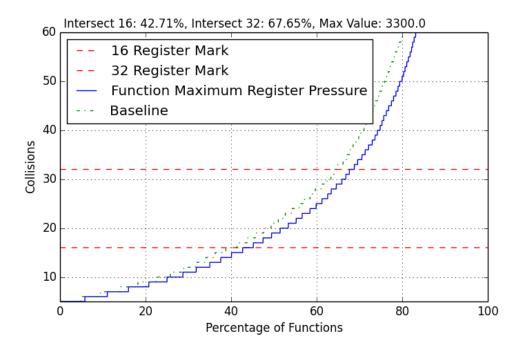

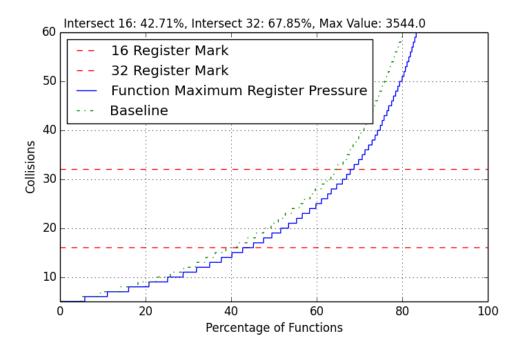

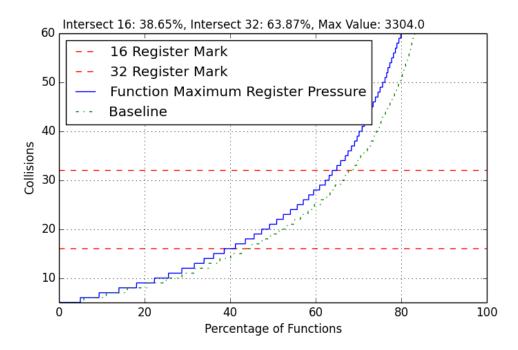

| 4.4    | Baseline Maximum Register Collisions by Function                                                                           | 25   |

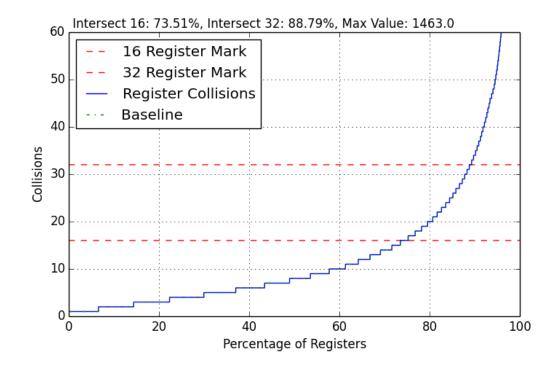

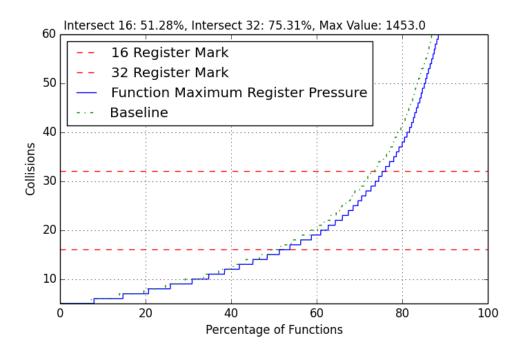

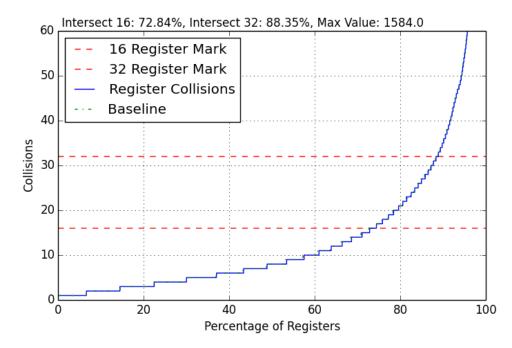

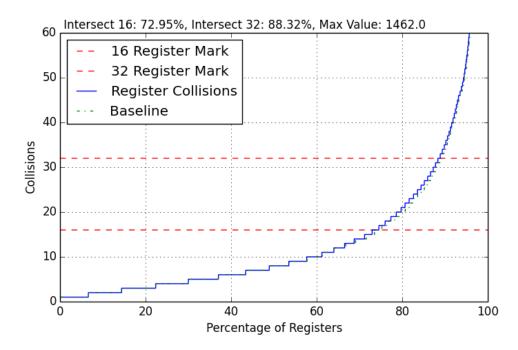

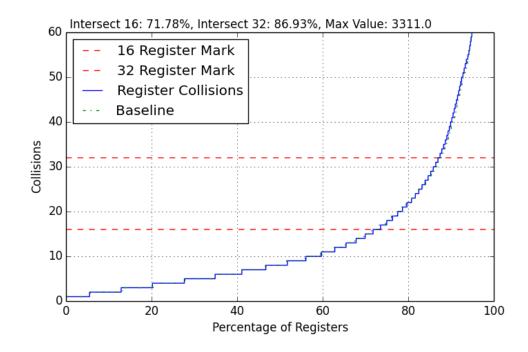

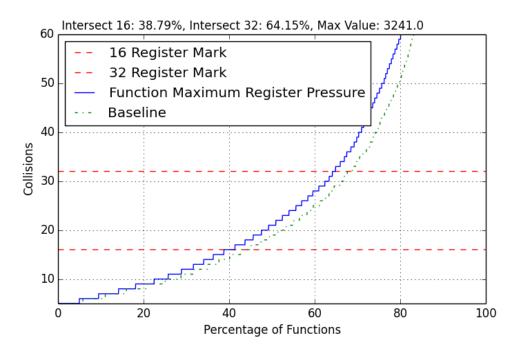

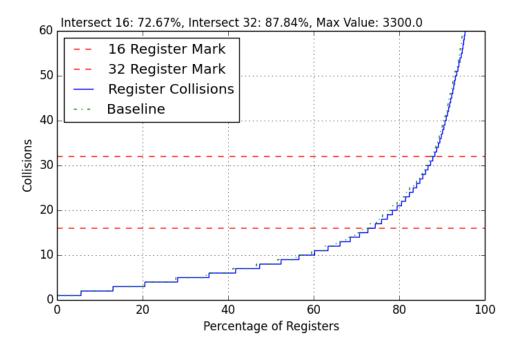

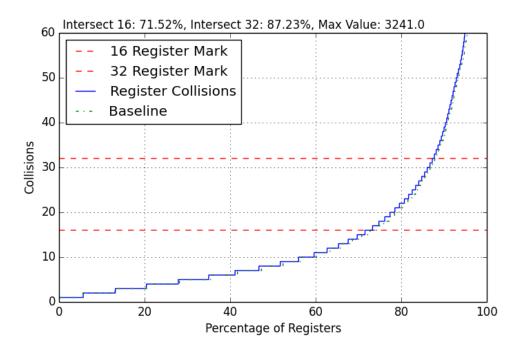

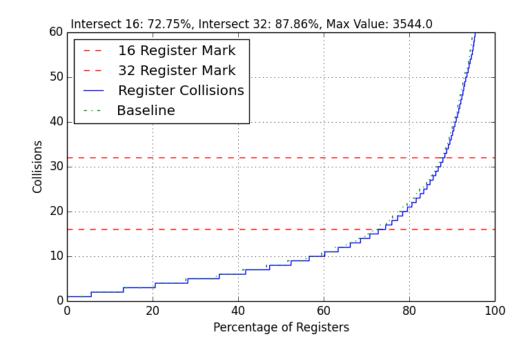

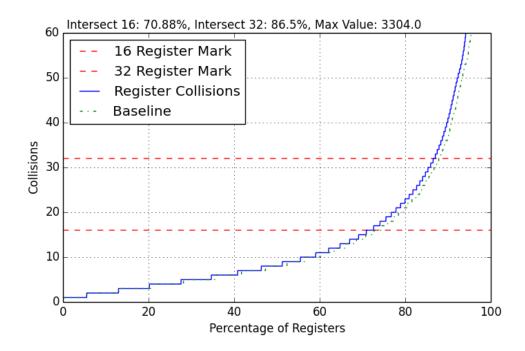

| 4.5    | Baseline Register Collisions by Register                                                                                   | 26   |

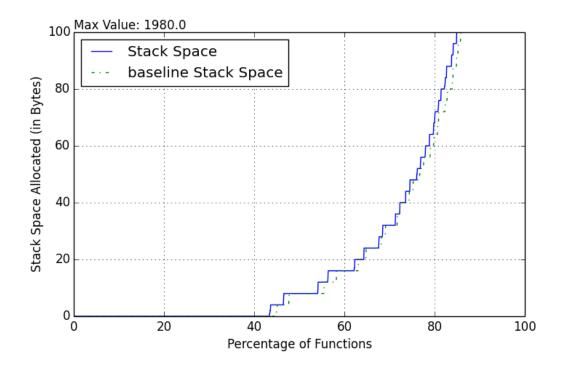

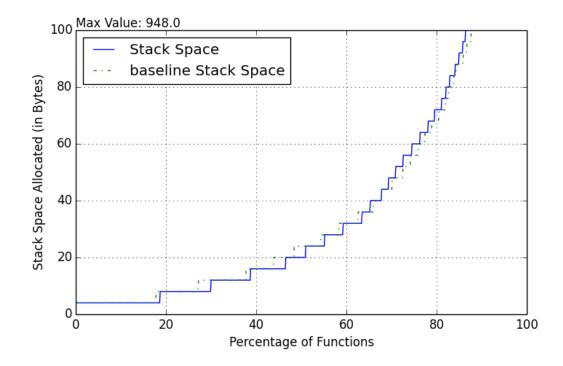

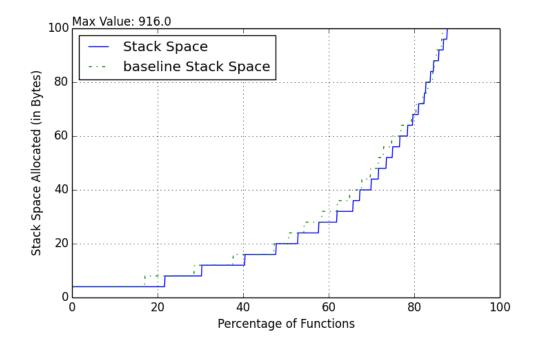

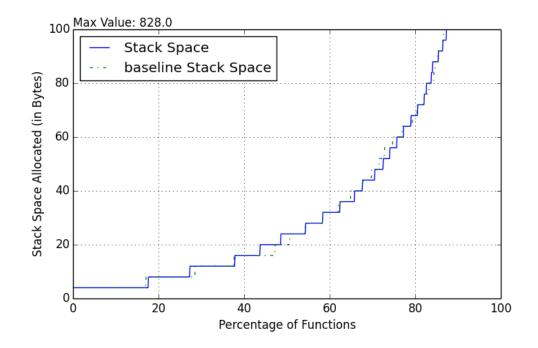

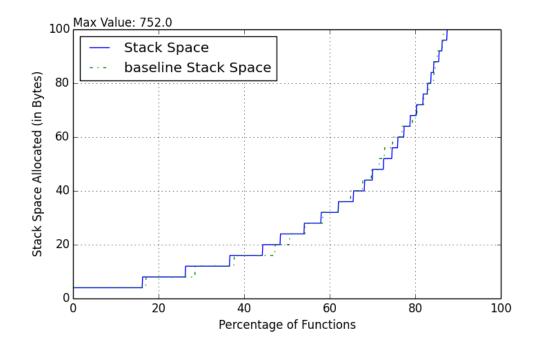

| 4.6    | Baseline Stack Space                                                                                                       | 27   |

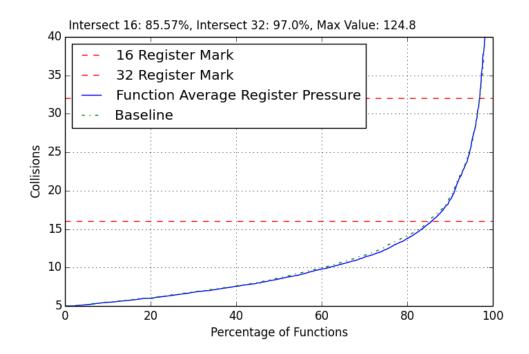

| 4.7    | Average Register Collisions by Function, All-Loops On                                                                      | 29   |

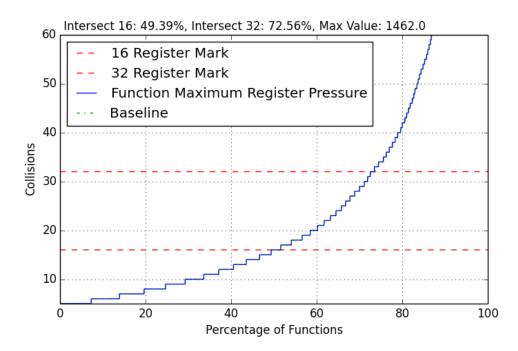

| 4.8    | Maximum Register Collisions by Function, All-Loops On                                                                      | 30   |

| 4.9    | Register Collisions by Register, All-Loops On                                                                              | 30   |

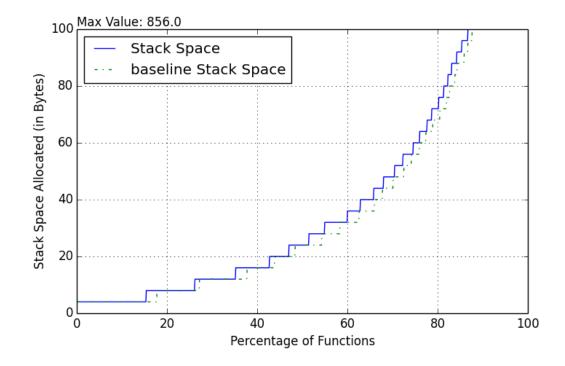

| 4.10   | Stack Space All-Loops On                                                                                                   | 31   |

| 4.11   | Average Register Collisions by Function, All-Loops Off                                                                     | 33   |

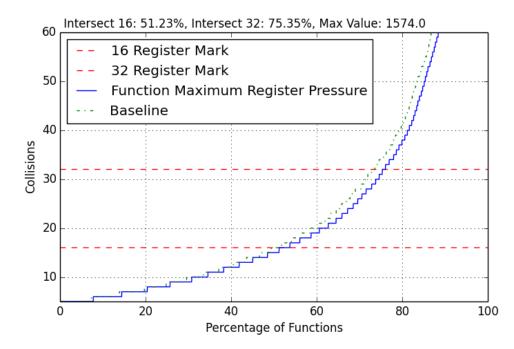

| 4.12   | Maximum Register Collisions by Function, All-Loops Off                                                                     | 33   |

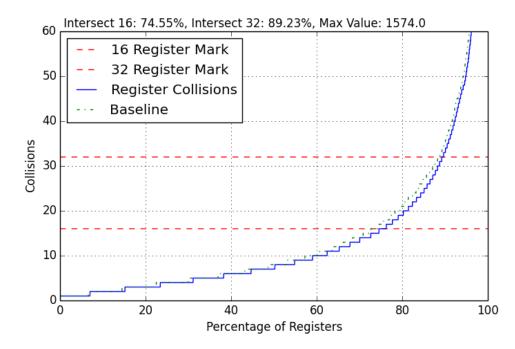

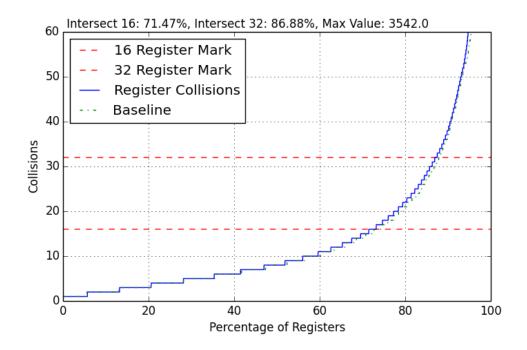

| 4.13   | Register Collisions by Register, All-Loops Off                                                                             | 34   |

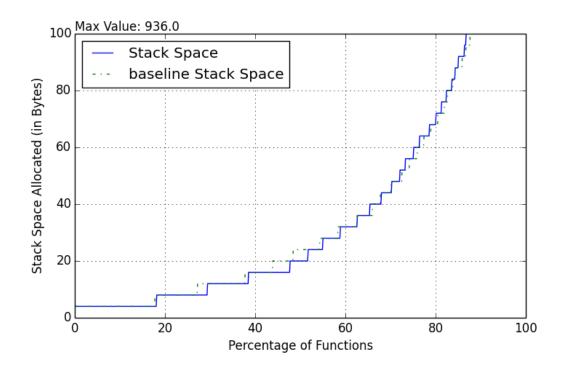

| 4.14   | Stack Space All-Loops Off                                                                                                  | 35   |

| 4.15   | x86 Average Register Collisions by Function,<br>Collision Statistics (Percentage at or Below Threshold)                    | 36   |

| 4.16   | x86 Maximum Register Collisions by Function,<br>Collision Statistics (Percentage at or Below Threshold)                    | 37   |

| 4.17   | x86 Register Collisions by Register<br>Statistics (Percentage at or Below Threshold)                                       | 37   |

| 4.18   | Stack On LICM                                                                                                              | 38   |

| 4.19 | Stack On Tail Call Elimination                                                                                     |

|------|--------------------------------------------------------------------------------------------------------------------|

| 4.20 | Stack Off LICM                                                                                                     |

| 4.21 | x86 Double Optimization Average Collisions by Function, CollisionStatistics (Percentage at or Below Threshold)42   |

| 4.22 | x86 Double Optimization Maximum Collisions by Function, CollisionStatistics (Percentage at or Below Threshold)42   |

| 4.23 | x86 Double Optimization Register Collisions by Registers, CollisionStatistics (Percentage at or Below Threshold)43 |

| 4.24 | Register Level On All-Loops and Argpromotion                                                                       |

| 4.25 | Register Collisions by Register Level OffAll-Loops and Argpromotion45                                              |

| 4.26 | Stack On All-Loops and Argpromotion                                                                                |

| 4.27 | Stack Off All-Loops and Argpromotion                                                                               |

| 4.28 | Stack On Licm and All-Loops                                                                                        |

| 4.29 | Stack Off, Licm and All-Loops                                                                                      |

| 4.30 | Stack On, Licm and Argpromotion                                                                                    |

| 4.31 | Stack Off Licm and Argpromotion                                                                                    |

| 4.32 | Thumb Average Register Collisions by Function Statistics 53                                                        |

| 4.33 | Thumb Maximum Register Collisions by Function Statistics $\dots$ 53                                                |

| 4.34 | Thumb Register Collisions by Register Statistics                                                                   |

| 4.35 | ARM Average Register Collisions by Function, All-loops Off $\ldots 55$                                             |

| 4.36 | ARM Stack Space All-loops Off 55                                                                                   |

| 4.37 | ARM Average Register Collisions by Function,Off Early-CSE-Memssa57                                                 |

| 4.38 | ARM Average Register Collisions by Function,Off Jump-Threading58                                                   |

| 4.39 | ARM Stack Space Off Early-CSE-Memssa                                                                               |

| 4.40 | ARM Stack Space Off Jump-Threading                                                                                 |

| 4.41 | Number of Spills in the x86 Architecture                                                                           |

| 4.42 | Number of Spills in the Thumb Architecture                                                                         |

| B.1  | THUMB Average Register Collisions by Function Statistics 69                                                        |

| B.2  | THUMB Maximum Register Collisions by Function Statistics 69                                                        |

| B.3  | THUMB Register Collisions by Register Statistics                                                                   |

| C.1  | x86 Average Register Collisions by Function, Off Licm                          | 70 |

|------|--------------------------------------------------------------------------------|----|

| C.2  | x86 Average Register Collisions by Function, On Licm                           | 71 |

| C.3  | x86 Maximum Register Collisions by Function, On Lic<br>m $\ \ .$               | 71 |

| C.4  | x86 Maximum Register Collisions by Function, Off Lic<br>m $\ \ .$              | 72 |

| C.5  | x86 Register Collisions by Register, On Licm                                   | 72 |

| C.6  | x86 Register Collisions by Register, Off Licm                                  | 73 |

| C.7  | x86 Average Register Collisions by Function,<br>Off Tail Call Elimination      | 73 |

| C.8  | x86 Average Register Collisions by Function,<br>On Tail Call Elimination       | 74 |

| C.9  | x86 Maximum Register Collisions by Function,<br>Off Tail Call Elimination      | 74 |

| C.10 | x86 Maximum Register Collisions by Function,<br>On Tail Call Elimination       | 75 |

| C.11 | x86 Register Collisions by Register, Off Tail Call Elimination                 | 75 |

| C.12 | x86 Register Collisions by Register, On Tail Call Elimination                  | 76 |

| C.13 | x86 Stack Space, Off Tail Call Elimination                                     | 76 |

| C.14 | x86 Average Register Collisions by Function, Off<br>All-Loops and Argpromotion | 77 |

| C.15 | x86 Average Register Collisions by Function, On<br>All-Loops and Argpromotion  | 77 |

| C.16 | x86 Maximum Register Collisions by Function,<br>Off All-Loops and Argpromotion | 78 |

| C.17 | x86 Maximum Register Collisions by Function,<br>On All-Loops and Argpromotion  | 78 |

| C.18 | x86 Average Register Collisions by Function,<br>On Licm and All-Loops          | 79 |

| C.19 | x86 Average Register Collisions by Function,<br>Off Licm and All-Loops         | 79 |

| C.20 | x86 Maximum Register Collisions by Function,<br>On Licm and All-Loops          | 80 |

| C.21 | x86 Maximum Register Collisions by Function,<br>Off Licm and All-Loops         | 80 |

| C.22 | x86 Register Collisions by Register,<br>On Licm and All-Loops                  | 81 |

| C.23 | x86 Register Collisions by Register,<br>Off Licm and All-Loops            | 81 |

|------|---------------------------------------------------------------------------|----|

| C.24 | x86 Average Register Collisions by Function,<br>On Licm and Argpromotion  | 82 |

| C.25 | x86 Average Register Collisions by Function,<br>Off Licm and Argpromotion | 82 |

| C.26 | x86 Maximum Register Collisions by Function,<br>On Licm and Argpromotion  | 83 |

| C.27 | x86 Maximum Register Collisions by Function,<br>Off Licm and Argpromotion | 83 |

| C.28 | x86 Register Collisions by Register,<br>On Licm and Argpromotion          | 84 |

| C.29 | x86 Register Collisions by Register,<br>Off Licm and Argpromotion         | 84 |

| C.30 | ARM Average Register Collisions by Function, On All-Loops                 | 85 |

| C.31 | ARM Maximum Register Collisions by Function, On All-Loops $~$             | 85 |

| C.32 | ARM Maximum Register Collisions by Function, Off All-Loops $~$            | 86 |

| C.33 | ARM Register Collisions by Register, On All-Loops                         | 86 |

| C.34 | ARM Register Collisions by Register, Off All-Loops                        | 87 |

| C.35 | ARM Stack Space, On All-Loops                                             | 87 |

| C.36 | ARM Average Register Collisions by Function,<br>On Early-CSE-Memssa       | 88 |

| C.37 | ARM Maximum Register Collisions by Function,<br>On Early-CSE-Memssa       | 88 |

| C.38 | ARM Maximum Register Collisions by Function,<br>Off Early-CSE-Memssa      | 89 |

| C.39 | ARM Register Collisions by Register, On Early-CSE-Memssa                  | 89 |

| C.40 | ARM Register Collisions by Register, Off Early-CSE-Memssa                 | 90 |

| C.41 | ARM Stack Space, On Early-CSE-Memssa                                      | 90 |

| C.42 | ARM Average Register Collisions by Function,<br>On Jump-Threading         | 91 |

| C.43 | ARM Maximum Register Collisions by Function,<br>On Jump-Threading         | 91 |

| C.44 | ARM Maximum Register Collisions by Function,<br>Off Jump-Threading        | 92 |

| C.45 | ARM Register Collisions by Register, On Jump-Threading                | 92 |

|------|-----------------------------------------------------------------------|----|

| C.46 | ARM Register Collisions by Register, Off Jump-Threading $\ . \ . \ .$ | 93 |

| C.47 | ARM Stack Space, On Jump-Threading                                    | 93 |

| D.1  | Number of Spills in the x86 Architecture<br>(Double Optimizations)    | 94 |

| D.2  | Number of Spills in the ARM Architecture<br>(Double Optimizations)    | 94 |

#### Chapter 1

## INTRODUCTION

The main purpose of a compiler is to generate code. It is generally desirable that the resulting code is fast. Multiple factors contribute to the performance of the generated code. Of utmost importance is proper utilization of the memory hierarchy and registers, in particular. Accessing a value in a register is orders of magnitude faster than retrieving a value from memory [12]. In addition, optimizing compilers transform the code to improve processor utilization. This thesis explores the effects of optimizations on register utilization.

To generate code, there are many phases that the compiler will go through to translate a high-level language such as Java or C into low-level assembly. This chapter gives a high-level overview of the compiler process, the optimizations, the motivation, and the contributions of this thesis.

#### 1.1 Register Collisions

A modern compiler might first parse the source file and create an Abstract Syntax Tree (AST) that represents the overall structure of the program. The AST is then converted into an intermediate representation (IR) and a control flow graph (CFG), which contains the instructions of the language. Any variables in the original language are translated to symbolic representations or virtual registers in the IR. Because a compiler can target many different architectures that have a different amount of physical registers, it assumes that it first has an unlimited number of virtual registers for use in the IR. The compiler can perform various optimizations to modify the code. Finally, the compiler performs register allocation where it targets the architecture that the code will run on.

Because the IR may use an unlimited amount of virtual registers, the compiler needs to map these virtual registers to the actual physical registers that the CPU architecture supports. One register allocation technique creates an interference graph where the graph nodes are the virtual registers and the edges represent when the virtual registers will hold values that are used at the same time. The edges in the interference graph are a representation of collisions between virtual registers. Register allocation is then reduced to a graph coloring problem where the physical registers are the colors. This coloring maps the virtual registers to physical registers. The number of edges is also linked to register pressure, which is a measure of the number of values that are simultaneously active or live and will ideally all be mapped to physical registers.

Loop:

L.D F0, 0(R1) ADD.D F4, F0, F2 S.D F4, 0(R1) DADDI R1, R1, -8 BNE R1, R2, Loop Loop:

L.D F0, 0(R1) ADD.D F4, F0, F2 S.D F4, 0(R1) L.D F0, -8(R1) ADD.D F4, F0, F2 S.D F4. -8(R1) DADDI R1, R1, -16 BNE R1, R2, Loop

Figure 1.1: Example of the loop-unrolling compiler optimization. Left side is original loop. Right side is with loop-unrolling applied.

#### 1.2 Optimizations

Code optimization is one of the many phases of the compiler that takes place before register allocation. When the code is in its IR, the compiler can perform various optimizations to the IR to improve the final target assembly. Each optimization might affect the use of virtual registers. If there are more virtual registers that are being used at the same time, we say that there is higher register pressure, so increasing the overlap of virtual registers may increase register pressure. Optimizations can also be run multiple times and in different orders to combat certain inefficiencies that other optimizations may introduce into the code and may make the overall code a bit more efficient.

For example, loop unrolling, a compiler optimization seen in Figure 1.1, duplicates the code within a loop. In the original code, there are five instructions for one iteration of the loop. After loop-unrolling, there are eight instructions for two iterations (or four instructions per iteration) of the loop. The duplicated code is updated to use the correct offset for an additional iteration and increment to get the next two iterations. Overall, we are able to save an instruction, which can save many CPU cycles if the loop is executed many times. This optimization can additionally expose opportunities for other optimizations such as simplifying consecutive L.D (load) and S.D (store) instructions. A drawback of this optimization is that more virtual registers may be introduced when unrolling the loop. This may increase register pressure to the point of causing a spill (the use of memory as a backing store for a register) to occur within the loop, which can be detrimental to performance. While optimizations are meant to make the overall code more efficient, they may actually hinder the runtime.

#### 1.3 Motivation

Previous studies have focused on improving the efficiency of register allocation through advanced heuristics [5, 20, 7]. Additionally, researchers have also looked at different ways of coloring the interference graph [8, 11]. This thesis explores how compiler optimizations might affect register pressure and whether the optimizations actually help or hinder the overall performance of the assembly.

### 1.4 Contributions

This paper explores the effects of select compiler optimizations on register collisions, which is related to register pressure and acts as an upper bound to register pressure. More specifically, we study register collisions across a suite of programs to measure general characteristics both with and without optimizations. To see if there is any significant change in register collisions, we modify *Clang*, which is the compiler front end for C/C++ and uses *LLVM* as its backend. This is used to gather register collisions and analyze the resulting assembly to see the effects on the stack space allocated for spills. This paper is organized as follows: Chapter 2 provides background information on the compiler phases we are looking at and the different elements that the optimizations will affect and discusses related work. Chapter 3 outlines the tool, implementations, experiments, and technologies used in this project. Chapter 4 presents an analysis of the gathered data. Finally, Chapter 5 proposes potential future work given the results of this study and concludes the paper.

#### Chapter 2

## BACKGROUND & RELATED WORKS

This section gives an overview of important background information related to the portion of the compiler that this work focuses on. A more in-depth explanation of the topics can be found in [21].

#### 2.1 Control-Flow Graph

The compiler creates a Control-Flow Graph (CFG) for each function to represent the flow of control through the function and to store instructions. A CFG contains nodes that represents basic blocks of code that may potentially be executed. As control flow constructs, such as an *if*, *else*, *while*, or *for* statement, are processed, new nodes are created to hold the instructions that lie within the basic blocks. An edge then connects from the previous node to any new nodes to signify potential paths along which execution of the code can follow.

An example of a CFG is given in Figure 2.1, where the left side contains the program code and the right side contains the corresponding CFG. The CFG construction process starts with a node to contain the instructions before a control-flow statement. When a control-flow statement is reached, new nodes are created to hold the code that may be executed along different paths, with edges connecting these paths. In this example, two new nodes are created, one node for the *if* block and one node for the *else* block. After creating the two nodes, an additional node is created that joins the two paths and that holds the rest of the code following the control-flow statement. When working with loops, a node may indirectly link to itself to execute the loop body multiple times. The nodes in Figure 2.1 contain C code for illustrative

#### Figure 2.1: Example of creating a CFG given a program

purposes, but would typically be translated to the IR the compiler is using and could eventually be translated to the target assembly.

## 2.2 Live Ranges

The compiler represents variables used in the original code and intermediate values as symbolic placeholders or virtual registers in the IR. Virtual registers are used as an abstraction of the actual target architecture. The compiler can potentially use a different number of virtual registers before and after optimizations. The live range of a register is the union of the sequences of instructions from each instruction that defines the register (i.e. targets it) to the last instruction that uses that definition.

Figure 2.2 gives an example of the live ranges of virtual registers. The bars depict the live range of each register. Note that v1 and v2 are not defined by these instructions so their live ranges begin prior to this code segment.

The compiler could use the same virtual register for a single identifier in the

Figure 2.2: Example of a live range with virtual registers

original source code throughout the IR and then allocate one physical register for that virtual register when coloring. This may cause that virtual register's live range to collide with many other registers and potentially make the graph uncolorable more often because there are less colors available to assign other virtual registers. To mitigate long live ranges, many compilers split the live range when a variable is redefined; this can be accomplished using static single assignment form (SSA). SSA uses a new virtual register each time a new value is computed and each variable definition is then updated within the compiler with that value. When that value is needed for computation again, the compiler will use the most recent virtual register as the representation for that value. This essentially splits the live range for each definition of a value used in the code and makes the resulting interference graph simpler. An example can been seen in Figure 2.3.  $v\beta$  and v4 are split into new virtual sub-registers each time they are assigned a new value. Note that in this example, under non-SSA  $v\beta$  conflicts with both v4 and v2. Under SSA,  $v3_0$  and v2conflict, but not with v4.

Figure 2.4 shows another example of how SSA form may be beneficial. Without SSA form, variable a's live range would collide with many of the other virtual registers in multiple blocks. By splitting a into different virtual registers  $a_1, a_2, a_3, a_4$ , variable

Figure 2.3: Example of Non-SSA form when compared to SSA form

a now has different pieces that intersect with only the other registers in its respective block. Note that the union of the sub-registers of a will effectively go back to non-SSA form of using one virtual register for a. SSA is primarily beneficial because it encodes the use-def chains (the most recent virtual register that contains the value needed) of the virtual registers and makes analysis and optimizations on the code more efficient [3, 10], but the partitioning of live ranges also provides benefits.

## 2.3 Register Allocation

Register allocation is the process of mapping the set of virtual registers to the more limited set of physical registers. There are various register allocation methods including linear scan [18], a combinatorial approach [19], and graph coloring [6]. This thesis frequently references, as a concrete example, a variation of the graph coloring approach which was introduced and formalized by Chaitin in 1982 [6]. Note that the effects of register pressure are independent of the graph coloring algorithm, but register pressure may affect how well the graph coloring algorithm performs. Chaitin's approach starts with building an interference graph and then applying a

Figure 2.4: Example of why SSA may be beneficial

graph coloring algorithm.

#### 2.3.1 Interference Graph

The interference graph contains information about which virtual registers are used concurrently with other virtual registers. In the interference graph, each virtual register is a node, and when the live ranges of two virtual registers intersect at any point in the IR, an edge connects the two corresponding nodes.

Recall the live ranges in Figure 2.2. In our example, v1 would need to be placed in a physical register and v2 would need to be placed in a different physical register because their values are live at the same time. Furthermore, in this example, v1 will have an edge to every other node in this subgraph because its live range intersects with all of them, whereas v2 will only have an edge to v1 and v3. From this simple example, we can see that an optimization that might move the print(v1) instruction immediately after the first instruction would reduce the live range of v1 and, thus, the number of edges found in the interference graph.

#### 2.3.2 Graph Coloring

The problem of register allocation as encoded in an interference graph reduces to a graph coloring problem. We want to assign physical registers to the virtual registers and the interference graph denotes when two registers cannot be in the same physical registers. We can then use the physical registers as the colors available to color the interference graph, guaranteeing that adjacent nodes (conflicting virtual regs) are assigned different colors (physical registers).

Graph coloring is an NP-Hard problem [14]. Because of the complexity of coloring a graph, there are a variety of graph coloring algorithms that reduce the time it takes to find a coloring at the cost of not being able to find a coloring unless the graph is simplified. Some of these expand on the original work of Chaitin, such as the Chaitin-Briggs algorithm [4], that focuses on using heuristics for simplifying the graph. Another approach to graph coloring is semidefinite programming that builds on the concept of 3-colorable graphs and approximates how many colors are actually needed to color the graph of k-colors [13].

If the graph coloring algorithm cannot find a proper coloring, it will insert spill code to effectively reduce the live range for that particular virtual register. The spill code includes a store instruction after the virtual register is defined and a load instruction right before the virtual register is used. Spilling makes the resulting code less efficient because of the extra instructions and the extra cycles the CPU needs to spend waiting for the value to be stored to or loaded in from memory. The quality of register allocation is thus dependent on compiler optimizations because optimizations may change live ranges and, in so doing, register pressure. The ideal final assembly code keeps all the values in fast registers and does not spill.

#### 2.4 Related Works

Some research related to register pressure and allocation focuses on developing heuristics to choose which register to spill or modifying the way the graph coloring algorithm chooses registers to color.

## 2.4.1 Heuristics

A way to reduce the costs of spills is to use heuristics to choose which register to spill. One heuristic is to look at program structure as a whole to avoid spills from being inserted in a spot that can cause the overall code to slow down. One method, the Callahan-Koblenz algorithm [9], looks at the overall program structure (e.g. the CFG and code blocks) and chooses registers to spill given those properties. It can also choose where to put the spill code to potentially avoid continuous memory accesses from happening within a loop and to choose the more ideal registers to spill.

Other studies try splitting or combining live ranges to change the interference graph presented to the graph coloring algorithm [16]. Another heuristic is to use the properties of nodes in the interference graph as seen in [5, 20, 7]. They look specifically at the interference graph and use properties of the graph to choose which register to spill. Common methods include removing the node with the highest amount of edges to find a coloring faster or analyzing and creating a directed graph from the interference graph to figure out which node can potentially split the graph into smaller subgraphs.

## 2.4.2 Graph Coloring Algorithm

Other related works look specifically at the graph coloring algorithm and propose changes to how to color the interference graph. In [8], a decoupled approach is taken by using both the graph coloring and linear scan methods. The method introduces spills early and takes advantage of both to assign the physical registers. Xavier, et. al. [11] compare the *basic*, *fast*, *greedy*, and *pbqp* graph coloring algorithms found in the clang compiler [15]. They concluded that the *greedy* algorithm produced code with fewer cache accesses and generated the least amount of spill code, but took the longest time to compile. They also concluded that *fast* and *basic* were good options if the goal is faster compile time.

#### Chapter 3

## SETUP & EXPERIMENTAL DESIGN

To examine the effects that compiler optimizations have on register pressure, we instrument the Clang/*llvm* compiler to report the number of collisions for each virtual register. Various optimizations are toggled to collect collision data under different configurations. This information is aggregated using Python to present a summary of the results.

#### 3.1 Clang and LLVM

This study uses the *llvm* version 5.0 ecosystem that has Clang as the C compiler and targets *llvm*. To explore the effects of optimizations on register collisions, various configurations of optimizations are explored. Clang has an optimization flag "-O3" that turns on all possible optimizations for the compiler. A complete list of the optimizations that are run with this flag can be found in Appendix A. The set of all possible configurations, however, is too expansive. Instead, this study focuses on configurations from a subset of optimizations deemed to potentially affect register pressure the most, but also considered to be potentially optional. This choice was made to limit the number of configurations with the hope of exposing edge case optimizations.

Below is a list of the optimizations included in this study, each with a short description. These were identified as likely to affect register pressure.

## loop-distribute

Distribute loops that cannot be vectorized due to dependence cycles. Tries

to isolate the offending dependencies into a new loop for vectorization of remaining parts.

## loop-rotate

Put loops into canonical form to expose opportunities for other optimizations.

#### loop-unroll

Perform loop unrolling utility to duplicate the body of the loop.

## loop-unswitch

Transform loops that contain branches on loop-invariant conditions to multiple loops based on a threshold.

#### loop-vectorize

Combine consecutive loop iterations into a single wide iteration. Index is incremented by SIMD vector width.

## argpromotion

Promote "reference" arguments to be "by value" arguments.

## $\mathbf{dse}$

A trivial dead store elimination that deletes local redundant stores.

## early-cse-memssa

An early simple dominator tree walk that eliminates trivially redundant instructions.

## globaldce

Global dead code elimination is designed to eliminate unreachable internal globals from the program.

## indvars

Canonicalize induction variables to transform induction variables to simpler forms suitable for subsequent analysis and transformation.

## jump-threading

Find distinct threads of control flow running through a basic block and if a predecessor of a block can prove to always jump to a successor, the edge is forwarded.

## licm

Loop invariant code motion attempts to remove as much code from the body of a loop as possible by hoisting code to a preheader block or sinking code to an exit block if safe.

#### memoryssa

Provides an SSA based form for memory with def-use and use-def chains for users to find memory operations quickly.

### $\operatorname{sccp}$

Sparse conditional constant propagation rewrites provably constant variables with immediate values and constant conditional branches with unconditional jumps.

#### $\mathbf{sroa}$

Scalar replacement of aggregates breaks up alloca instructions of aggregate types into individual alloca instructions for each member and transforms them into clean scalar SSA form.

## tailcallelim

Tail Call Elimination transforms a call from the current function that does not access the stack frame before executing a return instruction into a branch to the entry of the function being called.

Data is collected for the following configurations based on the experiment's subject optimization. There are two starting baselines. For the first baseline, we have the set of -O3 optimizations turned on with the subject list turned off. We then turn on each of the subjects independently. For the second baseline, we start with the full -O3 optimizations and then turn each of the subjects independently off. Additional experiments were run by combining subjects based on analysis of these initial configurations and what we thought would greatly affect register collisions based on the nature of the subjects.

These experiments are conducted over multiple steps. First, a source file to examine is compiled to *llvm* using clang. This step does not perform any compiler optimizations. The *llvm* files are then run through *opt*, with applicable compiler optimization flags, to produce another *llvm* file with the optimizations applied.

Once the *llvm* files for each configuration in the set are created, each *llvm* file is processed by *llc*, which will compile the *llvm* file to create an assembly file. As part of compilation, *llc* builds the interference graph and performs register allocation to assign the virtual registers to physical registers of the target machine. We modified *llc* to write to a JSON file with the information of which virtual registers collide with other virtual registers. We do this instrumenting *llc*'s *basic* register allocator, right before the coloring algorithm takes place, to report register collisions. The instrumentation code loops through all possible pairs of virtual registers and calls clang's **overlaps** function, which returns true if a virtual register overlaps with another one. If it is true, the two registers are logged to a JSON file. Note that the modified *llc* outputs a JSON file per function and that this information is enough to rebuild the interference graph representation that is used for coloring.

## 3.2 Aggregation

Once the register information is in the JSON files, a Python script is run to count the number of register collisions and to aggregate the data. To get a sense of the register collisions per function, the maximum number of collisions and the average number of collisions are calculated. This data is analyzed at the function level and across all functions. To see the effects of register collisions at a register level, the number of collisions for each individual register is also calculated. Finally, to see the effects that register collisions may have on stack space, the stack size data is gathered from the generated assembly files. This is done by processing the assembly file for the comment "-byte spill", which indicates that there is spill code inserted at that line in the code. This comment also includes a number before indicating how many bytes were allocated on the stack for the spill so we sum the bytes together.

*MatPlotLib* is used to graph all the data. The resulting graphs show, for each subject optimization toggled on and off, the average and max register collisions across functions, the number of collisions of registers across registers, and the stack size generated.

### 3.3 Benchmarks

The benchmarks include programs from the SPEC CPU2000 Benchmarks [2] and programs downloaded from Github. This set represents a sampling of real-world programs. Below is a list of the programs along with a brief description of what they do:

164.gzip - GNU zip compression algorithm.

175.vpr - Versatile place and route algorithm for an integrated circuit computeraided design program.

**176.gcc** - Gcc version 2.7.2.2 that generates code for a Motorola 88100 processor.

**181.mcf** - Derived from a program used for single-depot vehicle scheduling in public mass transportation.

**186.crafty** - High-performance computer chess program made around a 64-bit word.

**197.parser** - Link grammar parser is a syntactic parser of English, based on a link grammar.

**253.perlbmk** - A cut-down version of perl v5.005\_03, the once popular scripting language.

**254.gap** - A standard gap-speed benchmark exercising combinatorial functions, a big number library, and test functions for a finite field.

**255.vortex** - A single-user, object-oriented database transaction benchmark which exercises a system kernel coded in C.

**256.bzip2** - Compression and decompression algorithm extending bzip that performs no file I/O other than reading input.

**300.twolf** - Algorithm that determines placement and local connections for groups of transistors which constitute the microchip.

capnproto - A protocol for sharing data capabilities.

ccv - A portable modern computer vision library.

CHL - A hypertext library for writing web applications in C.

**crypto-algorithms** - Standard implementations of cryptographic algorithms such as AES and SHA1.

dht - A variant of Kademlia distributed hash table used in a bittorrent network.

hiredis - A minimalistic C client library for the Redis database.

http-parser - A Parser for HTTP messages in C that parses both requests and responses.

huffman - An implementation of the huffman lossless data compression algorithm.

**Kore** - A scalable and secure web application framework for writing web APIs in C.

lz4 - A fast lossless compression algorithm.

SilverSearcher - A code searching tool similar to ack with a focus on speed.

SQLite - A lightweight portable database system written in C.

zlib - A general purpose data compression library.

#### Chapter 4

## **RESULTS & ANALYSIS**

This section covers the results of each configuration of optimizations. We start by covering the baseline configuration (i.e. average register collisions across functions, maximum register collisions across functions, register collisions across registers, and the stack space). We then move onto analyzing specific configurations that give interesting results and then discuss general trends. Analysis of the effects of two optimizations toggled on or off together follows. We conclude by comparing the x86 architecture to the Thumb (ARM) architecture to see if there are any interesting differences between them.

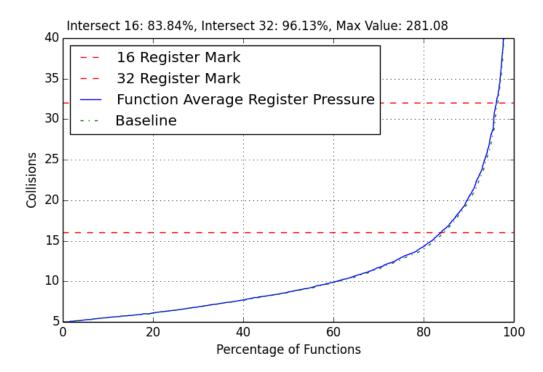

The graphs include a line at the 16 and 32 register collision points because these are common sizes for a processor's register file. For example, on the x86-64 architecture, there are 32 registers available, but only about 16 are used for the current program running. Note that some of those 16 registers are reserved for the stack pointer, program counter, and passing variables to functions to run the program so the actual registers available may actually be less.

To avoid trivial functions that are too simple and that do not provide any interesting register collision statistics, a check for functions that have at least five register collisions is included in the script. An example of the graph with no threshold can be seen in Figures 4.1 and 4.2, but for the rest of the graphs, we have the threshold script on. This check effectively zooms in on the portion of the graph that is more likely to be affected by the optimizations. This removes most trivial functions and makes it easier to spot differences between optimizations. Note that there is one function found in the gcc benchmark that has a switch statement that extends over roughly 2,000 lines of code and 374 cases. This function is one of the many contributors, among a couple of others, to cause larger numbers to appear in the graphs. For register collisions by register, we include every single register regardless of whether the function met the requirements.

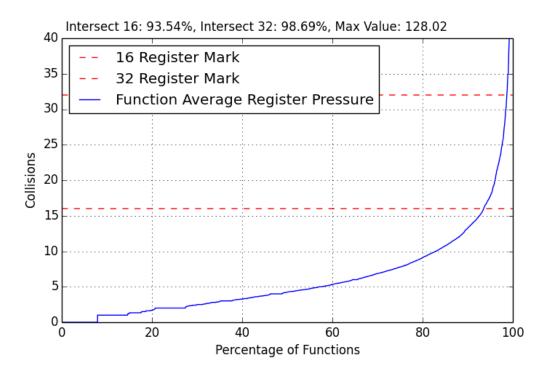

Figure 4.1: Average Reg Collisions by Function, Baseline All Subject Optimizations Off, No Minimum Register Collisions Threshold

### 4.1 Baseline Graph Anaylsis

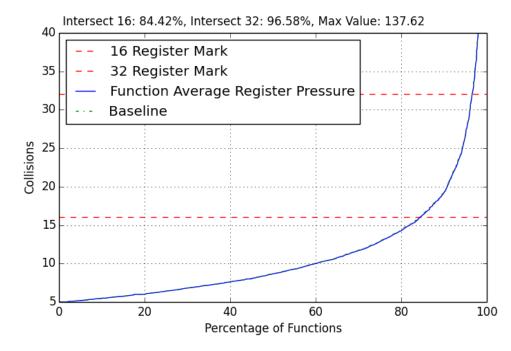

#### 4.1.1 Average Register Collisions Across Functions

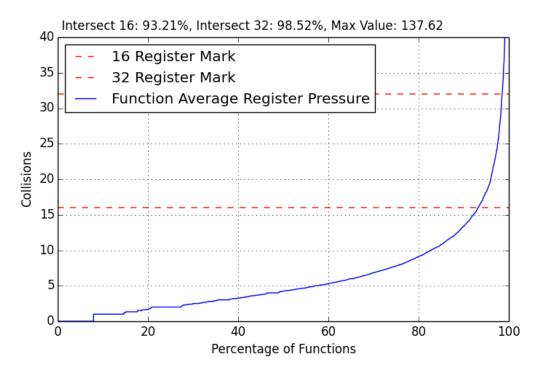

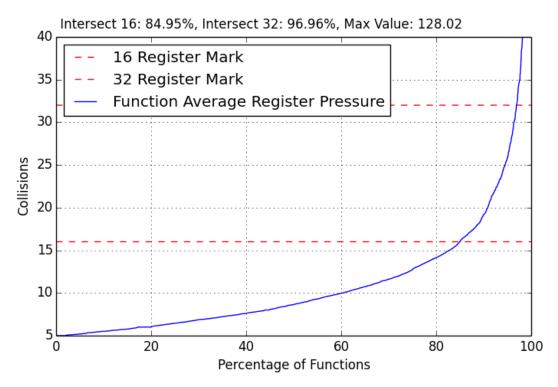

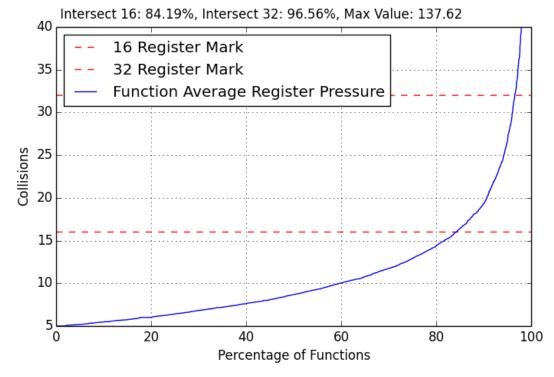

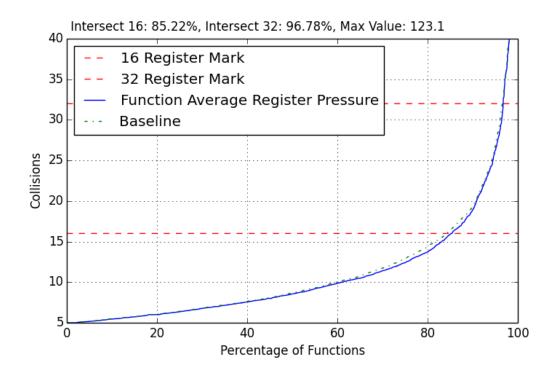

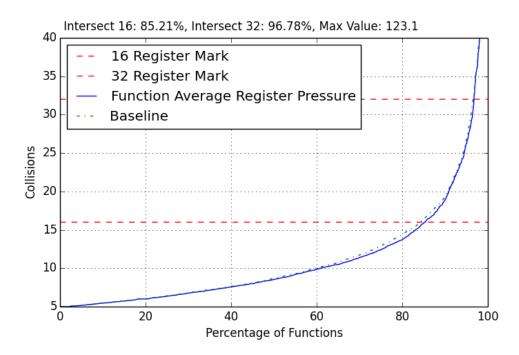

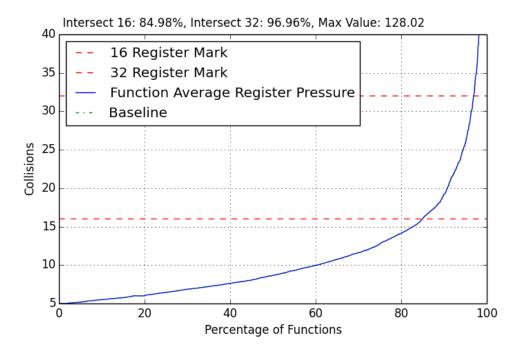

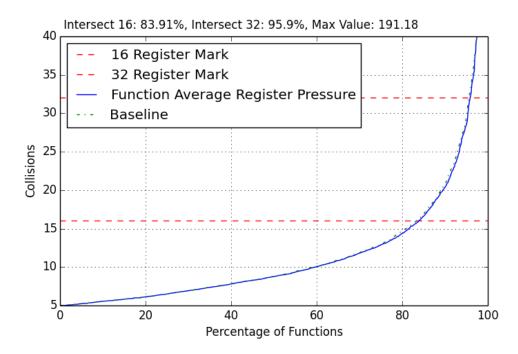

The baseline average register collisions across functions, with subject optimization on and off, look relatively similar. The interesting points are that when all subject optimizations are off, shown in Figure 4.3a, 84.95% of functions are below 16-collisions. In Figure 4.3b, 84.19% of functions are below the 16-register mark for all subject optimizations on. Looking at the average register collisions per function, compiler optimizations overall increased register collisions across all functions. The maximum

Figure 4.2: Average Reg Collisions by Function, Baseline All Subject Optimizations On, No Minimum Register Collisions Threshold

number of collisions that occur in average register collisions however, increased from 128.02 to 137.62 collisions from optimizations off to on, respectively.

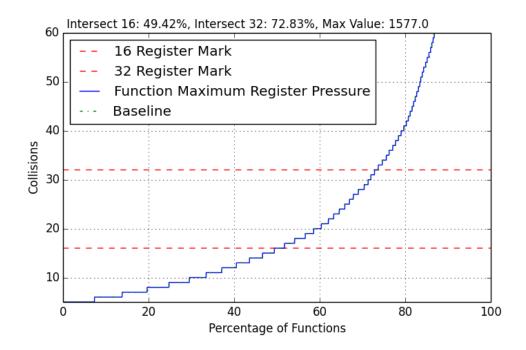

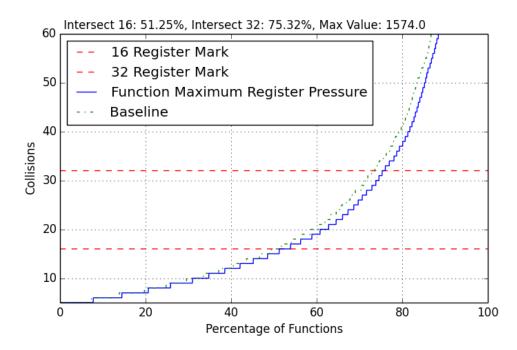

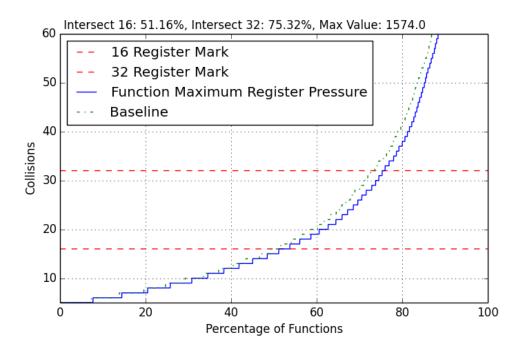

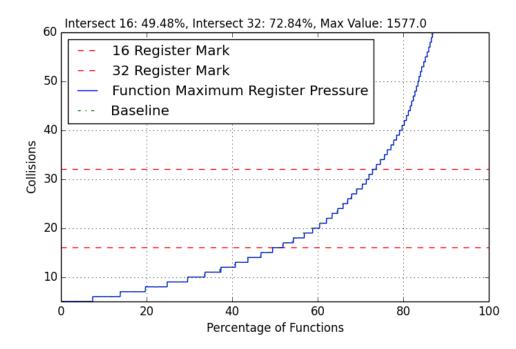

#### 4.1.2 Maximum Register Collisions Across Functions

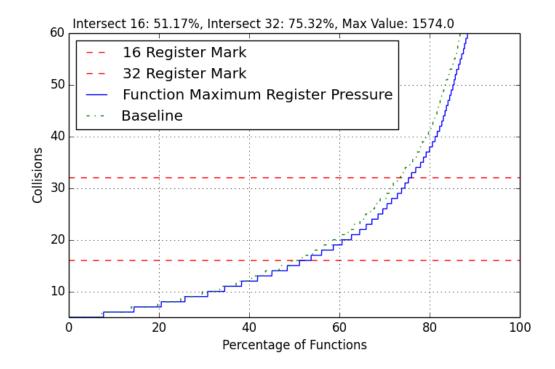

The baseline maximum average register collisions across functions are different for subject optimizations on and off. Because the maximum register collision value is taken per function and it has a better chance of meeting the requirements of at least five collisions for the script, there are more data points for this graph compared to the average register collisions across functions. In Figure 4.4a, the 16-register mark is at 49.31% for all optimizations off. In Figure 4.4b, the 16-register mark is at 49.42% for all optimizations on. At the maximum register collision level, the effects of optimizations differ from the trend that happens on an average level. Turning on

(a) Average Reg Collisions by Function, Baseline All Subject Optimizations Off

(b) Average Reg Collisions by Function, Baseline All Subject Optimizations On

optimizations actually caused an extra 0.11% of functions to now meet the 16 collisions mark. Overall on the graph, there are slight shifts of the line to the right signifying smaller maximum values for a few functions. Functions towards the 80-100% range do seem to increase slightly in maximum register collisions (line is slightly towards the left). Looking at the maximum value in the graph, there was an in increase from 1463 to 1577 collisions, so the optimizations did increase the maximum collisions for a function by a significant amount in that range.

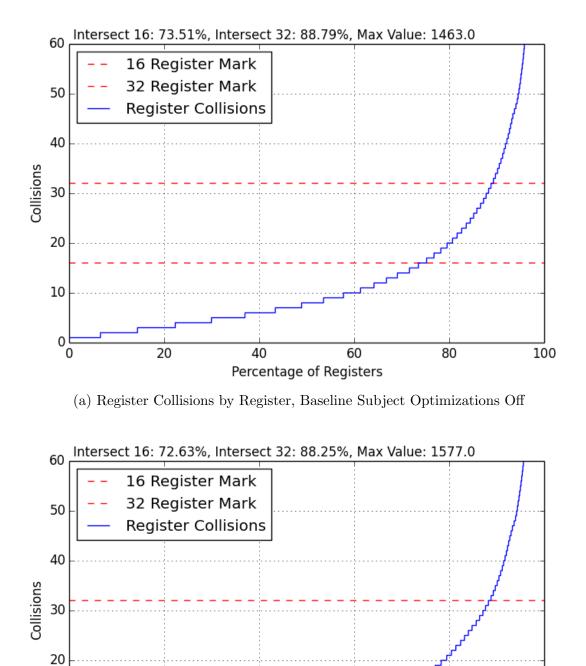

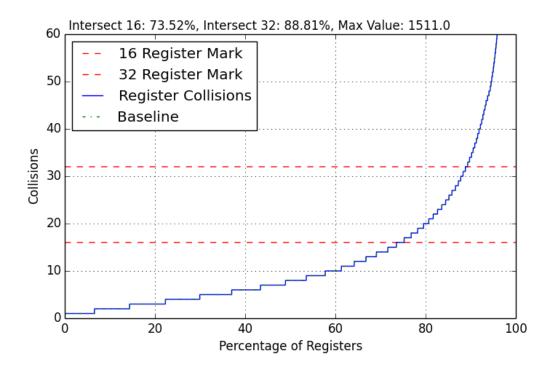

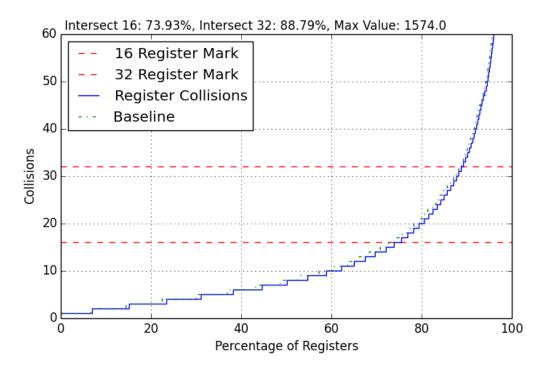

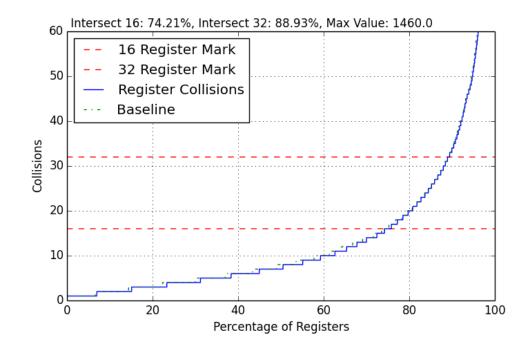

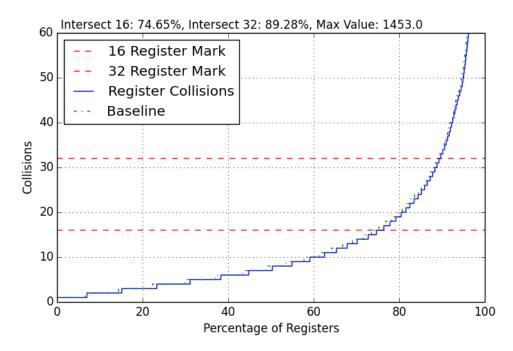

#### 4.1.3 Register Collisions Across Registers

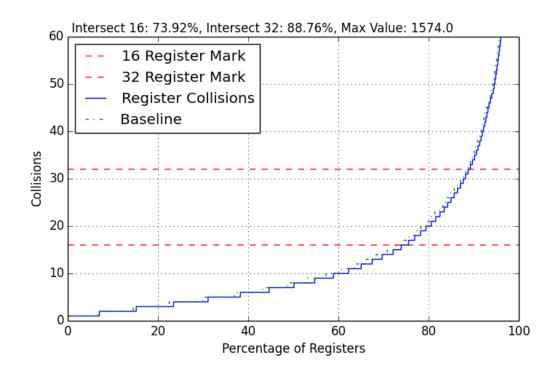

The baseline for average register collisions on the register level has a slight difference as seen in Figures 4.5b and 4.5a. All subject optimizations on when compared to all subject optimizations off increases the amount of collisions that happen. The data shows that 0.88% of registers are increased to above or at the 16-intersection line, 0.54% of registers are increased to above or at the 32-intersection line, and the maximum collisions has increased by 114.

This data is consistent with the average register collisions per function graph. The difference between the on and off optimization baselines is small and the amount of registers that changed reflected that. Note that the change in the number of collisions is minimal and the number does not get higher until the later ranges. With more registers colliding with other registers, it caused some functions to increase in register collisions and caused the average and maximum values to increase for some parts. Observe that at around the 15% range, the collisions for some registers were decreased, which explains why the maximum register collisions by functions decreased slightly for some of the functions in the previous graphs. Overall, most registers experience an increase in number of collisions.

(a) Maximum Reg Collisions by Function, Baseline All Subject Optimizations Off

(b) Maximum Reg Collisions by Function, Baseline All Subject Optimizations On

(b) Register Collisions by Register, Baseline Subject Optimizations On

Percentage of Registers

Figure 4.5: Baseline Register Collisions by Register

(b) Stack Space Baseline All Subject Optimizations On

Figure 4.6: Baseline Stack Space

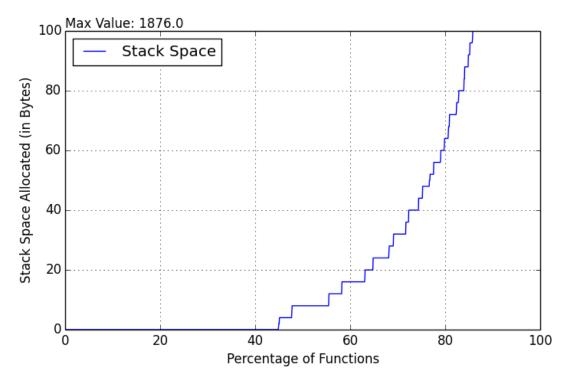

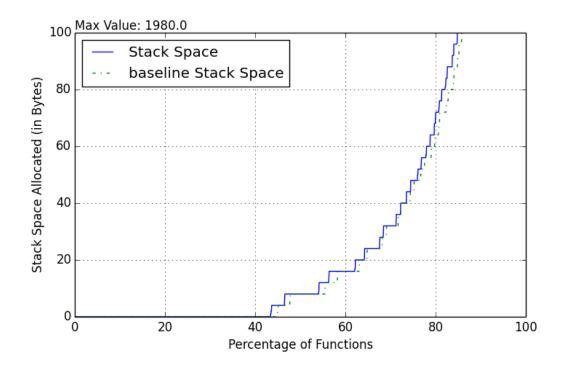

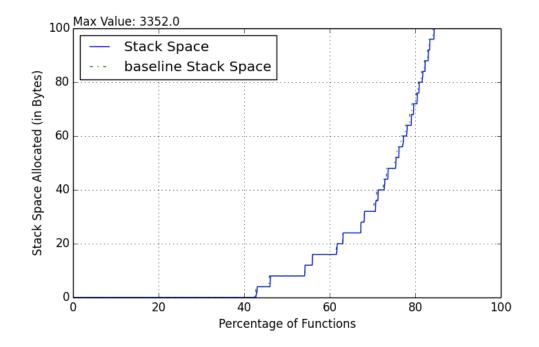

#### 4.1.4 Stack Space

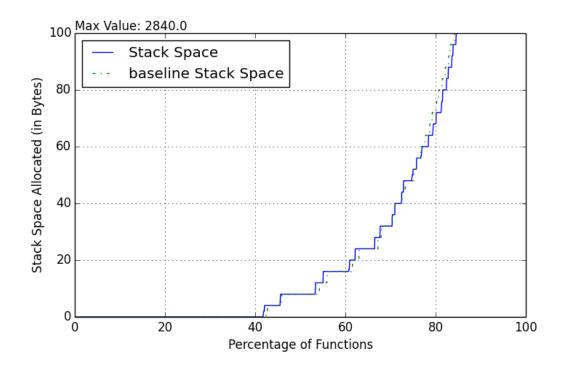

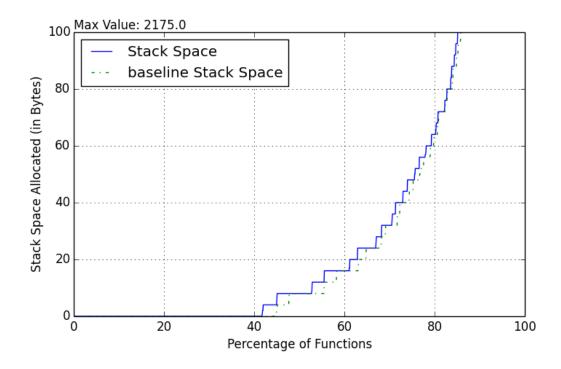

The stack space caused by spills differed by a significant amount when comparing the configurations for all subject optimizations on versus all subject optimizations off. By turning on optimizations, about 2.7% of functions have more spills and their stack space allocated increased. The maximum stack space increased from 1876 bytes for no optimizations to 3352 bytes for having all optimizations on.

The stack space data agrees with the rest of the baseline graphs. Generally, having subject optimizations on increased the amount of register collisions that occured at the function and register level. At the function level, it increased certain functions slightly. At the register level, it caused more registers to collide with each other. The maximum number of collisions also increases by 114 and thus it causes the stack space to increase. This shows that although compiler optimizations are meant to help clean up code and make it more efficient, it may actually hinder performance by introducing many spills.

### 4.2 All-Loops Configuration

For this configuration, any optimizations that have to deal with loops are grouped and toggled on or off together. The optimizations grouped together include: loopdistribute, loop-rotate, loop-unroll, loop-unswitch, and loop-vectorize.

#### 4.2.1 All-Loops Optimization On

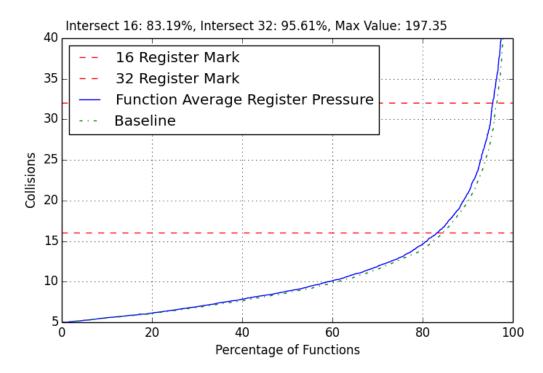

The *all-loops* configuration on (with other subject optimizations off) did not particularly change register collisions as seen in Figure 4.7. At the 16-collisions line, 84.94% of functions meet the line compared to the baseline value of 84.95%. So 0.01% of functions experienced an increase in register collisions slightly. The 32-collisions line and maximum value stayed the same.

Figure 4.7: Average Register Collisions by Function, All-Loops On

Looking at the maximum register collisions in Figure 4.8, the *all-loops* optimization also did not seem to change much from the baseline. It increased maximum register collisions by function overall by 0.01% at the 16-collisions line and by 0.02%at the 32-collisions line. *All-loops* very slightly increases register collisions by function for a few functions.

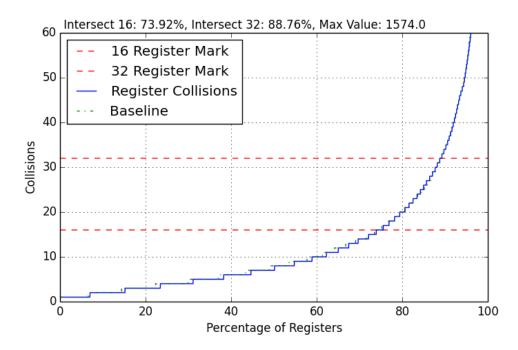

The results of *all-loops* increasing register collisions can be seen in Figure 4.9. At the register level, *all-loops* does not seem to affect register collisions at all. The line created by turning the subject optimization on does not seem to change the amount of register collisions or changes an insignificant amount of them to notice from the graph.

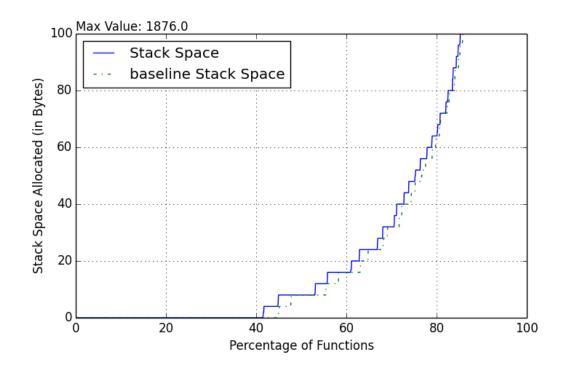

The effects of turning *all-loops* on can be seen when we look at the stack space

Figure 4.8: Maximum Register Collisions by Function, All-Loops On

Figure 4.9: Register Collisions by Register, All-Loops On

Figure 4.10: Stack Space All-Loops On

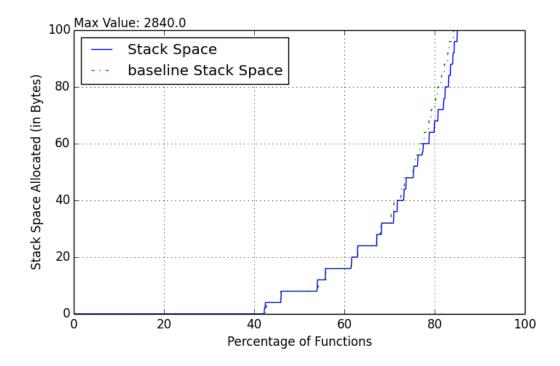

allocated in the assembly files in Figure 4.10. Functions, overall, now allocate more stack space due to spills. The maximum value for stack space is also increased by 104 bytes when compared to the baseline. Looking at the generated assembly code, specifically at loops and spills that happen within loops, more spills seem to occur in the main body of the loop and less spills occur at the beginning of the loop where offsets are calculated. These optimizations are expected to cause more spills when turned on mainly because *loop-unroll* unrolls loops and adds more register usage within the body of the loop. This may cause more spills to occur in that area. *Loopdistribute* and *loop-vectorize* attempt to minimize the amount of offset calculations by vectorizing offsets, thus more spills are removed at the beginning or ending of the loops where offsets for the next iteration are calculated. Generally, more spills happen with the loop optimizations and as a result, they increase stack space for functions. The register collisions that we saw earlier, however, did not seem to reflect these changes. In the assembly code, the number of registers stayed the same, but the placement of their live-ranges was shifted. To cause the spill, the live ranges were probably shifted in such a way that the coloring algorithm had to spill to be able to color the interference graph. Another reason why register collisions did not shift much is probably the lack of other optimizations. The loop optimizations may depend on other optimizations to open up opportunities for the optimization to be able to actually be useful to register collisions.

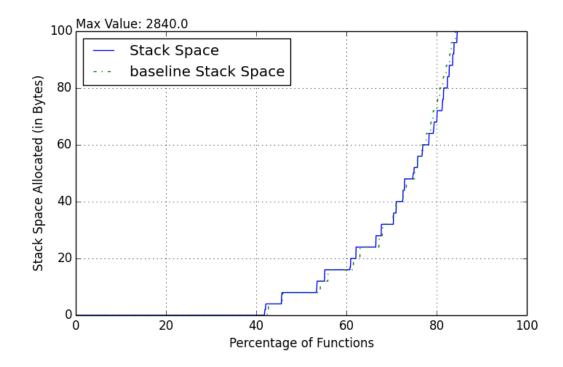

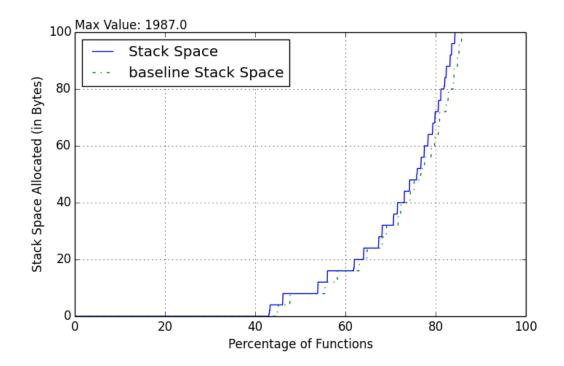

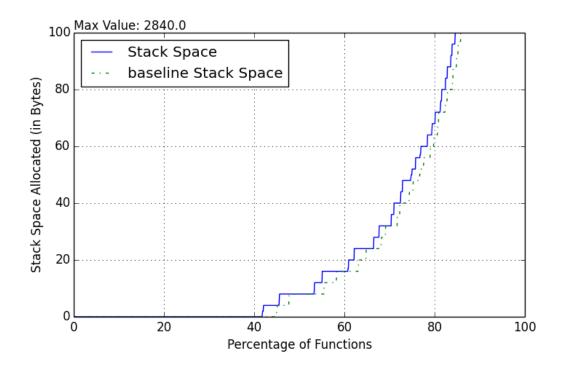

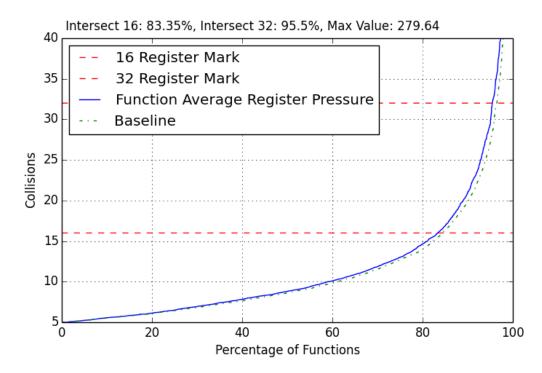

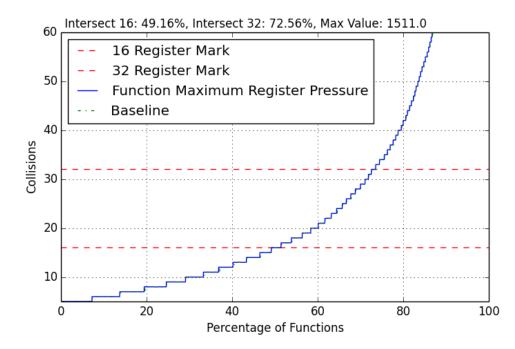

## 4.2.2 All-Loops Optimization Off

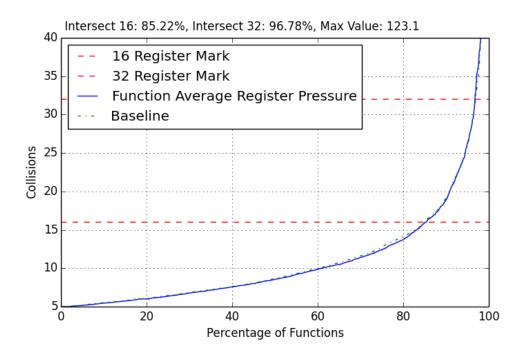

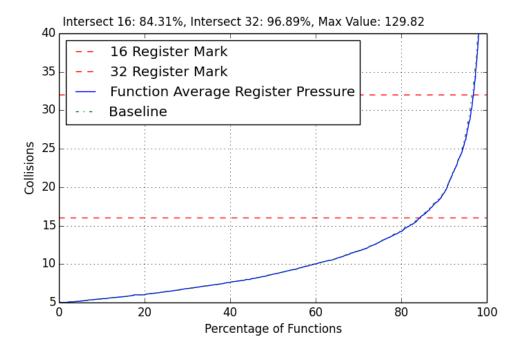

Toggling *all-loops* off helps functions reduce average register collisions by function from the 40-95% range as seen in Figure 4.11. This is seen by observing that the line moves to the right of the original baseline. This means that not having any loop optimizations actually helps reduce average register collisions for many functions. 1.03% of functions were now able to meet the 16-register collision mark when compared to having all subject optimizations on. The 32-collisions threshold changes slightly by 0.22% more functions that now meet that mark. The maximum register collisions was also reduced from 137.62 to 123.1 collisions between the baseline and *all-loops* configuration.

Comparing the maximum register collisions by function for *all-loops* to the baseline, we see another reduction in register collisions as seen Figure 4.12. At 16collisions, there is a difference of 1.75% functions that now have 16-collisions with *all-loops* turned off. The difference gets larger with a value of 2.47% at the 32collisions line and those functions actually have slightly increased register collisions. The maximum value is reduced by 3 register collisions. Overall from the 55-100% range, there is a reduction of about 1-4 collisions and more functions were shifted to have a lower maximum register collision by function.

Figure 4.11: Average Register Collisions by Function, All-Loops Off

Figure 4.12: Maximum Register Collisions by Function, All-Loops Off

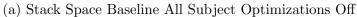

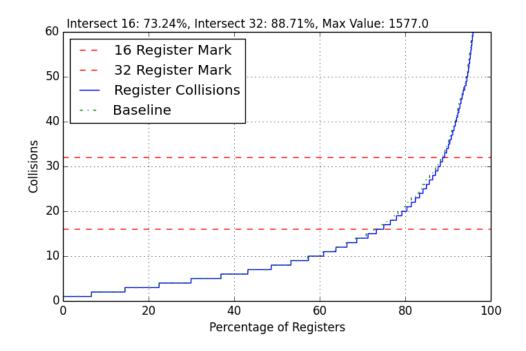

The register collisions at the by-register level behave as one would expect when following the pattern of what has been happening in the average and maximum register collisions by-function as seen in Figure 4.13. When *all-loops* is turned off, the register collisions are decreased by a small amount for a small percentage of registers. About 1.29% of registers are shifted downward to meet the 16-collisions line and 0.51% of registers are also shifted downward to meet the 32-collisions line. Looking at the maximum value, the number of collisions is reduced by 3.

Figure 4.13: Register Collisions by Register, All-Loops Off

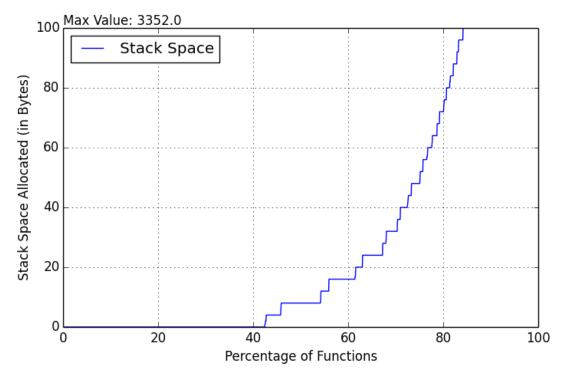

The stack space change resulting from turning off *all-loops* varies as seen in Figure 4.14. The stack space increases for roughly 23% of functions starting at the 42% mark, but then it reduces starting at around the 77% mark. Turning off *all-loops* also reduced the maximum stack space, when compared to the baseline of all optimizations on, by 512 bytes. This is interesting, because for some functions, having *all-loops* on helps reduce spills and for other functions, it increased spills. Within the

assembly code, the registers did not have their live ranges shifted around from the loop optimizations, so the spills that occur within the loops are not observed. The general difference of the structure of the code is that the spills occur outside of loops, in the header, or other blocks because of the other optimizations affecting the code.

Figure 4.14: Stack Space All-Loops Off

# 4.3 General Observations

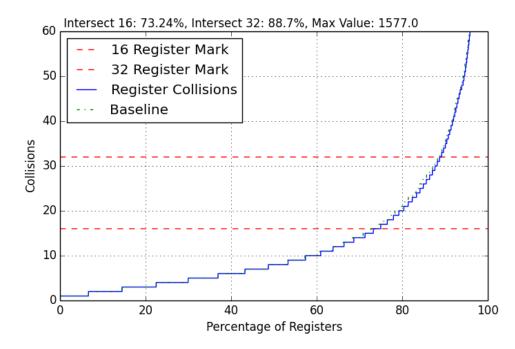

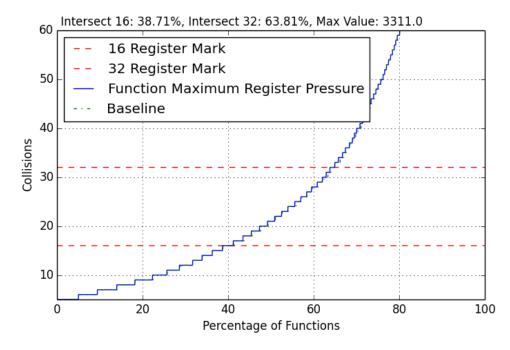

Many of the other configurations produced about the same results. The graphs for average function, maximum function, and register level collisions for the general optimization case can be seen in the appendix. To give a better sense of how the optimizations affect register collisions, we aggregate all the data for register collisions and put them in the chart as seen in Figures 4.15, 4.16, and 4.17. The "Off" means that all optimizations were on and the corresponding optimization is turned off and vice versa for "On". For baseline "Off", nothing is turned off or they are all on and vice versa for "On". Looking at the tables, many of the optimizations give about roughly the same results, with the exception of a few, when comparing the numbers between each single toggle optimization. In particular, *argpromotion* seemed to have the highest change in average register collisions by function and reduced it. *Jump-threading* seemed to change the maximum register collisions the most for the maximum column. It has 1577 collisions (the highest increase) when turning it on and 1514 collisions when turning it off. *Licm* is another interesting optimization that seemed to deviate from the pattern of the other optimizations in register collision by registers. Many of the other optimizations have around 72.6% of functions that hit the 16-collisions line when turning it off, but *licm* is at 73.24% of functions that hit the 16-collisions line (slightly below the value of *all-loops*).

| X86              | Avg-Off-16 | Avg-Off-32 | Avg-Off-Max | Avg-On-16 | Avg-On-32 | Avg-On-Max |

|------------------|------------|------------|-------------|-----------|-----------|------------|

| baseline         | 84.19      | 96.56      | 137.62      | 84.95     | 96.96     | 128.02     |

| all-loops        | 85.22      | 96.78      | 123.1       | 84.94     | 96.96     | 128.02     |

| argpromotion     | 84.14      | 96.56      | 137.62      | 85.71     | 97.2      | 123.65     |

| dse              | 84.17      | 96.56      | 137.62      | 85.69     | 97.2      | 123.65     |

| early-cse-memssa | 84.32      | 96.63      | 129.25      | 85.65     | 97.11     | 123.85     |

| globaldce        | 84.19      | 96.56      | 137.62      | 85.7      | 97.2      | 123.65     |

| indvars          | 84.4       | 96.62      | 141.38      | 85.67     | 97.09     | 121.98     |

| jump-threading   | 84.09      | 96.51      | 139.12      | 85.69     | 97.17     | 122.73     |

| licm             | 84.36      | 96.89      | 129.82      | 85.57     | 97        | 124.8      |

| memoryssa        | 84.19      | 96.56      | 137.62      | 85.7      | 97.2      | 123.65     |

| sccp             | 84.19      | 96.56      | 137.62      | 85.7      | 97.2      | 123.65     |

| sroa             | 84.2       | 96.55      | 137.62      | 85.63     | 97.18     | 123.65     |

| tailcallelim     | 84.42      | 96.58      | 137.62      | 85.51     | 97.15     | 123.65     |

Figure 4.15: x86 Average Register Collisions by Function, Collision Statistics (Percentage at or Below Threshold)

## 4.3.1 Stack Space On Optimization

Looking at the general stack space "on" configurations, all of the optimizations that were toggled "on" increased the amount of spills that occurred in the assembly

| X86              | Max-Off-16 | Max-Off-32 | Max-Off-Max | Max-On-16 | Max-On-32 | Max-On-Max |

|------------------|------------|------------|-------------|-----------|-----------|------------|

| baseline         | 49.42      | 72.85      | 1577        | 49.31     | 72.62     | 1463       |

| all-loops        | 51.17      | 75.32      | 1574        | 49.3      | 72.6      | 1463       |

| argpromotion     | 49.48      | 72.88      | 1577        | 51.08     | 75.15     | 1460       |

| dse              | 49.41      | 72.85      | 1577        | 51.22     | 75.21     | 1460       |

| early-cse-memssa | 49.38      | 72.92      | 1506        | 51.16     | 75.22     | 1451       |

| globaldce        | 49.42      | 72.85      | 1577        | 51.2      | 75.21     | 1460       |

| indvars          | 49.55      | 72.8       | 1577        | 51.15     | 75.04     | 1460       |

| jump-threading   | 49.25      | 72.76      | 1514        | 51.28     | 75.38     | 1577       |

| licm             | 49.42      | 72.83      | 1577        | 51.18     | 75.15     | 1460       |

| memoryssa        | 49.42      | 72.85      | 1577        | 51.2      | 75.21     | 1460       |

| sccp             | 49.42      | 72.85      | 1577        | 51.2      | 75.21     | 1460       |

| sroa             | 49.43      | 72.84      | 1577        | 51.19     | 75.23     | 1460       |

| tailcallelim     | 49.24      | 72.79      | 1584        | 51.28     | 75.31     | 1453       |

Figure 4.16: x86 Maximum Register Collisions by Function, Collision Statistics (Percentage at or Below Threshold)

| X86              | Reg-Off-16 | Reg-Off-32 | Reg-Off-Max | Reg-On-16 | Reg-On-32 | Reg-On-Max |

|------------------|------------|------------|-------------|-----------|-----------|------------|

| baseline         | 72.63      | 88.25      | 1577        | 73.51     | 88.79     | 1463       |

| all-loops        | 73.92      | 88.76      | 1574        | 73.51     | 88.79     | 1463       |

| argpromotion     | 72.64      | 88.26      | 1577        | 74.85     | 89.35     | 1460       |

| dse              | 72.63      | 88.27      | 1577        | 74.85     | 89.34     | 1460       |

| early-cse-memssa | 72.75      | 88.3       | 1506        | 74.78     | 89.29     | 1451       |

| globaldce        | 72.63      | 88.25      | 1577        | 74.84     | 89.34     | 1460       |

| indvars          | 72.77      | 88.3       | 1577        | 74.77     | 89.2      | 1460       |

| jump-threading   | 72.55      | 88.15      | 1514        | 74.92     | 89.41     | 1577       |

| licm             | 73.24      | 88.71      | 1577        | 74.21     | 88.93     | 1460       |

| memoryssa        | 72.63      | 88.25      | 1577        | 74.84     | 89.34     | 1460       |

| sccp             | 72.63      | 88.25      | 1577        | 74.84     | 89.34     | 1460       |

| sroa             | 72.63      | 88.2       | 1577        | 74.85     | 89.38     | 1460       |

| tailcallelim     | 72.84      | 88.35      | 1584        | 74.65     | 89.28     | 1453       |

Figure 4.17: x86 Register Collisions by Register Statistics (Percentage at or Below Threshold)

Figure 4.18: Stack On LICM

slightly, but most of the maximum values stayed the same. *Jump-threading* is an optimization that did reduce stack space for many of the functions and reduces the maximum stack space by 128 bytes. Turning this optimization on gave the best result in terms of stack space when compared to the stack spaces created by other optimizations.

The optimization that seemed to increase the stack space the most for many functions is *licm* followed by *tailcallelim* as seen in Figure 4.18 and 4.19. The full graphs for these can be found in Appendix C.1 - C.6 and C.7 - C.13.

Upon closer inspection of the register collision numbers, *licm* and *tailcallelim* did not seem to differ greatly from the pattern that other optimizations have across register collisions. In the assembly, for *licm-on* configuration, there are a couple more lines of code in the loop preheader that load values into registers. For *tailcallelim*,

it changes multiple recursive calls into one recursive call, with an extra branch that jumps back to the original block and creates a loop. In a particular example, found in *huffman*, *tailcallelim* actually caused an extra spill to occur because of the loop back into the block.

Generally, both of these optimizations move code from blocks to other blocks or create more blocks to increase performance, and they both end up increasing the amount of spills by the greatest amount according to the graphs. A possible cause could be the way that these optimizations move code around. They extend live ranges for certain registers and may affect the interference graph in such a way that it causes the graph coloring algorithm to spill more before it actually becomes colorable.

Figure 4.19: Stack On Tail Call Elimination

Figure 4.20: Stack Off LICM

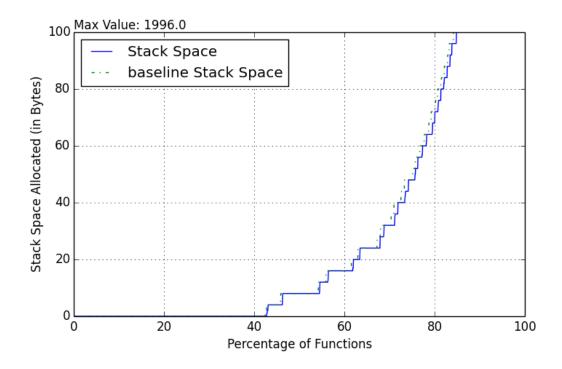

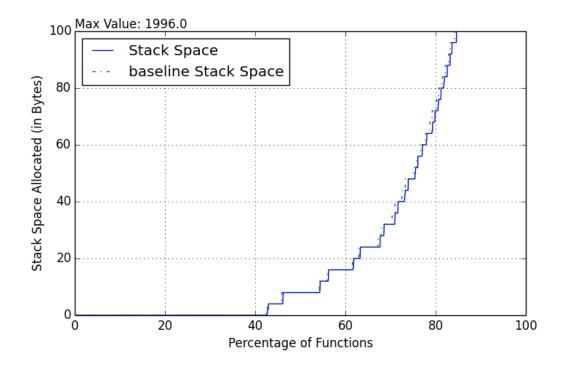

# 4.3.2 Stack Space Off Optimization

At the other end of the spectrum, for general stack space off configurations, many of the optimizations that were toggled off varied in how they affected the stack space. For example, *argpromotion* increased stack space slightly, while *early-cse-memssa* decreased stack space slightly. The biggest reduction in stack size that affected most functions is found in turning off *licm*. By turning off *licm*, the maximum stack space was reduced by 1356 bytes (from 3352 to 1996 bytes). For about 35% of functions, the stack space was reduced by about 4-8 bytes. Aside from these, most of the other optimizations did not seem to have any impact on stack space.

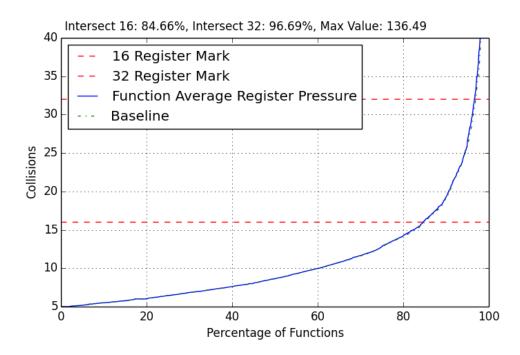

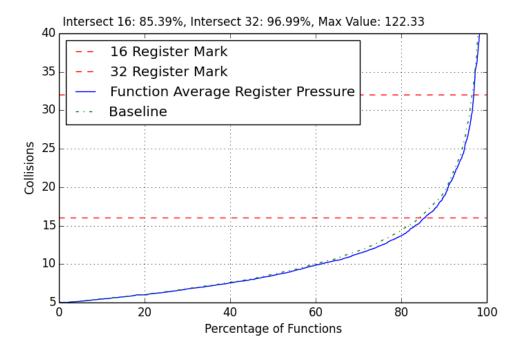

# 4.4 Double Optimizations

After looking at the single optimization configuration, we take a closer look at the effects of turning two optimizations on or off concurrently. Again, the combinations of optimizations is numerous, so we choose the more interesting optimizations based on the results from the single optimization analysis and choose the second optimization based on what we think will help reduce collisions. *All-loops* is one of the more interesting optimizations and we thought that *argpromotion* would be beneficial to replace any memory references that may be happening within a loop and reduce the amount of extra *allocas* in the code. This would reduce the amount of extra registers needed within a loop and may reduce spills from happening. *Memoryssa* would also be another beneficial option to reduce any multiple memory access operations happening within a loop, so we also pair that with *all-loops*.

Licm is another interesting optimization because it causes many spills and reduces many spills when turned off. We pair it with *all-loops* to see if having loop optimizations would help the purpose of *licm*, which is to take as much code out of the loop block. Having code out of the loop block and then applying the loop optimizations, can help reduce the amount of registers being used in a loop. For example, *loopunroll* would duplicate less code found within the loop and can potentially reduce stack space used. Additionally, we also wanted to pair *licm* with *argpromotion* to see if it would reduce the number of register collisions, help simplify the interference graph, and reduce the stack space allocated similarly to *all-loops*.

We present only *all-loops/argpromotion*, *licm/all-loops*, and *licm/argpromotion* double optimizations in this analysis because *memoryssa/all-loops* did not change anything in the register collisions or stack space when compared to only *all-loops*. The single optimization data suggests that *all-loops* is creating opportunities for other optimizations to make the overall code better, so we examine *licm/argpromotion* to test a pair of optimizations that does not include *all-loops*.

Figures 4.21, 4.22, and 4.23 show the data collected in general for having two optimizations on. Note that some of the graphs in these sections are found in Appendix C.

| x86 Single Optimizations | Avg-Off-16 | Avg-Off-32 | Avg-Off-Max | Avg-On-16 | Avg-On-32 | Avg-On-Max |

|--------------------------|------------|------------|-------------|-----------|-----------|------------|

| all-loops                | 85.22      | 96.78      | 123.1       | 84.94     | 96.96     | 128.02     |

| argpromotion             | 84.14      | 96.56      | 137.62      | 85.71     | 97.2      | 123.65     |

| licm                     | 84.36      | 96.89      | 129.82      | 85.57     | 97        | 124.8      |

| memoryssa                | 84.19      | 96.56      | 137.62      | 85.7      | 97.2      | 123.65     |

| x86 Double Optimizations | Avg-Off-16 | Avg-Off-32 | Avg-Off-Max | Avg-On-16 | Avg-On-32 | Avg-On-Max |

| all-loops-argpromotion   | 85.21      | 96.78      | 123.1       | 84.98     | 96.96     | 128.02     |

| all-loops-memoryssa      | 85.22      | 96.78      | 123.1       | 84.94     | 96.96     | 128.02     |

| licm-all-loops           | 85.39      | 96.99      | 122.33      | 84.66     | 96.69     | 136.49     |

| licm-argpromotion        | 84.31      | 96.89      | 129.82      | 85.22     | 96.78     | 123.1      |

Figure 4.21: x86 Double Optimization Average Collisions by Function, Collision Statistics (Percentage at or Below Threshold)

| Max-Off-16 | Max-Off-32                                                                | Max-Off-Max                                                                                                                                                                                        | Max-On-16                                                                                                                                                                                                                                                                                                                   | Max-On-32                                                                                                                                                                                                                                                                                                                               | Max-On-Max                                                                                                                                                                                     |

|------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 51.17      | 75.32                                                                     | 1574                                                                                                                                                                                               | 49.3                                                                                                                                                                                                                                                                                                                        | 72.6                                                                                                                                                                                                                                                                                                                                    | 1463                                                                                                                                                                                           |

| 49.48      | 72.88                                                                     | 1577                                                                                                                                                                                               | 51.08                                                                                                                                                                                                                                                                                                                       | 75.15                                                                                                                                                                                                                                                                                                                                   | 1460                                                                                                                                                                                           |