Publicly Accessible Penn Dissertations

2018

## Strong Memory Consistency For Parallel Programming

Christian Delozier University of Pennsylvania, crdelozier@gmail.com

Follow this and additional works at: https://repository.upenn.edu/edissertations

**One of the Computer Engineering Commons, and the Computer Sciences Commons**

## Recommended Citation

Delozier, Christian, "Strong Memory Consistency For Parallel Programming" (2018). Publicly Accessible Penn Dissertations. 2933. https://repository.upenn.edu/edissertations/2933

This paper is posted at Scholarly Commons. https://repository.upenn.edu/edissertations/2933 For more information, please contact repository@pobox.upenn.edu.

## Strong Memory Consistency For Parallel Programming

#### **Abstract**

Correctly synchronizing multithreaded programs is challenging, and errors can lead to program failures (e.g., atomicity violations). Existing memory consistency models rule out some possible failures, but are limited by depending on subtle programmer-defined locking code and by providing unintuitive semantics for incorrectly synchronized code. Stronger memory consistency models assist programmers by providing them with easier-to-understand semantics with regard to memory access interleavings in parallel code. This dissertation proposes a new strong memory consistency model based on ordering-free regions (OFRs), which are spans of dynamic instructions between consecutive ordering constructs (e.g. barriers). Atomicity over ordering-free

regions provides stronger atomicity than existing strong memory consistency models with competitive performance. Ordering-free regions also simplify programmer reasoning by limiting the potential for atomicity violations to fewer points in the program's execution. This dissertation explores both software-only and hardware-supported systems that provide OFR serializability.

## Degree Type

Dissertation

#### **Degree Name**

Doctor of Philosophy (PhD)

## **Graduate Group**

Computer and Information Science

#### First Advisor

Joseph Devietti

## **Second Advisor**

Steve Zdancewic

#### Keywords

Atomicity, Memory Consistency, Parallel Programming

#### **Subject Categories**

Computer Engineering | Computer Sciences

## STRONG MEMORY CONSISTENCY FOR PARALLEL PROGRAMMING

Christian DeLozier

## A DISSERTATION

in

Computer and Information Science

Presented to the Faculties of the University of Pennsylvania

in

Partial Fulfillment of the Requirements for the

Degree of Doctor of Philosophy

2018

| Supervisor of Dissertation                                     |

|----------------------------------------------------------------|

| Joseph Devietti                                                |

| Assistant Professor of Computer and Information Science        |

| Graduate Group Chairperson                                     |

| Lyle Ungar                                                     |

| Professor of Computer and Information Science                  |

|                                                                |

| Dissertation Committee                                         |

| Steve Zdancewic, Professor of Computer and Information Science |

Jonathan Smith, Olga and Alberico Pompa Professor of Engineering and Applied Science

Brandon Lucia, Assistant Professor of Computer Engineering, Carnegie Mellon University

Boon Thau Loo, Professor of Computer and Information Science

# STRONG MEMORY CONSISTENCY FOR PARALLEL PROGRAMMING COPYRIGHT

2018

Christian Robert DeLozier

This work is licensed under a Creative Commons Attribution 4.0 License.

To view a copy of this license, visit:

https://creativecommons.org/licenses/by/4.0/

To my wife Allyson and my working buddies Lily, Guen, and Tony

#### **ACKNOWLEDGMENTS**

I would like to thank my advisor, Joe Devietti, for his enthusiasm and support over the past five years. Joe has been an excellent mentor, and I would not have been able to finish this thesis without his help. Joe has constantly provided me with interesting problems to work on and helpful insights on how to solve those problems. His enthusiasm for research in Computer Science is unparalleled and has inspired me to continue performing research in my career. He has also been understanding and supportive of my desire to teach and has allowed me to siphon a significant amount of time from research in pursuit of teaching opportunities. I am proud to have been Joe's first PhD student.

I would also like to thank Milo Martin for advising me through the first three years of my PhD. Milo mentored me through my first research project, and his advice has stuck with me throughout the years and will continue to influence how I conduct research in the future.

I thank my dissertation committee chaired by Steve Zdancewic, and with Boon Thau Loo, Jonathan Smith, and Brandon Lucia as members, for their comments and guidance on this dissertation. I would especially like to thank Brandon Lucia for collaborating on this work for many years and suffering through the countless rejections and rewrites. I would also like to thank Steve Zdancewic for his help on my WPE II committee, for collaborating on my first research project, and for his advice on teaching.

I owe a huge amount of thanks and gratitude to my parents for helping me to achieve this goal. Without their love, support, and encouragement, I would not have been able to pursue a PhD. They provided me with every opportunity to further my education and succeed. They have both been patient in listening to me when I struggled and offering thoughtful advice on how to proceed throughout the years. Thank you as well to my sister Laura for her love and for helping me with my teaching materials and techniques over the past few years. I also need to thank all the Heslops for being a second family to me.

I was lucky to collaborate with a fantastic group of people during my time at Penn. Thank you to Peter-Michael Osera, Richard Eisenberg, Santosh Nagarakatte, Yuanfeng Peng, Ariel Eizenberg, Kavya Lakshminarayanan, Shiliang Hu, and Gilles Pokam for their ideas, insights, advice, and work over the many years I have been at Penn. The work in this thesis and outside of it would not have been possible without such great collaborators.

In my time at Penn, I have also made a number of friends who have made campus a friendly and fun environment. I would like to thank Abhishek Udupa, Arun Raghavan, Santosh Nagarakatte, Laurel Emurian, Salar Moareff, Mukund Raghothaman, Ben Karel, Nikos Vasilakis, Yuanfeng Peng, Nimit Sighania, Peter-Michael Osera, Jennifer Paykin, Katie Gibson, Omar Navarro Leija, Kelly Shiptoski, Akshitha Sriraman, and Liang Luo for their friendship and advice. I apologize if I missed anyone, and I hope to keep in touch in years to come.

Outside of Penn, I would also like to thank my extended family for their love and support.

I would like to thank my friends from Pitt and elsewhere for helping me to have fun and escape from school. Thanks especially to Josh Picozzi, Dave Hynek, Emily DeLeo, and Holey Boley.

I would not have been interested in graduate school if not for the early research experiences I had at the University of Pittsburgh. I would like to thank Brian Primack and Bruce Childers for getting me started in research and encouraging me to continue. I would also like to thank John Ramirez and John Aronis for helping me prepare for and apply to graduate school.

Last but certainly not least, I would like to thank my wife Allyson for her love, support, encouragement, and patience over the past eight years. Allyson has tirelessly listened to my outloud thinking about research, paper reviews, rebuttals, rejections, and occasionally acceptances over the time I have worked on my PhD. Without her emotional support, I would not have earned this degree. She has also preserved my sanity by forcing me to occasionally step away from my research to explore the world, both near and far. Allyson, I love you, and you probably deserve to have your name on this work as much as I do.

The work in this dissertation was supported by NSF grant #XPS-1337174.

## **ABSTRACT**

## STRONG MEMORY CONSISTENCY FOR PARALLEL PROGRAMMING

## Christian DeLozier

## Joseph Devietti

Correctly synchronizing multithreaded programs is challenging, and errors can lead to program failures (e.g., atomicity violations). Existing memory consistency models rule out some possible failures, but are limited by depending on subtle programmer-defined locking code and by providing unintuitive semantics for incorrectly synchronized code. Stronger memory consistency models assist programmers by providing them with easier-to-understand semantics with regard to memory access interleavings in parallel code. This dissertation proposes a new strong memory consistency model based on ordering-free regions (OFRs), which are spans of dynamic instructions between consecutive ordering constructs (e.g. barriers). Atomicity over ordering-free regions provides stronger atomicity than existing strong memory consistency models with competitive performance. Ordering-free regions also simplify programmer reasoning by limiting the potential for atomicity violations to fewer points in the program's execution. This dissertation explores both software-only and hardware-supported systems that provide OFR serializability.

## TABLE OF CONTENTS

| ABST   | RACTVI                               |

|--------|--------------------------------------|

| LIST C | OF TABLESX                           |

| LIST C | OF ILLUSTRATIONSXI                   |

| LIST C | OF ALGORITHMSXIII                    |

| 1 IN   | TRODUCTION 1                         |

| 2 BA   | CKGROUND6                            |

| 2.1    | MEMORY CONSISTENCY6                  |

| 2.2    | DATA-RACES AND ATOMICITY VIOLATIONS7 |

| 2.3    | STRONG MEMORY CONSISTENCY MODELS8    |

| 2.4    | SERIALIZABILITY11                    |

| 3 OR   | RDERING-FREE REGIONS13               |

| 3.1    | ORDERING-FREE REGIONS API            |

| 3.2    | PROOF OF CORRECTNESS                 |

| 3.3    | QUANTIFYING ATOMICITY21              |

| 4 IM   | PLEMENTING ORDERING-FREE REGIONS25   |

|   | 4.1 | Overview                                       |

|---|-----|------------------------------------------------|

|   | 4.2 | Locks                                          |

|   | 4.3 | Shadowspace                                    |

|   | 4.4 | Deadlock Detection                             |

|   | 4.5 | Allocator Support45                            |

|   | 4.6 | Compiler Support                               |

|   | 4.7 | Working with Libraries50                       |

|   | 4.8 | Summary51                                      |

|   |     |                                                |

| 5 | HA  | RDWARE SUPPORT FOR ORDERING-FREE REGIONS52     |

|   | 5.1 | Address Translation                            |

|   | 5.2 | Caching53                                      |

|   | 5.3 | ISA Support55                                  |

|   | 5.4 | Extending ORCA Hardware to SOFRITAS56          |

|   |     |                                                |

| 6 | API | PLYING ORDERING-FREE REGIONS TO APPLICATIONS58 |

|   | 6.1 | Annotations59                                  |

|   | 6.2 | Bug Detection67                                |

|   | 6.3 | Case Studies71                                 |

|   | 6.4 | User Study74                                   |

|   |     |                                                |

| 7 | PEI | RFORMANCE OF ORDERING-FREE REGIONS79           |

|   | 7.1 | MAMA79                                         |

|   | 7.2 | SOFRITAS83                                     |

|   | 7.3 | Hardware Support90                             |

|   | 7 / | Discussion 95                                  |

| 8 | RE   | LATED WORK                    | 97  |

|---|------|-------------------------------|-----|

| 9 | CO   | NCLUSIONS AND FUTURE WORK     | 99  |

| , | 9.1  | Hardware Support for SOFRITAS | 100 |

| , | 9.2  | Further User Study            | 101 |

| ы | BLIC | OGRAPHY                       | 102 |

## LIST OF TABLES

| 4.1 | Characterization of memory accesses and lock acquires       | 26 |

|-----|-------------------------------------------------------------|----|

| 4.2 | Characterization of lock acquires as reads or writes        | 27 |

| 6.1 | Lines of code and static synchronization in Java benchmarks | 59 |

| 6.2 | Dynamic synchronization in Java benchmarks                  | 60 |

| 6.3 | Dynamic deadlock counts for Java applications               | 61 |

| 6.4 | Static annotations needed for Java benchmarks               | 62 |

| 6.5 | Ordering and atomicity annotations for ORCA/SOFRITAS        | 63 |

| 6.6 | Qualitative ease of adding OFR annotations                  | 65 |

| 6.7 | Summary statistics for survey questions                     | 77 |

## LIST OF ILLUSTRATIONS

| 1.1  | An atomicity violation that may occur in money transfers     | 1  |

|------|--------------------------------------------------------------|----|

| 1.2  | Comparison between OFR serializability and prior models      | 4  |

| 2.1  | An atomicity violation found in Firefox                      | 8  |

| 2.2  | Code that demonstrates required atomicity                    | 9  |

| 2.3  | Fail-on-conflict semantics and conflict serializability      | 12 |

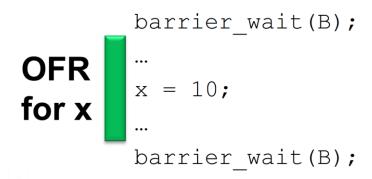

| 3.1  | The ordering-free region for a variable                      | 13 |

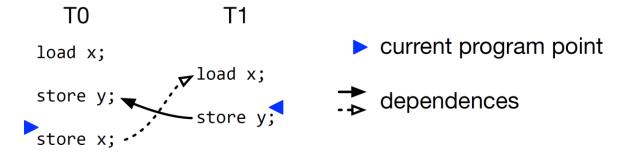

| 3.2  | Scenario in which an OFR exception will be raised            | 15 |

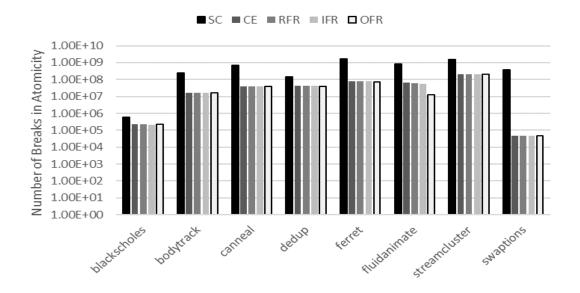

| 3.3  | Number of breaks in atomicity for each model                 | 21 |

| 3.4  | CDF plot showing length and width of regions in blackscholes | 22 |

| 3.5  | CDF plot showing length and width of regions in ferret       | 23 |

| 3.6  | CDF plot showing length and width of regions in fluidanimate | 24 |

| 4.1  | Pipeline staged locking                                      | 30 |

| 4.2  | Barrier staged locking                                       | 31 |

| 4.3  | Coarse mapping leads to false OFR exceptions                 | 33 |

| 4.4  | Lock shadowspace granularity                                 | 35 |

| 4.5  | Rigid mapping from data to locks                             | 36 |

| 4.6  | Lock trie                                                    | 36 |

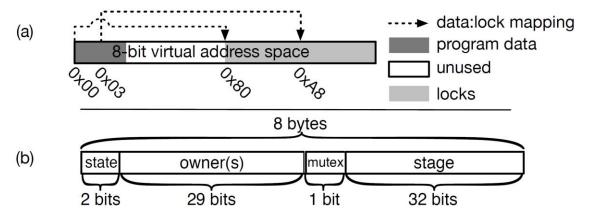

| 4.7  | Design of ORCA's reader-writer locks                         | 38 |

| 4.8  | SOFRITAS distributed lock implementation                     | 40 |

| 4.9  | SOFRITAS lock state transitions                              | 42 |

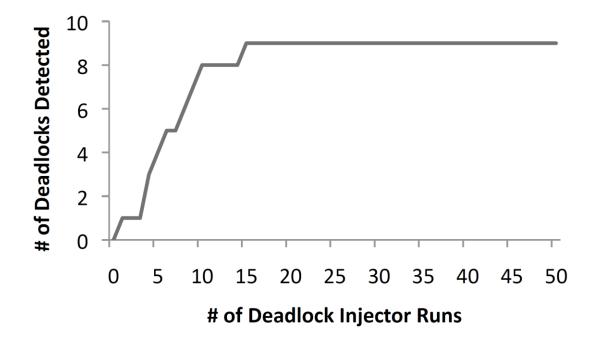

| 4.10 | Number of OFR exceptions generated after N runs              | 44 |

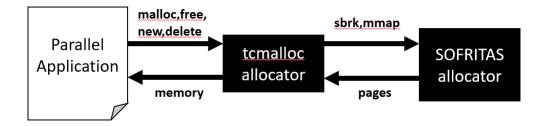

| 4.11 | Allocation via temalloc                                      | 45 |

| 4.12 | Subsequent access optimization for read-write upgrades       | 48 |

| 5.1  | Translation from data to lock with hardware support          | 53 |

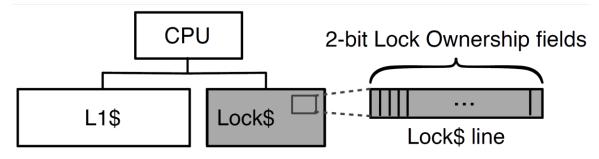

| 5.2  | Lock cache design                                            | 54 |

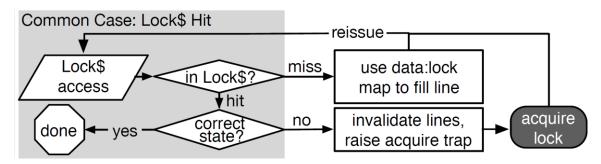

| 5.3  | Flow-chart of lock cache operations                          | 54 |

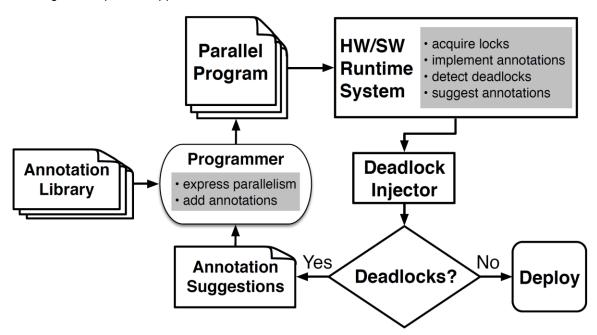

| 6.1  | Workflow for applying OFRs to an application                 | 58 |

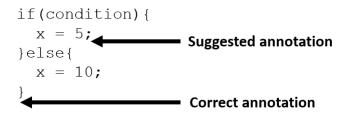

| 6.2  | A "close" annotation suggestion                              | 66 |

| 6.3  | Call chain for construction bug in bodytrack                 | 68 |

| 6.4  | Data-race found in fluidanimate                              | 69 |

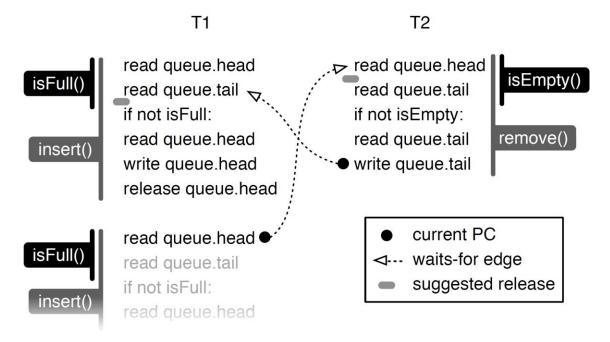

| 6.5  | Buggy interleaving in memcached-127                          | 70 |

| 6.6  | Example from dedup queue                                     | 72 |

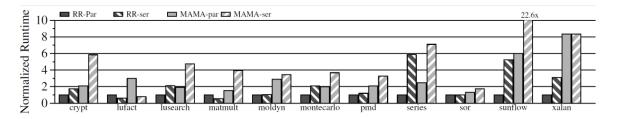

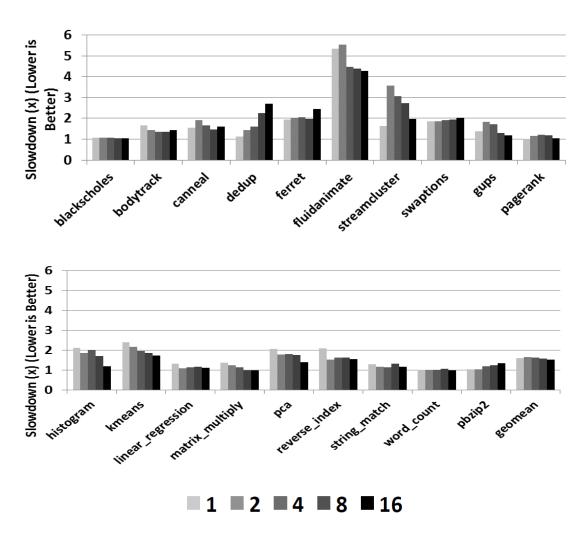

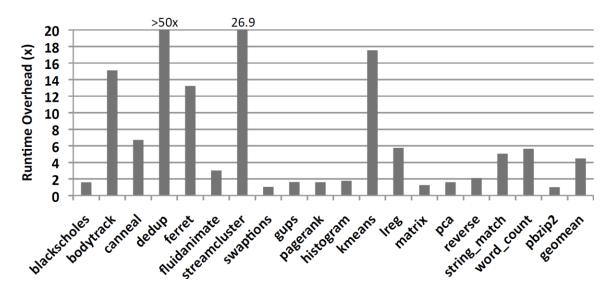

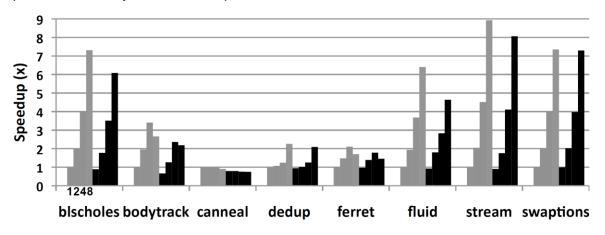

| 7.1  | Runtime performance of MAMA                                  | 80 |

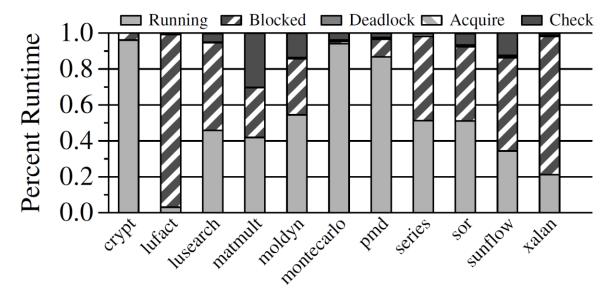

| 7.2  | Performance breakdown for MAMA                               | 81 |

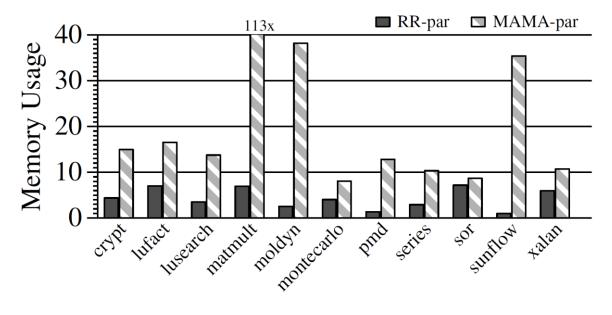

| 7.3  | Memory usage for MAMA                                        | 82 |

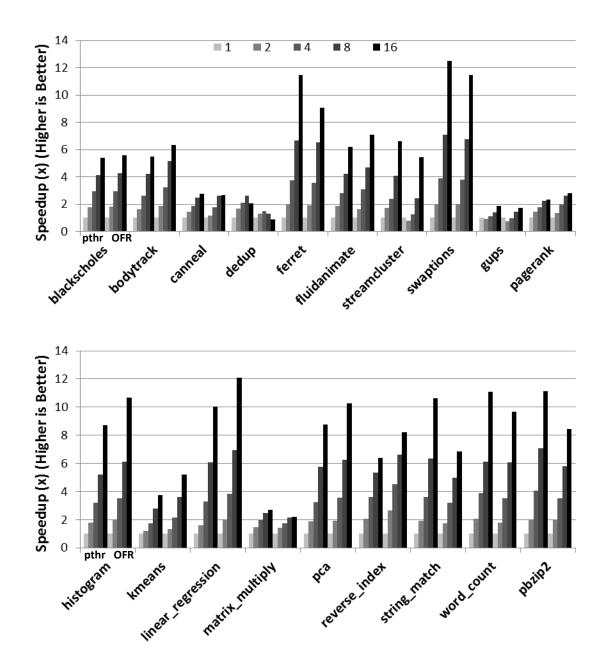

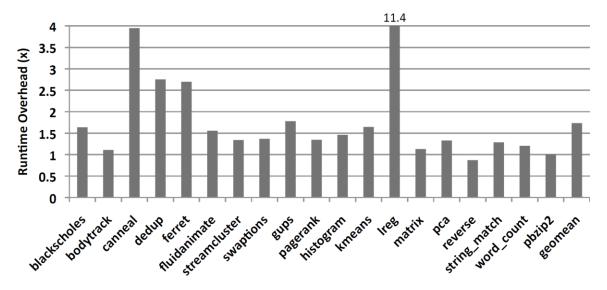

| 7.4  | Runtime performance of SOFRITAS                              | 84 |

| 7.5  | Scalability of SOFRITAS                                      | 85 |

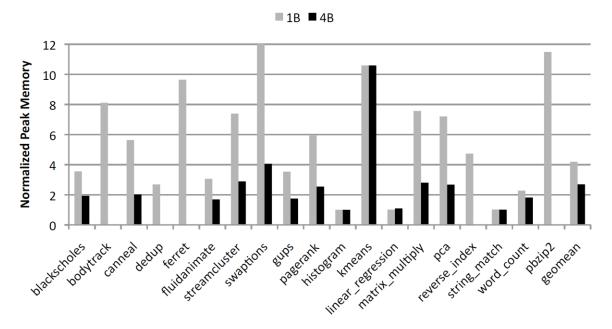

| 7.6  | Memory overheads for SOFRITAS with 1B and 4B mappings        | 86 |

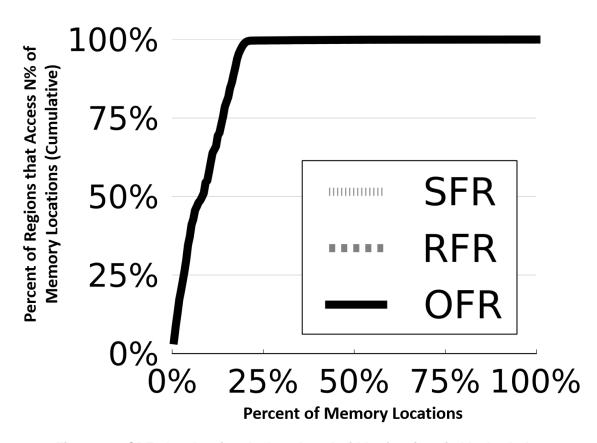

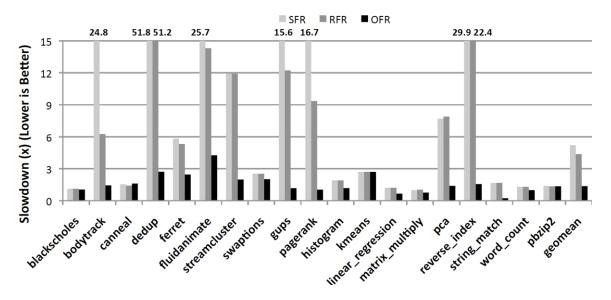

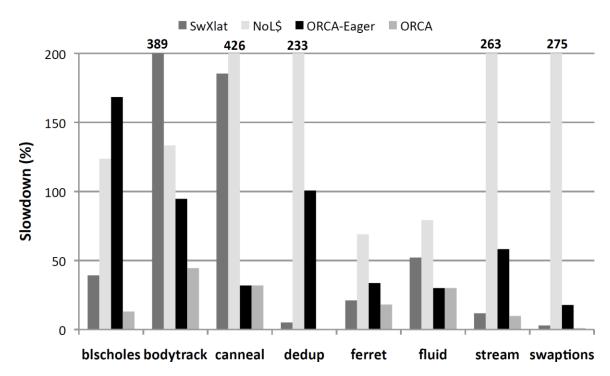

| 7.7  | Comparison to SFR and RFR models                             | 87 |

| 7.8  | Overheads of using memset                                    | 89 |

| 7.9  | Overheads of not inlining lock checks | 90 |

|------|---------------------------------------|----|

| 7.10 | Runtime performance of ORCA           | 92 |

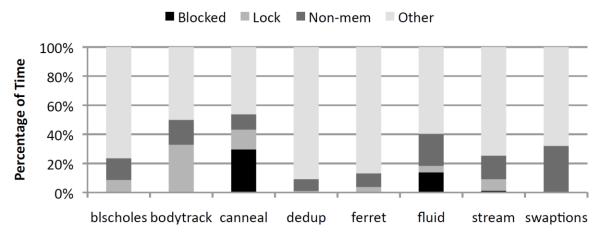

| 7.11 | Performance breakdown for ORCA        | 93 |

| 7.12 | Scalability of ORCA                   | 94 |

## LIST OF ALGORITHMS

| 4.3.1 | Distributed deadlock detection    | 43 |

|-------|-----------------------------------|----|

| 4.5.1 | Inline ASM lock check             | 47 |

| 4.5.3 | Read-only arrays in streamcluster | 49 |

| 6.4.1 | User Study Sample Code            | 75 |

| 6.4.2 | User Study Solution               | 76 |

| 6.4.3 | Survey Questions                  | 77 |

## 1 INTRODUCTION

Despite decades of research progress, writing correct and efficient multi-threaded programs remains an open challenge. Multi-threaded applications are becoming increasingly common on all execution platforms, including the cloud, mobile devices, and even embedded systems [30]. Given the pervasiveness of multi-threaded code and increasing complexity of systems, programmers must be able to manage the complexity of developing parallel applications.

Writing a parallel program can be divided into two subtasks: identifying the parallelism in a problem and properly expressing that parallelism in an implementation. Programmers are creative and generally good at identifying parallelism in problems, but they frequently make mistakes while trying to express that parallelism. This dissertation focuses on helping the programmer properly express parallelism. Properly expressing parallelism requires both writing code that implements a parallel task and coordinating the execution of that code so that the parallel execution produces a correct result. Without proper coordination, parallel applications can suffer from bugs such as data-races and atomicity violations that can lead to program crashes or silent data corruption.

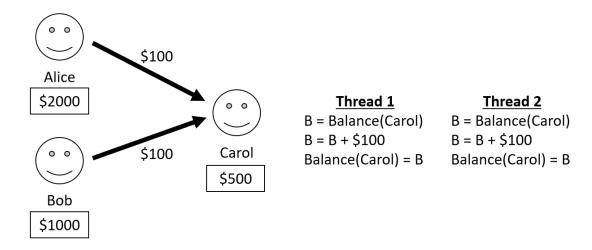

Figure 1.1: An atomicity violation that may occur when processing money transfers

As an example, consider the problem of processing transfers of money from one bank account to another. Processing one transfer at a time is safe but does not take advantage of multi-core hardware. To improve performance, transfers can be processed concurrently in multiple threads, but a multi-threaded implementation must ensure that transfers to or from the same accounts are not processed concurrently. Figure 1.1 demonstrates how transferring money in parallel may lead to an error. If Alice and Bob each transfer \$100 to Carol and those transfers are processed concurrently, Carol could end up with less money than she expects. To process each transfer, the machine would read Carol's account balance, add \$100 to that balance, and then save the new balance. If the balance reads happen at the same time, Carol may end up with \$600 instead of \$700. Parallel programming models must help the programmer reason about concurrent executions in order to avoid bugs.

A system's memory consistency model is a key factor in helping the programmer understand how a parallel execution executes on a multi-core system. The memory models for languages like Java [52], and C++ [11], and for various hardware architectures [51, 66, 68] permit aggressive optimization, but tend to be complex and inaccessible to most programmers due to the fact that they allow instructions to be interleaved in ways that a programmer may not expect. Systems with a Sequentially Consistent model [10, 16, 53, 76] give parallel executions sequential interleaving semantics, but do so at instruction granularity, which remains complex. Yet stronger models have semantics that execute coarse-grained, parallel code regions atomically and as a sequential interleaving [8, 28, 48, 67]. Reasoning about a system with region interleaving semantics is much simpler than reasoning about instruction interleaving [61].

Region-based systems for enforcing strong memory consistency must decide how to define the coarse-grained code regions that are interleaved during an execution. Some systems define regions arbitrarily [53] or implicitly [67] according to program sub-structures. The size of such regions is limited by architectural parameters and features of the program unrelated to parallelism. Other systems [8, 48] define regions in terms of programmer-provided

synchronization operations, such as synchronization-free regions [48, 61] (SFRs), release-free regions [8] (RFRs), and interference-free regions [28]. The size of regions determines how safe the execution will be and how easy it is for a programmer to reason about the parallel execution.

This work proposes a new region-based memory consistency model. The key insight is to provide coarse regions by default that are not as dependent on the correctness of the program's synchronization as prior models. Thus, the need to trust programmer-defined locking code, which can often be incorrect even in well-tested applications, is largely eliminated from the process of writing a parallel application. The programmer defines a thread's work and defines the points when threads' operations must explicitly form an order – at thread creation and completion, condition wait, and barrier wait. The sequence of dynamically executed instructions between ordering primitives is referred to as an ordering-free region (OFR). A program is OFR serializable if a program's behavior is equivalent to a serialization of atomically-executed ordering-free regions. Although OFR serializability is defined as the serialization of regions, the implementation does not necessarily need to serialize all ordering-free regions and can instead execute them partially or completely in parallel, as long as the illusion of serialization is preserved.

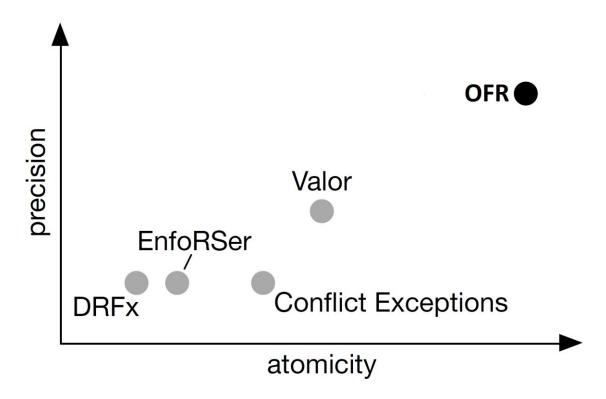

Figure 1.2: Comparison between OFR serializability and prior models

Figure 1.2 provides a visual comparison of the atomicity provided by various region-based memory consistency models. EnfoRSer [67], DRFx [53], and Conflict Exceptions [48] are all synchronization-free region (SFR) models, which enforce regions based on the acquisition and release of locks. Valor [8] is based on release-free regions (RFRs), which enforce regions only at lock release boundaries. OFRs provide more atomicity and precision than both SFR and RFR models. Later sections provide both quantitative and qualitative evaluations to support this claim.

Ordering-free regions provide a number of benefits to the programmability of parallel applications. The main benefit is that OFRs provide more atomicity than existing strong memory consistency models by enforcing atomicity across larger regions of code and more memory locations. Within an OFR, every memory location accessed by a thread is accessed atomically (without conflicting interference from another thread). Runtime systems based on ordering-free regions can help inform the necessary locking synchronization in a parallel application, and an initial user study indicated that novice programmers are better at applying correct synchronization

with the assistance of reports from an ordering-free region system than with the assistance of reports from data-race detection systems.

The subsequent chapters of this dissertation are organized as follows. Chapter 2 discusses background and related work that informed the design and implementation of ordering-free regions. Chapter 3 introduces ordering-free regions and formalizes the guarantees provided by ordering-free regions. Chapter 4 describes and compares multiple implementations or ordering-free regions, including the benefits and drawbacks of each implementation. Chapter 5 introduces hardware support for ordering-free regions. Chapter 6 provides examples and experiences in applying ordering-free regions to existing parallel applications through multiple case studies and experiments. Chapter 7 compares the performance of various implementations of software-only and hardware-supported implementations of ordering-free regions. Chapter 8 describes possible avenues for future work, and chapter 9 concludes the dissertation.

This dissertation draws on multiple published works. The Java implementation of OFR serializability, MAMA (Mostly Automatic Management of Atomicity), described in section 4 and evaluated in sections 6 and 7, was originally presented at WoDet 2014 [20]. Hardware support for OFR serializability included in sections 4 and 5 was originally proposed in the ORCA (Ordering-Free Regions for Consistency and Atomicity) technical report [23]. The technical report on ORCA also included an evaluation of the usability and performance of ordering-free region serializability with hardware support, as discussed in sections 6 and 7. SOFRITAS (Serializable Ordering-Free Regions for Increasing Thread Atomicity Scalably) was presented at ASPLOS 2018 [22]. Section 3 defines ordering-free regions and related terms as described by SOFRITAS, and section 4 provides details on the implementation of SOFRITAS. Sections 6 and 7 include the evaluation of SOFRITAS. The memory allocator described in section 4 was first introduced by TMI [21], which was presented at MICRO 2017. The remaining content is original work.

## 2 BACKGROUND

Strong memory consistency based on ordering-free regions is motivated by several areas of prior work on multithreaded programmability. This section provides a brief overview of each of these related areas of work and discusses recent works on each topic.

## 2.1 MEMORY CONSISTENCY

The **memory consistency model** of a system specifies how memory accesses in a parallel system will behave, as observed by the programmer [2]. Strong memory consistency models require memory accesses to behave as if they had been executed serially. Weak memory consistency models permit memory accesses to be reordered with respect to the serial order. Memory accesses can be reordered by compiler and hardware optimizations that can improve the performance of both serial and parallel executions. However, reordering memory accesses can be confusing to the programmer because an application may produce results that do not seem like they should be possible.

One of the strongest memory consistency models is **sequential consistency**. Sequential consistency requires that "the result of an execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program" [42]. In general, sequential consistency prevents loads and stores from being reordered with other loads and stores. Weaker consistency models permit more reorderings of loads and stores because reordering loads and stores can improve the overall performance of the system. x86 architectures implement total-store order, which allows loads to be reordered, but not stores. More relaxed consistency models, such as those implemented by ARM processors, permit reordering both loads and stores.

Many approaches to providing strong atomicity focus on enforcing sequential consistency. Several schemes have been proposed for detecting sequential-consistency violations with custom hardware support [27, 55, 62]. These systems detect violations of sequential consistency and halt the program. Enforcing sequential consistency forms a baseline for other strong memory consistency models. Other systems provide sequential consistency for a parallel execution [10, 16, 53, 76]. These systems require hardware modifications to existing systems because current processors do not support sequential consistency.

## 2.2 DATA-RACES AND ATOMICITY VIOLATIONS

Although sequential consistency is a useful property, it only prevents incorrect results due to memory reorderings. Parallel programs must still use synchronization to avoid data-races and atomicity violations. A *data-race* occurs when two memory operations on different threads access the same location, one of the accesses is a write, and there is no happens-before ordering between the two memory operations. A *happens-before ordering* is a chronological ordering between two threads due to some operation, such as a lock acquire or a barrier.

An *atomicity violation* occurs when a set of memory accesses on one thread does not have a happens-before ordering with a set of memory accesses performed by another thread or threads and at least one of the memory accesses in both sets is a write to the same location.

Data-races can be considered atomicity violations, but not all atomicity violations are data-races.

Figure 2.1 demonstrates an atomicity violation where each memory location (*str* and *length*) is properly protected by a lock, but the set of memory accesses performed by both threads exhibit an atomicity violation due to the lack of a happens-before ordering between the sets of accesses. The reads of *str* and *length* by Thread 1 need to occur within the same critical section to be ordered with the writes performed by Thread 2. No data-race will be detected in the code because each access has a happens-before ordering with all other accesses due the acquisition of lock L.

```

// shared vars protected by lock L

int length;

char *str;

Thread 2

Thread 1

lock(L);

tmpstr = str;

lock(L);

unlock (L);

str = newstr;

unlock (L);

lock(L);

length = 15;

lock(L);

unlock(L);

tmplen = length;

unlock(L);

```

Figure 2.1: An atomicity violation found in Firefox

Many prior works have developed systems for detecting data-races and atomicity violations [17, 18, 31, 33, 44–46, 49, 62, 77]. Data-race detectors generally use vector clock algorithms to determine when a happens-before ordering does not exist between pairs of memory accesses. Atomicity violation detectors use heuristics to decide where atomic regions should start and end, allowing atomicity violations to be detected when the application's synchronization provides less atomicity than might be necessary.

## 2.3 STRONG MEMORY CONSISTENCY MODELS

There have been several proposals of strong memory consistency models that help catch bugs and simplify program reasoning. Although sequential consistency can help the programmer to understand a parallel execution, it still forces the programmer to reason about how individual instructions can be interleaved. Region-based memory models group instructions into regions of

code and allow the programmer to reason about the interleaving of regions rather than the interleaving of individual instructions. As Figure 1.2 shows, strong memory consistency models can be characterized along two dimensions: the granularity of the code regions at which serializability is guaranteed, and the precision with which serializability violations are detected. Ordering-free regions improve upon prior work along both dimensions.

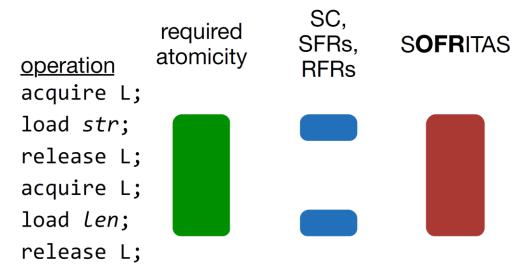

Figure 2.2: Code that demonstrates that programmer-defined acquires and releases may not match the required atomicity of an application

Synchronization-free regions [48, 61] (SFRs) span a region of instructions from one dynamic synchronization operation to the next. For example, a critical-section (between a lock and unlock operation) forms a synchronization-free region. Synchronization operations considered by synchronization-free regions include lock operations, barrier waits, condition variable waits, thread joins, thread creates, and other such operations. Release-free regions [8] (RFRs) strengthen the atomicity provided by synchronization-free regions by ending regions on release operations only. Only a subset of synchronization operations are considered to be release operations, including lock releases, barrier waits, condition variable waits, and thread creates. More generally, a release operation forms a happens-before order with other synchronization operations that occur later than itself in a trace of a program's execution [28]. All

operations that are not considered release operations are acquire operations. Interference-free regions [28] (IFRs) provide stronger atomicity than both synchronization-free regions and release-free regions. The interference-free region for a memory location extends from the acquire operation prior to the memory access to the first release operation that occurs after that access. The IFR for a memory location can be extended in both directions (of the execution trace) if it can be proven that the synchronization that formed a region should not affect the memory location. For example, in Figure 2.2, the IFRs for str and length match the critical regions that contain them. If the program used another variable x before, between, and after these two critical sections, the IFR for x would extend through the entire listed program because x should not be affected by the synchronization present in the program. Although IFRs offer stronger atomicity than both SFRs and RFRs, using IFRs in practice can be difficult because determining a memory location's IFR requires a trace of the application's execution, which is not available at runtime.

## 2.3.1 LENGTH AND WIDTH OF REGIONS

Region-based parallel programming models like synchronization-free regions, release-free regions, and ordering-free regions all provide atomicity over both instructions and memory locations. The *length* of the region is the number of dynamic instructions between the start and end of the region. In general, longer regions provide more atomicity but can lead to more conflicts between regions. Ordering-free regions (OFRs), which will be defined in Section 3, tend to be longer than SFRs and RFRs because ordering constructs tend to be used less frequently in existing parallel applications than lock acquires and releases. The *width* of a region is the number of memory locations that are atomic within the region, meaning that no other concurrent region can access those memory locations in a way that conflicts with the atomicity required by the region. For SFR, RFR, and OFR models, the width of the region is related to the length in that all memory location accessed by the dynamic instructions will be accessed atomically. Other

models, such as data-centric synchronization, may not protect all memory locations within each region and have regions that are less wide.

## 2.4 SERIALIZABILITY

A parallel execution is **serializable** If it is equivalent to some serial execution.

Serializability is a desirable safety property for parallel applications because it is easier for programmers to reason about serial code than to reason about parallel code. Strong memory consistency models enforce region serializability. An execution is **region serializable** if the parallel execution of its regions, as defined by the region-based memory consistency model, is the same as some serial execution of its regions.

The concepts of atomicity and serializability are not only found in parallel programming. Databases and distributed systems have similar notions of atomicity and serializability, and one common implementation of serializability in these systems is **conflict-serializability**. Conflict-serializability requires that the parallel schedule of transactions is equivalent to a serial schedule with the same transactions such that all conflicting operations in the serial and parallel schedules occur in the same chronological order.

Two-phase locking (2PL) enforces conflict-serializability [6]. In two-phase locking, locks can only be acquired in a growing phase and released in a shrinking phase. With this approach, locks cannot be acquired after any lock has been released. While there are more refined notions of serializability than 2PL, they are expensive to maintain and do not offer much additional flexibility [6]. Ordering-free regions employ an algorithm based on 2PL.

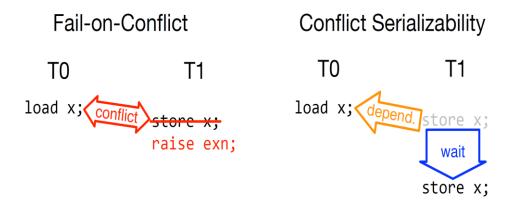

Conflicts that violate the serializability of a parallel execution can either be detected or avoided. Prior work on strong memory consistency models [8,47,60] detects violations of region serializability to report data races to the programmer. With this fail-on-conflict approach, the application exits and reports the violation of serializability to the programmer when one occurs. Conflict-serializability avoids conflicts rather than detecting them by serializing regions before a

conflict occurs. Serializing the execution to avoid a conflict can automatically prevent a bug, but too much serialization can decrease performance.

Figure 2.3: Demonstration of fail-on-conflict semantics and conflict serializability

Figure 2.3 demonstrates both a fail-on-conflict approach and conflict serializability. In the fail-on-conflict approach, an exception is raised when one region conflicts with another. The fail-on-conflict approach brings the programmer into the loop by indicating that a conflict exists. With conflict serializability, regions that would otherwise conflict can be serialized instead, preventing the conflict at runtime. Conflict serializability requires knowing how long the threads must be serialized to prevent the conflict from affecting the program's required semantics. Ordering-free regions rely on an algorithm based on 2PL to implement conflict serializability when possible. In the event that conflict serializability fails, ordering-free regions fall back to the fail-on-conflict approach and ask the programmer for help.

## 3 ORDERING-FREE REGIONS

This dissertation introduces a new strong memory model based on ordering-free regions (OFRs). Ordering-free regions function similarly to other strong memory consistency models such as SFRs, RFRs, and IFRs. Ordering-free regions rely on conflict serializability as much as possible and only fail-on-conflict when necessary. Unlike these prior models, ordering-free regions do not rely on programmer-defined lock acquires and releases to define region boundaries.

## **DEFINITION 3.0.1: Ordering-Free Region**

The **ordering-free region** for a memory access to a location extends from the previous ordering construct to the next ordering construct, chronologically, in the dynamic execution of the program.

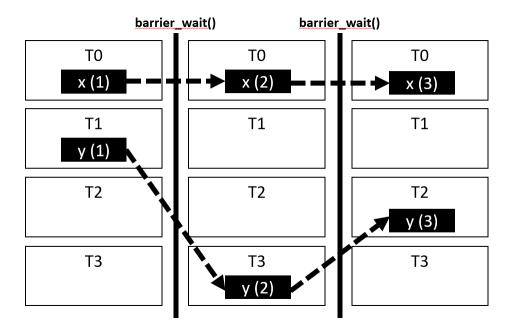

Figure 3.1: The ordering-free region for a variable

In the example above, the ordering-free region for x extends from the barrier wait before the write to x until the barrier wait after the write to x.

## **DEFINITION 3.0.2: Ordering Constructs**

**Ordering constructs** are defined as barrier waits, condition variable waits, thread exits, and thread joins. These constructs all indicate that the waiting thread needs one or more other threads to make progress before it continues its execution.

Ordering-free regions conservatively approximate the atomicity that a parallel program might require. Although it is theoretically possible that a program could require atomicity that spans an ordering construct, it is difficult in practice to find an application with this requirement.

An initial study of 780K lines of parallel code from the PARSEC benchmark suite [7], memcached, apache, and pbzip2 found that none of the applications studied required atomicity over an ordering construct on any of the tested inputs. More generally, requiring atomicity across an ordering construct may lead to a deadlock in the case that thread T<sub>1</sub> is waiting for thread T<sub>2</sub> to perform some action, but thread T<sub>1</sub> also holds a lock that thread T<sub>2</sub> requires. Thus, ordering constructs seem to be a reasonable delimiter for the atomicity required by most parallel programs.

## **DEFINITION 3.0.3: OFR Serializability**

An execution is OFR serializable if the dynamic, parallel execution of ordering-free regions is conflict serializable.

To enforce OFR serializability on a parallel execution, the accesses to all memory locations must occur atomically between ordering constructs. To this end, each memory location x is associated with a lock  $L_x$ . Before each memory access to x by a thread T, T acquires  $L_x$  if T does not already hold  $L_x$ . At the end of an OFR, when T encounters an ordering construct – a fork, join, wait, or barrier – T releases all the locks it holds. If T is ever unable to acquire a lock,  $L_x$ , then some other thread U must have accessed x in U's current OFR. T's inability to acquire  $L_x$  indicates a memory conflict between T and U. Prior consistency models raise an exception on T's access to x because of the memory conflict, but OFR serializability instead tracks a dependence from T to U and waits until U releases  $L_x$ , avoiding unnecessary exceptions on conflicts that do not compromise serializability.

This algorithm constructs the ordering-free region for each variable as shown in Figure 3.1. If the thread T is able to acquire the lock  $L_x$  within an OFR, no other thread has made a conflicting access within that OFR. Otherwise, the lock acquire of  $L_x$  by T would fail. After T acquires  $L_x$ , no other thread can acquire the lock until T releases it at the barrier\_wait(). Therefore, T has atomicity over x between the two calls to barrier\_wait(), which is what is required by ordering-free region serializability.

This simple algorithm does not account for read-sharing, which is common in parallel applications. In order to support read-sharing, the lock  $L_x$  that protects each memory location x is a reader-writer lock. A reader-writer lock permits multiple threads to acquire a read lock concurrently but only a single thread can hold an exclusive write lock. A reader-writer lock only permits an exclusive writer if there are no concurrent readers. With reader-writer locks, a dependence between threads only exists when the accesses by the threads to the location x conflict, meaning that one of the accesses must be a write. This use of reader-writer locks (instead of mutex locks) increases parallelism by allowing read-sharing of data, which is crucial for performance and scalability.

## **DEFINITION 3.0.4: OFR Exceptions**

An OFR exception occurs when a cyclic dependence exists between two threads within concurrent OFRs. An OFR exception indicates that the two OFRs are not OFR serializable.

Figure 3.2: A scenario in which an OFR exception will be raised

OFR serializability triggers an OFR exception when executing OFRs have at least two conflicts and the conflicts form a cycle in the conflict graph [6]. An OFR exception indicates that the program permitted an unserializable execution of its regions and that its OFRs must be divided into smaller atomic regions to permit additional region interleavings. An OFR exception suggests how to avoid the same exception in future executions. Figure 3.2 demonstrates two OFRs that are not OFR serializable and raise on OFR exception when executed concurrently. In this example, T0 acquires a read lock on L<sub>x</sub> when it loads the value of x. T1 then acquires a read

lock on  $L_x$  when it loads the value of x, causing  $L_x$  to be in a shared read state. To then acquires a write lock on  $L_y$  and stores a new value to y. T1 attempts to acquire a write lock on  $L_y$  but is unable to because T0 already holds a write lock on  $L_y$ . Finally, T0 attempts to acquire a write lock on  $L_x$  but is unable to because  $L_x$  is in a shared read state, which conflicts with T0's attempt to acquire a write lock.

An OFR exception indicates that the atomicity enforced by OFR serializability is too strong for the program. The atomicity must be relaxed to prevent the exception in future executions. Examining the code in Figure 3.2, the exception can be prevented by either (1) releasing the lock on y in T1, (2) releasing the lock on x in T0, (3) releasing both locks, or (4) ensuring that x and y are updated together by changing x to use mutex locking or altering the order of stores in T0. The choice of how to prevent the exception in future executions is made by the programmer using a small annotation API described in the next section. The programmer must examine the code that caused the exception and determine how much atomicity is required for each of the memory locations involved.

## 3.1 ORDERING-FREE REGIONS API

Programming with ordering-free regions requires a small API that allows programmers to refine a program's region specification and optimize performance.

A Release() annotation refines a program's region specification, sub-dividing a region into smaller regions, e.g., to eliminate an exception. The basic Release() annotation explicitly releases a specified location's lock and we include "syntactic sugar" API calls that batch release locks on objects and arrays. ReleaseObject() releases the locks on all fields of an object, and ReleaseArray() releases the locks on all elements of an array.

A RequireMutex() annotation associates a mutex lock with a memory location, rather than a reader-writer lock to avoid upgrade cycles. A post-dominator compiler analysis can often identify cases that might require a mutex and avoid the need for the programmer to manually add

RequireMutex() annotations. However, due to the need to be conservative, the programmer does occasionally need to add these annotations manually.

An EndOFR() annotation ends an ordering-free region before execution reaches an ordering operation. The EndOFR() annotation can be used when the atomicity requirements of thread allow the bulk release of all locks held by that thread. For example, pipeline parallel applications tend to perform operations on an object and then pass that object to the next stage of the pipeline for further processing. When this hand-off between pipeline stages occurs, ownership of the object transfers completely from the earlier pipeline stage to the later pipeline stage. Therefore, the earlier pipeline stage can release all of its locks on the object to allow those locks to be acquired by the later stages of the pipeline. These locks could be individually released using Release() annotations, but the EndOFR() annotation can instead be used to batch release all of the locks instead.

A ContinueOFR() annotation specifies that its containing region should not end at the next ordering operation executed. ContinueOFR() would be useful when a program requires atomicity coarser than an OFR (although we never encountered such a situation). ContinueOFR() can also be useful to improve performance by avoiding frequent lock releases at region boundaries. For example, in canneal, not releasing locks at a barrier does not affect correctness because Release() annotations release all locks that cause OFR exceptions.

## 3.2 PROOF OF CORRECTNESS

This section shows formally that OFR serializability enforces conflict serializability. The following definitions are used to support the arguments and can be assumed from this implementation of ordering-free regions.

## **DEFINITION 3.2.1: OFR Locking**

Ordering-free regions associate a single reader-writer lock L<sub>x</sub> with each memory location x.

## **DEFINITION 3.2.2: OFR Acquire**

No access to a memory location x by a thread T proceeds without first holding the location's lock in the correct mode for the access (i.e., read vs. write mode).

## **DEFINITION 3.2.3: OFR Release**

No lock L<sub>x</sub> is released by a thread until the end of the thread's current ordering-free region.

## **DEFINITION 3.2.4: OFR Deadlock Detection**

OFR serializability performs precise cyclic lock waiting (i.e. deadlock) detection.

## **THEOREM 3.2.5: Exception-Free Serializability**

If an execution of OFRs is free of OFR exceptions, then the execution is conflict serializable.

**Proof by contradiction**. Assume that an OFR exception-free execution was not conflict serializable. This proof assumes two ordering-free regions, but the argument generalizes to arbitrary-length conflict cycles.

If an execution is not conflict serializable, then the definition of conflict serializability for OFRs implies that there is a set of conflicts between OFRs that form a cycle in the conflict graph. Consider O<sub>i</sub> and O<sub>j</sub>, two OFRs from different threads that both access a location x leading to a conflict. By (3.2.1) and (3.2.2), OFR serializability ensures O<sub>i</sub> and O<sub>j</sub> acquire the lock for x in the correct mode before each access. By the definition of a conflict, one (or both) of O<sub>i</sub> or O<sub>j</sub> is writing x and by (3.2.2) the writer(s) must hold the lock in write mode before the write. By (3.2.3),

whichever region successfully acquired x's lock continues executing, holding the lock until its region ends. The region that did not acquire x's lock waits until the lock is released.

By the assumption that the execution is not conflict serializable, there is another conflict between O<sub>i</sub> and O<sub>j</sub> on another arbitrary location y. As with x, one region acquires y's lock and one waits. If the same region acquires y's lock as acquired x's lock, then that region completes and releases both locks; in the absence of other conflicts, the regions serialize, violating the assumption that the execution is not conflict serializable. If, instead, the region that acquires y's lock was not the one that acquired x's lock, the regions deadlock, each waiting for the other to release its lock. By (3.2.4), OFR serializability precisely detects this deadlock and reports an exception, violating the assumption that the execution was exception-free. Thus, the assumption leads to a contradiction, proving that an exception-free execution is conflict serializable.

## **THEOREM 3.2.6: Unserializability of OFR Exceptions**

If an execution triggers an OFR exception, then the execution is not conflict serializable.

**Proof**. As above, this proof covers the two OFR case, but the argument generalizes to arbitrary conflicts. Assume an OFR exception has been generated. By (3.2.4), an OFR exception corresponds to OFR serializability detecting that two regions are mutually waiting for one another to release locks: region O<sub>i</sub> waits for O<sub>i</sub> to release a lock on location x and O<sub>i</sub> waits for O<sub>i</sub> to release a lock on location y. By (3.2.2), if a region proceeds it will next immediately access the location protected by the lock it waits for. At least one region's imminent access to each variable is a write, because pairs of reads would be allowed to execute concurrently, by (3.2.1). Consequently, the regions' impending accesses form two conflicts, one on x and one on y. Furthermore, by (3.2.1) and (3.2.4), because the regions cyclically wait to acquire locks, the corresponding access conflicts are also cyclic. A case-based analysis shows that an OFR exception indicates a violation of conflict serializability. By the definition of conflict serializability [6], a conflict graph cycle indicates a violation of conflict serializability.

Case 1. In the single variable case, an OFR exception may be triggered by O<sub>i</sub> and O<sub>j</sub> acquiring a lock on x in read-mode and then attempting to upgrade to write-mode. This violates conflict serializability because both threads are attempting to both read and write to the same location x.

Case 2. With two variables, x and y, there are multiple, similar cases that may result in an OFR exception. In all of these cases, O<sub>i</sub> writes to either x or y, and O<sub>j</sub> writes to the opposite location. If both O<sub>i</sub> and O<sub>j</sub> write to the same location and do not incur an upgrade cycle, as in Case 1, the OFRs will serialize on one of the writes. Therefore, the OFRs must write to opposite locations. By the same logic, each OFR must read from the location that it does not write to because writing to both locations would also cause the OFRs to serialize. These conflicting read-write pairs violate conflict serializability.

Note that the correctness proof is sound and complete – an execution free of exceptions is conflict serializable and an exception indicates that an execution is not conflict serializable. By contrast, prior work [8, 47, 66] provided a weaker correctness argument – an exception-free execution is serializable, but an exception corresponds only to a conflict, indicating a data-race, but not a violation of conflict serializability.

## 3.3 QUANTIFYING ATOMICITY

While OFRs have intuitive benefits over finer-grained atomic regions, it may be the case that these advantages do not materialize due to the structure of real programs. To quantify atomicity, it is necessary to consider both the length and width of regions as described in Section 2.3.1.

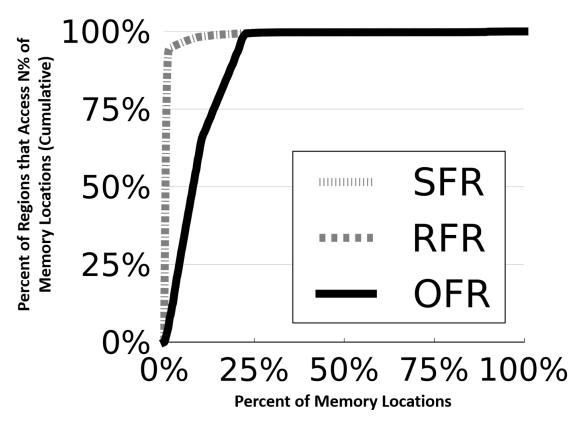

Figure 3.3: Number of breaks in atomicity for each model

Figure 3.3 shows the number of times that atomicity is broken in each programming model. Sequential consistency (SC) logically breaks atomicity after each memory access. Conflict Exceptions (CE, representative of SFRs) breaks atomicity at each lock acquire and release. Release-free regions (RFR) break atomicity at each lock release. IFRs extend CE and RFR to not break atomicity if the memory location will be accessed in the next region. OFRs break atomicity at each ordering construct. As shown, CE, RFR, IFR, and OFR break atomicity a similar number of times when considering only the length of regions. Thus, it is necessary to consider the width of regions to properly quantify the amount of atomicity provided by each of these programming models.

By considering both the length and width of regions, the atomicity of each model can be quantified by examining how many variables (width) are protected by a region of a given size

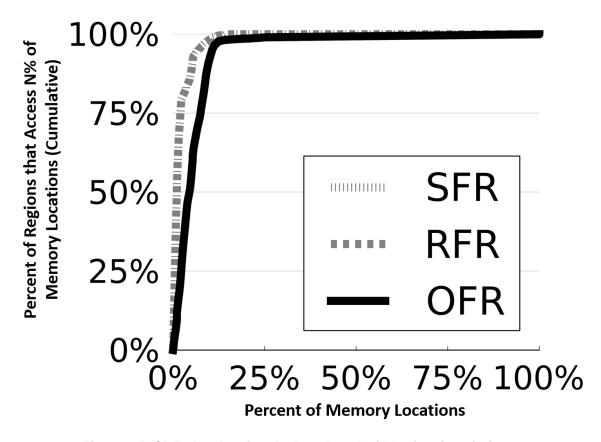

(length). The following CDF plots quantify the atomicity of three parallel applications: blackscholes, ferret, and fluidanimate. The length and width of all regions R were recorded. The length of the region R is the number of dynamic instructions included in that region. The width of the region R is the number of memory locations accessed within that region. These plots detail how many regions have a width of w as a fraction of all regions as a cumulative distribution function. The width metric captures the ability of a consistency model to enforce atomicity across memory locations, reducing the probability of multi-variable atomicity violations. In these CDFs, curves that rise more gently indicate greater atomicity, as there are a substantial proportion of wide regions and a small proportion of low-width (narrow) regions. Curves that rise steeply indicate that most regions are narrow.

Figure 3.4: CDF plot showing the length and width of regions in blackscholes

Figure 3.4 quantifies the amount of atomicity provided by SFRs, RFRs, and OFRs on blackscholes. On this application, the amount of atomicity provided is the same for all three models because blackscholes is an embarrassingly parallel application, meaning that it requires no lock acquires or releases. Therefore, the three models use the same regions.

Figure 3.5: CDF plot showing the length and width of regions in ferret

Figure 3.5 quantifies the amount of atomicity provided by SFRs, RFRs, and OFRs on ferret. ferret is a pipeline parallel application that passes objects from one stage of the pipeline to the next. Each stage of the pipeline executes in parallel and performs disjoint work from all other pipeline stages. Objects are passed from one stage to the next using a queue that employs ordering constructs to prevent threads from dequeuing from an empty queue or enqueuing into a full queue. Most regions applied by SFRs and RFRs are quite small in ferret. The regions used by OFRs tend to be slightly larger, both in length and in width.

Figure 3.6: CDF plot showing the length and width of regions in fluidanimate

Figure 3.6 quantifies the amount of atomicity provided by SFRs, RFRs, and OFRs in fluidanimate. fluidanimate uses complex, fine-grained locking that causes frequent region boundaries for SFRs and RFRs while OFRs are considerably wider due to infrequent barrier synchronization.

Overall, the theoretical benefits of OFRs manifest more clearly in programs with more complicated parallel structure, which are arguably the programs likeliest to suffer from concurrency bugs. From this analysis, there appears to be no significant difference in atomicity between SFRs and RFRs, suggesting that the practical benefits of moving from SFRs to coarsergrained RFRs are limited. However, OFRs clearly provide longer and wider regions than both SFRs and RFRs, indicating that they provide increased atomicity for parallel programs.

# 4 IMPLEMENTING ORDERING-FREE REGIONS

The following section discusses the tradeoffs and decisions in implementing a system that enforces atomicity based on ordering-free regions. These implementations feature a few common components that are required to implement OFR serializability. Each implementation requires a lock design that permits high-performance execution and a shadowspace design that allows efficient retrieval of locks as needed. Similarly, each implementation requires the common API of runtime functions for managing OFR serializability. A distributed deadlock detector is used to detect and report OFR exceptions, and some amount of allocator and compiler support may be required to identify allocations, loads, stores, and other functions of interest.

#### 4.1 Overview

This section examines and discusses three runtime systems that implement OFR serializability. MAMA [20] was implemented as part of our initial investigation into the applicability of OFR serializability to parallel applications. This software-only runtime system leveraged the RoadRunner [32] framework to associate locks with data and provided insights into how future implementations could be made more efficient. From our experiences with the MAMA prototype, we believed that hardware support would be necessary for a reasonably efficient implementation of OFR serializability. We also decided to implement future systems in C and C++ instead of Java due to our desire to use LLVM for compiler optimizations. ORCA [23] introduced hardware support for OFR serializability. We used the Pin [50] dynamic binary instrumentation tool to apply OFR serializability to C and C++ applications in a simulated environment. Although ORCA enforces OFR serializability at low performance overheads, the need for new hardware support was undesirable. SOFRITAS [22] provides OFR serializability using a software-only runtime system and simple compiler instrumentation. SOFRITAS builds upon both MAMA and ORCA to provide OFR serializability efficiently in a software system.

#### 4.2 Locks

Implementing ordering-free regions using locks requires a highly efficient lock design. As described in Section 3, the system that enforces OFR serializability requires that a thread holds a lock in the correct mode on each access to a memory location protected by that lock. This functionality does not necessarily have to be implemented using locks, but the systems designed for this dissertation all rely on locks in their implementations. These locks must be efficient enough to limit the overheads of associating a lock with every memory location and acquiring those locks on every memory access.

Table 4.1: Characterization of memory accesses and lock acquires

| Benchmark         | Memory Accesses | Reads (%) | Writes (%) | Acquires (%) |

|-------------------|-----------------|-----------|------------|--------------|

| blackscholes      | 7.1 Billion     | 85.13%    | 14.87%     | 2.81%        |

| bodytrack         | 95.7 Billion    | 93.23%    | 6.77%      | 3.39%        |

| canneal           | 21.6 Billion    | 96.07%    | 3.93%      | 23.49%       |

| dedup             | 3.1 Billion     | 98.97%    | 1.03%      | 28.79%       |

| ferret            | 187.9 Billion   | 89.43%    | 10.57%     | 5.91%        |

| fluidanimate      | 228.7 Billion   | 88.00%    | 12.00%     | 20.17%       |

| streamcluster     | 428.3 Billion   | 99.57%    | 0.43%      | 51.46%       |

| swaptions         | 196.0 Billion   | 76.58%    | 23.42%     | 0.00%        |

| gups              | 500 Million     | 40.00%    | 60.00%     | 80.00%       |

| kmeans            | 3.2 Billion     | 91.73%    | 8.27%      | 15.12%       |

| pagerank          | 1.2 Billion     | 93.61%    | 6.39%      | 25.30%       |

| histogram         | 3.8 Billion     | 62.50%    | 37.50%     | 0.00%        |

| kmeans            | 14.8 Billion    | 99.80%    | 0.20%      | 1.13%        |

| linear_regression | 4.9 Thousand    | 17.57%    | 82.43%     | 2.46%        |

| matrix_multiply   | 2.0 Billion     | 99.95%    | 0.05%      | 0.05%        |

| рса               | 16.1 Billion    | 99.80%    | 0.20%      | 0.42%        |

| reverse_index     | 2.1 Billion     | 99.56%    | 0.44%      | 49.26%       |

| string_match      | 1.4 Billion     | 34.55%    | 65.45%     | 0.00%        |

| word_count        | 740.5 Million   | 97.46%    | 2.54%      | 0.49%        |

Table 4.1 characterizes the memory accesses performed by 19 parallel applications.

These access characteristics heavily influenced the lock designs used to implement OFR serializability. The *Memory Accesses* column lists the total number of memory accesses

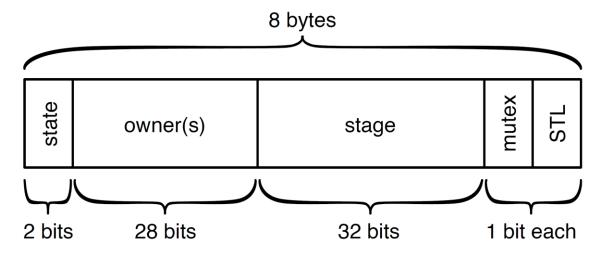

performed by each application. The number of accesses is abnormally low for linear\_regression because most of the memory accesses performed by this application are to a read-only mapped memory region holding file input, which can be safely ignored by the OFR algorithm considering that all accesses must be reads. The accesses shown for gups are round numbers due to the synthetic nature of the benchmark. The second two columns show the percentage of Reads and Writes over all memory accesses. Reads tend to be more common, but some application like gups and string\_match do exhibit a larger number of writes than reads. For this reason, the locks used to implement OFR serializability should be biased toward reads but still allow for efficient writes. The final column (Acquires) shows the percentage of memory accesses that cause a lock acquire under OFR serializability. The non-acquire memory accesses simply check to see if the lock is currently held in the correct permission. Aside from a few outliers, the percentage of acquires tends to be low compared to checks. Thus, the lock design should be biased toward fast checks but still permit relatively fast acquires when possible.

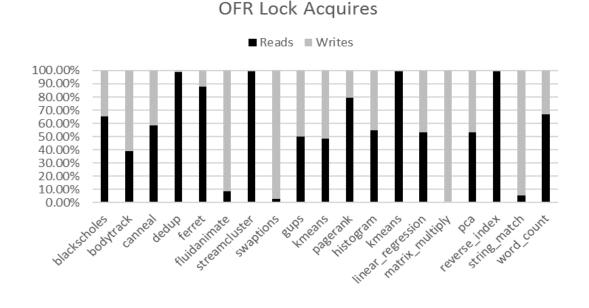

Table 4.2: Characterization of lock acquires as reads or writes

Table 4.2 characterizes the modes that locks are acquired in to enforce OFR serializability. Although the applications are more likely to favor read acquires over write

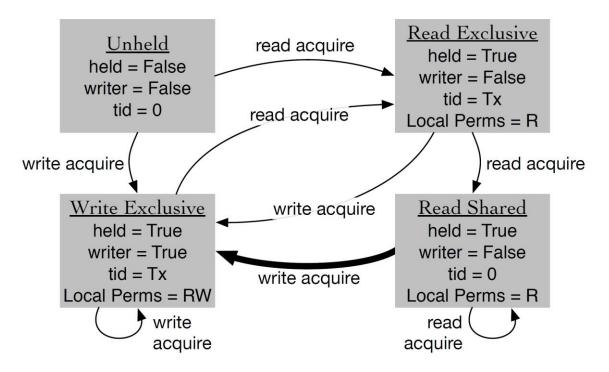

acquires, there are many applications that instead favor write acquires over read acquires. Therefore, the lock designs should not heavily bias to one type of acquire over the other. In general, the locks used to implement OFR serializability attempt to optimize for common case transitions between lock states. For example, threads may use the same variables in successive ordering-free regions. In this case, the lock should be designed to allow the thread to efficiently reacquire the locks that it held in the previous OFR.

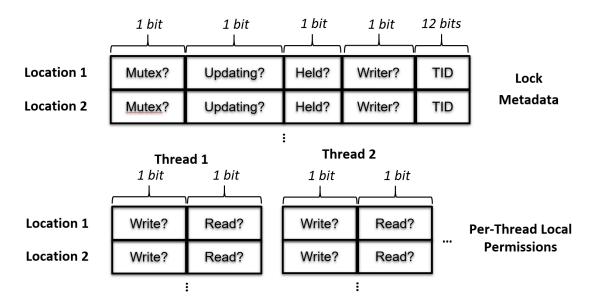

Aside from being efficient, the locks used to implement OFR serializability must provide the features necessary to interact with the rest of the OFR runtime system. First, both reader-writer and mutex locks must be available, whether the same lock implements both or two separate lock types are used. Neither reader-writer nor mutex locks avoid strictly more deadlocks, so both types must be available to the runtime system. Second, the locks must indicate the current owners and state to allow the system to detect cycles, which in turn are forwarded to the user as exceptions. Unlike conventional locks used in multithreaded systems, OFR locks cannot simply indicate whether the lock is currently held or not. OFR locks are similar to re-entrant locks that track which thread currently holds the lock and allows a simple check rather than an acquire if the current owner attempts to acquire the lock a second time.

#### 4.2.1 Eager or Lazy Releases

The OFR execution model discussed thus far **eagerly** releases all locks at every ordering construct, which is sufficient to guarantee 2PL serializability of OFRs but comes with a large performance tax. Eagerly releasing locks at all ordering constructs can be accomplished in a number of ways. In any implementation, logically, a list of locks held by each thread must be maintained in some way, or the lock structures must be designed to make such a list unnecessary. A naïve solution might simply maintain a per-thread list of every lock the thread has acquired. This solution would require additional overhead on every lock acquire, and eagerly releasing locks would require a list traversal to release every lock held by the thread. A per-

thread version number could also be added to each lock to identify which locks have been acquired in the current ordering-free region, but this solution would increase the size and complexity of the locks substantially (similarly to maintaining a vector clock for data-race detection.

Alternatively, locks can be released using a **lazy** policy that only releases locks when another thread attempts to acquire them. This lazy release policy holds locks across ordering constructs. Locks can still be released by threads waiting at an ordering construct: if a thread  $T_0$  holds a lock  $L_x$  and is blocked at a barrier, another thread  $T_1$  can **steal**  $L_x$ .  $T_0$ 's OFR serializability is preserved because the OFR in which  $T_0$  acquired  $L_x$  must have ended, as  $T_0$  is at an ordering construct. Lazy releases do not compromise OFR atomicity, and in fact strengthen it – in the absence of steals, a variable's atomicity is preserved across multiple OFRs. A subtlety of lazy releases is that a dependence cycle may not violate 2PL serializability. Consider the case in which a thread  $T_0$  holds a lock  $L_x$  on some location x and does not release that lock at the end of its ordering-free region  $O_1$ . If another thread  $T_1$  similarly holds a lock  $L_y$  on location y and does not release that lock at the end of its ordering free region  $O_1$ ,  $T_0$  and  $T_1$  may deadlock if  $T_0$  attempts to acquire  $L_y$  in its new OFR  $O_2$  and  $T_1$  attempts to acquire  $L_x$  in its new OFR  $O_2$ . Both threads have moved on to new ordering-free regions  $O_2$  and  $O_2$ , but the lazy release of locks has caused a dependence cycle that would not have existed if locks had been eagerly released.

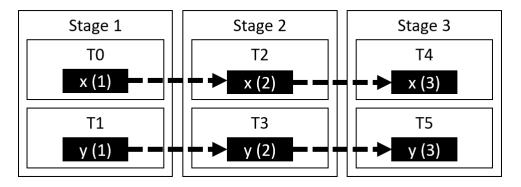

Precisely supporting lazy releases would require an implementation similar to a vector-clock, which would be unlikely to provide improved performance. In practice, it is possible to use a more targeted form of lazy releases that does not require a full vector clock. Both pipeline parallelism and barrier-based synchronization can be supported by a scalar **stage** that enables lazy releases of locks between ordering-free regions.

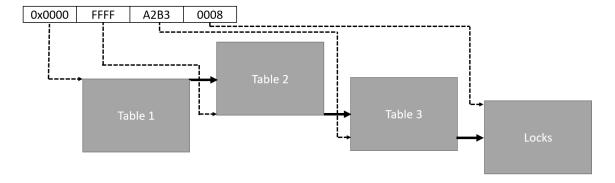

Figure 4.1: Pipeline stages using staged locking to lazily pass locks from one stage of the pipeline to the next. Stage is shown in parentheses

Figure 4.1 demonstrates how stages can be used to lazily transfer locks from one stage of a pipeline to the next. This pattern is found in applications like dedup and ferret which pass objects through a parallel pipeline. Within the same stage, locks cannot be stolen. For example, To and T1 would not be able to steal each other's locks. If T0 and T1 produce an OFR exception, it is a true exception and not generated due to the structure of the parallelism. T2 and T3 can steal locks from T0 and T1 because they are part of a later stage of the pipeline and often receive data that T0 and T1 are no longer using. Supporting pipeline parallelism with a scalar stage requires a small stage due to the limited number of pipeline stages that will practically be used in most parallel applications. The programmer must indicate via an annotation which threads belong to which pipeline stages. Staging annotations are untrusted and are verified at runtime: an incorrect staging annotation that contradicts the program's sharing patterns will trigger an OFR exception to support straightforward debugging. However, pipeline parallelism is not the only type of parallelism that can be aptly supported by a scalar stage.

Figure 4.2: Stages of a barrier-based application

Parallel applications often use barriers to delimit phases of the parallel algorithm. Such applications also lend themselves to the use of a scalar stage for lazy lock releases. Figure 4.2 demonstrates how locks can be passed from one stage of a barrier-based application to the next. As shown, some memory locations (*e.g. x*) may be locked by the same thread in subsequent stages. In these cases, the stage is updated when the lock is tested for proper permissions. In a barrier-based application, a thread may steal a lock from another thread if the current stage of execution is greater than the scalar stage indicated by the lock. A thread can steal locks held by a thread in a previous stage, but not from its own stage or future stages. This use of stages assumes that all threads that are sharing data participate in the same barriers and therefore have matching stages. Unlike pipeline stages, barrier stages can be automatically identified at runtime (i.e. as each barrier\_wait() occurs).

# 4.2.2 Debugging Metadata and Annotation Suggestions

To apply OFR serializability to a parallel application, the programmer must properly apply annotations from the OFR API to the code. A runtime system can assist the programmer with this task by providing suggestions based on the behavior of locks. However, the runtime system must use additional metadata to provide useful suggestions, and therefore this functionality is generally used for debugging and not during production.

When a dependence cycle occurs, the execution of the two or more threads involved will stop precisely at the lines of code that complete the cycle. Although the information found on those lines of code may be useful to the programmer, it may not identify the root cause of the dependence cycle. To locate the root cause, the programmer needs to know where the data associated with each lock was last accessed by that lock's owner. In debugging mode, locks track the last read and last write source-code location for each memory location. This information can be represented as an integer that maps to a source-code file and line number. This information is updated on each read or write to a memory location. When a dependence cycle is detected, the runtime system will suggest that the programmer place a Release() annotation at either the last read or last write line of source-code, depending on structure of the dependence cycle. The runtime system can also suggest RequireMutex() annotations in the case of read-to-write upgrade dependence cycles.

The behavior of the runtime system can also provide useful suggestions to the programmer to improve the performance of the application under OFR serializability. By examining lock contention, the runtime system can identify instances in which the application serializes on accesses to some memory location and suggest that the programmer add a Release() annotation to avoid unnecessary serialization. The runtime system can also identify frequent lock reacquires, which may indicate that a ContinueOFR() annotation can be applied. These performance suggestions should be carefully considered by the programmer so to not compromise safety for performance.

# 4.3 Shadowspace

Efficiently checking and acquiring locks in a system that provides OFR serializability requires an efficient mapping from each memory location to its associated lock. Locks are stored in a **shadowspace** that corresponds to the memory allocated by a parallel application. Multiple design choices can influence the runtime and space overheads of retrieving locks, including the granularity of mapping, the flexibility of mapping, and the use of a monolithic or distributed mapping.

# 4.3.1 Mapping Granularity

The mapping granularity of the shadowspace affects both the efficiency and the usability of ordering-free regions. A coarse mapping may provide better performance, but a coarse mapping may also cause false OFR exceptions to be generated.

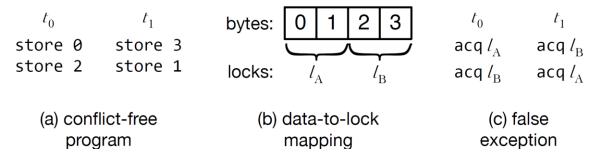

Figure 4.3: Example demonstrating how a coarse mapping leads to a false OFR exception

Figure 4.3 shows how a coarse mapping can lead to a false exception. The example assumes a mapping from each set of 2 bytes to a lock.  $T_0$  accesses byte 0 and then byte 2 while  $T_1$  accesses byte 3 and then byte 1. Due to the lock mapping, this access pattern causes  $T_0$  to acquire  $L_A$  and then attempt to acquire  $L_B$  while  $T_1$  acquires  $L_B$  and then attempts to acquire  $L_A$ , leading to a cycle. With a byte-to-lock mapping, there would be no cycle in the lock acquires because the bytes accessed by  $T_0$  and  $T_1$  do not overlap.

In C and C++, there is no mapping provided from bytes of data to their structure. By default, the runtime system does not know the structure of objects in memory. Thus, a straightforward way to map data to locks in C and C++ is to choose a fixed mapping from some number of bytes to a lock. Many parallel applications do not access data at byte granularity, but some do. For the applications that only access data at word (4-byte) granularity, a shadowspace mapping from words to locks would be appropriate to save space. However, for the applications that access data at byte granularity, a byte to lock mapping is necessary to avoid false exceptions. The evaluation of the systems used to enforce OFR serializability quantifies the tradeoff between byte and word mappings.

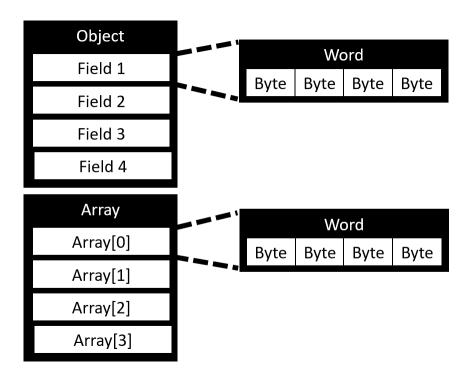

Languages like Java provide details on the structure of objects in memory that are available to a runtime system [32]. By default, Java maintains mappings of bytes and words to the fields and elements that comprise objects and arrays. Therefore, Java permits a more coarse-grained mapping than C and C++ because the runtime system is aware of the granularity at which the application will access data. The system can still choose a coarse or fine-grained mapping for locks in Java. For objects, the system can choose to either map from fields to locks or from objects to locks, and for arrays, the system can choose to either map from array elements to locks or from arrays to locks. These mappings have the same tradeoffs as byte and word granularity mappings for C and C++.

Figure 4.4: The lock shadowspace can be coarse or fine-grained

Figure 4.4 shows the granularity of mappings available in both C++ and Java. In Java, object fields and array elements can be mapped to locks because the runtime system is aware of the structure of data. In C++, only groups of bytes can be mapped to locks because the runtime system does not maintain mappings of bytes to structures. Java also permits an inline instrumentation that adds locks next to the fields or array elements that those locks protect. In C and C++, there is no guarantee that the code will not create a pointer and walk over the bytes of an object, so it is generally not safe to add locks to objects or array inline. Thus, a lock shadowspace for C and C++ applications should be disjoint from the memory being shadowed.

# 4.3.2 Rigid or Flexible Mapping

As mentioned in the previous section, associating locks with memory locations in C and C++ necessitates the use of a shadowspace that is disjoint from program memory. This disjoint shadowspace can be structured as either a rigid or flexible mapping from program memory to the lock shadowspace.

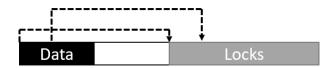

Figure 4.5: Rigid mapping from data to locks

A rigid mapping uses arithmetic to translate from each program memory address to the address of a corresponding lock. A rigid mapping requires a fixed lock format and a specific memory layout. Figure 4.5 demonstrates how a rigid mapping translates from data addresses to lock addresses. Using a fixed mapping requires few arithmetic instructions and limits the work necessary to check the state of a lock.

Figure 4.6: A lock trie maps data addresses to lock addresses

A more flexible translation process would admit different lock representations for different memory locations, e.g., more space-efficient mutex locks and contention-aware locks for frequently-accessed locations. To provide this flexibility, we explored an alternative shadowspace design that uses a four-level trie (like a page table) to map data to locks. Figure 4.6

demonstrates how a lock trie maps data addresses to lock addresses. The bytes of the data address are used to index tables that store pointers to lower level tables. The lowest level of tables stores the locks. This approach requires more instructions to access locks compared to the fixed mapping approach. However, the trie approach allows flexible lock formats and flexible mappings from data to locks. For example, this mapping would allow a single lock to protect a large set of data addresses. The performance evaluation of OFR serializability in later sections examines the performance tradeoffs associated with using a lock trie instead of a fixed mapping.

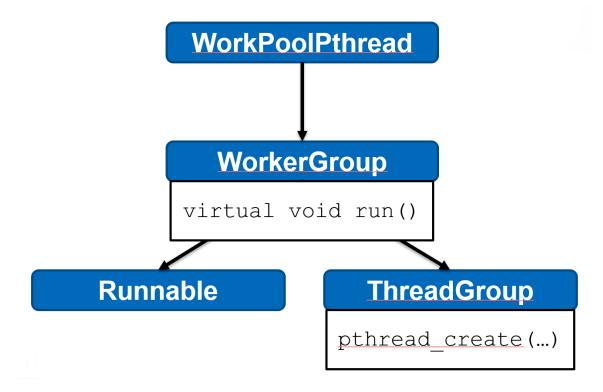

#### 4.3.3 Lock and Shadowspace Design: MAMA