**Publicly Accessible Penn Dissertations**

2017

## Flexible, Photopatterned, Colloidal Cdse Semiconductor Nanocrystal Integrated Circuits

Franklin Scott Stinner *University of Pennsylvania*, stinnerf@seas.upenn.edu

Follow this and additional works at: https://repository.upenn.edu/edissertations

Part of the <u>Electrical and Electronics Commons</u>, <u>Mechanics of Materials Commons</u>, and the <u>Nanoscience and Nanotechnology Commons</u>

#### Recommended Citation

Stinner, Franklin Scott, "Flexible, Photopatterned, Colloidal Cdse Semiconductor Nanocrystal Integrated Circuits" (2017). *Publicly Accessible Penn Dissertations*. 2698.

https://repository.upenn.edu/edissertations/2698

This paper is posted at ScholarlyCommons. https://repository.upenn.edu/edissertations/2698 For more information, please contact repository@pobox.upenn.edu.

### Flexible, Photopatterned, Colloidal Cdse Semiconductor Nanocrystal Integrated Circuits

#### **Abstract**

As semiconductor manufacturing pushes towards smaller and faster transistors, a parallel goal exists to create transistors which are not nearly as small. These transistors are not intended to match the performance of traditional crystalline semiconductors; they are designed to be significantly lower in cost and manufactured using methods that can make them physically flexible for applications where form is more important than speed. One of the developing technologies for this application is semiconductor nanocrystals.

We first explore methods to develop CdSe nanocrystal semiconducting "inks" into large-scale, high-speed integrated circuits. We demonstrate photopatterned transistors with mobilities of 10~cm2/Vs on Kapton substrates. We develop new methods for vertical interconnect access holes to demonstrate multi-device integrated circuits including inverting amplifiers with ~7 kHz bandwidths, ring oscillators with <10 >  $\mu s$  stage delays, and NAND and NOR logic gates.

In order to produce higher performance and more consistent transistors, we develop a new hybrid procedure for processing the CdSe nanocrystals. This procedure produces transistors with repeatable performance exceeding 40 cm2/Vs when fabricated on silicon wafers and 16 cm2/vs when fabricated as part of photopatterned integrated circuits on Kapton substrates.

In order to demonstrate the full potential of these transistors, methods to create high-frequency oscillators were developed. These methods allow for transistors to operate at higher voltages as well as provide a means for wirebonding to the Kapton substrate, both of which are required for operating and probing high-frequency oscillators. Simulations of this system show the potential for operation at MHz frequencies. Demonstration of these transistors in this frequency range would open the door for development of CdSe integrated circuits for high-performance sensor, display, and audio applications.

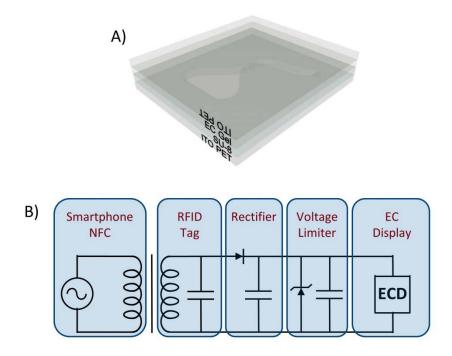

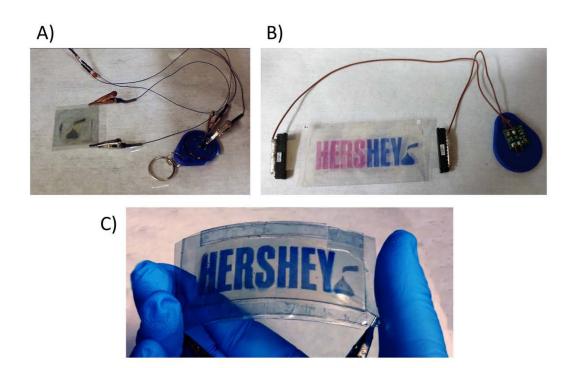

To develop further applications of electronics on flexible substrates, procedures are developed for the integration of polychromatic displays on polyethylene terephthalate (PET) substrates and a commercial near field communication (NFC) link. The device draws its power from the NFC transmitter common on smartphones and eliminates the need for a fixed battery. This allows for the mass deployment of flexible, interactive displays on product packaging.

#### Degree Type

Dissertation

#### Degree Name

Doctor of Philosophy (PhD)

#### **Graduate Group**

**Electrical & Systems Engineering**

#### First Advisor

Cherie R. Kagan

# FLEXIBLE, PHOTOPATTERNED, COLLOIDAL CdSe SEMICONDUCTOR NANOCRYSTAL INTEGRATED CIRCUITS

#### F. Scott Stinner

#### A DISSERTATION

in

Electrical and Systems Engineering

Presented to the Faculties of the University of Pennsylvania

in

Partial Fulfillment of the Requirements for the

Degree of Doctor of Philosophy

2017

| Supervisor of Dissertation                                                                            |

|-------------------------------------------------------------------------------------------------------|

| Dr. Cherie Kagan, Stephen J. Angello Professor, Electrical and Systems Engineering                    |

| Graduate Group Chairperson                                                                            |

| Dr. Alejandro Ribeiro, Associate Professor, Electrical and Systems Engineering                        |

| Dissertation Committee  Dr. Mark Allen (Chair), Alfred Fitler Moore Professor, Electrical and Systems |

Dr. Firooz Aflatouni, Skirkanich Assistant Professor, Electrical and Systems Engineering

Engineering

To my family, my friends, and all who supported me, especially cheese doodles

#### Acknowledgments

I would like to thank:

My advisor, Cherie Kagan, for an unfathomable amount of support and guidance, both financially and scholastically, and for continuing to believe I would get here someday, even when I did not.

My wife for loving me, supporting me, and giving me happiness every day.

My collaborators, Yuming Lai, David Kim, E.D. Goodwin, Daniel Straus, and Ben Diroll for being my mentors, training me, teaching me everything I needed to know, and making everything I needed. Your tireless efforts made my research possible.

The whole of the Kagan and Murray Groups for keeping the labs running and sharing with me all of your invaluable knowledge and experience.

My doctoral committee, Firooz Aflatouni and Mark Allen, for their guidance and support.

The staff of the Wolf/Quattrone Nanofabrication Facility for your guidance, support, and for working hard to keep things running smoothly.

Paul Horng and the rest of the staff at the University of Delaware Nanofabrication Facility for providing me with access to and guidance within their facilities.

Pete Angeline and the Hershey Digital Innovation Lab for providing me with interesting project while I wrapped up my dissertation.

The countless other students, faculty, and staff who assisted me in a variety of ways. Your efforts are appreciated.

The Penn Band Nation for keeping me [in]sane. There are far too many of you to list individually but all of your support, advice, and friendship is invaluable.

All of my family and friends for their unwavering support and for always understanding that I am "around two years" from graduating.

My financial support from The Ashton Fellowship, The NSF, under Award No. PFI: AIR ENG-1312202, and The Hershey Digital Innovation Lab.

#### **ABSTRACT**

# FLEXIBLE, PHOTOPATTERNED, COLLOIDAL CdSe SEMICONDUCTOR NANOCRYSTAL INTEGRATED CIRCUITS

#### F. Scott Stinner

#### Cherie Kagan

As semiconductor manufacturing pushes towards smaller and faster transistors, a parallel goal exists to create transistors which are not nearly as small. These transistors are not intended to match the performance of traditional crystalline semiconductors; they are designed to be significantly lower in cost and manufactured using methods that can make them physically flexible for applications where form is more important than speed. One of the developing technologies for this application is semiconductor nanocrystals.

We first explore methods to develop CdSe nanocrystal semiconducting "inks" into large-scale, high-speed integrated circuits. We demonstrate photopatterned transistors with mobilities of  $10~{\rm cm^2/Vs}$  on Kapton substrates. We develop new methods for vertical interconnect access holes to demonstrate multi-device integrated circuits including inverting amplifiers with ~7 kHz bandwidths, ring oscillators with <10  $\mu$ s stage delays, and NAND and NOR logic gates.

In order to produce higher performance and more consistent transistors, we develop a new hybrid procedure for processing the CdSe nanocrystals. This procedure produces transistors with repeatable performance exceeding 40 cm<sup>2</sup>/Vs when fabricated

on silicon wafers and 16 cm<sup>2</sup>/vs when fabricated as part of photopatterned integrated circuits on Kapton substrates.

In order to demonstrate the full potential of these transistors, methods to create high-frequency oscillators were developed. These methods allow for transistors to operate at higher voltages as well as provide a means for wirebonding to the Kapton substrate, both of which are required for operating and probing high-frequency oscillators. Simulations of this system show the potential for operation at MHz frequencies. Demonstration of these transistors in this frequency range would open the door for development of CdSe integrated circuits for high-performance sensor, display, and audio applications.

To develop further applications of electronics on flexible substrates, procedures are developed for the integration of polychromatic displays on polyethylene terephthalate (PET) substrates and a commercial near field communication (NFC) link. The device draws its power from the NFC transmitter common on smartphones and eliminates the need for a fixed battery. This allows for the mass deployment of flexible, interactive displays on product packaging.

#### TABLE OF CONTENTS

| ACKNOWLEDGMENTSIII                                                    |

|-----------------------------------------------------------------------|

| ABSTRACTIV                                                            |

| TABLE OF CONTENTSVI                                                   |

| LIST OF ILLUSTRATIONSIX                                               |

| CHAPTER 1 : BACKGROUND 1                                              |

| 1-1 : Colloidal Semiconductor Nanocrystals1                           |

| 1-2 : Nanocrystal TFTs2                                               |

| 1- 3 : Low-Speed Flexible Nanocrystal Integrated Circuits3            |

| 1-4: Air Stable CdSe NC TFTs7                                         |

| 1-5 : Flexible, Photopatterned CdSe Nanocrystal Integrated Circuits10 |

| 1-6 : References                                                      |

| CHAPTER 2 : FLEXIBLE, HIGH-SPEED CDSE NANOCRYSTAL                     |

| INTEGRATED CIRCUITS14                                                 |

| 2-1 : Introduction14                                                  |

| 2-2 : Methods                                                         |

| 2-3: Results and Discussion                          |

|------------------------------------------------------|

| 2-4 : Conclusions30                                  |

| 2-6 : Appendix31                                     |

| 2-5 : References                                     |

| CHAPTER 3 : THE HYBRID EXCHANGE PROCEDURE46          |

| 3-1: Background and Motivation46                     |

| 3-2: Methods49                                       |

| 3-3: Results51                                       |

| 3-4: Conclusions60                                   |

| 3-5 : References                                     |

| CHAPTER 4 : FLEXIBLE CDSE NANOCRYSTAL OSCILLATORS 64 |

| 4-1: Introduction64                                  |

| 4-2: Methods68                                       |

| 4-3: Discussion and Results72                        |

| 4-4: Conclusions78                                   |

| 4-5: Appendix80                                      |

| 4-6 : References86                                   |

## CHAPTER 5 : NFC POWERED FLEXIBLE ELECTROCHROMIC DISPLAYS 88

|      | 5-1: Introduction                      | 88  |

|------|----------------------------------------|-----|

|      | 5-2: Materials and Methods             | 90  |

|      | 5-3: Results                           | 94  |

|      | 5-4: Conclusions                       | 99  |

|      | 5-5 : References                       | 100 |

| СНАІ | PTER 6 : FUTURE DIRECTIONS             | 101 |

|      | 6-1: Nanocrystal Oscillators           | 101 |

|      | 6-2 : Multi-Stage Integrated Circuits  | 102 |

|      | 6-3 : Non-Linear CdSe NC-TFT Modeling  | 103 |

|      | 6-4 : CdSe Nanocrystal Photopatterning | 108 |

|      | 6-5 : References                       | 112 |

#### LIST OF ILLUSTRATIONS

#### Chapter 1: Background

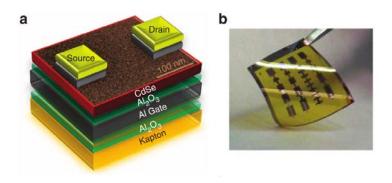

- **Figure 1-1** (A) Schematic of shadow mask patterned CdSe NC FET on Kapton substrate. (B) Photograph of shadow mask patterned CdSe TFTs. (Reproduced from Kim, D. *et al*, 2012)

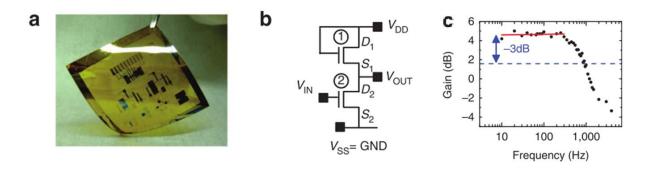

- **Figure 1-2** (A) Photograph of shadow mask patterned CdSe NC TFT inverter. (B) Circuit schematic of CdSe NC inverter. (C) Bode Plot of the output of a shadow mask patterned CdSe NC TFT inverting amplifier. (Reproduced from Kim, D. *et al*, 2012)

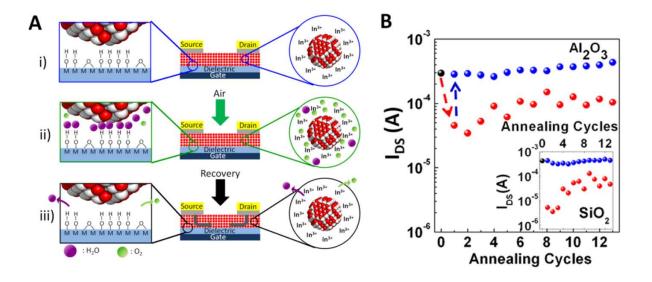

- **Figure 1-3** (A) Schematic representation of indium-driven CdSe recovery. (B) Plot of maximum drain current after exposure to atmosphere (red) and subsequent recovery annealing (blue). (Reproduced from Choi, J. *et al*, 2013)

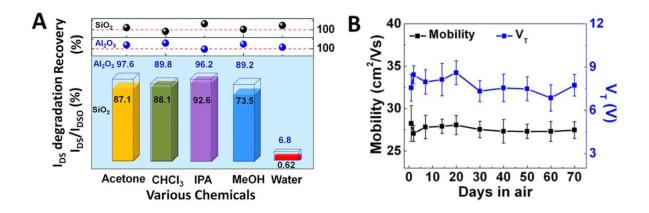

- **Figure 1-4** (A) Plot of percentage maximum drain current (I<sub>DS</sub>) loss following exposure to different solvents for CdSe NC TFTs (bar graph) on SiO<sub>2</sub> (black) and Al<sub>2</sub>O<sub>3</sub> (blue) substrates as well as a plot of the percentage recovery after annealing (dots at top). (B) Plot of mobility (black) and threshold voltage (blue) vs. time of NC TFTs stored and measured in atmosphere. (Reproduced from Choi, J. *et al*, 2013)

#### Chapter 2: Flexible, High-Speed CdSe Nanocrystal Integrated Circuits

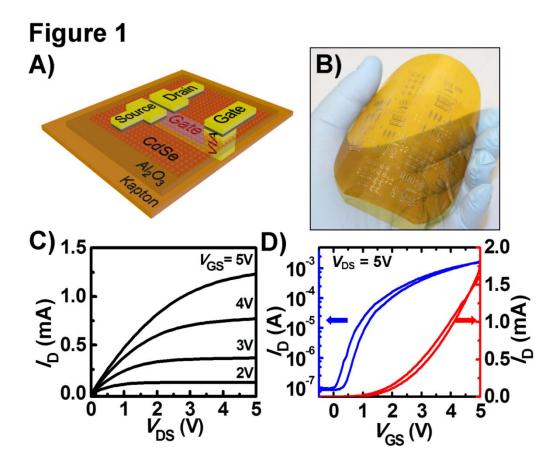

- **Figure 2-1** (A) Schematic of a CdSe NC-FET and a VIA used as building blocks to construct NCICs. (B) Photograph of an array of CdSe NCICs fabricated on a 4 inch, flexible, Kapton substrate. (C) Output  $I_D$ - $V_{DS}$  and (D) transfer  $I_D$ - $V_{GS}$  characteristics of a flexible CdSe NC-FET with photolithographically-patterned electrodes defining a channel length L= 10  $\mu$ m and width W= 1000  $\mu$ m.

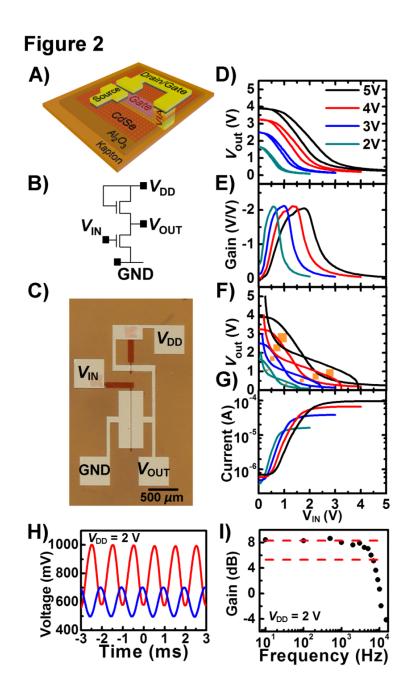

- **Figure 2-2** (A) Schematic of the load transistor used to construct the NCIC inverter. (B) Circuit diagram and (C) photograph of a flexible, CdSe NCIC inverter. The output voltage ( $V_{OUT}$ ) is measured as a function of the input voltage ( $V_{IN}$ ) for different supply voltages ( $V_{DD}$ ) applied with respect to ground (GND). (D) Voltage transfer characteristics ( $V_{OUT}$ - $V_{IN}$ ), (E) voltage gain, (F) noise margin (orange squares), and (G) drain current for a CdSe NCIC inverter as a function of the supply voltage  $V_{DD}$ . (H) Output waveform (red) of a NCIC voltage amplifier in response to a 1 kHz, 200 mV sinusoidal input on a 600 mV DC input bias (blue). (I) Frequency response (Bode Plot) of a NCIC voltage amplifier (black circles). A linear fit (red dashed line, top) shows a 8.3 dB voltage gain at low frequency, which is used to find the 3 dB bandwidth (red dashed line, bottom).

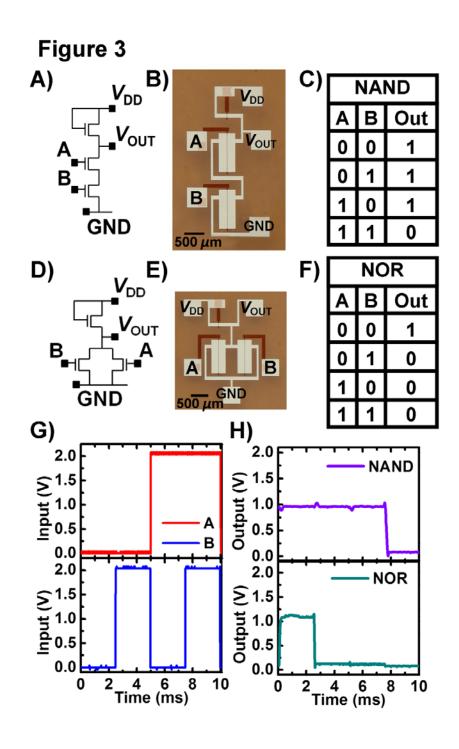

**Figure 2-3** Circuit diagrams, photographs, and truth tables of flexible, CdSe NCIC (A, B, C) NAND and (D, E, F) NOR logic gates. (G) Waveforms for input voltages ( $V_{IN}$ ) on the A (red) and B (blue) driver NC-FETs, which are switched at 100 Hz and 200 Hz, respectively. (H) Output waveforms ( $V_{OUT}$ ) for NCIC NAND (purple) and NOR (green) logic gates with VDD = 2 V.

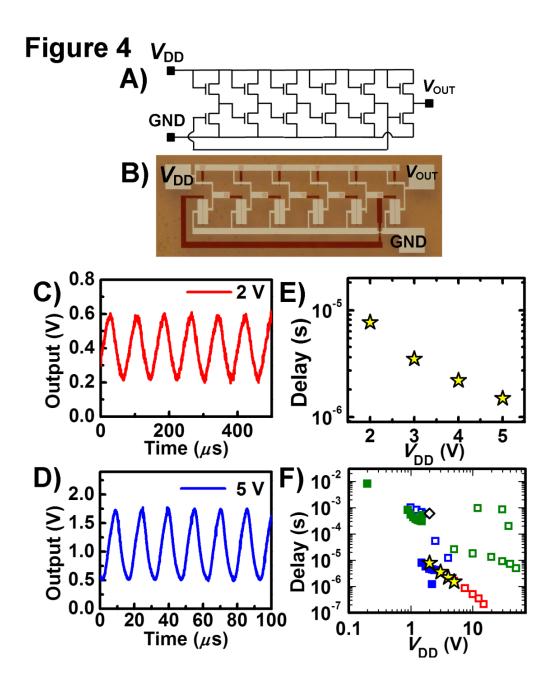

**Figure 2-4** (A) Circuit diagram, (B) photograph, and output characteristics at (C) 2 V and (D) 5 V supply voltages ( $V_{DD}$ ) for a five-stage CdSe NCIC ring oscillator with a sixth stage buffer. (E) Delay per stage versus supply voltage ( $V_{DD}$ ) for a CdSe NCIC ring oscillator. (F) Comparison of the delay per stage versus supply voltage ( $V_{DD}$ ) for solution-processable, semiconducting (green) organic, (blue) carbon nanotube array, (red) sol-gel metal oxide, and (black) colloidal nanocrystal channel layers. Circuits are fabricated on (filled symbols) rigid substrates and (open symbols) flexible substrates. The flexible, CdSe NCICs reported here are highlighted as yellow-filled, black stars.

#### Chapter 3: The Hybrid Exchange Procedure

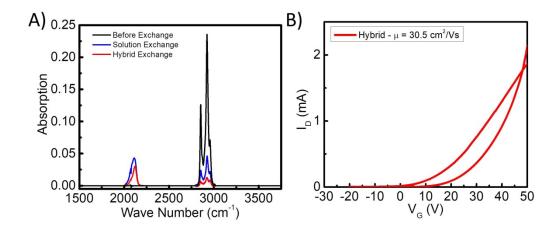

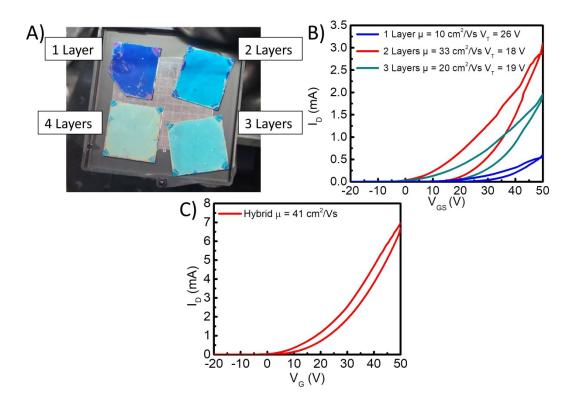

**Figure 3-1** (A) Comparison of FTIR measurements of NC films formed from assynthesized particles as well as following solution and hybrid exchange. (B) Transfer characteristics ( $I_D$ - $V_{GS}$ ) of hybrid exchanged CdSe NC-TFT with channel length L=50  $\mu$ m and channel width W=750  $\mu$ m.

**Figure 3-2** (A) Photograph of a step-by-step addition of layers of a hybrid exchanged CdSe NC film deposited on  $SiO_2$  coated silicon wafer. (B) Comparison of transfer characteristics ( $I_D$ - $V_{GS}$ ) of multiple layers of hybrid exchanged CdSe NC-TFTs with channel length L=50  $\mu$ m and channel width W=750  $\mu$ m. The 4 layer result is omitted due to the lack of current modulation. (C) Transfer characteristic of optimized 2-layer hybrid device.

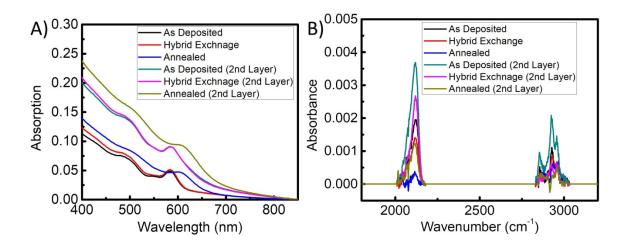

**Figure 3-3** (A) UV-Vis and (B) FTIR measurements comparing each step in the process of depositing 2 layers of hybrid exchanged CdSe NCs.

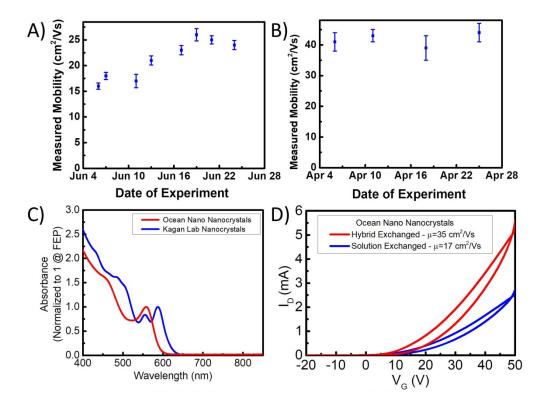

**Figure 3-4** Average mobility as calculated from a fit of the transfer characteristics over time for (A) solution and (B) hybrid exchnaged NC TFTs. Each data point represents two CdSe thin films on silicon with  $Al_2O_3/SiO_2$  dielectric stack ,measuring 6-8 TFTs measured on each, depending on yield. (C) Comparison of UV-Vis measurements of CdSe NCs made in the Kagan Lab and by Ocean Nanotechnology. (D) Comparison of transfer characteristics ( $I_D$ -V<sub>GS</sub>) of hybrid and solution exchanged CdSe NC-TFTs made from Ocean Nanotechnology NCs with channel length L=50 μm and channel width W=750 μm.

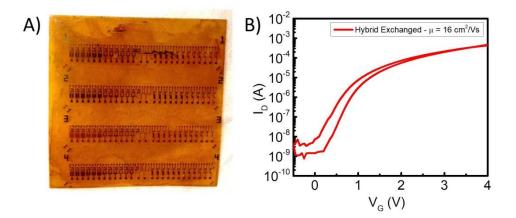

**Figure 3-5** (A) Photograph of sample with hybrid exchanged CdSe NC-TFTs with photopatterned electrodes. (B) Transfer characteristics (I<sub>D</sub>-V<sub>GS</sub>) of hybrid exchanged NC-

TFT with photopatterned electrodes with channel length L=40  $\mu$ m and channel width W=1000  $\mu$ m.

#### Chapter 4: Flexible CdSe Nanocrystal Oscillators

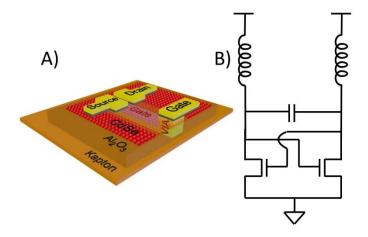

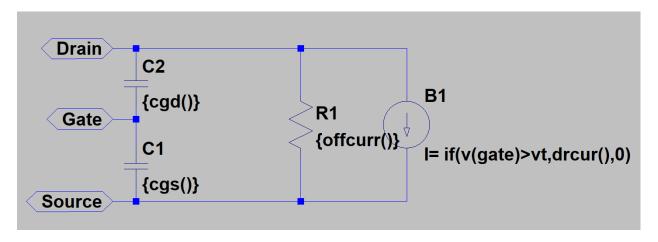

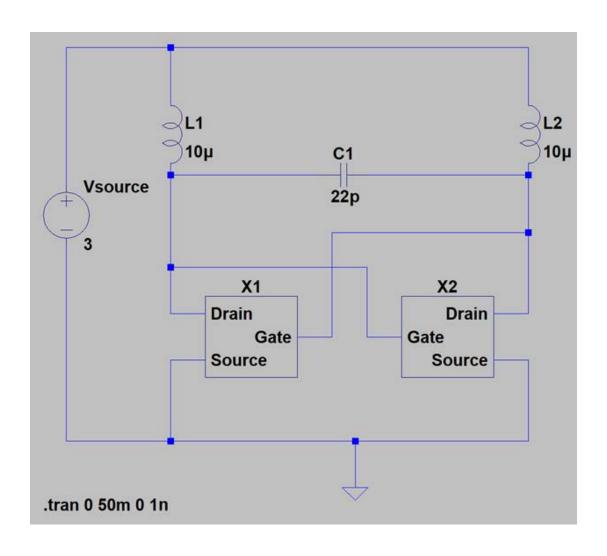

- **Figure 4-1** (A) Schematic of a CdSe NC-TFT. (B) Circuit diagram of simple oscillator structure.

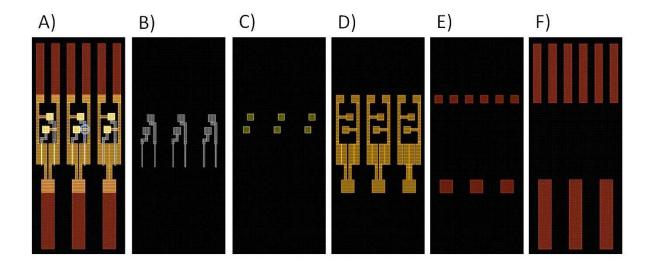

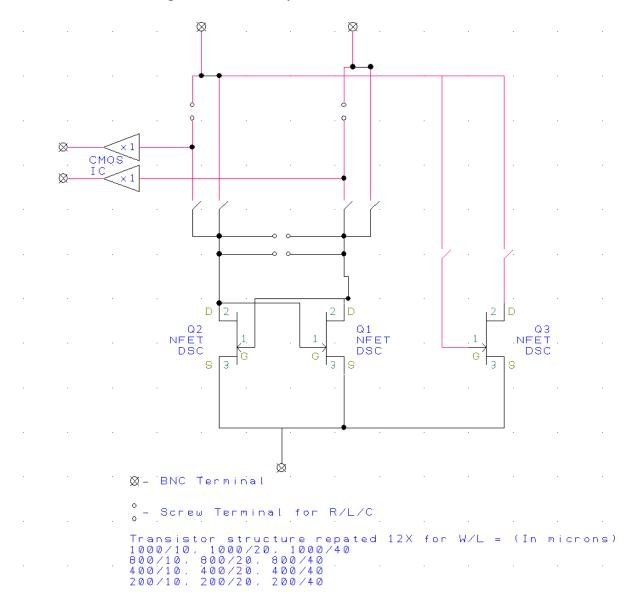

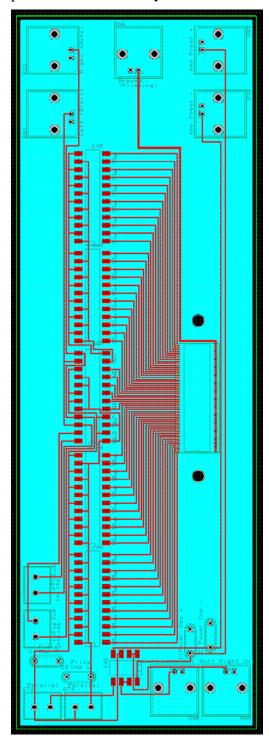

- **Figure 4-2** A small section of the photomask designs for NC oscillators with TFT channel width  $W=800~\mu m$  and channel length L=10, 20, 40  $\mu m$  including (A) all layers overlaid, (B) the gate, (C) VIA, (D) source and drain electrodes, (E) contact pad wirebonding electrodes, and (F) extended wirebonding electrode patterns, respectively. The source of the overlap capacitance is indicated in the overlaid image by the blue circle, resulting from an overlap of the gate and source and drain electrode layers.

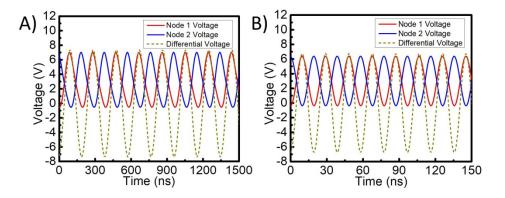

- **Figure 4-3** Output of simulation of oscillator circuit using (A) 10  $\mu$ H (~5 MHz) and (B) 100 nH (~50 MHz) external inductors.

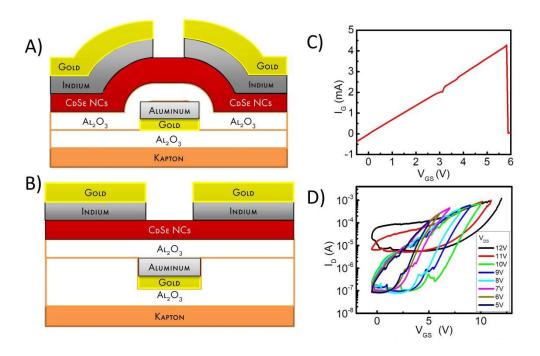

- **Figure 4-4** Diagram of a CdSe NC-TFT (A) without and (B) with gate electrodes inset into an oxide foundation. (C) Gate current measurement ( $I_{G}$ - $V_{GS}$ ) of device oxide breaking down at  $V_{GS} > 5V$ . (D) Transfer characteristics ( $I_{D}$ - $V_{GS}$ ) of a CdSe NC-TFT with gate inset into the oxide foundation.

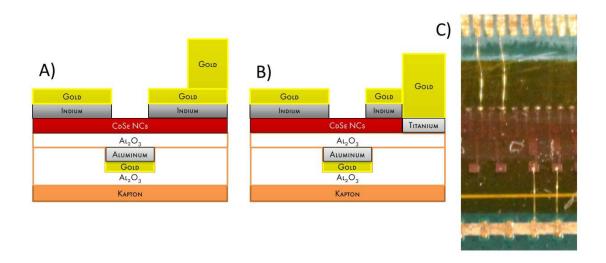

- **Figure 4-5** (A) Diagram of CdSe NC-TFT with wirebond contact on top of source and drain contacts and (B) with wirebond contacts directly placed on gate oxide. (C) Photograph of successfully wirebonded contacts.

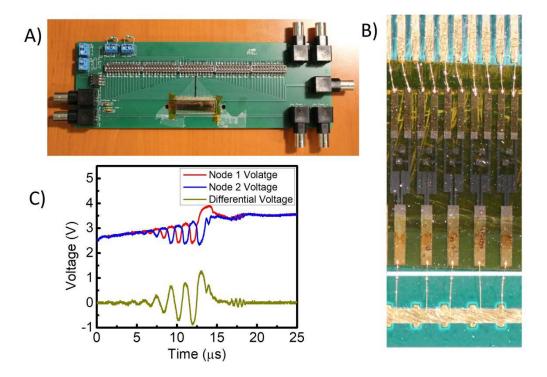

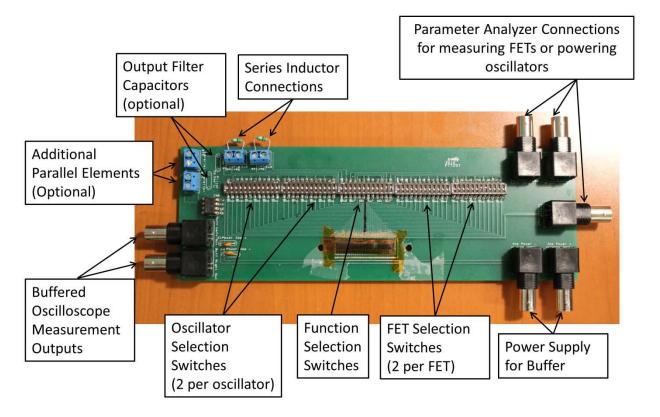

- **Figure 4-6** (A) Photograph of complete printed circuit board used for probing CdSe NC-TFT oscillators with sample mounted (lower middle) for wirebonding. (B) Photograph of complete devices wirebonded to the PCB. (C) Oscilloscope readout of measured oscillator with a 1  $\mu$ H inductor and CdSe NC TFTs with channel length L=10  $\mu$ m and channel width W=800  $\mu$ m.

#### Chapter 5: NFC Powered Flexible Electrochromic Displays

- **Figure 5-1** (A) Schematic of the electrochromic display structure. (B) Circuit diagram of NFC power harvesting circuit connected to electrochromic display.

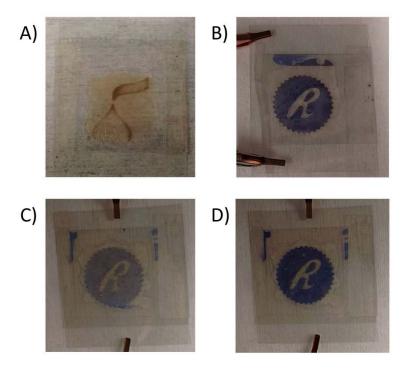

- **Figure 5-2** Photographs of electrochromic displays with (A) MVHFP dye, (B) MVHFP dye with added DMF, and (C) DHVHFP dye.

- **Figure 5-3** (A) Photograph of electrochromic display with burned-in image. (B) Photograph of thin MVHFP dye display after 5 seconds active. Photograph of thick MVHFP dye display after (C) 5 seconds and (D) 10 seconds active.

**Figure 5-4** Photograph of (A) monochromatic and (B) polychromatic electrochromic display after being activated by the NFC link. (C) Photograph of monochromatic display being bent.

#### Chapter 6: Future Directions

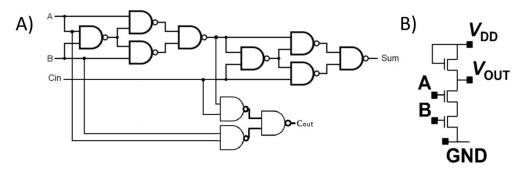

**Figure 6-1** (A) Logic diagram of a 1-bit full adder. (B) Circuit Diagram of a unipolar CdSe NAND logic gate.

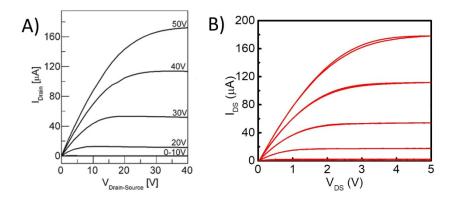

**Figure 6-2** Output characteristics (I<sub>DS</sub> vs. V<sub>DS</sub>) for a CdSe TFT fabricated on (A) silicon wafer with SiO<sub>2</sub> dielectric and (B) Kapton with Al<sub>2</sub>O<sub>3</sub> dielectric. (Figure A reproduced from Fafarman, A., *et al*, 2012)

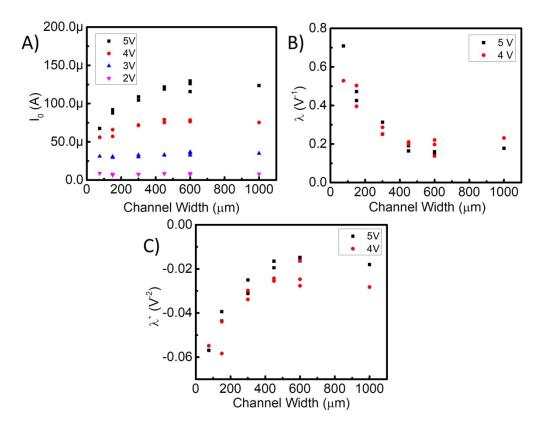

**Figure 6-3** Plots of fitting results vs. channel length for different drain voltages for second order CdSe TFT model for (A)  $I_0$  (constant term), (B) Early Voltage (linear term), and (C) second-order correction term. Each point represents a fit of measurements from a single device. 2V and 3V are excluded from parameter results due to wide variation in results.

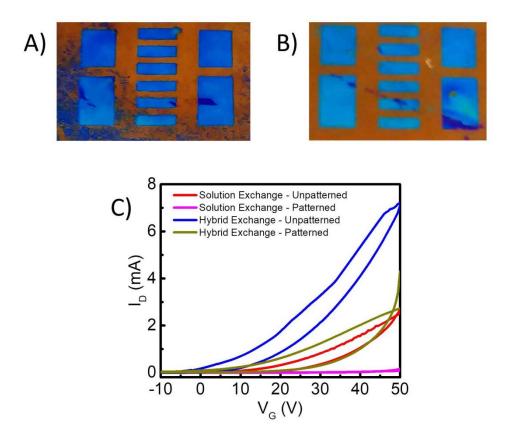

**Figure 6-4** Photograph of patterned CdSe NC thin film on silicon wafer coated with a  $SiO_2/Al_2O_3$  dielectric stack following (A) solution and (B) hybrid exchange. (C) Comparison of transfer characteristics ( $I_D$ - $V_{GS}$ ) of unpatterned and patterned samples form solution and hybrid exchanges.

#### Chapter 1: Background

#### 1-1: Colloidal Semiconductor Nanocrystals

Nanocrystals are being broadly developed for a variety of applications, including sensors, displays, thermoelectric cells, integrated circuits (IC)<sup>4,5</sup>, and solar cells<sup>6,7</sup>. Their solution processability and low cost make them a desirable material for emerging technologies looking to exploit novel deposition techniques for unconventional applications, such as flexible electronics. Their tunable optical properties make them desirable for making photodetectors with a broad range of parameters as well as solar cells competitive with cells made from more expensive fabrication methods.

A wide variety of nanocrystals can be made in large quantities with monodisperse properties using chemical synthesis techniques. Changing parameters and materials in these syntheses can adjust properties of the product including size, shape, chemical composition, and surface chemistry.<sup>8–10</sup> These parameters allow the particles to be synthesized with properties matching their desired usage. Further processing after synthesis allows these properties to be changed as well as for the introduction of surface chemistries not compatible with the synthesis process.<sup>11–13</sup>

This work focuses on the use of cadmium selenide (CdSe) nanocrystals (NCs). They are formed using a hot injection synthesis process, as described in literature.<sup>14</sup> The size and surface chemistry of these particles can be tuned to fit their application. For the work described in this dissertation, we use NCs that are approximately 4 nm in diameter and are stabilized in solution using trioctylphosphine oxide (TOPO) ligands on their

surface. Following synthesis, the TOPO ligands are replaced in a chemical exchange process by thiocyanate (SCN). As SCN is a much shorter molecule than TOPO, this allows increased interparticle coupling and greater transport of electronic carriers through films formed from this material.

#### 1-2 : Nanocrystal TFTs

In order to create a direct application of these materials, thin-film transistors (TFTs) can be formed using CdSe NC films with SCN ligands as the semiconducting layer. The simplest form of these TFTs uses a heavily doped silicon wafer coated with thermal oxide as the gate and oxide of the transistor. The semiconducting material is then deposited on this substrate and patterned metal contacts are added to create the source and drain. These types of TFTs have been demonstrated with multiple exchange procedures 15,16 with varying results.

These TFTs can also be doped using a variety of different techniques including chemical treatments<sup>17–19</sup> as well as the direct deposition of metals.<sup>15,20–22,11</sup> For this work, indium is used as a dopant as it can be easily deposited by thermal evaporation. It then diffuses into the NC film by annealing as it has very low melting point.<sup>15</sup>

Using these techniques, high performance TFTs have been demonstrated with mobilities exceeding 30 cm<sup>2</sup>/Vs.<sup>15</sup> This performance, while not competitive with crystalline semiconductors, is competitive with other low-cost, solution processable semiconductors including MoSe<sub>2</sub> (50 cm<sup>2</sup>/Vs<sup>23</sup>), carbon nanotube arrays (35 cm<sup>2</sup>/Vs<sup>24</sup>),

sol-gel metal oxides (14 cm<sup>2</sup>/Vs<sup>25</sup>) and sol-gel IZO and IGZO (30 and 20 cm<sup>2</sup>/Vs, respectively<sup>26</sup>) This performance is adequate for many low-speed applications including sensors and displays.

#### 1-3: Low-Speed Flexible Nanocrystal Integrated Circuits

Single TFT devices, while interesting, have very few direct applications. In order to transition CdSe NC-TFTs from concept to applicable technology, multi-TFT integrated circuits (ICs) have to be demonstrated. Thus, our group previously developed multi-TFT ICs which utilize shadow mask patterning allowing simple fabrication.<sup>4</sup> This technique avoids air and chemical exposure of the NC films, both of which can cause significant damage. This allows simple demonstrations to be developed using procedures not drastically different than those used for the original single-TFT demonstrations.

When creating ICs, the most important structure is called the vertical interconnect access or VIA. This structure creates a vertical connection between different layers of metal in a circuit, such as between a layer used for gating and a layer used for contact to the source and drain of the TFTs, as was needed for CdSe NC-ICs. For these simple TFTs, a method was developed to exploit the chemical instability of oxides on gold.

**Figure 1-1** (A) Schematic of shadow mask patterned CdSe NC FET on Kapton substrate. (B) Photograph of shadow mask patterned CdSe TFTs. (Reproduced from Kim, D. *et al*, 2012)

The bottom layer of the transistor structure is the gating layer, shown schematically in Figure 1-1A. Aluminum is used due to its similar work function to that of doped CdSe NCs as well as its chemical compatibility with the high-k dielectric constant material alumina, which is used as the gate dielectric layer in these TFTs. A patterned gold layer can be deposited on top of this aluminum layer, creating a vertical pillar of gold used as the VIA. Following this gold deposition, a layer of alumina is deposited by atomic layer deposition (ALD) which is a chemical vapor deposition process. For thin layers of alumina, this process creates an unstable oxide top of the gold.

This unstable layer of oxide is believed to be removed during subsequent processing steps leaving an oxide on top of the aluminum gate sections and a bare gold surface where the VIAs are deposited creating a conductive vertical pathway.

This work also utilized a flexible substrate for fabricating these TFTs. The substrate used is polyimide film, which is purchased commercially and is commonly known under the DuPont trade name Kapton, shown in Figure 1-1B. This film has a high tensile strength, chemical resistance, and melting point allowing it to be easily incorporated into procedures common to semiconductor manufacturing.

The largest drawbacks to this material during fabrication are its inherent flexibility and high coefficient of thermal expansion. To remedy this issue, a thin layer of alumina is deposited on the Kapton film prior to the deposition of any other layers. This layer is thin enough to maintain the flexibility of the substrate but strong enough to prevent the Kapton film from significantly deforming in subsequent thermal processing steps. The flexibility of the substrate is managed during processing using a carrier wafer when a stable base capable of holding the Kapton flat is not provided by the tool. This method utilizes a soft polydimethylsiloxane (PDMS) adhesive film, purchased commercially under the trade name GelPak, mounted on a silicon wafer as a temporary carrier.

The TFTs produced from this worked showed modest performance. Single transistors were demonstrated with mobilities around 20 cm<sup>2</sup>/Vs. While this does not

match the performance of single TFTs previously demonstrated this degradation was not unexpected. As the NC films are very chemically and situationally sensitive, some depletion in performance can be expected as the structure they are being incorporated within increases in complexity.

This work also demonstrated simple ICs based on the inverter structure including digital inverters, analog inverting amplifiers, and ring oscillators. As the CdSe NC transistors fabricated are solely n-type, these TFTs utilize a unipolar, saturated load design. Due to the limitations of shadow mask patterning, these TFTs were unfortunately very large. For two TFTs, as needed to demonstrate the inverter, the total pattering area was around 1 cm<sup>2</sup> (Figure 1-2A). This greatly limited their performance in the frequency domain due to large intrinsic capacitances and also makes them impractical for applications. These constraints limited the TFTs to a measured 3dB bandwidth of only 900 Hz (Figure 1-2C).

**Figure 1-2** (A) Photograph of shadow mask patterned CdSe NC TFT inverter. (B) Circuit schematic of CdSe NC inverter. (C) Bode Plot of the output of a shadow mask patterned CdSe NC TFT inverting amplifier. (Reproduced from Kim, D. *et al*, 2012)

Extending the development of the inverter, 5 stage ring oscillators were also fabricated. These TFTs were again limited by their large sizes. The measured results showed ring oscillators with 150 Hz oscillation frequencies. While the speed of these devices is limited, this work marked the first demonstrations of CdSe NC-ICs and provides much of the basic methods needed to further develop CdSe NC TFTs into faster and more complex ICs.

#### 1-4: Air Stable CdSe NC TFTs

In order to scale down the device dimensions, a procedure must be developed which allows sub-10 µm patterning and alignment of metal electrodes. One route to fabricate TFTs on these length scales is the development of photolithographic processes. However, these processes will expose the TFTs to air and solvents not present when patterning with shadow masks. Like many solution processable semiconductors, CdSe NCs must be handled inside of a nitrogen glovebox to avoid exposure to oxygen and water which can greatly degrade their performance. This air sensitivity significantly limits their potential applications as their performance is diminished in atmosphere. The desire to mitigate these limitations led to the development of methods to make CdSe NC TFTs recoverable after exposure to air and solvents as well as being stable long-term outside of an inert atmosphere.<sup>20</sup>

**Figure 1-3** (A) Schematic representation of indium-driven CdSe recovery. (B) Plot of maximum drain current after exposure to atmosphere (red) and subsequent recovery annealing (blue). (Reproduced from Choi, J. *et al*, 2013)

The use of indium as a dopant for CdSe is widely accepted in both polycrystalline and NC TFT applications. <sup>15,20–22,11</sup> Given its low meting point, indium can be easily deposited by thermal evaporation and subsequently melted by annealing to drive diffusion of the material into the semiconducting film, acting an n-type dopant. As it would turn out, the annealing process also causes the desorption of oxygen from CdSe NC films (Figure 1-3A). Oxidation is the biggest cause of degradation in performance of CdSe NC films following exposure to atmosphere. Oxygen adsorbed into a CdSe NC film acts as a carrier trap, greatly reducing the number of available carriers and the conductivity of the film. <sup>27</sup> This causes a drastic reduction in current. Annealing the CdSe

NC films in the presence of indium causes this oxygen to be desorbed and/or gettered and provides additional indium dopant to the NC surface (Figure 1-3B).<sup>20</sup>

**Figure 1-4** (A) Plot of percentage maximum drain current (I<sub>DS</sub>) loss following exposure to different solvents for CdSe NC TFTs (bar graph) on SiO<sub>2</sub> (black) and Al<sub>2</sub>O<sub>3</sub> (blue) substrates as well as a plot of the percentage recovery after annealing (dots at top). (B) Plot of mobility (black) and threshold voltage (blue) vs. time of NC TFTs stored and measured in atmosphere. (Reproduced from Choi, J. *et al*, 2013)

This concept allows recovery of the TFTs from exposure to atmosphere as well as a wide variety of solvents, as shown in Figure 1-4A. This also allowed for the creation of a procedure for encapsulation the TFTs. Conformal metals and oxides are completely impermeable to gasses. As metals are conductive, this is not an option for creating the needed impermeable barrier. Therefore, an oxide was required. Using atomic layer deposition, a thin, impermeable, conformal layer of aluminum oxide can be deposited onto the CdSe NC TFTs. As it would turn out, this layer acted not only as a barrier to exposure, but also reduced the observed hysteresis of the TFTs, making them more stable for IC applications.<sup>20</sup>

This development opens the door for developing these materials into large-area, photolithographically patterned ICs. By being able to recover the material from chemical and atmospheric exposure, we can reverse the effects of photolithographic processing techniques, almost all of which are performed in atmosphere and utilize harsh chemicals.

#### 1-5: Flexible, Photopatterned CdSe Nanocrystal Integrated Circuits

In this thesis, we demonstrate photopatterned CdSe-TFT ICs. This includes the demonstration of procedures to produce low-voltage, photopatterned ICs on Kapton substrates. It is extended by the demonstration of chemical processing procedures which improve the performance of CdSe NC-TFTs. We further the evolution of CdSe NC-ICs with the development of procedures which allow for the demonstration of high-frequency NC-TFT oscillators on Kapton substrates. We extend the development of low-power, flexible substrate electronics with the demonstration of flexible electrochromic displays which can be powered with a near field communication (NFC) receiver.

The work in Chapter 2 develops and demonstrates the procedures used for fabricating photolithographically patterned CdSe-TFT ICs on Kapton substrates. These ICs include the demonstration of TFTs with motilities of 10 cm<sup>2</sup>/Vs , high-speed inverting amplifiers with 6.7 kHz bandwidths, 5-stage ring oscillators with 65 kHz oscillating frequencies, as well as multi input logic including NAND and NOR gates. This shows the viability of fabricating CdSe NC-TFT ICs with photolithographic techniques.

Chapter 3 introduces a hybrid procedure for exchange, incorporating both a solution as well as a solid state thiocyanate ligand exchange process. This process demonstrates CdSe NC- TFTs with mobilities up to 40 cm<sup>2</sup>/Vs on silicon with shadow mask patterns and 17 cm<sup>2</sup>/Vs with photolithographic IC patterns on Kapton, besting the values previously reported for thiocyanate capped CdSe.

Chapter 4 develops methods by which CdSe NC-TFTs fabricated on Kapton substrates can be formed into simple cross-coupled oscillators and wirebonded directly on to a printed circuit board. These methods show the potential for CdSe-TFTs to be demonstrated and probed at MHz frequencies. This will not only demonstrate the full potential of CdSe-NC TFTs without being limited by transistor sizing, but may also provide insight into the movement of carriers in the NC film.

Chapter 5 furthers the development of low-power electronics on flexible electronics with a demonstration of flexible electrochromic displays which can be powered using an NFC link. These displays are demonstrated with large-area patterns activated and powered by a wireless NFC link available in most smartphones. This shows the potential for deploying small, low-power displays without the need for a battery.

#### 1-6: References

- 1. Konstantatos, G. *et al.* Ultrasensitive solution-cast quantum dot photodetectors. *Nature* **442**, 180–183 (2006).

- 2. Wood, V. *et al.* Inkjet-printed quantum dot-polymer composites for full-color AC-driven displays. *Adv. Mater.* **21**, 2151–2155 (2009).

- 3. Wang, R. Y. *et al.* Enhanced thermopower in PbSe nanocrystal quantum dot superlattices. *Nano Lett.* **8,** 2283–2288 (2008).

- 4. Kim, D. K., Lai, Y., Diroll, B. T., Murray, C. B. & Kagan, C. R. Flexible and low-voltage integrated circuits constructed from high-performance nanocrystal transistors. *Nat. Commun.* **3**, 1216 (2012).

- 5. Stinner, F. S. *et al.* Flexible, High-Speed CdSe Nanocrystal Integrated Circuits. *Nano Lett.* **15**, 7155–7160 (2015).

- 6. Ning, Z. *et al.* All-inorganic colloidal quantum dot photovoltaics employing solution-phase halide passivation. *Adv. Mater.* **24,** 6295–6299 (2012).

- 7. Zhao, T. *et al.* Advanced Architecture for Colloidal PbS Quantum Dot Solar Cells Exploiting a CdSe Quantum Dot Buffer Layer. *ACS Nano* **10**, 9267–9273 (2016).

- 8. Rogach, A. L. *et al.* Organization of matter on different size scales: Monodisperse nanocrystals and their superstructures. *Adv. Funct. Mater.* **12**, 653–664 (2002).

- 9. Ye, X. *et al.* Improved size-tunable synthesis of monodisperse gold nanorods through the use of aromatic additives. *ACS Nano* **6**, 2804–2817 (2012).

- 10. Murray, C. B., Kagan, C. R. & Bawendi, M. G. Synthesis and Characterization of Monodisperse Nanocrystals and Close-Packed Nanocrystal Assemblies. *Annu. Rev. Mater. Sci.* **30**, 545–610 (2000).

- 11. Liu, W., Lee, J. S. & Talapin, D. V. III-V nanocrystals capped with molecular metal chalcogenide ligands: High electron mobility and ambipolar photoresponse. *J. Am. Chem. Soc.* **135**, 1349–1357 (2013).

- 12. Kovalenko, M. V., Scheele, M. & Talapin, D. V. Colloidal Nanocrystals with Molecular Metal Chalcogenide Surface Ligands. *Science* (80-. ). **324**, 1417–1420 (2009).

- 13. Liu, Y. *et al.* Dependence of carrier mobility on nanocrystal size and ligand length in pbse nanocrystal solids. *Nano Lett.* **10**, 1960–1969 (2010).

- 14. Fafarman, A. T. *et al.* Thiocyanate-capped nanocrystal colloids: Vibrational reporter of surface chemistry and solution-based route to enhanced coupling in nanocrystal solids. *J. Am. Chem. Soc.* **133**, 15753–15761 (2011).

- 15. Choi, J. H. *et al.* Bandlike transport in strongly coupled and doped quantum dot solids: A route to high-performance thin-film electronics. *Nano Lett.* **12,** 2631–

- 2638 (2012).

- 16. Goodwin, E. D. *et al.* Effects of post-synthesis processing on CdSe nanocrystals and their solids: Correlation between surface chemistry and optoelectronic properties. *J. Phys. Chem. C* **118**, 27097–27105 (2014).

- 17. Sahu, A. *et al.* Electronic impurity doping in CdSe nanocrystals. *Nano Lett.* **12**, 2587–2594 (2012).

- 18. Norris, D. J., Efros, A. L. & Erwin, S. C. Doped Nanocrystals. *Science* (80-. ). **319**, 1776–1779 (2008).

- 19. Erwin, S. C. et al. Doping semiconductor nanocrystals. *Nature* **436**, 91–94 (2005).

- 20. Choi, J. H. *et al.* In situ repair of high-performance, flexible nanocrystal electronics for large-area fabrication and operation in air. *ACS Nano* **7**, 8275–8283 (2013).

- 21. Oh, S. J. *et al.* Stoichiometric control of lead chalcogenide nanocrystal solids to enhance their electronic and optoelectronic device performance. *ACS Nano* **7**, 2413–2421 (2013).

- 22. Dolzhnikov, D. S. *et al.* Composition-matched molecular 'solders' for semiconductors. *Science* (80-. ). **347**, 425–428 (2015).

- 23. Wang, X. *et al.* Chemical Vapor Deposition Growth of Crystalline Monolayer MoSe 2 SI. *ACS Nano* **8**, 5125–5131 (2014).

- 24. Sun, D. *et al.* Flexible high-performance carbon nanotube integrated circuits. *Nat. Nanotechnol.* **6,** 156–161 (2011).

- 25. Kim, Y.-H. *et al.* Flexible metal-oxide devices made by room-temperature photochemical activation of sol–gel films. *Nature* **489**, 128–132 (2012).

- 26. Street, R. A. *et al.* Sol-gel solution-deposited InGaZnO thin film transistors. *ACS Appl. Mater. Interfaces* **6,** 4428–4437 (2014).

- 27. Bube, R. H. The Basic Significance of Oxygen Chemisorption on the Photoelectronic Properties of CdS and CdSe. *J. Electrochem. Soc.* **113,** 793–798 (1966).

#### **Chapter 2 : Flexible, High-Speed CdSe Nanocrystal Integrated Circuits**

#### 2-1: Introduction

Solution and low-temperature processable semiconductors are being explored to realize low-cost, large-area, flexible electronics and to enable emerging mobile, wearable, and implantable devices. Applications including displays, <sup>1,2</sup> sensors, <sup>3</sup> integrated circuits (ICs), <sup>4–8</sup> and radio frequency identification (RFID) systems <sup>9,10</sup> have been demonstrated through the solution-based casting and printing of semiconducting organic molecules and polymers, <sup>1,2,4,9,10</sup> carbon nanotube arrays, <sup>3,5,8</sup> and sol-gel metal oxides. <sup>7</sup> Recently, colloidal nanocrystals (NCs) have emerged as a new member of this family of solution-processable semiconductors with demonstrations of high mobility (>10 cm<sup>2</sup>/Vs) electronic transistors <sup>11–16</sup> and integrated circuits. <sup>6,17</sup>

Colloidal semiconductor NCs are typically synthesized with long-chain organic ligands on the NC surface allowing 1) the controlled growth of NC samples that are monodisperse and tunable in size and shape and 2) the dispersion of NCs in non-polar organic solvents, creating inks. <sup>18–20</sup> However, these long organic ligands serve as barriers to charge transport when NCs are assembled to form thin film solids. The introduction of compact ligand chemistries and processes to exchange these long ligands greatly enhances the electronic coupling between NCs in solids. <sup>15,21,22</sup> The combination of strong coupling through ligand exchange and of recently reported synthetic <sup>23–25</sup> and post-synthetic <sup>11–15</sup> methods to dope NC thin films are responsible for the dramatic increase of carrier mobility in colloidal NC-based thin films. Previously, our group exploited these

high mobility NC thin films in field-effect transistors to demonstrate solution-processable and flexible, low-voltage analog and digital integrated circuits (ICs).<sup>6</sup> However, in this first demonstration of nanocrystal integrated circuits (NCICs), the transistor wiring was defined by shadow masks which created large transistor sizes and electrode overlap and therefore introduced large parasitic capacitances that limited the bandwidth to ~900 Hz and switching speed to 600 µs for low-voltage analog and digital circuits, respectively.

In this chapter, we exploit methods we introduced for in-situ device repair that allows us to take these semiconducting NC materials, which are typically highly sensitive to their environment, out of the nitrogen glovebox and into the cleanroom, where they are exposed to the air and to the solvents commonly used in fabrication processes. 11 Here we use photolithography to pattern device electrodes enabling us to scale down device dimensions, drastically reducing parasitic capacitances from electrode overlap, and scale up fabrication across large 4 inch flexible Kapton substrates. We demonstrate NC fieldeffect transistors (NC-FETs) with channel lengths ranging from 5-40 µm and electron mobilities up to 10 cm<sup>2</sup>/Vs. We integrate these NC-FETs using a newly developed process to fabricate vertical interconnect access (VIA) holes, which allows us to realize complex integrated circuits. These circuits include the fundamental building blocks for analog and digital circuits such as inverters and NAND and NOR gates. Taking advantage of reduced parasitic capacitances, we use these building blocks to realize amplifiers with  $\sim$ 7 kHz bandwidth and ring oscillators with a 7.7  $\mu$ s delay per stage at a 2 V supply voltage. The delay per stage decreases with increasing supply voltage, reaching  $1.5 \mu s$  at a 5 V supply voltage. To the best of our knowledge, these NCIC ring oscillators are the fastest solution-processable, semiconductor-based ring oscillators fabricated on a flexible substrate and operating at low voltages.

#### 2-2: Methods

We use contact photolithographic techniques to pattern the gate, VIA holes and source/drain layers to realize flexible, wafer-scale CdSe NCICs. First, a 4 inch diameter, 50  $\mu$ m thick, Kapton film is encapsulated in a 20 nm layer of alumina (Al<sub>2</sub>O<sub>3</sub>) grown by atomic layer deposition (ALD). This process preshrinks the Kapton and prevents the deformation of the plastic during following thermal processing steps, which can otherwise cause the delamination of subsequently deposited layers. Next, a photolithographically-defined and thermal (Al) and e-beam (Ti, Au) evaporated metal stack of Ti/Au/Ti/Al is fabricated to form gate electrodes. Aluminum, rather than gold, is required as the top layer of this stack in order to grow a stable, conformal oxide on top of the gate electrodes. The gate electrodes are oxidized by an oxygen reactive ion etching (RIE) process in order to promote further oxide growth. A 20 nm, high-k, Al<sub>2</sub>O<sub>3</sub> layer is then grown by ALD on top of the RIE-oxidized gate electrodes to form a high quality, high unit capacitance (220 nF/cm<sup>2</sup>) gate dielectric layer. Holes in the insulating Al<sub>2</sub>O<sub>3</sub> layer are defined by photolithography and created by a chlorine RIE process. Chlorine etching of the Al<sub>2</sub>O<sub>3</sub> layer is very aggressive and not only etches the Al<sub>2</sub>O<sub>3</sub> dielectric layer, but also etches the underlying aluminum.<sup>26</sup> The gold layer in the stack is introduced to provide a robust etch stop and to maintain conductivity between the gate

layer and the subsequently deposited VIA. The VIA holes are filled by e-beam evaporation of gold. The VIA is essential as it creates vertical connections between different metal electrode layers through the insulating  $Al_2O_3$  layer, required to develop complex, IC topologies. To test VIA conductivity, we measure a test structure composed of many VIAs of identical size. The VIAs show Ohmic contact to the gate layer with a resistance of  $60 \pm 15~\Omega$  for each VIA hole [Appendix 2-2]. This robust VIA process may be generally useful for devices fabricated from different solution-processable semiconductors as it desirably allows the use of  $Al_2O_3$  as a gate dielectric layer for low-voltage, low-hysteresis flexible devices.

To fabricate the CdSe NC active layer, 4 nm CdSe NCs are prepared, following literature procedures.<sup>27</sup> The long-chain organic ligands introduced during synthesis are exchanged in solution with the compact ligand thiocyanate (SCN). These SCN-exchanged CdSe NCs are dispersed in dimethylformamide (DMF) at a concentration of 19.6 mg/mL, as estimated from the optical density at the first excitonic peak,<sup>28</sup> and deposited by spincoating to form 40 nm thin film, CdSe NC semiconducting channel layers, as previously reported.<sup>14</sup> Following spincasting, the CdSe NC thin films are annealed at 200 °C for 10 minutes to promote their adhesion to the substrate. To further prevent NC thin film delamination during processing, an ultrathin, 1 nm ALD Al<sub>2</sub>O<sub>3</sub> layer is deposited. Source and drain electrodes composed of a metal stack of indium and gold are defined by photolithography and deposited by thermal evaporation to complete bottom-gate, top-contact NC-FETs and NCICs. The devices are annealed at 300 °C for 30

min in order to drive indium diffusion from the source and drain electrodes through the 40 nm thickness of the CdSe NC thin film, heavily doping the contact region, and into and across the 5-40  $\mu$ m long CdSe NC thin film active area, lightly doping the channel [Appendix 2-6]. In order to better control doping at the contacts and in the channel and realize high mobility and current modulation in devices as we scale down the channel length in comparison to our previous work, we deposit an additional 5 Å layer of indium by thermal evaporation across the entire NC film and then anneal the devices at 300 °C for 10 min, an approach used previously to dope poly-crystalline CdSe transistors.<sup>29</sup> Next, devices are encapsulated in an additional 50 nm ALD Al<sub>2</sub>O<sub>3</sub> layer to passivate the CdSe NC thin film surface and reduce device hysteresis.<sup>11</sup> Finally, the devices are annealed at 300 °C for 10 min to complete the doping of the channel from the added indium as well as to repair the CdSe NC thin film after oxygen and solvent exposure during photolithographic patterning and ALD encapsulation. Detailed methods are discussed in Appendix 2-1.

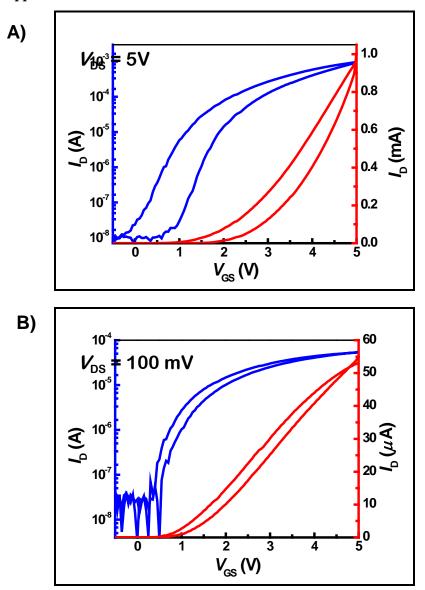

**Figure 2-1** (A) Schematic of a CdSe NC-FET and a VIA used as building blocks to construct NCICs. (B) Photograph of an array of CdSe NCICs fabricated on a 4 inch, flexible, Kapton substrate. (C) Output  $I_D$ - $V_{DS}$  and (D) transfer  $I_D$ - $V_{GS}$  characteristics of a flexible CdSe NC-FET with photolithographically-patterned electrodes defining a channel length L= 10  $\mu$ m and width W= 1000  $\mu$ m.

Figure 2-1A details a schematic of a completed CdSe NC FET and a VIA defined to realize NCICs. We successfully fabricate many individual transistors, inverters,

voltage amplifiers, NOR and NAND gates and ring oscillators on a single 4 inch, wafersized, flexible Kapton substrate [Figure 2-1B]. Figure 2-1C, D shows representative NC-FET device output  $(I_D-V_{DS})$  and transfer  $(I_D-V_{GS})$  characteristics used as the building blocks to construct the NCICs. The NC-FETs show well-behaved, n-type characteristics at low operating voltages, seen by the linear increase and then saturation of the drain current  $(I_D)$  with increasing drain bias  $(V_{DS})$  and the increase in drain current  $(I_D)$  with increasing gate bias  $(V_{GS})$ , as electrons are accumulated at low fields in the channel across the high unit capacitance, Al<sub>2</sub>O<sub>3</sub> gate dielectric layer. Averaged over 30 measured NC-FETs with channel lengths ranging from 5 to 40  $\mu$ m, in the saturation regime [Figure 2-1D] the electron field-effect mobility ( $\mu_e$ ) is 10.1  $\pm$  0.28 cm<sup>2</sup>/Vs with a threshold voltage  $(V_T)$  of 1.07  $\pm$  0.03 V and a low hysteresis  $(\Delta V_T)$  of 0.22  $\pm$  0.02 V. In the linear regime [Appendix 2-6]  $\mu_e$  is 6.2  $\pm$  0.15 cm<sup>2</sup>/Vs with a  $V_T$  of 0.84  $\pm$  0.073 V and a  $\Delta V_T$  of  $0.32 \pm 0.02$  V. The drain current on/off ratio is greater than  $10^4$ , with an average subthreshold swing of 350  $\pm$  9 mV per decade. The calculated semiconductor-dielectric interface trap density is  $7.14 \pm 0.05 \times 10^{12} \text{ cm}^{-2}$ , similar to our previous reports on highperformance CdSe NC-FETs.<sup>6,14</sup> The metal-semiconductor contact resistance is probed using the transmission line method [Appendix 2-7] and is consistent with the formation of low-resistance, Ohmic contacts. 30

**Figure 2-2** (A) Schematic of the load transistor used to construct the NCIC inverter. (B) Circuit diagram and (C) photograph of a flexible, CdSe NCIC inverter. The output voltage  $(V_{\text{OUT}})$  is measured as a function of the input voltage  $(V_{\text{IN}})$  for different supply voltages  $(V_{\text{DD}})$  applied with respect to ground (GND). (D) Voltage transfer characteristics  $(V_{\text{OUT}}-V_{\text{IN}})$ , (E) voltage gain, (F) noise margin (orange squares), and (G) drain current for a CdSe NCIC inverter as a function of the supply voltage  $V_{\text{DD}}$ . (H)

Output waveform (red) of a NCIC voltage amplifier in response to a 1 kHz, 200 mV sinusoidal input on a 600 mV DC input bias (blue). (I) Frequency response (Bode Plot) of a NCIC voltage amplifier (black circles). A linear fit (red dashed line, top) shows a 8.3 dB voltage gain at low frequency, which is used to find the 3 dB bandwidth (red dashed line, bottom).

Since our NC-FETs are n-type and have a positive  $V_T$ , we implement an enhancement-load design to form NCIC inverters. This topology uses two NC-FETs operating in unison where one FET serves as the driver and the other as the load [Figure 2-2B]. The load, shown schematically in Figure 2-2A, is built by connecting the drain and gate of the NC-FET through a VIA and operates as a two terminal, linear resistor. Figure 2-2C shows a photograph of a fabricated NCIC enhancement-load inverter.

Figure 2-2D-G show the inverter voltage transfer characteristics (VTCs), voltage gain, noise margin, and drain current for different supply voltages ( $V_{\rm DD}$ ). The circuit shows the expected VTCs, inverting a low voltage input ( $V_{\rm IN}$ ) to yield a high voltage output ( $V_{\rm OUT}$ ) and *vice versa* [Figure 2-2D]. The voltage swing in the VTCs for all supply voltages remains constant at 78 +/- 1 % of  $V_{\rm DD}$ . This is in agreement with the ideal  $V_{\rm DD}$ - $V_{\rm T}$  voltage swing for an enhancement-load inverter as  $V_{\rm T}$  depends on the applied voltage, consistent with a gate bias dependent mobility common to amorphous semiconductor transistors.  $^{31,32}$

The voltage gain, defined as the slope of the VTCs, shows a maximum gain of - 2.1 V/V for all input voltages and a wide region where the output voltage gain is greater than unity. For an enhancement-load inverter, the theoretical maximum gain is defined

as Gain =  $\frac{g_{m_{Driver}}}{g_{m_{Load}} + g_{ds_{load}} + g_{ds_{driver}}}$ . For an ideal device, the values of drain-to-source conductance  $(g_{ds})$  for the driver and load are several orders of magnitude smaller than the transconductance  $(g_m)$  of the load which for this device  $g_m$  is 14.4  $\mu$ S. However,  $g_{ds}$  is 1.7  $\mu$ S, as seen by the residual slope in the saturation regime of the NC-FET output curves [Figure 2-1C], and is too large to be neglected. This effectively reduces the gain, yielding a calculated gain of 2.18 in strong agreement with our measured value [Appendix 2-3].

The noise margin is the measure of the ability of one device to switch another, thus allowing multi-stage digital circuit operation. It is determined by calculating the difference between the output voltage swing when the gain is greater than unity and the input voltage swing over the same range.<sup>33</sup> It can be shown visually by overlaying the inverter VTCs and its inverse at each  $V_{\rm DD}$ , as highlighted by the orange rectangles in Figure 2-2F. The noise margin increases from 450 mV at  $V_{\rm DD} = 2$  V to 1130 mV at  $V_{\rm DD} = 5$  V [Appendix 2-5].

The NCIC inverter gain opens the door for use of these devices in analog circuit applications, such as voltage amplifiers. As an example, we drive an inverter with a  $V_{\rm DD}$  = 2 V and a  $V_{\rm IN}$  composed of a 200 mV, 1 kHz peak-to-peak sinusoidal input superimposed on a 600 mV DC offset [Figure 2-2H]. The DC offset is chosen to operate the inverter at its point of maximum gain, as shown in Figure 2-2E. The output waveform is amplified with a gain of approximately -2V/V and is offset at 780 mV, consistent with the inverter VTCs, and it shows a 180 degree phase shift, originating from

the negative gain of the inverter. The frequency response of the voltage amplifier is measured by taking a series of these measurements at varying frequency and recording the amplitude of the input and output signals to find the voltage gain in decibels (dB). The results of these measurements are summarized in a Bode Plot in Figure 2-2I. The bandwidth, defined as the point where the gain has been reduced by 3 dB from that at low frequency, is estimated from the plot to be 6.8 kHz. Amplification remains above unity, or 0 dB, for frequencies of up to 10 kHz. Approximating the resistances and capacitances in the inverter as a single time constant network, we calculate a theoretical bandwidth of 9.8 kHz, in strong agreement with the measured result [Appendix 2-4]. This measured 3 dB bandwidth is almost 8 times larger than our previous voltage amplifiers and is primarily attributed to the smaller device features sizes realized here, which greatly reduce the parasitic capacitances from the gate to source/drain overlap from 277 pF [Ref. 6] to 36 pF.

**Figure 2-3** Circuit diagrams, photographs, and truth tables of flexible, CdSe NCIC (A, B, C) NAND and (D, E, F) NOR logic gates. (G) Waveforms for input voltages ( $V_{\rm IN}$ ) on the A (red) and B (blue) driver NC-FETs, which are switched at 100 Hz and 200 Hz,

respectively. (H) Output waveforms ( $V_{\rm OUT}$ ) for NCIC NAND (purple) and NOR (green) logic gates with  $V_{\rm DD}=2$  V.

Figure 2-3 shows circuit diagrams, photographs, and truth tables for flexible CdSe NCIC NAND and NOR logic gates. The logic gates are each constructed from three NC-FETs. The NAND gate uses two driver NC-FETs connected in series [Figure 2-3A]. Both NC-FETs must be on (state "1") to switch the output off (state "0"), as described by the truth table in Figure 2-3C. The NOR gate uses two driver NC-FETs in parallel [Figure 2-3D] allowing either to be switched on (state "1") to switch the output off (state "0"), as shown in the truth table Figure 2-3F. In order to test the function of these gates, we simulate the input conditions by connecting the gates of the A and B driver NC-FETs to two function generators. The function generators are setup to produce 0 to 2 V square wave voltages, switching at 100 Hz for the A NC-FET and at 200 Hz for the B NC-FET as shown in Figure 2-3G. The output waveform of each logic gate is captured on an oscilloscope and is shown in Figure 2-3H. The results are consistent with the NAND and NOR truth tables, where an output from each device close to 0 V corresponds to a "0" and an output of >1 V corresponds to a "1". The two distinct potentials at the "0" state output from the NOR gate correspond to a higher drain current achieved when both driver transistors are active. If only one driver transistor is turned on, the device current is halved, giving rise to slightly higher "0". This difference, however, is only ~50 mV which is a negligible difference for digital circuit applications as it is well below the

noise margin. The demonstration of robust NCIC NAND and NOR gates shows promise for applications in complex digital circuitry.

**Figure 2-4** (A) Circuit diagram, (B) photograph, and output characteristics at (C) 2 V and (D) 5 V supply voltages ( $V_{\rm DD}$ ) for a five-stage CdSe NCIC ring oscillator with a sixth stage buffer. (E) Delay per stage *versus* supply voltage ( $V_{\rm DD}$ ) for a CdSe NCIC ring oscillator. (F) Comparison of the delay per stage *versus* supply voltage ( $V_{\rm DD}$ ) for solution-processable, semiconducting (green) organic, (blue) carbon nanotube array, (red) sol-gel metal oxide, and (black) colloidal nanocrystal channel layers. Circuits are

fabricated on (filled symbols) rigid substrates and (open symbols) flexible substrates. The flexible, CdSe NCICs reported here are highlighted as yellow-filled, black stars.

To further probe the switching speed of our NCICs and highlight the larger scale device uniformity, 5-stage ring oscillators are fabricated [Figure 2-4A]. A 6th stage is used as a buffer to isolate the output probe from the ring oscillators. Figure 2-4B is a photograph of a 5-stage ring oscillator built from the NCIC inverters shown in Figure 2-2. The output waveforms under  $V_{\rm DD}=2$  V and 5 V are shown in Figure 2-4C,D. At  $V_{\rm DD}=2$  V, there is a 400 mV output swing oscillating at 13 kHz, equal to a 7.7  $\mu$ s delay per stage ( $\tau$ ) calculated from  $\tau=\frac{1}{2\times N\times f}$ , where N is the number of stages and f is the oscillation frequency. This delay per stage is two orders of magnitude smaller than the first NCIC based ring oscillator ( $\tau=600~\mu$ s), demonstrated at a 2 V  $V_{\rm DD}$ . At  $V_{\rm DD}=5$ V, there is a 1.2 V output swing oscillating at ~65 kHz, yielding a 1.5  $\mu$ s delay per stage. Figure 2-4E shows the relationship between stage delay and  $V_{\rm DD}$  between 2 V and 5 V. Faster switching speed is seen at higher  $V_{\rm DD}$  as more current [see Figure 2-2G] passes through the devices allowing them to more quickly charge and discharge the capacitive loads.

Figure 2-4F compares the supply voltage dependent switching speed from ring oscillators constructed using our solution-deposited colloidal NCICs<sup>6</sup> and solution-processable organic semiconductors,<sup>34–40</sup> carbon nanotube arrays,<sup>5,41,42</sup> and sol-gel metaloxides.<sup>7</sup> The primary challenge in creating a ring oscillator for all of these materials is

integrating them into IC fabrication processes. The secondary challenge is realizing devices which operate at less than 5 V, crucial for applications in portable electronics and sensors powered by batteries or inductive charging. In many other solution-processable materials, surface defects, high contact resistances, thick oxides, and large channel lengths limit their applications to higher operating voltages. The switching speed of our NCICs [Figure 2-4F (yellow-filled, black stars)] outperforms other solution-processable materials on flexible substrates at low voltages. As we have also developed processes to make NCICs compatible with conventional photolithography, NCICs can be adapted to currently available large-area fabrication equipment and techniques, boosting its development toward lost-cost, large-area electronics.

## 2-4: Conclusions

In summary, we use photolithography to scale down device dimensions and reduce parasitic capacitance and scale up device fabrication to demonstrate large-area and flexible, solution-processable CdSe NCICs that operate at high bandwidth and high-speed for analog and digital electronics. We demonstrate the first NCIC NOR and NAND logic gates and report voltage amplifiers with a 6.8 kHz bandwidth at 2 V and ring oscillators with a 1.5  $\mu$ s switching speed at 5 V. The higher bandwidth and higher speed of NCICs shows the promise of colloidal NCs as a materials class for large-area, flexible, high-speed circuits.

## Appendix 2-1: Detailed Methods

CdSe NC Synthesis, Ligand Exchange, and Deposition

4 nm CdSe NCs capped with trioctylphosphine oxide (TOPO) are synthesized using a modified version of methods found in Ref. 27. The selenium precursor for NC synthesis is created by combining 100 mL 97% tributylphosphine (Aldrich) and 9.9 g 99.99% selenium shot (Strem) under nitrogen and stirring them overnight to form tributylphosphine selenide. The cadmium precursor for NC synthesis, cadmium stearate, is created by combining 55 g 97% stearic acid (Acros), 10 g 99% CdO (Strem), and 50 mL 90% octadecene (Aldrich) and heating it under nitrogen to 280 °C. The solution is held at temperature until bubbling ceases. The reaction is allowed to cool, and then the mixture is precipitated with acetone, vortexed at high speed until sufficiently mixed to a uniform color, and centrifuged at the highest speed available in order to recover as much precursor as possible. The supernatant is discarded. The acetone precipitation, vortexing, and centrifuging process is repeated, and the supernatant is again discarded. The precipitant is then dried in a vacuum oven at 50 °C. Once dry, the cadmium stearate is pulverized in a mortar and pestle. The washing, vortexing, precipitation, drying, and pulverization procedure is repeated twice with methanol and then twice with acetone in order to insure the precursor is sufficiently clean.

CdSe NCs are synthesized by mixing 40 g of 90% TOPO (Aldrich), 40g of 90% octadecylamine (Acros), and 4.2 g of cadmium stearate (prepared as described above). The solution is heated to 135 °C and degassed under vacuum. The mixture is then heated under nitrogen to 320 °C. 20 mL of tributylphosphine selenide is then quickly injected to nucleate the NCs. Growth is continued at 290 °C for 15 min. The reaction is stopped by adding 50 mL of anhydrous toluene. The solution is transferred into a nitrogen glovebox. Anhydrous methanol is added to the solution until precipitation of the particles is observed. The mixture is then centrifuged at the highest speed available in order to recover as many NCs as possible. The supernatant is discarded. 16 mL of anhydrous hexanes are used to redisperse the precipitant. The resulting solution is then centrifuged and the supernatant is retained. The NCs are then redispersed in 16 mL anhydrous hexanes. Anhydrous ethanol is then added until precipitation of particles is observed. This mixture is vortexed until the mixture is a uniform color, and then centrifuged at the highest speed available and the supernatant is discarded. The process of redispersion in 16 mL of hexane, adding anti-solvent until precipitation is observed, vortexing,

centrifuging, and discarding the supernatant is repeated with anhydrous acetone and anhydrous isopropanol. The final precipitant is then dispersed in 16 mL of anhydrous hexane for storage until use.

Ligand exchange with ammonium thiocyanate (NH<sub>4</sub>SCN) is performed in an inert environment using the recipe found in Ref. 14, scaled proportionately to create a 450  $\mu$ L dispersion of SCN-capped CdSe NCs in dimethylformamide (DMF) at an optical density (OD) of 40. This is performed by starting with 2.4 mL of TOPO-capped, CdSe NCs at an OD of 20 and combining it in a centrifuge tube with 3.6 mL of hexane and 3.2 mL of NH<sub>4</sub>SCN in acetone at a concentration of 10 mg/mL. This mixture is vortexed at 3000 rpm for 2 min, centrifuged at 2000g for 1 min, and then the supernatant is discarded. 4.8 mL of tetrahydrofuran is added to the precipitated NCs and this mixture is vortexed at 3000 rpm for 2 min, centrifuged at 2000g for 1 min, and the supernatant is discarded. 4.8 mL of toluene is then added to the precipitated NCs and this mixture is vortexed for 1 min at 3000 rpm, centrifuged at 2000g for 1 min, and the supernatant is discarded. The precipitated NCs are then dispersed into 400  $\mu$ L of DMF.

Thin films are deposited in an inert atmosphere by passing the resulting NC dispersion through a 1 inch diameter,  $0.2 \ \mu m$  pore polytetrafluorethylene filter onto the substrate, then spinning the sample at 500 rpm for 15 s, ramping to 800 rpm over 15 s, and then holding at 800 rpm for an additional 30 sec.

### Device Fabrication

CdSe NCICs are fabricated on 50  $\mu$ m DuPont Kapton substrates. These substrates are encapsulated by 20 nm of Al<sub>2</sub>O<sub>3</sub> deposited at 280°C in a Cambridge Nanotech Savannah 200 ALD system using trimethylaluminium and water precursors. Photolithographic patterns are defined in a bilayer of photoresists, MicroChem LOR3A and MicroChem S1813, deposited by spincoating at 3000 rpm for 45 s and 4000 rpm for 25 s, respectively, then baked at 180 °C for 105 s and 115 °C for 60 s, respectively. For the VIA and source/drain layer only S1813 is used. Patterns are exposed by contact photolithography using a Nanonex NX2600 system for a time of 6.3 s at 14.3 mW/cm<sup>2</sup>. Exposed patterns are developed in Microposit MF-CD-26 for 60 s. Metal layers are deposited in a Kurt Lesker PVD75 system by thermal (Al) and e-beam (Ti, Au) methods at a deposition rate of 0.5 Å/s. For the gate metal, a stack of 2 nm Ti, 20 nm Au, 2 nm Ti, and 40 nm Al is used. MicroChem Remover PG heated to 70 °C in an ultrasonic bath is used for lift-off. The gate layer is oxidized by an Oxford 80 Plus RIE system with a 150 sccm flow of O<sub>2</sub> for 10 min at an RF power of 150 W. The gate dielectric layer is 20 nm

of Al<sub>2</sub>O<sub>3</sub>, deposited by the same ALD method described above. VIAs are defined by photolithographic methods (as above) and etched using a Trion Phantom III RIE/ICP system with a 50 sccm flow of BCl<sub>3</sub> gas for 35 s at an RF power of 300 W. VIAs are refilled using a stack of 2 nm Ti and 80 nm Au. CdSe NCs are exchanged as previously described and then deposited using a Specialty Coating Systems G3P spincoater installed inside of a nitrogen glovebox. The sample is heated on a Torrey Pines HP40 hotplate in an inert environment for 10 min at 200 °C to promote CdSe NC thin film adhesion. 1 nm Al<sub>2</sub>O<sub>3</sub> is deposited by ALD at 150° C to protect the CdSe NC layer. The source/drain layer is defined by photolithography and consists of a stack of 40 nm In/50 nm Au, deposited at 0.5 Å/s in a custom Angstrom Engineering thermal evaporator installed inside a nitrogen glovebox. Following liftoff of the source/drain layer, the sample is heated at 300 °C in an inert atmosphere for 30 min. 5 Å of In is deposited at 0.05 Å/s by thermal evaporation in an inert atmosphere to further control the channel doping. To complete the channel doping, the sample is annealed at 300 °C for 10 min in an inert atmosphere. A 50 nm Al<sub>2</sub>O<sub>3</sub> encapsulation layer is deposited by ALD at 150 °C. To complete recovery from air exposure for encapsulation, the sample is annealed at 300 °C for 10 min in an inert atmosphere.

### NCIC Measurement

Devices are probed with a Suss MicroTec PM5 probe system enclosed in a nitrogen glovebox. Current and VTC measurements are performed using an Agilent 4156C semiconductor parameter analyzer. AC inverter measurements, NAND and NOR measurements, as well as ring oscillator output characteristics are collected using a Tektronix TDS 2014B oscilloscope buffered by a TI TL074CN operational amplifier chip setup on a custom printed circuit board as a unity gain buffer. Inputs for these measurements are provided by HP 33120A function generators. Unit capacitance is measured by an HP 4192A impedance analyzer.

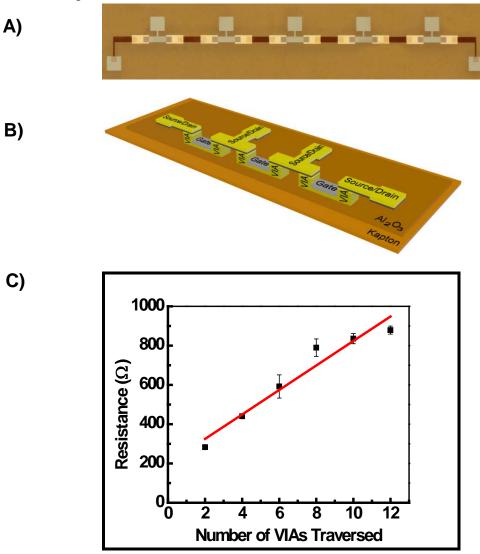

# Appendix 2-2: VIA resistance

The VIA resistance is probed by applying 1 V across an even number of VIAs of equal size connected in a serpentine structure and measuring the current. Figure A2A shows a photograph of a 10 VIA structure and Figure A2B a schematic of a 6 VIA structure. The resistance is calculated using Ohm's Law and is shown as a function of increasing number of VIAs in Figure A2C. The resulting fit line gives us a resistance of 60  $\Omega$  per VIA and a probe contact resistance of 200  $\Omega$ .

**Figure A2-2** (A) Photograph of 10 fabricated VIAs and (B) schematic showing only 6 VIAs in the serpentine structure used to probe VIA resistance. (C) Plot of resistance versus number of VIAs traversed.

# Appendix 2-3 : Inverter Gain

The gain for an enhancement load inverter is defined as: Gain  $=\frac{g_{\rm m_{Driver}}}{g_{\rm m_{Load}}+g_{\rm ds_{load}}+g_{\rm ds_{driver}}}$

The parameters are defined and calculated in Appendix 2-4.

$$g_{\mathrm{m_{load}}} = 14.4~\mu\mathrm{S}$$

$$g_{\mathrm{m_{driver}}} = 35.2 \, \mu\mathrm{S}$$

$$g_{\mathrm{ds}_{\mathrm{driver}}} = 1.7~\mu\mathrm{S}$$

$$g_{\mathrm{ds_{load}}} \sim 10^{\text{--}2} \; \mu \mathrm{S}$$

Using these parameters, we see a result of: Gain =  $2.18 \frac{\text{V}}{\text{V}}$

# Appendix 2-4: Single-time Constant Network Analysis of Amplifier Bandwidth

In order to determine the theoretical bandwidth, we used the approximation of a single time constant network. This defines the bandwidth as  $f_{3dB} = \frac{1}{2\pi * \tau}$ , where  $\tau = R_{tot} * C_{tot}$ . The total resistance ( $R_{tot}$ ) can be approximated in this structure as the inverse of the sum of the conductance of the driver and load transistors ( $g_{ds}$ ) and the transconductance ( $g_m$ ) of the load transistor. The total capacitance at the node is the sum of the gate-to-source overlap capacitance of the load, the decoupled Miller drain-to-source overlap capacitance of the driver, and the cables used to connect the amplifier to the buffer and isolate the measurement from the large load capacitance of the oscilloscope. The capacitance of the cables is approximated from the capacitance per unit length of an RG-58 BNC cable (93 pF/m) and the length of two 4 ft. sections of cable required for electrical connection. We also used mobility and threshold voltage for the measured devices, which is 8 cm²/Vs and 0.4 V, respectively. We used the same biasing conditions as described in the paper of 600 mV and 780 mV DC input and output bias, respectively.

$$C_{\rm ds_{driver}} = 22 \, \rm pF$$

$$C_{\text{gs}_{\text{load}}} = C_{\text{Overlap}} + C_{\text{channel}} = 3.7 \text{ pF}$$

$$Gain = 2.1$$

$$C_{\text{miller}_{\text{driver}}} = C_{\text{ds}_{\text{driver}}} \left( 1 + \frac{1}{\text{Gain}} \right) = 32.5 \text{ pF}$$

$$C_{\text{node}} = C_{\text{gs}_{\text{load}}} + C_{\text{miller}_{\text{driver}}} = 36.2 \text{ pF}$$

$$C_{\text{cables}} = L_{\text{cable}} * C/L_{\text{RG58}} = 223.2 \text{ pF}$$

$$C_{\text{tot}} = C_{\text{node}} + C_{\text{cables}} = 259.4 \text{ pF}$$

$$g_{\rm m_{load}} = \mu \, C_{\rm ox} \frac{W}{L} \big( V_{\rm gs} - V_{\rm t} \big) \, = 14.4 \; \mu \rm S \label{eq:gmload}$$

$g_{\mathrm{ds}_{\mathrm{driver}}} = 1.7~\mu\mathrm{S}$  (Calculated from slope of the  $V_{\mathrm{ds}}$  curves)

$$g_{\rm ds_{load}} \sim 10^{-2} \ \mu \rm S$$

$$R_{\text{tot}} = \frac{1}{g_{\text{mload}} + g_{\text{ds}_{\text{driver}}} + g_{\text{ds}_{\text{load}}}} = 62.1 \text{ k}\Omega$$

$$f_{3\text{dB}} = \frac{1}{2\pi R_{\text{tot}} C_{\text{tot}}} = 9.8 \text{ kHz}$$

If we perform this calculation after eliminating the cable capacitance, we see:

$$f_{3\mathrm{dB}_{\mathrm{proj}}} = \frac{1}{2\pi R_{\mathrm{tot}} C_{\mathrm{node}}} = 70.1 \mathrm{\ kHz}$$

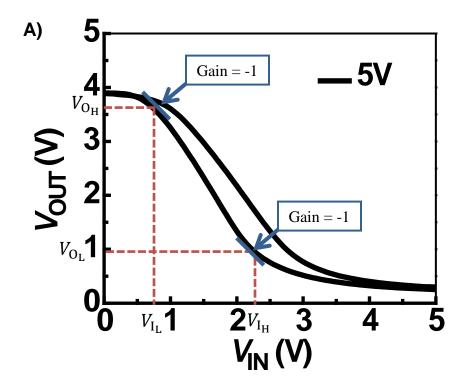

# Appendix 2-5: Noise Margin

The noise margin of an inverter is defined by the difference between the output voltage range and the input voltage range when the gain is greater than 1.

Noise Margin =

$$\left(V_{\mathrm{O_{H}}} - V_{\mathrm{O_{L}}}\right) - \left(V_{\mathrm{I_{H}}} - V_{\mathrm{I_{L}}}\right)$$

This is illustrated for a CdSe NC inverter with a 5 V supply voltage in Figure A2-5A.

| B) | Noise Margin |         |

|----|--------------|---------|

|    | 2 V          | 450 mV  |

|    | 3 V          | 740 mV  |

|    | 4 V          | 950 mV  |

|    | 5 V          | 1130 mV |

**Figure A2-5** (A) Illustration of the noise margin calculation from VTCs collected with a 5V  $V_{\rm DD}$ . (B) Table of noise margin values.

**Figure A2-6** (A) Transfer ( $I_D$ - $V_{GS}$ ) characteristics of a flexible CdSe NC-FET prior to channel doping. The device has an electron field-effect mobility ( $\mu_e$ ) of 8.6 cm<sup>2</sup>/Vs with a threshold voltage ( $V_T$ ) of 1.9 V. (B) 3 Transfer ( $I_D$ - $V_{GS}$ ) characteristics of a flexible CdSe NC-FET in the linear regime.

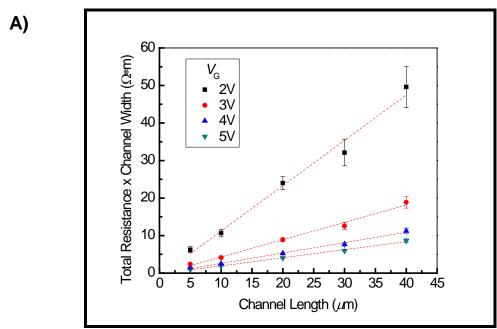

Appendix 2-7 : Contact Resistance

B)

| Gate Voltage | Channel Resistance ( $\Omega^*m/\mu m$ ) | Contact Resistance (Ω*m) |

|--------------|------------------------------------------|--------------------------|

|              |                                          |                          |

| 2 V          | 1.20764                                  | -0.84074                 |

|              |                                          |                          |

| 3 V          | 0.46184                                  | -0.33599                 |

|              |                                          |                          |

| 4 V          | 0.27629                                  | -0.17863                 |

|              |                                          |                          |

| 5 V          | 0.21618                                  | -0.24037                 |

|              |                                          |                          |

| <b>C</b> \   |                        |                                                                                  |  |

|--------------|------------------------|----------------------------------------------------------------------------------|--|

| Gate Voltage | Channel Resistance (Ω) | Contact Resistance ( $\Omega$ )                                                  |  |

| 2 V          | 80.5 x 10 <sup>3</sup> | $-2.8 \times 10^3$                                                               |  |

| 3 V          | $30.8 \times 10^3$     | $-1.1 \times 10^3$                                                               |  |

| 4 V          | $18.4 \times 10^3$     | -0.59 x 10 <sup>3</sup>                                                          |  |

| 5 V          | $14.4 \times 10^3$     | -0.80 x 10 <sup>3</sup>                                                          |  |

|              | 2 V 3 V 4 V            | 2 V 80.5 x 10 <sup>3</sup> 3 V 30.8 x 10 <sup>3</sup> 4 V 18.4 x 10 <sup>3</sup> |  |

**Figure A2-7** (A) Total transistor resistance scaled by channel width vs. channel length used to extract the Channel Resistance (slope) and Contact Resistance (y-intercept). (C) Example resistance values are calculated for each voltage using a transistor with a channel length of 20  $\mu$ m and a channel width of 300  $\mu$ m.

## 2-5: References

- 1. Gelinck, G. H. *et al.* Flexible active-matrix displays and shift registers based on solution-processed organic transistors. *Nat. Mater.* **3,** 106–110 (2004).

- 2. Wood, V. *et al.* Inkjet-printed quantum dot-polymer composites for full-color AC-driven displays. *Adv. Mater.* **21,** 2151–2155 (2009).

- 3. Takahashi, T., Takei, K., Gillies, A. G., Fearing, R. S. & Javey, A. Carbon Nanotube Active-Matrix Backplanes for Conformal Electronics and Sensors. *Nano Lett.* 5408–5413 (2011).

- 4. Min, S.-Y. *et al.* Large-scale organic nanowire lithography and electronics. *Nat. Commun.* **4,** 1773 (2013).

- 5. Sun, D. *et al.* Flexible high-performance carbon nanotube integrated circuits. *Nat. Nanotechnol.* **6,** 156–161 (2011).