Publicly Accessible Penn Dissertations

2017

### Smart Sensor Networks For Sensor-Neural Interface

Hongjie Zhu University of Pennsylvania, matthewhzhu@gmail.com

Follow this and additional works at: https://repository.upenn.edu/edissertations

Part of the Electrical and Electronics Commons

#### Recommended Citation

Zhu, Hongjie, "Smart Sensor Networks For Sensor-Neural Interface" (2017). Publicly Accessible Penn Dissertations. 2669. https://repository.upenn.edu/edissertations/2669

This paper is posted at Scholarly Commons. https://repository.upenn.edu/edissertations/2669 For more information, please contact repository @pobox.upenn.edu.

#### Smart Sensor Networks For Sensor-Neural Interface

#### **Abstract**

One in every fifty Americans suffers from paralysis, and approximately 23% of paralysis cases are caused by spinal cord injury. To help the spinal cord injured gain functionality of their paralyzed or lost body parts, a sensor-neural-actuator system is commonly used. The system includes: 1) sensor nodes, 2) a central control unit, 3) the neural-computer interface and 4) actuators. This thesis focuses on a sensor-neural interface and presents the research related to circuits for the sensor-neural interface.

In Chapter 2, three sensor designs are discussed, including a compressive sampling image sensor, an optical force sensor and a passive scattering force sensor. Chapter 3 discusses the design of the analog front-end circuit for the wireless sensor network system. A low-noise low-power analog front-end circuit in 0.5µm CMOS technology, a 12-bit 1MS/s successive approximation register (SAR) analog-to-digital converter (ADC) in 0.18µm CMOS process and a 6-bit asynchronous level-crossing ADC realized in 0.18µm CMOS process are presented. Chapter 4 shows the design of a low-power impulse-radio ultra-wide-band (IR-UWB) transceiver (TRx) that operates at a data rate of up to 10Mbps, with a power consumption of 4.9pJ/bit transmitted for the transmitter and 1.12nJ/bit received for the receiver. In Chapter 5, a wireless fully event-driven electrogoniometer is presented. The electrogoniometer is implemented using a pair of ultra-wide band (UWB) wireless smart sensor nodes interfacing with low power 3-axis accelerometers. The two smart sensor nodes are configured into a master node and a slave node, respectively. An experimental scenario data analysis shows higher than 90% reduction of the total data throughput using the proposed fully event-driven electrogoniometer to measure joint angle movements when compared with a synchronous Nyquist-rate sampling system.

The main contribution of this thesis includes: 1) the sensor designs that emphasize power efficiency and data throughput efficiency; 2) the fully event-driven wireless sensor network system design that minimizes data throughput and optimizes power consumption.

#### Degree Type

Dissertation

#### Degree Name

Doctor of Philosophy (PhD)

#### **Graduate Group**

**Electrical & Systems Engineering**

#### **First Advisor**

Jan Van der Spiegel

#### **Second Advisor**

Nader Engheta

| Keywords compressive image sensor, event-driven, force sensor, sensor-neural interface, wireless sensor network |

|-----------------------------------------------------------------------------------------------------------------|

| Subject Categories Electrical and Electronics                                                                   |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

#### SMART SENSOR NETWORKS FOR SENSOR-NEURAL INTERFACE

Hongjie Zhu

#### A DISSERTATION

in

Electrical and Systems Engineering

Presented to the Faculties of the University of Pennsylvania

in

Partial Fulfillment of the Requirements for the

Degree of Doctor of Philosophy

2017

| Supervisor of Dissertation                  | Co-Supervisor of Dissertation                  |

|---------------------------------------------|------------------------------------------------|

| Jan Van der Spiegel                         | Nader Engheta                                  |

| Professor of Electrical and Systems         | H. Nedwill Ramsey Professor of Electrica       |

| Graduate Group Chairperson                  |                                                |

| Alejandro Ribeiro, Rosenbluth Associate P   | rofessor of Electrical and Systems Engineering |

| Dissertation Committee                      |                                                |

| Dwight Jaggard, Professor of Electrical and | d Systems Engineering                          |

| Kenneth Laker Emeritus Professor of Elec    | trical and Systems Engineering                 |

Thomas Farmer, Lecturer of Electrical and Systems Engineering

## Acknowledgments

I would like to thank my academic advisors, Dr. Jan Van der Spiegel and Dr. Nader Engheta, for their support and guidance on my research.

I would like to thank my collaborators, Dr. Milin Zhang, Mr. Srihari Sritharan, Dr. Timothy Lucas, Dr. Andrew Richardson, Dr. Dengteng Ge, Dr. Shu Yang, Dr. Yuanming Suo, Dr. Trac D. Tran, Dr. Brian Edwards, Dr. Jie Zhang and Dr. Ralph Etienne-Cummings, for the inspiration of research as well as the hard work together.

I would also like to thank my thesis committee, Dr. Kenneth Laker, Dr. Dwight Jaggard and Dr. Thomas Farmer, for the support and advice on my thesis.

I would like to thank my dear friend, Mr. Robert Ottogalli III, for the moral support and the great help on proofreading my thesis.

#### ABSTRACT

#### SMART SENSOR NETWORKS FOR SENSOR-NEURAL INTERFACE

#### Hongjie Zhu

#### Jan Van der Spiegel

#### Nader Engheta

One in every fifty Americans suffers from paralysis, and approximately 23% of paralysis cases are caused by spinal cord injury [1]. To help the spinal cord injured gain functionality of their paralyzed or lost body parts, a sensor-neural-actuator system is commonly used. The system includes: 1) sensor nodes, 2) a central control unit, 3) the neural-computer interface and 4) actuators. This thesis focuses on a sensor-neural interface and presents the research related to circuits for the sensor-neural interface.

In Chapter 2, three sensor designs are discussed, including a compressive sampling image sensor, an optical force sensor and a passive scattering force sensor. Chapter 3 discusses the design of the analog front-end circuit for the wireless sensor network system. A low-noise low-power analog front-end circuit in  $0.5\mu m$  CMOS technology, a 12-bit 1MS/s successive approximation register (SAR) analog-to-digital converter

(ADC) in  $0.18\mu m$  CMOS process and a 6-bit asynchronous level-crossing ADC realized in  $0.18\mu m$  CMOS process are presented. Chapter 4 shows the design of a low-power impulse-radio ultra-wide-band (IR-UWB) transceiver (TRx) that operates at a data rate of up to 10Mbps, with a power consumption of 4.9pJ/bit transmitted for the transmitter and 1.12nJ/bit received for the receiver. In Chapter 5, a wireless fully event-driven electrogoniometer is presented. The electrogoniometer is implemented using a pair of ultra-wide band (UWB) wireless smart sensor nodes interfacing with low power 3-axis accelerometers. The two smart sensor nodes are configured into a master node and a slave node, respectively. An experimental scenario data analysis shows higher than 90% reduction of the total data throughput using the proposed fully event-driven electrogoniometer to measure joint angle movements when compared with a synchronous Nyquist-rate sampling system.

The main contribution of this thesis includes: 1) the sensor designs that emphasize power efficiency and data throughput efficiency; 2) the fully event-driven wireless sensor network system design that minimizes data throughput and optimizes power consumption.

## Contents

| 1        | Mot | tivatio      | n and Background                          | 1  |

|----------|-----|--------------|-------------------------------------------|----|

| <b>2</b> | Sen | nsors Design |                                           |    |

|          | 2.1 | Comp         | ressive Sampling Image Sensor             | 17 |

|          |     | 2.1.1        | Introduction                              | 18 |

|          |     | 2.1.2        | Design of the Image Sensor Array          | 21 |

|          |     | 2.1.3        | Image Reconstruction and Simulation       | 31 |

|          |     | 2.1.4        | Chip Fabrication and Experimental Results | 37 |

|          |     | 2.1.5        | Conclusion                                | 46 |

|          | 2.2 | Optica       | al Force Sensor                           | 48 |

|          |     | 2.2.1        | Introduction                              | 48 |

|          |     | 2.2.2        | Design of the Optical Force Sensor        | 49 |

|          |     | 2.2.3        | Experimental Results                      | 54 |

|          |     | 2.2.4        | Conclusion and Future Work                | 60 |

|          | 2.3 | Passiv       | re Scattering Force Sensor                | 61 |

|   |     | 2.3.1                                     | Introduction                                              | 61         |

|---|-----|-------------------------------------------|-----------------------------------------------------------|------------|

|   |     | 2.3.2                                     | Design of the Passive Scattering Force Sensor             | 62         |

|   |     | 2.3.3                                     | Simulation and Experiment Results                         | 68         |

|   |     | 2.3.4                                     | Conclusion and Future Work                                | 74         |

| 3 | Fro | $\mathbf{nt}	ext{-}\mathbf{E}\mathbf{nd}$ | l Circuit Design                                          | <b>7</b> 5 |

|   | 3.1 | A Low                                     | v-Noise Low-Power Analog Front-End Circuit                | 76         |

|   |     | 3.1.1                                     | Introduction                                              | 76         |

|   |     | 3.1.2                                     | Low-Noise Low-Power Amplifier Circuit Design              | 77         |

|   |     | 3.1.3                                     | A 12-bit 1MS/s SAR ADC Circuit Design in $0.5 \mu m$ CMOS |            |

|   |     |                                           | Process                                                   | 81         |

|   |     | 3.1.4                                     | Experimental Results and Discussion                       | 83         |

|   | 3.2 | A 12-1                                    | oit 1MS/s SAR ADC in $0.18\mu m$ CMOS Process             | 85         |

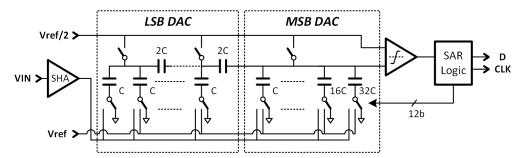

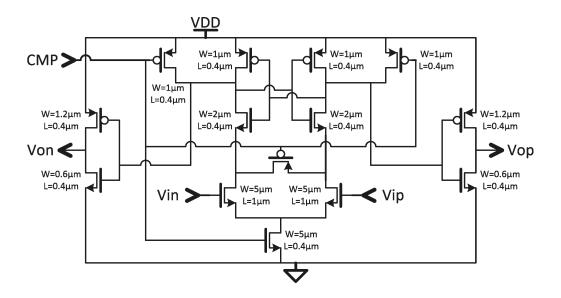

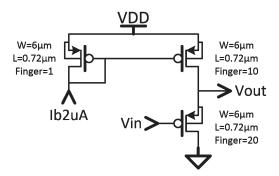

|   |     | 3.2.1                                     | Circuit Design                                            | 89         |

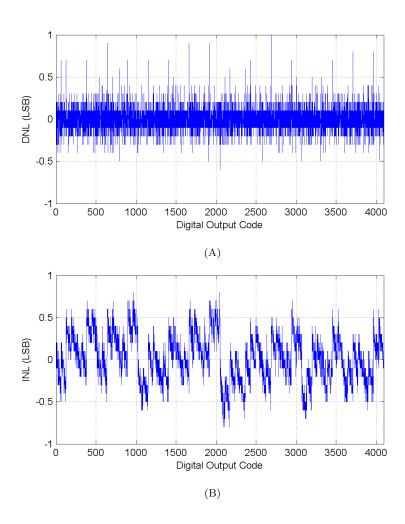

|   |     | 3.2.2                                     | Measurement Results                                       | 92         |

|   | 3.3 | An As                                     | synchronous Level-Crossing ADC                            | 92         |

|   |     | 3.3.1                                     | Introduction                                              | 95         |

|   |     | 3.3.2                                     | Circuit Design                                            | 96         |

|   |     | 3.3.3                                     | Measurement Results                                       | 105        |

|   | 3.4 | Concl                                     | usion                                                     | 105        |

| 4 | Wiı | eless (                                   | Circuit Design                                            | 110        |

|   | 4.1 | Impul   | se-Radio Ultra-Wide Band Transceiver         | 110 |

|---|-----|---------|----------------------------------------------|-----|

|   |     | 4.1.1   | Transeiver Design                            | 111 |

|   |     | 4.1.2   | Measurement Results                          | 115 |

|   | 4.2 | Concl   | usion                                        | 120 |

| 5 | Sys | tem In  | ategration                                   | 122 |

|   | 5.1 | A Wir   | reless Fully Event-Driven Electrogonio-meter | 122 |

|   |     | 5.1.1   | Introduction                                 | 123 |

|   |     | 5.1.2   | Architecture of the Entire System            | 125 |

|   |     | 5.1.3   | Configuration of the Electrogoniometer       | 128 |

|   |     | 5.1.4   | Static Body Joint Angle Measurement          | 131 |

|   |     | 5.1.5   | Chip Design                                  | 132 |

|   |     | 5.1.6   | Data Analysis                                | 134 |

|   |     | 5.1.7   | Scenario Data Analysis                       | 134 |

|   |     | 5.1.8   | Conclusion                                   | 137 |

| 6 | Cor | nclusio | ns and Outlook                               | 139 |

# List of Figures

| 1.1 | An illustration of the key functional blocks in a typical sensor-neural- |   |

|-----|--------------------------------------------------------------------------|---|

|     | actuator system.                                                         | 3 |

| 1.2 | The schematics of a comprehensive system for SCI rehabilitation. It      |   |

|     | combines physiological system modeling, biosensors, medical therapy,     |   |

|     | advanced adaptive control, and neural interface technology in central    |   |

|     | and peripheral levels for improved understanding and treatment of        |   |

|     | neural motor disorders due to spinal cord injury. [2]                    | 6 |

| 1.3 | High-level block diagram presenting an overview of the hybrid BCI        |   |

|     | system [3]                                                               | 7 |

| 1.4 | The structural diagram of the sensory feedback system: (a) the front     |   |

|     | module; (b) the signal processing module; (c) the electrical stimulator  |   |

|     | module. [4]                                                              | 8 |

| 1.5  | Hand prostnesis with mounted lights. It is attached at the fingers        |    |

|------|---------------------------------------------------------------------------|----|

|      | (the index finger to turn right, and the fifth finger to turn left) and   |    |

|      | at the forearm (the first light to open the hand, and the second one      |    |

|      | to close it) [5]                                                          | 9  |

| 1.6  | Medical sensor network (MSN) sensor node components. [6]                  | 10 |

| 1.7  | Wireless sensor networks (WSNs) for mobile health (M-Health). [6].        | 10 |

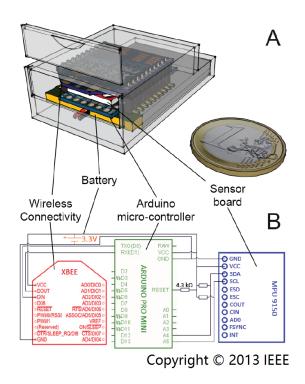

| 1.8  | A) CAD drawing of the internal components of the wireless body            |    |

|      | sensor node, showing one possible packaging option. B) A schematic of     |    |

|      | the 4 main internal sensor components and their in-between connection     |    |

|      | paths. [7]                                                                | 11 |

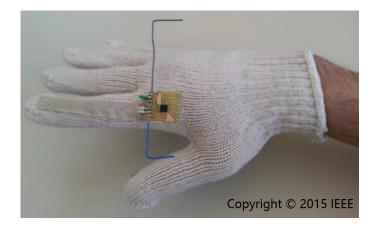

| 1.9  | Glove with the Flex Sensor sewed on and the battery-free wireless         |    |

|      | smart sensor node attached. [8]                                           | 12 |

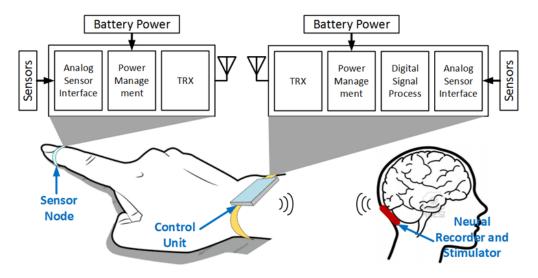

| 1.10 | A pair of typical wireless sensor nodes for tactile sensation restoration |    |

|      | application                                                               | 13 |

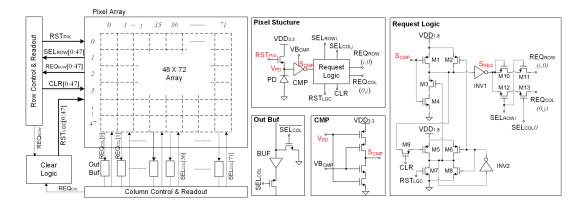

| 2.1  | Architecture of the $48\times72$ all-digital address event image sensor   |    |

|      | array. Each pixel includes a reset transistor, a photodiode, a inverter-  |    |

|      | based tunable-threshold-voltage comparator, and an all-digital 17-        |    |

|      | transistor focal plane request logic unit. Column-level output buffers    |    |

|      | are employed for the readout of the requests generated in each pixel.     | 22 |

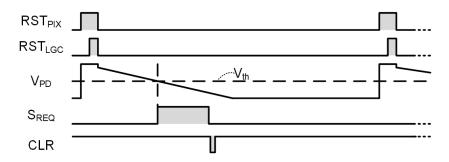

| 2.2 | Timing of a single address event driven pixel. Both the photodiode                |    |

|-----|-----------------------------------------------------------------------------------|----|

|     | and the focal plane logic unit are reset by $RST_{PIX}$ and $RST_{LGC}$           |    |

|     | during the reset phase, respectively. After the reset phase, the voltage          |    |

|     | of the photodiode, $V_{PD}$ , drops proportionally to the illumination            |    |

|     | intensity. A request, $S_{REQ}$ , will be generated when $V_{PD}$ is lower than   |    |

|     | a preset threshold voltage $V_{th}$ . $CLR$ will clear the request signal and     |    |

|     | lock the request logic until the next $RST_{LGC}$                                 | 23 |

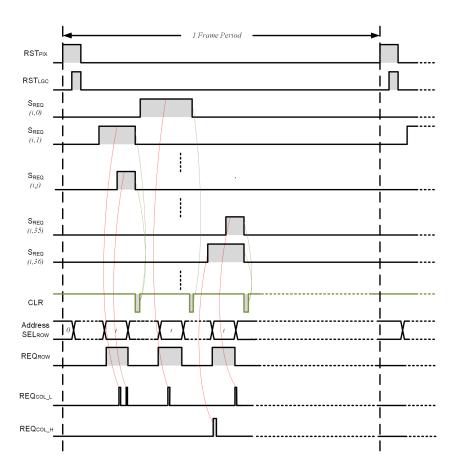

| 2.3 | Timing control of the readout process of the proposed image sensor                |    |

|     | array under video capture mode. The $i^{th}$ row is taken as an example.          |    |

|     | Once the $i^{th}$ row is selected by $SEL_{ROW}[i]$ , if an active $ROW_{REQ}$ is |    |

|     | detected due to the existence of one or more uncleared fired pixel(s)             |    |

|     | in the current row, a column scanning will be triggered to readout all            |    |

|     | the addresses of all the unclear fired pixels. A clear signal, $CLR$ , will       |    |

|     | be enabled to clear all the fired pixels by the end of current scanning           |    |

|     | iteration                                                                         | 27 |

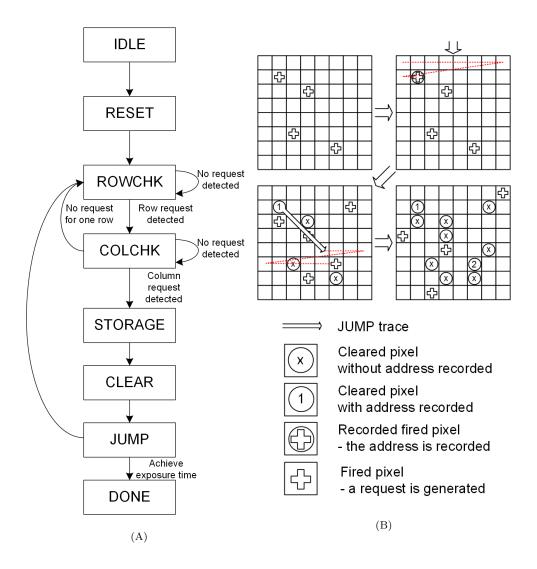

| 2.4 | (A) State machine of the readout logic for the compressive acquisition            |    |

|     | mode with one-pixel-one-iteration readout. (B) A demonstration of                 |    |

|     | the "Winner-takes-all" readout strategy                                           | 28 |

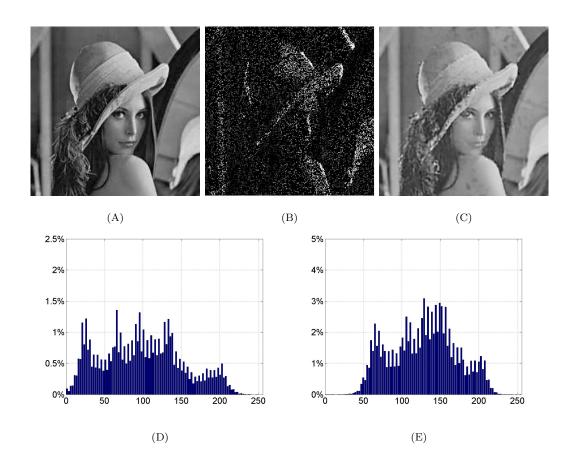

| 2.5  | (A) A 24-bit $256 \times 256$ original sampled image is employed for the  |            |

|------|---------------------------------------------------------------------------|------------|

|      | demonstration of the proposed image processing. The grayscale             |            |

|      | is equally divided into $2^{13}$ levels. N-continuous-pixel-one iteration |            |

|      | readout method is used to form (B) the compressive sampled matrix         |            |

|      | $I_{smp}(i,j)$ . (C) Reconstructed image from (B). A PSNR of 23dB and     |            |

|      | a SSIM of 0.835 is achieved. (D) and (E) show the histogram of the        |            |

|      | raw image and reconstructed image, respectively.                          | 34         |

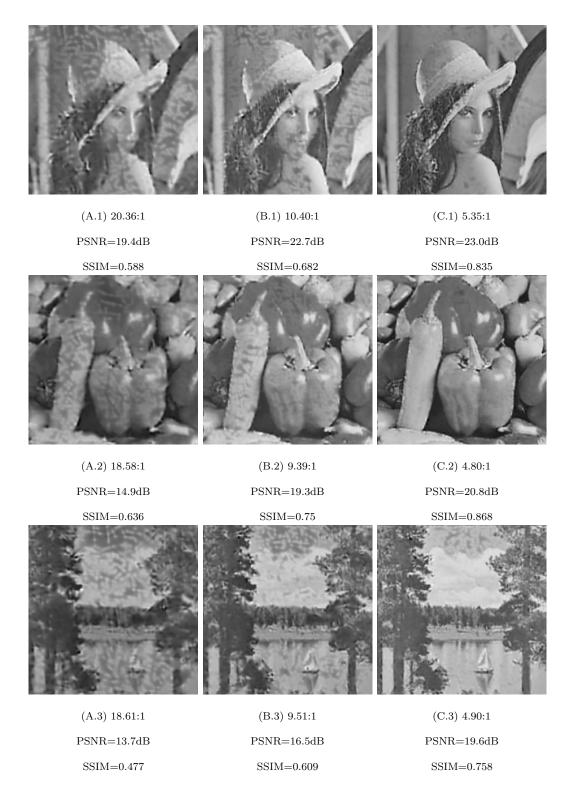

| 2.6  | Reconstructed sample images with different compression ratios la-         |            |

|      | belled underneath each figure                                             | 35         |

| 2.7  | A simulation is performed on a $16 \times 16$ array. (A) 136 requests are |            |

|      | captured and recorded. The value of unrecorded pixels are filled by       |            |

|      | zero. (B) Reconstructed image from the captured results                   | 37         |

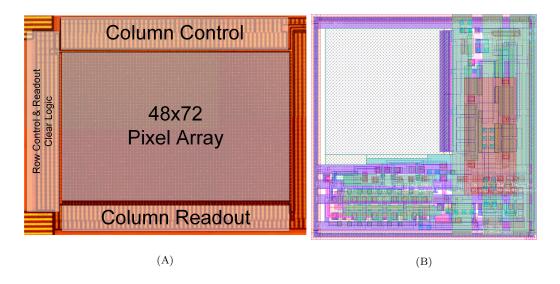

| 2.8  | (A) Chip photograph (size of 1.125mm $\times$ 0.85mm), and (B) pixel      |            |

|      | layout $(15\times15\mu m^2)$                                              | 39         |

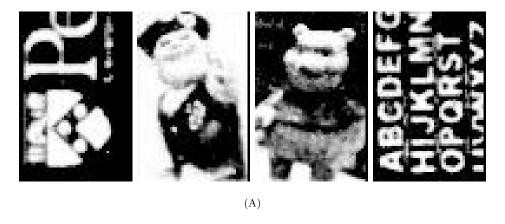

| 2.9  | (A) Sample images captured without compressive sensing                    | 40         |

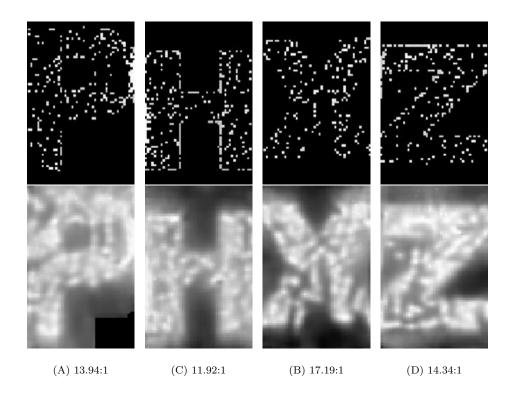

| 2.10 | (A) Raw sample images captured with compressive sensing. (B)              |            |

|      | Sample images reconstructed from corresponding captured as shown          |            |

|      | in (A). N-continuous-pixel-one-iteration mode is used. And N is           |            |

|      | assigned to 7                                                             | <b>⊿</b> 1 |

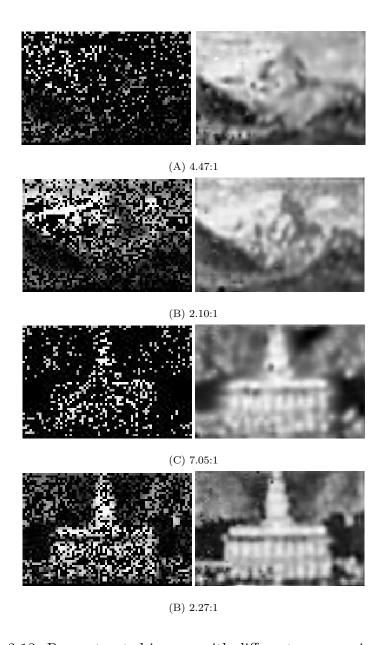

| 2.11 | Sample images captured under compressive sensing mode, and the         |    |

|------|------------------------------------------------------------------------|----|

|      | corresponding reconstructed results from the captured samples. The     |    |

|      | compression ratio is listed under the figures                          | 42 |

| 2.12 | Reconstructed images with different compression ratios                 | 43 |

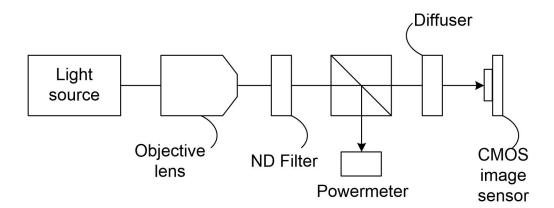

| 2.13 | Optical test setup for the evaluation of the response of the image     |    |

|      | sensor to different incident light intensities. A beamsplitter is used |    |

|      | to split the incident beam of light into two. A fixed proportion of    |    |

|      | one of the two beams is applied to a powermeter for a quantitative     |    |

|      | evaluation of the incident light intensity                             | 44 |

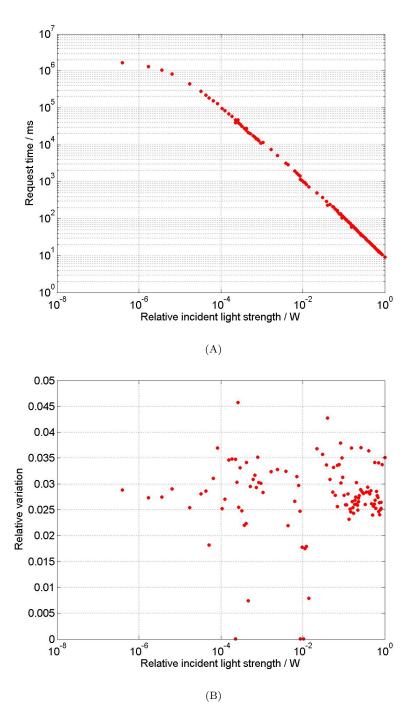

| 2.14 | (A) Average requests generating time, and (B) relative variation error |    |

|      | of the test pixels while the strength of the incident light increases. |    |

|      | The incident power is normalized by the maximum power used during      |    |

|      | this experiment                                                        | 45 |

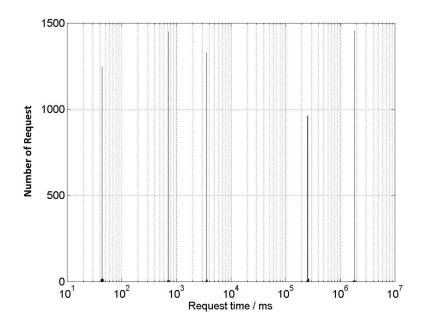

| 2.15 | Histogram plot of the request time under different request times       | 47 |

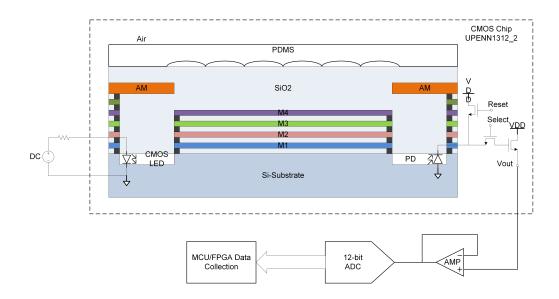

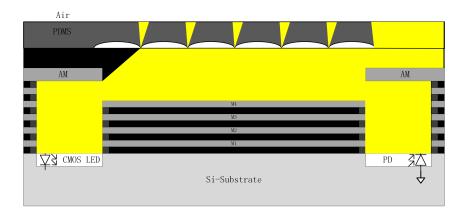

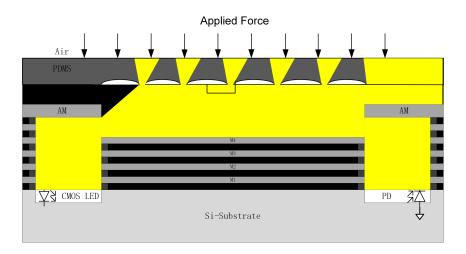

| 2.16 | System view of the optical force sensor. (Layer Mi: metal layer i;     |    |

|      | layer AM: top metal layer.)                                            | 51 |

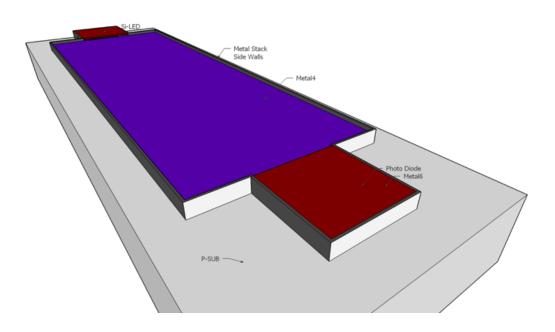

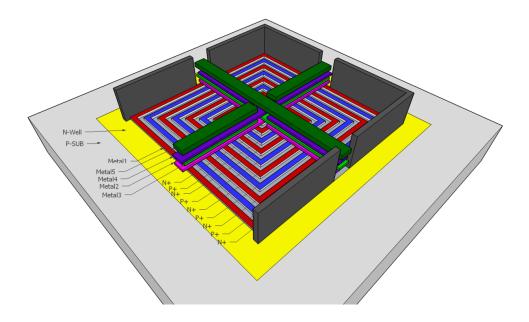

| 2.17 | 3-dimension view of the optical channel                                | 51 |

| 2.18 | Operating mechanism of the optical force sensor. Geometry not drawn    |    |

|      | to scale                                                               | 52 |

| 2.19 | 3-dimension view of the silicon LED                                    | 53 |

| 2.20 | Layout of the optical force sensor chip                                | 54 |

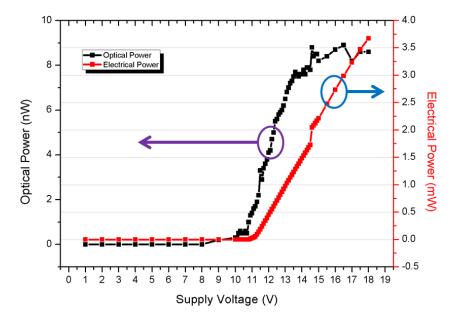

| 2.21 | Electric and optical power of the silicon LED                           | 55 |

|------|-------------------------------------------------------------------------|----|

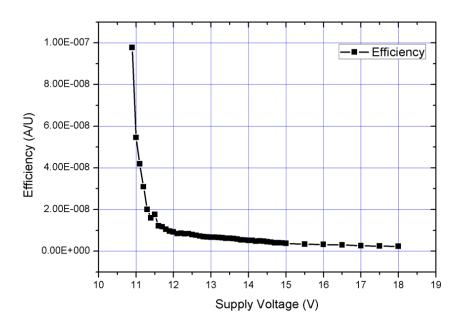

| 2.22 | Electric-to-optical conversion efficiency of the silicon LED            | 56 |

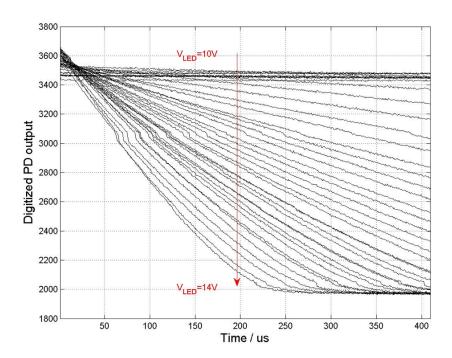

| 2.23 | Experimental response of the optical channel for different reverse bias |    |

|      | voltages of the SiLED                                                   | 57 |

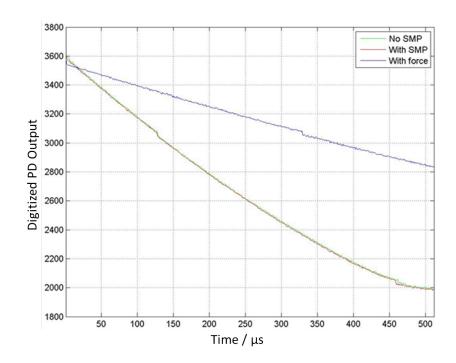

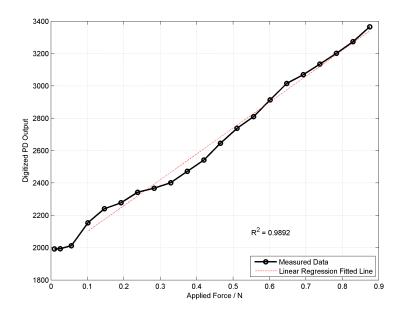

| 2.24 | Measured sensor response: digitized photodiode voltage with respect     |    |

|      | to applied force. The photodiode discharges faster when no PDMS         |    |

|      | film sample (SMP) is present and when no force is applied to the        |    |

|      | PDMS SMP on top of the optical waveguide channel. The photodiode        |    |

|      | discharges much more slowly as a result of more light escaping from     |    |

|      | the waveguide when force is applied to PDMS SMP                         | 58 |

| 2.25 | Measured sensor response: digitized photodiode voltage with respect     |    |

|      | to applied force. Linearity of the force sensor is given by the fitted  |    |

|      | regression line R-squared value of 0.9892 over an applied force range   |    |

|      | from 0.1N to 0.87N                                                      | 59 |

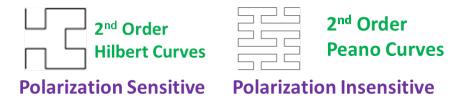

| 2.26 | Space filling curves: (left)2nd-order Hilbert curve, (right) 2nd-order  |    |

|      | Peano curve                                                             | 62 |

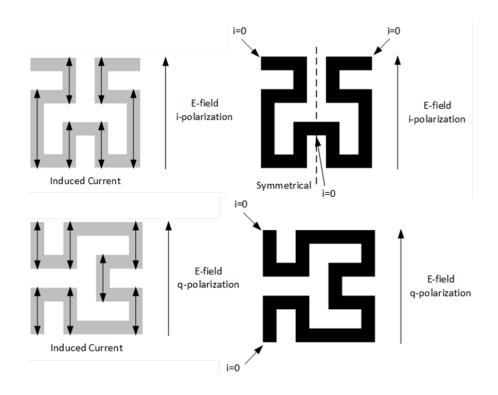

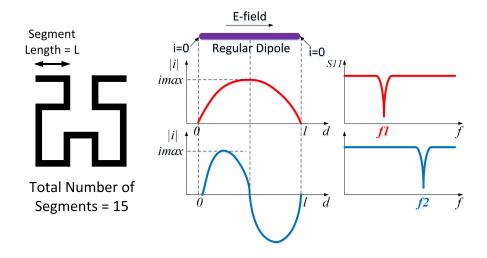

| 2.27 | Resonance mechanism of a 2nd-order Hilbert curve                        | 64 |

| 2.28 | Resonance mechanism of a 2nd-order Hilbert curve                        | 64 |

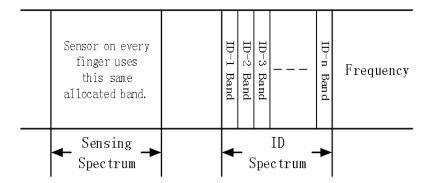

| 2.29 | Spectrum allocation of the passive scattering wireless sensor node .    | 66 |

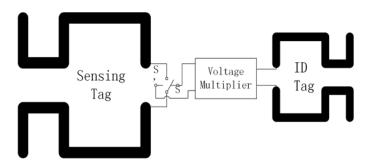

| 2.30 | Schematic of the passive scattering wireless sensor node                | 67 |

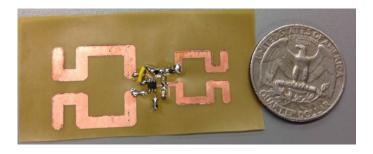

| 2.31 | A picture of a sample of the passive scattering wireless sensor node    | 67 |

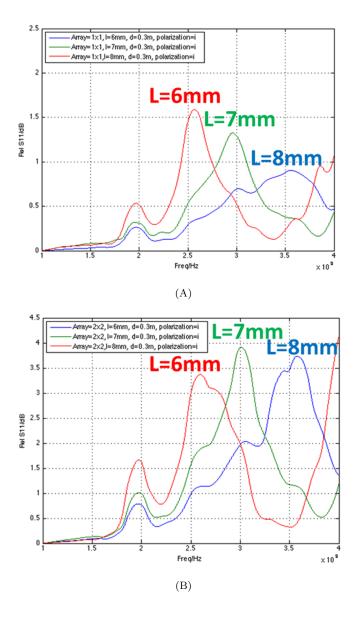

| 2.32 | (A) Measured responses of single 2nd-order Hilbert-curve tags with                   |    |

|------|--------------------------------------------------------------------------------------|----|

|      | different sizes. (B) Measured responses of $2\times 2$ arrays of 2nd-order           |    |

|      | Hilbert-curve tags with different sizes                                              | 70 |

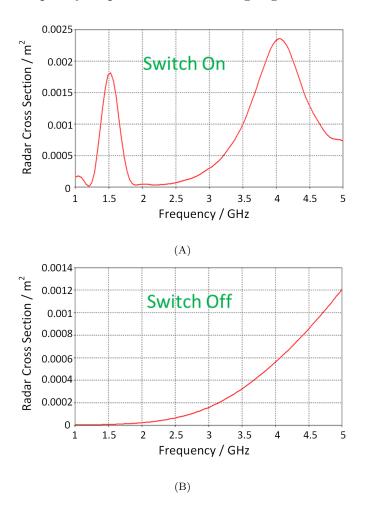

| 2.33 | (A) Simulated radar cross section (RCS) response of the sensing tag                  |    |

|      | when switched on. (B) Simulated RCS response of the sensing tag                      |    |

|      | when switched off                                                                    | 71 |

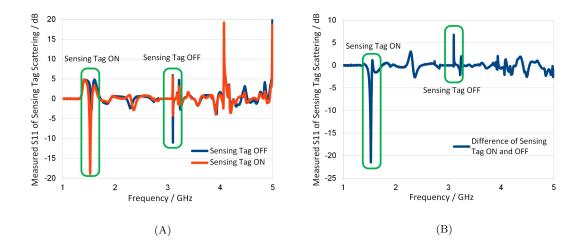

| 2.34 | Experimental results of the selection of the passive scattering wireless             |    |

|      | sensor node. (A) Measured S11 of Sensing tag scattering response                     |    |

|      | when turned on and off. (B) The difference in the S11 response                       |    |

|      | between sensing tag turned on and off                                                | 72 |

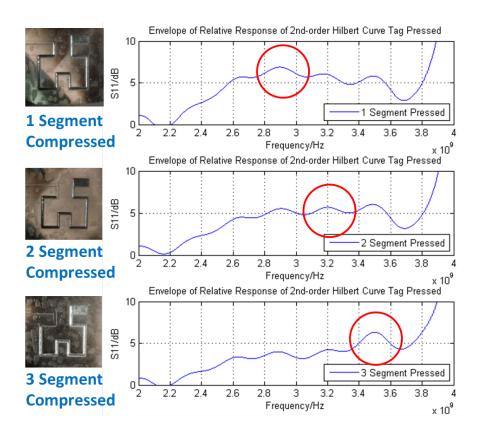

| 2.35 | Measured responses of the 2nd-order Hilbert-curve force sensor made                  |    |

|      | of GaIn liquid metal                                                                 | 73 |

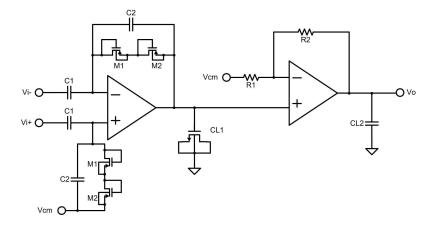

| 3.1  | Architecture of the low-noise low-power high-sensitivity amplifier                   | 78 |

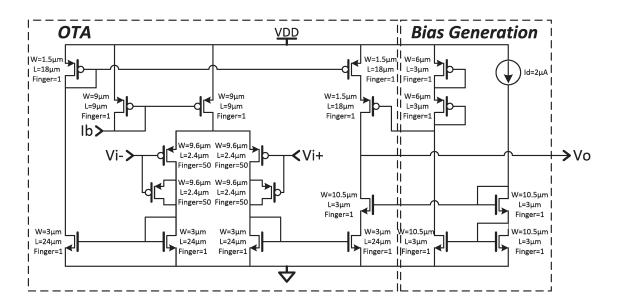

| 3.2  | Schematic of the first-stage operational transconductance amplifier                  |    |

|      | (OTA) of front-end amplifier                                                         | 79 |

| 3.3  | Schematic of the second-stage operational amplifier (OpAmp) of                       |    |

|      | front-end amplifier                                                                  | 79 |

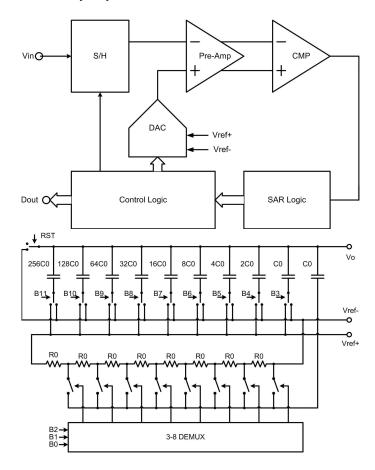

| 3.4  | Architecture of the 12-bit resolution 1M samples/s on-chip successive-               |    |

|      | approximation-register ADC                                                           | 82 |

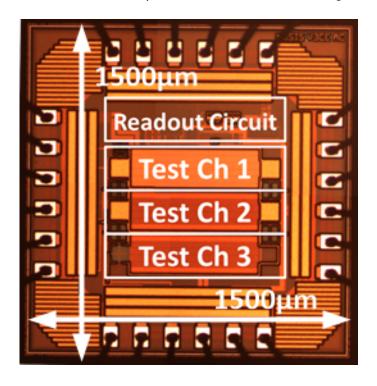

| 3.5  | A microphotograph of the analog front-end. The size of chip is $1500 \mu \mathrm{m}$ |    |

|      | by 1500 <i>µ</i> m.                                                                  | 83 |

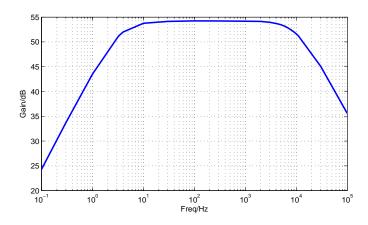

| 3.6  | The measured AC gain of the low-power low-noise amplifier               | 85 |

|------|-------------------------------------------------------------------------|----|

| 3.7  | The output-referred noise spectrum of the low-noise low-power low-      |    |

|      | noise amplifier                                                         | 86 |

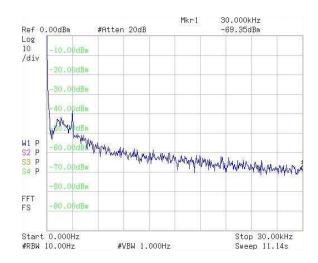

| 3.8  | Measured (A) DNL and (B) INL of the SAR ADC in $0.5 \mu m$ CMOS         |    |

|      | process                                                                 | 87 |

| 3.9  | Measured spectrum of the SAR ADC in $0.5 \mu m$ CMOS process            | 88 |

| 3.10 | Architecture of the of 12-bit resolution successive approximation       |    |

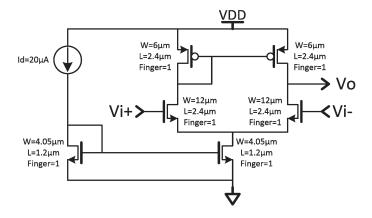

|      | register (SAR) analog-to-digital converter (ADC)                        | 90 |

| 3.11 | Schematic of the comparator in the SAR ADC                              | 91 |

| 3.12 | Schematic of the Sample/Hold Amplifier (SHA) in the SAR ADC for         |    |

|      | the image sensor column level ADC version                               | 91 |

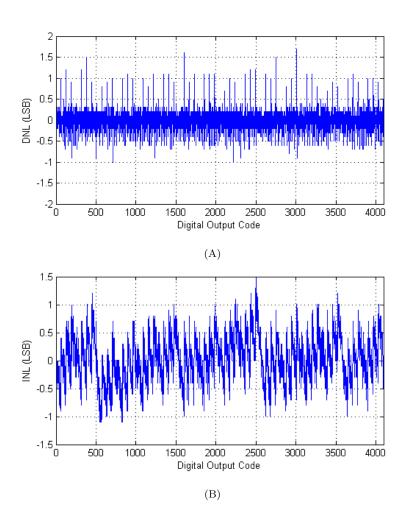

| 3.13 | Measured (A) DNL and (B) INL of the SAR ADC in $0.18 \mu m$ CMOS        |    |

|      | process                                                                 | 93 |

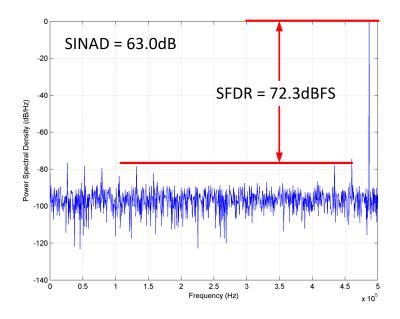

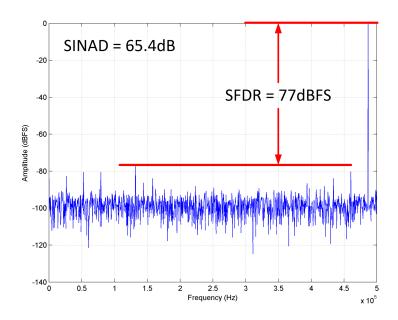

| 3.14 | Measured spectrum of the SAR ADC in $0.18 \mu m$ CMOS process           | 94 |

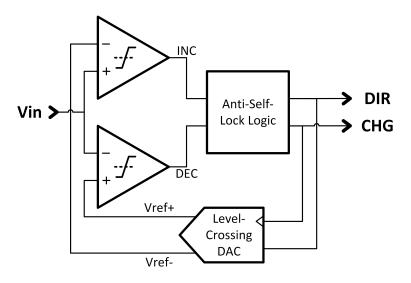

| 3.15 | Block Diagram of the Asynchronous Level-Crossing ADC, integrating       |    |

|      | a pair of comparators, an anti-self-locking logic, and a level-crossing |    |

|      | DAC                                                                     | 97 |

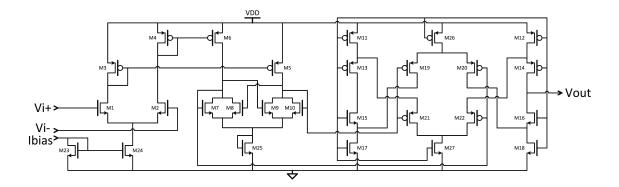

| 3.16 | Schematic of the low-power, wide-common-mode-range comparator           |    |

|      | in the level-crossing ADC                                               | 98 |

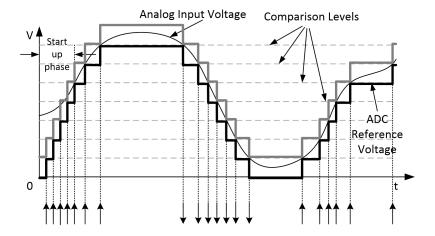

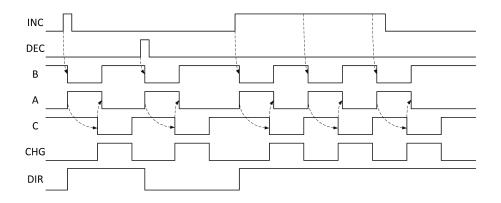

| 3.17 | Operation principles of an 8-level asynchronous level-crossing ADC.                  |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | $\uparrow$ and $\downarrow$ represent an "increase" (INC) or "decrease" (DEC) output |     |

|      | of the ADC, respectively                                                             | 99  |

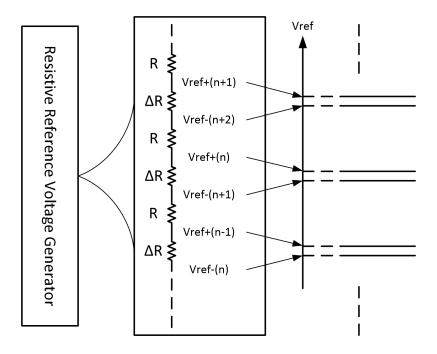

| 3.18 | Schematic of the hysteresis resistive reference voltage generator                    | 99  |

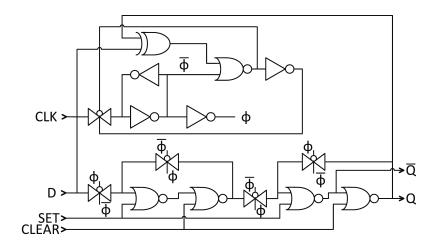

| 3.19 | Schematic of the low-power clock-gating D-flip-flop (DFF)                            | 100 |

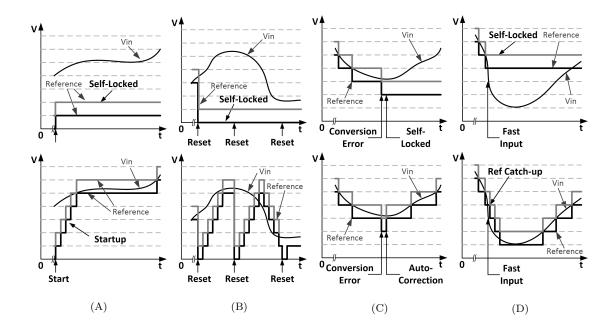

| 3.20 | Self-locking state of the level-crossing ADC (upper row) and non-self-               |     |

|      | locking of the ADC with the proposed anti-self-locking "CHG" signal                  |     |

|      | generation circuit (lower row) (a) during ADC startup, (b) during                    |     |

|      | asynchronous resets, (c) during conversion error, and (d) when the                   |     |

|      | input signal changing faster than the fastest ADC response speed                     | 103 |

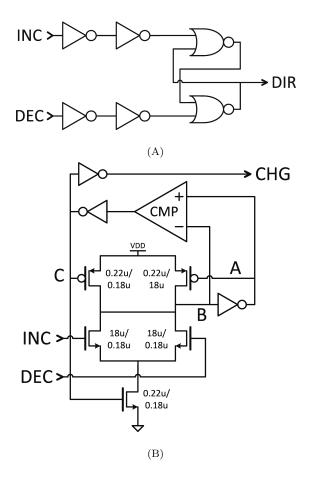

| 3.21 | Schematic of (A) "Change" and (B) "Direction" circuit                                | 104 |

| 3.22 | Timing diagram of the CHG signal generation circuit                                  | 104 |

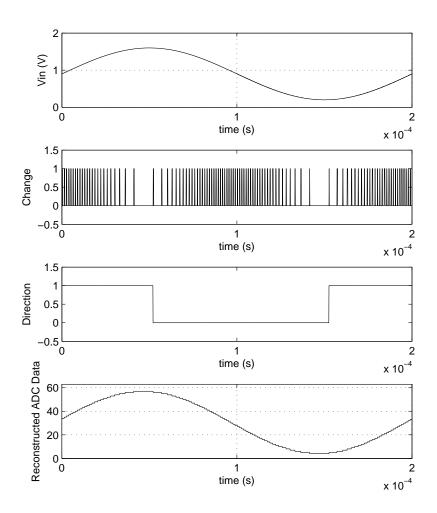

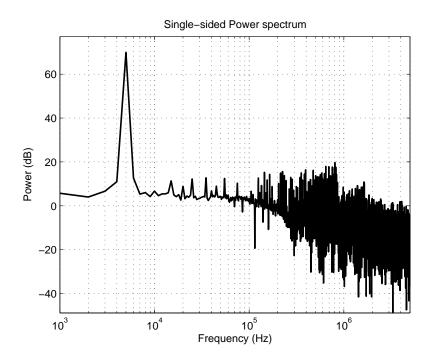

| 3.23 | The spectrum of the level-crossing ADC output data                                   | 106 |

| 3.24 | The spectrum of the level-crossing ADC output data                                   | 107 |

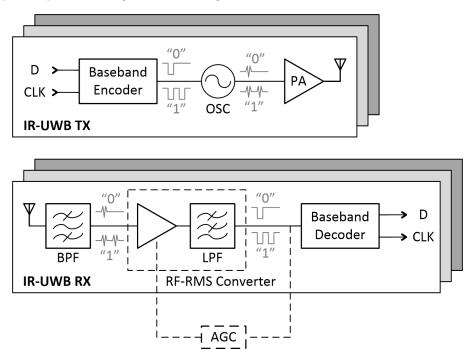

| 4.1  | Block diagram of the IR-UWB transceivers. Three parallel, asyn-                      |     |

|      | chronous and independent channels are implemented                                    | 112 |

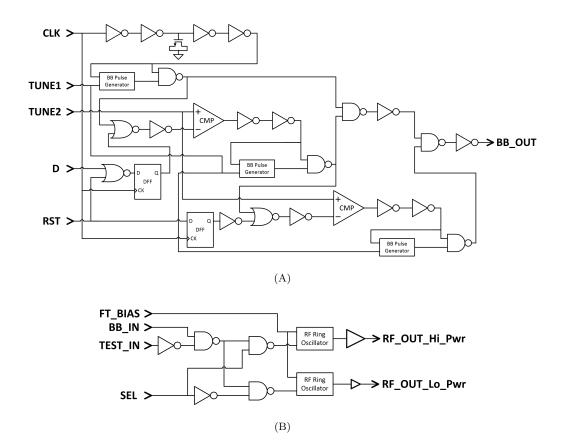

| 4.2  | Architecture of (A) the baseband generator of the transmitter, which                 |     |

|      | converts digital data input into short pulses with a tunable width                   |     |

|      | from 10ns to 250ns, and (B) the RF pulse generator of the transmitter,               |     |

|      | which modulates the short pulses output of the baseband generator                    |     |

|      | to RF frequencies.                                                                   | 113 |

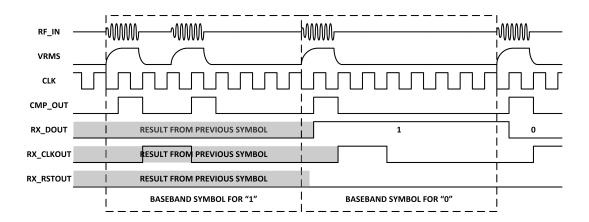

| 4.3 | Timing diagram of the IR-UWB transmitter. Logic "0" is encoded          |     |

|-----|-------------------------------------------------------------------------|-----|

|     | into one short pulse in a baseband clock cycle, while logic "1" is      |     |

|     | encoded into two short pulses in a baseband clock cycle. An output      |     |

|     | of three continuous short pulses in a baseband clock cycle represents   |     |

|     | a global reset signal of the entire circuit                             | 114 |

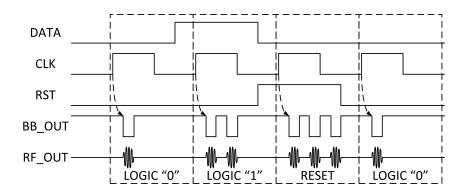

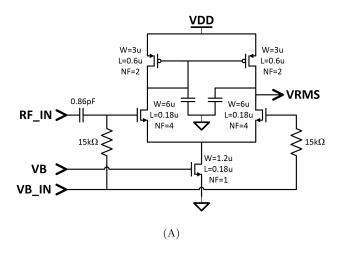

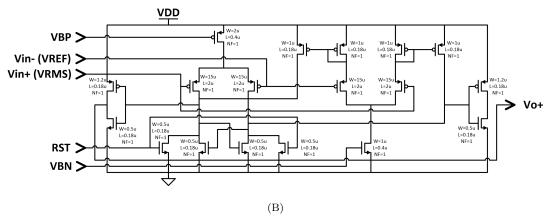

| 4.4 | Architecture of the (A) RF-RMS converter and (B) the comparator         |     |

|     | used in the RF-RMS detector, which compares the output of the           |     |

|     | RF-RMS converter with a reference voltage                               | 116 |

| 4.5 | Timing diagram of the IR-UWB receiver. The output of the RF-            |     |

|     | RMS is decoded in a digital pattern-recognition logic circuit with the  |     |

|     | output in the format of received data (RX_DOUT), received clock         |     |

|     | (RX_CLKOUT) or received reset (TX_RSTOUT)                               | 117 |

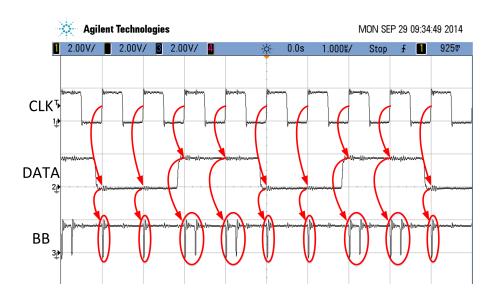

| 4.6 | Waveforms of the output pulses of the transmitter. "DATA" and           |     |

|     | "CLK" are the input data and clock to the transmitter, respectively.    |     |

|     | "BB" is the baseband short pulses of the transmitter. A clock frequency |     |

|     | of 0.5Mbps is used in this measurement                                  | 118 |

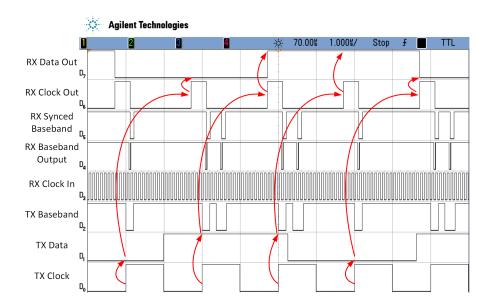

| 4.7 | Measured waveforms of the transceiver signals. A clock frequency of       |     |

|-----|---------------------------------------------------------------------------|-----|

|     | $0.5 \mathrm{Mbps}$ is used in this measurement. "TX Data" and "TX Clock" |     |

|     | are the transmitted data and clock signals at the UWB transmitter.        |     |

|     | "TX Baseband" is the baseband short pulses at the transmitter. "RX        |     |

|     | Clock In" is the digital sampling clock for the comparator and pattern    |     |

|     | recognition logic at the receiver. "RX Baseband Output" and "RX           |     |

|     | Synced Baseband" are the comparator instantaneous output and the          |     |

|     | synchronised output at the receiver. "RX Data Out" and "RX Clock          |     |

|     | Out" are the received data and clock at the receiver, respectively.       |     |

|     | "BB" is the baseband short pulses of the transmitter                      | 121 |

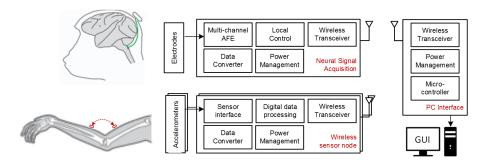

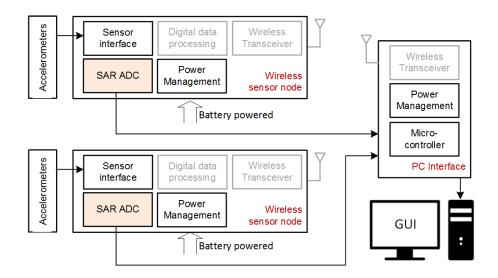

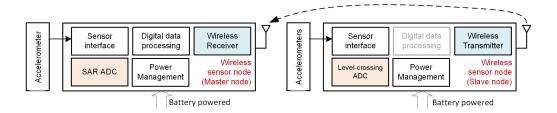

| 5.1 | Block diagram of the entire electrogoniometer system, consisting of       |     |

|     | i) a neural signal acquisition device, ii) a wireless electrogoniometer,  |     |

|     | and iii) a PC interface                                                   | 127 |

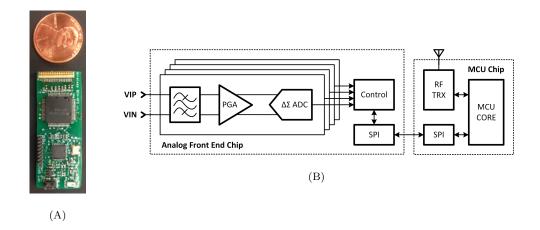

| 5.2 | (A) Photo of the neural signal acquisition device. (B) Block diagram      |     |

|     | of the neural signal acquisition, consisting of a four channel analog     |     |

|     | front end, a microcontroller, and a 2.4<br>GHz wireless transceiver       | 127 |

| 5.3 | Block diagram of the entire system under high resolution data acqui-      |     |

|     | sition mode. Digitized sensory data read from the SAR ADC are sent        |     |

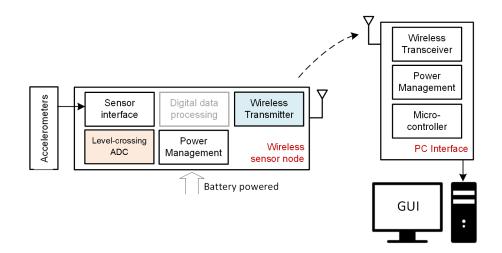

|     | back to the PC through the PC interface board                             | 129 |

| 5.4  | Block diagram of the entire system under low power data acquisition      |     |

|------|--------------------------------------------------------------------------|-----|

|      | mode. The sensory data are digitized using a level-crossing ADC and      |     |

|      | wirelessly sent to the PC interface board                                | 130 |

| 5.5  | Block diagram of the entire system under angle measurement mode.         |     |

|      | Both sensor nodes are powered by batteries. The joint angle is           |     |

|      | calculated in the on-chip digital data processing unit                   | 130 |

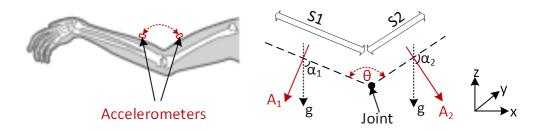

| 5.6  | Experimental setup of the dual accelerometers system for joint angle     |     |

|      | measurement. The measured joint connects two rigid body segments,        |     |

|      | $S_1$ and $S_2$                                                          | 131 |

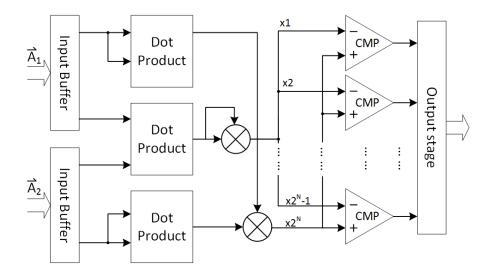

| 5.7  | Architecture of the real-time joint angle calculation digital processing |     |

|      | unit                                                                     | 133 |

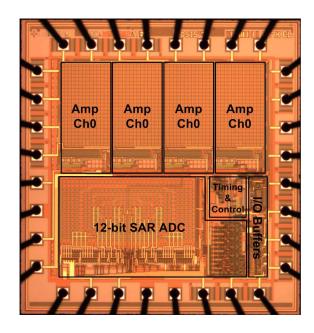

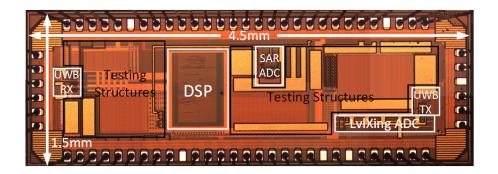

| 5.8  | Microphotograph of the proposed design                                   | 133 |

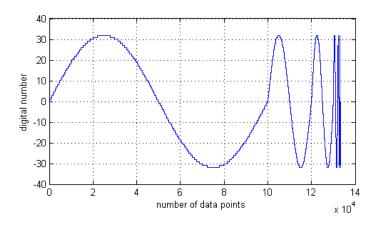

| 5.9  | 10Hz-5kHZ frequency sweep input signal                                   | 135 |

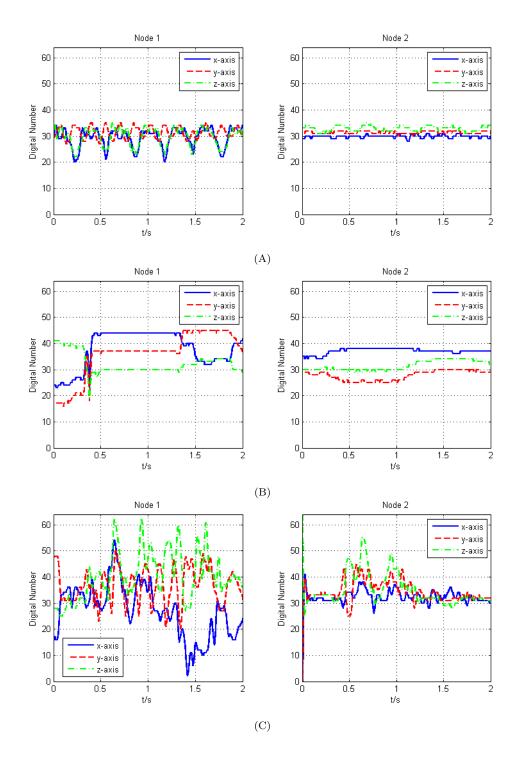

| 5.10 | Measured results of scenarios of (A) walking at a normal pace, (B)       |     |

|      | sitting at a browsing the Internet, and (C) intense indoor movements.    | 136 |

## List of Tables

| 2.1 | Summary of the measured performances                          | 38  |

|-----|---------------------------------------------------------------|-----|

| 3.1 | Front-End Amplifier Performance Summary                       | 86  |

| 3.2 | Amplifier Performance Summary                                 | 88  |

| 3.3 | Measured performance summary of the SAR ADC                   | 94  |

| 3.4 | Measured performance summary of the level-crossing ADC $$     | 107 |

| 4.1 | Summary of the measured performance of the IR-UWB transmitter | 119 |

| 4.2 | Measured performance summary of the IR-UWB receiver           | 120 |

## Chapter 1

## Motivation and Background

Paralysis has been one of the major illnesses that affect large populations both worldwide and in the United States of America. According to a study conducted by the Christopher & Dana Reeve Foundation in 2009, approximately 1.9% of American population (5.6 million) suffer from paralysis, either transient or permanent [1]. The study also listed the top causes of paralysis, including stroke, spinal cord injury (SCI) and multiple sclerosis. Spinal cord injury, as the second leading cause, was responsible for 23% of the 5.6 million paralysis cases in the U.S.

The study [1] showed that families with SCI patients were generally concentrated towards the lower annual household income brackets Associated with paralysis, the loss of productivity of paralyzed patients coupled with the expensive medical bills usually cause a decline in quality of life for the whole family. According to the 2016 Annual Statistical Report [9] by the National Spinal Cord Injury Statistical Center

(NSCISC) at the University of Alabama at Birmingham, 58.1% of SCI patients were employed at the time of the injury, but only 12.4% were able to be employed one year after the injury. The Report [9] also pointed out that the estimated lifetime costs directly due to SCI is around 4.7 million dollars (discounted at 2%) if the patient acquires high tetraplegia at 25 years old [10, 11, 12, 13]. The annual costs of a patient indirectly due to SCI, including losses in wages, fringe benefits and productivity, have an average of 72 thousand dollars per year [9].

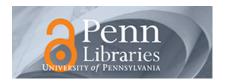

To help paralyzed subjects, extensive research work has been conducted in the fields of Neural-Computer Interface (NCI)[14, 15, 16, 17, 18, 19], prosthesis [20, 21, 3, 22, 23, 24, 2] and wearable sensor network [25, 26, 6, 7, 27, 28]. A typical sensor-neural-actuator (SNA) system includes: 1) sensor nodes, 2) a central control unit (CCU), 3) the NCI and 4) actuators. Fig. 1.1 illustrates the blocks of a typical system and the information flow among the blocks.

Sensor nodes consist of sensors and signal processing circuits. Sensors are used to capture the physical interactions between the individual subject and the environment and to convert the interactions into electrical signals [29, 30, 31, 32, 33, 34, 35, 36]. With the advancement of material science, fabrication processes as well as information technology, low-power and miniaturized sensors are emerging rapidly. Accelerometers are usually used in sensing positions, gestures and angles [29, 30]. Gyroscopes are commonly used to sense movements and rotations [31, 32]. Strain gauges are widely used to sense forces and deformations [34, 35, 36]. Photodiodes and

Figure 1.1: An illustration of the key functional blocks in a typical sensor-neural-actuator system.

image sensors are mostly used to sense ambient lighting, environment and motion [37, 38, 39]. The signal processing circuits interface with the sensors and condition (amplify, filter, digitize and digitally process) the electrical signals from the sensors [40, 41, 42, 43, 44, 45]. The signal processing circuits can be built with off-the-shelf components [40, 41] for low budget and short turnaround time, or they can be built with customized integrated circuits (IC) [43, 44, 45] for optimized functionality, low power consumption and miniaturized size.

The central control unit (CCU) acts as a relay of the sensory data from the sensor nodes as well as the neural activity information from the central nervous system [22, 5]. More extensively, it works collaboratively with the central nervous system [46, 47]. The CCU processes the data from the sensor nodes and encodes it into "neural language" by controlling the neural stimulator in the NCI to stimulate the central nervous system, which helps recreate the feeling of sensation [47, 48, 49, 4]. At the same time, the CCU takes the neural signals and decodes them into control signals to drive the actuators [5, 46, 50].

The neural-computer interface is the interface between the central nervous system and the central control unit. It delivers stimulations, either electrical [47, 50, 51, 52] or optical [53, 54, 55], to the central nervous system. Depending on the region where the stimulations are applied, sensations or body movements could be created [48, 49, 4, 52, 56]. Meanwhile, the NCI also gathers and records the electrical signals from the central nervous system [57, 58, 59, 60]. The signals are passed to the CCU

for analysis and further actions in the system.

Actuators convert electrical control signals into physical quantities [61, 62, 63], such as movements. Common actuators include but are not limited to: limb prosthesis [20, 21, 3, 22] to help amputated individuals gain mobility and muscle stimulations [21, 64, 65] to help individuals to gain control of the muscles whose functionalities were compromised by injury to the corresponding nerves. The sensors and the actuators can be integrated at the same site to form a bi-directional sensor-neural-actuator closed loop [48, 49, 4].

Depending on the applications, a combination of some or all of the blocks in the sensor-neural-actuator system can be implemented to help subjects compensate for the loss of physiological functions caused by paralysis.

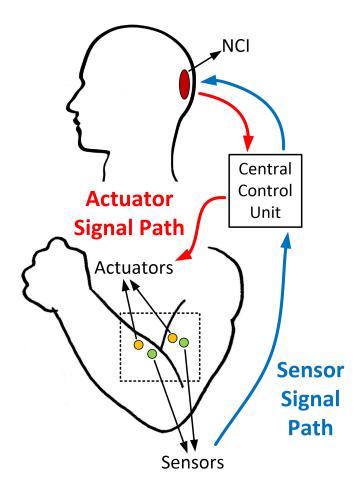

J. He, et al., reviewed the neural prosthetics "for rehabilitation of lower limb function spinal cord injured" in [2]. As shown in Fig. 1.2, SCI rehabilitation involves both and "assessments" and "therapies." For a sensor-neural-actuator system, the sensor signal path (blue path in Fig. 1.1) realizes the "assessments," while the actuator signal path (red path in Fig. 1.1) implements the "therapies."

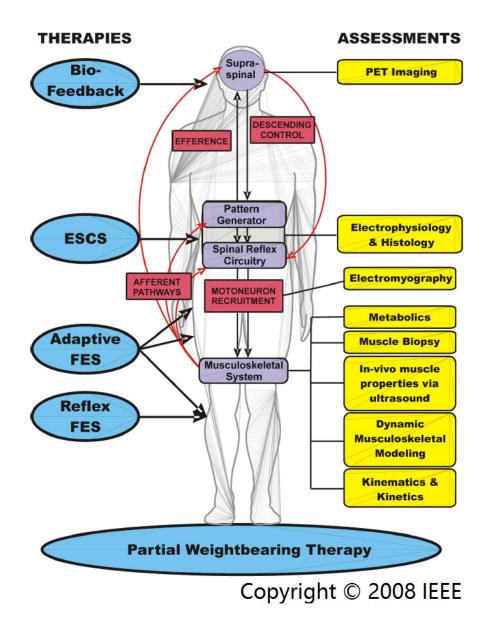

K. D. Katyal, et al., introduced a hybrid brain-computer interface (BCI) system which "combines elements of autonomous robotic manipulation with neural decoding algorithms" to control a prosthetic hand [3]. As illustrated in Fig. 1.3, the hybrid BCI provides a good example of the implementation of a sensor-neural-actuator loop in Fig. 1.1. In-vivo experiments on a spinal cord injury patient have demonstrated

Figure 1.2: The schematics of a comprehensive system for SCI rehabilitation. It combines physiological system modeling, biosensors, medical therapy, advanced adaptive control, and neural interface technology in central and peripheral levels for improved understanding and treatment of neural motor disorders due to spinal cord injury. [2]

a 97.6% success rate for the patient to "grasp a known spherical object and place it at a desired location on a table" [3].

Figure 1.3: High-level block diagram presenting an overview of the hybrid BCI system [3].

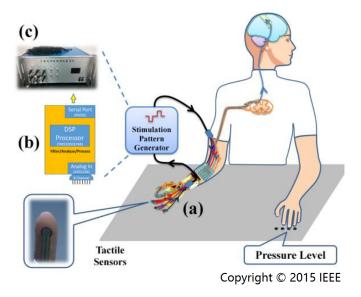

In [4], X. Liu, et al., presented "a sensory feedback system for a prosthetic hand" including the sensor nodes, a partial CCU and a partial neural-computer interface blocks (actuator (blue) signal path in Fig. 1.1) in order to help upper limb amputated subjects recreate tactile sensation, as illustrated in Fig. 1.4. Tactile sensors are placed on the tips of the prosthetic fingers to sense the pressure on each finger tip. The pressure information is converted into "invoked tactile sensation at the stump skin of residual limb" in the form of transcutaneous electrical nerve stimulation (TENS). In-vivo tests have shown promising results.

G. R. Müller-Putz, et al., proposed a neural-actuator system that utilizes steadystate visual evoked potentials (SSVEPs) to control a two-axis electrical prosthetic

Figure 1.4: The structural diagram of the sensory feedback system: (a) the front module; (b) the signal processing module; (c) the electrical stimulator module. [4]

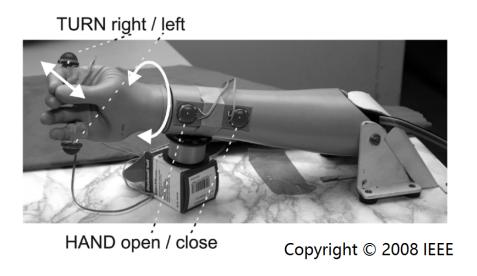

hand [5], as shown in Fig. 1.5, to implement a partial neural-computer interface, a partial CCU and actuators (sensor (red) signal path in Fig. 1.1). An up to 88% online classification accuracy has been achieved in experiments on four trained human test subjects.

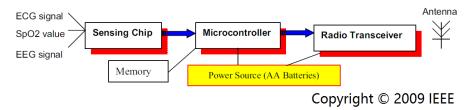

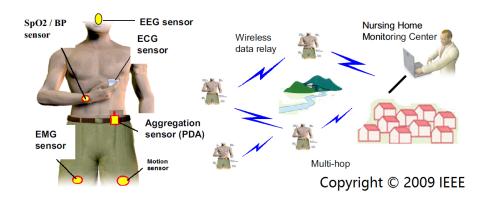

A sensor network for mobile health (M-Health) applications is presented by F. Hu, et al., in [6]. A wireless sensor node implementation is depicted in Fig. 1.6. Biomedical signals such as electrocardiogram (ECG), electroencephalogram (EEG) and blood oxygen saturation (SpO2) are captured by the sensing chips. A microcontroller (MCU) processes the signals at each sensor motenode and sends the data out by a radio transceiver. A aggregation sensor (PDA), acting as a CCU (in

Figure 1.5: Hand prosthesis with mounted lights. It is attached at the fingers (the index finger to turn right, and the fifth finger to turn left) and at the forearm (the first light to open the hand, and the second one to close it) [5].

Fig. 1.1), gathers data from the sensor nodes and relays them to M-Health network, as shown in Fig. 1.6.

Figure 1.6: Medical sensor network (MSN) sensor node components. [6].

Figure 1.7: Wireless sensor networks (WSNs) for mobile health (M-Health). [6].

C. Gavriel, et al., showed a low-cost wireless body sensor network implemented with off-the-shelf components [7]. As shown in Fig. 1.8, the battery-powered wireless sensor node features a nine-axis motion-tracking sensor, an Arduino MCU and a wireless transceiver module in a coin-sized package. Real-time body motion (natural joint kinematics) streaming and recording are achieved with high accuracy.

A battery-free wireless smart glove is proposed by R. V. Aroca, et al., in [8], as "an assessment technology in stroke rehabilitation." The smart glove, as shown in

Figure 1.8: A) CAD drawing of the internal components of the wireless body sensor node, showing one possible packaging option. B) A schematic of the 4 main internal sensor components and their in-between connection paths. [7].

Fig. 1.9, is capable of measuring finger bending events utilizing a sensor node with ultra-high-frequency (UHF) radio-frequency identification (RFID) technology. The sensor node harvests energy from RF signals and uses the harvested energy to drive the strain gauge "Flex" sensor as well as to power an integrated analog-to-digital converter (ADC). The digitized sensor data is "backscattered" to the RFID reader by modulating the RFID antenna load at the sensor node.

Figure 1.9: Glove with the Flex Sensor sewed on and the battery-free wireless smart sensor node attached. [8].

Despite encouraging state-of-the-art research, a fully operational sensor-neural-actuator system, with which the paralyzed individual is able to manipulate a prosthesis as his or her own body part, has not been extensively studied. One of the major challenges in such a system is absence of somatosensory feedback [66]. Even healthy individuals can experience difficulty in performing simple manual tasks without proper touch, posture and movement sensations [67]. Therefore, the research of this thesis focuses on the sensor-neural interface in the sensor-neural-actuator

system as shown in Fig. 1.1. Power efficiency and data-throughput efficiency of the sensor nodes are emphasized. As illustrated in Fig. 1.10, a pair of typical wireless sensor nodes for tactile sensation restoration application consists of a slave sensor on the finger tip and a master sensor on the wrist. Each sensor node has sensors, analog sensor interface circuits, power management circuits and wireless transceiver circuits. At the master sensor node, digital signal processing could also be implemented.

Figure 1.10: A pair of typical wireless sensor nodes for tactile sensation restoration application.

This thesis is organized as follows. Chapter 2 discusses the sensor design, including a compressive sampling image sensor, a standard-CMOS compatible optical force sensor and a passive scattering force sensor. Analog front-end circuit design is presented in Chapter 3, including a low-noise low-power analog front-end amplifier, 2 successive approximation register (SAR) ADCs and an asynchronous level-crossing ADC. Wireless circuit design is shown in Chapter 4. An impulse-radio ultra-wide-

band (IR-UWB) transceiver (TRx) is discussed. Chapter 5 shows a wireless fully event-driven electrogoniometer, as a system integration application of the wireless sensor network built with all the circuit blocks presented in this thesis. Chapter 6 concludes the thesis.

The main contribution of this thesis includes: 1) the sensor designs that emphasize power efficiency and data throughput efficiency; 2) the fully event-driven wireless sensor network system design that minimizes data throughput and optimizes power consumption.

# Chapter 2

# Sensors Design

Sensors, as the most front-end components in most modern sensor network systems, convert physical quantities into electrical signals. The research in sensor designs presented in this chapter provides sensors for the realization of smart sensor networks for sensor-brain interface. The research process also provides a good understanding of the properties and limitations of sensors, which as a result helps determine the specifications for the electrical circuit designs in the following chapters.

As the media between the physical world and the electric signals, several parameters play important roles in the sensor design. These parameters include sensitivity, range, power consumption, physical dimension and manufacturability.

Sensitivity reflects the sensor's accuracy to convert the physical quantity into electricity. Sensitivity is usually limited by the sensing mechanism, the sensing material and the sensor structure.

Range defines the extreme levels of the physical quantities that the sensor is able to handle in operation. Range, commonly known as the dynamic range of an image sensor, is mostly limited by the pixel design as well as the readout circuit design. The range of mechanical-to-electricity sensors is usually determined by the amount of mechanical deformation of the sensing material.

Power consumption reflects the sensor's efficiency of converting the physical quantity into electricity. It is mostly determined by the sensing mechanism. In addition, other factors such as the signal readout method, the sensing material and the fabrication process also affect the power consumption of the sensor.

The physical dimension of a sensor is determined by the sensor's applications. Miniaturized sensors are commonly used in, but not limited to, medical applications, since the artificial devices are expected to have minimal impact on physiology. On the other hand, large-scale sensors have been used as part of the structural materials in applications in robotics, architecture and civil engineering, etc.

Manufacturability is related to the difficulty in fabricating the sensor. It is also directly related to the cost and yield in the fabrication of the sensor as well as the sensor's ability to be integrated with the rest of the system, such as signal analysis and processing units. The less complicated the fabrication process of the sensor is, the better the yield and the easier the system integration are.

In the process of the sensor design, tradeoffs among the important parameters are necessary. For every sensor, the tradeoff between sensitivity and range is always essential. This is mainly due to the properties and physical limitations of the sensing materials. The tradeoff between sensitivity and power consumption is usually the key factor in determining the sensing mechanism. A good sensor design takes a reasonable compromise of the parameters to meet the design specifications.

In this chapter, three sensor designs are presented, including a compressive sampling image sensor, an optical force sensor and a passive scattering force sensor. The compressive sampling image sensor is optimized for its low power consumption. The optical force sensor is optimized for its sensitivity as well as its ease of manufacture. The passive scattering force/stretch sensor is optimized for its power consumption, physical dimension and manufacturability.

# 2.1 Compressive Sampling Image Sensor

The content in the Compressive Sampling Image Sensor section was originally published in [68] ©2016 IEEE. Reprinted, with permission, from H. Zhu, M. Zhang, Y. Suo, T. D. Tran and J. Van der Spiegel, "Design of a Digital Address-Event Triggered Compressive Acquisition Image Sensor," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 63, no. 2, pp. 191-199, Feb. 2016.

In reference to IEEE copyrighted material which is used with permission in this thesis, the IEEE does not endorse any of University of Pennsylvania's products or services. Internal or personal use of this material is permitted. If interested in reprinting/republishing IEEE copyrighted material for advertising or promotional purposes

or for creating new collective works for resale or redistribution, please go to http://www.ieee.org/publications\_standards/publications/rights/rights\_link.html to learn how to obtain a License from RightsLink.

#### 2.1.1 Introduction

CMOS image sensors have experienced a rapid development in the past two decades. Its compatibility with the highly scaled modern CMOS technology enables a rapid increase of the image resolution, frame rate, and digital signal processing abilities. The recently reported commercial CMOS image sensors features higher than 20 mega pixels (MP) resolution with a frame rate of up to 90 frames per second (fps) for still image capture, or more than 4K resolution with up to 120fps for video recording [69, 70]. This fast growing requirement of image resolution and frame rate places an increased burden in terms of power consumption and readout rate. Image sensors that implement various on-chip, off-array image compression algorithms effectively reduce the throughput of the entire sensor, but cannot reduce the frame rate, or the amount of analog-to-digital conversion processing, which are typically the most power hungry functional units in an image sensor [71]. The concept of compressive acquisition realizes image compression during the image capture phase, which provides an alternative solution to on-chip image compression algorithm implementation.

Compressive sensing enables signal sampling at a rate lower than the Nyquist rate

without greatly sacrificing the quality of the original signal [72, 73, 74, 75]. Image sensors that implement on-chip compressive sensing algorithms have been reported in the literature [76, 77, 78, 79]. E.g. in [76], an analog compressive sensing processing unit is integrated at the focal plane. However, it suffers from poor linearity and large noise. Authors of [79] proposed a  $\Delta\Sigma$ -based single-shot compressive sensing image sensor, which divides the array into  $4\times4$  pixel blocks. Power reduction is realized by doing an analog-to-digital conversion of only one randomly selected pixel from each block.

Time-to-first-spike image sensors that usually employ address-event representation (AER) as readout method, encode light intensity to time, which completely eliminates the A/D converter, and significantly reduces the readout data rate [80, 81, 82, 83, 84, 85, 86, 87, 88, 89]. In [81, 82, 80], the authors introduced three versions of time-to-first-spike image sensor designs, in which the each pixel is capable of generating a request when a photodiode is exposed to a certain intensity level, and requests are arbitrated for compressive AER readout. In [80], an arbitration time-to-first spike imager with on-chip histogram equalization was discussed. The design suffers from timing errors since it acknowledges pixel requests on a one-by-one basis instead of globally. Paper [83] and [84] proposed an image sensor enabling lossless compressive video acquisition as well as motion detection. AER is used to record the scene information captured by the imager, such as temporal contrast and grey scale. Paper [85] presented an image sensor using asynchronous time-based

image sensor (ATIS) with a real-time compressive sensing image reconstruction block implemented with a field-programmable gate array (FPGA). Images from the real-time reconstruction are shown to be comparable in quality to the images from state-of-the-art offline reconstruction. The authors of [88, 89] presented a time-to-first-spike imager for high dynamic range video recording. Paper [86] introduced an arbitration AER digital imager, which queues and arbitrates the read out sequence of the addresses of the exposed pixels. However, designs in [88, 89, 86] did not employ compressive sensing, therefore the amount of readout data is not reduced. [87] presented an imager with hybrid pixels implementing asynchronous dynamic event sensing and synchronous intensity sensing in the same pixel. However, the complicated structure of the hybrid pixel results in large pixel area and low fill factor.

In this chapter, an all-digital address-event triggered compressive acquisition image sensor, which combines the advantages of compressive sensing and AER, is presented. The imager is implemented in IBM  $0.18\mu\mathrm{m}$  standard CMOS technology, featuring an array of  $48\times72$  22-transistor pixels, occupying a silicon area of  $15\times15\mu\mathrm{m}^2$  with a fill factor of 32.4%. After a global reset phase, each pixel raises a request when the integration voltage drops below a pre-set threshold of the pixel-level comparator. Requests are scanned, recorded and cleared in each request search cycle. A self-lock circuit is integrated in each pixel to make sure that one pixel only generates a single request in a frame capture phase. The all-digital nature of the proposed pixel design

guarantees its scalability in size with future CMOS technologies.

### 2.1.2 Design of the Image Sensor Array

#### Architecture and circuits of the pixel

Fig. 2.1 shows the architecture of the image sensor, consisting of a  $48\times72$  array of all-digital image pixels with row and column control and address-event triggered readout circuitry. Each pixel consists of an inverter-based tunable-threshold-voltage comparator and a focal plane request logic unit. Fig. 2.2 illustrates the timing of a single pixel. The processing of each single pixel begins from a global reset phase, during which both the photodiode and the focal plane logic unit are reset (by " $RST_{PIX}$ ") and cleared (by " $RST_{LGC}$ "), respectively, in each pixel. After the reset phase, the voltage of the photodiode,  $V_{PD}$ , drops proportionally to the illumination intensity. A "logic high" request signal,  $S_{REQ}$ , will be fired in the focal plane logic unit once the voltage of the photodiode is lower than a preset threshold voltage,  $V_{th}$ , of the pixel-level comparator. Readout circuitry records the address of the selected requesting pixels; subsequently a clear signal, CLR, is triggered to clear all the request signals in the fired pixels. A self-lock circuit is integrated in the focal plane logic unit to make sure that one pixel only generates a single request in the same frame capture phase. The "locked" status will be cleared during the next global reset phase by the focal plane logic reset signal,  $RST_{LGC}$ . If the darkest pixel is not fired by the end of the last loop, the readout logic will not wait any longer, but will

assign a value 0 to represent all the intensities that are smaller than the detectable threshold.

Figure 2.1: Architecture of the 48×72 all-digital address event image sensor array. Each pixel includes a reset transistor, a photodiode, a inverter-based tunable-threshold-voltage comparator, and an all-digital 17-transistor focal plane request logic unit. Column-level output buffers are employed for the readout of the requests generated in each pixel.

An inverter-based comparator, as illustrated in Fig. 2.1, is used to compare the voltage of the photodiode,  $V_{PD}$ , and a preset threshold. The threshold voltage  $V_{th}$  of the comparator is tunable between 1.0V to 2.0V which enables high tuning range for the pixel without occupying a large area. The simulated performance of the inverter-based comparator is close to a typical regenerative latch comparator which occupies at least twice as much of silicon area. Pre-amplifiers with offset cancellation are usually employed to reduce the offset of the comparators. However, they are not suitable for use in-pixel due to the area limitation and its complicated

Figure 2.2: Timing of a single address event driven pixel. Both the photodiode and the focal plane logic unit are reset by  $RST_{PIX}$  and  $RST_{LGC}$  during the reset phase, respectively. After the reset phase, the voltage of the photodiode,  $V_{PD}$ , drops proportionally to the illumination intensity. A request,  $S_{REQ}$ , will be generated when  $V_{PD}$  is lower than a preset threshold voltage  $V_{th}$ . CLR will clear the request signal and lock the request logic until the next  $RST_{LGC}$ .

timing controls. To ensure a sufficient fill factor of the pixel, the mismatch of the comparators is traded off with comparator input gate area. Monte Carlo simulations of the comparator show that the standard deviation of the threshold voltage due to device mismatch and process variation is smaller than 30mV. The mismatch of the comparators contributes to the standard deviation of the fixed pattern noise (FPN) in dark, which is 30mV/(3.3V-0.7V-1.2V) = 2.14%, where 3.3V is the pixel reset supply voltage, 0.7V is the threshold voltage of the pixel reset NMOS switch, and 1.2V is the comparator threshold voltage.

The circuit of the focal plane logic unit is integrated in an all digital circuit with 17 transistors, as illustrated on the right of Fig. 2.1. The transistors  $M_{1-3}$  (with sizes of  $0.5\mu m/0.32\mu m$  (thick oxide device),  $0.4\mu m/0.18\mu m$  and  $0.4\mu m/0.18\mu m$ , respectively) and  $INV_1$  (2.4 $\mu m/0.18\mu m$  for PMOS and 0.4 $\mu m/0.18\mu m$  for NMOS for driving the row and column data buses) generate a pixel-level request,  $S_{REQ}$ , when the voltage of the photodiode is lower than the comparator threshold  $V_{th}$ . A pixel with a request generated is denoted as a "fired" pixel.  $M_5$  and  $M_9$  clear the request after it has been recorded. The W/L ratio of transistor  $M_5$  (3 $\mu m/0.18\mu m$ ) is much larger than that of  $M_8$  (0.22 $\mu m/2\mu m$ ), making sure the common drain node of  $M_5$  and  $M_8$  is pulled up during the clear period. The self-lock logic consists of  $M_{4,6,8}$  (with sizes of  $0.5\mu m/0.32\mu m$  (thick oxide device),  $0.5\mu m/0.18\mu m$  and  $0.22\mu m/2\mu m$ , respectively) and  $INV_2$ , which lock the pixel output. All the  $REQ_{ROW}(i,j)$  signals generated in a same row are connected to the row request bus.  $SEL_{ROW}$  signal

selects the row to be readout. The request of the selected row is transferred to the  $REQ_{ROW}$  output. The  $REQ_{COL}(i,j)$  signal can only be read when a corresponding row is selected. In the row and column readout circuitry, buffers are added for an effective readout. The 72 columns are divided into two equal halves to double the processing speed of the triggered requests.

#### Timing and readout control logic

There are two different modes enabled in this design: i) video capture mode, and ii) compressive acquisition mode. Under video capture mode, the address of all the fired pixels will be readout, while under compressive acquisition mode, only the address of selected fired pixels will be readout. The value of the discarded pixels will be restored during the image reconstruction phase off-line, which will be detailed in the next section.

Fig. 2.3 illustrates the timing control of the readout process of the designed image sensor array under video capture mode. As mentioned in the previous subsection, for each pixel, after the reset phase, a request signal,  $S_{REQ}$ , will be generated once the photodiode voltage drops below  $V_{th}$ . A shift-register chain is included in both the row and column periphery circuits enabling a continuous scanning of the entire array. Take the  $i^{th}$  row for example. During one iteration, when the  $i^{th}$  row is selected  $(SEL_{ROW}[i]$  is enabled), an active  $REQ_{ROW}$  (logic high) will be detected if one or more uncleared fired pixel(s) can be detected in the  $i^{th}$  row. A column scanning will

be triggered to readout the addresses of all the uncleared fired pixels. As mentioned earlier, there are two sets of column control and readout circuits for each half of the array. Fired pixels located in each half will be readout correspondingly. A clear signal, CLR, will be enabled to clear all the fired pixels by the end of current scanning iteration. No column scanning will be triggered if a low  $REQ_{ROW}$  is detected, in order to speed up the readout process. Pixels readout in the same iteration loop will be encoded to the same digitized gray level. The gray level is increased by one for each iteration. The digitized image will be further scaled up into the full range of a gray color map during image reconstruction.

Under compressive acquisition mode, the address(es) of only one or several fired pixels will be readout during one scanning iteration. The clear logic block enables: 1) one-pixel-one-iteration readout, which records address of the first detected fired pixel for each iteration. 2) N-continuous-pixel-one-iteration readout, which records the first N addresses of the detected fired pixels for each iteration. The value of N can be assigned from two configuration pins. The time span of each loop is controlled by a counter as part of the logic. The counter increases by one during each clock cycle. Once it counts to a preset threshold, one iteration is done. The value of the threshold can be preset through the two configuration pins as well. No matter which readout method is used, the start location of each scanning iteration is randomly assigned.

Fig. 2.4 (A) illustrates the state machine of the readout logic for the compressive

Figure 2.3: Timing control of the readout process of the proposed image sensor array under video capture mode. The  $i^{th}$  row is taken as an example. Once the  $i^{th}$  row is selected by  $SEL_{ROW}[i]$ , if an active  $ROW_{REQ}$  is detected due to the existence of one or more uncleared fired pixel(s) in the current row, a column scanning will be triggered to readout all the addresses of all the unclear fired pixels. A clear signal, CLR, will be enabled to clear all the fired pixels by the end of current scanning iteration.

Figure 2.4: (A) State machine of the readout logic for the compressive acquisition mode with one-pixel-one-iteration readout. (B) A demonstration of the "Winner-takes-all" readout strategy.

acquisition mode with one-pixel-one-iteration readout. After the global reset of the photodiode as well as of the request of the logic circuit, the voltage of the photodiode from the overall array will drop proportionally to the light intensity. The system shifts the state from RESET to ROWCHK. In the ROWCHK state, the off array vertical control logic keeps scanning row by row. The row request from the selected row is taken as an input to the state machine during the ROWCHK state. One active row request input will shift the state to COLCHK. The column readout will then be triggered by scanning the requested row column by column until one pixel request is readout. Since the entire array is divided into two halves, the first half is denoted as the higher priority half in case two pixels requests are detected at the same time by the column readout circuit. The address of the request pixel will be recorded. There is a chance that a glitch may cause a false row request input. In order to increase the robustness of the system, a protection is applied in the COLCHK state, that if no column request is detected after scanning of the entire row, the state machine will be pulled back to ROWCHK state. A "Winnertake-all" strategy is applied to the compressive readout procedure, a clear signal, CLR, is triggered to clear all the request signals in the fired pixels, once one pixel is selected under one-pixel-one-iteration readout mode, or N pixels are selected under N-continuous-pixel-one-iteration readout mode. Only the address of the selected pixel/pixel-pair (if a column request is detected for both halves) is recorded, while all the unrecorded requests will be cleared together with the recorded one/ones. The

nature of the address event driven pixel design causes an uneven requests workload during the readout process. More pixels may be fired at some gray levels. The delay may mess up the relative histogram between pixels. The compressive acquisition readout method discards the majority of the pixels for each gray level, reducing the readout delay. The state machine enters a JUMP state to relocate to the next "start pixel" and then jump back to the ROWCHK state for the next scanning loop. An exposure time is preset for the control of the termination of the readout procedure. A graphic demonstration of the readout procedure is illustrated in Fig. 2.4 (B). An 8x8 array is taken as an example. The scanning begins from location [0,0], from the top left figure to top right one. It takes 10 clock cycles to scan to location [1,1], which is the second pixel on the second row. A off-chip field-programmable gate array (FPGA) pseudo random number generater is used in the JUMP state. A random number of clocks will be pushed into the horizontal and vertical control chain to shift the readout circuit from the currently selected pixel to another randomly selected pixel. As in this example, it takes 7 clock cycles to jump from [1,1] to [5,5]. If no pixel is readout before the counter achieves the threshold, only [1,1] and [5,5] will be readout, while all the other fired pixels are cleared. The bottom right array shows after a CLR signal is triggered, what the array looks like. It shows the readout pixels from the previous loop, the discarded pixels and newly fired pixels.

### 2.1.3 Image Reconstruction and Simulation

#### Algorithm for Image Reconstruction

The Algorithm presented in this section was provided by Dr. Yuanming Suo and Dr. Trac D. Tran from the Department of Electrical and Computer Engineering at Johns Hopkins University.

For the image acquisition method presented in the previous section, assume that the scene to be detected can be represented by an N-bit resolution grayscale digital image using a matrix  $\mathbf{X}$ , in which the intensity value of each pixel is  $\mathbf{X}_{i,j}$ , where i and j correspond to the horizontal and vertical locations of each pixel, respectively. The histogram of the image can be divided into a group of non-overlapping sets  $\Sigma_k$ , which can be defined as

$$\Sigma_k = \{(i,j) \mid \mathbf{X}_{i,j} \in [I_k, I_{k+1})\},$$

(2.1.1)

where the intensity level  $I_k \in [0, 2^N)$  and  $I_k < I_{k+1}$ . Under compressive acquisition mode, selected pixels are readout during each scanning iteration. The pixels readout during the same iteration will be assigned the same digital number to present the grayscale. Thus, the selected pixels within each set could be used to form a new matrix  $\mathbf{X}_{\Sigma_k}$ , where

$$\mathbf{X}_{\Sigma_{k}} = \begin{cases} \mathbf{X}_{i,j} & if \ (i,j) \in \Sigma_{k} \\ 0 & if \ (i,j) \notin \Sigma_{k} \end{cases}$$

(2.1.2)

Compared with the original matrix  $\mathbf{X}$ , the new sample image  $\mathbf{X}_{\Sigma_k}$  has the values of pixels that do not belong to the set  $\Sigma_k$  replaced by zero. In other words, the

non-readout pixels are set to zero for image reconstruction. This is equivalent to using compressive sensing (CS) with a binary matrix, where the row number is the same as the number of non-zero pixels and the column number is the total number of pixels. For every row, there is only one non-zero value being one and the location of the non-zero value corresponds to the location of non-zero pixel (after the image is stretched into a vector).

Recovering the original image matrix  $\mathbf{X}$  from a partially observed sample image  $\mathbf{X}_{\Sigma_k}$  is an image completion problem, for which we take a dictionary learning based approach. First, we learn a dictionary or basis of image patches  $\mathbf{D}$  using K-SVD [90] such that each image patch  $\mathbf{x}$  (in a vector format) could be modeled using a linear combination of a few dictionary atoms as below,

$$\mathbf{x} = \mathbf{D}\mathbf{a}^{\star} \quad s.t. \quad ||\mathbf{a}^{\star}||_{0} < s, \tag{2.1.3}$$

where  $\ell_0$ -norm counts the non-zero value in the ground-truth sparse coefficient  $\mathbf{a}^*$  and there will be less than s non-zero coefficient values. This model can be naturally extended to a partially sampled version as below,

$$\mathbf{x}_{\Sigma_k} = \mathbf{D}_{\Sigma_k} \mathbf{a}^* \quad s.t. \quad ||\mathbf{a}^*||_0 < s, \tag{2.1.4}$$

where  $\mathbf{x}_{\Sigma_k}$  is the sub-vector formed by extracting values on the active supports within  $\Sigma_k$  and  $\mathbf{D}_{\Sigma_k}$  is the sub-matrix formed by extracting active rows corresponding to  $\Sigma_k$ .

In this work, 69 images [91] are used for dictionary learning. The images are mainly natural scenes, including pictures of flowers, fruits and cars. The training

images are chosen not to be similar to the test images to verify the generality of the proposed approach. After learning such a dictionary  $\mathbf{D}$  from some training images, we will reconstruct the full image  $\mathbf{X}$  from its partial observation  $\mathbf{X}_{\Sigma_k}$  by solving the  $\ell_0$ -norm minimization problem using orthogonal matching pursuit (OMP) [92] or its  $\ell_1$ -norm relaxation in the framework of Convex Optimization [93]. For each sampled patch  $\mathbf{x}_{\Sigma_k}$ , we solve for its optimal sparse coefficient  $\mathbf{a}$  with following formulation,

$$\min_{\mathbf{a}} ||\mathbf{x}_{\Sigma_k} - \mathbf{D}_{\Sigma_k} \mathbf{a}|| \quad s.t. \quad ||\mathbf{a}||_0 < s. \tag{2.1.5}$$

Then each patch is approximated by  $\tilde{\mathbf{x}} = \mathbf{Da}$ . To measure the recovery performance, we adopt Peak signal-to-noise ratio (PSNR) as well as structural similarity index (SSIM) [94]. PSNR is most commonly used to measure the quality of reconstruction of lossy compression techniques while its result might be inconsistent with human eye perception. SSIM improves upon PSNR and captures the context structure in the image better.

#### Simulation Results

The simulation presented in this section was performed by Dr. Milin Zhang from Department of Electrical and Systems Engineering, University of Pennsylvania.

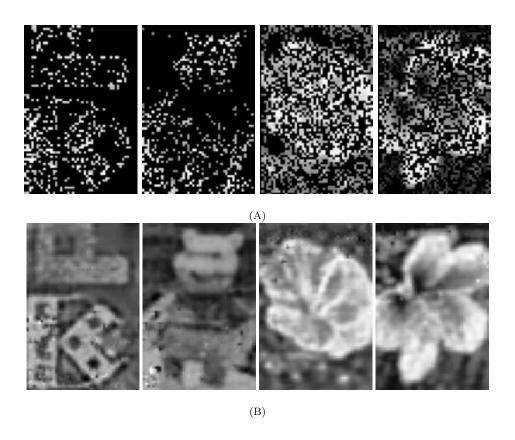

The compression ratio of the algorithm can be calculated from the total amount of members selected from each set. Take the Lena image for example. The resolution of the original image is 24-bit with an array size of  $256\times256$ , as shown in Fig. 2.5 (A). All the pixels are classified into  $2^{13}$  equally divided grayscale sets. N-continuous-

Figure 2.5: (A) A 24-bit  $256\times256$  original sampled image is employed for the demonstration of the proposed image processing. The grayscale is equally divided into  $2^{13}$  levels. N-continuous-pixel-one iteration readout method is used to form (B) the compressive sampled matrix  $I_{smp}(i,j)$ . (C) Reconstructed image from (B). A PSNR of 23dB and a SSIM of 0.835 is achieved. (D) and (E) show the histogram of the raw image and reconstructed image, respectively.

Figure 2.6: Reconstructed sample images with different compression ratios labelled underneath each figure.