University of East London Institutional Repository: <a href="http://roar.uel.ac.uk">http://roar.uel.ac.uk</a>

This paper is made available online in accordance with publisher policies. Please scroll down to view the document itself. Please refer to the repository record for this item and our policy information available from the repository home page for further information.

To see the final version of this paper please visit the publisher's website. Access to the published version may require a subscription.

Author(s): Lota, Jaswinder. Al-Janabi, Mohammed., Kale, Izzet

Article Title: System and circuit level design and analysis of a 16-bit sigma-delta

ADC for a TETRA-2 network mobile station application

Year of publication: 2008

**Citation:** Lota, J. Al-Janabi, M., Kale, I. (2008) 'System and circuit level design and analysis of a 16-bit sigma-delta ADC for a TETRA-2 network mobile station application.' In: 2008 IEEE Instrumentation and Measurement Technology Conference Proceedings. IMTC 2008. IEEE 12-15 May, pp. 663-667.

Link to published version: http://dx.doi.org/10.1109/IMTC.2008.4547119

**DOI:** 10.1109/IMTC.2008.4547119

# **Publisher statement:**

http://www.ieee.org/web/publications/rights/policies.html

# System and Circuit Level Design and Analysis of a 16-Bit Sigma-Delta ADC for a TETRA-2 Network Mobile Station Application

Jaswinder Lota†\*, MIEEE, Mohammed Al-Janabi\*, MIEEE, Izzet Kale\*, MIEEE

†Sepura plc, Radio House, St. Andrew's Road, Cambridge CB4 1GR, UK

\*Applied DSP & VLSI Research Group, Dept of Electronic Systems, University of Westminster, London, UK

jasi@ieee.org, M.Al-Janabi@wmin.ac.uk, kalei@wmin.ac.uk

Abstract: - This paper outlines a comprehensive design evaluation for development of a 16-bit Sigma-Delta (\$\sum\_{\Delta}\$) Analog-to-Digital Converter (ADC) for TETRA-2 Network Mobile Station (MS). A step-by-step design approach is described commencing from system-level evaluation leading to the circuit design, which would serve as a useful reference to designers involved with development of ADCs for wireless equipment.

# I. INTRODUCTION

Terrestrial Trunked Radio (TETRA) [1] is a digital trunked mobile standard developed by the European Telecommunications Standards Institute (ETSI). The purpose of the TETRA is to meet the traditional Professional Mobile Radio (PMR) user organizations and Public Access Mobile Radio (PAMR) applications e.g. public safety (fire, ambulance and rescue services), transportation, utilities (water and electricity) and government (police, border control and military). Like GSM moving to GPRS, EDGE and UMTS/3G, due to increasing user demand for new services and facilities, the end of 2005 saw new standards being finalized as part of TETRA Release 2 [1]. The Mobile Station (MS) for the TETRA-2 applications is a Time Division Multiple Access (TDMA) based OFDM system, capable of supporting channel bandwidths of 25 kHz, 50 kHz, 100 kHz and 150 kHz [1]. A single ADC design solution therefore must be able to support a channel bandwidth of at least 150 kHz. The modulation schemes supported are pi/4 DQPSK, pi/8 D8PSK, 4 QAM, 16 QAM and 64 OAM.

This paper pertains to a systematic design evaluation for development of a 16-bit  $\Sigma$ - $\Delta$  ADC for baseband processing of TETRA-2 MS. Various  $\Sigma$ - $\Delta$  ADC designs have been developed to-date for GSM, CDMA and DECT applications, however the design evaluation for the TETRA-2 MS is novel as the TETRA-2 specifications are still in the process of being finalized by ETSI and to the best knowledge of the authors there is no publication on this in the open literature to date.

This paper will therefore provide a valuable reference for designers involved with the development of TETRA-2 radio equipment. A step-by-step design approach is described commencing from system-level evaluation all the way to the circuit design, which is verified by lengthy

HSPICE simulations. Section II describes the Radio Frequency (RF) Front-End (FE) assumed for the receiver. In section-III the system design is analyzed with the circuit non-idealities and nonlinear stability analysis. This is followed by simulation results in section-IV and conclusions are enumerated in section-V.

#### II. RECEIVER ARCHITECTURE

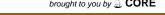

The receiver designs implemented for wireless applications are the superhetrodyne, low-IF or the zero-IF type [2]. The receiver assumed in this study is a conventional superhetrodyne design [2] as seen in Figure 1. The FE consists of the first-RF filter, Low Noise Amplifier (LNA), second-RF filter (II-RF φ) and a mixer. The IF and baseband consist of the IF filter, the Automatic Gain Control (AGC) amplifier with a variable gain and the Quadrature Demodulator that give the In-phase and Quadrature-phase channel inputs to the respective ADCs. The  $\Sigma$ - $\Delta$  modulator outputs the digital samples to the SLINK filters [3], [4]. SLINK filters offer considerable advantages in terms of VLSI/hardware implementation for high sample rates [3], [4], [5]. A single-stage down-conversion from the SLINK filter, to the Root Raised Cosine (RRC) filter is employed to offer sufficient attenuation to the adjacent channel interference.

# III. ADC ARCHITECTURE

The  $\Sigma$ - $\Delta$  ADC architecture is detailed and developed in this section. System level evaluation is undertaken for the design of the Noise Transfer Function (NTF), circuit non-idealities and nonlinear stability analysis. This is followed by the circuit design of the  $\Sigma$ - $\Delta$  modulator.

# A. Channel Bandwidth and System Design.

The channel bandwidth requirements for the receiver determine what Dynamic Range (DR) and Effective Number of Bits ( $E_{NOB}$ ) are achieved for various clock frequencies/Oversampling Ratio (OSR). The DR and the  $E_{NOB}$  are given by [6]:

Figure 1. TETRA-2 Receiver

$$DR = 10 \log \frac{3}{2} \left[ 2^{B} - 1 \right]^{2} \frac{(2L+1)OSR^{2L+1}}{\pi^{2L}}$$

(1)

$$E_{NOB} = \frac{DR - 1.76}{6.02} \tag{2}$$

The minimum required E<sub>NOB</sub> is dictated by the hardware options available in the DSP/FPGA/ASIC for the system and the RF-FE. The parameters in (1) viz., quantizer bits (B), modulator order (L) and OSR (i.e. the clock frequency) can be changed to achieve the required DR for the minimum E<sub>NOB</sub>. For TETRA2 the receiver bandwidth  $f_B$  is given by (3) [1] where  $\beta$  is the bandwidth expansion factor having a value of 1.125, with  $S_BR$  being the symbol rate of 2400 Hz, and Nsc the number of the subcarriers. From (3) the bandwidths obtained are given in Table 1.

$$f_B = \beta \times S_B R \times Nsc \tag{3}$$

| Parameters           | Channel Bandwidth |        |         |         |  |

|----------------------|-------------------|--------|---------|---------|--|

|                      | 25 kHz            | 50 kHz | 100 kHz | 150 kHz |  |

| Nsc                  | 8                 | 16     | 32      | 48      |  |

| f <sub>B</sub> (kHz) | 21.6              | 43.2   | 86.4    | 128.6   |  |

Table 1. TETRA-2 Channel Bandwidth

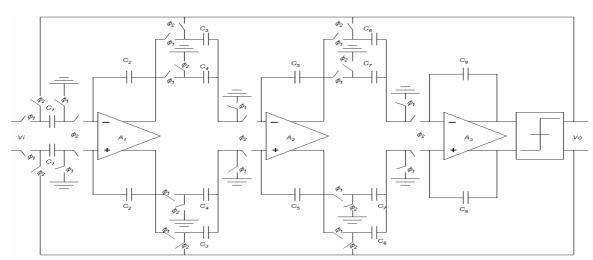

Assuming a minimum required resolution of 16bits, a  $3^{\text{rd}}$ -order  $\Sigma$ - $\Delta$  modulator would require a clock rate of 8.294 MHz, which is feasible to design and implement. The structure of a 3<sup>rd</sup>- order  $\Sigma$ - $\Delta$  modulator meeting the above requirements along with the coefficient values are shown in Figure 2. The single-loop 3<sup>rd</sup>-order structure is chosen since it offers a straightforward simple configuration for evaluation and implementation. The  $\Sigma$ - $\Delta$  modulator is designed with a lowpass NTF using the 'Cookbook' methodology [7]. The required coefficients are obtained after the desired signal scaling.

Figure 2.  $3^{rd}$ -order single-loop  $\Sigma$ - $\Delta$  modulator

#### B. Circuit Non-Idealities.

Incorporating the non-ideal blocks and undertaking system level simulations quantify the degradation in the Signal-to-Noise Distortion (SNDR) as a result of the circuit non-idealities. The various nonideal blocks developed in Simulink/Matlab are used for analysis [8], [9]. As a result of the nonidealities, the net reduction in the SNDR is given in Table 2.

| SI.  | Parameter                   | Reduction in SNDR |

|------|-----------------------------|-------------------|

| I.   | Sampling Jitter: 15 ns      | 1.70 dB           |

| II.  | Switch thermal Noise        | 0.62 dB           |

| III. | Input-referred op-amp       | 1.75 dB           |

|      | noise: 30 $\mu V_{rms}$     |                   |

| IV.  | GBW: 11.5 MHz               | 0.00 dB           |

|      | 100 kHz                     | 28.0 dB           |

| V.   | Slew Rate (SR): 4 V/μs      | 0.00 dB           |

|      | : 1 V/ <i>μ</i> s           | 28 .0dB           |

| VI.  | All non-idealities combined | 4.50 dB           |

Table. 2 Net reduction in SNDR

The resultant reduction in the SNDR due to all of the non-idealities considered together is 4.5 dB. Therefore the required clock frequency of the  $\Sigma$ - $\Delta$ modulator increases to 10.24 MHz from (1) and (2), to account for this reduction in SNDR for a minimum of 16-bit resolution in the baseband, providing us with a safety margin of 5 dB at the same time.

# C. Nonlinear Stability Analyses

The NTF of the

$$\Sigma$$

- $\Delta$  modulator is given by [7]:

$$H(z) = \frac{1 - 3z^{-1} + 3z^{-2} - z^{-3}}{1 - 2.2z^{-1} + 1.688z^{-2} - 0.443z^{-3}}$$

(4)

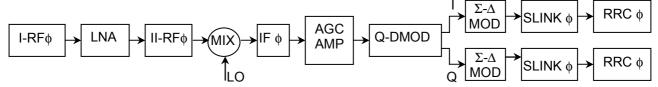

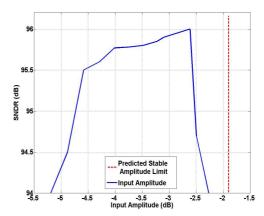

The stability analysis is undertaken using the Noise Amplification Curve (A(K)) proposed in [10] and established for various  $\Sigma$ - $\Delta$  modulators in [11]. The A(K) curve for the  $\Sigma$ - $\Delta$  modulator is plotted in Figure 3. The  $\Sigma$ - $\Delta$  modulator becomes unstable as A(K) approaches the global minimum value of the curve which is 0.9 [10]. This instability sets in when the equivalent quantizer gain K has a value of 0.75. The stable amplitude limits can therefore be predicted for the NTF for DC, sinusoidal and dualsinusoidal inputs from the quantizer gain values and the noise amplification curves as explained in [11], for which the values obtained for this  $\Sigma$ - $\Delta$ modulator are given in section IV.

Figure 3. A(K) Curve

# D. Sigma-Delta Modulator Circuit Design

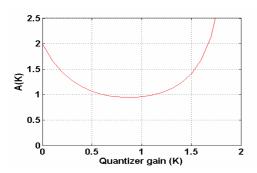

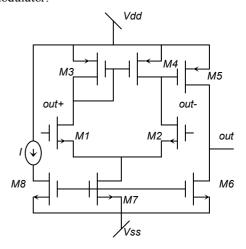

The circuit of the  $3^{\rm rd}$ -order  $\Sigma$ - $\Delta$  modulator was modelled in HSPICE deploying a 0.35  $\mu$ m CMOS process in a differential configuration is shown in Figure 4.  $\phi_1$  and  $\phi_2$  are the complimentary clocks operating at the OSR clock frequency. The op-amp is a single-stage folded-cascode configuration as shown in Figure 5. One bias  $I_{ss}$  provides the drain current of both the input transistors M1, M2 and the cascade devices M3 and M4. The two-stage gain boosting is implemented at the transistors M3 and M4, which increases the output impedance of the differential op-amp. The output impedance in this way can be 'boosted' substantially without stacking more cascade devices on top of M1 and M2.

Figure 5. Folded-cascode op-amp

The comparator is designed to be fast and a simple differential amplifier as circuit shown in Figure 6 fulfils this requirement. The integrator settling speed is the only limiting factor for the sampling rate of the  $\Sigma$ - $\Delta$ modulator. The  $\Sigma$ - $\Delta$ modulator performance is relatively insensitive to the comparator offsets and hysteresis, because these are attenuated by the noise shaping structure of the  $\Sigma$ - $\Delta$ modulator.

Figure 6. Differential Comparator Circuit

# IV. SIMULATION RESULTS

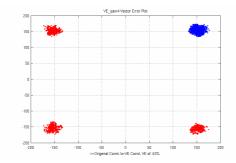

A TETRA-2 OFDM based system has been modeled in SIMULINK for simulations with a RRC filter having a roll-off factor of 0.2 [1]. The 25 kHz channel signal for QAM-4 modulation produced an Error Vector Magnitude (EVM) of 2.5 % without the  $\Sigma$ - $\Delta$  ADC, which increased to 4.7 % with the  $\Sigma$ - $\Delta$  ADC and is plotted in Figure 7. Since the system is TDMA, in order to obtain the EVM perfect synchronization is required between the transmitter and the receiver. This along with the OSR increases the simulation time considerably. Therefore for the other channel bandwidths (50 kHz, 100 kHz & 150 kHz) the RRC output spectrum was measured and was found to be as per the TETRA -2 specifications.

Figure 4. Sigma-Delta Differential Circuit

Figure 7. QAM-4 constellation.

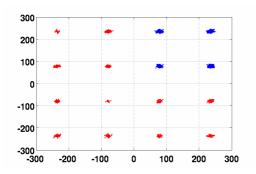

For QAM-16 modulation the EVM is plotted in Figure 8. The % EVM is well below the specified 10% limit for TETRA-2 [1].

Figure 8. QAM-16 Constellation.

As observed accurate mappings are produced as a result of the correct parameter selection in Table 2. The parameters can be varied in order to observe the effects of degradation, but the same has not been quantified as is considered beyond the scope of this paper.

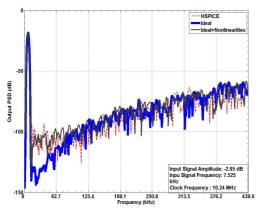

HSPICE transient analyses were undertaken at a clock frequency of 10.24 MHz. It was observed that the predicted non-ideal SNDR response matches very closely to the SNDR response obtained from HSPICE simulations as shown in Figure 9.

Figure 9. Non-ideal  $\Sigma$ - $\Delta$  Modulator Response

To obtain the maximum stable input amplitude limits, simulations were undertaken at 10.24 MHz for which the values obtained are shown in Table.

| SI   | Input Signal | Stable Amplitude Limit |        |

|------|--------------|------------------------|--------|

|      |              | Estimated              | Actual |

| I.   | DC           | 0.60                   | 0.63   |

| II.  | Sinusoidal   | 0.80                   | 0.75   |

| III. | Dual-Sine    | 0.35                   | 0.36   |

Table 3. Stable Amplitude Limits

The stable amplitude limit obtained by HSPICE simulations for the sinusoidal signal at 7.525 kHz is plotted in Figure 10.

Figure 10. Stable Input Amplitude: Sinusoidal Signal

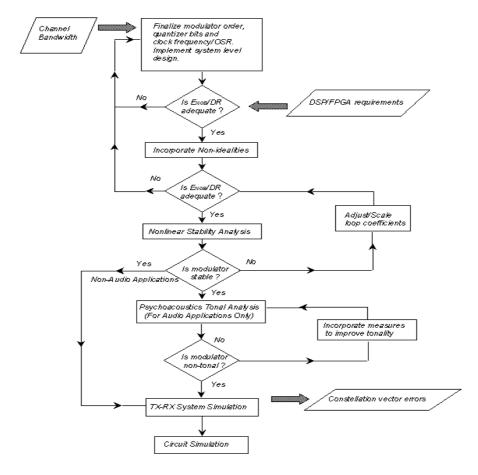

The step-by step approach for the design analysis in this section is given in Figure 11. Although tonal analysis has been included in the methodology, it has not been explained since the application considered is for wireless. The tonal analysis is applicable for audio applications. The tonal analysis is described in details in [12].

# V. CONCLUSIONS

A comprehensive design methodology and performance evaluation of a 16-bit  $\Sigma$ - $\Delta$  ADC for TETRA-2 MS is presented and is validated by system and circuit level simulations. The design approach reported here would provide a valuable reference for designers involved with design of  $\Sigma$ - $\Delta$  ADCs for TETRA-2 receivers.

Figure 11. Steps in Design Methodology

# VI. REFRENCES

- [1] ETSI TETRA-2 Design Specifications ETSI TS 100 392-2 V3.1.1 (2006-09).

- [2] Crols, J. & M.S.J. Steyaert, "Low-IF topologies for High-Perfromance Analog Front-End of Fully Integrated Receivers", *IEEE Trans. Circuits & Systems-II*, vol. 45, issue 3, Mar 1998, pp. 269-282.

- [3] Hogenauer, E. B., "An Economical Class of Digital Filters for Decimation & Interpolation", *IEEE Trans. ASSP*, ASSP-29(2):155-162, 1981.

- [4] Kale, I & R.C.S. Morling, "An Integrated  $\Delta$ - $\Sigma$  Codec for Mobile Telephone Applications", *Proc.*  $38^{th}$  *Midwest Symposium of Circuits & Systems*, vol2, pp. 945, Aug 95.

- [5] Kale, I., R.C.S. Morling & F. Custode, "DSPEngine for Ultra-Low Power AudioApplications", *Proc. IEEE ISCAS 2003*, vol5, pp. 357-360, May 03.

- [6] Medeiro, F. & A. Rodriquez-Vazquez, "Design Considerations For the  $\Delta$ - $\Sigma$  Modulators Beyond ADSL", *Instituto de Microelectronica de Sevilla*, IMSE-CNM (CSIC), Universidad de Sevilla, 41012 Sevilla, Spain.

- [7] Norsworthy, S.R., R. Schreier & G.C. Temes, Delta-Sigma Converters: Theory, Design & Simulation, Wiley-IEEE Press, 1996.

- [8] Brigati, S., F. Francesconi, P. Malcoveti & F. Maloberti, "Modelling  $\Delta$ - $\Sigma$  Modulators Non-Idealities in Simulink", *Proc. IEEE ISCAS*, pp. 384-387, 1999.

- [9] Zare-Hoseini, H., O. Shoai, & I. Kale, "Precise Behavioral Modeling of High-Resolution Switched-Capacitor  $\Sigma$ - $\Delta$  Modulators", *Proc. IEEE IMTC 2004*, Como, Italy, 18-20 May 2004

- [10] Risbo, L., "Stability Predictions for Higher-Order Sigma-Delta Modulators Based on Quasilinear Modeling", *Proc. IEEE ISCAS*, Vol 5, pp. 361–364, 1994.

- [11] Lota, J., Mohammed Al-Janabi & Izzet Kale, "Nonlinear Stability Analysis of Higher-Order  $\Delta$ - $\Sigma$  Modulators for DC & Sinusoidal Inputs", *IEEE Transactions On Instrumentation & Measurement*, Vol 57, Issue 3, pp. 530-542, Mar 2008.

- [12] ] Lota, J., Mohammed Al-Janabi & Izzet Kale, "Tonality Index of Sigma-Delta Modulators: A Psychoacoustics Model Based Approach", *Proc. IEEE ISCAS 2007*, pp. 729 732, May 2007.