University of Parma Research Repository

Estimation of DAC Weighting Capacitors Mismatch in Pipelined ADCs Employing Finite Gain Op-Amps

This is the peer reviewd version of the followng article:

Original

Estimation of DAC Weighting Capacitors Mismatch in Pipelined ADCs Employing Finite Gain Op-Amps / M. Tonelli; G. Chiorboli; C. Morandi. - STAMPA. - (2011), pp. 67-72. ((Intervento presentato al convegno IMEKO TC4 International Workshop on ADC Modelling, Testing and Data Converter Analysis and Design, and IEEE 2011 ADC Forum tenutosi a Orvieto, Italy nel 30 June, 1 July 2011.

Availability: This version is available at: 11381/2350962 since: 2016-07-13T09:18:20Z

*Publisher:* Paolo Carbone, Antonio Moschitta

Published DOI:

Terms of use: openAccess

Anyone can freely access the full text of works made available as "Open Access". Works made available

Publisher copyright

(Article begins on next page)

Proceedings of IMEKO TC4 IWADC 2011

# IMEKO TC4 International Workshop on ADC Modelling, Testing and Data Converter Analysis and Design

and

# IEEE 2011 ADC Forum

Orvieto, Italy - 30 June, 1 July 2011

Archivio fotografico Servizio Comunicazione Istituzionale Regione dell'Umbria, foto di Paolo Ficola.

**General Chair**: Paolo Carbone, University of Perugia, Italy

# Honorary Chairman: Mario Savino (Italy)

# Advisory board

D. Dallet (France)

P. Daponte (Italy)

T. Linnenbrink (USA)

L. Michaeli (Slovak Republik)

J. Mindykowski (Poland)

M. Sedlacek (Czech Republic)

A. Serra (Portugal)

## International programme committee

- D. Agrez (Slovenia)

- E. Balestrieri (Italy)

- J. Blair (USA)

- B. Boyer (USA)

- N. Björsell (Sweden)

- M. Cretu (Romania)

- V. Didenko (Russia)

- C. Eugène (Belgium)

- S. Fakhry (Egypt)

- V. Haasz (Czech R.)

- J. Halttunen (Finland)

- P. Händel (Sweden)

- D. Ilic (Croatia)

- J. Jargon (USA)

- J. Kap Jung (Korea)

- I. Kale (UK)

- O. Kanoun (Germany)

- E. Kayafas (Greece)

- I. Kodjabashev (Bulgaria)

- I. Kollar (Hungary)

G. Kush (USA)

- R. Land (Estonia)

- D. Larson (USA)

- R. Liggiero (USA)

- N. Paulter (USA)

- U. Pogliano (Italy)

- S. Rapuano (Italy)

- P. Ramos (Portugal)

- G. Rocha (Brazil)

- A. Salcenau (Romania)

- J. Saliga (Slovak Republik)

- G. Semenchinsky (Russia)

- S. Max (USA)

- Y. Tesyk (Ukraine)

- S. Tilden (USA)

- S. Turhan (Turkey)

- L. van Biesen (Belgium)

- V. Vujicic (Serbia)

- F. Xu (USA)

Publication Chair: Antonio Moschitta

# Organizing committee:

Antonio Moschitta Emilia Nunzi Pasquale Napolitano

## Editors:

Paolo Carbone, Antonio Moschitta Perugia, Italy, 2011. ISBN: 978-88-906201-0-2

**Copyright:** International Measurement Confederation IMEKO - © 2011.

## Estimation of DAC Weighting Capacitors Mismatch in Pipelined ADCs Employing Finite Gain Op-Amps.

Matteo Tonelli, Giovanni Chiorboli, Carlo Morandi

Dip. di Ingegneria dell'Informazione, University of Parma, V.le Usberti 181/A, 43100, Parma ITALY Phone: (39) 0521 905809 Fax: (39) 0521 905822 E-Mail: {giovanni.chiorboli,carlo.morandi}@unipr.it

*Abstract* - A D/A subconverter (DASC) error correction scheme based on weighting capacitor rotation is adapted to account for finite op-amp gain. Simulations show that reasonable estimates of capacitor mismatch can be obtained even if the actual gain is replaced by a nominal gain differing by as much as a factor of two.

DASC capacitor mismatch might therefore be estimated in the foreground at power-up, and most part of the corresponding mismatch noise and mismatch-induced interstage gain error might be cancelled, possibly delegating to a background calibration the task of correcting the remaining interstage gain error, induced by finite op-amp gain and drift with temperature.

## I. Introduction

Pipelined A/D converters are the preferred choice for low-power applications requiring high speed and mediumhigh resolution, when a moderate amount of latency is tolerated.

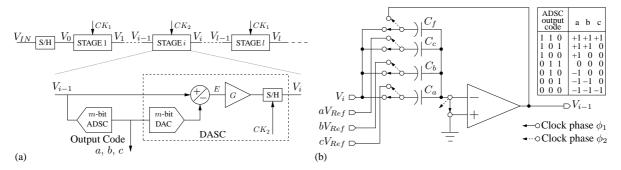

The architecture of a pipelined A/D converter is shown in Figure 1. Each stage in the pipeline includes an analog-todigital sub-converter (ADSC) and a digital-to-analog sub-converter module (DASC), including a DAC, a subtractor, a residue amplifier and a sample-and-hold amplifier.

Figure 1. (a) A pipelined A/D converter. (b) Simplified model of a 2.5-bit DASC with 4 equal weighting capacitors. During clock phase  $\phi_2$ , capacitors  $C_a$ ,  $C_b$  and  $C_c$  are connected, respectively, to  $aV_{Ref}$ ,  $bV_{Ref}$ , and  $cV_{Ref}$ .

Each stage in the pipeline processes the residue  $V_{i-1}$  from the previous stage.  $V_{i-1}$  is measured by an analog-todigital sub-converter ADSC, whose output drives an *m*-bit DAC. If the DAC output level corresponds to the centre of the quantisation cell where the input is classified, the output *E* of the subtractor block represents the quantisation error of the ADSC. *E* is then amplified by a suitable gain *G*, so that all the stages in the pipeline may operate on signals of comparable level, and fed to a S/H which provides residue  $V_i$  to the following stage.

ADSC non-linearity can be easily eliminated by digital correction [1], which requires a few additional decision levels in the ADSC and output levels in the DASC. The discussion which follows refers to a 2.5-bit ADSC (G = 4) with 6 decision levels, driving a 2.5-bit DAC with 7 output levels by means of three, 2-bit output signals a, b, c.

A simplified DASC circuitry is shown in Figure 1(b) in single-ended form. Unlike the correction of ADSC non linearities, correction of interstage gain errors and DASC non linearity errors poses significant challenges. Mismatch between the DASC weighting capacitors contributes both to the so called "mismatch noise" and to interstage gain error. Several techniques reported in the literature [2, 3, 4, 5, 6] allow estimating mismatch, and canceling its effects provided the op-amp gain is infinite; a recent survey of the state of the art can be found in [7].

The method proposed in [6] for the calibration of a 2.5 bit DASC requires rotating the position of the four nominally equal weighting capacitors at each sampling instant, according to predefined pseudo-random-noise (PN) sequences.

By estimating the correlation between the measured residue of the stage to be calibrated and the PN sequences, it is possible to quantify the errors of the weighting elements and thus compute, in real time, digital correction terms to be added to the raw ADSC output. This allows achieving a considerable improvement of the noise floor, if the op-amp gain may be considered infinite.

The technology trend towards low supply voltages and low power consumption encourages, on one hand, the use of op-amps with low and inaccurate voltage gain, and on the other hand the use of weighting capacitors of the smallest size compatible with noise specifications, in order to reduce the op-amp bias current for equal clock frequency. Thus interstage gain error is no longer determined by capacitor mismatch only, but also by the uncertainty affecting op-amp gain, while mismatch noise becomes more relevant since relative mismatch increases with decreasing capacitor size.

Thanks to capacitors' stability, capacitor mismatch alone can be approximately determined at power-up even if a poor estimate of op-amp gain is available: this enables partial cancellation of mismatch noise and approximate correction of that part of interstage gain error which depends upon mismatch. The task of correcting the remaining interstage gain error, induced by finite op-amp gain and gain drift with temperature, can then be delegated to a background calibration technique like that described in [8].

This paper reconsiders the mismatch calibration procedure described in [6] taking finite op-amp gain into account, and demonstrates that useful mismatch estimates can be obtained even if the op-amp gain is known with poor approximation.

### II. Capacitors' mismatch estimation in the case of finite op-amp gain

With reference to the switched capacitor DASC of Figure 1(b) during clock phase  $\phi_1$ , input voltage  $V_{i-1}$  is processed by the 2.5-bit flash ADSC, which provides the three 2-bit output signals a, b, and c described in the insert of the figure. In the same phase the G = 4 identical capacitors are pre-charged to  $V_{i-1}$ , so that the total charge stored on the four capacitors is  $Q = V_{i-1}(C_a + C_b + C_c + C_f)$ . In phase  $\phi_2$ , the bottom switch is connected to the amplifier's inverting input, capacitor  $C_f$  is placed in the feedback loop while the other capacitors are connected to ground or to  $\pm V_{Ref}$  depending on the ADSC outputs a, b, and c,  $V_{Ref}$  being the reference voltage.

Leaving  $C_a = C_0(1 + \varepsilon_a)$ , where  $C_0$  is the average of the four capacitances and  $\varepsilon_a$  is the relative weighting error, and similarly for  $C_b, C_c, C_f$ , it turns out that  $\varepsilon_a + \varepsilon_b + \varepsilon_c + \varepsilon_f = 0$ . Assuming an op-amp gain  $A_v$ , the residue is  $V_i = V_{i-1} \cdot C_0 G/(C_f + C_0 G/A_v) - V_{Ref} \cdot (aC_a + bC_b + cC_c)/(C_f + C_0 G/A_v)$ . By recalling that the quantisation error of the ADSC is  $E = V_{i-1}/V_{Ref} - (a + b + c)/G$ , the residue, normalised to  $V_{Ref}$ , becomes

$$\widehat{V}_i \stackrel{\triangle}{=} V_i / V_{Ref} = \frac{GE}{1 + \varepsilon_f + \frac{G}{A_v}} - \frac{a\varepsilon_a + b\varepsilon_b + c\varepsilon_c}{1 + \varepsilon_f + \frac{G}{A_v}}$$

(1)

Here, G = 4 is the nominal gain of the 2.5-bit DASC, and the difference  $\hat{V}_i - GE$  represents the error arising from capacitor mismatch in the DASC and finite op-amp gain. Finite op-amp input capacitance  $C_p$  and unity-gain bandwidth, neglected here, should be taken into account [9] if comparable to  $C_0G$ , to the sampling frequency, respectively. Op-amp gain variation with input signal level can probably be covered by combining capacitor mismatch estimation in the foreground with an interstage gain calibration procedure operating in background mode and covering non-linear effects in the interstage amplifier [8].

Eq. (1) can be used for the correction of DASC errors, once estimates of  $\varepsilon_a, \varepsilon_b, \varepsilon_c, \varepsilon_f$  and of the op-amp gain  $A_v$  are available.

By linearizing (1), under the assumption of small  $\varepsilon$ 's and  $G \ll A_v$ ,

$$\widehat{V}_i = V_i / V_{Ref} \cong GE - \left( a\varepsilon_a + b\varepsilon_b + c\varepsilon_c + GE\varepsilon_f + G^2 \frac{E}{A_v} \right).$$

<sup>(2)</sup>

The calibration procedure proposed in [6] assigns, at each sampling instant, the role of  $C_a$ ,  $C_b$ ,  $C_c$ , and  $C_f$  to a different arrangement, obtained by rotation, of the four capacitors  $\{C_1, C_2, C_3, C_4\}$  physically present in the DASC. The assignment is controlled by two zero-mean, PN sequences  $P_0$  and  $P_1$ , with values  $\pm 1$ , according to Table 1. By simple algebra, following step by step the procedure described in [6],  $\varepsilon_a$  may be written in the form

$$\varepsilon_a = \frac{1}{G} \left\{ -P_0(\Delta_2 + \Delta_3) - P_1 \Delta_1 + P_1 P_0(\Delta_2 - \Delta_3) \right\}$$

(3)

where

$$\Delta_1 = \varepsilon_1 + \varepsilon_2 - \varepsilon_3 - \varepsilon_4; \qquad \Delta_2 = \varepsilon_1 - \varepsilon_2; \qquad \Delta_3 = \varepsilon_3 - \varepsilon_4. \tag{4}$$

| $P_1$ | $P_0$ | $C_a$ | $C_b$ | $C_c$ | $C_f$ |

|-------|-------|-------|-------|-------|-------|

| -1    | -1    | $C_1$ |       |       | $C_4$ |

| -1    | +1    | $C_2$ |       | $C_4$ | $C_1$ |

| +1    | -1    | $C_3$ | $C_4$ | $C_1$ | $C_2$ |

| +1    | +1    | $C_4$ | $C_1$ | $C_2$ | $C_3$ |

Table 1. Capacitor rotation scheme

Similar expressions can be derived for  $\varepsilon_b, \varepsilon_c, \varepsilon_f$ : by substituting these in (2)

$$\widehat{V}_{i} = \frac{V_{i}}{V_{Ref}} = GE\left(1 - \frac{G}{A_{v}}\right) - \frac{1}{G}\left[P_{0}(\Delta_{2} + \Delta_{3})(-a + b - c + GE) + + P_{1}[\Delta_{1}(-a + c) + (\Delta_{2} - \Delta_{3})(b - GE)] + P_{1}P_{0}[(\Delta_{2} - \Delta_{3})(a - c) + \Delta_{1}(b - GE)]\right].$$

(5)

Note that, taking the expectation value of both sides of (5), it is found that

$$\mathcal{E}\left\{GE\right\} = (1 - G/A_v)^{-1} \mathcal{E}\left\{\widehat{V}_i\right\},\tag{6}$$

since the terms in the large square bracket are products of PN sequences like  $P_0, P_1$  and  $P_0P_1$  with sequences, like (-a + b - c + GE) or (-a + c) which depend only upon the ADSC and the input signal, and are uncorrelated with the previous ones. It is thus natural to consider  $\overline{GE} = \hat{V}_i/(1 - \frac{G}{A_v})$  as a noisy estimate of GE.

Assuming at first that (-a+b-c) and GE are independent processes and that  $P_1$  and  $P_0$  are orthogonal sequences, so that  $\mathcal{E} \{P_1P_0\} = 0$ , if the zero-distance correlation A between the sequence of residues  $\hat{V}_i$  and the sequence  $P_0(-a+b-c)$  is computed, only the term multiplying the unknown  $\Delta_2 + \Delta_3$  survives:

$$A = \mathcal{E}\left\{\widehat{V}_{i}P_{0}(-a+b-c)\right\}$$

$$= -\frac{(\Delta_{2}+\Delta_{3})}{G}\left[\mathcal{E}\left\{(-a+b-c)^{2}\right\} + \mathcal{E}\left\{-a+b-c\right\} \cdot \mathcal{E}\left\{GE\right\}\right].$$

(7)

Quite similarly

$$B = \mathcal{E}\left\{\widehat{V}_{i}P_{1}(-a+c)\right\}$$

$$= -\frac{\Delta_{1}}{G}\mathcal{E}\left\{(-a+c)^{2}\right\} - \frac{(\Delta_{2}-\Delta_{3})}{G} \cdot \left[\mathcal{E}\left\{b(-a+c)\right\} - \mathcal{E}\left\{-a+c\right\}\mathcal{E}\left\{GE\right\}\right],$$

(8)

assuming (-a + c) and GE as independent, and

$$C = \mathcal{E}\left\{\widehat{V}_{i}P_{1}P_{0}(a-c)\right\}$$

$$= -\frac{\Delta_{1}}{G}\left[\mathcal{E}\left\{b(a-c)\right\} - \mathcal{E}\left\{a-c\right\}\mathcal{E}\left\{GE\right\}\right] - \frac{(\Delta_{2}-\Delta_{3})}{G}\mathcal{E}\left\{(a-c)^{2}\right\}.$$

(9)

Now  $\mathcal{E} \{GE\}$  can be replaced by the expression in (6),  $A_v$  by its nominal value  $A_{vnom}$ , and the expectation values can be computed as exponential moving averages requiring knowledge of the sequences a, b, c, available at the ADSC output, and  $\hat{V}_i$ , the calibrated output of the back-end of the considered stage. At this point the three linear equations (7), (8), (9) may be solved in terms of the unknowns  $\Delta_1, \Delta_2 + \Delta_3$  and  $\Delta_2 - \Delta_3$ . In the following, this approach will be referred to as procedure "five", since it leads to a system matrix with five non zero elements.

However, as it will be shown in the next section, the mismatch estimates obtained by this procedure are fair, but not sufficient to improve to the desired level the performance of the pipeline converter. Thus, the validity of the assumptions behind (7) (8) and (9) was questioned.

It was remarked that, since during real world operation the input signal is unknown, the only possibility is replacing GE by the estimate  $\overline{GE}$ . Correlations (7), (8) and (9) were therefore evaluated, in simulation, removing any assumption of incorrelation between the amplified quantization error  $GE \simeq \overline{GE}$ , the ADSC outputs a, b, c, and the PN sequences  $P_0$  and  $P_1$ . A, for instance, was evaluated as

$$A = \mathcal{E}\left\{\widehat{V}_{i}P_{0}(-a+b-c)\right\}$$

=  $\mathcal{E}\left\{P_{0}(-a+b-c)\overline{GE}(1-G/A_{v})\right\} - \frac{(\Delta_{2}+\Delta_{3})}{G}\left[\mathcal{E}\left\{(-a+b-c)(-a+b-c+\overline{GE})\right\}\right] + \frac{\Delta_{1}}{G}\left[\mathcal{E}\left\{P_{0}P_{1}(-a+b-c)(-a+c)\right\} + \mathcal{E}\left\{P_{1}(-a+b-c)(b-\overline{GE})\right\}\right] + \frac{(\Delta_{2}-\Delta_{3})}{G}\left[\mathcal{E}\left\{P_{0}P_{1}(-a+b-c)(b-\overline{GE})\right\} + \mathcal{E}\left\{P_{1}(-a+b-c)(b-\overline{GE})\right\}\right]$  (10)

Now  $\overline{GE}$  is proportional to  $\hat{V}_i$  and therefore depends on the capacitor permutation, and thus on  $P_0$  and  $P_1$ , and also depends on a, b, c. Therefore, the expectations appearing in (10) can make all the three coefficients of the unknowns  $\Delta_1, \Delta_2 + \Delta_3$  and  $\Delta_2 - \Delta_3$  non negligible, and indeed this was confirmed by simulations. Similar considerations hold when B and C are evaluated without incorrelation assumptions.

A problem arises from the first terms on the r.h.s., which become coincident with the term on the l.h.s. if  $\overline{GE}$  is used in place of GE, making the system homogeneous, i.e. with null trivial solutions. With some surprise, however, it was experimentally verified that, if the first term at the r.h.s. of (10) and the likes is ignored (forced to zero), a system leading to a considerable improvement of the mismatch estimates is obtained. This second approach, supported only by the experimental evidence of improved performances, will hereafter be referred to as procedure "nine", since all the nine system matrix elements may be non negligible, depending on the mismatch and on the signal statistics.

Once the solutions  $\overline{\Delta_1}$ ,  $\overline{\Delta_2 + \Delta_3}$  and  $\overline{\Delta_2 - \Delta_3}$  are known, by combining them with (3) and companions, expressions of the estimates  $(1 + \varepsilon_f)$  and of  $(a\varepsilon_a + b\varepsilon_b + c\varepsilon_c)$  in terms of  $P_0$ ,  $P_1$ ,  $\overline{\Delta_1}$ ,  $\overline{\Delta_2 + \Delta_3}$ , and  $\overline{\Delta_2 - \Delta_3}$  are easily obtained, so that a rough estimate of GE may be obtained from (1), by replacing the op-amp gain with its nominal value. Note that the computation of the mismatch estimates  $\overline{\Delta_1}$ ,  $\overline{\Delta_2 + \Delta_3}$  and  $\overline{\Delta_2 - \Delta_3}$ , and the accumulations required to estimate the expected values can be carried out only at power-up. Only the calculations related to the correction of mismatch noise (and, in case, some calculations related to interstage gain calibration) require real time processing and substantially contribute to power dissipation.

### **III. Simulation results**

The performance of the procedure for the estimation of mismatch parameters  $\Delta_1$ ,  $\Delta_2 + \Delta_3$  and  $\Delta_2 - \Delta_3$  in the case of finite gain of the op-amp was investigated, using Matlab-Simulink, by functional simulation of a pipeline formed by a 2.5-bit front-end stage followed by an ideal 12 bit back-end converter. Blocks describing the operation of the front-end were implemented using a floating point representation of the analog data within the pipeline. They include the ADSC with the error correction logic described in [1], the DASC/subtractor/amplifier and the capacitor rotation logic. Expectation values were estimated as exponential averages.

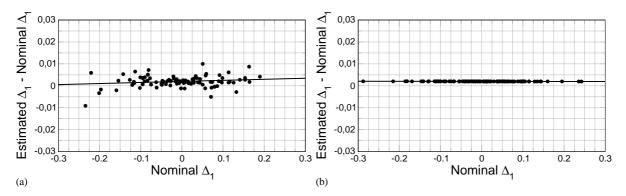

A first set of simulations aims at comparing the estimation error of procedures "five", Figure 2(a), and "nine", Figure 2(b), with different capacitor sets. The figures summarize the results of 100 simulations where the values of the four nominally equal weighting capacitors were extracted from a gaussian distribution with a standard deviation of 5% of the nominal value, and for each simulation the same PN sequences  $P_0$ ,  $P_1$  were used, with seeds chosen as large prime numbers. The dots represent the  $\Delta_1$  estimation error, i.e. the difference between the value of  $\overline{\Delta_1}$ ,

Figure 2. The graphs report the estimation error for mismatch parameter  $\Delta_1$  as a function of  $\Delta_1$  for  $A_v = A_{vnom} = 10^6$ , obtained (a) using procedure "five"; (b) using procedure "nine".

estimated using an averager time constant w of  $10^5$  time ticks, and the true value of  $\Delta_1$ , known in simulation, as a function of the true value of  $\Delta_1$ . It appears that the estimates obtained with procedure "nine" are affected by a much smaller dispersion than those of procedure "five". The two graphs correspond to a high value of the op-amp gain,  $A_v = A_{vnom} = 10^6$ , a condition in which the finiteness of the op-amp gain has limited impact. Besides a certain amount of dispersion, the estimation error includes an offset (intercept of the regression line) of about  $2 \times 10^{-3}$  plus a relative error (slope of the regression line) of  $-2 \times 10^{-4}$  in the case of Figure 2(b).

In a similar experiment, where for each set of capacitors different PN sequences were used, with seeds chosen at random, the offset ( $\approx 1.1 \times 10^{-4}$ ) virtually disappears, while the experimental dots are nearly as dispersed as those obtained by procedure "five" in Figure 2(a). This suggests that the offset in Figure 2(b) may be related to the specific sequences  $P_0$ ,  $P_1$  used, and of course, that the PN sequences should not be chosen at random.

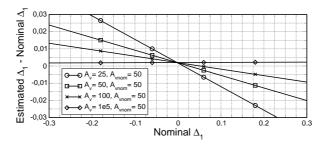

Figure 3. The regression lines for the  $\Delta_1$  estimation error obtained with procedure "nine" for different values of  $A_v$  and a fixed  $A_{vnom}$ .

Figure 3 represents the regression lines of the  $\Delta_1$  estimation error, obtained with procedure "nine" when  $A_{vnom} = 50$  and  $A_v = 25, 50, 100, 1 \times 10^5$ , respectively, and demonstrates the strong influence of the true op-amp gain  $A_v$  on the relative error contribution: the largest the op-amp gain, the smallest the relative error term. For each value of  $A_v$ , similar slopes are obtained for  $\Delta_2$  and  $\Delta_3$ ; more noisy results were obtained with procedure "five". For both procedures "five" and "nine", on the contrary, the influence of the nominal op-amp gain  $A_{vnom}$  is minimal. The fact that the estimation error is not minimal when  $A_v = A_{vnom}$  is rather surprising, anyway the results suggest that the relative error term is always negative and can be made small at desire, by ensuring that the actual op-amp gain never drops below a certain value.

Note that the estimates discussed so far were obtained using an ideal 12-bit back-end. In order to investigate the impact of a non-ideal back-end, simulations were carried out with back-ends with no linearity errors but different resolutions. It turned out that mismatch estimates are unaffected, provided the back-end resolution is larger than 6-bit and the input signal determines an amplified residue spanning most of the back-end input range.

In summary, irrespective of nominal op-amp gain, even with a low op-amp gain, the estimated values of the mismatch parameters are reasonably close to the exact values known in simulation. Therefore, the estimates thus obtained can be used to directly evaluate GE according to (1), in order to reduce mismatch noise, and to achieve an improvement of the complete converter performance.

Alternatively, mismatch estimation can be performed in the foreground, at power-up, and the estimates obtained can be used to approximately correct mismatch noise, while interstage gain calibration may be delegated to a background technique like that in [8], capable of tracking gain drifts.

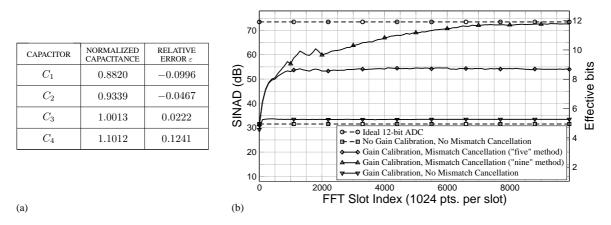

In an experiment according to this last approach, mismatch estimation was performed in the first  $2 \times 10^6$  conversion cycles, and the mismatch parameters were evaluated according to procedures "five" or "nine". Afterwards, the four capacitors were held in fixed positions, and the obtained estimates of  $\varepsilon_1$ ,  $\varepsilon_2$ ,  $\varepsilon_3$ ,  $\varepsilon_4$  were stored in memory.

The background interstage gain calibration algorithm was then activated, with mismatch noise subtraction according to (1) enabled.

The experiment simulated a 2.5-bit stage using a high nominal gain op-amp, with the four nominally equal weighting capacitors shown in 4(a), followed by an ideal 12-bit back-end, representing the rest of the pipeline after proper calibration, for a total of 14-bit. Assuming a target resolution of 12-bit, the converter performance was evaluated in terms of SINAD ratio calculated on the 12 MSBs of the output word. The interstage gain calibration was carried out with averaging time constant  $w = 2 \times 10^5$  time ticks.

Figure 4(b) shows the evolution with time of the SINAD ratio of the entire converter as the estimate of interstage gain improves. The bottom line represents the SINAD of the converter if no calibration is performed; the top line the SINAD of an ideal 12-bit converter. The second line from the bottom shows that interstage gain calibration alone, without mismatch cancellation, brings limited improvement. The next line demonstrates a relevant improvement when interstage gain calibration is combined with mismatch noise cancellation according to procedure "five".

Figure 4. Mismatch cancellation effect. (a) Capacitor test set. (b) The SINAD transient evolution during interstage gain calibration.

The best result however is obtained by interstage gain calibration combined with mismatch noise cancellation according to procedure "nine": this last combination allows to recover about three additional effective bits, and thus to achieve the target SINAD.

## **IV.** Conclusions

A correlation-based procedure for mismatch parameters estimation proved its effectiveness even in the case of limited gain op-amps. A procedure with improved performances was defined on the basis of heuristic considerations. By combining foreground mismatch parameters estimation with background interstage gain calibration, real time tracking of op-amp gain drift is possible, and significant performance improvements can be obtained.

## References

- [1] S.H. Lewis et al., "A 10-b 20-MSample/s analog-to-digital converter," *IEEE J. Solid-State Circuits*, vol.27, pp.351-358, 1992.

- [2] I. Galton, "Digital cancellation of D/A converter noise in pipelined A/D converters," *IEEE Transactions on Circuit and Systems II*, vol.47, pp.185-196, 2000.

- [3] E. Siragusa and I. Galton, "A digitally enhanced 1.8-V 15-bit 40-MSample/s CMOS pipelined ADC," *IEEE J. Solid-State Circuits*, vol.39, pp.2126-2138, 2004.

- [4] P.C. Yu et al, "A 14-b 40MSample/s pipelined ADC with DFCA," Proc. IEEE Int. Solid-State Circ. Conf., ISSCC 2001, San Francisco, CA, pp.136-137, 2001.

- [5] S. Shehata, P.C. Yu, and R.Gharpurey, "Pipelined analog to digital converter using digital mismatch noise cancellation," *United States Patent*, US 6456223 B1, September 2002.

- [6] G. Chiorboli et al, "DAC calibration by weighting capacitor rotation in a pipelined ADC," Proc. 3rd IASTED Int. Conf. CIRCUITS, SIGNALS AND SYSTEMS, Marina del Rey, CA, pp.31-35, Oct.24-26,2005.

- [7] A.J. Gines, E.J. Peralias, and A. Rueda, "A survey on digital background calibration of ADCs," European Conference on Circuit Theory and Design, ECCTD 2009, pp.101-104, 23-27 Aug. 2009.

- [8] J.P. Keane, P.J. Hurst, and S.H. Lewis, "Background Interstage Gain Calibration Technique for Pipelined ADCs," *IEEE Transactions on Circuits and Systems I*, vol.52, pp. 32-43, 2005.

- [9] M. Parenti et al, "Systematic design and modelling of high-resolution, high-speed pipeline ADCs," *Measure*ment, vol.37, pp. 344-351, 2005.