#### Augsburg University Idun

**Zyzzogeton Posters**

Undergraduate

2018

#### How do Topological Properties of Ripple-Carry Adders Affect Time Delay?

Alexander Boukal *Augsburg University*

Follow this and additional works at: https://idun.augsburg.edu/zyzzogeton Part of the <u>Physics Commons</u>, and the <u>Systems Architecture Commons</u>

#### **Recommended** Citation

Boukal, Alexander, "How do Topological Properties of Ripple-Carry Adders Affect Time Delay?" (2018). Zyzzogeton Posters. 4. https://idun.augsburg.edu/zyzzogeton/4

This Book is brought to you for free and open access by the Undergraduate at Idun. It has been accepted for inclusion in Zyzzogeton Posters by an authorized administrator of Idun. For more information, please contact bloomber@augsburg.edu.

# How do Topological Properties of Ripple-Carry Adders Affect Time Delay? Alexander Boukal, Dr. Lanzerotti, Dr. Engebretson

## Abstract

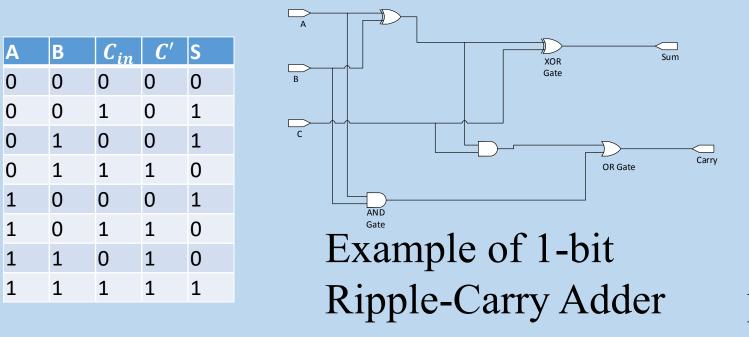

This poster presents topological properties of N-bit ripple-carry adders and the effects of their topology, specifically their genus, on the speed of current flow. An adder is a very simple computer that takes input numbers (0 and 1) from logic gates and then adds them together. To create a ripple-carry adder, we take N number of adder circuits and arrange them in parallel. We differentiate between two kinds of adder circuits: half adders and full adders. Half adders are non-planar (has loops) circuits with genus = 1 that let us perform elementary addition operations using logic gates. Full adder circuits are non-planar circuits with genus = 2 that comprise three inputs (A, B, and the Carry input) and two outputs (Sum and the Carry output), sending the carry input from one adder to the next. We can think of the genus of a circuit as the number of loops a surface needs in order for a circuit to be drawn on it without any crossings.

#### Introduction

We hypothesized that if we increase the number of bits, then the speed for the ripplecarry adder would decrease (time delay become maximized) as well because a circuit with more pieces has longer routes for current to flow. It had previously been shown by Sam Swanson's research that the genus of an N-bit ripple-carry adder increases as the number of bits increases. This led to us thinking that there must be a direct relationship between the genus of a N-bit ripple-carry adder circuit and the speed of the circuit's current flow. From this we thought that we could construct ripple-carry adder circuits that maximize the speed of current flow while using fewer bits.

# Method

First, we constructed a truth table.

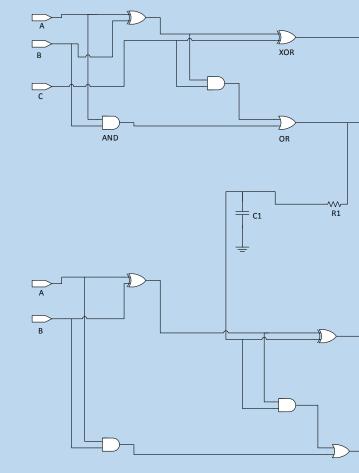

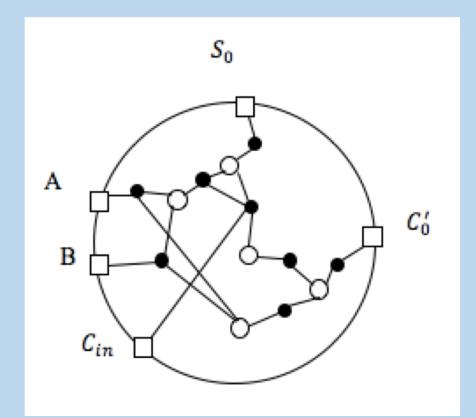

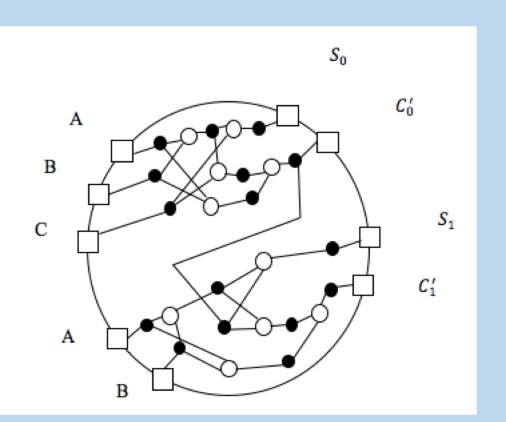

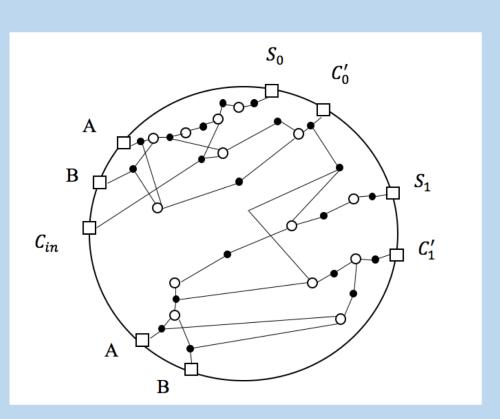

Example of 2-bit Ripple-Carry Adder

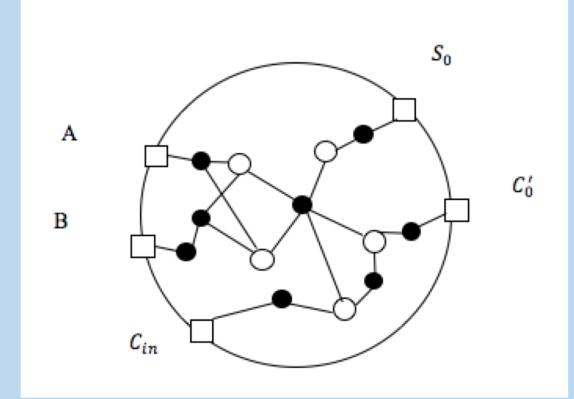

Next, we constructed a 1-bit and a 2-bit ripple-carry adder circuit simulation using OrCAD. We began by considering a 1-bit full adder with inputs A, B, a carry-in bit C, and outputs called Sum and Carry. Next, we constructed a 1-bit ripple-carry adder using OrCAD Capture CIS. First, we created a schematic design of our ripple-carry adder circuit. This is done by first opening up a schematic design template and adding necessary circuit parts and wires. We processed our design using part references and prepared our design for simulation. Following that, we created and edited a simulation profile. This was followed by running the simulation. From here, we added in any resistors and capacitors, connecting them with the wire bridging 2 adjacent full ripplecarry adders. Then, we constructed a 2-dimensional circuit map for each adder circuit. We tracked the number of vertices, edges, and faces of each circuit. For each of the ripple-carry adder circuits, we created a circuit map detailing the vertices and edges.

#### Method Continued

From this we calculated the genus. Following that, we added a resistor to each of the circuits in the OrCAD simulation and experimented with varying the resistance in the ripple-carry adder circuits to see how that affects the time-delay of the current flow. Finally, we used Microsoft Visio to create models of the circuits we simulated in OrCAD.

#### Results

Topological properties were extracted for ripple-carry adders increases, so does the time delay of the device. constructed from full adder cells. Two ripple-carry adders with N = 1Acknowledgements bit and two with N = 2 bits are shown. The genus calculated from each circuit is shown in the table. The results show that the genus I would like to acknowledge Dr. Lanzerotti and Dr. equals 2N, where N is the number of bits in a ripple-carry adder. The Engebretson for their roles in advising me in my research, worst-case delay in a ripple-carry adder is proportional to the number Eric Strom in helping with technical issues surrounding of bits N. This is because the carry-input bit propagates from the OrCAD software, and Alex Sushko (an alumnus) for giving least significant bit position all the way to the most significant bit. me pointers in the construction of ripple-carry adders. Furthermore, the results indeed show that as the genus is increased, the time delay increases proportionally.

1-bit Ripple-Carry Adder with XOR,AND,OR gates g = 2

Time Delay for the above 2-bit ripple-carry adder = 5.0275us

1-bit Ripple-Carry Adder with NAND, AND, OR gates

g = 4

Time Delay for the above 2-bit ripple-carry adder = 5.0420us

2-bit Ripple-Carry Adder with XOR,AND,OR gates g = 2Time Delay for the above 2-bit

2-bit Ripple-Carry Adder with NAND, AND, OR gates

g =4

ripple-carry adder = 10.0550us

Time Delay for the above 2-bit ripple-carry adder = 10.0840us

#### Summary/Conclusions

Research in the area of topological constraints and their effects extends previous work that sought how the genus value changes as the number of bits is increased for ripplecarry adder circuits. For any N-bit ripple-carry adder, the genus as studied in this research, is equal to 2N. We found that using fewer bits we can maximize the speed, and therefore minimize the time delay of current flow. The results show that as the genus of a ripple-carry adder circuit

## Future Work

Future work will focus on extracting topological properties and their effects on the time delay of current flow of increasingly complex integrated circuits.

## References

(1)Vernizzi, G., M. Y. Lanzerotti, J. Kujawski, and A. Weatherwax. "Topological Constraints for E. F. Rent's Work on Microminiature Packaging and Circuitry." *Topological* Constraints for E. F. Rent's Work on Microminiature Packaging and Circuitry - IEEE Xplore Document. N.p., 13 Aug. 2013. Web. 22 June 2017.

(2)OrCAD Flow Tutorial, Product Version 16.6, Cadence Design Systems Inc., San Jose, CA, October 2012 (3)"PCB Design Forums." Cadence Community. Ed. Cadence Design Systems, Inc. Cadence Design Systems, Inc., 2017. Web. 23 June 2017.

(4)PSpice Community. "Model Library." *Logic Gates PSpice*. N.p., 2016. Web. 23 June 2017.

# AUGSBURG UNIVERSITY<sub>®</sub>