## Old Dominion University ODU Digital Commons

Electrical & Computer Engineering Theses & Disssertations

**Electrical & Computer Engineering**

Summer 2017

### The Efficacy of Programming Energy Controlled Switching in Resistive Random Access Memory (RRAM)

David Malien Nminibapiel Old Dominion University

Follow this and additional works at: https://digitalcommons.odu.edu/ece\_etds

Part of the <u>Electronic Devices and Semiconductor Manufacturing Commons</u>, and the <u>Nanoscience and Nanotechnology Commons</u>

#### Recommended Citation

Nminibapiel, David M.. "The Efficacy of Programming Energy Controlled Switching in Resistive Random Access Memory (RRAM)" (2017). Doctor of Philosophy (PhD), dissertation, Electrical/Computer Engineering, Old Dominion University, DOI: 10.25777/b5dj-7c62

https://digitalcommons.odu.edu/ece\_etds/21

This Dissertation is brought to you for free and open access by the Electrical & Computer Engineering at ODU Digital Commons. It has been accepted for inclusion in Electrical & Computer Engineering Theses & Disssertations by an authorized administrator of ODU Digital Commons. For more information, please contact digitalcommons@odu.edu.

# THE EFFICACY OF PROGRAMMING ENERGY CONTROLLED SWITCHING IN RESISTIVE RANDOM ACCESS MEMORY (RRAM)

by

David Malien Nminibapiel B.S. December 2010, Old Dominion University M.S. August 2012, Old Dominion University

A Dissertation Submitted to the Faculty of Old Dominion University in Partial Fulfillment of the Requirements for the Degree of

DOCTOR OF PHILOSOPHY

ELECTRICAL AND COMPUTER ENGINEERING

OLD DOMINION UNIVERSITY August 2017

Approved by:

Helmut Baumgart (Director)

Kin P. Cheung (Member)

Gon Namkoong (Member)

Zhili Hao (Member)

Christopher Bailey (Member)

ABSTRACT

THE EFFICACY OF PROGRAMMING ENERGY CONTROLLED SWITCHING IN

RESISTIVE RANDOM ACCESS MEMORY (RRAM)

David Malien Nminibapiel Old Dominion University, 2017

Director: Dr. Helmut Baumgart

Current state-of-the-art memory technologies such as FLASH, Static Random Access

Memory (SRAM) and Dynamic RAM (DRAM) are based on charge storage. The semiconductor

industry has relied on cell miniaturization to increase the performance and density of memory

technology, while simultaneously decreasing the cost per bit. However, this approach is not

sustainable because the charge-storage mechanism is reaching a fundamental scaling limit.

Although stack engineering and 3D integration solutions can delay this limit, alternate strategies

based on non-charge storage mechanisms for memory have been introduced and are being

actively pursued.

Resistive Random Access Memory (RRAM) has emerged as one of the leading

candidates for future high density non-volatile memory. The superior scalability of RRAMs is

based on the highly localized active switching region and filamentary conductive path. Coupled

with its simple structure and compatibility with complementary metal oxide semiconductor

(CMOS) processes; RRAM cells have demonstrated switching performance comparable to

volatile memory technologies such as DRAMs and SRAMs. However, there are two serious

barriers to RRAM commercialization. The first is the variability of the resistance state which is

associated with the inherent randomness of the resistive switching mechanism. The second is the

filamentary nature of the conductive path which makes it susceptible to noise.

In this experimental thesis, a novel program-verify (P-V) technique was developed with the objective to specifically address the programming errors and to provide solutions to the most challenging issues associated with these intrinsic failures in current RRAM technology. The technique, called Compliance-free Ultra-short Smart Pulse Programming (CUSPP), utilizes subnanosecond pulses in a compliance-free setup to minimize the programming energy delivered per pulse. In order to demonstrate CUSPP, a custom-built picosecond pulse generator and feedback control circuit was designed. We achieved high (10<sup>8</sup> cycles) endurance with state verification for each cycle and established high-speed performance, such as 100 ps write/erase speed and 500 kHz cycling rate of HfO<sub>2</sub>-based RRAM cells. We also investigate switching failure and the short-term instability of the RRAM using CUSPP.

Copyright, 2017, by David Malien Nminibapiel, All Rights Reserved.

This dissertation is dedicated to my parents, Clement Kojo Nminibapiel and Victoria Assibi Nminibapiel and to my siblings Victor, Edna, Elsie and Shequita.

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to thank Dr. Helmut Baumgart for giving me the opportunity to pursue both a Masters and a Ph.D. degree under his guidance. On countless occasions in my graduate school career, he has been supportive and has provided me opportunities that I will be forever grateful for.

I would like to thank Dr. Kin P. Cheung for his guidance and patience in my dissertation research. He accepted me into his group at the National Institute of Standards and Technology (NIST) and has always encouraged me to be the best researcher I can be.

I would like to thank the other members of my Ph.D. committee, Dr. Zhili Hao, Dr. Gon Namkoong and Dr. Christopher Bailey for their guidance.

I want thank Dr. Jason Campbell, Dr. Jason Ryan and Dr. Dmitry Veksler for their unwavering willingness to assist me during my research work. I would have not been successful otherwise.

I am thankful to Dr. Pragya Shrestha, Dr. Ji-Hong Kim, Dr. Asahiko Matsuda and Vasileia Georgiou at NIST for their assistance during my research work. Particularly, I would like to express my gratitude to Dr. Shrestha for her support and guidance.

I would like to thank Dr. Yaw Obeng and Dr. Albert Jones at NIST for his advice and assistance, and Dr. Kai Zhang at the Applied Research Center in Newport News, Virginia for his support and assistance during the course of my graduate career.

I would like to thank my parents and siblings for their never-ending love, support and encouragement and lastly, I would like to thank Ms. Safia Hurst for her support and encouragement.

#### TABLE OF CONTENTS

|     |                    |                                                             | Page |

|-----|--------------------|-------------------------------------------------------------|------|

| LIS | ST OF FI           | GURES                                                       | viii |

| Ch  | apter              |                                                             |      |

| 1.  | INTRO              | DDUCTION                                                    | 1    |

|     | 1.1                | Background                                                  |      |

|     | 1.2                | Origins of Filamentary Resistive Switching                  | 9    |

|     | 1.3                | HfO <sub>2</sub> -based RRAM                                |      |

|     | 1.4                | Dissertation Objective                                      |      |

| 2.  | EXPERIMENTAL SETUP |                                                             | 26   |

|     | 2.1                | HfO <sub>2</sub> RRAM Device                                | 26   |

|     | 2.2                | 100 picosecond Pulse Generator                              | 27   |

|     | 2.3                | CUSPP Control Circuit                                       | 38   |

|     | 2.4                | Compliance-free Ultra-short Smart Pulse Programming (CUSPP) | 44   |

|     | 2.5                | Summary                                                     | 50   |

| 3.  | CYCLI              | ING ENDURANCE                                               | 51   |

|     | 3.1                | Experimental Details                                        | 51   |

|     | 3.2                | Results and Discussion                                      |      |

|     | 3.3                | Summary                                                     |      |

| 4.  | SHOR               | Γ-TERM INSTABILITY                                          | 67   |

|     | 4.1                | Experimental Details                                        | 67   |

|     | 4.2                | Results and Discussion                                      | 68   |

|     | 4.3                | Summary                                                     | 89   |

| 5.  | CONC               | LUSIONS AND FUTURE WORK                                     | 91   |

| RE  | FEREN              | CES                                                         | 101  |

| Vľ  | ТΔ                 |                                                             | 113  |

#### LIST OF FIGURES

| Figure Page                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

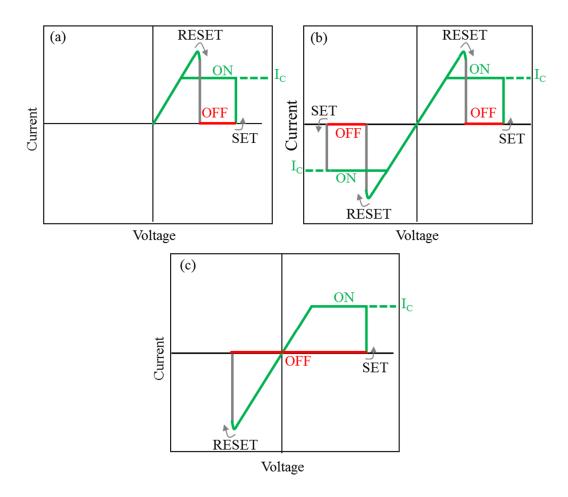

| 1. Schematic of a) unipolar, b) nonpolar and c) bipolar switching modes of RRAM cells under voltage sweep                                                      |

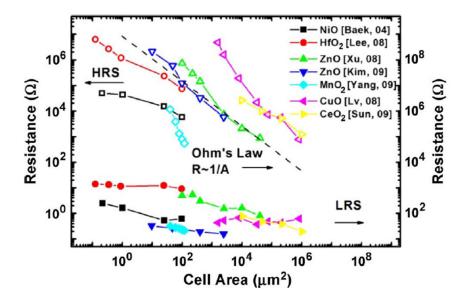

| 2. LRS and HRS dependence on cell area for different RRAM stacks [13]                                                                                          |

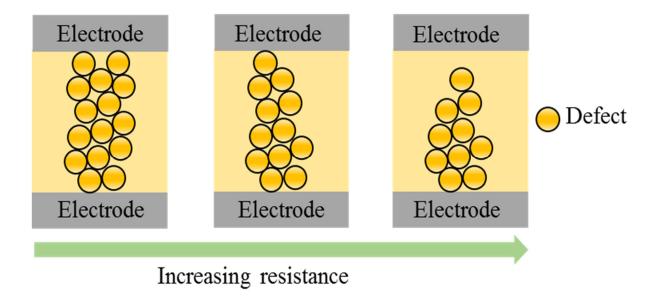

| 3. Illustration of the possible physical configuration of the CF in an RRAM cell                                                                               |

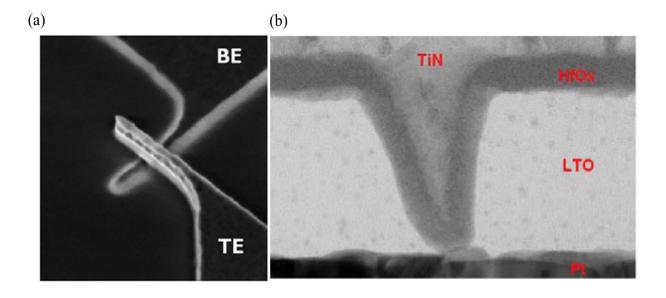

| 4. (a) Top view SEM image of TIN/Hf/HfOx/TiN cell. Cell area is defined at the crossing of TE (10 nm line width) and BE (10 nm line width) [33]                |

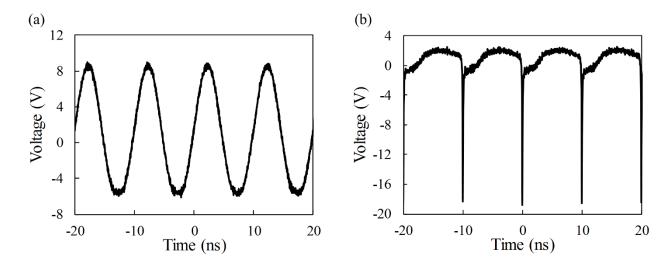

| 5. (a) Input to and (b) output from a step recovery diode comb generator                                                                                       |

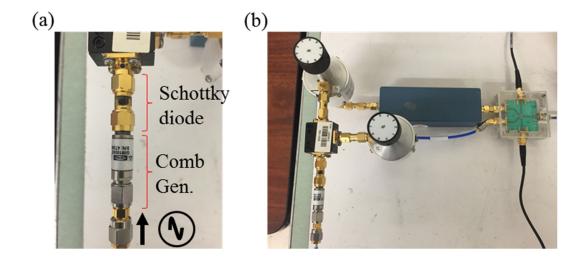

| 6. (a) Commercial comb generator and engineered connector to house the Schottky diode 31                                                                       |

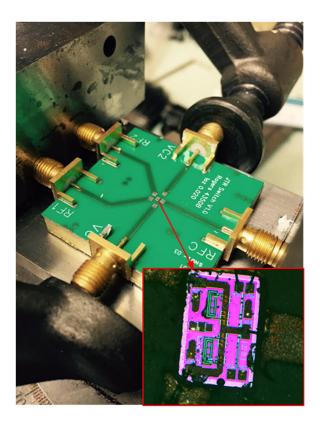

| 7. PCB layout for the high-speed switch with a brass base designed to provide mechanical support, electrical and thermal contact to the backside of the switch |

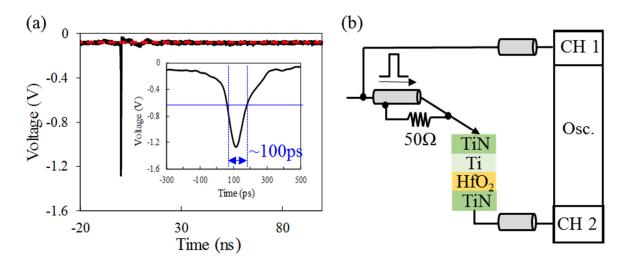

| 8. (a) Typical V <sub>RESET</sub> pulse offset by a low DC voltage(V <sub>READ</sub> ) used for read                                                           |

| 9. (a) Displacement current before (blue) and after (red) the RRAM forming event                                                                               |

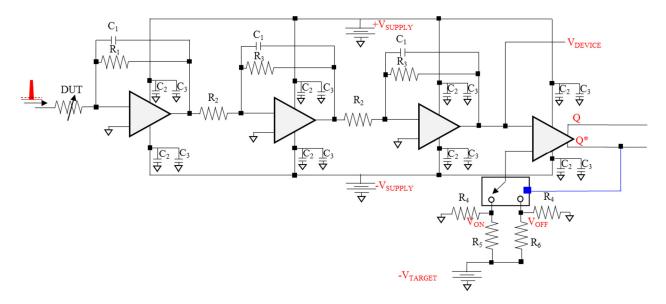

| 10. Schematic circuit diagram of CUSPP control circuit. Specific R values are dependent on the desired amplifier gain, $V_{ON}$ and $V_{OFF}$ .                |

| 11. Picture of CUSPP control circuit. 40                                                                                                                       |

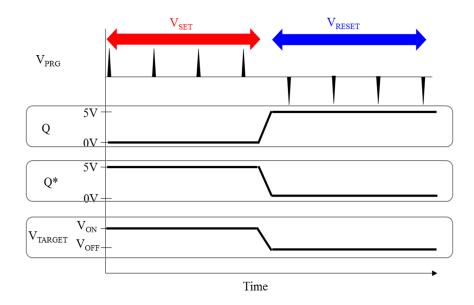

| 12. Timing diagram schematic of control signals and programming pulse during CUSPP operation                                                                   |

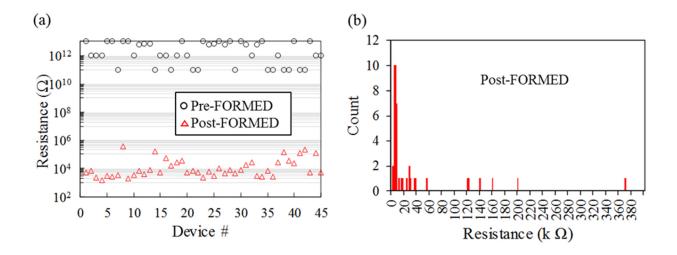

| 13. (a) Typical Pre-FORMED and Post-FORMED resistance levels                                                                                                   |

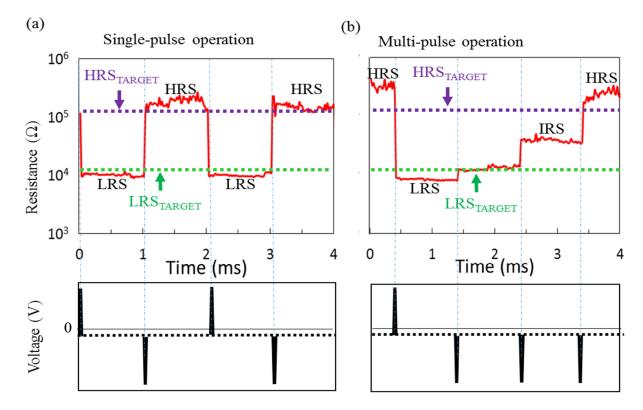

| 14. Representative time traces of the resistance evolution (red) during (a) single pulse operation and (b) multi-pulse operation modes                         |

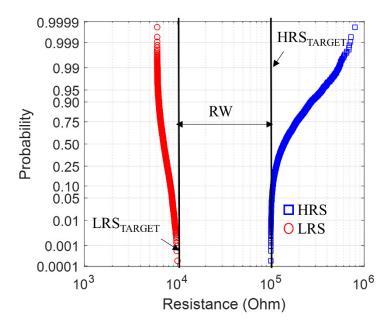

| 15. Probability distribution of LRS and HRS obtained after 2000 cycles using CUSPP 47                                                                          |

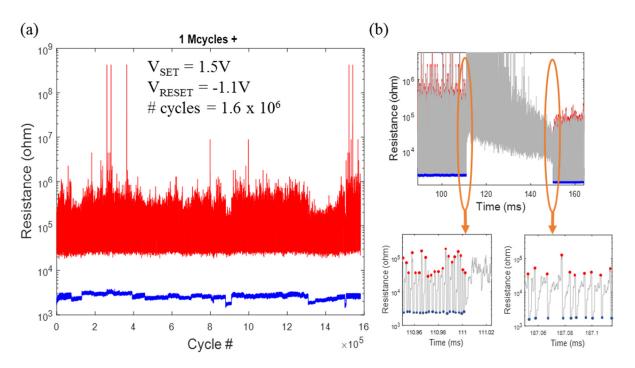

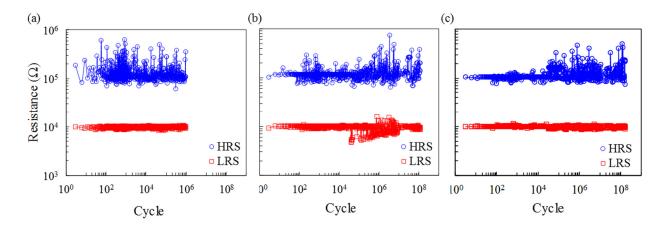

| 16. (a) $10^6$ endurance between 3 k $\Omega$ and 30 k $\Omega$ target LRS and HRS, respectively using CUSPP                                                   |

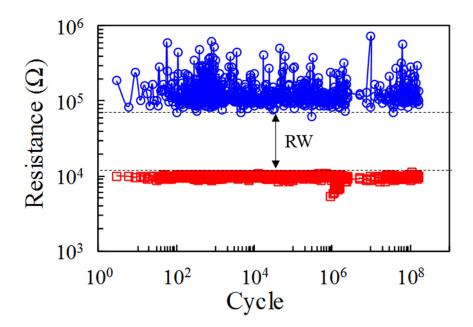

| 17. Endurance performance of the bipolar HfO <sub>2</sub> RRAM device using CUSPP53                                                                            |

| Figure                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|

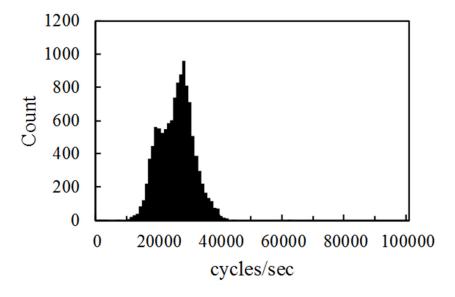

| 18. Cycling rate distribution acquired for 12,000 sec of cycling using CUSPP 55                                                                        |

| 19. (a) Evolution of cycling rate during the endurance study                                                                                           |

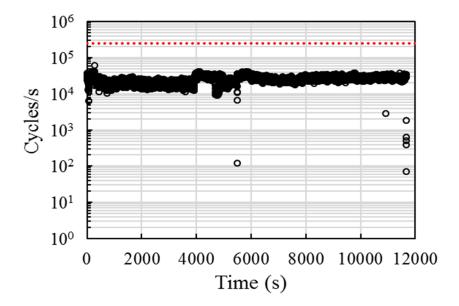

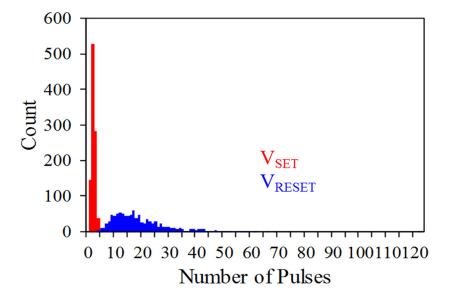

| 20. Distribution of number of V <sub>SET</sub> /V <sub>RESET</sub> pulses during normal operation for 1000 cycles 57                                   |

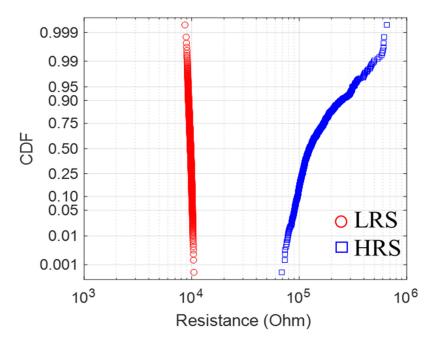

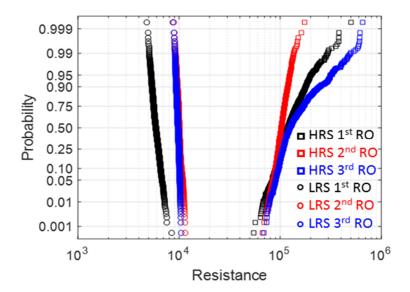

| 21. Cumulative distribution of 1000 cycles of LRS and HRS during normal switching operation                                                            |

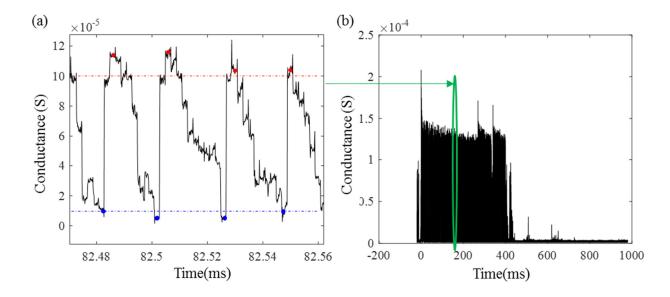

| 22. Conductance time trace showing the (a) normal cycling behavior of the RRAM and (b) occurrence of stuck HRS failure                                 |

| 23. Endurance using +1V V <sub>SET</sub> of a single cell after the (a) first, (b) second and (c) third recovery operation (RO)                        |

| 24. LRS and HRS distributions for 1000 cycles obtained after three different recovery operations using RP2                                             |

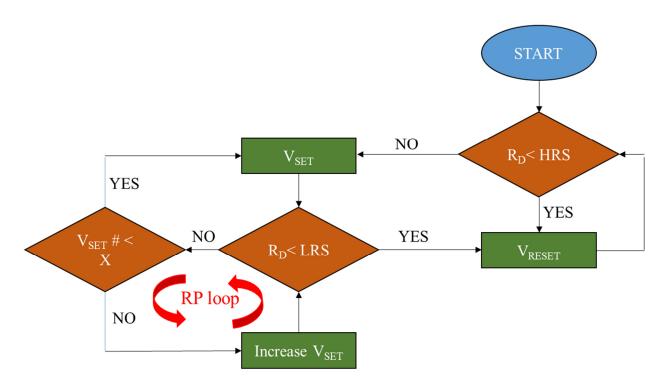

| 25. Flow chart of the proposed programming algorithm to achieve high endurance yield on a RRAM wafer                                                   |

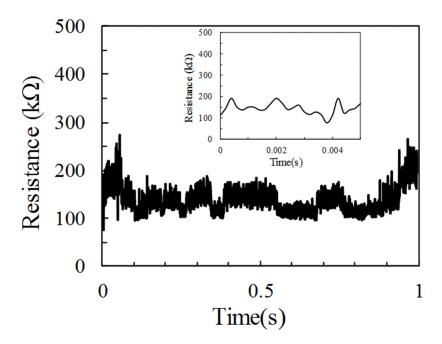

| 26. HRS read trace captured during normal cycling between LRS and HRS                                                                                  |

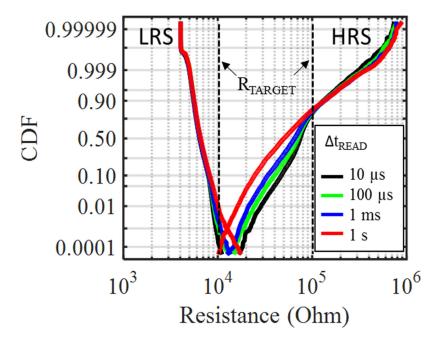

| 27. Cumulative distribution (10 <sup>4</sup> cycles) of LRS and HRS measured 10 μs, 100 μs, 1 ms and 1 s post-programming                              |

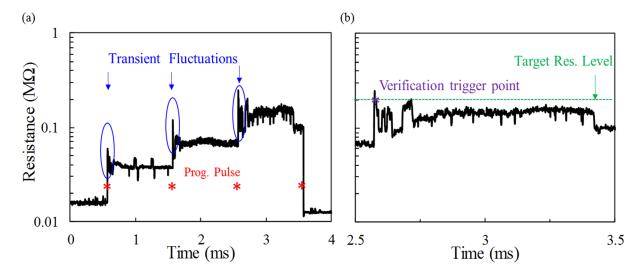

| 28. (a) Measured resistance ( $V_{READ} = -8mV$ ) as a function of time for a complete cycle                                                           |

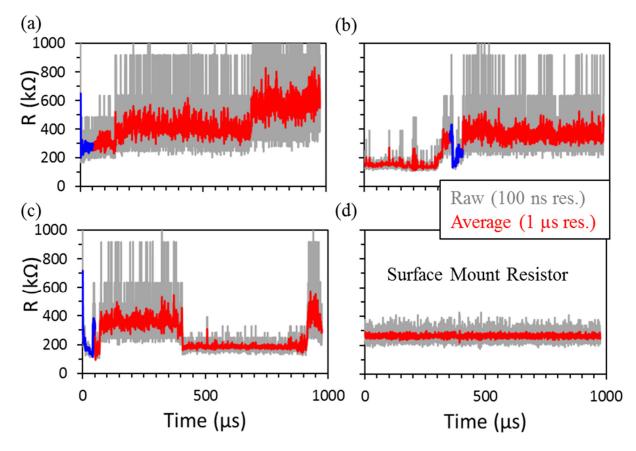

| 29. (a), (b) and (c) Representative HRS read traces captured during normal operation between HRS and LRS                                               |

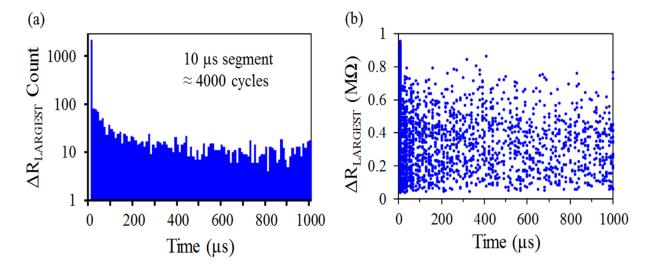

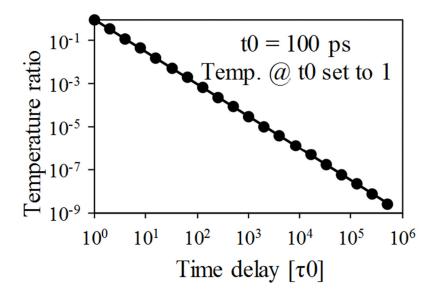

| 30. (a) Distribution of time segments (10 $\mu$ s) containing the largest fluctuation, $\Delta R_{LARGEST}$ 76                                         |

| 31. Distribution of time segments (100 µs long) containing the largest fluctuation                                                                     |

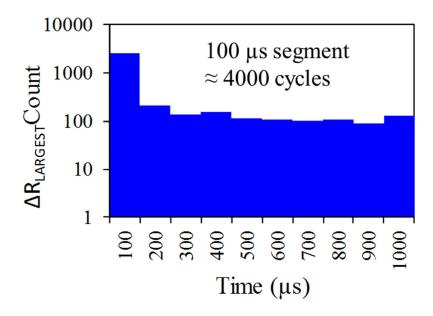

| 32. Distribution of time segments (10 µs long) in which the minimum resistance point (HRS <sub>MIN</sub> ) in HRS occurred                             |

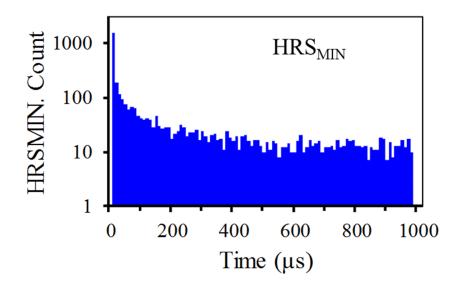

| 33. Calculated temperature drop ratio referenced to an initial temperature as a function of multiples of characteristic time $\tau 0$ (pulse duration) |

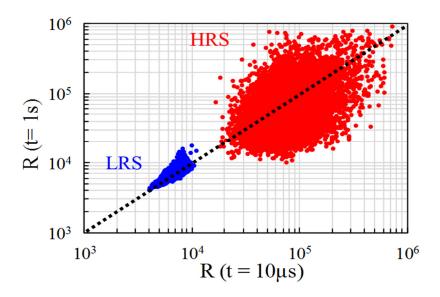

| 34. Time lag representation of HRS and LRS taken at 10 µs and 1s post-programming                                                                      |

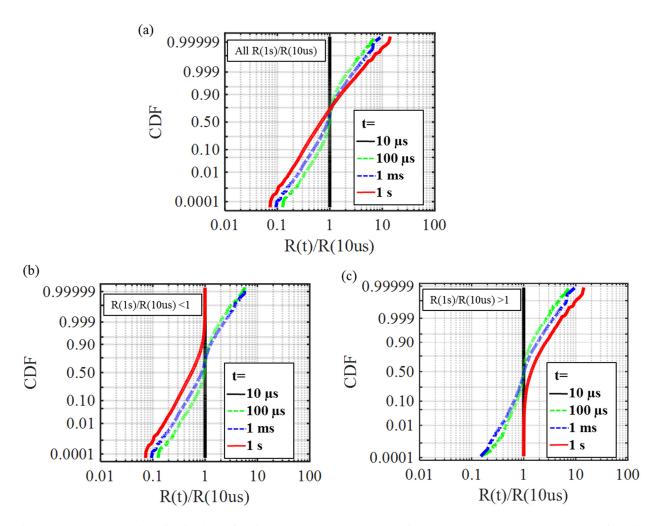

| 35. (a) Cumulative distribution of resistance ratio, $R(t)/R(10 \mu s)$ for $t = 10 \mu s$ , $100 \mu s$ , $1 ms$ and $1 s$ for all cycles             |

| gure                                                                                                                                                                                                                                           | ge |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

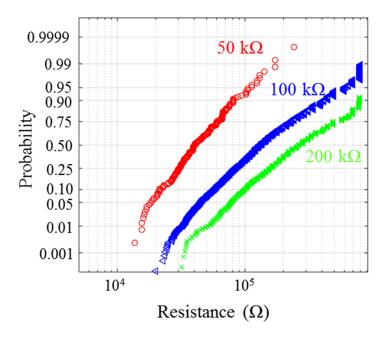

| 5. HRS distributions for different target resistances                                                                                                                                                                                          | 36 |

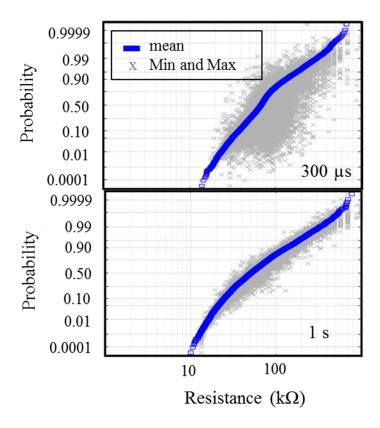

| 7. Cumulative distribution of HRS for 300 µs and 1 s post programming                                                                                                                                                                          | 38 |

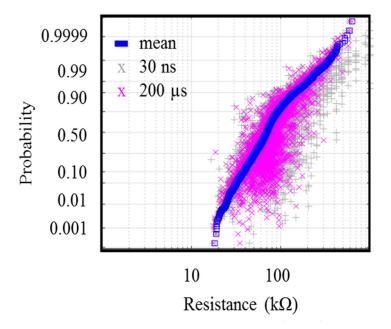

| 3. Increased read averaging of the resistance distributions for 200 µs (purple) vs. 30 ns (gray) duces the amplitude of fluctuations, but the widely distributed temporal distribution of the actuations limits the usefulness of this tactic. | 39 |

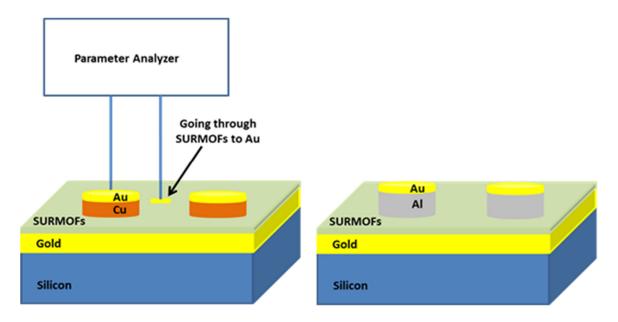

| 9. Illustration of SURMOF device test structure and measurement setup                                                                                                                                                                          | €  |

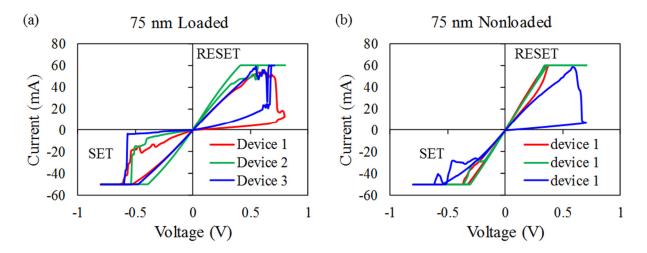

| ). Measured I-V curve for SURMOF device A (a) loaded with ferrocene and (b) pristine non aded                                                                                                                                                  | 96 |

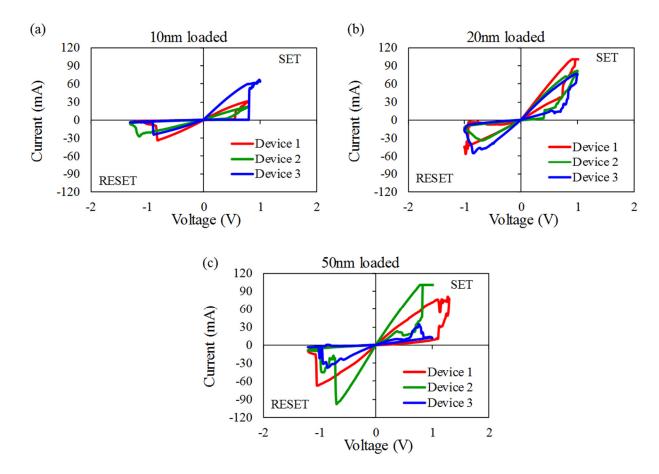

| 1. Measured I-V curve for device B with loaded SURMOF films of thickness (a)10 nm, 20 nm and (c) 50 nm                                                                                                                                         | €7 |

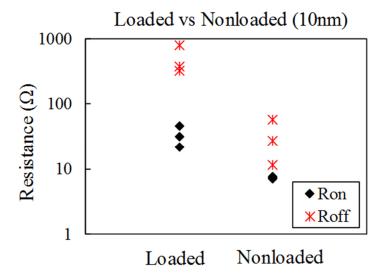

| 2. ON-state and OFF-state of loaded and pristine nonloaded 10 nm SURMOF devices                                                                                                                                                                | 98 |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Background

Resistive switching (RS) refers to the phenomenon where insulators, under an applied electrical field, can undergo reversible resistance change from their normal insulating state to an abnormal conductive state. This phenomenon was first discovered in the 1960s [[1-4] and was proposed for use in memory applications. However, memory technology based on RS remained primarily a field of scientific study for the next 30 years, mainly because of the advancements of Si-based memory technology. It saw a re-emergence in the late 1990s in perovskite oxides [5-7]. Shortly thereafter, Baek et al. [8] demonstrated a robust memory device based on a binary transition metal oxide insulating layer. This breakthrough renewed interest in memory devices based on the RS mechanism [9-12]. These devices are called Resistive Random Access Memory (RRAM).

In its basic configuration, an RRAM cell comprises an insulating layer sandwiched between two conducting layers in a capacitor-like structure. The conducting layers are typically either a metal or a conductive nitride; the insulating-layer material, however, varies across a wide range of organic, inorganic, and hybrid materials [13, 14]. The working principle of these devices is based on modulating the conductivity of the metal-insulator-metal (MIM) structure by applying the appropriate bias. When this bias is removed, the cell retains the resistance level, making RRAM a non-volatile memory. The active region of RS can be as large as the entire insulating layer or a 1-dimensional (1-D) conductive path that electrically connects the two conductors [15]. The former is usually observed in Phase Change RAM (PCRAM) [16]. RRAM devices based on a 1-D conductive path are desirable because of the promise of extremely high

scalability enabling continued growth in density for future technology nodes [17]. The conductive filament (CF) is widely accepted to be composed of metal atoms or reduced oxides [18, 19]. The localized nature and composition have been verified through various methods, which include conductive atomic force microscopy (C-AFM) [20], high resolution transmission electron microscopy (TEM) [21], electron energy loss spectroscopy (EELS) [22] and X-ray absorption spectromicroscopy [23].

In a single bit cell, two distinct states are programmed: high resistance state (HRS) and low resistance state (LRS), representing the low (0) and high (1) states, respectively. The transition from HRS to LRS is referred to as SET while the opposite transition from LRS to HRS is referred to as RESET. Prior to performing SET or RESET or cycling, a FORMING step is required. V<sub>FORM</sub>, V<sub>SET</sub> and V<sub>RESET</sub> represent the voltages required for FORMING, SET and RESET. The read-out operation is performed with a low voltage (V<sub>READ</sub>), which should not disturb the resistance state.

Traditionally, switching modes are classified as either unipolar or bipolar. This classification is based on the sensitivity of the switching direction on the bias polarity. Unipolar devices can SET and RESET at the same fixed polarity, while bipolar devices can only SET and RESET at opposite polarity. The switching mode is not an intrinsic property of the cell but can be controlled by the stack properties and programming currents [24-26]. This explains the appearance of a so-called non-polar mode where switching direction is independent of polarity [13]. In regard to implementation, unipolar devices have the advantage of requiring a simpler programming algorithm since polarity is fixed. All switching modes are schematically shown in Figure 1.

Filament formation in the FORMING and SET step is accompanied by an inrush of current which must be controlled to avoid permanent damage [27]. Usually, a current-limiting element such as a resistor or transistor is placed in series with the RRAM to set a current compliance (Ic) limit. Ic is not only necessary to prevent thermal damage; it also serves to control the post-FORMED/SET state resistance value [28]. The inrush of current is a result of the abrupt change of the RRAM cell from high resistance to low resistance under the programming voltage. Ideally, the compliance element should limit the maximum allowable current that flows through the cell. However, this function can be undermined by the response time of the system. If the transition time of the RRAM cell is faster than the RC time of the system, a current overshoot is inevitable. This overshoot current exceeds the current limit set by the compliance element and therefore defeats the purpose of the compliance element [29]. To minimize current overshoot, strict control of parasitics in the system is required. For this reason, advanced RRAM cells either included an additional layer to serve as a series resistor or are integrated directly on the transistor gate.

Figure 1. Schematic of a) unipolar, b) nonpolar and c) bipolar switching modes of RRAM cells under voltage sweep.

#### **Cell level**

Several aspects of the resistive switching mechanism in RRAMs have led to its emergence as a serious candidate for future nonvolatile memory. Conversely, these aspects also have given rise to most of the issues still hindering the full commercialization of RRAM-based memory chips. The wide variety of material systems which display RS enables an equally wide application space for RRAM [14]. RRAMs based on novel hybrid insulator materials like metal organic framework (MOF) films [30], and novel transparent electrode materials like Indium tin oxide (ITO) [31] have been demonstrated. In addition, switching performance is highly sensitive

to the cell stack and structure, which allows for stack engineering strategies to improve performance [32]. For instance, TaOx-based devices tend to exhibit superior retention [33], while conductive-bridge RRAM devices using electrochemically active electrodes tend to display large, resistance-memory windows [34]. On the other hand, because there are several stack options, it is challenging to construct models that can fully explain the different aspects of resistive switching. Without these models, device optimization and performance predictions become difficult. Also, the issue is reflected in the literature, where there are conflicting reports of the switching behavior even within the same RRAM material system. The confusion can be related to the interplay of multiple physical processes present during cell operation and their dependence on the material stack and programming environment.

Several features of the RRAM conductive path make it highly attractive for high density and low-power NVM. At the same time, these features are the root cause of its most severe challenges. Theoretically, the size of the conductive path can reach atomic scales without degrading performance while in some cases, scaling has been shown to improve performance [35, 36]. Generally, resistance levels increase with scaling, which is advantageous for power considerations. Also, ionic transport at the nanometer scale can cause sufficient resistance change; therefore, overall programming energy for RRAM is low.

However, it is this highly localized active region and filamentary conductive path which generate severe reliability and variability issues because of the reduced number of participating defects [37]. At these scales, the charge state or motion of a single defect within or close to the CF can dramatically change the resistance of the CF and give rise to instability [38-40]. Uniformity is affected by this behavior because the exact arrangement of defects changes for each cycle causing the so-called cycle to cycle variability. Read operation is prone to Random

Telegraph Noise (RTN) signals which not only degrade the resistance window [41, 42] but also disrupt program-verify techniques [43]. In a Multilevel (MLC) the number of states is limited by instability in the resistance state [44-46]. Therefore, thin conductive paths, which are desirable for high density and low-power applications, are susceptible to large fluctuations that affect stability and uniformity.

#### Array level

Ideally, a RRAM memory array can be a true cross bar architecture where the device area is defined by the cross point of the bitline (BL) and wordline(WL), which are arranged orthogonal to each other [47-50]. Due to the scalability of RRAMs, the linewidths and line spacing can be minimized to achieve a high density array. An RRAM cell footprint is 4F<sup>2</sup>, where F is the smallest feature size of a given process [51]. The memory cell area can be further reduced by utilizing the MLC capability of RRAMs or multi-stack cell structure [52]. With this approach, the cell area becomes 4F<sup>2</sup>/n, where n is the number of levels or stacks per device [53]. In addition to the cycle to cycle variability, device to device variability is also present at the array level. This variability is in part unavoidable due to the intrinsic randomness of the RS mechanism. However, cell to cell variability is more prone to additional extrinsic sources of variability such as poor process uniformity across the chip.

Sneak current is another serious issue at the array level. In the crossbar architecture, multiple cells share common BL and WL. Therefore, in addressing a device in HRS, current can sneak past the higher resistance device and flow through devices in LRS. Sneak currents are problematic because they increase the thermal budget, decrease array size, and reduce read-out margins [54]. Sneak current solutions involve integrating the RRAM cell with a selector device such as a diode or transistor in a 1 Diode - 1 RRAM (1D1R) configuration or a 1 Transistor - 1

RRAM configuration (1T1R), respectively [55, 56]. Although both configurations can eliminate sneak currents, the additional element increases the cell footprint.

An alternate solution relies on the non-linearity of the RS mechanism to minimize sneak current. This strategy, referred to as 1 RRAM (1R) configuration, eliminates the need for an area-consuming selector device. Dimin Niu et al. [57] investigated the performance of all three configurations – 1R, 1T1R, 1D1R – and determined that 1D1R is suitable for devices operated at high operating current and low nonlinearity, while 1R is suitable for low operation current and high nonlinearity. An anti-serial connected TaOx-based cell has also been demonstrated to minimize sneak current [54, 58].

#### **Programming solutions to RRAM issues**

Strategies to improve reliability and uniformity can be separated into two groups: programming and non-programming. In the latter approach, common strategies to improve performance involve material selection, stack engineering, doping and cell-structure optimization [33, 59-64]. H.Y. Lee et al. improved the resistance window (>1000) and achieved low operation voltage by incorporating a Ti layer to a HfOx cell [11]. Traore et al. observed better retention in HfOx-based devices doped with Al and Ti [65]. However, these strategies can be nullified by improper programming.

Programming current control remains one of the key parameters responsible for improving several key performance markers of RRAMs. High endurance and retention are linked to optimizing the programming currents since excessive and insufficient currents can result in failure [66, 67]. The former case results in reversible failures [68], while the latter results in permanent failures [69]. The RS mechanism is highly sensitive to temperature which in turn is generated by the current flowing through the conductive filament. As will be discussed in

Section 1.2, thermochemical cells rely on temperature for filament formation and rupture [70]. Therefore, it is particularly important to limit the maximum current or energy dissipated in the CF.

As previously stated, current control is traditionally executed with a series current limiting element such as a resistor or transistor [71, 72]. However, current control without the additional series element can be achieved by pulse width controlled current duration [73] and by current sweep programming [74, 75]. The former achieves current control by limiting programming energy and has been demonstrated in forming studies and endurance studies [43, 76]. The latter approach takes advantage of the gradual filament formation of the current sweep to eliminate excessive programming current. Improved retention has been demonstrated in the current sweep approach [77].

Although constant stress (DC) and sweep programming modes are commonly used in RRAMs [69, 74, 78], pulse programming is preferred for practical studies of switching performance [79]. This is because pulse programming is fast, energy efficient and mimics the true programming operation at the chip level. Chen et al. demonstrated a high endurance obtained by balancing V<sub>SET</sub> and V<sub>RESET</sub> [68], indicating the need to optimize pulse parameters such as rise/fall time, width and amplitude to improve endurance [80-82].

Variability remains one of the major challenges in RRAMs because it is intrinsic to the nature of the resistive switching process [83]. Along the filament, the exact location and extent of filament formation and rupture cannot be reproduced from cycle to cycle or from device to device. Therefore, post programmed states are represented as distributions instead of well-defined values. To enable accurate state determination during read-out operation, the distributions must never overlap. Program-verify techniques have been developed primarily to

ensure distinguishable resistance distributions or sufficient resistance window (RW). Generally, program verify algorithms adjust the pulse number [43, 84], width [85] and amplitude [86-88] until the desired RW is achieved. Program-verify has also been used to tighten the resistance distribution which is highly desirable for MLC applications of RRAMs [86].

#### 1.2 Origins of Filamentary Resistive Switching

The memory function in RRAM is based on the reversible change of the cell resistance between at least two distinct resistance states. As described earlier, the memory cell structure is composed of two conductive layers separated by an insulating layer, in this case an oxide. Therefore, to change the resistance of this otherwise insulating cell would require the presence of some conductive path through the oxide connecting the two electrodes: top electrode (TE) and bottom electrode (BE). The conductive path may be related to an interface effect such as Schottky barrier modulation or a localized path adjoining TE and BE. The former is usually observed when a semiconductor is used as the insulating layer [14]. Therefore, based on the type of semiconductor and electron metal work function, an Ohmic contact or Schottky barrier that can be modulated is formed [51]. The switching mechanism may also be due to charge trap/detrap in the insulator. In which case, the presence or absence of charge can affect conduction at the interface [89, 90]. Cells that rely on interface modulation to switch are referred to as interface-type cells. In LRS (On-State), conduction ideally occurs homogeneously across the entire interface, making the LRS of interface-type cells strongly sensitive to area scaling [91].

Figure 2. LRS and HRS dependence on cell area for different RRAM stacks [13].

On the other hand, some RRAM cells show a very weak, sometimes negligible, dependence of LRS on the device area. Figure 2 shows the dependence of LRS and HRS on the cell area. It is evident that HRS decreases considerably with scaling, while LRS shows negligible change. This suggests that the conductive path is localized with lateral dimensions much smaller than the device area. These cells are referred to as filamentary-type cells. In HRS, the filament is ruptured, disconnecting TE and BE, while in LRS the filament is intact. Ideally, in filamentary-type cells, a single, localized, conductive filament is responsible for RS. Due to the highly localized filament, device performance frequently remains, more or less, unchanged; however, in some cases, performance actually improved by area scaling [35, 36]. The filament dimensions will limit the extent to which area scaling does not impact LRS. In this thesis work, we examine filamentary-based RRAMs.

The conductive filament (CF), which is electrically more conductive than its surrounding insulating matrix, is a localized path in the insulating layer [92]. Therefore, conduction is unaffected by area scaling until the device area approaches the lateral dimensions of the filament. The resistance state of the memory cell is determined by the physical and geometric properties of the CF. As depicted in Figure 3, higher resistance states are accessed when the CF shrinks in width. Even higher resistance states are accessed when the CF is completely severed, i.e., electrically disconnecting the two electrodes.

Prior to direct observations of the localized conductive path in the switching matrix, the localized nature was observed through C-AFM [93-95] techniques. In LRS, nanoscale conductive paths are present, while in HRS these paths disappear or are reduced in size or number. The appearance of multiple conductive paths suggests multi-filament formation. However, direct observations of the CF, particularly non-metallic filaments, are challenging because of the localized nature and the difficulty in differentiating the CF from its surrounding insulator matrix. Transmission electron microscopy (TEM) has been used to identify conductive paths in metal oxides [21]. Using X-ray absorption spectroscopy, Strachan et al. observed a localized reduced region in TiO<sub>2</sub>, which was responsible for the large increase in conductivity in LRS [96].

Figure 3. Illustration of the possible physical configuration of the CF in an RRAM cell. CF resistance increases as length and/or width of CF decreases.

The CF may display metallic-like or semiconductor-like conduction based on its composition, which is ultimately determined by the cell material stack and the programming currents. Metallic-like conduction is usually observed in RRAM cells whose electrochemically active metal electrode is dissolved and deposited in the insulating matrix. In these cells, the CF is composed of metal atoms. However, metallic-like conduction was observed in a Pt/NiO/Pt cell which has two inert electrodes [97, 98]. Therefore, metallic conduction is not limited to cells which include an electrochemically active electrode. Semiconductor-like conduction occurs where defects (oxygen vacancies, cation vacancies) are generated and accumulated in the insulator to form a conductive path. In such cases, the CF is not composed of metal precipitates from an electrochemically active electrode. Rather, they are usually composed of sub-oxides, which undergo a redox reaction due to the concentration of oxygen vacancies, in the switching

layer. F. Pan et al. describe two switching mechanisms based on ion migration: cation migration and anion migration mechanisms [14].

In the cation migration model, an electrochemically active electrode such as Ag is positively biased (anode) leading to the dissolution of the electrode (Ag→Ag<sup>+</sup> + e<sup>-</sup>). The resultant cations (Ag+) migrate under the applied field towards the negative biased electrode (cathode). At the cathode, the cations are reduced back to metal (Ag<sup>+</sup> + e<sup>-</sup> → Ag) and begin to form the metallic dendritic filament that eventually bridges the two electrodes. The nucleation and mobility of the cations in the insulating layer determine the growth direction of the metallic filament. In Ag/SiO2/Pt [99], Ag/a-Si/W [25] and Ag/PEDOT:PSS/Pt [100] the filament has been shown to grow from cathode to anode, anode to cathode, and in both directions, respectively. RRAM cells where cation migration is responsible for RS are referred to as electrochemical metallization cells (ECM), conductive bridge RAM (CBRAM) or programmable metallization cells (PCM). The conductive filament in CBRAM-type devices have been confirmed with TEM analysis [101]. Using electron energy loss spectroscopy (EELS) and energy dispersive X-ray (EDX), Xing Wu et al. determined that the CF in HfOx cell with a Ni TE was composed of Ni that migrated from the TE into the HfOx layer [22].

In the anion migration model, the electrodes do not contribute species to form the CF. Usually, the CF is composed of a localized sub oxide that is more conductive than the parent oxide material. Redox reactions driven by the migration of oxygen ions (anions) in the oxide are attributed to the RS. Under the applied electric field, anions migrate to the positively biased electrode leaving behind oxygen vacancies and a subsequent valance state change of the cation sublattice. This modifies the electronic conductivity and forms the conductive path during FORMING and SET [102]. By applying the positive electric field, anions migrate back into the

oxide and recombine with oxygen vacancies during RESET. These oxygen-vacancy defects result in the generation of sub stoichiometric oxides which form the conductive path. It is common for RS to be described by oxygen vacancy migration analogous to hole movement. RS based on oxygen ion/vacancy migration is referred to as Valence Change Memory (VCM). Typical oxides which exhibit anion-migration induced redox reaction include, Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub> and ZrO<sub>2</sub>. It is common for the oxides to be represented as TaOx, HfOx, ZrOx as they are purposefully deposited with significant oxygen content deficiency. In TiO<sub>2</sub>, for example, the conductive path was observed to be a result of the formation of Ti<sub>4</sub>O<sub>7</sub> in the TiO<sub>2</sub> matrix [21, 96].

The oxygen vacancy concentration distribution is critical to the switching kinetics in VCM cells. Cells that have uniform distribution of oxygen vacancies tend to exhibit both bipolar or unipolar switching modes. In the bipolar case, filament formation and rupture are caused by anion migration induced by the applied field [103]. In the unipolar case, temperature drives both filament formation and rupture [104]. Cells can be structured intentionally to have a non-uniform distribution of oxygen vacancies to make the switching direction more sensitive to polarity. This can be achieved by using a top metal electrode (eg., Ta, Al or Ti) with a high oxygen affinity [105] or introducing a layer (eg., TaO<sub>2-x</sub>) with high concentration of oxygen vacancies. This creates a disproportionate number of oxygen vacancies close to TE which favors a positive bias on TE for SET since negative bias would initially drive oxygen ions back into the vacancies.

RS based on field-induced ion processes (generation, migration, redox) were described above; however, these processes may be thermally induced. A third class of cells dominated by thermal effects are referred to as Thermochemical memory (TCM) [106] or fuse-antifuse cells [22]. During FORMING/SET, filament formation is driven by thermal decomposition of the oxide layer. The deficiency of oxygen results in CF of either oxygen vacancies [107] or metal

precipitates [108] or a mixture of both [22][31]. The driving force for the formation of metallic CFs is the energetically favored, lower-valence states of these metal oxides at high temperatures [14]. TCM cells usually show metallic conduction in the ON state and semiconductor-like conduction in the OFF state [97]. During RESET, thermally activated O<sup>2-</sup> diffusion driven by the concentration gradient of the oxygen deficient CF and the oxygen rich surrounding matrix oxidizes the CF to create a dielectric barrier. Lee et al. [95] observed evidence of O<sup>2-</sup> migration in a Pt/NiO/Pt cell by secondary mass ion spectroscopy. Because joule heating is independent of the polarity of the applied voltage, the nonpolar switching mode is usually observed. TCM switching behavior has been shown in CoO, TiO<sub>2</sub>, NiO, ZnO based oxides sandwiched between two inert electrodes in a symmetric cell [109].

Regardless of the switching mechanism, ECM, TCM or VCM, the as-deposited RRAM oxide typically requires an initial step to construct the conductive path. This is the FORMING step. FORMING can be interpreted as a soft breakdown event [110], which generates the minimum number of species needed to electrically connect TE and BE. Time-dependent, dielectric-breakdown measurements show that the relationship between FORMING voltage and FORMING time is exponential [111]. Therefore, the percolation theory of dielectric breakdown can be used to explain the FORMING process [112]. RS generally involves an interplay of electrochemical and thermochemical processes, where one may dominate depending on the specifics of the stack and the programming procedure. V<sub>FORM</sub> decreases with oxide thickness suggesting that FORMING is a field driven process [113]. At high (> 10 MV/cm) electric fields, metal oxide bonds can be broken creating both ions and defects. However, the temperature due to leakage current is expected to contribute significantly to bond breaking and filament formation. For example, in a polycrystalline film, grain boundaries act as precursor sites for the

CF because of enhanced leakage current paths via defects [97]. Electron transport through such vacancies is accompanied by energy dissipation resulting in local temperature increases [27], which can enhance vacancy generation. This, in turn, lowers the activation energy barrier for subsequent vacancies. Coupling this lower activation energy with the exponential dependence of vacancy generation on both the electric field and the temperature leads to positive feedback that can accelerate CF formation.

High voltages are typically needed for FORMING since it generates the prerequisite number of defect species to construct the entire CF. Because of the required voltages, FORMING is usually undesirable because it increases power consumption and the high voltage can easily initiate thermal damage. Consequently, several strategies have been employed to obtain so-called 'FORMING free' [60] [114, 115] devices or, at a minimum, 'decreased FORMING voltages'. Some strategies take advantage of the linear relationship between V<sub>FORM</sub> and oxide thickness, where simply decreasing the oxide thickness will decrease V<sub>FORM</sub>. Other strategies to decrease V<sub>FORM</sub>, involve purposefully depositing defect rich oxides by controlling oxygen content or anneal ambiance during oxide deposition [116]. The higher leakage current of these defective oxides dominates the FORMING process while keeping V<sub>FORM</sub> low. Hot forming has also been used to reduce the FORMING voltage and time [78]. At elevated programming temperatures, the electron transfer rate increases, and an associated increase in dissipated power during charge trap/detrap accelerates the generation of defects. This sensitivity of the forming step to temperature of the device corroborates the role of temperature in resistive switching.

RESET and SET do not scale with oxide thickness. This suggests that only a small portion of the CF participates in RESET and SET. This is also evident by the lower  $V_{\text{SET}}$  and  $V_{\text{RESET}}$  voltages compared to  $V_{\text{FORM}}$ . The SET operation is a scaled down version of FORMING

as it reforms the rupture portion of the CF. Therefore, current compliance is required during SET. RESET operation makes the CF less conductive. This can be explained either by a reduction of CF dimension or the creation of a dielectric barrier in the CF. In the former scenario, the filament is still intact while in the latter, the filament is ruptured. Two prominent models have been proposed to explain the RESET process in filamentary RRAM cells: the thermal-dissolution model [117] and ionic-migration model [118]. In the thermal-dissolution model, the applied voltage causes current to flow through the CF. Joule heating leads to a temperature rise that leads to dissolution of the CF. This process is self-accelerated because the hottest spot on the filament shrinks the fastest, enhancing the electric field and current density. Since this process is independent of the polarity of the applied voltage, it describes unipolar or nonpolar RESET. However, in the case where voltage polarity is required such as in bipolar RESET, the electric field drives the dissolution of the CF. Oxygen ions (O<sup>2-</sup>) drift to recombine with oxygen vacancies [119].

The physical and chemical properties of the CF are affected by the material stack, the interface, the film structure, and the thermodynamics associated with programming. Because of the direct impact of these parameters on the CF, switching performances such as endurance and retention can be tuned. For instance, the higher performance of some material systems is associated with the stable oxides that constitute the CF. Like in TaOx-based systems, two thermodynamically stable solid phases are achievable, resulting in more stable CF compared to TiOx [120, 121]. Programming also directly influences the physical and chemical nature of the CF.

#### 1.3 HfO<sub>2</sub>-based RRAM

As previously described, several materials can be used as the insulator or storage layer. Of these materials, transition metal oxides are favored based on several key factors. In transition metal oxides, the stoichiometry can be adjusted to control material properties and improve switching performance [95]. Most metal oxides (CuOx, WOx, HfOx, SiOx) already in use in complementary metal oxide semiconductors (CMOS) show the resistive switching phenomenon. This simplifies and dramatically reduces the cost of implementing memory technologies based on RRAM. For some stacks, such as WOx and CuOx, a simple, additional oxidation step is enough to integrate RRAMs with a transistor [122]. For RRAM arrays that require a selector diode or transistor, the thermal stability of metal oxides becomes an indispensable feature as well. The popularity of oxide-based RRAM cells is also based on the merit of their switching performance in comparison to other material systems [13].

One of the more mature metal oxides explored for RRAM is HfO<sub>2</sub>. RRAMs based on HfO<sub>2</sub> switching layers have shown excellent switching scalability and performance. In addition, HfO<sub>2</sub> has proven compatibility with CMOS technology, where it is employed as a high-κ gate dielectric for high-performance MOSFETs. Figure 4 shows a SEM and TEM image of two different HfOx devices. Govoreanu et al. demonstrated a cross point (Figure 4 (a)) 10 x 10 nm<sup>2</sup> TiN/Hf/HfOx/TiN cell with good endurance (10<sup>7</sup> cycles) and stability (30 hrs @ 200<sup>o</sup>C) [35]. Zhang et al. fabricated devices, shown in Figure 4 (b) with an active area of a few nanometers (< 10nm) with multilevel functionality and 10<sup>8</sup> endurance [36]. In addition to MLC capability, S. Yu et al. fabricated vertical cells for use in a three-dimensional (3D) cross point architecture which would further increase the storage capacity of the memory chip [52]. In regard to

switching performance, ultra-low (pJ) switching energy, sub ns switching speeds,  $10^{10}$  endurance has been demonstrated in HfO<sub>2</sub> based devices [11, 43, 123].

Figure 4 (a) Top view SEM image of TIN/Hf/HfOx/TiN cell. Cell area is defined at the crossing of TE (10 nm line width) and BE (10 nm line width) [33]. (b) Cross-sectional TEM image of TiN/HfOx/Pt device. The active area is < 10nm, defined by TE (TiN) [34].

The RS mechanism in HfO<sub>2</sub> is widely accepted to be attributed to the formation and rupture of a conductive filament due to oxygen ion and vacancy processes. [66-68]. Unless an electrochemically active electrode is used [22], most HfO<sub>2</sub>-based devices are categorized as VCMs. However, unlike CBRAM where the CF is composed of metal atoms, the CF in VCM is mostly composed of a reduced valence state of the oxide. Therefore, observing CF using TEM is not easily accomplished [124]. However, the conductive path has been evidenced by U. Celano et al. using an AFM based tomography technique [20]. Kumar et al. [23] observed lateral oxygen migration using X-ray absorption spectromicroscopy. The conductance of the CF may display

semiconductor-like or metallic-like properties depending on the programming currents and material stack [125].

Usually, amorphous or polycrystalline HfO<sub>2</sub> layers are deposited for RRAM using various deposition techniques including atomic-layer deposition (ALD) [126], rf-magnetron reactive sputtering [127] and atomic-vapor deposition [128]. Generally, single crystalline films show lower V<sub>FORM</sub> compared to polycrystalline and amorphous oxide films. This is attributed to grain boundaries in the crystalline films, which provide favorable sites for CF growth [93]. The grain boundaries also serve as low-energy diffusion paths for oxygen ions to easily diffuse through [129]. For polycrystalline films, the oxygen vacancies form an extended defect or percolation path as observed in NiO [130]. In amorphous oxide material, however, there are no preferable sites for CF formation; hence, the CF growth location is extremely random [131] and V<sub>FORM</sub> is high [132]. During deposition, the ambient [132] and annealing conditions [127] can impact switching parameters. This is due to the role of oxygen ions in RS as these processes control the oxygen content during deposition.

HfOx-based RRAM cells can exhibit unipolar, nonpolar, and bipolar switching modes [109, 127, 133]. As discussed earlier, the switching mode is not intrinsic to the insulating layer but is dependent on the complete material stack of the cell. Unipolar and nonpolar are usually achieved in symmetric cells, for example a Pt/HfOx/Pt cell, since both TE and BE interfaces are the same. However, unipolar switching has also been observed in asymmetric cells. L. Goux [134] et al. observed both unipolar and bipolar switching in TiN/HfO2/Pt asymmetric cells. For TiN-HfO2-Pt stacks, poor RESET was observed for both unipolar and bipolar when positive bias was applied to TiN electrode. RESET and cycling were better with a positive bias applied to the Pt electrode. This behavior suggests that the switching mode classification should be based on

switching yield since some devices can display multiple modes depending on the chosen bias. Bertaud et al. [135] observed that the switching mode did show a dependence on electrode choice. Metals like Pt and Cu, with high enthalpy of formation of oxides lead to unipolar switching, while metals such as Al, Hf, Ti with low enthalpy of oxide formation lead to bipolar switching.

Most advanced HfO<sub>2</sub> devices have at least one additional layer in the MIM structure which is inserted between TE and HfO<sub>2</sub>. To explain RS, it is generally accepted that mobile O<sup>2</sup>ions diffuse back and forth to modulate the defect rich CF [24]. This movement of mobile oxygen ions is central to the RS mechanism. The additional layer is purposefully incorporated in the MIM structure to store and release O<sup>2</sup>- ions during programming. These functional layers are commonly referred to as oxygen-exchange layers (OEL), scavenging layers, or insertion layers [136, 137]. Multilayer cells are also fabricated not for oxygen scavenging, but to create an internal series resistance for low-power operation [63][[64, 84, 138].

Typical materials used as OEL include Ti, Ta, Hf and Zr [120]. These metal layers easily form metal oxides in the memory stack by extracting oxygen from the HfO<sub>2</sub> layer. For example, a Ti OEL layer leads to the formation of TiOx at the interface [139]. This process leaves behind a defect rich, non-stoichiometric oxide layer. The extent of this extraction process is determined by the choice of metal cap material and its thickness. HfOx cells with Ta OEL typically exhibit better retention compared to Ti and Hf [120]. This is attributed to the higher oxygen diffusion barrier of the Ta-O compared to Ti-O. Yuzheng Guo et al. [33] used defect energy calculations to determine that OEL can control both vacancy concentration and its charge state. However, this means release of O<sup>2-</sup> for RESET is harder and affects repeated cycling. This endurance-retention trade-off was reported by Y.Y Chen et al. [140]. The OEL thickness also affects cell resistance

and switching voltages. In a study of the cell resistance on OEL to oxide ratio, D. Walczyk et al. [55] found that the pristine resistance of a Ti/HfO<sub>2</sub>/Ti/TiN cell decreased with decreasing HfO<sub>2</sub> to Ti ratio. This is explained by the degree of oxygen gettering from the HfO<sub>2</sub> layer by Ti. Thicker or more reactive OEL layers extract more oxygen, which dramatically lowers the resistance and voltages required for switching. Additional benefits of OEL include, improved read disturb, increased HRS, and improved window [134] [141].

Cells with OEL generally support the bipolar mode because of the imbalance distribution of defects along the thickness of the oxide. This is because oxygen gettering is more aggressive close to the OEL [142]. The VCM model postulates that oxygen ions drift to the positively biased electrode, leaving behind defects (oxygen vacancies) to create the conductive path. Due to the spatial distribution of defects, it is preferred to apply a positive voltage at the OEL – oxide layer to initiate FORMING. It is expected that the filament grows from TE to BE and should therefore assume a conical shape as confirmed by C-AFM [20] and scanning TEM [143]. During repeated cycling, it is conceivable that over time, the location of the constriction might change, giving rise to different shaped filaments [144]. Forming-free HfO<sub>2</sub> based devices have been demonstrated [60, 114, 132]. These devices are usually functionalized by stack engineering and doping methods. However, Butcher et al. [78] demonstrated a programming solution to decreasing  $V_{\rm FORM}$ , where FORMING was performed under elevated temperatures.

RESET is expected to occur at the thinnest portion (constriction) of the CF. This is because current density and temperature are highest at the constriction. For a conical shaped filament, the RESET location should be located at the BE (opposite from OEL interface). L. Goux et al. [134] observed a high sensitivity of RESET on the BE interface, corroborating the role of BE in the RESET operation. Because the CF resistance increases in RESET, the process

is assigned to a decrease in CF dimensions or dielectric barrier in the filament. Usually, a complete rupture results in deeper HRS. To RESET the device, a negative bias is applied to the TE with BE grounded. The O<sup>2-</sup> stored in the OEL drifts under the applied field into the bulk oxide and recombines with the vacancies to re-oxidize the filament, either partially or completely. Note, the RESET may also be initiated thermally due to joule heating of the CF. Both unipolar and bipolar RESET has been observed in HfOx-based devices. In a model proposed by B. Gao et al. [119], the electric field creates Vo<sup>2+</sup> by depleting oxygen vacancies of electrons and O<sup>2-</sup> diffuse to the positively charged vacancy and recombine. However, in the bipolar case, O<sup>2-</sup> migration is field controlled, while in the unipolar case, O<sup>2-</sup> migration is thermally controlled.

L. Zhao et al. [145] proposed that the driving force for RESET changes during the process of filament rupture. In LRS, before RESET begins, a continuous filament exists. The applied voltage causes a temperature rise due to joule heating. O<sup>2-</sup> then diffuses according to the concentration gradient towards the oxygen vacancy rich CF. Once a dielectric barrier (gap) is created, the electrical field dominates since current and temperature significantly decreases. Therefore, thermal diffusion dominates the RESET operation when a continuous filament is present while drift dominates when a gap is created. The SET process is similar to FORMING; however, to re-construct the continuous filament only the portion ruptured (gap) in the RESET operation has to be re-formed. Consequently, V<sub>SET</sub> is lower than V<sub>FORM</sub>. In HfOx memory, conduction in HRS at low bias regime has been shown to be dominated by trap assisted tunneling[146], hopping [71] and Poole-Frenkel [147]. Su et al. investigated current conduction as a function of resistance and observed that current conduction transforms from hopping to

Ohmic as resistance decreases [71]. Conduction in LRS has been shown to be metallic-like for low resistance values ( $< 103 \Omega$ ).

Like most other RRAM systems, the switching performance of HfOx based cells can be enhanced using different strategies, which include interface and stack engineering, doping and programming. In [59], the authors showed that implanting Gd in the HfOx layer improved switching speed, enlarged the On/Off ratio, and improved uniformity. This improvement is attributed to Gd ions decreasing the energy of vacancy formation in the oxide. This is desirable for systems in which the CF is composed of oxygen vacancies. Likewise, CFs that are composed of metal, like in ECM, can be improved by incorporating metals of the same electrochemically active electrode into the HfOx layer [148]. Oxygen plasma treatment of the HfOx has been shown to improve switching performance by incorporating interstitial oxygen ions for repeated cycling [149].

#### 1.4 Dissertation Objective

Reliable RRAM memory operation requires that the ON (LRS) and OFF (HRS) state distributions are distinct enough to enable accurate state identification. However, the stochastic nature of the resistive switching mechanism causes incomplete or failed write/erase operations, which result in an overlap of the resistance distributions. To ensure that each operation is complete, state-verification during programming is mandatory. The primary objective of this experimental thesis work is to develop a program-verify technique purposefully to address the variability induced overlap of the state distributions. This special technique is uniquely based on utilizing low-programming energy for write/erase to promote gradual tuning and suppress over-programming – the major cause of irreversible switching failure. The combined benefit of the developed program-verify technique would therefore enable a high cycling lifetime with a

resistance memory window. This current work provides a feasible solution to one of the most challenging issues in filamentary-based RRAM devices. Prior to demonstrating this novel program-verify technique and as an integral part of this thesis work, a measurement setup was developed with two key components: (i) a novel home-made 100 picosecond pulse generator with adjustable pulse amplitude, repetition rate and pulse polarity and (ii) a custom-built control circuit board with maximum operation speed at 10 MHz.

### **CHAPTER 2**

### **EXPERIMENTAL SETUP**

This chapter describes the customized, pulse-programming setup called Compliance-free Ultra-Short Smart Pulse Programming (CUSPP), that was developed for studying the switching performance of RRAM devices. The setup integrates a custom-built, ultra-short, pulse generator with a custom-built control circuit. By implementing a new current-compliance approach and read operation, the programming setup enables unique, intrinsic studies of the RRAM high-speed switching characteristics. These studies include 1) the short-term (microsecond) instability of the post-programmed resistance state and 2) the intrinsic recovery behavior of RRAMs after failure. To date, some of the highest operational speeds of HfOx-based RRAM have been demonstrated with our new measurement setup: specifically, 100 ps write/erase speed and 500 kCycles/sec cycling rate have been achieved. The description is divided into three parts: (1) the custom-built 100 ps pulse generator, (2) custom- designed control circuit and (3) the fully integrated program-verify system (CUSPP).

### 2.1 HfO<sub>2</sub> RRAM Device

All RRAM devices used in the CUSPP setup were provided by SEMATECH. The oxide layer is polycrystalline HfO<sub>2</sub>, deposited using Atomic Layer Deposition. Three different oxide thicknesses were available: 4.5 nm, 5.8 nm and 6.8 nm. The top electrode (TE) and bottom electrode (BE) is TiN. A 5 nm thick Ti oxygen exchange layer (OEL) is deposited between the top TiN and HfO<sub>2</sub> layer. As previously discussed, OEL are purposefully deposited to create defects in the oxide layer and lower the switching voltages. Also, the asymmetry in the stack promotes the bipolar switching mode. In this work, voltages are applied to the TE, while the BE is grounded. A large range of device sizes were available, from 2000 x 2000 nm<sup>2</sup> down to 20 x

20 nm<sup>2</sup>. The device size is defined by the cross point of the top and bottom electrode because of the cross-bar architecture of the devices. Unless otherwise stated, all the results reported in this work were obtained using the 200 x 200 nm<sup>2</sup>, 5.8 nm thick HfO<sub>2</sub> devices because these devices generally showed higher switching yield.

## 2.2 100 picosecond Pulse Generator

In a previous study, it was determined that the forming energy was just as critical to proper control of the post-programmed resistance as the forming current [73]. This determination was based on the observation that devices, which were formed with the same maximum current but different energy levels, lead to different resistance states. High energy results in low resistance, low energy results in high resistance. Therefore, a new approach was devised to limit the current duration instead of the more conventional approach, which limits the current amplitude. In the latter approach, a current limiting element, such as a transistor or resistor, is placed in series with the RRAM to limit current amplitude [51].

Since programming energy is  $\int V(t) * I(t) dt$ , the approach of this thesis uses the pulse width (PW) to restrict the range over which dt can vary. This range, which is the current duration of the pulse, gives the upper and lower limits for that integral. However, the current duration is not necessarily equal to the PW of the applied voltage pulse. This is because the switching event in RRAM occurs randomly at some time during the pulse [85]. This pulse variability means that both the current duration and the programming energy are also variable. It was concluded that the key to minimizing dt and, consequently, the energy range is to minimize the programming PW. By using the ultra-short pulse approach, the range of energy (partially pulse width dependent) delivered per pulse is limited, and the maximum energy delivered per pulse is minimized. There are two major benefits of our approach. First, resistance

programming or tuning is expected to be more gradual since the maximum energy delivered per pulse is small. Second, any potential adverse effects associated with excessive currents or energy are minimized.

Normally, RRAM devices are programmed using PW in the nanosecond range [72, 150]. However, sub nanosecond programming has also been demonstrated [151] [152] [62]. These 100 ps switching time scales suggest that the processes responsible for RS are extremely short and demonstrate the feasibility of RRAM as a replacement for DRAM and possibly SRAM. In this work, we propose to use 100 ps pulses for programming. To generate these ultra-short pulses, a 100 ps (Full Width at Half Max) pulse generator was developed using various radio-frequency (rf) and microwave components. These components include a source, diodes, switches, attenuators, an inverter, pick-off tees, power splitters and a dc block. This system was designed to generate both negative and positive pulses with tunable pulse amplitudes and rates for RRAM programming.

The 100 ps pulse is generated by a commercial impulse generator that transforms a sinusoidal wave input into a negative output pulse with 100 ps rise and fall time. The impulse generator was more suited for programming the RRAM cells because of the higher output voltages (- 18V) for sub nanosecond PW compared to commercial picosecond pattern generators.

Figure 5 (a) and (b) show the respective input and output signal of the pulse generator, commonly referred to as a comb generator. The working principle of the comb generator is based on a Step Recovery Diode (SRD). In forward bias, the P-N junction conducts (turn on) and is full of charge carriers. When the device is reverse biased, the conduction remains high due to the stored charges in the junction. However, this reverse conduction lasts only until all the stored charge is removed. After that, the conductance decreases (turn off). The doping profile in SRD is

optimized so that all the stored charge is swept out almost instantaneously. Thus, the turn-off time is extremely short. The associated sudden drop in current produces a voltage spike with a wide range of harmonics. Based on the intended use, filters are used at the output to select the desired harmonics. Both the amplitude and spacing of the voltage spikes can be adjusted by the input sine wave. Here, a dual-channel pulse generator is used as the initial source of a sinusoidal shaped signal. This signal is amplified before it is delivered as the input to the comb generator.

Figure 5. (a) Input to and (b) output from a step recovery diode comb generator. The comb generator outputs voltage spikes with amplitude -18 V and PW  $\sim 100 \text{ps}$ . Note, the presence of a significant residual sinusoidal signal at the output.

As shown in Figure 5 (b), the output of the comb generator contains a residual signal from the input sine wave. This signal is undesirable because it is large enough (> +0.5 V) to program or, alternatively, disturb the device resistance state. Therefore, it must be removed. The output signal goes through multiple stages of pulse shaping to achieve this. With emphasis on

preserving the voltage spike amplitudes and bandwidth (3.5 GHz), several strategies were considered and tried.

A simple solution was to use a serial connection of attenuators and high-speed diodes. Although the attenuation decreased both spike (desired) and background signal, it greatly improved the ability of the diode to "clamp" the background signal. A fast Schottky diode was used for this purpose because of its low capacitance (pF) and low minority carrier lifetime (100 ps at 80 mA forward bias). These features allowed for minimal degradation of the pulse rise and fall time. The diode, which is packaged as a chip (SOT-323/SC-70), had to be housed in a module compatible with Subminiature Type-A (SMA) connectors. This was necessary because SMA connections are made throughout the system as shown in Figure 6. The diode module is engineered by carefully drilling a hole through a SMA connector to separate the center conductor and placing the diode to reconnect the signal path. The hole size was made as small as possible to avoid reflections and distortion of the fast pulse as shown in Figure 6.

Figure 6. (a) Commercial comb generator and engineered connector to house the Schottky diode. SMA connectors are used throughout to connect individual microwave components (b) Splitter, attenuators, inverter and switch assembly used to generate independently adjustable positive and negative pulses.

A limitation of the comb generator source is that it only outputs negative pulses as shown in Figure 5 (b). However, to operate bipolar devices, both negative and positive pulses are required. For the TiN/Ti/HfO<sub>2</sub>/TiN devices used in this work, SET and FORMING require positive polarity while RESET requires negative polarity. The voltage polarity is referenced to the BE which is grounded during programming. To produce positive pulses, an inverting stage was included. For cycling (SET and RESET) measurements such as endurance, alternating positive and negative pulses are needed. Therefore, both inverted and non-inverted signals must be produced. To achieve this, the pulse is first split into two halves. Then, a high-speed (15 ps) inverting transformer inverts one side to positive pulses. The power splitter and inverter are shown in Figure 6 (b). To allow for separate amplitude adjustment of the positive and negative

pulse trains, a digital high-speed (DC – 8 Ghz) attenuator with 1 dB step adjustments from 0 dB to 9 dB is used.

The inverter stage introduces a significant loss to the pulse amplitude because of the power splitter attenuation (6 dB) required to produce two separate pulse streams. For SET voltage (V<sub>SET</sub>) and RESET voltage (V<sub>RESET</sub>), the loss is minimal and does not affect programming; however, this loss is significant for FORMING voltage (V<sub>FORM</sub>). V<sub>FORM</sub> is typically up to 3 x larger than V<sub>SET</sub> and V<sub>RESET</sub>. We explored several strategies geared towards bypassing the splitter stage; this includes using a multiplexer to direct the initial negative pulse train towards an inverting or non-inverting path and amplifiers to compensate for the loss in amplitude. Although both remedies were feasible, both have their drawbacks. Because of this, we chose a different option. Since FORMING initiates cycling and is required once, we chose a simple solution: to exclude the splitter from the setup completely for just the FORMING step.

At this point, two separate pulse trains with opposite polarity have been generated on two separate lines. The signals must be recombined to construct a pulse train of alternating positive and negative pulses. However, both  $V_{SET}$  and  $V_{RESET}$  have the same clock cycle and repetition rate because they share a common source. To solve this problem, we used a high-speed switch (switch A) as a multiplexer. The switch selects between  $V_{SET}$  and  $V_{RESET}$  at a preset rate. This way, the separation (period) of the negative and positive pulse can be tuned by the switching rate of switch A. The resulting combined pulse train is sufficient for cycling the device. However, as will be discussed later, it is not adaptive and cannot avoid SET/RESET failures. In Section 2.2, we propose a complementary control circuit that uses feedback to control pulses such that failures can be dealt with.

Figure 7 shows switch A, which is a high-speed (DC – 18 GHz) single-pole double-throw (SPDT) FET switch in its customized housing. The switch is an extremely small die - 0.83 mm (L) x 1.11 mm (W) x 0.1 mm (D) - requiring wire bonds to make contact to all the pads (input, output and control) except rf ground. We used a microstrip transmission line with 50  $\Omega$  characteristic impedance, designed on a Printed Circuit Board (PCB), for this purpose. To ensure optimum insertion and return loss, single thin (0.001 in) wire bonds were made while bond lengths were kept short ( ~2.5 mm) so as to appear as a lumped element to the 100 ps rise and fall time.

A multi-functional heat sink was designed to make electrical contact to the rf ground located on the backside of the switch, and to provide mechanical support. The latter is important because the PCB is not rigid and therefore wire bonds can be easily detached during use. The switch is attached to the heat sink using a conductive silver epoxy, because it provides both thermal and electrical conductivity. A brass metal piece was designed using Autodesk ArtCAM and machined using a Computer Numeric Control (CNC) milling machine. The overall loss of the customized switch module is roughly -4 Db (up to 4 GHz). Although this is significant, the output voltages remain sufficient for the RRAM devices examined in this work. Because of our deliberate, transmission-line design, the output pulse after the switch maintains the 100 ps transition times.

Figure 7. PCB layout for the high-speed switch with a brass base designed to provide mechanical support, electrical and thermal contact to the backside of the switch. Inset shows image of chip with wire bonds connecting signal and control pads to microstrip transmission lines.

Figure 8 shows a representative V<sub>RESET</sub> programming pulse and high-speed, measurement probe. The noticeable offset (indicated by the red dashed line in Figure 8 (a)) is supplied by a programming DC source through a pick-off tee. The low DC voltage (V<sub>READ</sub>) is used to read/sense the state of the device during programming. A RRAM is a two-terminal device meaning that both program and read operations are performed using the same two terminals. This can cause what is called "read disturb". To minimize the risk of read disturb, the read operation is commonly performed using a low voltage pulse. Because of this, the read pulse amplitude and length must be optimized to ensure that they can determine the resistance state of

the RRAM accurately. Typical read-pulse durations are in the microsecond to nanosecond range and read-pulse amplitudes are 10 x lower than the programming pulse [87, 153, 154]. Positive or negative read polarity can be used, although some novel read operations utilize a combined positive and negative pulse read to avoid any dielectric polarization effects [155]. In this work, negative read polarity is used always.

Figure 8. (a) Typical  $V_{RESET}$  pulse offset by a low DC voltage( $V_{READ}$ ) used for read. (Inset) Pulse FWHM is approximately 100 ps captured on a high-speed oscilloscope (Rise time contributions of osc. has not been deconvolved). (b) High-speed measurement setup with proper  $50\Omega$  termination directly at the probe tip. Notice the absence of a series current limiting element.

The DC read operation adopted in this work is based on traditional, electrical stress measurements that utilize constant voltage to study stability. Typical voltage amplitudes used in such measurements are > |0.1| V. Here, read voltages are usually < -0.1 V. For even longer  $V_{READ}$  duration ( $> 10^3$  s), voltages as low as -0.008 V are used. Stable LRS and HRS have been demonstrated in HfOx RRAM cells using +0.3 V for  $10^3$  sec [156]. Therefore, we do not expect

to disturb the resistance states using the constant voltage  $V_{READ}$ . By utilizing a DC read during programming in CUSPP, we essentially combine a stress measurement with cycling for stability and endurance studies, respectively. As will be discussed in Chapter 4, fluctuation behavior is observed in the short-term post programming in a manner that cannot be achieved using pulse read.

Delivering fast pulses to the RRAM cell without rise-time degradation and signal distortions requires transmission-line design at all stages of the setup. The entire system, therefore, is designed to have a 50  $\Omega$  characteristic impedance and to support frequencies higher than 3.5 GHz (100 ps rise). These requirements are maintained throughout the system but particularly at the launch site (probe needle to RRAM) where reflections and ringing can distort switching analysis. Traditionally, a Ground-Signal-Ground (GSG) probe is used for such high-speed measurements [151]. However, this requires a matching, probe-pad layout of the device under test (DUT). Since the devices in this work were not designed to fit a GSG probe setup, this is not a feasible option. Thus, we had to design a high-speed probe based on a fundamental transmission line to assure high signal fidelity.

Since a RRAM is a two-terminal device, two high-speed probes are sufficient for operation. To design the high-speed probes, three main strategies were employed. First, the probe needle is made as short as possible to appear as a lumped element to the fast, pulse-transition time. Second, a 50  $\Omega$  rf resistor is strategically placed in parallel to the RRAM as shown in Figure 8 (b) to guarantee an impedance matched load. This assures that for all targeted RRAM resistance values, which typically range from  $10^3 \Omega$  to  $10^6 \Omega$ , the signal "sees" a 50  $\Omega$  termination. The 50  $\Omega$  termination also provides a fast RC to discharge any parasitic capacitance quickly. This is important because parasitic capacitance, which is ubiquitous in any setup, would

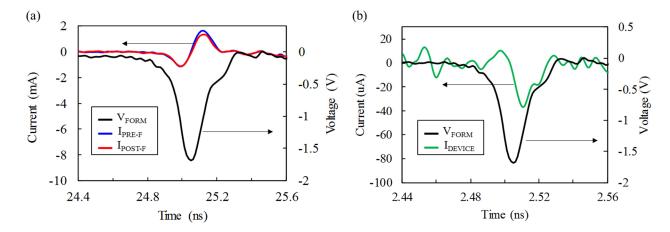

delay the response of the system to any abrupt resistance change. Any such delay is detrimental to our goal of minimizing programming energy. Third, a short ground loop connecting both input and output probe tips is soldered to minimize inductance. Total inductance at the probe tip is minimized by the mutual inductance of the signal and ground path. Without this mutual conductance component, total inductance increases and causes severe signal distortion.