#### **University of Denver**

# Digital Commons @ DU

**Electronic Theses and Dissertations**

**Graduate Studies**

8-1-2018

# Design and Evaluation of High Efficiency Power Converters Using Wide-Bandgap Devices for PV Systems

Fahad Almasoudi University of Denver

Follow this and additional works at: https://digitalcommons.du.edu/etd

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Almasoudi, Fahad, "Design and Evaluation of High Efficiency Power Converters Using Wide-Bandgap Devices for PV Systems" (2018). Electronic Theses and Dissertations. 1493. https://digitalcommons.du.edu/etd/1493

This Dissertation is brought to you for free and open access by the Graduate Studies at Digital Commons @ DU. It has been accepted for inclusion in Electronic Theses and Dissertations by an authorized administrator of Digital Commons @ DU. For more information, please contact jennifer.cox@du.edu,dig-commons@du.edu.

# DESIGN AND EVALUATION OF HIGH EFFICIENCY POWER CONVERTERS USING WIDE-BANDGAP DEVICES FOR PV SYSTEMS

\_\_\_\_

#### A Dissertation

Presented to

the Faculty of the Daniel Felix Ritchie School of Engineering and Computer Science

University of Denver

\_\_\_\_

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy

by

Fahad Almasoudi

August 2018

Advisor: Dr. Mohammad Matin

# © Copyright by Fahad Almasoudi 2018 All Rights Reserved

Author: Fahad Almasoudi

Title:

DESIGN AND EVALUATION OF HIGH EFFICIENCY POWER

CONVERTERS USING WIDE-BANDGAP DEVICES FOR PV SYSTEMS

Advisor: Dr. Mohammad Matin

Degree Date: August 2018

**Abstract**

The shortage of fossil resources and the need for power generation options that

produce little or no environmental pollution drives and motivates the research on

renewable energy resources. Power electronics play an important role in maximizing the

utilization of energy generation from renewable energy resources. One major renewable

energy source is photovoltaics (PV), which comprises half of all recently installed

renewable power generation in the world. For a grid-connected system, two power stages

are needed to utilize the power generated from the PV source. In the first stage, a DC-

DC converter is used to extract the maximum power from the PV panel and to boost the

low output voltage generated to satisfy the inverter side requirements. In the second

stage, a DC-AC inverter is used to convert and deliver power loads for grid-tied

applications. In general, PV panels have low efficiency so high-performance power

converters are required to ensure highly efficient PV systems.

The development of wide-bandgap (WBG) power switching devices, especially in

the range of 650 V and 1200 V blocking class voltage, opens up the possibility of

achieving a reliable and highly efficient grid-tied PV system. This work will study the

benefits of utilizing WBG semiconductor switching devices in low power residential

scale PV systems in terms of efficiency, power density, and thermal analysis.

ii

The first part of this dissertation will examine the design of a high gain DC-DC converter. Also, a performance comparison will be conducted between the SiC and Si MOSFET switching devices at 650 V blocking voltage regarding switching waveform behavior, switching and conduction losses, and high switching frequency operation.

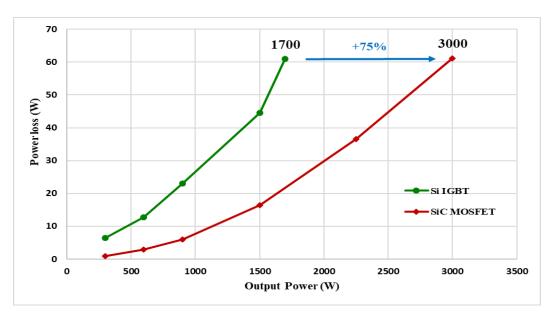

A major challenge in designing a transformerless inverter is the circulating of common mode leakage current in the absence of galvanic isolation. The value of the leakage current must be less than 300mA, per the DIN VDE 0126-1-1 standard. The second part of this work investigates a proposed high-efficiency transformerless inverter with low leakage current. Subsequently, the benefits of using SiC MOSFET are evaluated and compared to Si IGBT at 1200 V blocking voltage in terms of efficiency improvement, filter size reduction, and increasing power rating. Moreover, a comprehensive thermal model design is presented using COMSOL software to compare the heat sink requirements of both of the selected switching devices, SiC MOSFET and Si IGBT.

The benchmarking of switching devices shows that SiC MOSFET has superior switching and conduction characteristics that lead to small power losses. Also, increasing switching frequency has a small effect on switching losses with SiC MOSFET due to its excellent switching characteristics. Therefore, system performance is found to be enhanced with SiC MOSFET compared to that of Si MOSFET and Si IGBET under wide output loads and switching frequency situations. Due to the high penetration of PV inverters, it is necessary to provide advanced functions, such as reactive power generation to enable connectivity to the utility grid. Therefore, this research proposes a modified

modulation method to support the generation of reactive power. Additionally, a modified topology is proposed to eliminate leakage current.

#### Acknowledgments

I would like to thank my advisor, Dr. Mohammad Matin, for guiding me through the research process, teaching me valuable research skills, and helping me to develop my own research style. I would also like to thank him for sharing his expertise by helping me meet the challenges I encountered during my research. His support and advice made this dissertation possible.

I would also like to thank my committee members; Dr. David Gao, Dr. Amin Khodaei, and Dr. Jack Donnelly for their valuable feedback and help in refining my research.

Last but not least, I want to thank my parents, who have nourished me with their motivation and emotional support over the years. Finally, and most importantly, I wish to thank my wife, Reem, and my three wonderful children, who continually inspire me with their love and patience.

## **Table of Contents**

| Chapter 1. Introduction                                                      | 1  |

|------------------------------------------------------------------------------|----|

| 1.1 Research Objective                                                       | 3  |

| 1.2 Dissertation Outline                                                     | 4  |

|                                                                              | _  |

| Chapter 2. PV System Architecture                                            |    |

| 2.1 Introduction                                                             |    |

| 2.2 Configuration of PV Grid Integration                                     |    |

| 2.2.1 Central Configuration                                                  |    |

| 2.2.2 Module Configuration                                                   |    |

| 2.2.3 String Configuration                                                   | 8  |

| 2.2.4 Multi-String Configuration                                             | 8  |

| 2.3 Modeling of Photovoltaic Module                                          |    |

| 2.3.1. Design of a PV Module Using PSIM Simulation Environment               | 11 |

| 2.3.2. Physical Model of PV Panel in PSIM                                    | 12 |

| 2.3.3. Design of a 3 kW PV Array                                             |    |

| 2.4 High Gain Boost Converter for PV Application                             |    |

| 2.4.1 Review of High Gain DC-DC Converter                                    | 15 |

| 2.4.2 Structure of Proposed DC-DC Converter                                  |    |

| 2.4.3 Component Selection                                                    | 21 |

| 2.5 Simulation Results and Discussion                                        |    |

| 2.6 Conclusion                                                               |    |

| Chapter 3. Common-Mode Behavior.                                             | 26 |

| 3.1 Introduction                                                             |    |

| 3.2 Common Mode Model                                                        |    |

| 3.3 Methods of Leakage Current Reduction                                     |    |

| 3.3.1 Galvanic Isolation                                                     |    |

| 3.3.2 CMV Clamping                                                           |    |

| 3.4 Conclusion                                                               |    |

| 5.4 Colletusion                                                              | 51 |

| Chapter 4. Review and Comparison of Single Phase Transformerless PV Inverter |    |

| Topologies                                                                   |    |

| 4.1 Transformerless Inverter Based on Full Bridge Topology                   |    |

| 4.1.1 Full-Bridge Topology                                                   |    |

| 4.1.2 H5 Topology                                                            | 43 |

| 4.1.3 H6 Topology                                                            |    |

| 4.1.4 H6-I Topology                                                          | 49 |

| 4.1.5 Proposed Topology                                                      | 52 |

| 4.2 Power Loss Analysis                                                      | 58 |

| 4.3 Total Losses and Performance Analysis                                    | 60 |

| 4.4 Conclusion                                                               | 62 |

| Chapter 5. Wide-Bandgap (WBG) Power Devices                                      | 64  |

|----------------------------------------------------------------------------------|-----|

| 5.1 Introduction                                                                 | 64  |

| 5.2 Physical Characteristics of WBG Materials                                    | 64  |

| 5.2.1 Higher Operating Temperature                                               | 65  |

| 5.2.2 Low ON-State Resistance                                                    | 66  |

| 5.2.3 Higher Switching Speed                                                     | 66  |

| 5.3 Loss Evaluation of Si IGBT and SiC MOSFET Power Devices                      | 66  |

| 5.3.1 Evaluation of Conduction Losses                                            | 67  |

| 5.3.2 Evaluation of Switching Losses                                             | 68  |

| 5.4 Conclusion                                                                   | 72  |

| Chapter 6. Benefits of SiC MOSFET in PV System                                   | 73  |

| 6.1 Introduction                                                                 |     |

| 6.2 Performance Enhancement of the Proposed High Gain DC-DC Converter            | 73  |

| Using SiC MOSFET                                                                 | 73  |

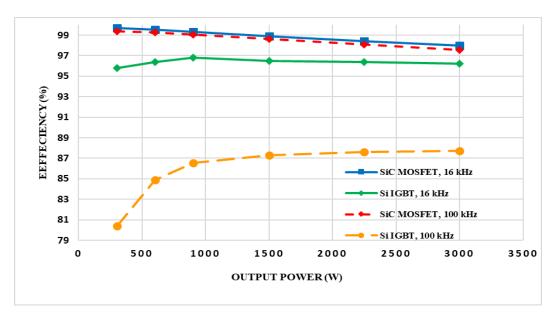

| 6.3 Benefits of SiC MOSFET in the Proposed Transformerless Inverter              | 77  |

| 6.3.1 Efficiency Improvement                                                     | 78  |

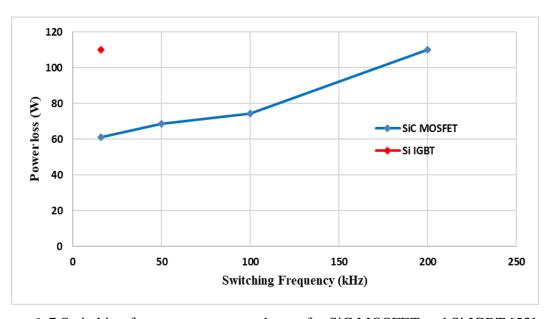

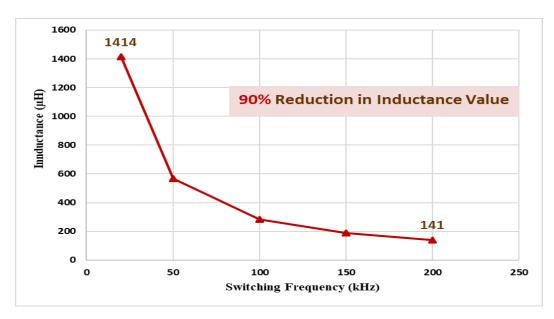

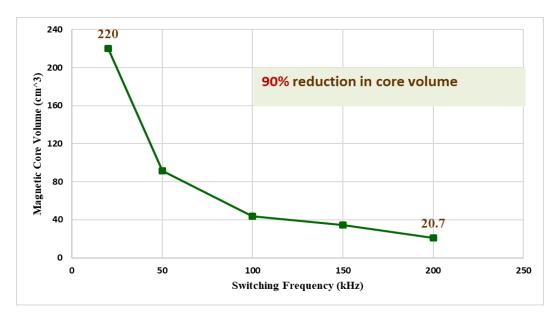

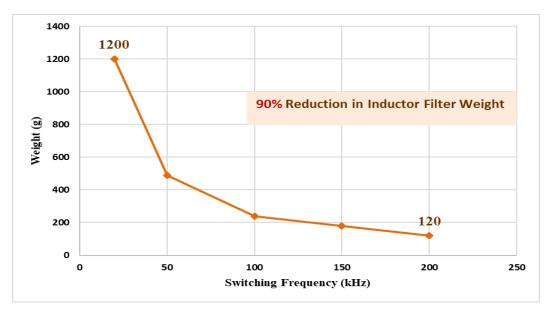

| 6.3.2 Switching Frequency vs. Inductor Volume                                    | 80  |

| 6.3.3 Increasing Power Rating                                                    | 83  |

| 6.4 Thermal Model Simulation and Heat Sink Design                                | 84  |

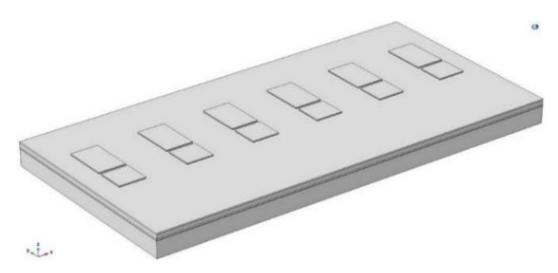

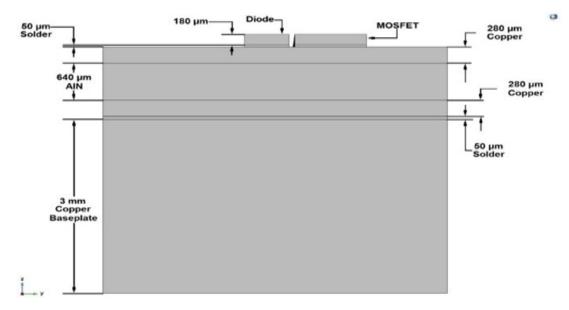

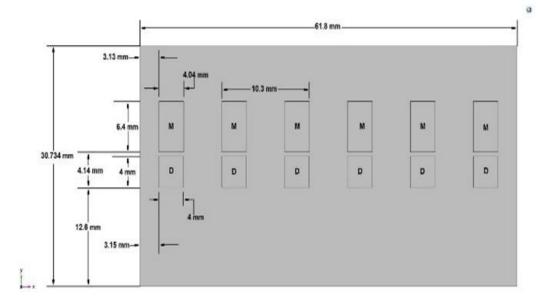

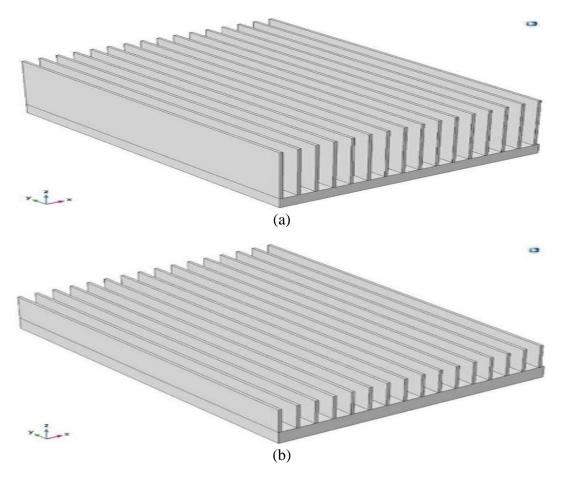

| 6.4.1 Model Geometry                                                             | 85  |

| 6.4.2 Material Properties                                                        | 88  |

| 6.4.3 Heat Transfer Physics Modelling                                            |     |

| 6.4.4 Model Simulation and Results                                               | 90  |

| 6.5 Conclusion                                                                   | 93  |

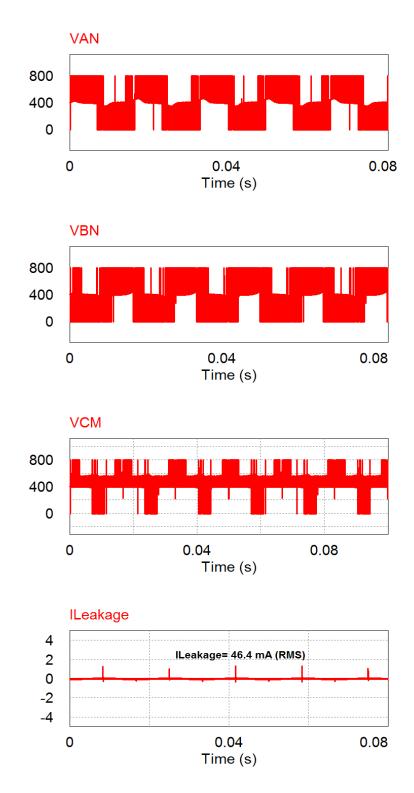

| Chapter 7. Improved Proposed Converter for Reactive Power Generation and Leakage | ;   |

| Current Elimination                                                              | 95  |

| 7.1 Introduction                                                                 | 95  |

| 7.2 Proposed Topology with Leakage Current Elimination and Reactive Power        | •   |

| Generation                                                                       |     |

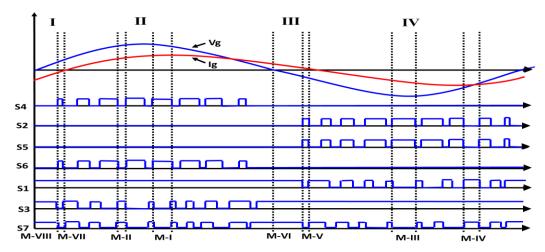

| 7.2 Modulation Technique for Reactive Power Generation                           | 100 |

| 7.3 Simulation Results                                                           |     |

| 7.4 Conclusion                                                                   | 115 |

| Chapter 8. Conclusion and Recommendations for Future Study                       | 117 |

| 8.1 Conclusion                                                                   |     |

| 8.2 Considerations for Future Research                                           | 118 |

| References                                                                       | 120 |

| List of Publications                                                             | 140 |

# **List of Figures**

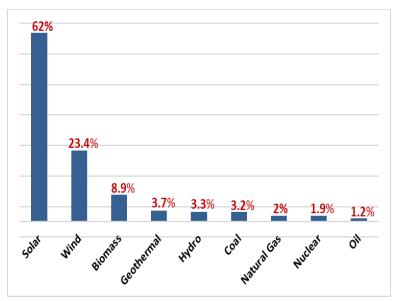

| Figure 2. 1. Global annual growth of energy [6]                                          | 6    |

|------------------------------------------------------------------------------------------|------|

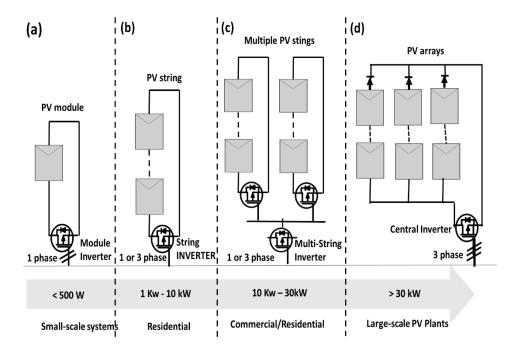

| Figure 2. 2 PV system configurations: (a) module inverter; (b) string inverter; (c) mul- | ti-  |

| string inverter; and, (d) central inverter [7]                                           | 9    |

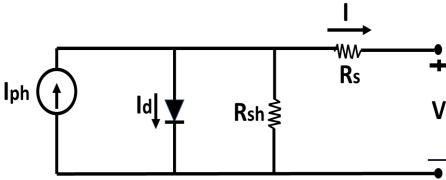

| Figure 2. 3 PV cell equivalent circuit                                                   | 10   |

| Figure 2. 4 PV module in PSIM                                                            | 12   |

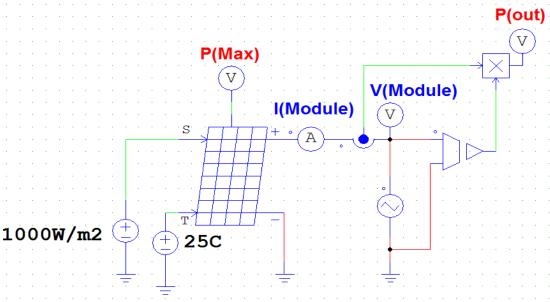

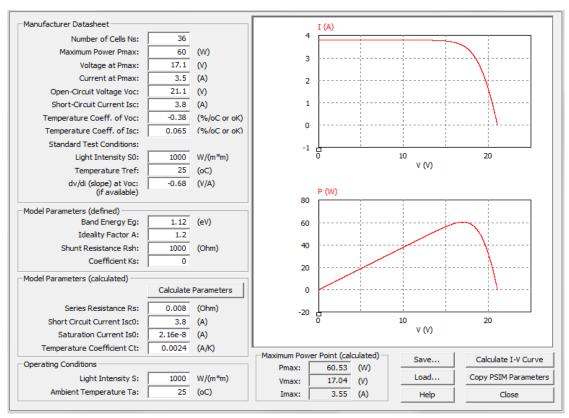

| Figure 2. 5 Physical model simulator of a PV cell in PSIM                                | 13   |

| Figure 2. 6 PV characteristics of solar array                                            |      |

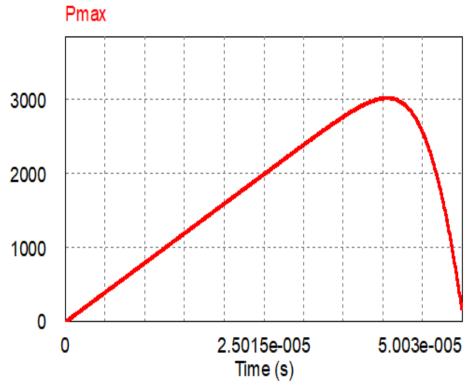

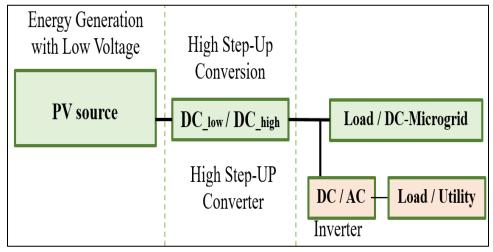

| Figure 2. 7 Structure of PV system                                                       |      |

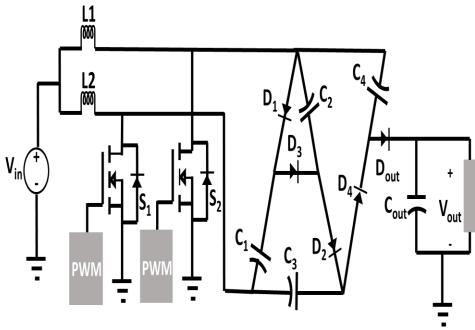

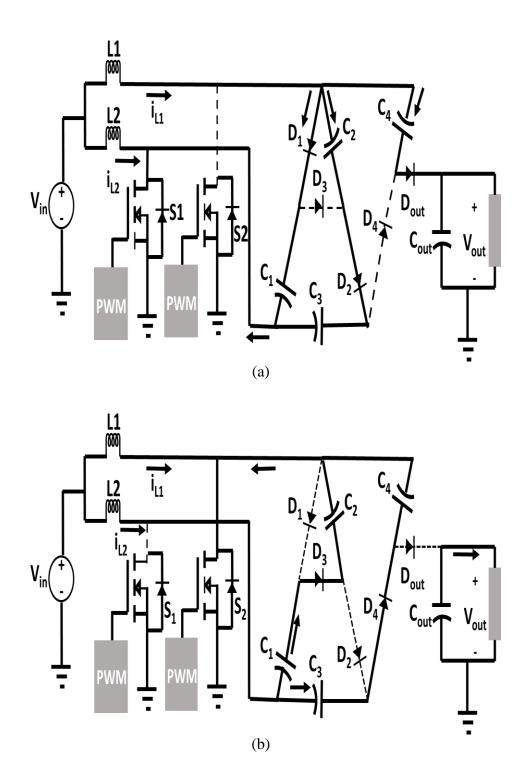

| Figure 2. 8 Circuit structure of the proposed topology                                   | 18   |

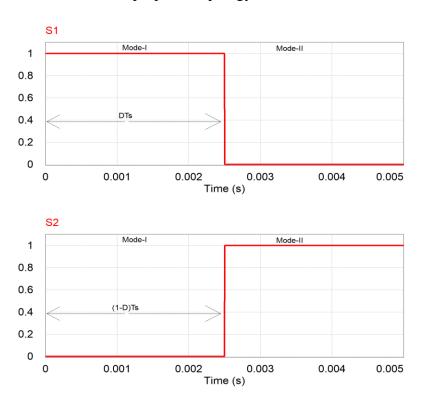

| Figure 2. 9 Switching signals of proposed topology                                       |      |

| Figure 2. 10 Operation modes. (a) Mode I; and, (b) Mode II                               | . 19 |

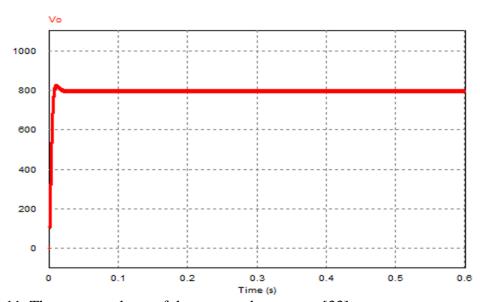

| Figure 2. 11 The output voltage of the proposed converter [33]                           |      |

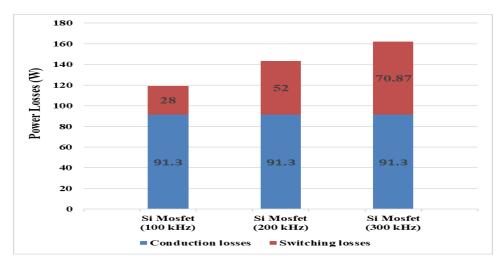

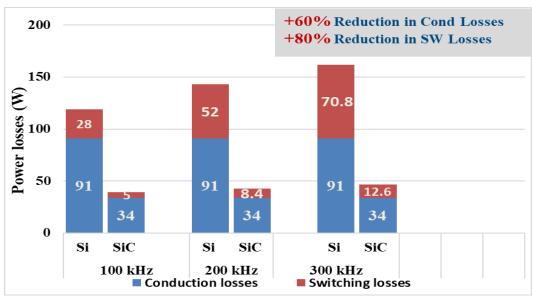

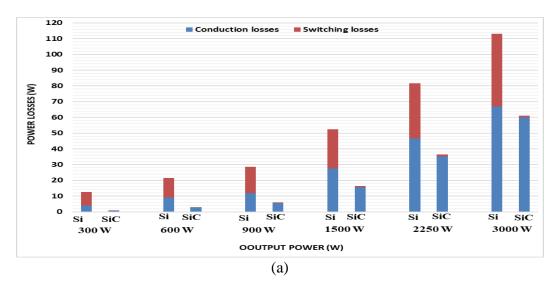

| Figure 2. 12 Conduction and switching losses of Si and SiC MOSFET at different           |      |

| switching frequencies [33]                                                               |      |

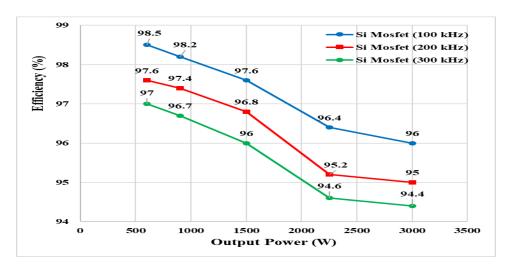

| Figure 2. 13 Efficiency comparison of Si MOSFET at different switching frequencies       |      |

| with different output power loads [33]                                                   |      |

|                                                                                          |      |

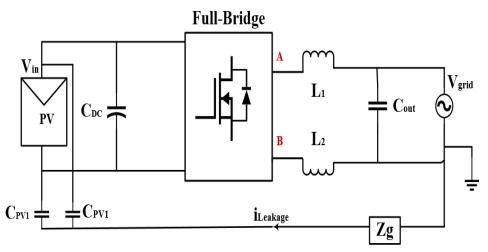

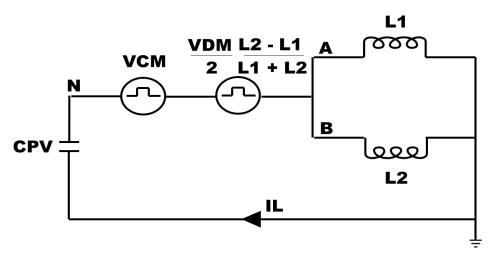

| Figure 3. 1 Current leakage path in resonant circuit                                     | 27   |

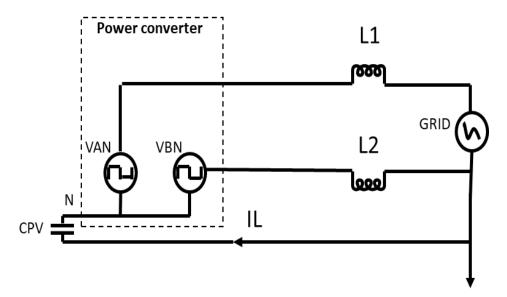

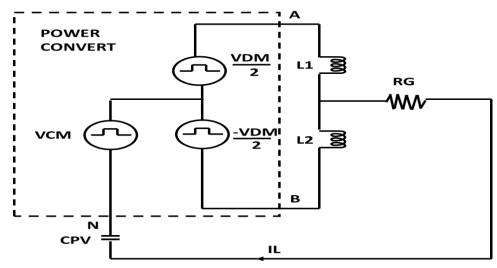

| Figure 3. 2 Simplified path of leakage current in single phase inverter                  | 29   |

| Figure 3. 3 The second simplified circuit of leakage current path                        |      |

| Figure 3. 4 The third and final simplified resonant circuit of leakage current path      | 31   |

| Figure 3. 5 Circuit structure of galvanic isolation with DC and AC decoupling metho      | d32  |

| Figure 3. 6 Conduction mode during positive active state with DC decoupling              |      |

| Figure 3. 7 Freewheeling mode with DC decoupling                                         |      |

| Figure 3. 8 Circuit structure with clamping method                                       |      |

| Figure 3. 9 Conduction mode during the positive active state with clamping method        |      |

| Figure 3. 10 Freewheeling mode with clamping method                                      |      |

|                                                                                          |      |

| Figure 4. 1 Circuit diagram of full bridge topology                                      | 39   |

| Figure 4. 2 Bipolar modulation strategy of H4 topology                                   | . 40 |

| Figure 4. 3 Common mode characteristics of H4 topology with bipolar modulation           |      |

| Figure 4. 4 Unipolar modulation strategy of H4 topology                                  | 42   |

| Figure 4. 5 Common mode characteristics of H4 topology                                   | 43   |

| Figure 4. 6 Circuit structure of H5 topology                                             | . 44 |

| Figure 4. 7 Switching waveform of H5 topology                                            | 45   |

| Figure 4. 8 Common mode characteristics of H5 topology                                   | . 46 |

| Figure 4. 9 Circuit diagram of H6 topology                                               |      |

| Figure 4. 10 Modulation strategy of H6 topology                                          | . 48 |

| Figure 4. 11 Common mode characteristics of H6 topology                                  |      |

| Figure 4. 12 Circuit structure of H6-I topology                                          |      |

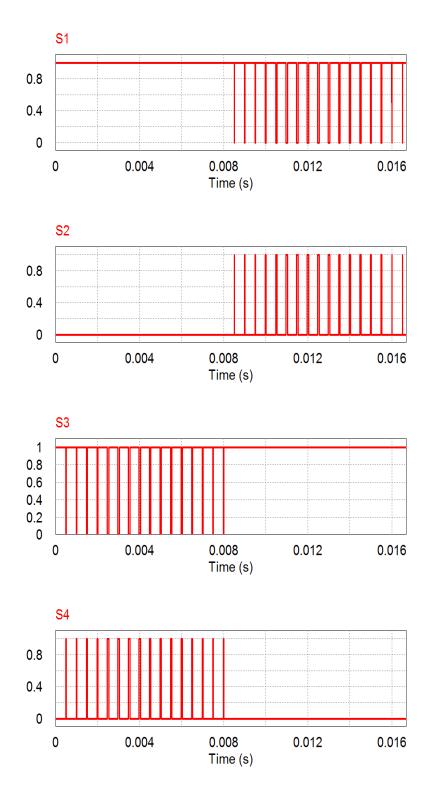

| Figure 4. 13 Switching waveforms of H6-I topology                                        |      |

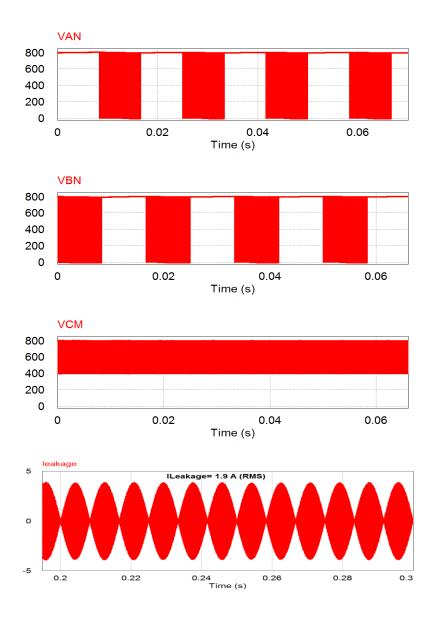

| Figure 4. 14 Common mode characteristics of H6-I topology                                |      |

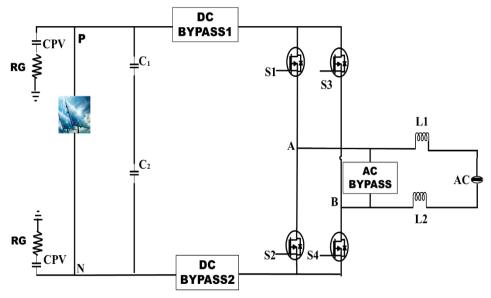

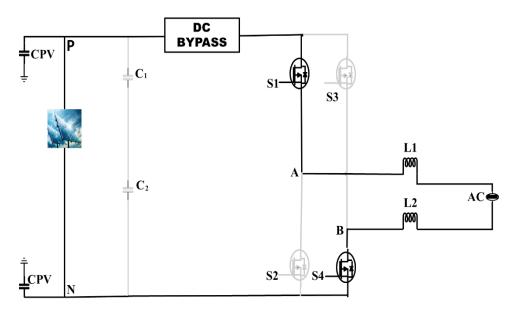

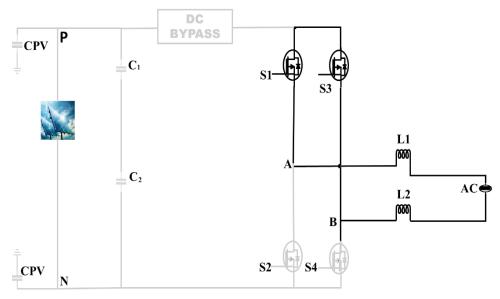

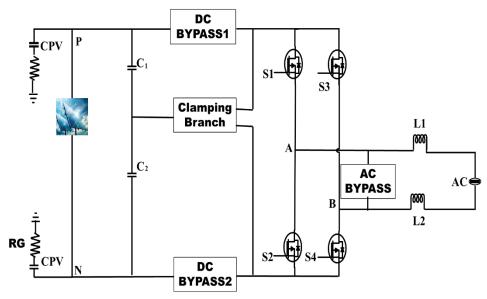

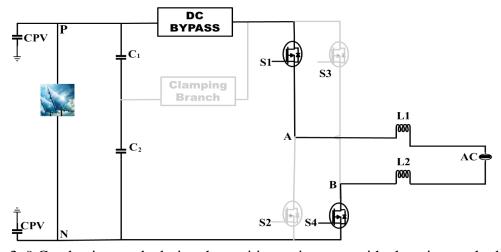

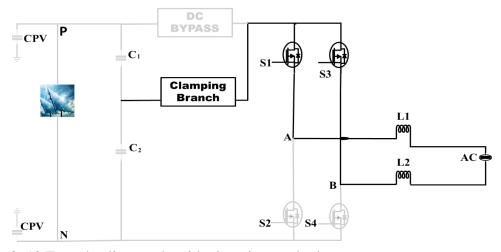

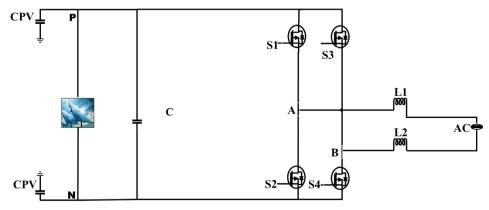

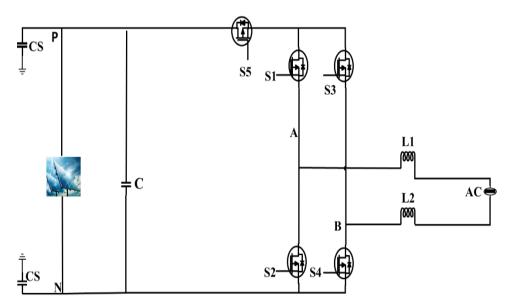

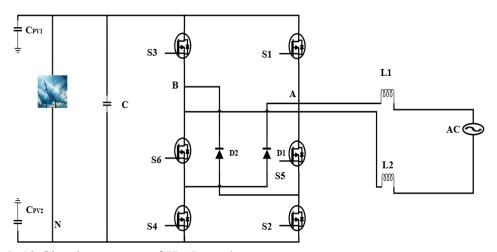

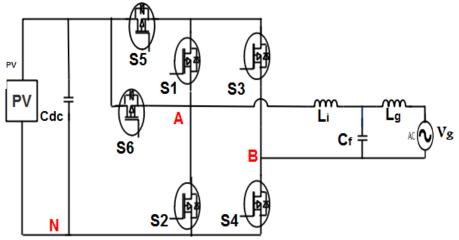

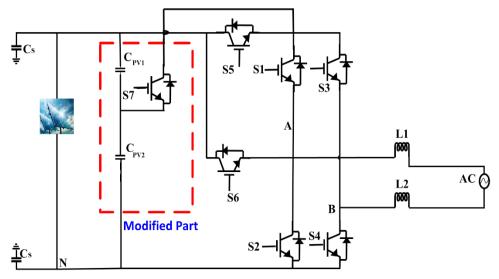

| Figure 4. 15 Circuit structure of the proposed topology                                  |      |

|                                                                                          |      |

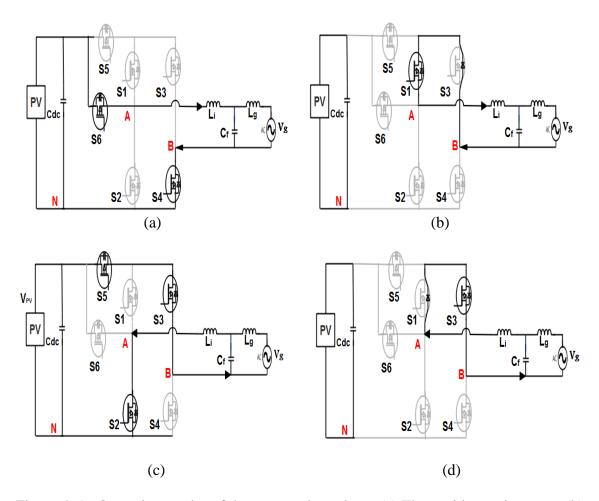

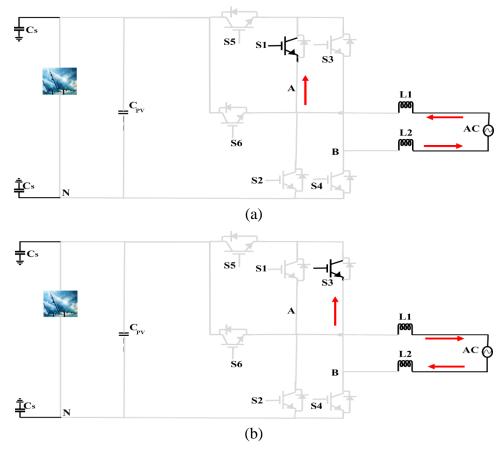

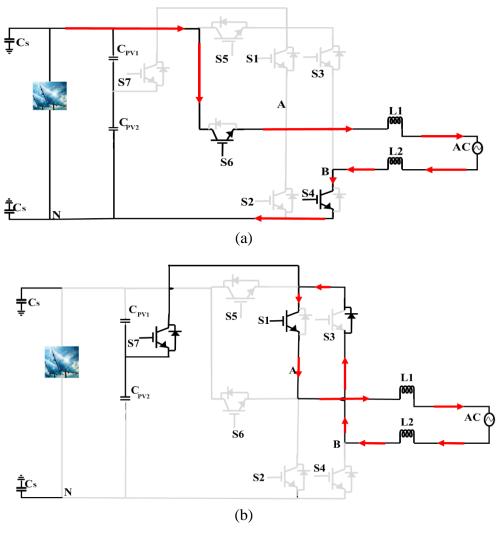

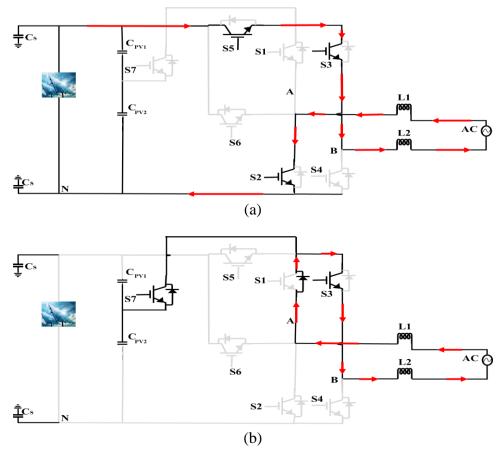

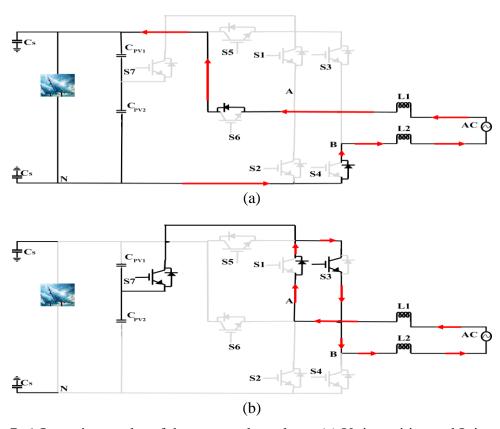

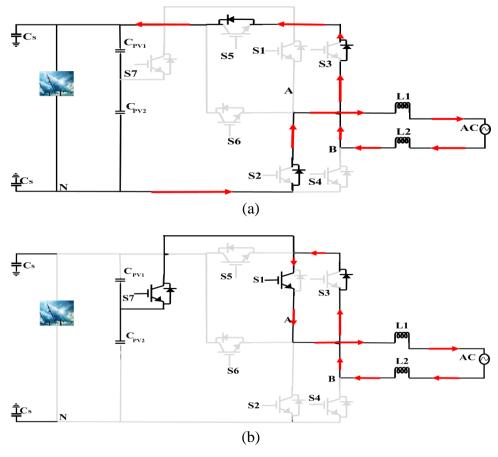

| Figure 4. 16 Operation modes of the proposed topology. (a) The positive active state; (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (b)   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| the zero state during the positive half period; (c) the negative active state; and, (d) the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

| zero state during the negative half period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54    |

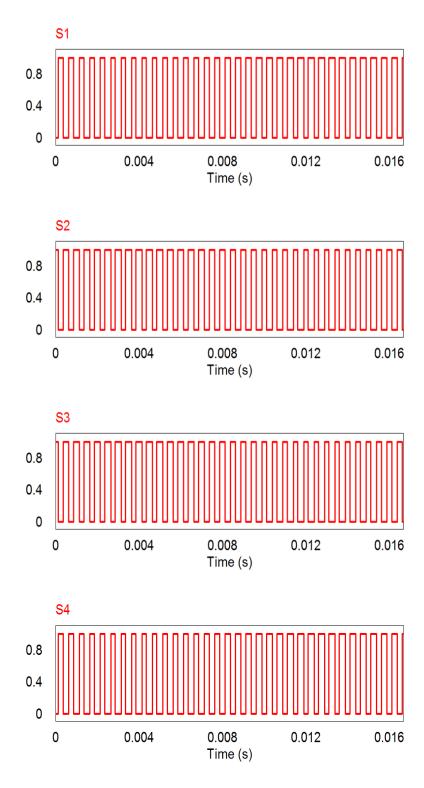

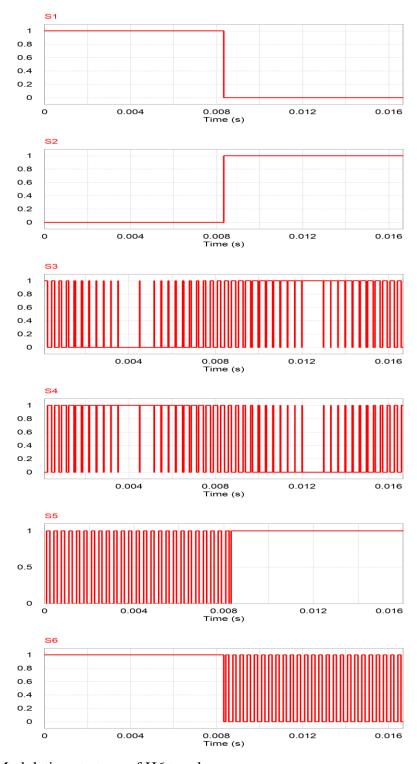

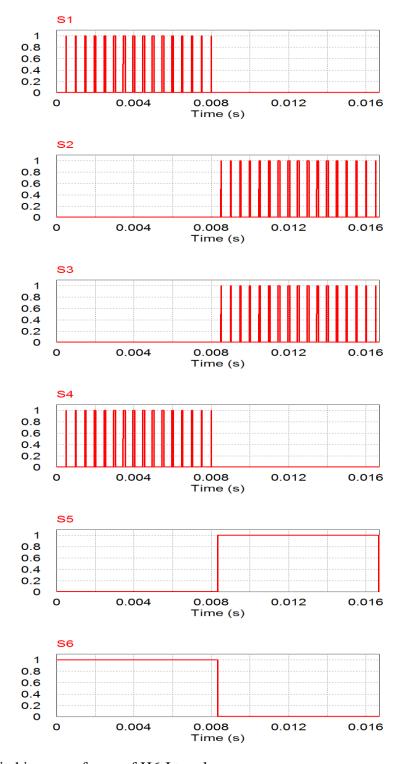

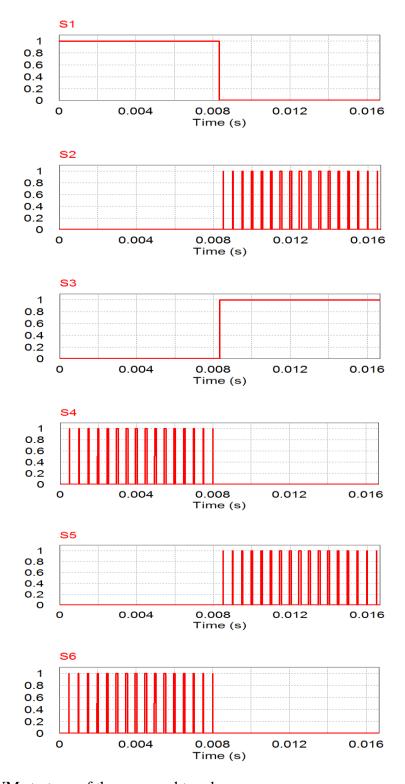

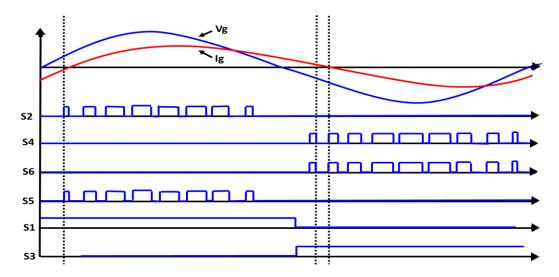

| Figure 4. 17 PWM strategy of the proposed topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55    |

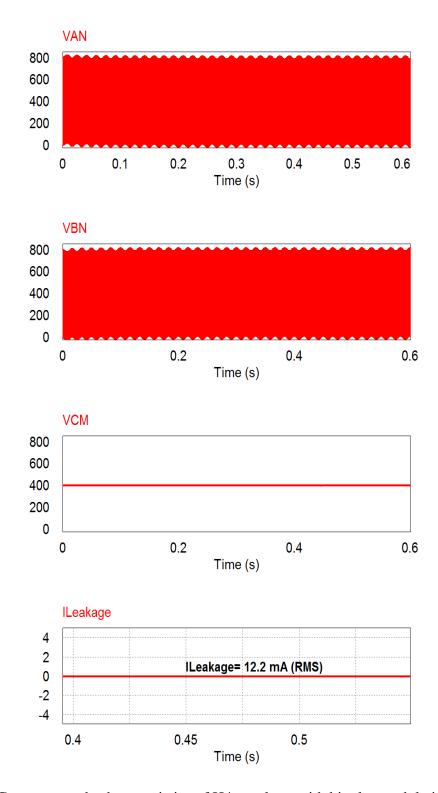

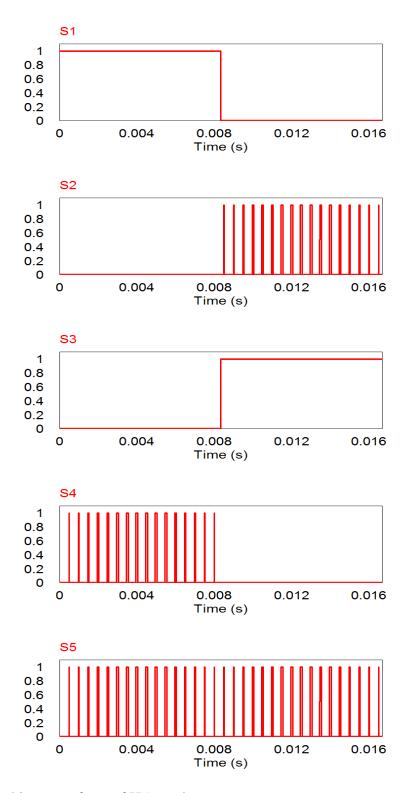

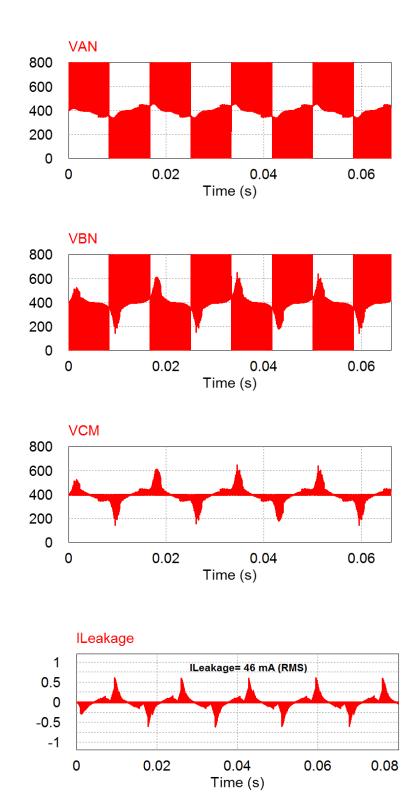

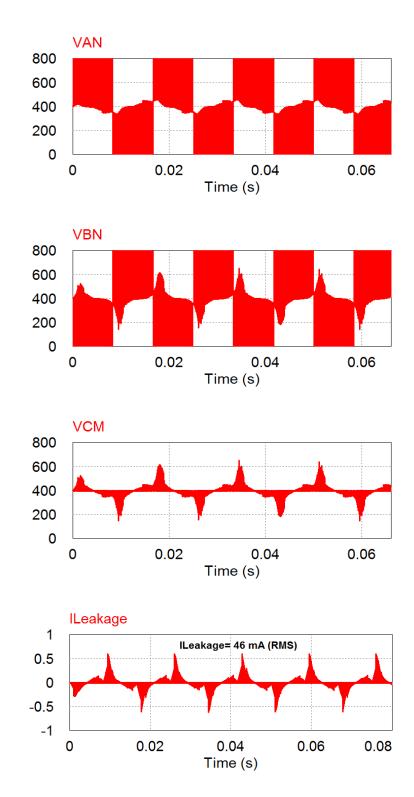

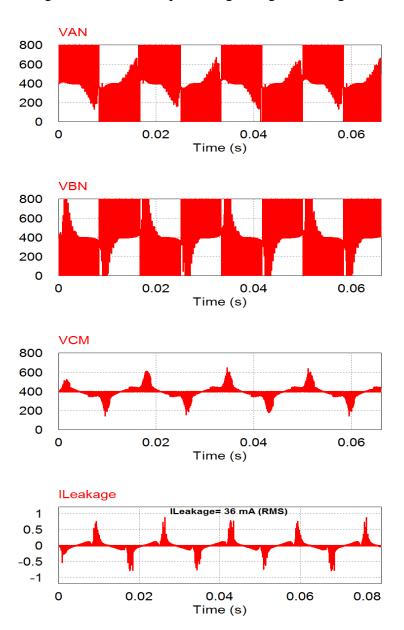

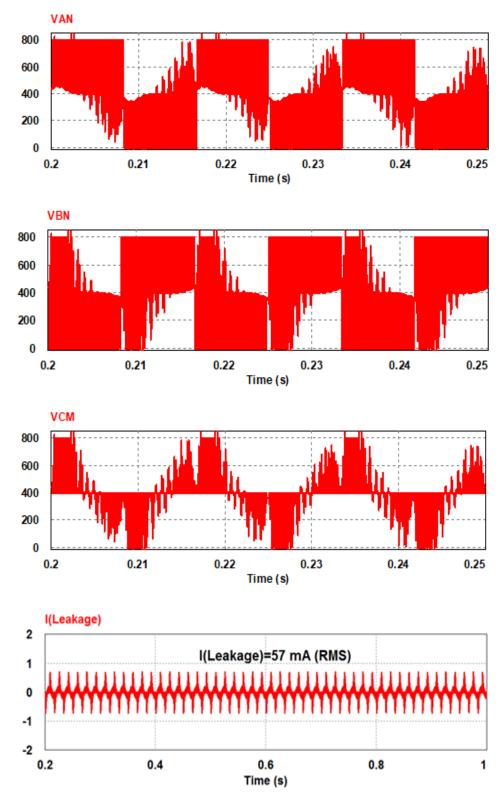

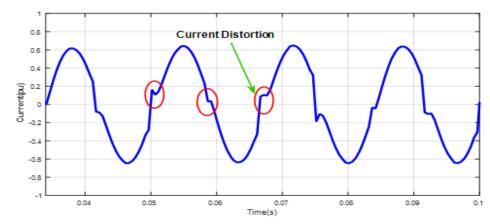

| Figure 4. 18 Common mode characteristics of the proposed topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

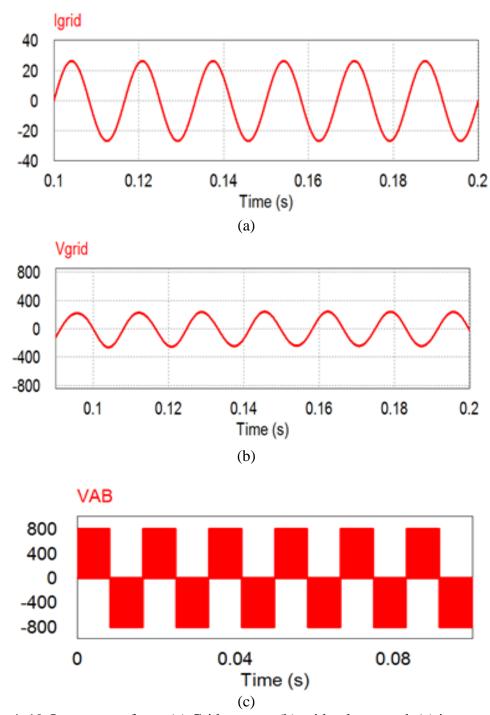

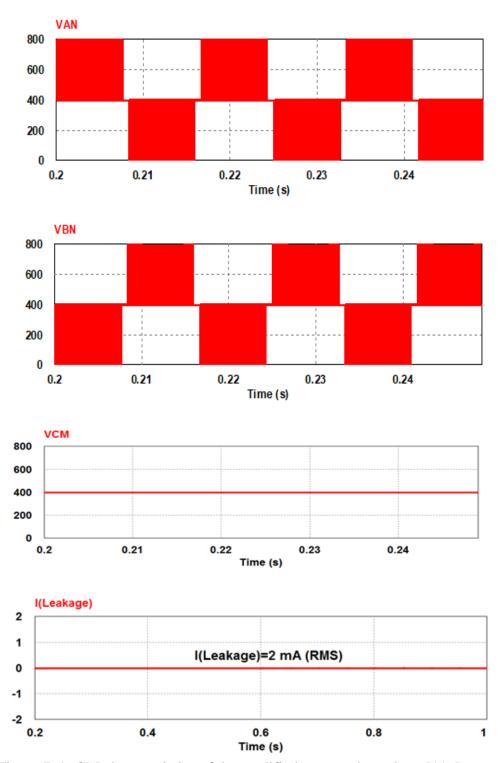

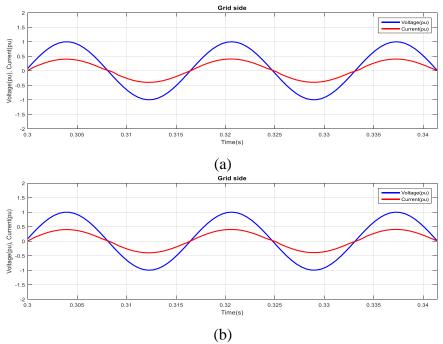

| Figure 4. 19 Output waveform. (a) Grid current; (b) grid voltage; and, (c) inverter outp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

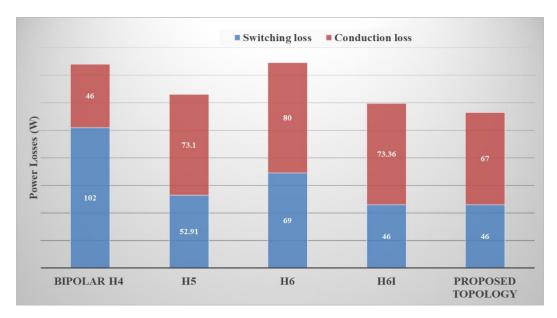

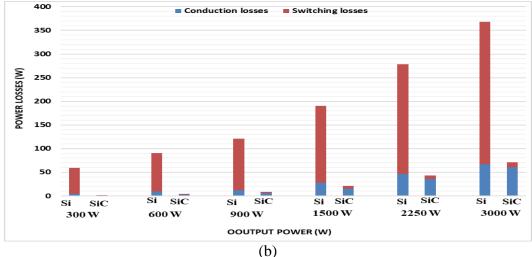

| Figure 4. 20 Conduction and switching losses of various transformerless inverters at 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| kHz [53]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

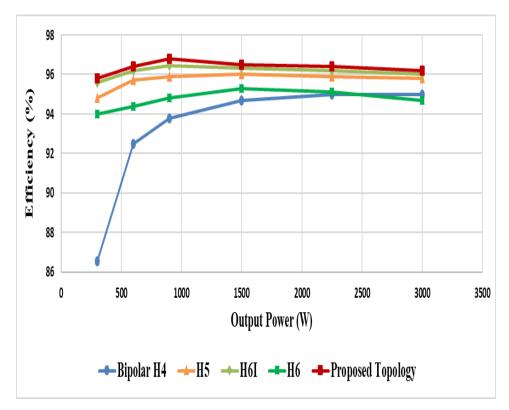

| Figure 4. 21 Efficiency comparison of various transformerless inverter topologies with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| different output power loads [53]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

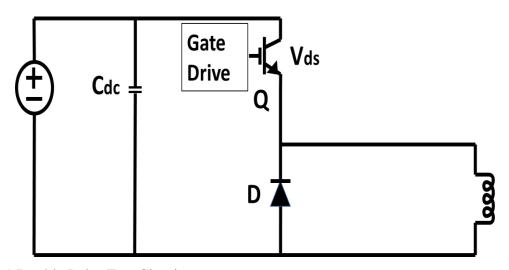

| Figure 5. 1 Double Pulse Test Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 67  |

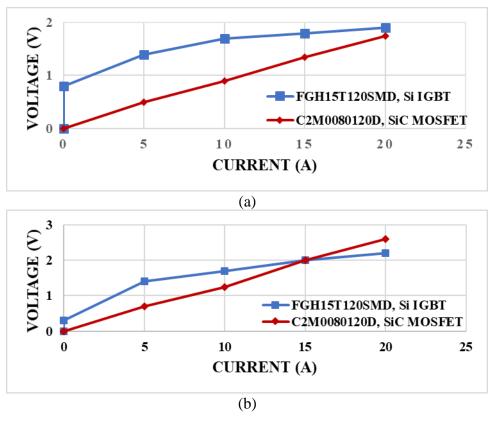

| Figure 5. 2 (a) Forward voltages of SiC MOSFET and Si IGBT at 25 °C; and, (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| forward voltages of SiC MOSFET and Si IGBT at 175 °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 68  |

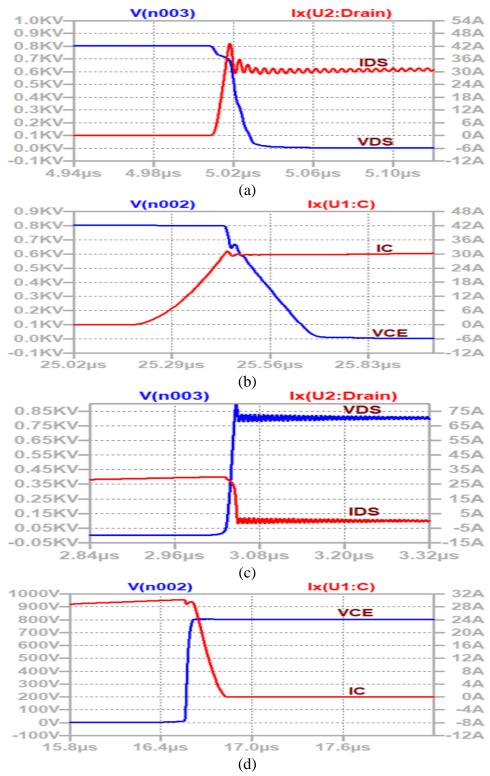

| Figure 5. 3 Switching transitions of switching devices for a voltage of 800 V and 30 A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| (a) Turn-ON SiC MOSFET; (b) turn-ON Si IGBT; (c) turn-OFF SiC MOSFET; and, (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| turn-OFF Si IGBT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

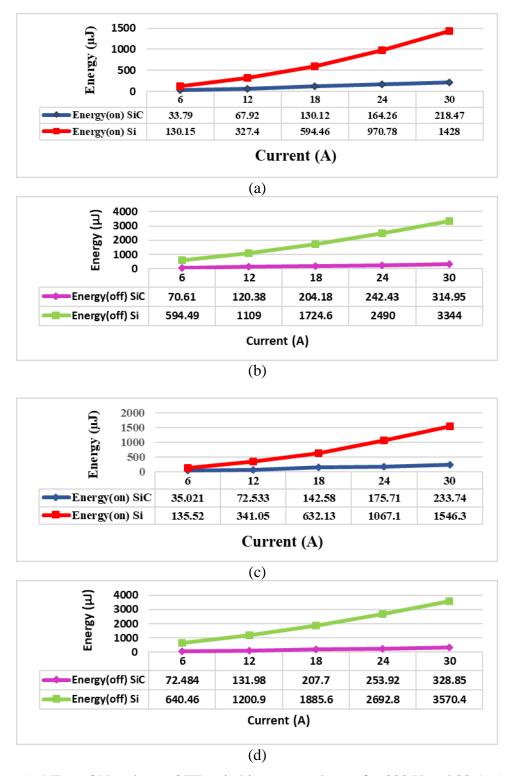

| Figure 5. 4 Turn-ON and turn-OFF switching energy losses for 800 V and 30 A. (a) Tu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

| ON energies at 25°C; (b) turn-OFF energies at 25°C; (c) turn-ON energies at 100°C; an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| (d) turn-OFF energies at 100°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ,     |

| (a) turn of the chergies at 100 dimensional management of the chercies at 100 dimensional management of the cherci | . , 1 |

| Figure 6. 1 Conduction and switching losses of Si and SiC MOSFET at different                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| switching frequencies [33]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 75  |

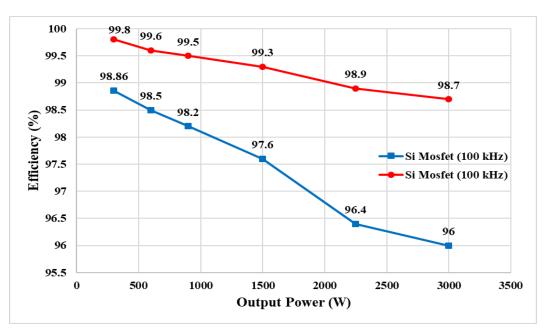

| Figure 6. 2 Efficiency comparison of Si and SiC MOSFET at 100 kHz with different                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| output power loads [33]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

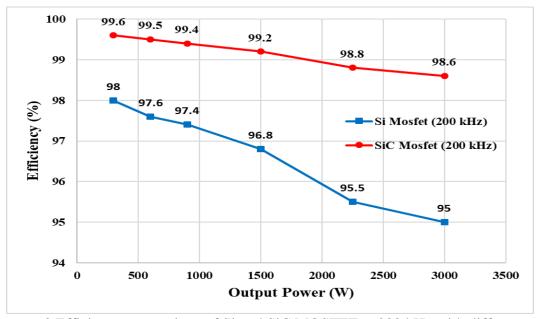

| Figure 6. 3 Efficiency comparison of Si and SiC MOSFET at 200 kHz with different                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| output power loads [33]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 76  |

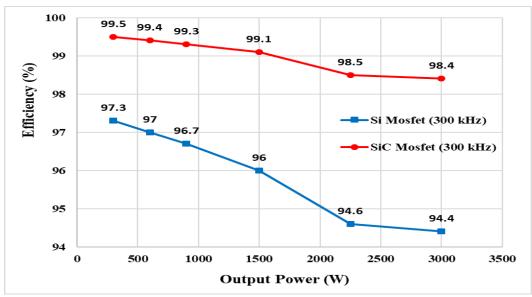

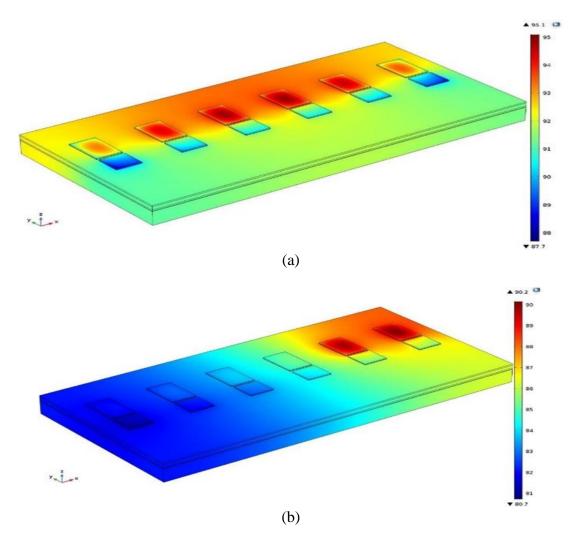

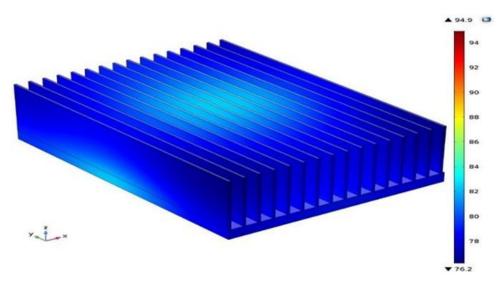

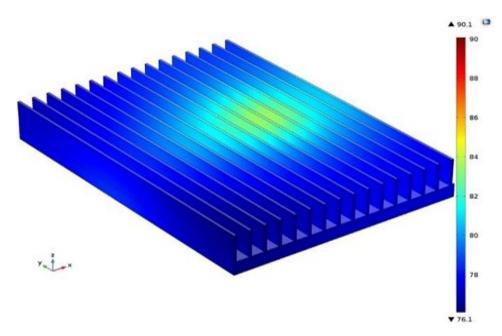

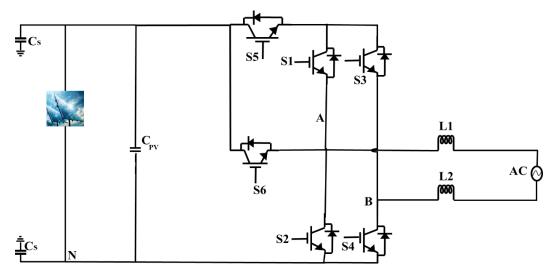

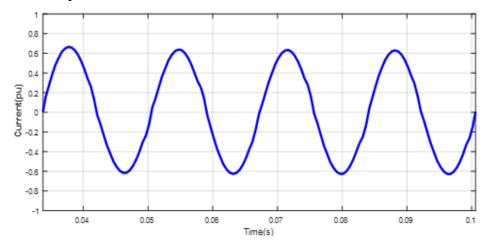

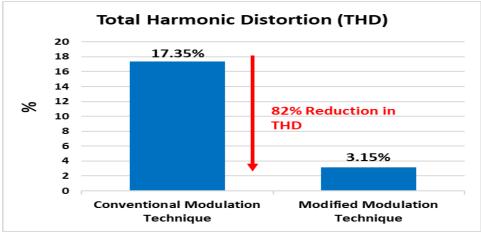

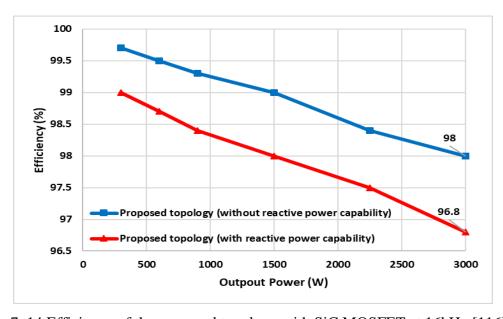

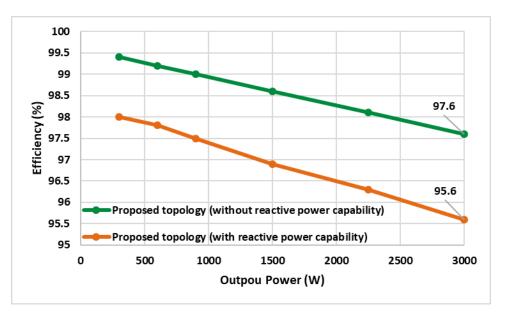

| Figure 6. 4 Efficiency comparison of Si and SiC MOSFET at 300 kHz with different                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |