University of Denver Digital Commons @ DU

**Electronic Theses and Dissertations**

**Graduate Studies**

1-1-2018

# Design of Power Switched-Capacitor Converters and Their Performance Analysis in a Soft-Charging Operation

Ayoob Alateeq University of Denver

Follow this and additional works at: https://digitalcommons.du.edu/etd

Part of the Power and Energy Commons

#### **Recommended Citation**

Alateeq, Ayoob, "Design of Power Switched-Capacitor Converters and Their Performance Analysis in a Soft-Charging Operation" (2018). *Electronic Theses and Dissertations*. 1531. https://digitalcommons.du.edu/etd/1531

This Dissertation is brought to you for free and open access by the Graduate Studies at Digital Commons @ DU. It has been accepted for inclusion in Electronic Theses and Dissertations by an authorized administrator of Digital Commons @ DU. For more information, please contact jennifer.cox@du.edu,dig-commons@du.edu.

# DESIGN OF POWER SWITCHED-CAPACITOR CONVERTERS AND THEIR PERFORMANCE ANALYSIS IN A SOFT-CHARGING OPERATION

A Dissertation

Presented to

the Faculty of the Daniel Felix Ritchie School of Engineering and Computer Science

University of Denver

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy

by

Ayoob Alateeq

November 2018

Advisor: Dr. Mohammad Matin

©Copyright by Ayoob Alateeq 2018

All Rights Reserved

Author: Ayoob Alateeq Title: DESIGN OF POWER SWITCHED-CAPACITOR CONVERTERS AND THEIR PERFORMANCE ANALYSIS IN A SOFT-CHARGING OPERATION Advisor: Dr. Mohammad Matin Degree Date: November 2018

#### Abstract

Switched-capacitor (SC) converters have gained more interest due to their high power density and appropriateness for small circuit integration. Building a SC DC-to-DC converter with only capacitors and switches is the main reason to seek a higher power density achievement. However, the SC converters suffer dominant losses related to their capacitors and switches. These losses can be determined and optimized by calculating the converter's output impedance in its two asymptotic limits.

We proposed a high voltage gain and a very low output impedance power switchedcapacitor converter (PSC) with a lower number of components compared to other step-up switched-capacitor topologies. The high output efficiency and the higher power density are two fundamental aspects of the PSC converter.

We can eliminate the current transient by applying the soft-charging technique that results a higher power density and a higher efficiency in PSC. The soft-charging operation is more preferable to the soft-switching technique (resonant operation) since it does not require any auxiliary components. Furthermore, soft-charging helps to resize capacitors and reduce the switching frequency of the PSC converter.

Furthermore, a split-phase control design is proposed to achieve the complete softcharging operation in a PSC. The control diagram was designed for a 1-to-4 PSC (two levels of the PSC) which controls eight switches to exhibit eight modes of operation. The complete soft-charging accomplishes a 96% efficiency due to the lower output impedance and the dead time switching. LT-spice software has been used to verify the proposed control, and the results were compared with hard-charging and incomplete soft-charging operations.

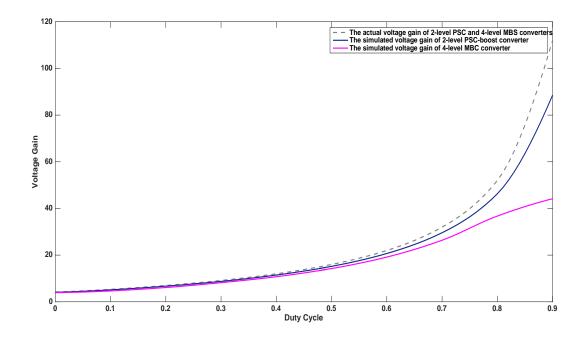

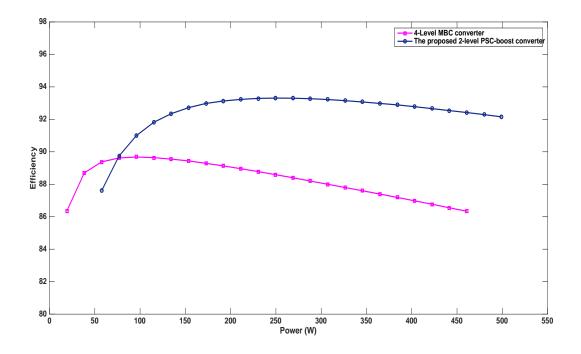

In this research, we also proposed a two-level power switched-capacitor boost converter (PSC-boost) for a high voltage gain application by integrating a PSC converter and a conventional boost converter. The PSC switched-capacitors and the conventional boost converter are respectively cascaded as a primary and a secondary side of the proposed converter. Without alerting of the secondary side (conventional boost), the conversion ratio can be increased by adding more switched-capacitors cells. The proposed converter similarly acts as an MBC; however, it can maintain the rated voltage gain at a higher duty cycle. Unlike the MBC converter, the simulated voltage gain is closer to the calculated voltage gain for PSC-boost converter. In addition to the switched-capacitors insertion, a switched inductor model is used instead of the single inductor in the traditional boost converter. Five switches, five capacitors, seven diodes, and three inductors are used to build a PSC-boost switched-inductor converter. The PSC-boost converter accomplishes 94% efficiency which a higher rated power.

#### Acknowledgements

I would like to express the deepest appreciation to my advisor Dr. Mohammad Matin for accepting me into his research group. This work would not have been accomplished without his support and motivation. Dr. Matin encouraged and supported me during the period of my doctoral program from my first day at the University of Denver until the last word I wrote in this dissertation. I also would like to thanks to my gratitude to committee members, Professor David Gao, Drs. Amin Khodaei, and Shimelis Assefa, for their cooperation and advice.

Special acknowledgments go to my father, my brothers, and my sisters who supported and motivated me in my life, especially in my study journey. Most importantly, acknowledgments go to my loving and supportive wife Reem and my wonderful daughter Miral, who provide unending inspiration.

| Abstractii                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                               |

| Acknowledgements iv                                                                                                                                                                                                                                                                                           |

| List of Figures                                                                                                                                                                                                                                                                                               |

| List of Tables ix                                                                                                                                                                                                                                                                                             |

| CHAPTER ONE: INTRODUCTION       1         1.1 DC-to-DC converters       .7         1.3 Slow-switching limit impedance of a 4-to-3 series to parallel SC converter       .12         1.4 Problem Statement       .15         1.5 Methodology       .15         1.6 The Structure of the Dissertation       .16 |

| CHAPTER TWO: A SERIES OF POWER SWITCHED-CAPACITOR (PSC)<br>CONVERTERS                                                                                                                                                                                                                                         |

| <ul> <li>2.2 Power switched-capacitor (PSC) converter; topology and operation</li></ul>                                                                                                                                                                                                                       |

| CHAPTER THREE: AN INCOMPLETE SOFT-CHARGING OPERATION OF THE SECOND ORDER PSC CONVERTER                                                                                                                                                                                                                        |

| CHAPTER FOUR: A COMPLETE SOFT-CHARGING OPERATION OF THE SECOND<br>ORDER PSC CONVERTER                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                               |

### **Table of Contents**

| CHAPTER FIVE: PSC CONVERTER APPLICATION FOR HIGH GAIN PROVIS                   | SION  |

|--------------------------------------------------------------------------------|-------|

|                                                                                | 62    |

| 5.1 Introduction                                                               | 62    |

| 5.2 The proposed design MBC with switched inductor model                       | 65    |

| 5.3 Modes of operation of MBC                                                  | 65    |

| 5.3.1 Mode 1                                                                   |       |

| 5.3.2 Mode 2                                                                   | 65    |

| 5.4 Analysis of the proposed switched inductors boost converter                | 66    |

| 5.5 A comparison between the proposed MBC and two other MBC topologies .       | 70    |

| 5.6 Using a PSC converter as a voltage multiplier for a DC-to-DC switched-indu |       |

| boost converter                                                                |       |

| 5.7 Analysis of the proposed switched inductors model by using PSC cells as vo | ltage |

| multipliers                                                                    | -     |

| 5.8 Modes of operation of PSC-boost converter                                  |       |

| 5.9 Analysis of the PSC-boost converter                                        |       |

| 5.10 Simulated results and a comparison of PSC-boost and MBC converter         |       |

| CHAPTER SIX: CONCLUSION AND FUTURE WORK                                        | 86    |

| 6.1 Conclusion                                                                 | 86    |

| 6.2 Future Work                                                                |       |

| References                                                                     | 90    |

| Appendix                                                                       | 105   |

| List of Publications                                                           |       |

## List of Figures

| Figure 1.1: Three step-up SC converter topologies (a) 1-to-4 Dickson (b) 1-to-4 ladder (c) 1-to-4 series-parallel                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: Output impedance of a typical SC converter                                                                                                                                                   |

| Figure 1.3: A comparison of four SC converter topologies including the proposed PSC in                                                                                                                   |

| the number of switches and capacitors                                                                                                                                                                    |

| Figure 1.4: A conventional boost converter design                                                                                                                                                        |

| Figure 1.5: A 4-to3 series to parallel SC converter [10]9                                                                                                                                                |

| Figure 1.6: A simulated LTspice result of a 4-to-3 series to parallel SC converter14                                                                                                                     |

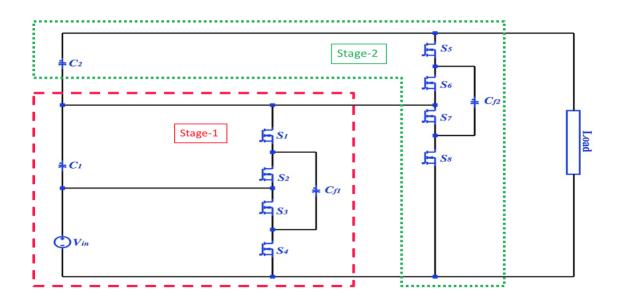

| Figure 2.1: A 1-to-4 PSC topology (two-stage)                                                                                                                                                            |

| Figure 2.2: LTspice design of a 1-to-4 PSC topology (two-stage)20                                                                                                                                        |

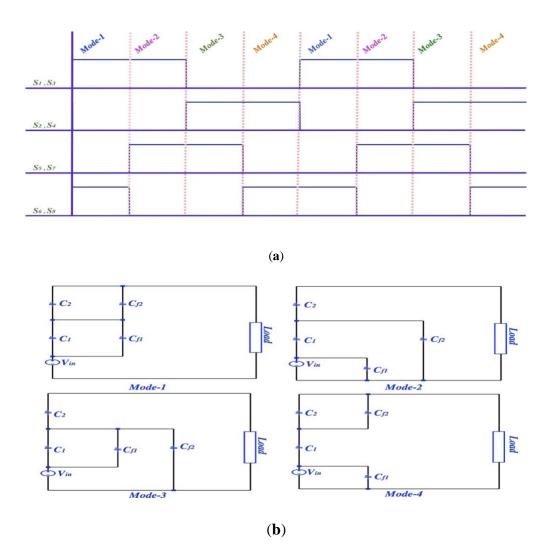

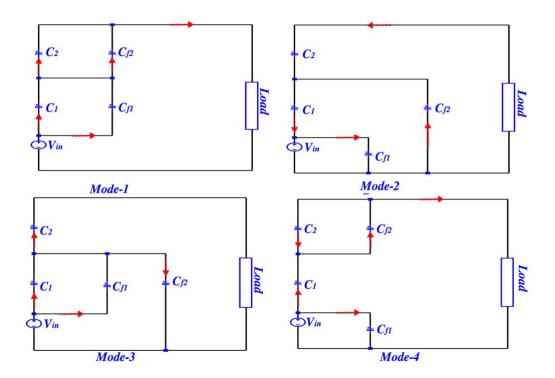

| Figure 2.3: (a) Timing diagram of a 1-to-4 PSC topology; (b) four-mode operation of a 1-to-4 PSC converter                                                                                               |

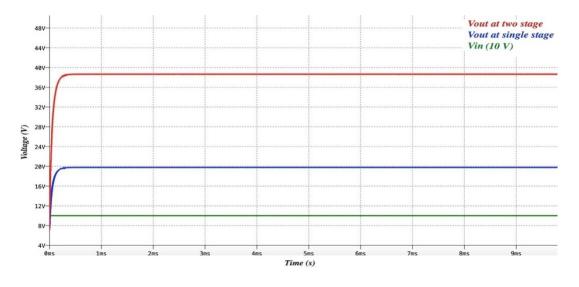

| Figure 2.4: The input and output voltages of a 1-to-4 and 1-to-2 of the proposed PSC converter.                                                                                                          |

| Figure 2.5: Efficiency vs rated power of a 1-to-4 at 10V and 5V input                                                                                                                                    |

| Figure 2.6: A 1-to-8 PSC topology (three-stage)                                                                                                                                                          |

| Figure 2.7: The charge flow for the operation modes in the 1-to-4 PSC converter                                                                                                                          |

|                                                                                                                                                                                                          |

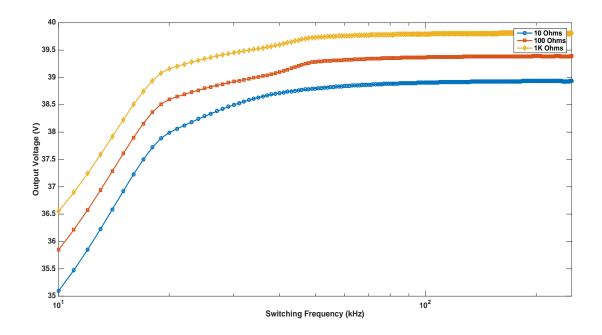

| Figure 2.8: Switching frequency against the output voltage                                                                                                                                               |

| Figure 2.9: The 1-to-4 PSC efficiency at different capacitors' sizes                                                                                                                                     |

| Figure 2.10: a) voltage doubler converter b) a generalized control diagram of the PSC                                                                                                                    |

| S2 Figure 2.11: Two cascaded voltage doubler converters and formalized two stages of PSC                                                                                                                 |

| converter                                                                                                                                                                                                |

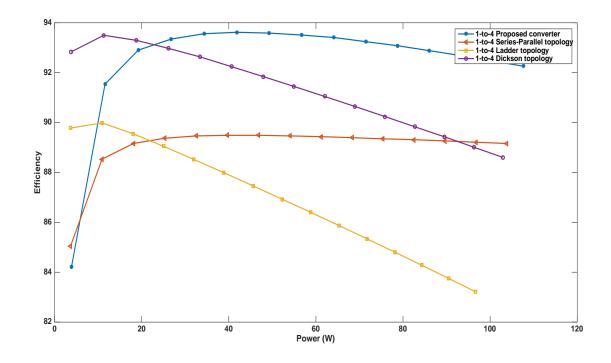

| Figure 2.12: The efficiency of four compared topologies at different rated power34                                                                                                                       |

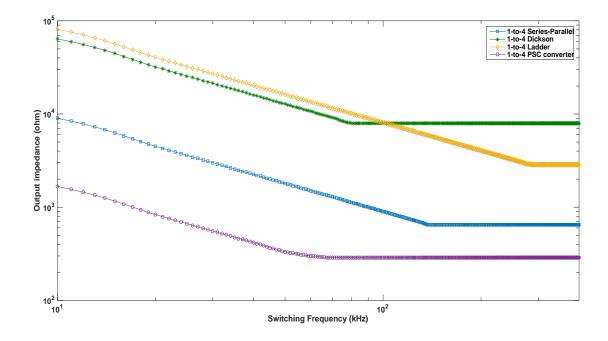

| Figure 2.13: The output impedance of four compared topologies at different switching frequency                                                                                                           |

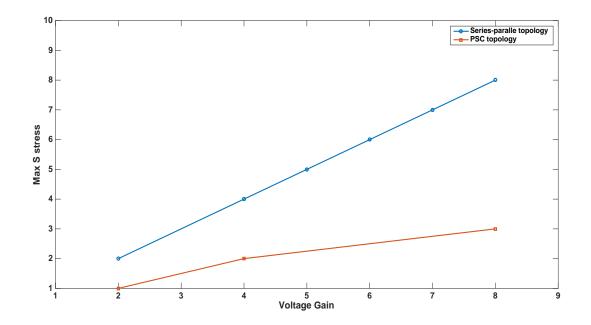

| Figure 2.14: A comparison between PSC and series to parallel topologies in maximum stress on switches                                                                                                    |

| Figure 2.15: A comparison between PSC and series to parallel topologies in number of                                                                                                                     |

| switches                                                                                                                                                                                                 |

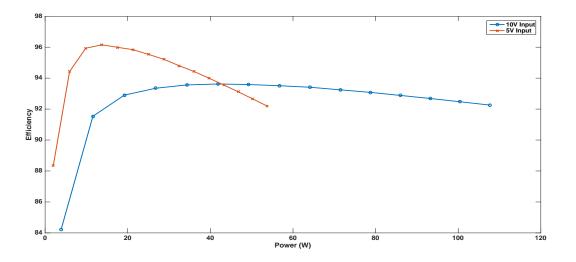

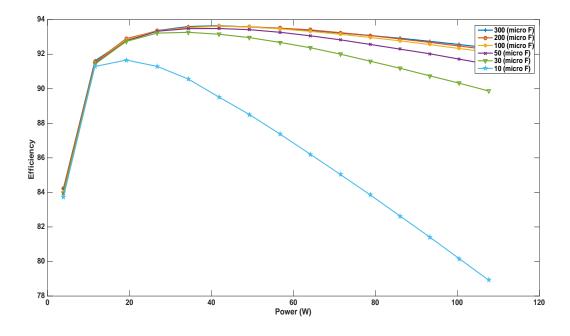

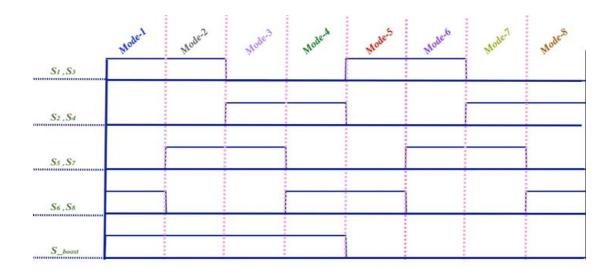

| Figure 4.1: (a) A proposed timing diagram to achieve a complete soft-charging in the 1-to-4 PSC converter; (b) eight operation modes of the 1-to-4 PSC converter in the complete soft-charging technique |

| Figure 4.2: The charge flow for the split operation modes in the 1-to-4 PSC converter46                                                                                                                  |

| Figure 4.3: The 1-to-4 PSC topology with an output LC filter                                                                                                                                             |

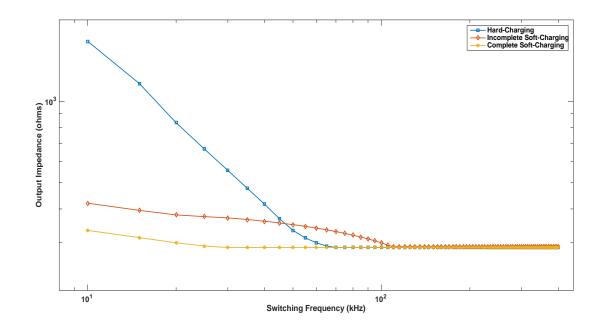

| Figure 4.4: Simulation output impedance of the 1-to-4 PSC converter vs the switching                                                                                                                     |

| frequency at three charging methods: hard-charging, incomplete soft-charging, complete soft-charging II                                                                                                  |

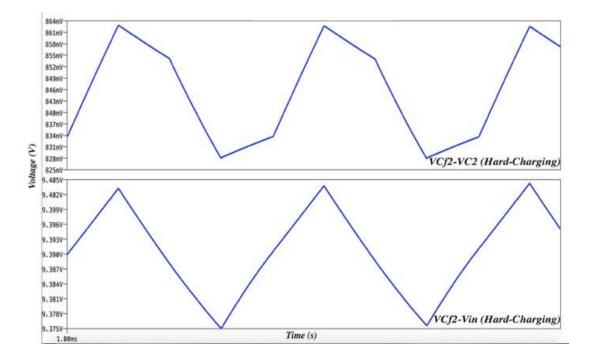

| Figure 4.5: Capacitor voltage mismatch during hard-charging between VCf2 – VC2 and                                                                                                                       |

|                                                                                                                                                                                                          |

| VCf2 – Vin                                                                                                                                                                                               |

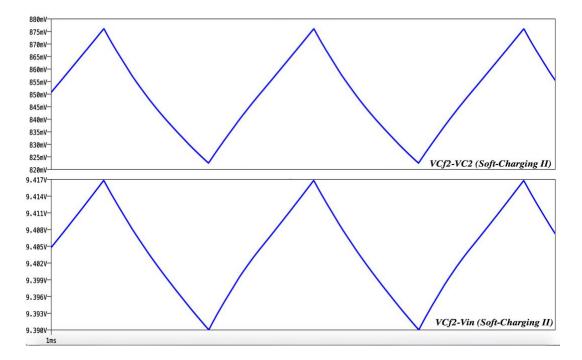

| Figure 4.6: The elimination of the capacitor voltage mismatch during complete soft-                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| charging II between VCf2 – VC2 and VCf2 – Vin                                                                                               |

| L of LC filter                                                                                                                              |

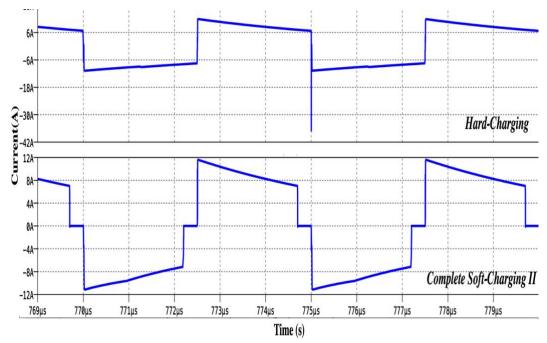

| Figure 4.7: The current waveform of Cf2 showing the transient in the hard-charging was eliminated by applying the complete soft-charging II |

|                                                                                                                                             |

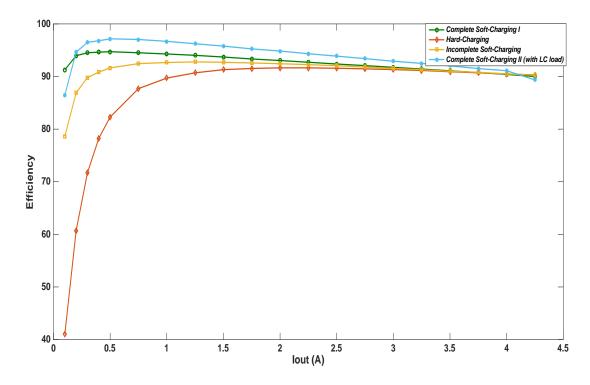

| Figure 4.8: The PSC converter efficiency vs the rated power at different operation                                                          |

| techniques: hard-charging, incomplete soft-charging, complete soft-charging I, and                                                          |

| complete soft-charging II (with LC filter)                                                                                                  |

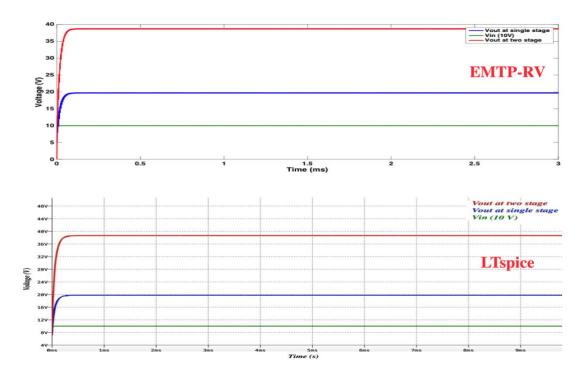

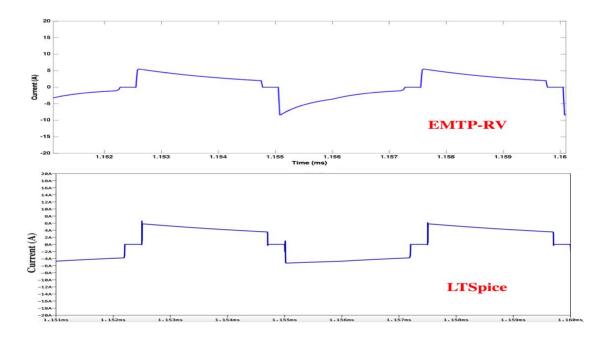

| Figure 4.9: The input and output voltages of a 1-to-4 and 1-to-2 of the proposed PSC converter by using LTspice and EMTP-EV simulators      |

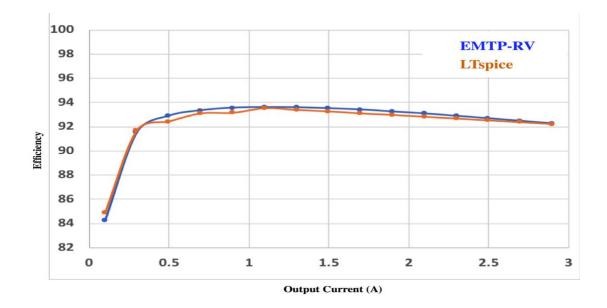

| Figure 4.10: The efficiency of a 1-to-4 and 1-to-2 of the proposed PSC converter by using                                                   |

| LTspice and EMTP-EV simulators                                                                                                              |

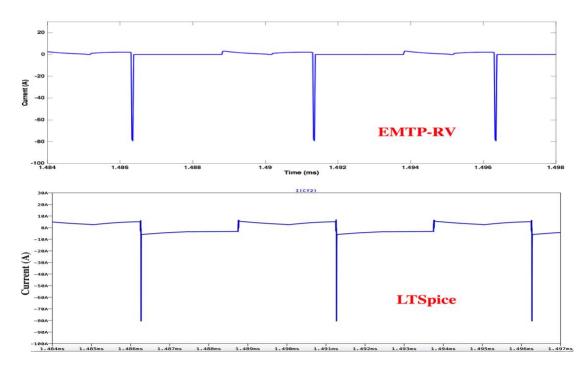

| Figure 4.11: The current transient at Cf2 hard-charging operation by using LTspice and                                                      |

| EMTP-EV simulators                                                                                                                          |

| Figure 4.12: The current transient at Cf2 is eliminated at complete soft-charging operation                                                 |

| by using LTspice and EMTP-EV simulators61                                                                                                   |

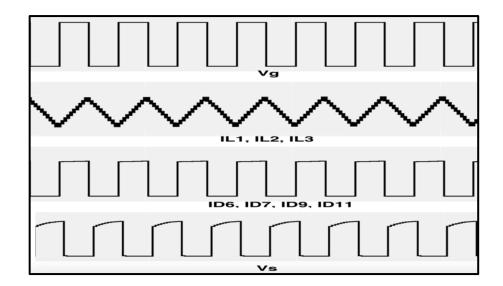

| Eigung 5.1. The MDC with the managed switched inductor                                                                                      |

| Figure 5.1: The MBC with the proposed switched inductor                                                                                     |

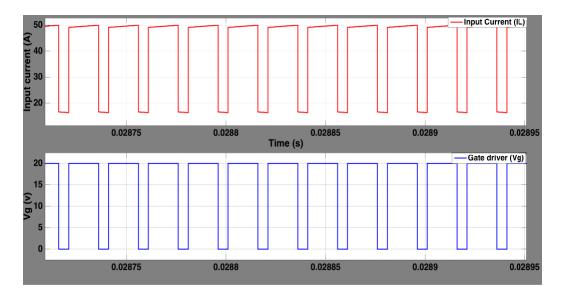

| Figure 5.2: Steady state waveforms in CCM with L1equal L2 and L3                                                                            |

| Figure 5.3: Mode 1 of the proposed three level MBC when S is on                                                                             |

| Figure 5.4: Mode 2 of the proposed three-level MBC when S is off                                                                            |

| Figure 5.5: Inwith the duty cycle, shows L1, L2 and L3 parallel and series connections.                                                     |

|                                                                                                                                             |

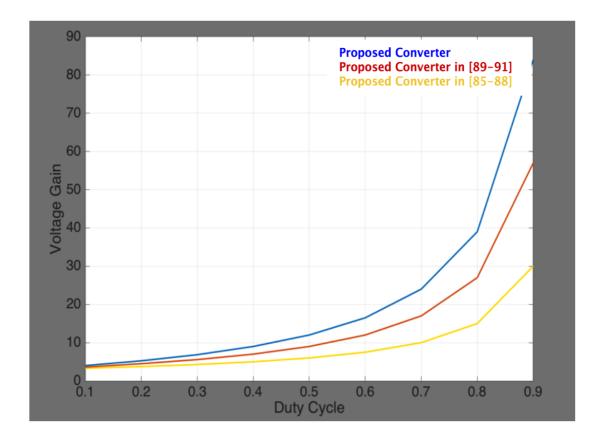

| Figure 5.6: Duty cycle vs conversion ratio of the three MBC types                                                                           |

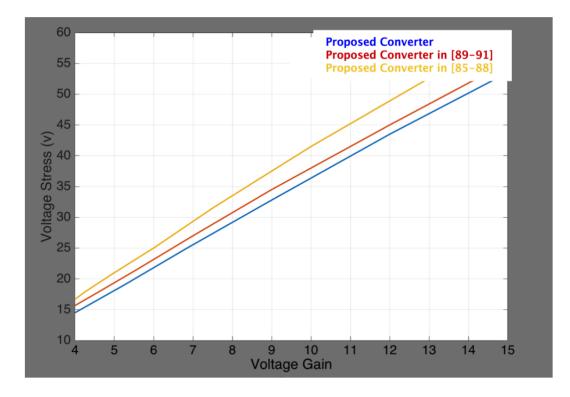

| Figure 5.7: Switch voltage stress versus voltage gain of proposed converter and compared,                                                   |

| [85- 88] and [89-91] between 4 to 15 voltage gains                                                                                          |

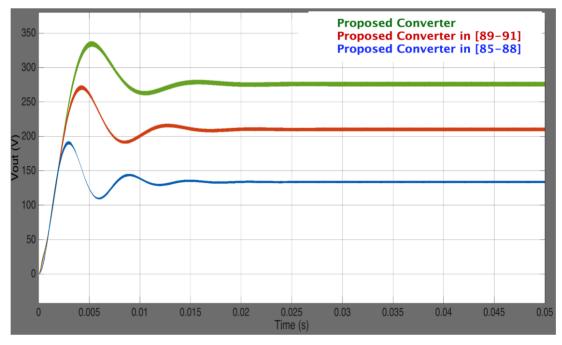

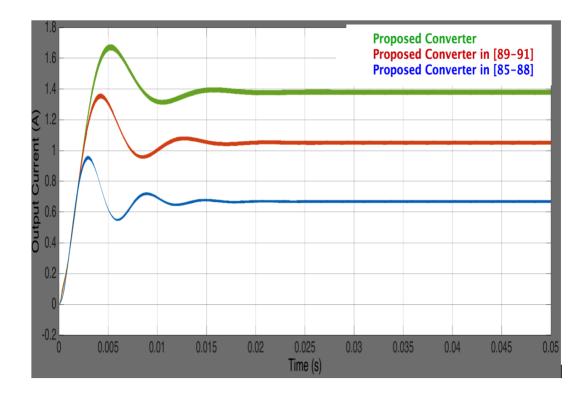

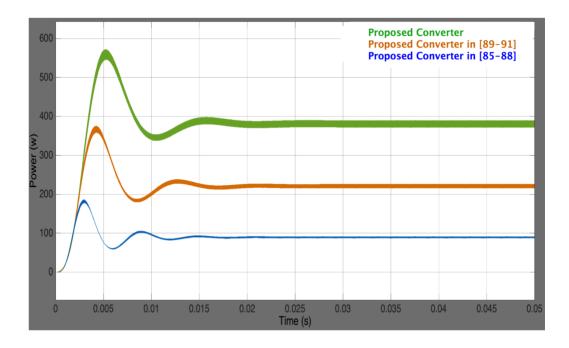

| Figure 5.8: Voutof the three compared MBC types                                                                                             |

| Figure 5.9: Ioutof the three compared MBC types                                                                                             |

| Figure 5.10: Poutof the three compared MBC types                                                                                            |

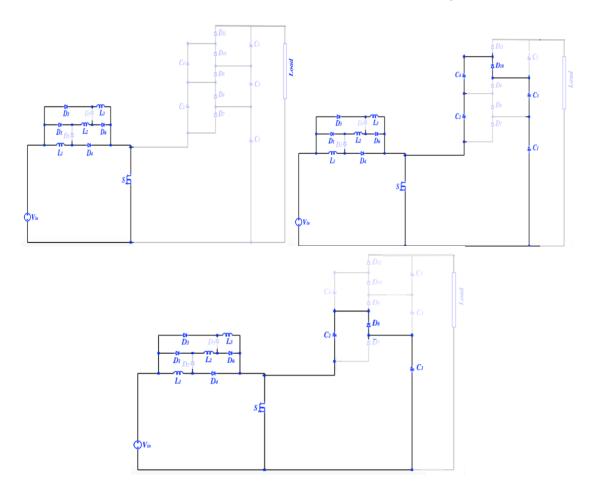

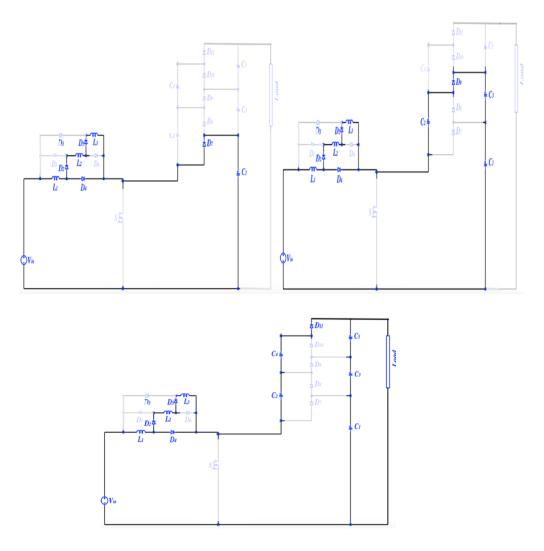

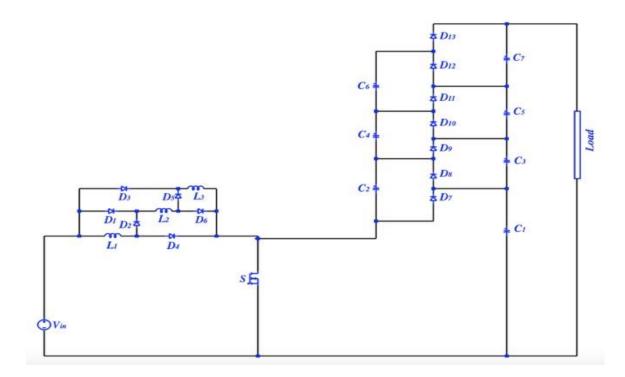

| Figure 5.11: The 4-level MBC converter:                                                                                                     |

| Figure 5.12: The 2 levels of the proposed PSC-boost converter proposed in [100]77                                                           |

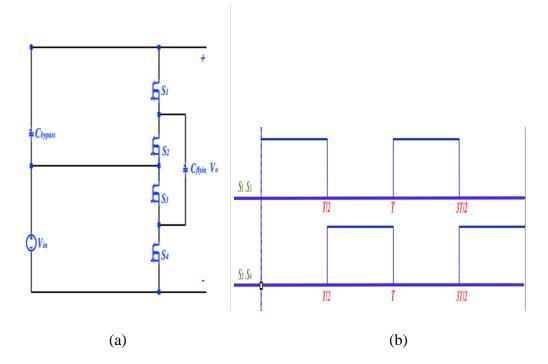

| Figure 5.13: a) The operation modes of the PSC-boost converter. b) Timing diagram of the                                                    |

| PSC-boost converter                                                                                                                         |

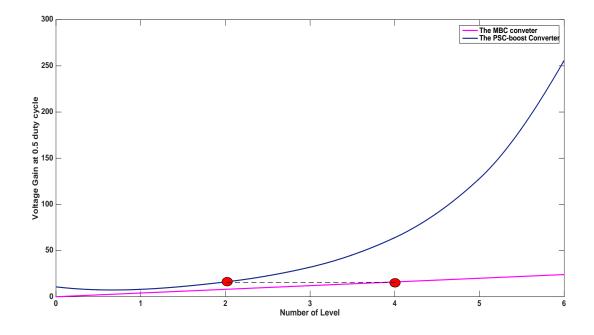

| Figure 5.14: The number of levels against the voltage gain at 50% duty cycle of the MBC                                                     |

| converter and the PSC-boost                                                                                                                 |

| Figure 5.15: The duty cycle against the voltage gain of the 4-level MBC converter and the                                                   |

| 2-level PSC-boost                                                                                                                           |

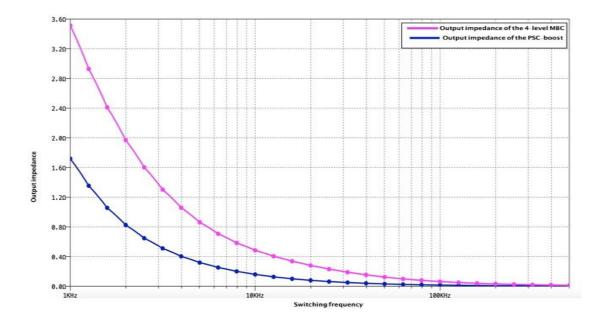

| Figure 5.17: The output impedance of the 2-level PSC boost and the 4-level-MBC at a                                                         |

| different switching frequency                                                                                                               |

### List of Tables

| Table 2.1: Simulation parameters of LTspice design                                      | 19      |

|-----------------------------------------------------------------------------------------|---------|

| Table 2.2: Charge Flow for the 1-to-4 PSC converter                                     |         |

| Table 2.3: Equation of the voltage stress on all semiconductors and capacitors.         |         |

| Table 4.1: Simulation parameters of PSC to operate in hard- and soft-charging.          |         |

| Table 4.2: A comparison among three charging operations in output calculations.         | -       |

| Table 4.3: Simulation parameters of LTspice and EMTP-RV simulators                      | 59      |

| Table 5.1: Conversion ratio of three different MBC types at ideal components a          | -       |

| Table 5.2: Design Parameters Calculated by [70]                                         |         |

| Table 5.3: A comparison between the proposed PSC-boost and the MBC conve                | rter 81 |

| Table 5.4: Simulation parameters of the PSC-boost and the MBC converter                 | 81      |

| Table 5.5: Prices of each elements in Figure 5.11 and Figure 5.12 according to company. |         |

|                                                                                         |         |

#### Abbreviations

DC "direct voltage"

**EV** "Electric Vehicle"

S-P "Series to Parallel"

SC "Switched-Capacitors"

SSL "Slow Switching Limit"

FSL "Fast Switching Limit"

$\mathbf{R}_{ds-on}$  "On Resistror of the MOSFET"

Rss "Slow Switching Limit impedance"

**R**<sub>FSL</sub> "Fast Switching Limit impedance"

PWM "Pulse-width modulated"

LNR "Line regulation"

**η** "Efficiency"

PSC "Power Switched-Capacitors"

*fsw* "Switching Frequency"

KCL "Kirchhoff's Current Low"

KVL "Kirchhoff's Voltage low"

MBC "Multilevel boost converter"

Vin "Input voltage"

Vout "Output voltage"

**q** "electric charge"

qin "Input electric charge"

qout "Output electric charge"

- $a_c$  "Charge multipliers of a capacitor"

- $a_r$  "Charge multipliers of the switch"

- A<sub>i</sub> "Reduced matrices loop"

- $B_i$  "Reduced incidence matrices"

- CCM "Continuous conduction mode"

#### **CHAPTER ONE: INTRODUCTION**

DC-to-DC converters are commonly designed with magnetic elements for energy storing purposes. Designing a DC-to-DC converter with magnetic components such as an inductor leads to low power density due to the inductor bulky size. An increase in the power density of DC-to-DC converters requires a higher switching frequency ( $f_{sw}$ ) since the inductor size is inversely proportionate to the switching frequency [1-3]. Increasing the  $f_{sw}$ can solve the problem partially; however, it will cause a switching loss produced by semiconductor elements. A growth in switching loss is conversely proportional to the converter efficiency [4][5]. High power density and high efficiency are two significant requirements for designing a DC-to-DC converter functional for tiny electronic circuit integration such as in battery electric vehicles (EV).

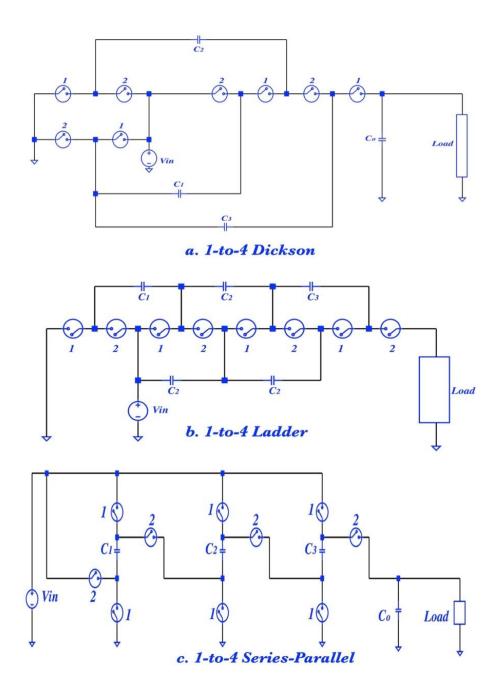

To satisfy these desires, the DC-to-DC switched-capacitors (SC) converters are widespread for EV. Because the DC-to-DC SC converters contain only capacitors and switches, they have a high-power density. The DC-to-DC SC converters come in many topologies such as, series to parallel [6-10], Dickson [11, 12], Fibonacci [13], ladder [14], and Voltage Doubler [15-20] where some of those are presented in Figure 1.1. Charging and discharging the capacitors allow the electric charge to flow from the input to the output to accomplish voltage regulation by alternating the switches' states. In addition to the high-power density, the SC converters tend to maintain the efficiency at a high voltage gain.

Because of their numerous topologies, analysis of the SC converters has been considered a challenging task. Several work tried to find a way to study and analyze the SC converters, such as [21-24]. Where in this work, the analysis in [5][25-26] has been applied. Two operation states occur in most types of SC converter, which are charging and discharging modes. The duty cycle of each mode is 50%. The DC-to-DC SC converter is simply a converter excluding inductor that operates to step up/down the voltage by changing the capacitor's terminals at high switching frequencies  $(f_{sw})$ . In the SC each capacitor terminal is connected to a number of switches, some of which operate in first mode while others work in the second mode. Changing the capacitor's connections to these two switches' operations allows electric charge q to flow in two different tracks, either to or from the capacitors. Raising power density using such a converter with only two types of components (switches and capacitors) is the main advantage of the SC converters. Moreover, SC converters have limited issues with electromagnetic interference because of the elimination of magnetic components such as the inductor. The number of capacitors and switches are selected regarding the conversion ratio and converter topology.

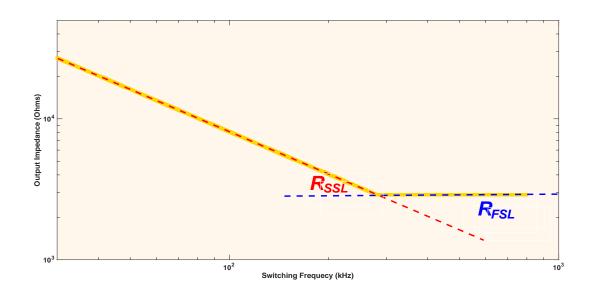

The total charge of the charging mode is assumed to equal the total charge in the discharging mode [5]. By studying and analyzing the charge flow, the SC converter voltage gain, the slow switching limit (SSL), and the fast switching limit (FSL) can be obtained. The output impedance at the SSL limit is proportional to the switching frequency and the capacitors' sizes while the output impedance at the FSL limit depends on the switches resistance  $R_{ds_on}$  [24]. Finding these two limits (SSL and FSL) helps to optimize the output impedance of the SC converter, and thus it would implement the efficiency. The desired value of the SSL limit is the intersection with the FSL limit asymptote as in Figure 1.2.

Figure 1.1: Three step-up SC converter topologies (a) 1-to-4 Dickson (b) 1-to-4 ladder (c) 1-to-4 series-parallel

However, the SC converters are not ideal or without drawbacks. For instance, providing a higher voltage gain is unlikely to be achieved with SC converters. Furthermore, the SC converters cannot normalize the output voltage in a lossless approach due to the

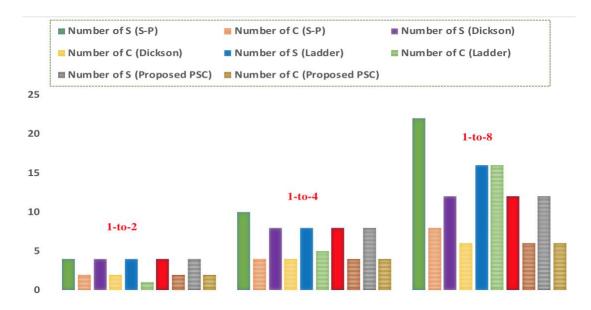

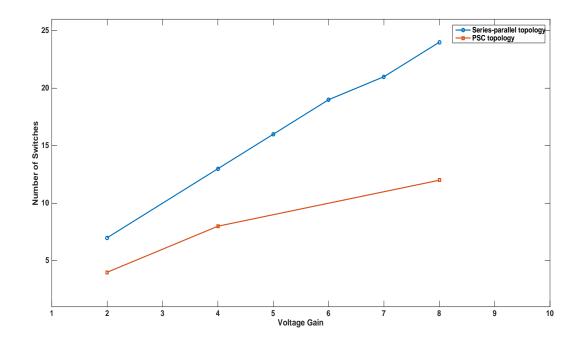

$R_{ds_on}$  resistors. In this work, a switched-capacitors converter is proposed to step-up a DCto-DC voltage [27][28]. The proposed SC converter is referred as a power switched capacitors (PSC) converter. As compared to other SC step up topologies the PSC provides a higher gain voltage at a smaller number of elements as in Figure 1.3

Figure 1.2: Output impedance of a typical SC converter

Figure 1.3: A comparison of four SC converter topologies including the proposed PSC in the number of switches and capacitors.

The PSC converter has a gain voltage of  $V_{out} = 2^n V_{in}$  where *n* is the number of stages. Each added stage requires two additional capacitors and four more switches [28]. Unlike the other SC converters' topologies, the number of operation modes increase with the number of levels. Each level of the PSC converter has two operation modes. For instance, the 1-to-4 PSC converter (two-levels) as in Figure 1 operates in four operation modes, where three levels operate in six operation modes. To achieve a superior efficiency , it is recommended that SC converters are designed with resonant soft-switching techniques. However, designing resonant SC converters requires additional components and hence a reduction in the power density is possible In addition to that, soft-switching techniques require a higher switching frequency to achieve the magnetic elements reduction [29–41].

The work in [42–46] proposed an alternative way of soft switching which is called a soft-charging operation. The soft-charging can be defined as a study of the voltage change across any capacitor's terminals in the circuit to reduce its size requirement and locate the potential charge flow. In [42-46], the soft-charging technique was applied to a 4-to-1 Dickson SC converter. The main advantage of applying the soft-charging technique instead of soft-switching is it is not essential to add more components to optimize the overall efficiency; however, optimizing the efficiency can be done by resizing the capacitors and reducing the output impedance [45]. In addition to that, the soft-charging operation helps to eliminate the current transient and voltage mismatch between any two parallel capacitors. In conventional operation (hard-charging), there are two ways to reduce the current transient, either by large capacitors selection or a higher  $f_{sw}$ . However, these two implementations reduce the power density and the fundamental efficiency respectively. To overcome the current transient issue, the complete soft-charging techniques are proposed to achieve that with a lower  $f_{sw}$  and smaller capacitors [42]. Resizing the capacitors in soft-charging techniques can be done theoretically by analyzing the voltage change and charge flow for each capacitor. In addition to resizing the capacitors, the output capacitor is eliminated in the soft-charging technique. Incomplete soft-charging and complete soft-charging are the two types of soft-charging. One significant difference between them is the complete soft-charging operation operates in a split-phase control diagram. The proposed control for Dickson SC converter in [42] splits each operation mode into two modes, which are the conventional modes besides the transition modes.

In this work, the complete soft-charging operation has been applied to the proposed PSC converter in [27]. A control diagram has been proposed to achieve a complete soft-charging in a 1-to-4 PSC converter. Achieving the complete soft-charging shows an output impedance reduction and a superior efficiency achievement to the 1-to-4 PSC converter. In addition, the split-phase successfully recovered the current transient. The reason for that is due to the dead time of the control diagram. However, reducing the capacitor size caused a high-output voltage ripple. To overcome the ripple issues, an output LC filter has been inserted into the 1-to-4 PSC converter.

The multilevel boost converter (MBC) is a boost converter contains voltage multiplier cells added to its output side in order to increase the output voltage. The conversion ratio could be increased by increasing its number of level where each additional level has two diodes and two capacitors. On the other hand, MBC has a drawback related to limited output power due to its lower output current. To overcome that, we proposed a switched inductor model for the MBC to increase the output current and expand MBC's applications. Furthermore, the new PSC converter has been used as voltage multipliers and inserted to a conventional boost converter. The new PSC-boost converter works similar to the MBC boost converter where PSC cells were used instead of multilevel cells to increase the voltage gain.

#### **1.1 DC-to-DC converters**

The regulated voltage by a DC-to-DC converter is essential to run electronic elements that are used on daily appliances such as personal computers or automobile devices. Either a DC or AC input voltage has to be regulated to a DC voltage. Regarding the input type, an appropriate device such as a transformer, rectifier, or filters is used to regulate the input voltage to a DC voltage. A DC-to-DC converter is mainly based on three switching regulator categories which are the pulse-width modulated (PWM) DC-to-DC, the resonant converters, and the switched-capacitor DC-to-DC converters [47].

Several measurements are used to validate the DC-to-DC converter where the main important aspect is the converter power conversion efficiency which is based on the ratio of the output power to the input power. The general equation to calculate the efficiency can be derived as the following

$$\eta = \frac{P_{out}}{P_{in}} \times 100 \tag{1.1}$$

In addition to the efficiency measurement, a measurement of the converter's strength to provide a supposed output voltage is another important parameter which is called the line regulation (LNR)

$$LNR = \frac{\Delta V_{out}}{\Delta V_{in}} \times 100 \tag{1.2}$$

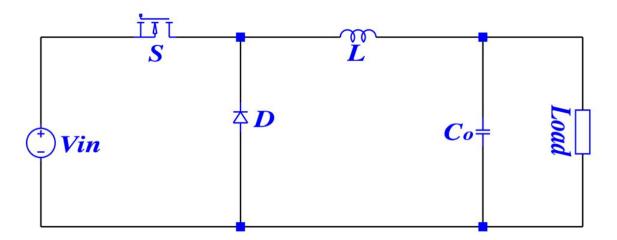

Similarly, a measurement of load strength to maintain the load current variation is another essential measurement in the DC-to-DC converter. Two popular types of the DCto-DC converter are the buck DC-to-DC converter and the boost DC-to-DC converter. Two switching elements, transistor and diode are used to either step down or step up the input voltage in the buck and boost DC-to-DC converters respectively. The inductor will be charged when the transistor is on and where it will discharge when transistor is off. The diode state usually conflicts the transistor's state to allow the charge's delivery to the output. 4-to-3 series to parallel SC converter

Figure 1.4: A conventional boost converter design.

A DC-to-DC switched-capacitor is an alternative converter to a traditional DC-to-DC converter with only switches and capacitors. The main advantage of the switchedcapacitors converter is the absence of the magnetic elements such as inductors. In this section a 4-to-3 series to parallel SC converter will be discussed. Three capacitors and ten switches are used to build the proposed model. The duty cycle is 50% for each mode, 1 and 2, as shown in Figure 1.5. Charging modes  $S_1$ ,  $S_4$ ,  $S_5$ ,  $S_7$ ,  $S_8$ , and  $S_{10}$  are conducting; however,  $S_2$ ,  $S_3$ ,  $S_6$ , and  $S_9$  are not. Charging modes C1, C2, and C3 are connected in parallel while they are in series in discharging mode. The total charge in charging mode equals the total charge of discharging mode [5] as in (1.3).

$$Q_T^1 = Q_T^2 \tag{1.3}$$

Figure 1.5: A 4-to3 series to parallel SC converter [10].

In mode-1 Figure 1-b, the voltage across  $C_1$ ,  $C_2$ , and  $C_3$  is the same because of the parallel connection (1.4).

$$V_1 = V_2 = V_3 = V_{in} - V_{out} \tag{1.4}$$

To satisfy (1.3) it is necessary to apply (1.4).

$$Q_T^1 = C_1 V_1 + C_2 V_2 + C_3 V_3 + C_L V_{out}$$

(1.5)

by substituting (1.4) into (1.5) to get (1.6)

$$Q_T^1 = V_{in}(C_1 + C_2 + C_3) + V_{out}(C_1 + C_2 + C_3) + C_L V_{out}$$

(1.6)

In discharging mode, the  $V_{out}$  is the voltage total across each capacitor (1.7).

$$V_{out} = V_1 + V_2 + V_3 \tag{1.7}$$

The total charge of this mode is presented in (1.8).

$$Q_T^2 = C_1 V_1 + C_2 V_2 + C_3 V_3 + C_L V_{out}$$

(1.8)

$$Q_T^2 = V_1(C_1 - C_2) + V_3(C_3 - C_2) + C_2 V_{out} + C_L V_{out}$$

(1.9)

(1.9) has three unknown variables, so one more equation is needed to get (1.9) in  $V_{out}$  and  $V_{in}$  only. In mode-2, the streaming current in  $C_1$ ,  $C_2$ , and  $C_3$  are the same and can be calculated by (1.10)

$$ic_1 = C_1 \frac{dv_1}{dt} = ic_2 = C_2 \frac{dv_2}{dt} = ic_3 = C_3 \frac{dv_3}{dt}$$

(1.10)

In this work, it is assumed that  $C_1$ ,  $C_2$ , and  $C_3$  have the same value (1.11).

$$dv1 = dv2 = dv3 (1.11)$$

The rate of change in  $C_1$ ,  $C_2$ , and  $C_3$  is simply the voltage across the capacitor in mode-1 subtracted by the voltage across the capacitor in mode-2 (1.12) (1.13) (1.14).

$$dv1 = V_1^1 - V_1^2 \tag{1.12}$$

$$dv2 = V_2^1 - V_2^2 \tag{1.13}$$

$$dv3 = V_3^1 - V_3^2 \tag{1.14}$$

Where  $V_1^1$ ,  $V_2^1$ ,  $V_3^1$  are the voltages across  $C_1$ ,  $C_2$ , and  $C_3$  respectively during the charging mode,  $V_1^2$ ,  $V_2^2$ ,  $V_3^2$  are their voltages in discharging mode. By rewriting (1.12) (1.13) (1.14), we get (1.15) (1.16) (1.17)

$$dv1 = V_{in} - V_{out} - V_1 \tag{1.15}$$

$$dv2 = V_{in} - V_{out} - V_2 \tag{1.16}$$

$$dv3 = V_{in} - V_{out} - V_3 \tag{1.17}$$

From (1.11), (1.15), (1.16) and (1.17) we can find a relationship between  $V_1$  and  $V_2$  and between  $V_1$  and  $V_3$  (1.18).

$$V_1 = V_2 = V_3 \tag{1.18}$$

By inserting (1.18) in (1.7) we get (1.19).

$$V_{out} = 3V_1 = 3V_2 = 3V_3 \tag{1.19}$$

Next, we substitute (1.19) into (1.9) to get  $Q_T^2$  in one variable which is  $V_{out}$  (1.20).

$$Q_T^2 = \frac{V_{out}}{3}(C_1 - C_2) + \frac{V_{out}}{3}(C_3 - C_2) + C_2 V_{out} + C_L V_{out}$$

(1.20)

To get the conversion ratio of the proposed SC, we equate (1.6) with (1.20).

$$V_{in}(C_1 + C_2 + C_3) = \frac{4}{3}V_{out}(C_1 + C_2 + C_3)$$

$$\frac{V_{out}}{V_{in}} = \frac{3}{4}$$

(1.21)

(1.21) shows that the gain of the proposed design is 3/4 under a lossless component assumption.

#### 1.3 Slow-switching limit impedance of a 4-to-3 series to parallel SC converter

Both capacitors and switches in the SC have losses related to either a switching, a charging, or a discharging of the switches and capacitors. This loss can be represented as an output impedance which is called a slow switching limit (SSL) impedance  $R_{ssl}$ . The conversion ratio in (1.21) is independent of capacitor size and also of  $f_{sw}$  of the design. Studying the charge flow for both modes as shown in Figure 1.5 and in order to calculate the charge multiplier for each capacitor  $a_c$  (1.22) [5]

$$q_c = a_c q_{out} \tag{1.22}$$

The input charge of mode-1  $q_{in}$  is divided into three input charges, and each one flows through each of the parallel capacitors  $q_{in}/3$ . For mode-2 the input current is  $-q_{in}/3$  so the charge flow in  $C_1$ ,  $C_2$ , and  $C_3$  in both mode-1 and mode-2 are represented in (21) and (22).

$$q_{c}^{1} = \begin{bmatrix} q_{in}/3 \\ q_{in}/3 \\ q_{in}/3 \end{bmatrix}$$

(1.23)

$$q_c^2 = \begin{bmatrix} -q_{in}/3 \\ -q_{in}/3 \\ -q_{in}/3 \end{bmatrix}$$

(1.24)

The total output charge (1.25)

$$q_{out} = q_{out}^1 + q_{out}^2 = q_{in} + q_{in}/3$$

(1.25)

by inserting (1.25) into (1.23) and (1.24) to get (1.26) and (1.27)

$$q_c^1 = \begin{bmatrix} q_{out}/4 \\ q_{out}/4 \\ q_{out}/4 \end{bmatrix}$$

(1.26)

$$q_{c}^{2} = \begin{bmatrix} -q_{out}/4 \\ -q_{out}/4 \\ -q_{out}/4 \end{bmatrix}$$

(1.27)

by inserting (1.22) into (1.26) and (1.27) to get (1.28) and (1.29)

$$a_c^1 = \begin{bmatrix} 1/4\\ 1/4\\ 1/4 \end{bmatrix}$$

(1.28)

$$a_c^2 = \begin{bmatrix} -1/4 \\ -1/4 \\ -1/4 \end{bmatrix}$$

(1.29)

by using Tellegen's theorem [5][9], to find  $R_{ssl}$  of our proposed design (1.30).

$$\frac{V_{out}}{q_{out}} + \sum_{i=1}^{number \ of \ C} \frac{(a_{c,i})^2}{c_i} = 0$$

(1.30)

where

$$\frac{V_{out}}{q_{out}} = R_{ssl}$$

$R_{ssl} = \frac{1}{16f_{sw}} \left[ \frac{1}{C1} + \frac{1}{C2} + \frac{1}{C3} \right]$  (1.31)

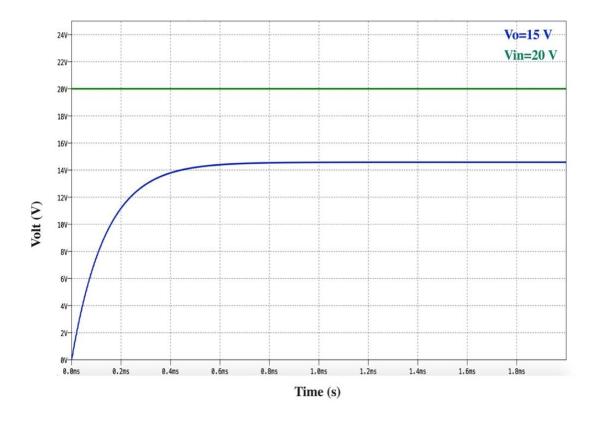

Figure 1.6: A simulated LTspice result of a 4-to-3 series to parallel SC converter.

#### **1.4 Problem Statement**

In addition to the discussion in section 1.1, how should a DC-to-DC converter's power density be increased and meet the small electronic circuit reequipment? DC-to-DC converters that contain magnetic elements require a higher switching frequency in order to minimize the magnetic sizes; however, this increase could affect their efficiency. The switched-capacitor converters are recommended instead due to the absence of magnetic elements. The most challenging task in designing SC converters is to maintain the efficiency and the number of elements at a higher voltage gain. The PSC converter has proven its efficiency and ability to provide a high voltage gain with a smaller number of elements. To improve the efficiency of the DC-to-DC converters, adding the resonant branches to achieve a soft switching operation is highly recommended. However, adding additional elements could affect the power density which is the fundamental aspect of SC converters. Instead of applying the soft switching operation, a soft-charging operation is more appropriate for SC converters due to the possibility of unnecessary insertion of additional components. Besides the efficiency improvement, the soft-charging operation helps to decrease the output impedance.

#### **1.5 Methodology**

The LTspice software simulation program is the main program used to analyze our model and study its performance in the soft-charging operation. The EMTP-RV program was used to validate the study of the soft-charging operation. The SIMULINK MATLAB was used to study the efficiency and analyze the voltage gain of the proposed model in Chapter Five. The outcome results of this dissertation have been validated by publication of a MDPI journal paper and several conference papers (IEEE and SPIE).

#### **1.6 The Structure of the Dissertation**

The next chapters of the dissertation are ordered as follows:

- Chapter two talks about the proposed power switched-capacitor converter and how it operates when two stages are selected. It also includes the calculation and derivation of the voltage gain, output impedance, and capacitor selection by applying the charge flow and voltage change. At the end of this chapter is a comparison between the proposed PSC and other SC topologies, in the efficiency and output impedance.

- Chapter three includes an incomplete soft-charging operation of the second order PSC converter. The analysis was applied to the PSC converter in order to resize the capacitors and reduce the output impedance.

- Chapter four contains a study of a complete soft-charging operation in the second stage

of the PSC. This chapter also includes a proposed control diagram to satisfy the split

phase operation. Besides that, a generalization of the split phase operation is discussed.

The implementations to the PSC efficiency and output impedance after applying the

complete soft-charging operation are proven in this chapter.

- Chapter five shows an application of the PSC converter to be used as voltage multiplier cells in the non-isolated DC-to-DC converter. The proposed converter acts similar to the MBC converter with some privileges.

- Chapter six contains the dissertation's summary and details future work. Also, some of my publications are listed in this chapter.

## CHAPTER TWO: A SERIES OF POWER SWITCHED-CAPACITOR (PSC) CONVERTERS

#### **2.1 Introduction**

Regarding the market's demand for a large voltage gain conversion, a single stage boost converter could not achieve a higher efficiency due to its duty cycles limits. To overcome a high gain requirement, designing two-stage converters has promised for being an efficient substitute for a traditional boost converter. The two-stage converter is based on using a SC converter as one stage where the other stage is a traditional boost converter. Several topologies of SC have been presented in previous chapter; however, most of those topologies require a large number of components to provide a higher voltage gain converter [48-50]. A proposed step-up power switched-capacitors (PSC) converter is presented in this chapter to fulfill the high voltage gain requirement [27]. The PSC converter successfully increases the voltage gain with a smaller number of elements and a lower voltage stress in switches. The procedure to analyze and obtain the voltage gain, output impedance limits, and capacitor sizes for the proposed PSC converter are discussed in this chapter under a steady state assumption. Efficiency calculations must be performed to determine the power of the SC converter.

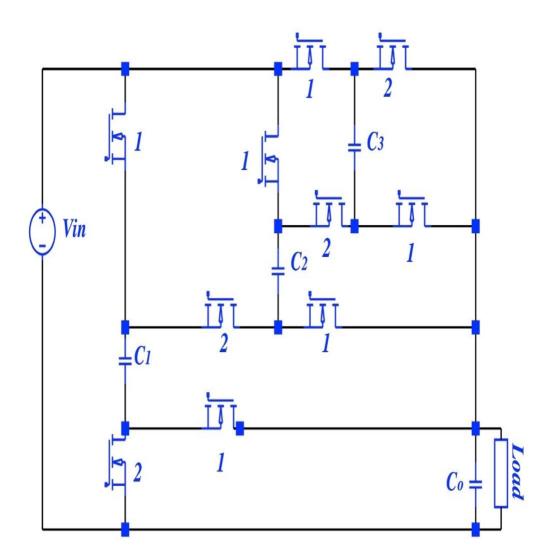

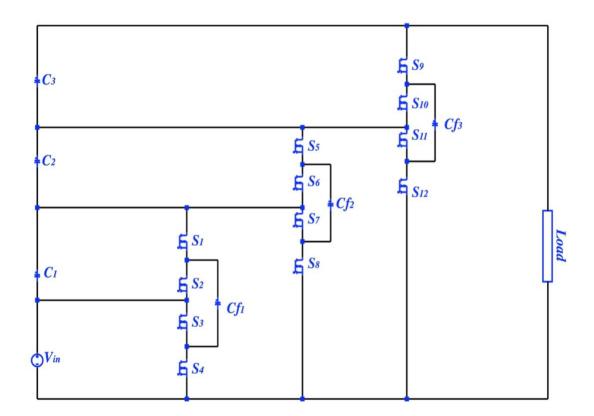

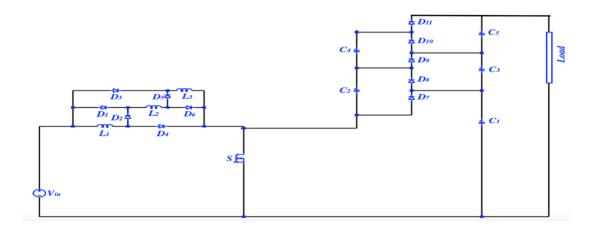

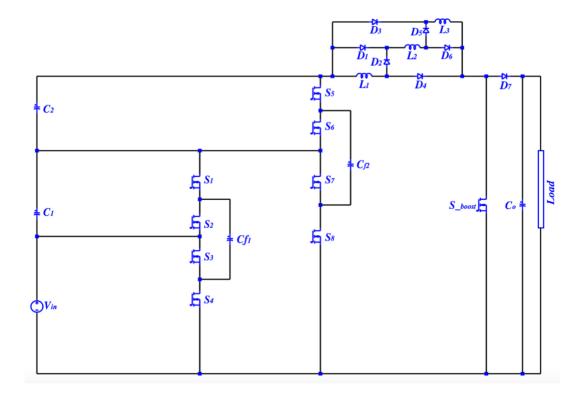

Figure 2.1: A 1-to-4 PSC topology (two-stage).

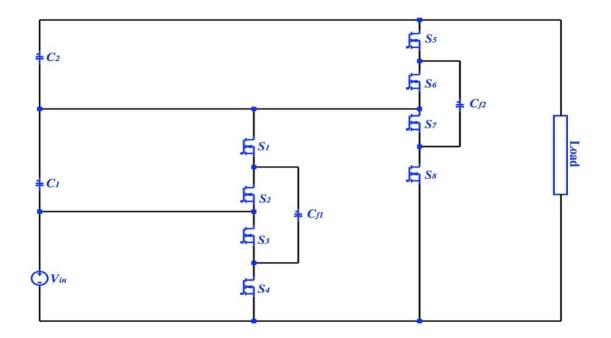

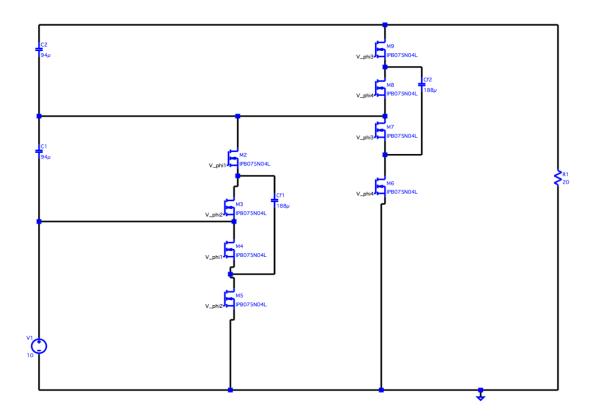

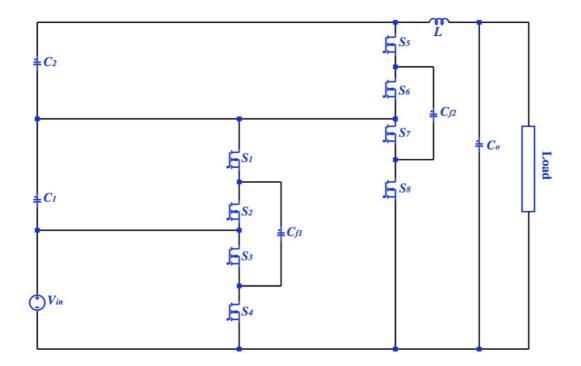

#### 2.2 Power switched-capacitor (PSC) converter; topology and operation

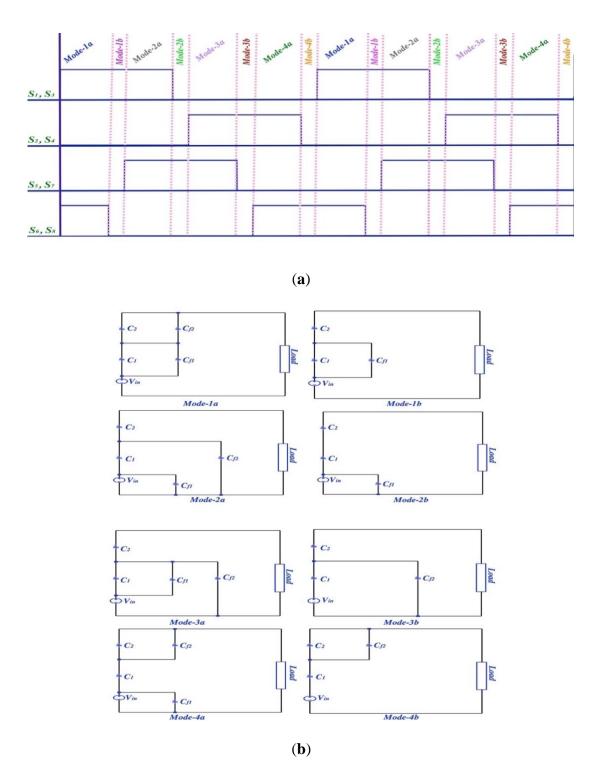

This section introduces the topology of the proposed power switched-capacitor converter. Figure 2.1 shows a two-stage topology of the 1-to-4 PSC converter which produces an output voltage equals to  $4V_{in}$ . The first level contains four switches,  $S_1 S_2 S_3$ and  $S_4$ , and two capacitors which are the bypass capacitor  $C_1$  and flying capacitor  $C_{f1}$ . Similar to the first stage, the second level contains four switches,  $S_5 S_6 S_7$  and  $S_8$ , and two capacitors; one of them is a bypass capacitor  $C_2$  where the other capacitor is a flying capacitor  $C_{f2}$ . Two control groups are needed to control the two levels of the PSC converter as shown in Figure 2.3a. The first and second groups have a  $\frac{T}{4}$  phase shift, wherein each group a  $\frac{T}{2}$  phase shift is between its two control signals. The input voltage is doubled at first stage where this doubled voltage will be doubled again at the second level.

The flying capacitors are either in parallel to the input source or to the bypass capacitors to pump the electric charge from the input to the output [51]. Related to the control diagram, four modes of operations are possible (Figure 2.3b). These operation modes come in the following sequence: Mode-1, Mode-2, Mode-3, Mode-4, and Mode-1. In each mode, the capacitors are connected differently for voltage regulation purposes. In Mode-1 the flying capacitor  $C_{f1}$  is charging; however, flying capacitor  $C_{f2}$  is discharging. In Mode-2, both flying capacitors  $C_{f1}$  and  $C_{f2}$  are discharging, whereas they are both charging in Mode-4. In Mode-3  $C_{f1}$  is discharging whereas  $C_{f2}$  is charging.

A LTspice design of the two stage PSC converter was designed with simulation parameters as in Table 2.1. Figure 2.2 shows a LTspice design of a 1-to-4 PSC topology (two-stage).

| Parameter                                   | Value      |

|---------------------------------------------|------------|

| V <sub>in</sub>                             | 10 V       |

| f <sub>sw</sub>                             | 200 KHz    |

| $C_{f1}C_{f2}$                              | 188 µF     |

| <i>C</i> <sub>1</sub> <i>C</i> <sub>2</sub> | 94 µF      |

| R <sub>L</sub>                              | 20         |

| Switches                                    | IPB075N04L |

Table 2.1: Simulation parameters of LTspice design

Figure 2.2: LTspice design of a 1-to-4 PSC topology (two-stage).

To find the voltage gain of the proposed converter, charge balance analysis is applied instead of discrete-time analysis as in [52][53]. Each mode has a total charge that can be derived from the following equations:

$$QT_i = V_{C_1}C_1 + V_{C_2}C_2 + V_{C_{f1}}C_{f1} + V_{f2}C_{f2}$$

(2.1)

where i is the number of modes 1, 2, 3 and 4 (from Mode-1 Figure 2.3).

$$V_{C_{f1}} = V_{C_1}$$

$V_{C_2} = V_{C_{f2}}$  (2.2)

$$V_{C_{f1}} = V_o - V_{in} - V_{C_{f2}}$$

(2.3)

by substituting (2.2), (2.3) and (2.4) in (2.1) we get the total charge of Mode-1 (2.5)

$$QT_1 = V_{in} (-C_{f1} - C_1) + V_{f2} (C_2 + C_{f2} - C_1 - C_{f1}) + V_o (C_1 + C_{f1})$$

(2.4)

To find the total charge of the rest of the modes, the same steps can be repeated

$$QT_2 = V_{in}(C_{f1} - C_1) + V_{f2}(C_1 + C_{f2} - C_2) + V_{out}C_2$$

(2.1)

$$QT_3 = V_{in} \left( -C_{f1} - C_1 \right) + V_{f2} \left( C_1 + C_{f1} + C_{f2} - C_2 \right) + V_{out} C_2$$

(2.2)

$$QT_4 = V_{in}(C_{f1} - C_1) + V_{f2}(-C_1 + C_{f2} + C_2) + V_{out}C_1$$

(2.3)

In the steady state operation, the total charge of any two modes is assumed to be equal. In this work, we assumed that

$$QT_1 = QT_4 \tag{2.4}$$

$$QT_2 = QT_3 \tag{2.5}$$

By simplifying (2.8) and (2.9) we get

$$2V_{in}C_{f1} + V_{f2}C_{f1} - V_{out}C_{f1} = 0 (2.6)$$

$$2V_{in}C_{f1} - V_{f2}C_{f1} = 0 (2.7)$$

By combining (2.10) and (2.11), the 1-to-4 PSC converter's voltage gain can be calculated (2.12)

$$V_{out} = 4V_{in} \tag{2.8}$$

The general form of the proposed converter is

$$V_{out} = 2^n V_{in} \tag{2.9}$$

where n is the number of the stage. The output voltages of the stage one and stage two of the PSC converter are presented in Figure 2.4. The converter efficiency at two different input voltages is presented in Figure 2.5

Figure 2.3: (a) Timing diagram of a 1-to-4 PSC topology; (b) four-mode operation of a 1-to-4 PSC converter.

For each added stage, two capacitors and four switches are needed. Figure 2.6 presents three stages of the proposed converter with 1-to-8 conversion ratio, each switch operates in a 50% duty cycle whereas a  $\frac{1}{2n}$  is phase shift between any two stages.

Figure 2.4: The input and output voltages of a 1-to-4 and 1-to-2 of the proposed PSC converter.

Figure 2.5: Efficiency vs rated power of a 1-to-4 at 10V and 5V input.

## 2.3 Slow-switching limit impedance $(R_{ssl})$ of the second order PSC converter

The SC converters suffer from losses related to the switches and the capacitors' charging or discharging process. This capacitors' loss can be characterized as an output impedance that is called a slow switching limit impedance,  $R_{ssl}$ . The charge flow analysis of the four modes has been applied to find the charge multiplier of the four capacitors  $a_c^i$

$$q_c^i = a_c^i \, q_{out} \tag{2.10}$$

$$q_c = [q_{c_1} q_{c_2} q_{c_{f_1}} q_{c_{f_2}}]^I$$

(2.11)

Figure 2.6: A 1-to-8 PSC topology (three-stage).

In [42-46] a useful technique was used to find the charge flow vectors of all the operation modes. For the *i*th mode, Kirchhoff's Current Low (KCL) can be derived by (2.16)

$$B_i q^i = 0 \tag{2.12}$$

where  $B_i$  is reduced incidence matrices of the four modes of 1-to-4 PSC converter. Each row in  $B_i$  corresponds to an independent KCL equation. The number of independent KCL equations can be derived by the number of nodes. Each element in the circuit has two nodes related to its positive and negative terminals as in Figure 2.7 [54][55]. The charge follow's direction is inspected as in Table 2.2.

Figure 2.7: The charge flow for the operation modes in the 1-to-4 PSC converter.

$$B_{1,a} = \begin{bmatrix} -1 & 1 & 0 & 1 & 0 & 0 \\ 0 & -1 & 1 & -1 & 1 & 0 \\ 0 & 0 & -1 & 0 & -1 & 1 \\ 1 & 0 & 0 & 0 & 0 & -1 \end{bmatrix}$$

$$B_{2,a} = \begin{bmatrix} -1 & 1 & 0 & 1 & 0 & 0 \\ 0 & -1 & -1 & 0 & 1 & 0 \\ 0 & 0 & 1 & 0 & 0 & -1 \\ 1 & 0 & 0 & -1 & -1 & 1 \end{bmatrix}$$

$$B_{3,a} = \begin{bmatrix} -1 & 1 & 0 & 1 & 0 & 0 \\ 0 & -1 & 1 & -1 & 1 & 0 \\ 0 & 0 & -1 & 0 & 0 & 1 \\ 1 & 0 & 0 & 0 & -1 & -1 \end{bmatrix}$$

$$B_{4,a} = \begin{bmatrix} -1 & 1 & 0 & 1 & 0 & 0 \\ 0 & -1 & -1 & 0 & 1 & 0 \\ 0 & 0 & 1 & 0 & -1 & 1 \\ 1 & 0 & 0 & -1 & 0 & -1 \end{bmatrix}$$

(2.13)

To find the charge flow's vectors, (2.17) can be solved for  $q^i$ .

$$q_{Flow}^{1} = \begin{bmatrix} 3\\1\\1\\2\\2\\3 \end{bmatrix} q_{Flow}^{2} = \begin{bmatrix} -3\\-1\\-1\\-2\\-2\\-2\\-1 \end{bmatrix}$$

$$(2.14)$$

$$q_{Flow}^{3} = \begin{bmatrix} 3\\1\\1\\2\\2\\1 \end{bmatrix} q_{Flow}^{4} = \begin{bmatrix} -3\\-1\\-1\\-2\\-2\\-2\\-1 \end{bmatrix}$$

| Mode 1                                     |                     | Mode 2      |                           | Mode 3       |                     | Mode 4       |                                |

|--------------------------------------------|---------------------|-------------|---------------------------|--------------|---------------------|--------------|--------------------------------|

| <i>q</i> <sup>1</sup> <sub><i>C</i>1</sub> | $\frac{q_{in}}{3}$  | $q_{C1}^2$  | $\frac{-q_{in}}{3}$       | $q_{C1}^{3}$ | $\frac{q_{in}}{3}$  | $q_{C1}^{4}$ | $\frac{-q_{in}}{3}$            |

| $q_{C2}^1$                                 | $\frac{q_{in}}{3}$  | $q_{C2}^2$  | $\frac{-q_{in}}{3}$       | $q_{C2}^{3}$ | $\frac{q_{in}}{3}$  | $q_{C2}^{4}$ | $\frac{-\ddot{q}_{in}}{3}$     |

| $q_{Cf1}^1$                                | $\frac{2q_{in}}{3}$ | $q_{Cf1}^2$ | $\frac{-2q_{in}}{3}$      | $q_{Cf1}^3$  | $\frac{2q_{in}}{3}$ | $q_{Cf1}^4$  | $\frac{-2q_{in}}{3}$           |

| $q_{Cf2}^1$                                | $\frac{2q_{in}}{3}$ | $q_{Cf2}^2$ | $\frac{-2q_{in}}{3}$      | $q_{Cf2}^3$  | $\frac{2q_{in}}{3}$ | $q_{Cf2}^4$  | $\frac{-2q_{in}}{3}$           |

| q <sup>1</sup> <sub>out</sub>              | $q_{in}$            | $q_{out}^2$ | $\frac{-\bar{q}_{in}}{3}$ | $q_{out}^3$  | $\frac{q_{in}}{3}$  | $q_{out}^4$  | $\frac{-\overline{q_{in}}}{3}$ |

Table 2.2: Charge Flow for the 1-to-4 PSC converter

The total output charge with respect to the output charge can be found in (2.18)

$$q_{out,total} = q_{out}^{1} + q_{out}^{2} + q_{out}^{3} + q_{out}^{4}$$

(2.15)

The total output charge with respect to the input charge is

$$q_{out,total} = q_{in} + \frac{q_{in}}{3} + \frac{q_{in}}{3} + \frac{q_{in}}{3} = 2q_{in}$$

(2.16)

By using (2.21), (2.19) can be rewritten with respect to the output charge of the capacitors and the load (2.22)

$$q^{1} = \begin{bmatrix} \frac{q_{out}}{2} \\ \frac{q_{out}}{2} \\ q_{out} \\ \frac{q_{out}}{2} \\ q_{out} \\ \frac{3q_{out}}{2} \end{bmatrix} q^{2} = \begin{bmatrix} \frac{-q_{out}}{2} \\ -q_{out} \\ -q_{out} \\ \frac{-q_{out}}{2} \\ \frac{-q_{out}}{2} \\ \frac{-q_{out}}{2} \\ \frac{q_{out}}{2} \\ q_{out} \\ \frac{q_{out}}{2} \\ q_{out} \\ \frac{q_{out}}{2} \\ \frac{-q_{out}}{2} \\ -q_{out} \\ \frac{-q_{out}}{2} \\ -q_{out} \\ \frac{-q_{out}}{2} \\ \frac{-q_{ou$$

By dividing (2.21) by (2.15), the charge multipliers are presented in (2.23)

$$a^{1} = \begin{bmatrix} \frac{1}{2} \\ \frac{1}{2} \\ 1 \\ \frac{1}{3} \\ \frac{1}{2} \end{bmatrix} a^{2} = \begin{bmatrix} \frac{-1}{2} \\ \frac{-1}{2} \\ -1 \\ -1 \\ \frac{-1}{2} \end{bmatrix}$$

$$a^{3} = \begin{bmatrix} \frac{1}{2} \\ \frac{1}{2} \\ 1 \\ \frac{1}{2} \\ \frac{1}{2} \end{bmatrix} a^{4} = \begin{bmatrix} \frac{-1}{2} \\ \frac{-1}{2} \\ -1 \\ -1 \\ \frac{-1}{2} \end{bmatrix}$$

(2.18)

Then by applying the Tellegen's theorem to the PSC converter, in its four modes of operation, concludes  $a^1 \cdot V^1 = a^2 \cdot V^2 = a^3 \cdot V^3 = a^4 \cdot V^4 = 0$ ,  $R_{ssl}$  limit of the output impedance can be found for our proposed design (2.23).

$$V_{out}(a_{out}^{1} + a_{out}^{2} + a_{out}^{3} + a_{out}^{4}) + \sum_{capacitors} a_{ci}^{1} V_{ci}^{1} + a_{ci}^{2} V_{ci}^{2} + a_{ci}^{3} V_{ci}^{3} + a_{ci}^{4} V_{ci}^{4} = 0$$

(2.23)

By recalling the output charge multipliers total  $(a_{out}^1 + a_{out}^2 + a_{out}^3 + a_{out}^4) = 3$ , and due to the periodic cycles,  $\Delta V^i = (V_{ci}^1 - V_{ci}^2) = (V_{ci}^3 - V_{ci}^4)$  and  $a_{ci} = a_{ci}^1 = -a_{ci}^2$  and  $a_{ci} = a_{ci}^3 = -a_{ci}^4$  are assumed. By rewriting (2.23) into (2.24).

$$3V_{out}q_{out} + \sum_{capacitors} \Delta V^i q_i = 0 \tag{2.24}$$

Where the capacitors' voltage ripple is represented as  $\Delta V^i = q_i/2C_i$ , then by dividing by  $q_{out}^2$  then

$$\frac{3V_{out}}{q_{out}} + \sum_{i=1}^{number \ of \ C} \frac{(a_{c,i})^2}{2C_i \ fsw} = 0$$

(2.25)

where

$$\frac{V_{out}}{q_{out}f_{sw}} = R_{ssl}$$

$$R_{ssl} = \frac{1}{6} \sum_{i=1}^{number \ of \ C} \frac{(a_{c,i})^2}{C_i \ fsw}$$

(2.26)

$R_{ssl}$  represents the charging and discharging loss caused by the capacitors. Based on (2.2 two possible ways to reduce  $R_{ssl}$  impedance either by increasing  $C_i$  or fsw. Figure 2.8 a Figure 2.9 show the increase in  $C_i$  and fsw optimized the output voltage and efficiency two-level PSC converter with 10V input voltage. However, this increase would reduce a increase the power density and switching loss, respectively [10].

Figure 2.8: Switching frequency against the output voltage.

Figure 2.9: The 1-to-4 PSC efficiency at different capacitors' sizes.

## 2.4 Fast-switching limit impedance of the second order PSC converter

Another important parameter can be determined by analyzing the SC converter to find the fast switching limit ( $R_{Fsl}$ ). Similar to  $a_{c,i}$ , each switch in the SC converter has a charge multiplier value that is represented as  $a_r$ .

$$a_r = [a_{r,s1} \ a_{r,s2} \ a_{r,s3} \ a_{r,s4} \ a_{r,s5} a_{r,s6} \ a_{r,s7} \ a_{r,s8}]^I$$

(2.27)

$a_r$  charge multipliers of the eight switches of the 1-o-4 PSC converter are presented in (2.28),

$$a_r = \begin{bmatrix} 1 & 1 & 1 & 1 & 1 & 1 & 1 \end{bmatrix}^T$$

(2.28)

The passing current trough of each switch is assumed to be constant. Since four modes of operation exist, the charge flow is multiplied by 4.

$$i_r = 4q_r f_{sw} \tag{2.29}$$

The average power loss of each switch can be calculated by multiplying the total of the multiplication  $R_{ds_on}$  by (2.29). Due to the four modes of operation,  $P_{Fsl}$  is divided by 4

$$P_{Fsl} = \sum_{i=1}^{number \ of \ S} \frac{1}{4} (4a_{r,i}iout)^2$$

(2.30)

$$R_{Fsl} = 4 \sum_{i=1}^{number \ of \ S} R_{ds_on}(a_{r,i})^2$$

(2.31)

where  $(a_{r,i})$  is the charge multiplier of eight switches in the 1-to-4 PSC converter.

| Elements               | Equation                 |

|------------------------|--------------------------|

| $S_1, S_2, S_3, S_4$   | V <sub>in</sub>          |

| $S_5, S_6, S_7, S_8$   | $2V_{in}$                |

| $C_{1}, C_{2}, C_{f1}$ | V <sub>in</sub>          |

| $C_{f2}$               | 2 <i>V</i> <sub>in</sub> |

Table 2.3: Equation of the voltage stress on all semiconductors and capacitors.

## 2.5 Generalized power switched-capacitor converter

The proposed PSC converter contains one or more voltage doublers depending on the number of stages (Figure 2.10-a). Each cascaded voltage doubler is considered as a single stage of the PSC converter; for instance, three stages of PSC mean three voltage doublers are cascaded. Since each voltage doubler works to double the input voltage, each output voltage of a stage (voltage doubler) is the input voltage of a higher stage where the last stage will be connected to the output load. To generalize the PSC converter voltage gain, each additional stage (voltage doubler) is supplied by the output of the previous stage. Doubling each output of a certain stage concludes that the output voltage is a multiplication of the input voltage by  $2^n$  where n is the number of stages. Each stage is controlled by group signals that contain two control signals with a  $\frac{T}{2}$  phase shift between them (Figure 2.10-b). For more than one stage, a phase shift is equal to  $\frac{T}{2n}$  between any control group where *n* is the number of the stage. For example, if PSC has three stages, then three control groups are needed, and each group has two control signals. The first group is the reference, whereas  $\frac{T}{4}$  and  $\frac{T}{6}$  are phase shifts of the second and third groups, respectively.

Figure 2.10: a) voltage doubler converter b) a generalized control diagram of the PSC converter.

Figure 2.11: Two cascaded voltage doubler converters and formalized two stages of PSC converter.

## 2.6 A comparison between the proposed PSC converter with three SC converter topologies

The comparison between the proposed PSC and three known SC converter topologies covers the fundamental efficiency and output impedance. The proposed PSC converter successfully shows a privilege over the three other topologies in high efficiency achievement whereas a 1-to-4 ladder has the lowest efficiency as in Figure 2.13. In addition to that, the PSC converter successfully achieves SSL limit at a lower switching frequency faster than the other topologies as in Figure 2.14. In other words, the PSC converter requires less switching frequency to achieve a lower output impedance. A second lowest output impedance among the compared topologies, which is a series to parallel topology, means an additional comparison must be calculated between the PSC converter and 1-to-4 series to parallel the number of switches and the maximum voltage stress across the switches.

Figure 2.12: The efficiency of four compared topologies at different rated power.

Figure 2.13: The output impedance of four compared topologies at different switching frequency.

Figure 2.14: A comparison between PSC and series to parallel topologies in maximum stress on switches

Figure 2.15: A comparison between PSC and series to parallel topologies in number of switches

## CHAPTER THREE: AN INCOMPLETE SOFT-CHARGING OPERATION OF THE SECOND ORDER PSC CONVERTER

### **3.1 Introduction**

The traditional technique to analyze a SC converter is known as a hardcharging operation where improving the output impedance depends on capacitors sizes and switching frequency. As an alternative technique of the hard-charging operation or the traditional technique, in this chapter the soft charging operation will be discussed. This technique is used to reduce the capacitors' sharing losses, improve their charging operation and reduce switching frequency requirement. To apply the soft-charging operation, a current load is placed as an output load. Across the current load, the voltage mismatch between capacitors and the input of the capacitors and the output is mostly presented. Charging and discharging capacitors losses which occur in the conventional SC converter (hard-charging) will be recovered by applying a soft-charging operation. Thus, resizing capacitors is possible and recommended. However, reducing capacitors' sizes causes a higher output voltage ripple which requires an insertion of an output LC filter to recover it. Moreover, a soft-charging operation helps to reduce the output impedance of the SC converter in its two limits, SSL and FSL. As mentioned in chapter 2, SSL limit is inversely proportional to switching frequency, thus the soft-charging operation helps to the SC converter achieve SSL limit at a lower switching frequency instead of a higher switching frequency as in hard-charging operation.

In this chapter an incomplete soft-charging operation of the proposed PSC converter will be discussed. Applying reduced voltage matrices of each operation mode and determining their null spaces are useful techniques to find the voltage change of each capacitor. The current transient and the voltage mismatch dispersions which are the essential benefits of the soft-charging technique are obtained for the second order of PSC converters. In addition to that, a reduction of the output impedance was determined by calculating its SSL limit [42-46].

### 3.2 An incomplete soft-charging operation of the second order PSC

To determine the flowing charge and the changing capacitors' voltage for the 1to-4 PSC converter, we applied a KCL. Corresponding to the timing diagram in Figure 2.3-a, four operation modes are presented in Figure 2.3-b. The elements of each circuit in Figure 2.3-b, which are  $V_{in}$ ,  $V_{C_1}$ ,  $V_{C_2}$ ,  $V_{C_{f1}}$ ,  $V_{C_{f2}}$  and  $V_{out}$ , can be written in a voltage vector form.

$$V = [V_{in} V_{C_1} V_{C_2} V_{C_{f1}} V_{C_{f2}} V_{out}]^T$$

(3.1)

Each phase in Figure 2.3-b has four possible loops that can be expressed in a reduced matrix loop (3.3) [55]

$$A_i V^i = 0 \tag{3.2}$$

The reduced matrix's loops for the four modes can be written as in (3.3),

$$A_{1} = \begin{bmatrix} -1 & -1 & -1 & 0 & 0 & 1 \\ -1 & -1 & 0 & 0 & -1 & 1 \\ -1 & 0 & 0 & -1 & -1 & 1 \\ -1 & 0 & -1 & -1 & 0 & 1 \end{bmatrix}$$

$$A_{2} = \begin{bmatrix} -1 & -1 & -1 & 0 & 0 & 1 \\ -1 & -1 & 0 & 0 & 1 & 0 \\ 0 & -1 & -1 & -1 & 0 & 1 \\ 0 & 0 & -1 & 0 & -1 & 1 \end{bmatrix}$$

$$A_{3} = \begin{bmatrix} -1 & -1 & -1 & 0 & 0 & 1 \\ -1 & 0 & 0 & -1 & 1 & 0 \\ -1 & 0 & -1 & -1 & 0 & 1 \\ -1 & -1 & 0 & 0 & 1 & 0 \end{bmatrix}$$

$$A_{4} = \begin{bmatrix} -1 & -1 & -1 & 0 & 0 & 1 \\ 0 & -1 & -1 & -1 & 0 & 1 \\ 0 & -1 & 0 & -1 & -1 & 1 \\ -1 & -1 & 0 & 0 & -1 & 1 \end{bmatrix}$$

(3.3)

At the end of each mode, the voltage vectors become  $\Delta V^i + V^i$

$$A_i \left( \Delta V^i + V^i \right) = 0 \tag{3.4}$$

where  $\Delta V^i$  is the voltage change related to the load received charge. From (3.2) and (3.4), we have

$$A_i \Delta V^i = 0 \tag{3.5}$$

In the steady state assumption, the total voltage changes for the four operation modes equal zero.

$$\Delta V^1 + \Delta V^2 + \Delta V^3 + \Delta V^4 = 0 \tag{3.6}$$

since  $V_{in}$  is a constant DC source, then  $\Delta V_{in} = 0$ . To satisfy  $\Delta V_{in} = 0$  a row with [1 0 0 0 0 0] is added to  $A_i$

$$\Delta V^{1} = a_{1}W_{1} + a_{2}W_{2}$$

$$\Delta V^{2} = b_{1}U_{1} + b_{2}U_{2}$$

$$\Delta V^{3} = c_{1}H_{1} + c_{2}H_{2}$$

$$\Delta V^{4} = d_{1}X_{1} + d_{2}X_{2}$$

(3.7)

where  $W_1, W_2, U_1, U_2, H_1, H_2, X_1, X_2$  are null spaces of the modified  $A_i$  matrices (after adding  $\begin{bmatrix} 1 & 0 & 0 & 0 & 0 \end{bmatrix}$ ).

$$W = \begin{cases} \begin{pmatrix} 0 \\ 0.3541 \\ -0.5891 \\ 0.3541 \\ -0.5891 \\ -0.235 \end{bmatrix}, \begin{bmatrix} 0 \\ 0.4996 \\ 0.1673 \\ 0.4996 \\ 0.1673 \\ 0.4996 \\ 0.1673 \\ 0.6669 \end{bmatrix} \end{cases}$$

$$U = \begin{cases} \begin{pmatrix} 0 \\ 0.6295 \\ -0.3832 \\ 0 \\ 0.6295 \\ 0.2463 \end{bmatrix}, \begin{bmatrix} 0 \\ 0.0612 \\ 0.6732 \\ 0 \\ 0.0612 \\ 0.7344 \end{bmatrix}$$

$$H = \begin{cases} \begin{pmatrix} 0 \\ -0.1035 \\ -0.642 \\ -0.1035 \\ -0.1035 \\ -0.7455 \end{bmatrix}, \begin{bmatrix} 0 \\ 0.5244 \\ -0.3991 \\ 0.5244 \\ 0.5244 \\ 0.5244 \\ 0.1253 \end{bmatrix} \end{cases}$$

$$X = \left\{ \begin{bmatrix} 0\\ 0.6136\\ -0.5569\\ 0\\ -0.5569\\ 0.0566 \end{bmatrix}, \begin{bmatrix} 0\\ 0.4728\\ 0.2997\\ 0\\ 0.2997\\ 0.7725 \end{bmatrix} \right\}$$

(3.8)

The voltage change  $\Delta V^i$  can be calculated by

$$\Delta V^{1} = a_{1}W_{1} + a_{2}W_{2}$$

$$\Delta V^{2} = b_{1}U_{1} + b_{2}U_{2}$$

$$\Delta V^{3} = c_{1}H_{1} + c_{2}H_{2}$$

$$\Delta V^{4} = d_{1}X_{1} + d_{2}X_{2}$$

(3.9)

where  $a_1$ ,  $a_2$ ,  $a_3$ ,  $a_4$ ,  $b_1$ ,  $b_2$ ,  $b_3$  and,  $b_4$  can be found by (3.10), and  $\overline{W_1}$   $\overline{W_2}$   $\overline{U_1}$   $\overline{U_2}$   $\overline{H_1}$   $\overline{H_2}$   $\overline{X_1}$   $\overline{X_2}$  are the reduced form of  $W_1, W_2 U_1, U_2 H_1, H_2, X_1$ , and  $X_2$  (after eliminating the last row corresponding to  $\Delta V_{out}$ ). The  $\Delta V_{out}$  is zero at an inductive load case.

$$\begin{bmatrix} \overline{W_1} & \overline{W_2} & \overline{U_1} & \overline{U_2} & \overline{H_1} & \overline{H_2} & \overline{X_1} & \overline{X_2} \end{bmatrix} \begin{bmatrix} a_1\\a_2\\a_3\\a_4\\b_1\\b_2\\b_3\\b_4 \end{bmatrix} = 0$$

(3.10)

$$\begin{bmatrix} a_1 \\ a_2 \\ a_3 \\ a_4 \\ b_1 \\ b_2 \\ b_3 \\ b_4 \end{bmatrix} = \begin{bmatrix} -0.6794 \\ 0.3024 \\ -0.3050 \\ -0.1486 \\ 0.0837 \\ 0.1872 \\ 0.4934 \\ -0.215 \end{bmatrix}$$

(3.11)

Now (3.9) can be solved to calculate  $\Delta V^i$ .

$$\Delta V^{1} = \begin{bmatrix} 0 \\ -0.0895 \\ 0.4508 \\ -0.0895 \\ 0.4508 \\ 0.3613 \end{bmatrix} \Delta V^{2} = \begin{bmatrix} 0 \\ -0.2011 \\ 0.0168 \\ 0 \\ -0.2011 \\ -0.1843 \end{bmatrix}$$

$$\Delta V^{3} = \begin{bmatrix} 0 \\ -0.0895 \\ -0.1284 \\ 0.0895 \\ 0.0895 \\ -0.0389 \end{bmatrix} \Delta V^{4} = \begin{bmatrix} 0 \\ 0.2011 \\ -0.3392 \\ 0 \\ -0.3392 \\ -0.1382 \end{bmatrix}$$

(3.12)

From (2.21) and (3.11) the capacitor sizes can be found by (3.13)

$$C_j = q_j / \Delta V_{Cj} \tag{3.13}$$

# 3.3 Slow-switching limit impedance $(R_{ssl})$ of second order PSC converter at a complete soft-charging operation

Similar to  $R_{ssl}$  calculation in section 2.3, the  $R_{ssl}$  of the PSC converter at softcharging operation can be determine by using the following equation.

$$R_{ssl} = \frac{1}{6} \sum_{i=1}^{number \ of \ C} \frac{(a_{c,i})^2}{C_i \ fsw}$$

(3.14)

Where

$$\sum_{i=1}^{number \ of \ C} (a_{c,i})^2 = \frac{25}{18}$$

the voltage change  $\Delta V_{Cj}$  of  $C_{f1}$  and  $C_{f2}$  is smaller than  $\Delta V_{Cj}$  of  $C_1$  and  $C_2$ , and as a result  $C_{f1}$  and  $C_{f2}$  need to be larger than  $C_1$  and  $C_2$ . Thus, a reduction in  $C_1$  and  $C_2$  sizes reduces their voltage multipliers. This reduction in the total of capacitors' voltage multipliers results in a lower output impedance. A lower output impedance means a lower switching frequency is required to charge and discharge capacitors with maintained losses.

## CHAPTER FOUR: A COMPLETE SOFT-CHARGING OPERATION OF THE SECOND ORDER PSC CONVERTER

### **4.1 Introduction**

To achieve a complete soft-charging operation of any SC topologies, a split-phase control diagram is needed. The split phase diagram includes a dead time interval between any operation modes which are called transition modes. Moreover, instead of 50% duty cycle, some switches in the circuit operate in a duty cycle less than 50%. In their traditional operation, SC converters' capacitors are exiting and participating their charging and discharging processes in all conventional operation modes. In the split phase soft-charging operations, each transition mode at which some of the capacitors are isolated is considered. Capacitors' losses are mostly recovered by applying a complete soft-charging operation because of some capacitors' isolation. In this chapter, a split-phase control for the 1-to-4 PSC converter has been proposed.

### 4.2 A complete soft-charging operation of the second order PSC converter

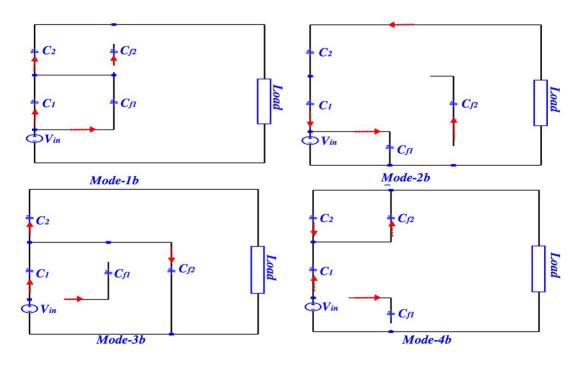

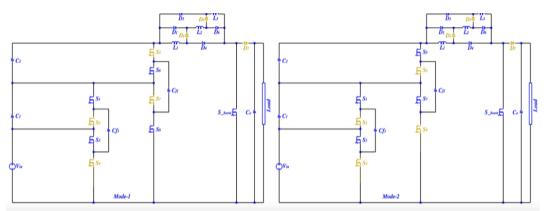

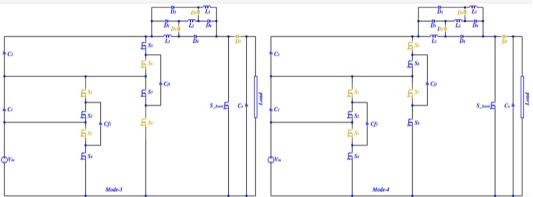

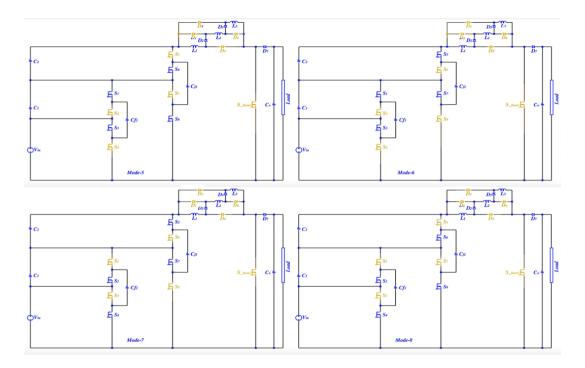

The complete soft-charging analysis can be satisfied if and only if the Kirchhoff's voltage low (KVL) exists at all operation modes including the four transition modes. The control diagram in Figure 4.1-a allows eight modes of operation to exist as in Figure 4.1b. Four of those modes are the same as the four modes of the conventional PSC converter in Figure 2.3-b where the new four modes are basically the transition modes. The same procedures as applied for the incomplete soft-charging are repeated in this section. The  $A_i$  and  $B_i$  matrices Mode-1a, Mode-2a, Mode-3a, and Mode-4a are the same matrices as in Section 3.2. Since the extra four transition modes have three capacitors, only two KVL loops are possible for  $A_i$  matrices, which are presented as in following reduced loop.

$$A_{1b} = \begin{bmatrix} -1 & -1 & -1 & 0 & 0 & 1 \\ -1 & 0 & -1 & -1 & 0 & 1 \end{bmatrix}$$

$$A_{2b} = \begin{bmatrix} -1 & -1 & -1 & 0 & 0 & 1 \\ 0 & -1 & -1 & -1 & 0 & 1 \end{bmatrix}$$

$$A_{3b} = \begin{bmatrix} -1 & -1 & -1 & 0 & 0 & 1 \\ -1 & -1 & 0 & 0 & 1 & 0 \end{bmatrix}$$

$$A_{4b} = \begin{bmatrix} -1 & -1 & -1 & 0 & 0 & 1 \\ -1 & -1 & 0 & 0 & -1 & 1 \end{bmatrix}$$

(4.1)

Although the transition modes contain three capacitors, their charge flow directions are the same as the charge flow direction of the basic modes as in Figure 2.7. However, the number of nodes in the transition modes is five instead of four due to the floating capacitor terminals. Since both terminals are floating, they are considered one node and expressed in an extra row in  $B_i$ . By using (2.17), the reduced matrices of the transition modes as in Figure 4.1 are presented as following (4.2).

Figure 4.1: (a) A proposed timing diagram to achieve a complete soft-charging in the 1-to-4 PSC converter; (b) eight operation modes of the 1-to-4 PSC converter in the complete soft-charging technique.

Figure 4.2: The charge flow for the split operation modes in the 1-to-4 PSC converter.

$$B_{1b} = \begin{bmatrix} -1 & 1 & 0 & 1 & 0 & 0 \\ 0 & -1 & 1 & -1 & 0 & 0 \\ 0 & 0 & -1 & 0 & 0 & 1 \\ 1 & 0 & 0 & 0 & 0 & -1 \\ 0 & 0 & 0 & 0 & 1 & 0 \end{bmatrix}$$

$$B_{2b} = \begin{bmatrix} -1 & 1 & 0 & 1 & 0 & 0 \\ 0 & -1 & -1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & -1 \\ 1 & 0 & 0 & -1 & 0 & 1 \\ 0 & 0 & 0 & 0 & 1 & 0 \end{bmatrix}$$

$$B_{3b} = \begin{bmatrix} -1 & 1 & 0 & 0 & 0 & 0 \\ 0 & -1 & 1 & 0 & 1 & 0 \\ 0 & 0 & 1 & 0 & 0 & -1 \\ 1 & 0 & 0 & 0 & 1 & 1 \\ 0 & 0 & 0 & 1 & 0 & 0 \end{bmatrix}$$

$$B_{4b} = \begin{bmatrix} -1 & 1 & 0 & 0 & 0 & 0 \\ 0 & -1 & -1 & 0 & 1 & 0 \\ 0 & 0 & 1 & 0 & -1 & 1 \\ 1 & 0 & 0 & 0 & 0 & -1 \\ 0 & 0 & 0 & 1 & 0 & 0 \end{bmatrix}$$

(4.2)

By applying the (2.17) the charge flow of the eight modes are the null space vectors of matrices  $B_i$

$$q_{c}^{1,a} = \begin{bmatrix} 3\\1\\1\\2\\2\\3 \end{bmatrix} q_{c}^{1,b} = \begin{bmatrix} -1\\1\\2\\0\\1 \end{bmatrix}$$

$$q_{c}^{2,a} = \begin{bmatrix} -3\\-1\\-1\\-2\\-2\\-2\\-1 \end{bmatrix} q_{c}^{2,b} = \begin{bmatrix} -1\\1\\-1\\-2\\0\\-1 \end{bmatrix}$$

$$q_{c}^{3,a} = \begin{bmatrix} 3\\1\\1\\2\\2\\1\\1 \end{bmatrix} q_{c}^{3,b} = \begin{bmatrix} 1\\1\\0\\2\\1\\1 \end{bmatrix}$$

$$q_{c}^{4,a} = \begin{bmatrix} -3\\-1\\-1\\-2\\-2\\-1\\1 \end{bmatrix} q_{c}^{4,b} = \begin{bmatrix} -1\\-1\\-1\\0\\-2\\-1\\1 \end{bmatrix}$$

(4.3)

By using (2.21), (2.19) can be rewritten with respect to the output charge of the capacitors and the load similar to (2.22).

The last rows in (4.3) represent the delivered charge. The total input charge equals 16, which is the sum of the input charges for all eight modes (4.3). The duty cycle of each mode to achieve a complete soft-charging is calculated in (4.4). Each mode has a certain duty cycle where the sum of the modes' duty cycles completes one period of the proposed split-phase control in as Figure 4.1-a.

$$D_{1a} = D_{2a} = D_{3a} = D_{4a} = \frac{q_{input\_i}}{q_{input\_total}} = \frac{3}{16}$$

$$D_{1b} = D_{2b} = D_{3b} = D_{4b} = \frac{q_{input\_i}}{q_{input\_total}} = \frac{1}{16}$$

(4.4)

## **4.3.** Generalized split-phase control diagram of the power switched-capacitors converter