# University of Wisconsin Milwaukee UWM Digital Commons

Theses and Dissertations

May 2017

# Theory, Simulation, and Implementation of Grid Connected Back to Back Converters Utilizing Voltage Oriented Control

Sean C. Cunningham University of Wisconsin-Milwaukee

Follow this and additional works at: https://dc.uwm.edu/etd Part of the <u>Electrical and Electronics Commons</u>

#### **Recommended** Citation

Cunningham, Sean C., "Theory, Simulation, and Implementation of Grid Connected Back to Back Converters Utilizing Voltage Oriented Control" (2017). *Theses and Dissertations*. 1460. https://dc.uwm.edu/etd/1460

This Thesis is brought to you for free and open access by UWM Digital Commons. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of UWM Digital Commons. For more information, please contact open-access@uwm.edu.

# THEORY, SIMULATION, AND IMPLEMENTATION OF GRID CONNECTED BACK TO BACK

# CONVERTERS UTILIZING VOLTAGE ORIENTED CONTROL

by

Sean Cunningham

A Thesis Submitted in

Partial Fulfillment of the

Requirements for the Degree of

Master of Science

in Engineering

at

The University of Wisconsin-Milwaukee

May 2017

#### ABSTRACT

## THEORY, SIMULATION, AND IMPLEMENTATION OF GRID CONNECTED BACK TO BACK CONVERTERS UTILIZING VOLTAGE ORIENTED CONTROL

by

Sean Cunningham

The University of Wisconsin-Milwaukee, 2017 Under the Supervision of Professor Adel Nasiri

This work presents a back to back converter topology with the ability to connect two power systems of different voltages and frequencies for the exchange of power. By utilizing indirect AC/AC conversion decoupling is achieved between the power systems with one of the three-phase, two-level voltage source converters performing the AC/DC conversion that maintains the required DC bus voltage level at unity power factor while the other converter operates in all four quadrants supplying/consuming active and/or reactive power with the other power system. The prototype implementation resides at UW-Milwaukee's USR Building microgrid test bed facility. A possible application topology would be the converter that maintains the DC bus voltage to be connected to the microgrid's electrical bus of distributed energy sources while the other converter is connected to the utility in order to supply the required active and/or reactive power to support the needs of the grid.

ii

© Copyright by Sean Cunningham, 2017 All Rights Reserved То

my parents

and sister

| LIST OF FIGURES                                              | viii |

|--------------------------------------------------------------|------|

| LIST OF TABLES                                               | xiii |

| LIST OF ABBREVIATIONS                                        | xiv  |

| LIST OF SYMBOLS                                              | xv   |

| 1. Introduction                                              | 1    |

| 2. Background and System Architecture                        | 1    |

| 2.1. Space Vector Modulation                                 | 2    |

| 2.2. Vector Control                                          | 3    |

| 2.2.1. Voltage Oriented Control and the System Dynamic Model | 3    |

| 2.3. Current Controllers                                     | 6    |

| 2.3.1. Proportional-Integral Controller Model                | 6    |

| 2.3.2. Converter Model                                       | 7    |

| 2.3.3. Feedforward and Disturbance Decoupling                | 8    |

| 2.3.4. Anti-Aliasing Filter Feedback Model                   | 9    |

| 2.3.5. Per-Unit Representation                               | 9    |

| 2.3.6. Block Diagram Representation of Transfer Functions    | 10   |

| 2.3.7. Modulus Optimum Tuning of Current Controller          |      |

| 2.4. Voltage Controller                                      | 15   |

| 2.4.1. Proportional-Integral Controller Model                | 15   |

| 2.4.2. Approximation of Current Controller Model             | 16   |

| 2.4.3. Power Balance Model                                   | 16   |

| 2.4.4. Digital Filter Feedback Model                         |      |

| 2.4.5. Per-Unit Representation                               | 18   |

| 2.4.6. Block Diagram Representation of Transfer Functions    | 19   |

| 2.4.7. Symmetrical Optimum Tuning of Voltage Controller      | 20   |

| 2.5. Active and Reactive Controller Models                   | 23   |

| 2.5.1. Open Loop Model                                       | 24   |

| 2.6. Phase-Locked Loop                                       | 24   |

| 2.6.1. Symmetrical Optimum Tuning of Phase-Locked Loop       | 26   |

|                                                              |      |

# **TABLE OF CONTENTS**

| 3 | Project Implementation                                                    | 28 |

|---|---------------------------------------------------------------------------|----|

|   | 3.1. Supply and Isolation Transformers                                    | 32 |

|   | 3.2. Converter                                                            | 34 |

|   | 3.3. DC Bus Connection                                                    | 34 |

|   | 3.4. Pre-Charge                                                           | 34 |

|   | 3.5. Voltage Divider and Virtual Neutral                                  | 34 |

|   | 3.6. GP-DSP                                                               | 35 |

|   | 3.7. Reactor Selection, DC Bus Level, and Converter Switching Frequency   | 35 |

|   | 3.8. Control Overview                                                     | 40 |

| 4 | Simulation                                                                | 41 |

|   | 4.1. Current Controller Frequency Domain Analysis                         | 41 |

|   | 4.2. Current Controller Time Domain Analysis                              | 45 |

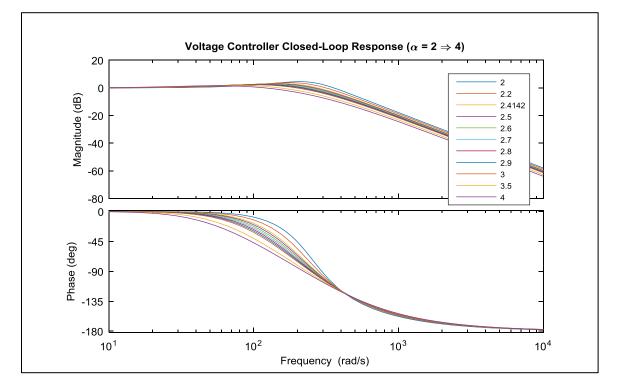

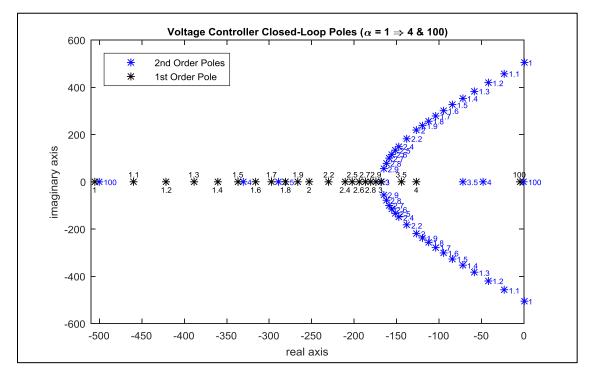

|   | 4.3. Voltage Controller Frequency Domain Analysis                         | 47 |

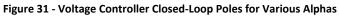

|   | 4.4. Voltage Controller Time Domain Analysis                              | 52 |

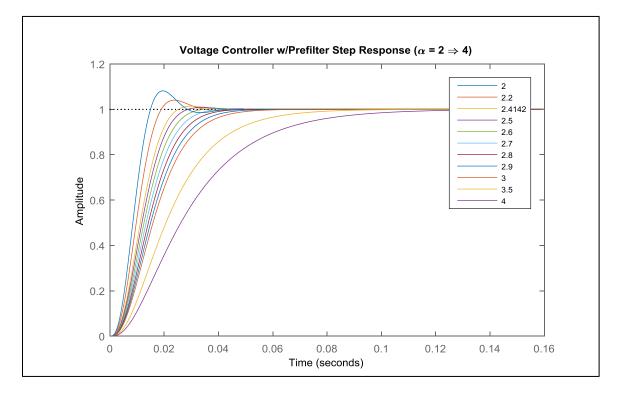

|   | 4.5. Voltage Controller with Prefilter Time Domain Analysis               | 53 |

|   | 4.6. Phase-Locked Loop Frequency Domain Analysis                          | 54 |

|   | 4.7. Continuous versus Discrete Time Domain Analysis                      | 55 |

| 5 | TI C2000 Simulink Implementations and Testing                             | 58 |

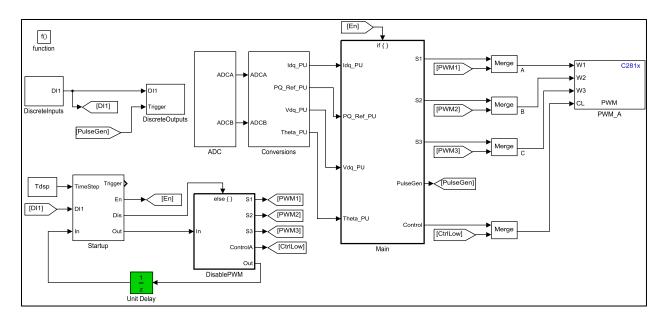

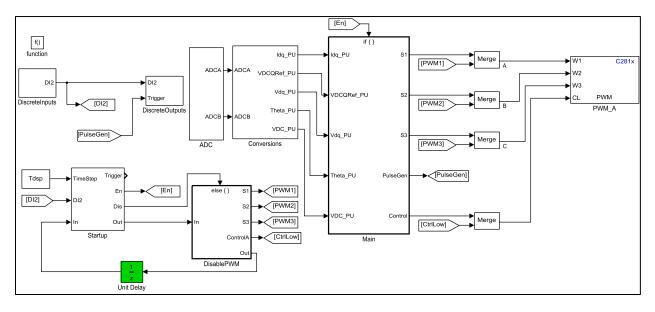

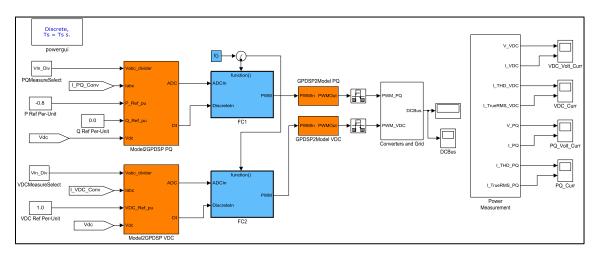

|   | 5.1. "PQ" and "VDC" Converter Simulink Implementations                    | 58 |

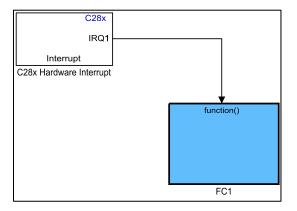

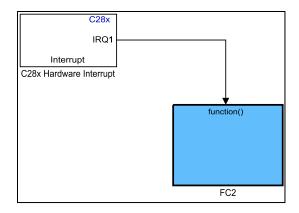

|   | 5.1.1. Hardware Interrupt                                                 | 58 |

|   | 5.1.2. Control Overview                                                   | 59 |

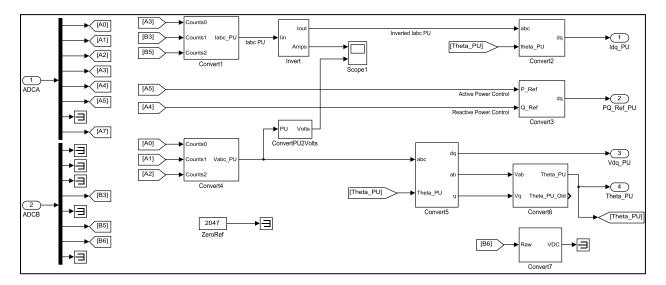

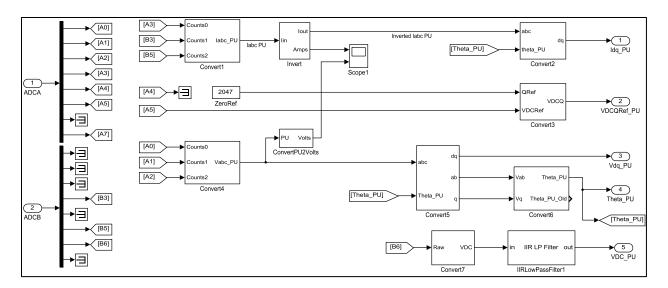

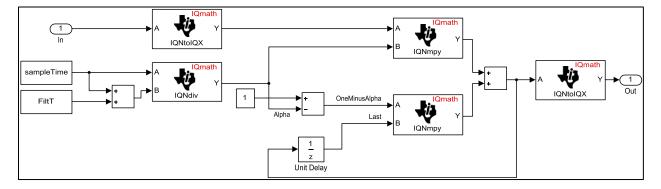

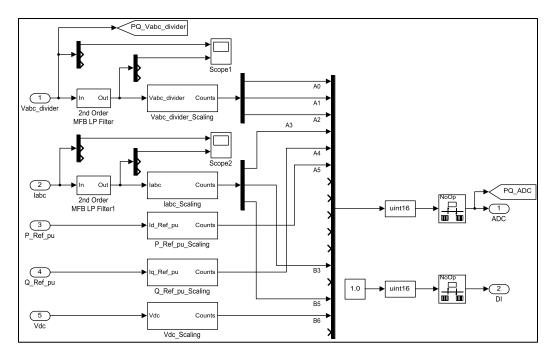

|   | 5.1.3. Signal Conversions                                                 | 60 |

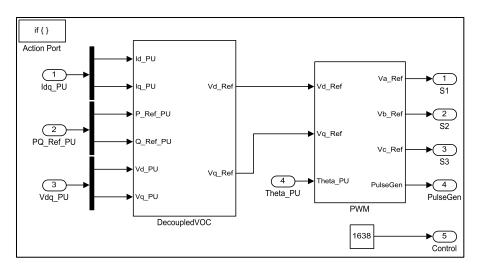

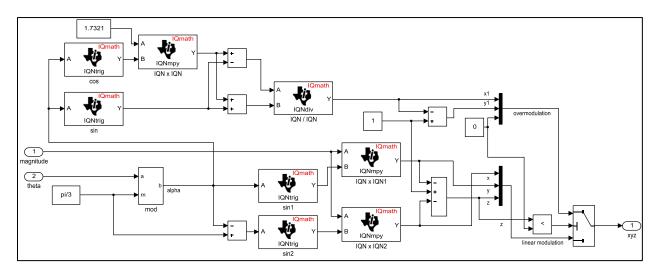

|   | 5.1.4. Decoupled Voltage Oriented Control and PWM References              | 62 |

|   | 5.2. Common Functionality between "PQ" and "VDC" Simulink Implementations | 64 |

|   | 5.2.1. PWM References                                                     | 64 |

|   | 5.2.2. PWM                                                                | 65 |

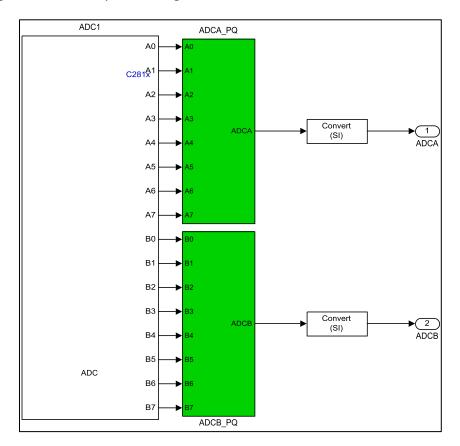

|   | 5.2.3. ADC                                                                | 68 |

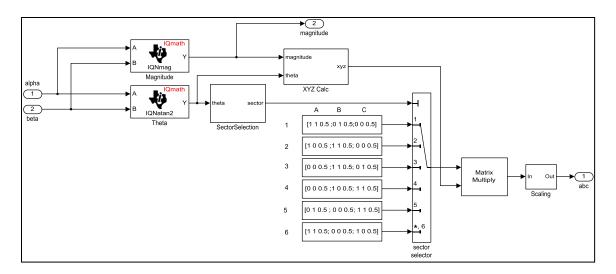

|   | 5.2.4. Space Vector PWM                                                   | 68 |

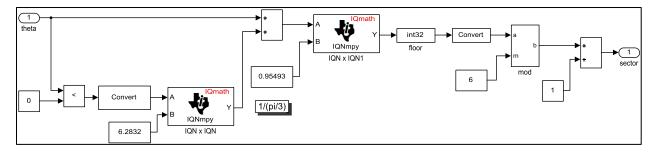

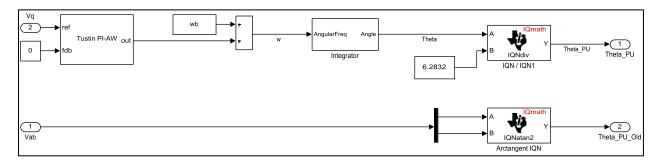

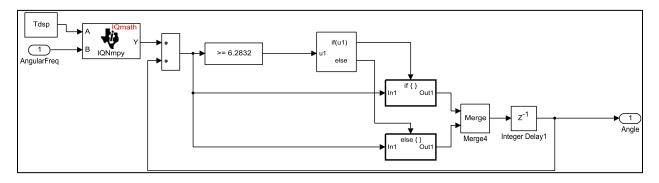

|   | 5.2.5. Phase-Locked Loop                                                  | 71 |

| 5.2.6. Coordinate Transformations                               | 72  |

|-----------------------------------------------------------------|-----|

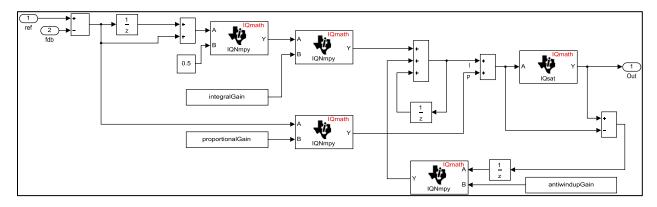

| 5.2.7. Tustin Proportional Integral Controller with Anti-Windup | 74  |

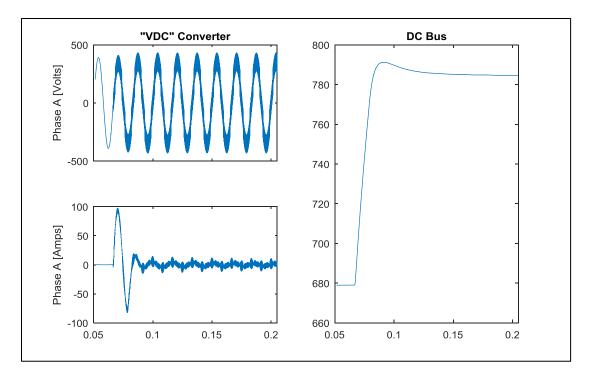

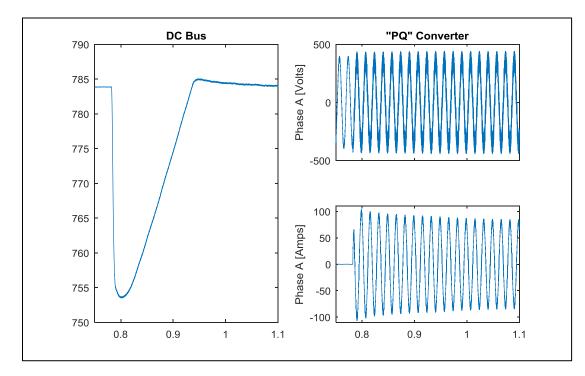

| 5.3. Model-in-the-Loop Simulink Implementation and Testing      | 76  |

| 5.4. Simulation vs. Analytical Harmonic Spectrum                | 82  |

| 6. Experimentation                                              | 85  |

| 6.1. Converter Testing with TI CC Studio GUI Composer           | 85  |

| 6.2. "VDC" Converter Steady-State and Dynamic Responses         |     |

| 6.3. "PQ" Converter Steady-State and Dynamic Responses          |     |

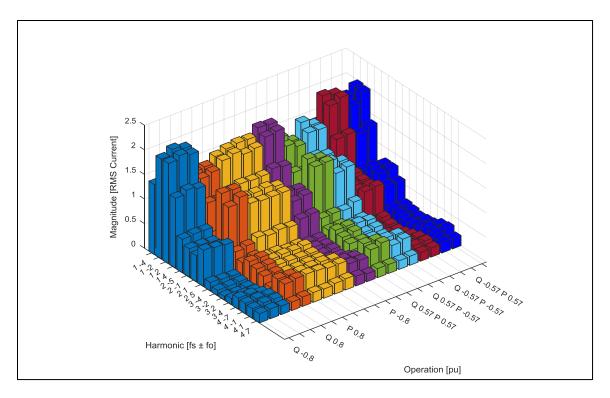

| 6.4. Measured vs. Analytical Harmonic Spectrum                  | 107 |

| 7. Conclusion                                                   | 110 |

| Works Cited                                                     | 111 |

| Appendix A: Per Unit Values                                     | 114 |

| Appendix B: Coordinate Transformations                          | 116 |

| Appendix C: Modulus Optimum                                     | 118 |

| Appendix D: Proportional-Integral Controller Forms              | 119 |

| Appendix E: Discretization Methods                              | 120 |

| Appendix F: Delta/Wye Transformer Equivalent Circuit            | 121 |

# LIST OF FIGURES

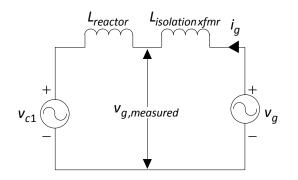

| Figure 1 - Single-Phase Representation of Complex Power Flow                                   |

|------------------------------------------------------------------------------------------------|

| Figure 2 - One Line Diagram Representation of Converter, Impedance, and Grid                   |

| Figure 3 - One Line Diagram Representation of Converter, Impedance, and Grid                   |

| Figure 4 - Three-Phase Representation of Converter, Impedance, and Grid                        |

| Figure 5 - Typical Closed-Loop Feedback System 11                                              |

| Figure 6 - Decoupled Current Controller (d-axis) 11                                            |

| Figure 7 - Decoupled Current Controller (q-axis) 12                                            |

| Figure 8 - Simplified Representation of the Decoupled Current Controller (d-axis) 12           |

| Figure 9 - Simplified Representation of the Decoupled Current Controller (q-axis) 12           |

| Figure 10 - Per Unit Voltage Controller 20                                                     |

| Figure 11 - Simplified Per Unit Voltage Controller 20                                          |

| Figure 12 - Simplified Per Unit Voltage Controller with Prefilter                              |

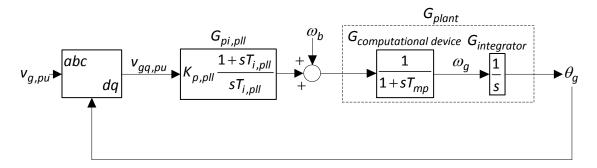

| Figure 13 - Phase-Locked Loop for Grid Voltage Angle Detection                                 |

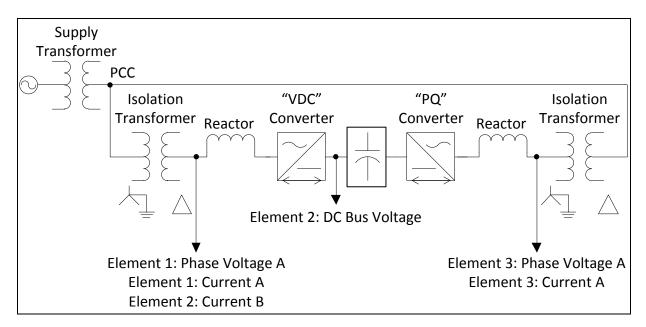

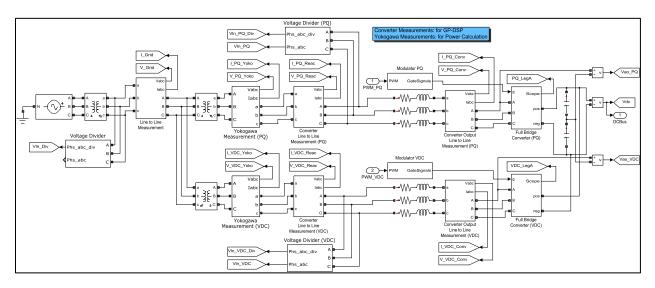

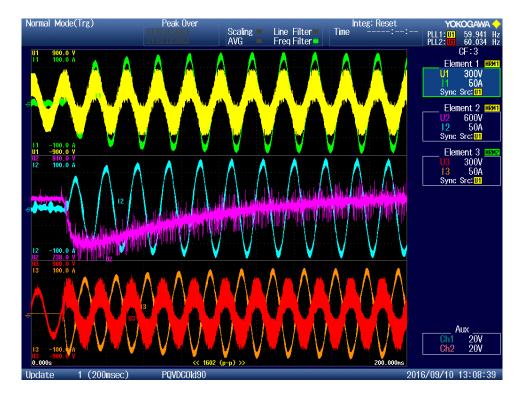

| Figure 14 - Project Implementation & Yokogawa Measurements                                     |

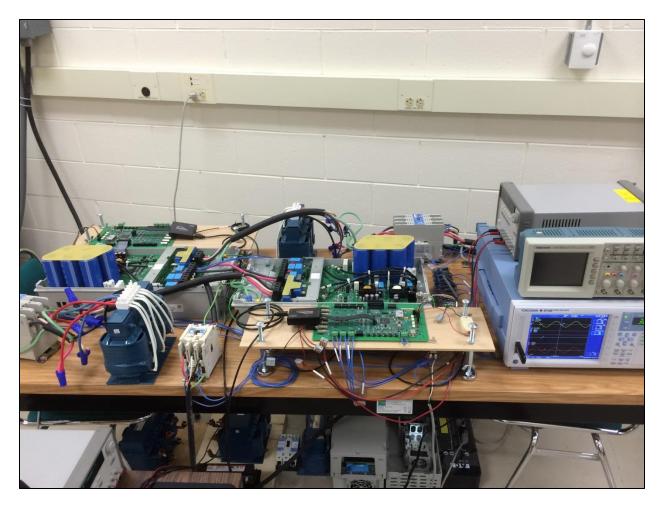

| Figure 15 - Project Photo 1 29                                                                 |

| Figure 16 - Project Photo 2 30                                                                 |

| Figure 17 - Project Photo 3                                                                    |

| Figure 18 - One Line Diagram Representation of Converter, Impedance, and Grid                  |

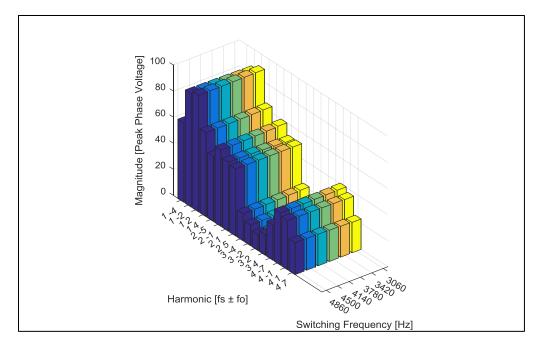

| Figure 19 - Analytical Harmonic Voltage vs. Switching Frequency for Double-edge Symmetrical    |

| Regular Sampled SVM 39                                                                         |

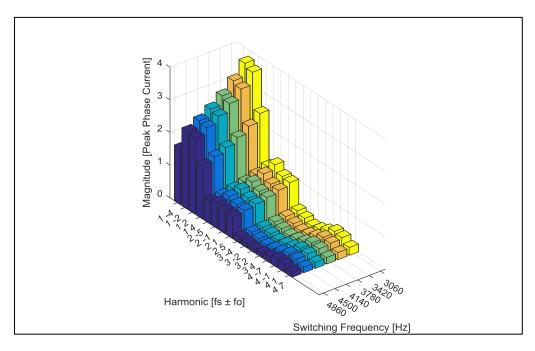

| Figure 20 - Analytical Harmonic Current vs. Switching Frequency for Double-Edge Symmetrical    |

| Regular Sampled SVM                                                                            |

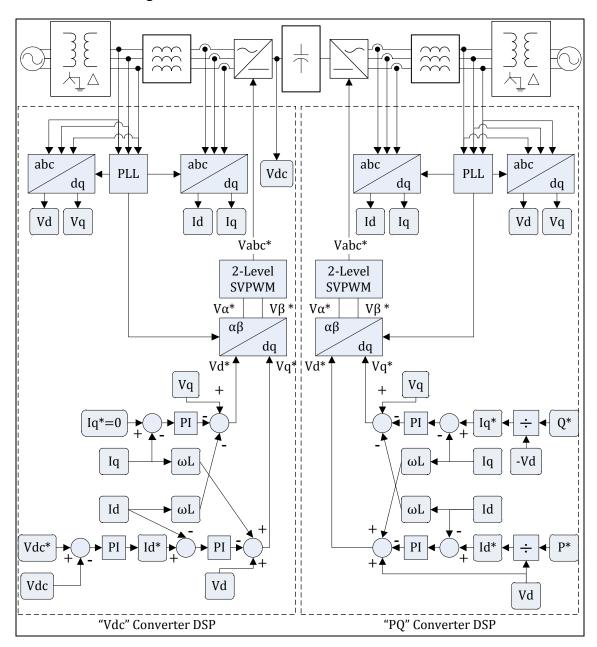

| Figure 21 - Control Overview in Per-Unit 40                                                    |

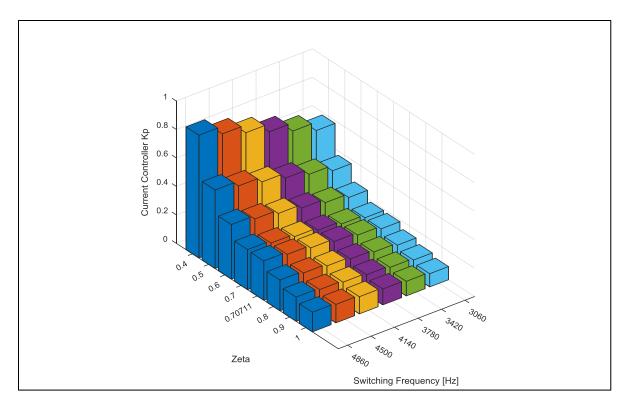

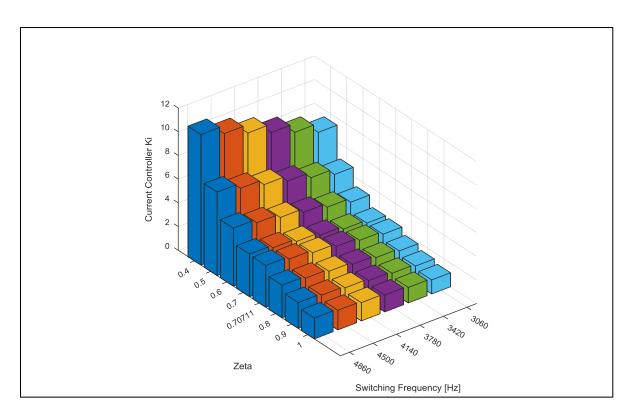

| Figure 22 - Current Controller Proportional Gain versus Switching Frequency versus Damping     |

| Ratio 42                                                                                       |

| Figure 23 - Current Controller Integral Gain versus Switching Frequency versus Damping Ratio42 |

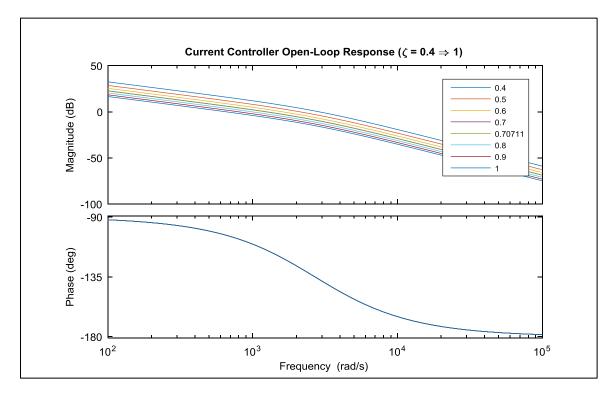

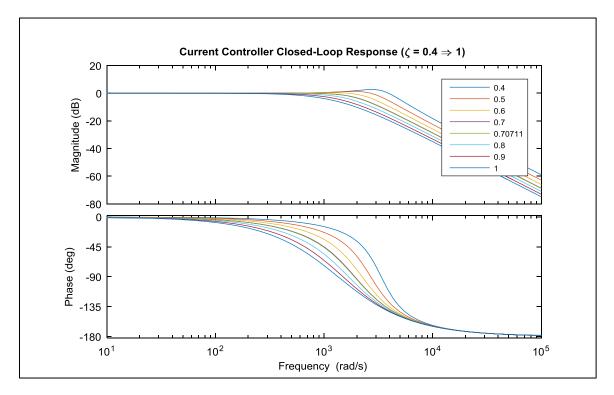

| Figure 24 - Current Controller Open-Loop Response for Various Damping Ratios                   |

| Figure 25 - Current Controller Closed-Loop Response for Various Damping Ratios                 |

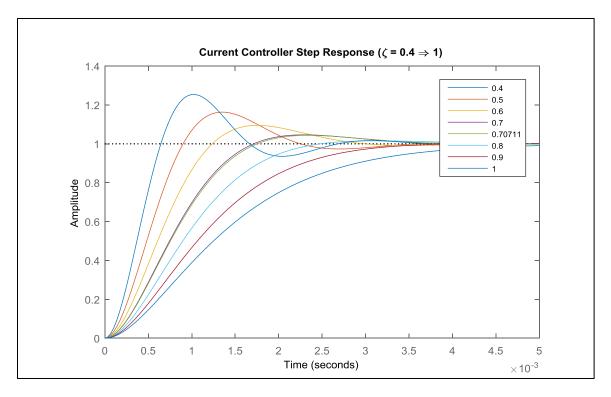

| Figure 26 - Current Controller Step Response for Various Damping Ratios                        |

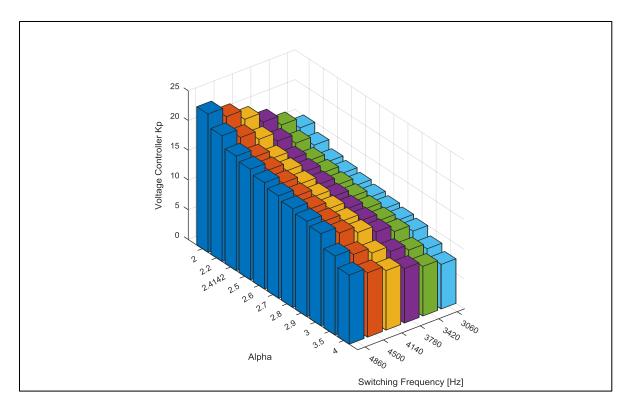

| Figure 27 - Voltage Controller Proportional Gain versus Switching Frequency versus Normalizing |

| Factor                                                                                         |

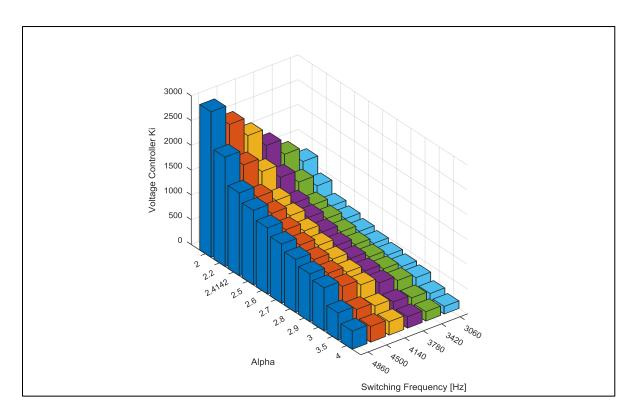

| Figure 28 - Voltage Controller Integral Gain versus Switching Frequency versus Normalizing     |

| Factor                                                                                         |

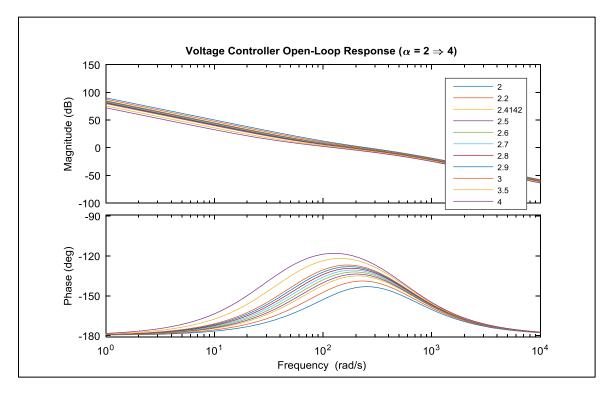

| Figure 29 - Voltage Controller Open-Loop Response for Various Normalizing Factors              |

| Figure 30 - Voltage Controller Closed-Loop Response for Various Normalizing Factors            |

| Figure 31 - Voltage Controller Closed-Loop Poles for Various Alphas                            |

| Figure 32 - Voltage Controller Step Response for Various Normalizing Factors                   |

| Figure 33 - Voltage Controller with Prefilter Step Response for Various Normalizing Factors | . 53 |

|---------------------------------------------------------------------------------------------|------|

| Figure 34 - Phase-Locked Loop Response for Normalizing Factor = 10.0                        | . 55 |

| Figure 35 - Continuous Current Controller                                                   | . 55 |

| Figure 36 - Continuous Voltage Controller                                                   | . 56 |

| Figure 37 - Discrete Current Controller                                                     | . 56 |

| Figure 38 - Discrete Voltage Controller                                                     | . 57 |

| Figure 39 - Discrete Tustin PI Controller with Anti-Windup                                  | . 57 |

| Figure 40 - Continuous vs. Discrete Voltage Controller Step Responses with Integrator Anti- |      |

| Windup                                                                                      | . 57 |

| Figure 41 - "PQ" Converter Hardware Interrupt                                               | . 58 |

| Figure 42 - "VDC" Converter Hardware Interrupt                                              | . 59 |

| Figure 43 - "PQ" Converter Control Overview                                                 | . 60 |

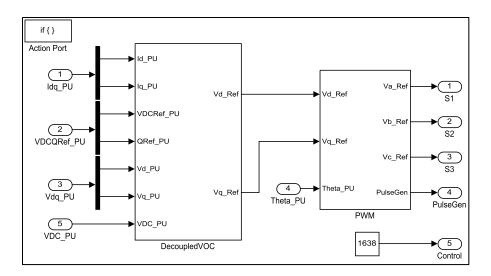

| Figure 44 - "VDC" Converter Control Overview                                                | . 60 |

| Figure 45 - "PQ" Converter Signal Conversions                                               | . 61 |

| Figure 46 - "VDC" Converter Signal Conversions                                              | . 62 |

| Figure 47 - "VDC" Converter IIR Low-Pass Filter for DC Bus Voltage                          | . 62 |

| Figure 48 - "PQ" Converter Decoupled VOC and PWM References                                 | . 63 |

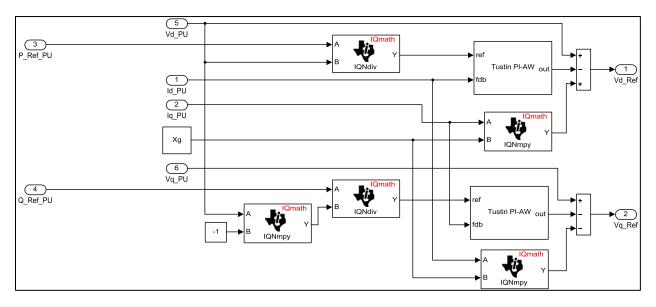

| Figure 49 - "PQ" Converter Decoupled VOC                                                    | . 63 |

| Figure 50 - "VDC" Converter Decoupled VOC and PWM References                                | . 64 |

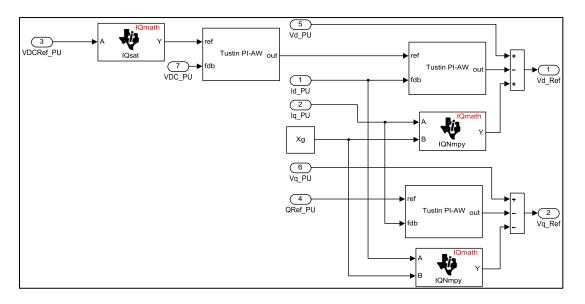

| Figure 51 - "VDC" Converter Decoupled VOC                                                   | . 64 |

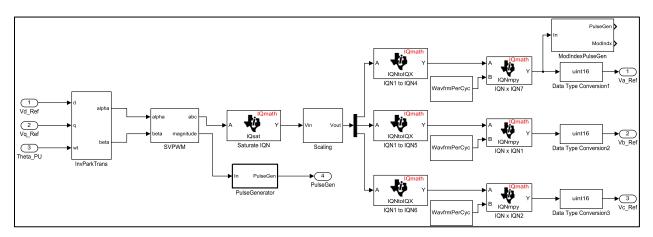

| Figure 52 - Direct-Quadrature Voltage References to TI C2000 PWM References                 | . 65 |

| Figure 53 - PWM Switching Frequency                                                         | . 66 |

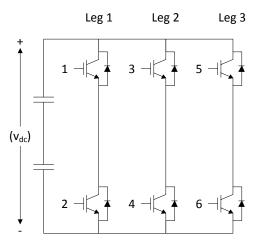

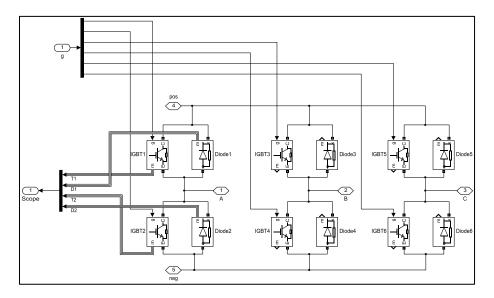

| Figure 54 - Three Phase Full Bridge Converter                                               | . 66 |

| Figure 55 - PWM IGBT Control                                                                | . 67 |

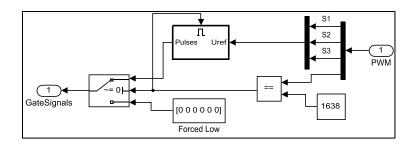

| Figure 56 - PWM Deadband                                                                    | . 67 |

| Figure 57 - "PQ" Converter ADC                                                              | . 68 |

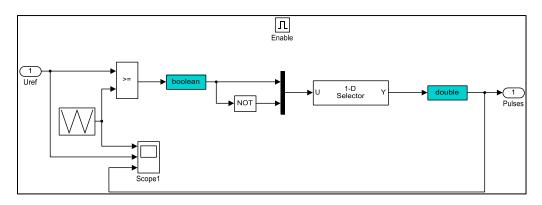

| Figure 58 - Space Vector PWM                                                                | . 69 |

| Figure 59 - SVPWM Sector Selection                                                          | . 69 |

| Figure 60 - SVPWM XYZ Calculation                                                           | . 70 |

| Figure 61 - Phase-Locked Loop                                                               | . 71 |

| Figure 62 - Integrator for PLL                                                              | . 71 |

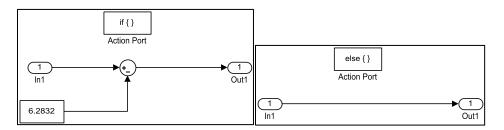

| Figure 63 - PLL Integrator If Else Subsystems                                               | . 71 |

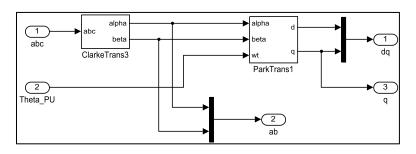

| Figure 64 - Transformation from ABC to Alpha-Beta to Direct-Quadrature                      | . 72 |

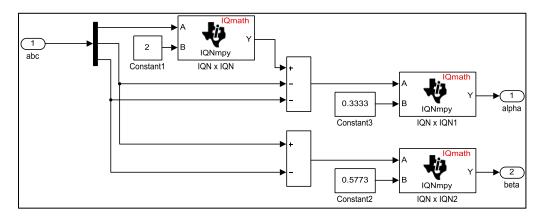

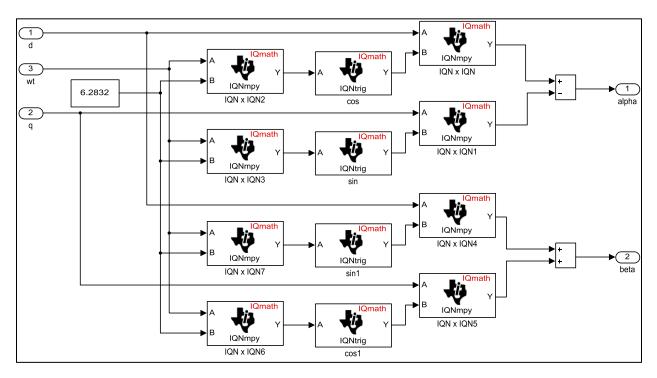

| Figure 65 - Clarke Transformation                                                           | . 72 |

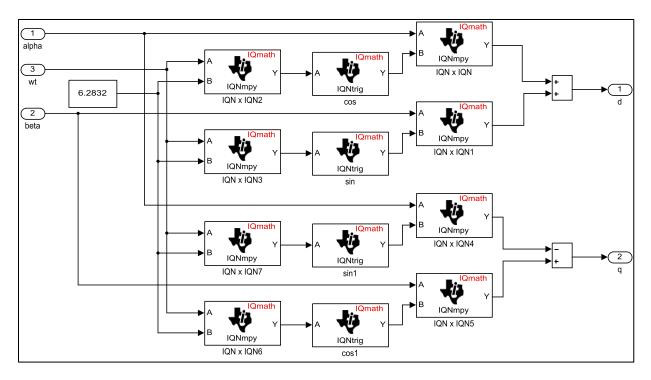

| Figure 66 - Park Transformation                                                             | . 73 |

| Figure 67 - Inverse Park Transformation                                                     | . 73 |

| Figure 68 - Continuous PI Controller with Anti-Windup                                       | . 74 |

| Figure 69 - Discrete PI Controller with Anti-Windup                                         | . 74 |

| Figure 70 - "PQ" Converter Tustin PI Controller with Anti-Windup                             | 75 |

|----------------------------------------------------------------------------------------------|----|

| Figure 71 - System-Level Representation for Model-in-the-Loop Implementation                 | 76 |

| Figure 72 - Three-Phase Two-Level Converter for Model-in-the-Loop Implementation             |    |

| Figure 73 - Modulator for Model-in-the-Loop Implementation                                   |    |

| Figure 74 - Gate Driver Signal Generation for Model-in-the-Loop Implementation               | 77 |

| Figure 75 - Model-in-the-Loop Implementation                                                 |    |

| Figure 76 - Model-in-the-Loop Link to "PQ" Converter Simulink Implementation                 |    |

| Figure 77 - "VDC" Converter Step at 4860Hz with Double-Edge Asymmetrical Regular Sampled     |    |

| SVM                                                                                          |    |

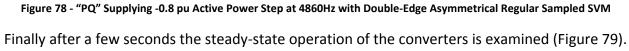

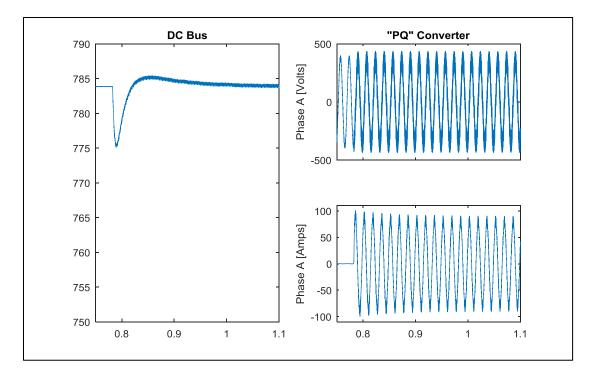

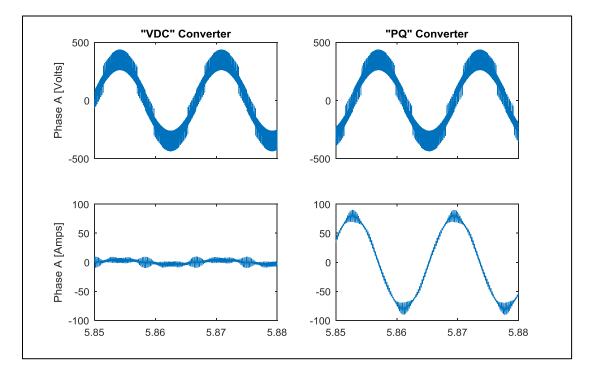

| Figure 78 - "PQ" Supplying -0.8 pu Active Power Step at 4860Hz with Double-Edge Asymmetri    |    |

| Regular Sampled SVM                                                                          |    |

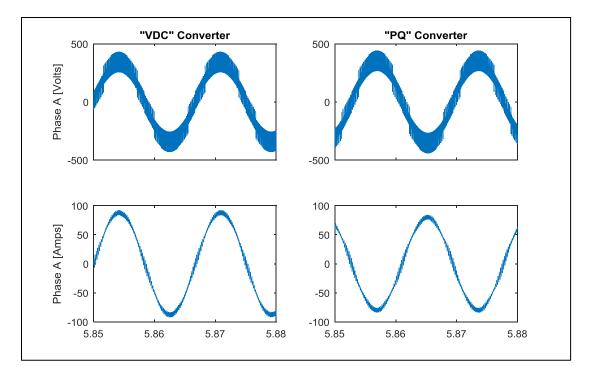

| Figure 79 - "PQ" Supplying -0.8 pu Active Power at 4860Hz with Double-Edge Asymmetrical      |    |

| Regular Sampled SVM                                                                          | 80 |

| Figure 80 - "PQ" Supplying -0.8 pu Reactive Power Step at 4860Hz with Double-Edge            |    |

| Asymmetrical Regular Sampled SVM                                                             | 81 |

| Figure 81 - "PQ" Supplying -0.8 pu Reactive Power at 4860Hz with Double-Edge Asymmetrical    |    |

| Regular Sampled SVM                                                                          | 81 |

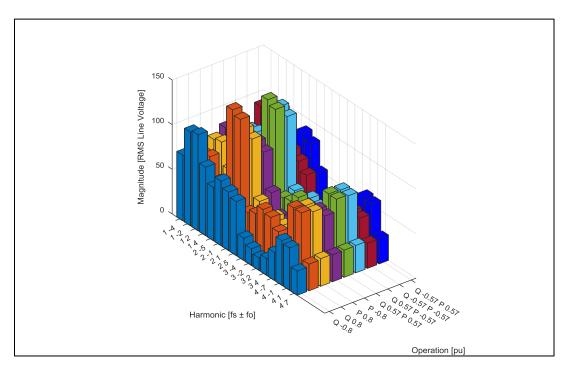

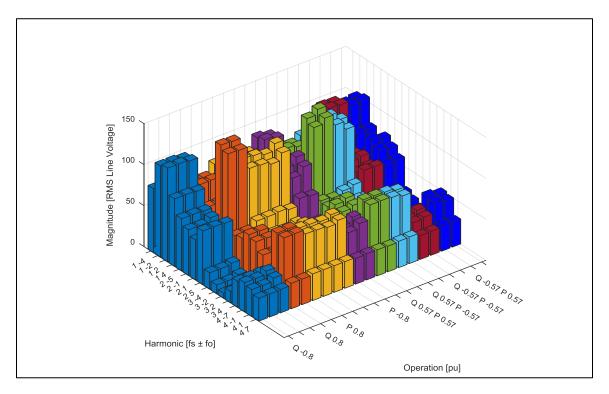

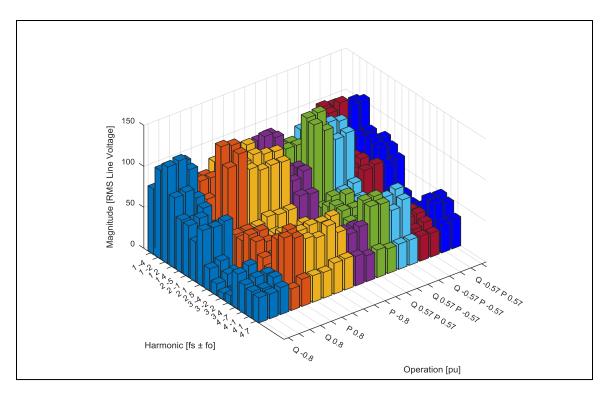

| Figure 82 - Model-in-the-Loop Simulation Spectrum of "PQ" Converter Harmonic Voltages at     |    |

| 4860Hz                                                                                       | 82 |

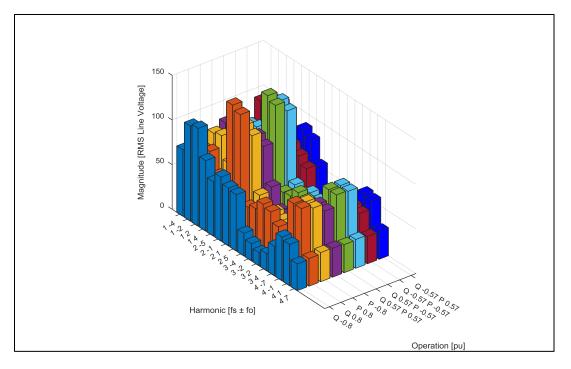

| Figure 83 - Analytical Spectrum of "PQ" Converter Harmonic Voltages at 4860Hz                | 83 |

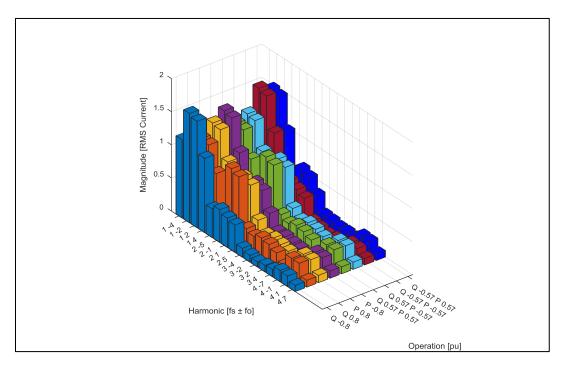

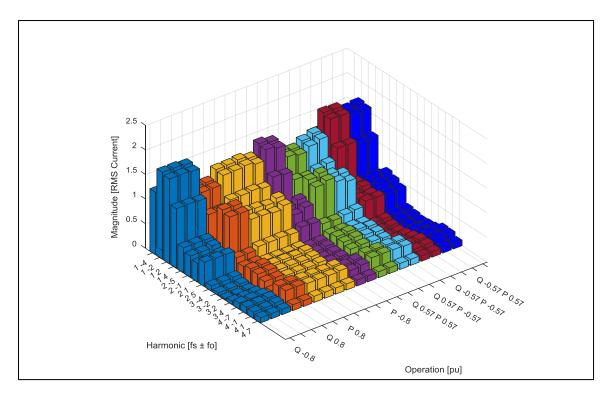

| Figure 84 - Model-in-the-Loop Simulation Spectrum of "PQ" Converter Harmonic Currents at     |    |

| 4860Hz                                                                                       | 83 |

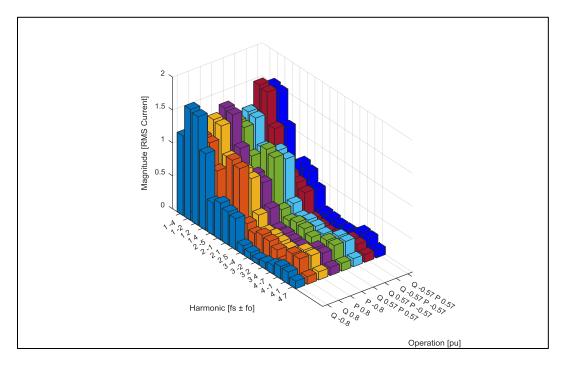

| Figure 85 - Analytical Spectrum of "PQ" Converter Harmonic Currents at 4860Hz                | 84 |

| Figure 86 - TI CCStudio GUI Composer Application                                             | 85 |

| Figure 87 - 1% and 50% Reference to PWM Module A Leg 1                                       | 85 |

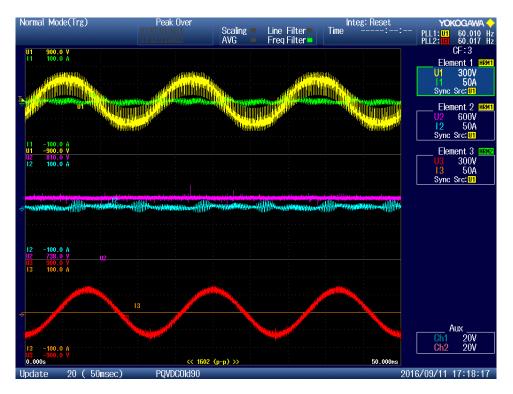

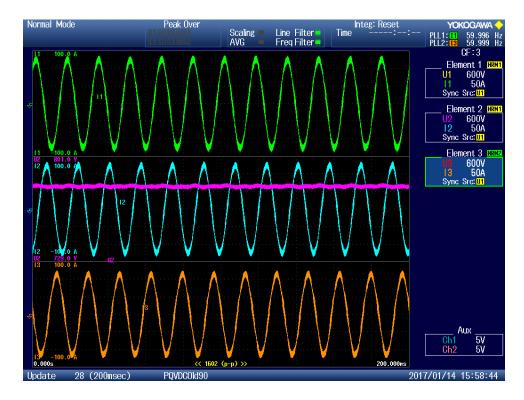

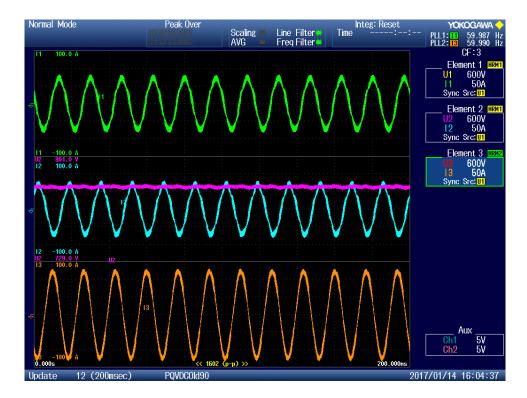

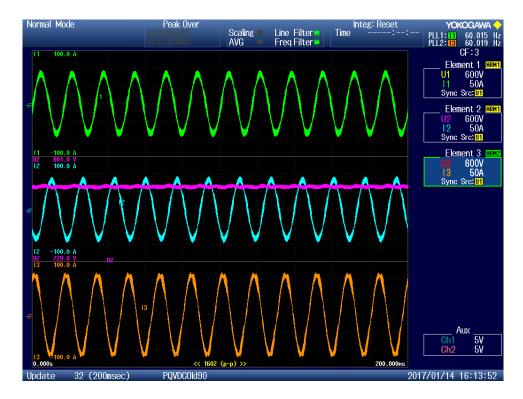

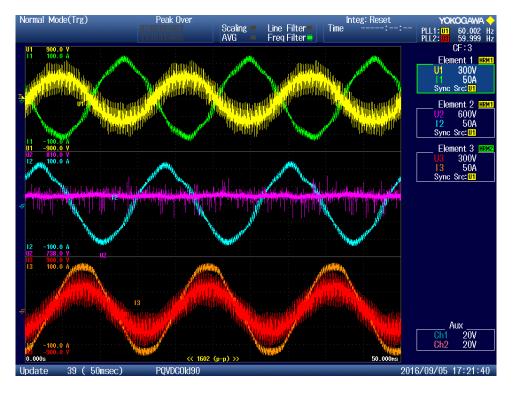

| Figure 88 - "VDC" Converter Operating at No Load at 4500Hz                                   | 86 |

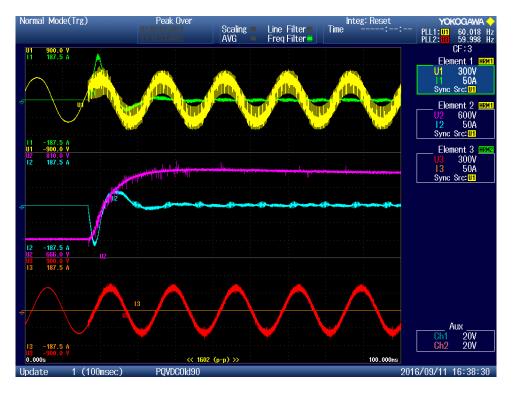

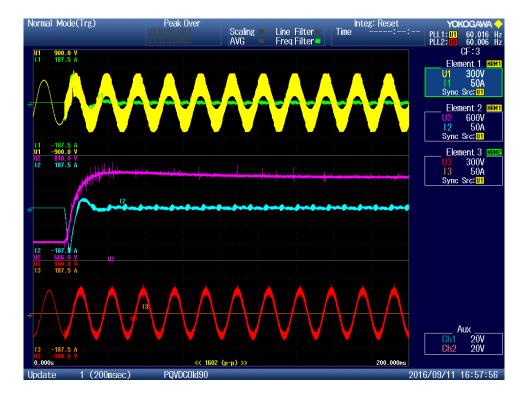

| Figure 89 - "VDC" Converter Step Change at 4500Hz (100ms Window)                             | 87 |

| Figure 90 - "VDC" Converter Step Change at 4500Hz (200ms Window)                             | 87 |

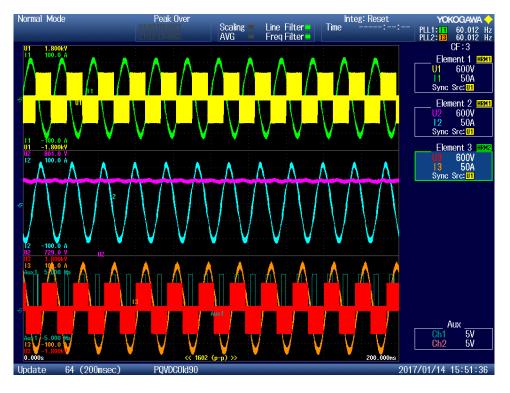

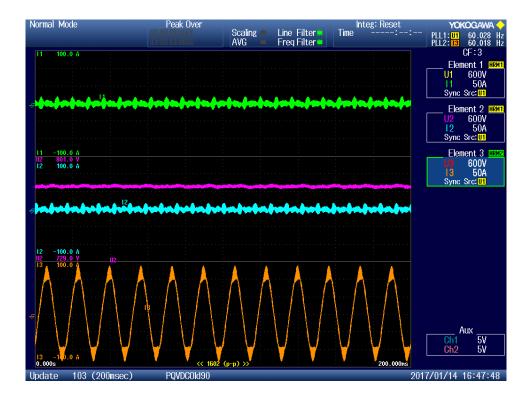

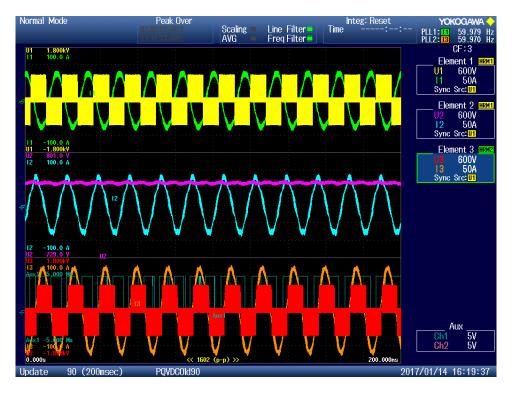

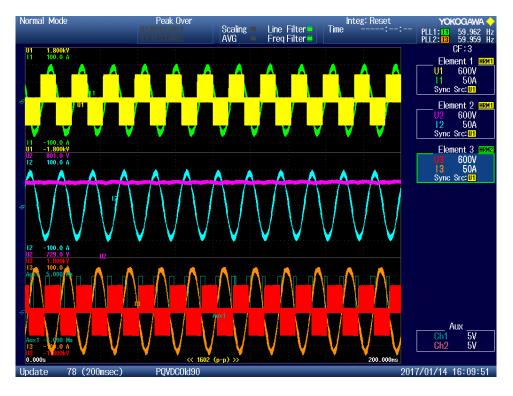

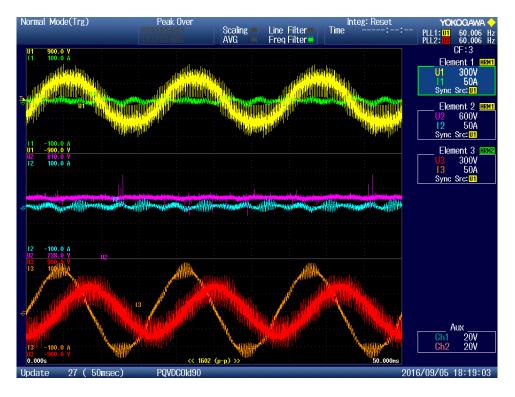

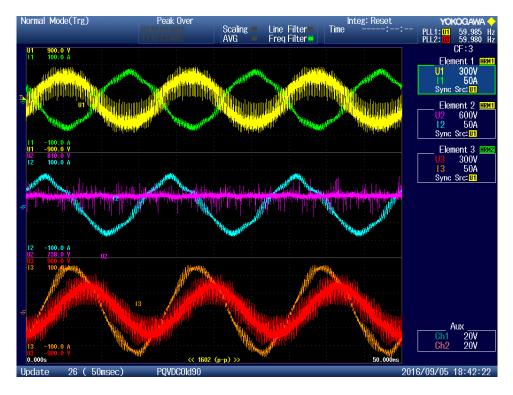

| Figure 91 - "PQ" Supplying -0.8 pu Active Power at Unity Power Factor at 4860Hz              | 89 |

| Figure 92 - "PQ" Supplying -0.8 pu Active Power at Unity Power Factor at 4860Hz without Line | Э  |

| Voltages                                                                                     | 89 |

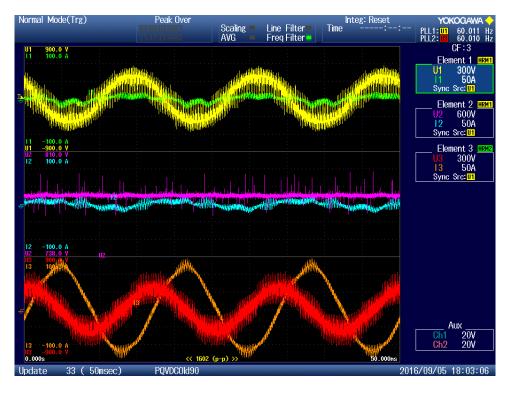

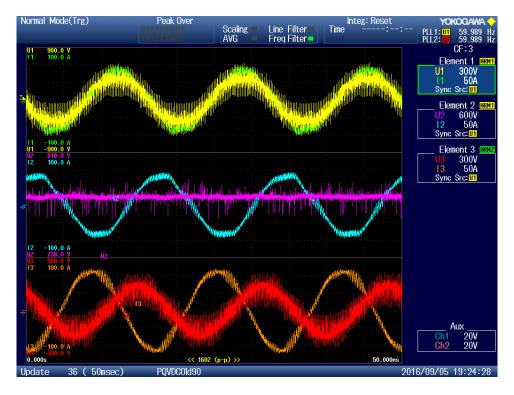

| Figure 93 - "PQ" Consuming 0.8 pu Active Power at Unity Power Factor at 4860Hz               | 90 |

| Figure 94 - "PQ" Consuming 0.8 pu Active Power at Unity Power Factor at 4860Hz without Lin   | e  |

| Voltages                                                                                     | 90 |

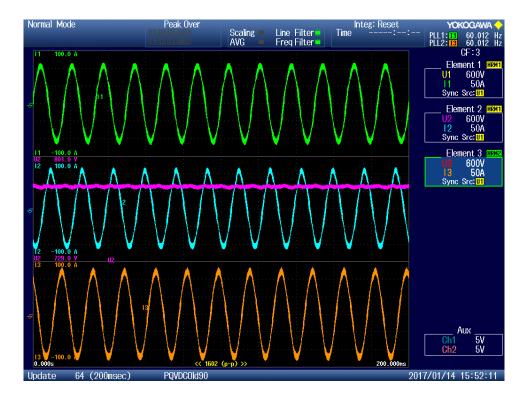

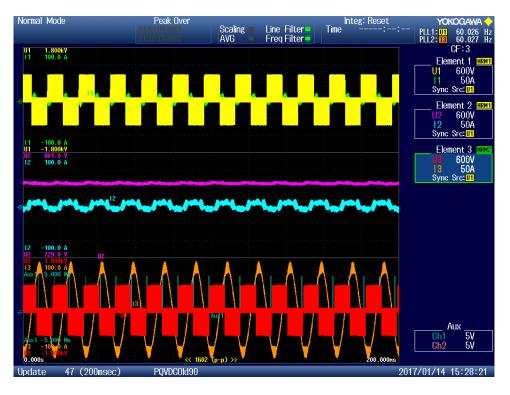

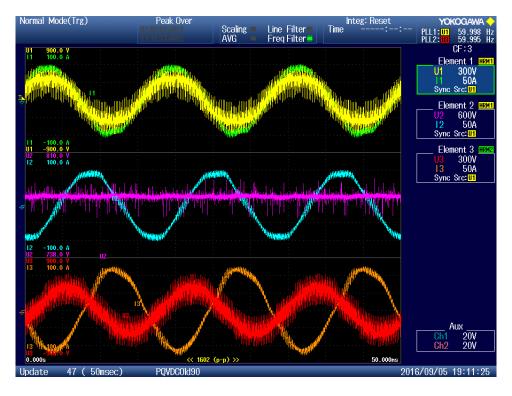

| Figure 95 - "PQ" Supplying -0.8 pu Reactive Power at Capacitor Operation at 4860Hz           |    |

| Figure 96 - "PQ" Supplying -0.8 pu Reactive Power at Capacitor Operation at 4860Hz without   |    |

| Line Voltages                                                                                | 91 |

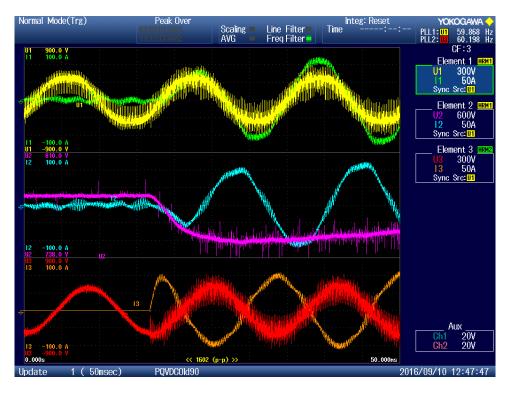

| Figure 97 - "PQ" Consuming 0.8 pu Reactive Power at Inductor Operation at 4860Hz             | 92 |

| Figure 98 - "PQ" Consuming 0.8 pu Reactive Power at Inductor Operation at 4860Hz without                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Line Voltages                                                                                                                                                                     |

| Figure 100 - "PQ" Consuming 0.57 pu Active and 0.57 pu Reactive Power at 4860Hz without Line                                                                                      |

| Voltages                                                                                                                                                                          |

| Figure 101 - "PQ" Consuming 0.57 pu Active and Supplying -0.57 pu Reactive Power at 4860Hz                                                                                        |

|                                                                                                                                                                                   |

| Figure 102 - "PQ" Consuming 0.57 pu Active and Supplying -0.57 pu Reactive Power at 4860Hz                                                                                        |

| without Line Voltages                                                                                                                                                             |

| Figure 103 - "PQ" Supplying -0.57 pu Active and -0.57 pu Reactive Power at 4860Hz                                                                                                 |

| Figure 104 - "PQ" Supplying -0.57 pu Active and -0.57 pu Reactive Power at 4860Hz without Line                                                                                    |

| Voltages                                                                                                                                                                          |

| -ingure 105 - PQ Supplying -0.57 pu Active and Consuming 0.57 pu Reactive Power at 4860Hz                                                                                         |

| Figure 106 - "PQ" Supplying -0.57 pu Active and Consuming 0.57 pu Reactive Power at 4860Hz                                                                                        |

| without Line Voltages                                                                                                                                                             |

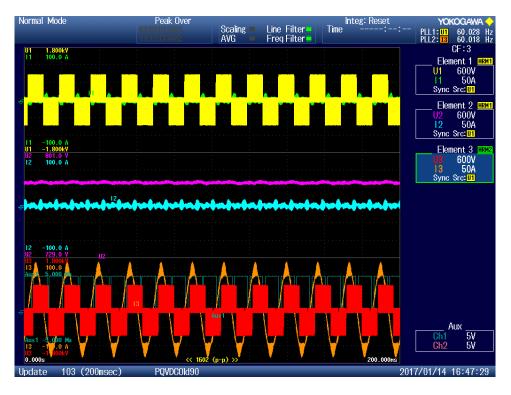

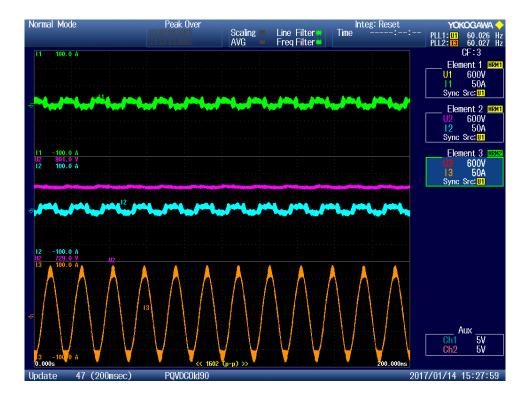

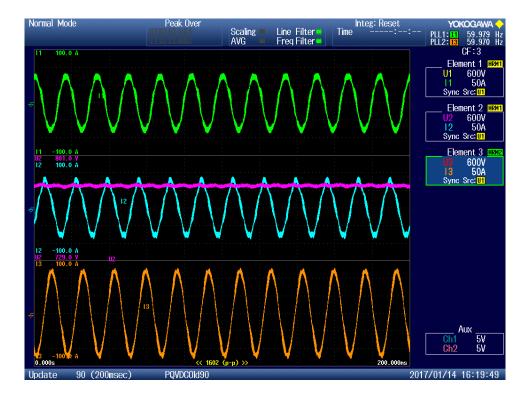

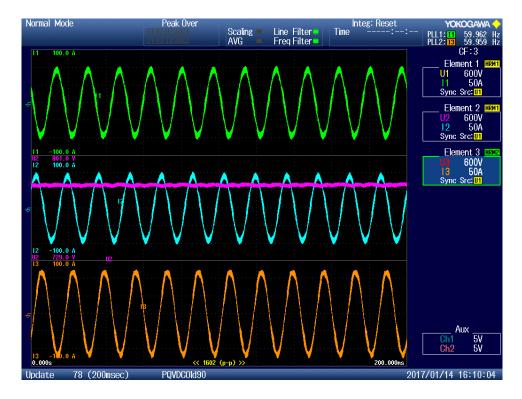

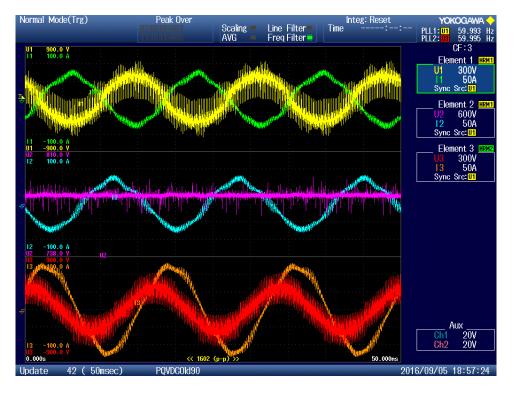

| Figure 107 - "PQ" Supplying -0.8 pu Active Power at Unity Power Factor at 4500Hz                                                                                                  |

| Figure 108 - Measurements of "PQ" Supplying -0.8 pu Active Power at Unity Power Factor at                                                                                         |

| 4500Hz                                                                                                                                                                            |

| Figure 109 - "PQ" Consuming 0.8 pu Active Power at Unity Power Factor at 4500Hz                                                                                                   |

| Figure 110 - Measurements of "PQ" Consuming 0.8 pu Active Power at Unity Power Factor at                                                                                          |

| 4500Hz                                                                                                                                                                            |

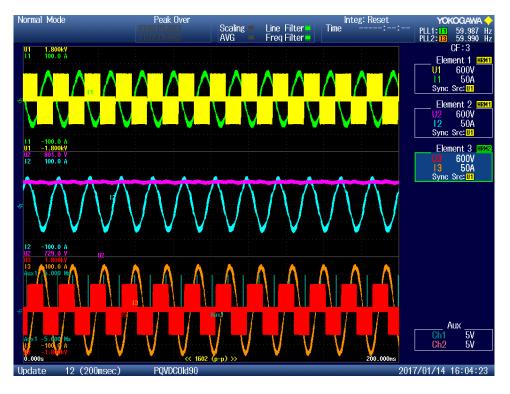

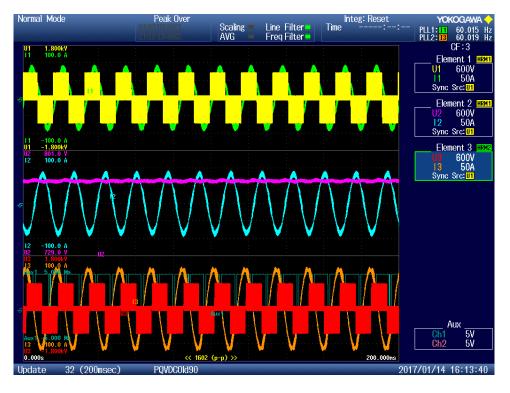

| Figure 111 - "PQ" Supplying -0.8 pu Reactive Power at Capacitor Operation at 4500Hz 100                                                                                           |

| Figure 112 - Measurements of "PQ" Supplying -0.8 pu Reactive Power at Capacitor Operation at                                                                                      |

| 4500Hz                                                                                                                                                                            |

| Figure 113 - PQ Consuming 0.8 pu Reactive Power at Inductor Operation at 4500H2 101<br>Figure 114 - Measurements of "PQ" Consuming 0.8 pu Reactive Power at Inductor Operation at |

| 4500Hz                                                                                                                                                                            |

| Figure 115 - "PQ" Consuming 0.57 pu Active and 0.57 pu Reactive Power at 4500Hz 102                                                                                               |

| Figure 116 - Measurements of "PQ" Consuming 0.57 pu Active and 0.57 pu Reactive Power at                                                                                          |

| 4500Hz                                                                                                                                                                            |

| Figure 117 - "PQ" Consuming 0.57 pu Active and Supplying -0.57 pu Reactive Power at 4500Hz                                                                                        |

|                                                                                                                                                                                   |

| Figure 118 - Measurements of "PQ" Consuming 0.57 pu Active and Supplying -0.57 pu Reactive                                                                                        |

| Power at 4500Hz                                                                                                                                                                   |

| Figure 119 - "PQ" Supplying -0.57 pu Active and -0.57 pu Reactive Power at 4500Hz 104                                                                                             |

| Figure 120 - Measurements of "PQ" Supplying -0.57 pu Active and -0.57 pu Reactive Power at                                                                                        |

| 4500Hz                                                                                                                                                                            |

| Figure 121 - "PQ" Supplying -0.57 pu Active and Consuming 0.57 pu Reactive Power at | 4500Hz   |

|-------------------------------------------------------------------------------------|----------|

|                                                                                     | 105      |

| Figure 122 - Measurements of "PQ" Supplying -0.57 pu Active and Consuming 0.57 pu   | Reactive |

| Power at 4500Hz                                                                     | 105      |

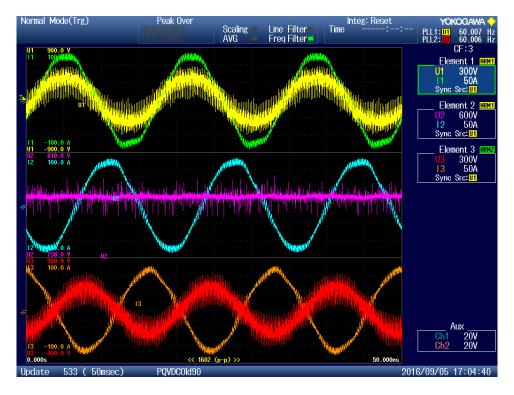

| Figure 123 - "PQ" Supplying -0.8 pu Active Power Step at 4500Hz (50ms Window)       | 106      |

| Figure 124 - "PQ" Supplying -0.8 pu Active Power Step at 4500Hz (200ms Window)      | 106      |

| Figure 125 - Analytical "PQ" Converter Voltage Harmonic Spectrum at 4860Hz          | 107      |

| Figure 126 - Measured "PQ" Converter Voltage Harmonic Spectrum at 4860Hz            | 108      |

| Figure 127 - Analytical "PQ" Converter Current Harmonic Spectrum at 4860Hz          | 108      |

| Figure 128 - Measured "PQ" Converter Current Harmonic Spectrum at 4860Hz            | 109      |

# LIST OF TABLES

# LIST OF ABBREVIATIONS

| ADC    | Analog to Digital Converter              |

|--------|------------------------------------------|

| VOC    | Voltage Oriented Control                 |

| DSP    | Digital Signal Processor                 |

| GP-DSP | General-Purpose Digital Signal Processor |

| GPIO   | General-Purpose Inputs/Outputs           |

| SVM    | Space Vector Modulation                  |

| PWM    | Pulse Width Modulation                   |

| SPWM   | Sinusoidal Pulse Width Modulation        |

| FFT    | Fast Fourier Transform                   |

| DFT    | Discrete Fourier Transform               |

| VAC    | Volts Alternating Current                |

| VSC    | Voltage Source Converter                 |

| DC     | Direct Current                           |

| AC     | Alternating Current                      |

| RMS    | Root Mean Square                         |

| IGBT   | Insulated Gate Bipolar Transistor        |

| IIR    | Infinite Impulse Response                |

| FIR    | Finite Impulse Response                  |

| PI     | Proportional Integral                    |

| PU     | Per-Unit                                 |

| MFB    | Multiple Feedback                        |

|                               | LIST OF SYMBOLS                                    |       |

|-------------------------------|----------------------------------------------------|-------|

| Abbreviation                  | Variable                                           | Unit  |

| C <sub>dc</sub>               | DC Capacitance                                     | farad |

| G <sub>cc,CL</sub>            | Current Controller Closed Loop Transfer Function   |       |

| G <sub>cc,OL</sub>            | Current Controller Open Loop Transfer Function     |       |

| G <sub>vc,CL</sub>            | Voltage Controller Closed Loop Transfer Function   |       |

| G <sub>vc,OL</sub>            | Voltage Controller Open Loop Transfer Function     |       |

| <b>G</b> <sub>converter</sub> | Converter Transfer Function                        |       |

| G <sub>feedback</sub> ,i      | Current Anti-Aliasing Filter Transfer Function     |       |

| G <sub>feedback</sub> ,v      | Voltage Digital Low Pass Filter Transfer Function  |       |

| G <sub>pi</sub>               | Proportional Integral Controller Transfer Function |       |

| G <sub>system,C</sub>         | System Capacitance Transfer Function               |       |

| <b>G</b> <sub>system,L</sub>  | System Inductance Transfer Function                |       |

| i <sub>g</sub>                | Instantaneous Grid Current                         | amp   |

| K <sub>conv</sub>             | Converter Gain                                     |       |

| K <sub>i,c</sub>              | Current Controller Integrator Gain                 |       |

| K <sub>i,v</sub>              | Voltage Controller Integrator Gain                 |       |

| K <sub>p,c</sub>              | Current Controller Proportional Gain               |       |

| K <sub>p,v</sub>              | Voltage Controller Proportional Gain               |       |

| L                             | Grid Inductance                                    | henry |

| m <sub>a</sub>                | Modulation Index                                   |       |

|                               |                                                    |       |

#

| Pg               | Grid Active Power                          | watt    |

|------------------|--------------------------------------------|---------|

| Qg               | Grid Reactive Power                        | VAR     |

| R                | Grid Resistance                            | ohm     |

| T <sub>a</sub>   | Sum of Minor Current Controller Delays     | sec     |

| T <sub>b</sub>   | Sum of Minor Voltage Controller Delays     | sec     |

| T <sub>aaf</sub> | Current Anti-Aliasing Filter Time Constant | sec     |

| T <sub>d</sub>   | Sum of Processing Delay and PWM            | sec     |

| T <sub>i,c</sub> | Current Controller Integral Time Constant  | sec     |

| T <sub>i,v</sub> | Voltage Controller Integral Time Constant  | sec     |

| T <sub>L</sub>   | Reactor Time Constant                      | sec     |

| T <sub>mp</sub>  | Processing Delay of Computational Device   | sec     |

| T <sub>PWM</sub> | Delay of PWM Converter                     | sec     |

| T <sub>s</sub>   | Computational Device Sample Time           | sec     |

| V <sub>c</sub>   | Instantaneous Converter Voltage            | volt    |

| V <sub>dc</sub>  | DC Bus Voltage                             | volt    |

| v <sub>g</sub>   | Instantaneous Grid Voltage                 | volt    |

| $	heta_g$        | Grid Voltage Angle                         | rad     |

| ω <sub>n</sub>   | Undamped Natural Frequency                 | rad/sec |

| ζ                | Damping Ratio                              |         |

## 1. Introduction

The purpose of this project is to connect two power systems of different voltages and frequencies for the exchange of power. An example of such an implementation could be the electric utility and a microgrid. The thesis project implementation resides at UW-Milwaukee's USR Building microgrid test bed facility. With indirect AC/AC conversion between the two power systems there is a DC bus that connects two converters that perform the AC/DC and DC/AC conversions. The benefit of indirect AC/AC conversion is the decoupling between the power systems while the disadvantage is the requirement of energy storage devices needed in the DC bus [1, p. 128]. One of the three-phase, two-level voltage source converters performing the AC/DC conversion maintains the required DC bus voltage level at unity power factor for the power system. The other two-level converter operates in all four guadrants supplying/consuming active and/or reactive power with the other power system. The designation of the converter type for the utility and microgrid is application specific. A possible topology would be the converter that maintains the DC bus voltage to be connected to microgrid's electrical bus of distributed energy sources while the other converter is connected to the utility in order to supply the required active and/or reactive power to support the needs of the grid.

# 2. Background and System Architecture

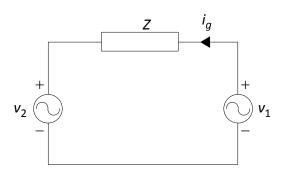

The AC/DC conversion that occurs between the power system and the two-level voltage source converter can be modeled as two AC voltage sources in Figure 1 by omitting the voltage harmonics produced by the converter other than the fundamental frequency of the power system. The amount and direction of active and reactive power can be controlled between two voltage sources by controlling the amplitude and phase angle of the voltage drop across the reactor. The leading voltage source will supply active power while the higher amplitude voltage source will supply reactive power [2, pp. 184-185].

Figure 1 - Single-Phase Representation of Complex Power Flow

The converter operates in rectifier mode of operation when active power is supplied from the power system to the DC bus. By supplying active power from the power system to the DC bus the capacitor is charged and the DC bus voltage increases functioning like a boost converter. The converter operates in inverter mode of operation when power is supplied from the DC bus into the power system. By supplying power from the DC Bus to the power system the capacitor is discharged and the DC bus voltage decreases functioning like a buck converter [3, p. 225].

The "PQ" converter supplies/consumes active and/or reactive power by the use of open loop control by commanding the desired active and reactive power references. The "VDC" converter maintains the DC bus voltage with the use of a feedback control loop referred to as the voltage controller which measures the difference between the desired DC bus voltage and the voltage measured across the capacitors of the DC bus. In addition to the "VDC" converter controlling the direction of active power, unity power factor of the power system is also achieved by controlling the reactive power.

#### 2.1. Space Vector Modulation

The linear region of sinusoidal PWM that can be achieved at the output of the converter for a modulation index when  $m_a \leq 1$  would not allow the converter to deliver reactive power to the grid without going into overmodulation, the nonlinear region of sinusoidal PWM, unless the DC Bus level was raised to a substantially high level. Higher DC bus levels increase the stress on the converter's IGBTs due to the increase in the switching losses, so it is advantageous to keep the DC Bus voltage level as low as practicable [1, p. 348]. Operation in the overmodulation region of sinusoidal PWM is undesirable since it causes an increase in the sideband harmonics generated by PWM [4, p. 208] as well as the introduction of nonlinearity into the current controller [1, p. 336]. Double-edge symmetrical regular sampled space vector modulation was chosen so the converter to the grid making the best utilization of the DC Bus.

SPWM Converter Output Fundamental Line Voltage =

$$\left(\frac{\sqrt{3}}{\sqrt{2}}\right) \left(m_a \frac{V_{dc}}{2}\right) [volts rms]$$

$\approx 0.612 m_a V_{dc} \because m_a \le 1.0$

(1)

SVM Converter Output Fundamental Line Voltage =

$$\left(\frac{\sqrt{3}}{\sqrt{2}}\right) \left(m_a \frac{V_{dc}}{\sqrt{3}}\right)$$

[volts rms]

$\approx 0.707 m_a V_{dc} \because m_a \le 1.0$  (2)

## 2.2. Vector Control

In order for the voltage source converter to consume or supply active and reactive power as needed a control scheme with high dynamic performance must be implemented for control. Vector control methods are based on the system dynamic model rather than scalar control methods which are based on the system steady-state model [3, p. 931].

# 2.2.1. Voltage Oriented Control and the System Dynamic Model

The vector control scheme selected is known as Voltage Oriented Control. VOC was chosen for simplicity in the selection of the input filter due to a fixed switching frequency. The disadvantage of this scheme is that it requires coordinate transformation from the three-phase stationary frame (known as *abc* or natural frame) to the synchronous frame (known as *dq*, direct-quadrature rotating frame), an internal current feedback loop (known as the current controller), as well as the decoupling between the active and reactive components [5, p. 457].

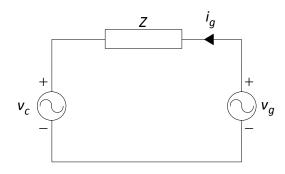

Figure 2 - One Line Diagram Representation of Converter, Impedance, and Grid

$$0 = v_g - v_z - v_c$$

$$v_g - v_c = v_R + v_L$$

(3)

Figure 2 results from the substitution of an ideal voltage source converter in place of a voltage source from Figure 1. Equation (3) is the result of applying Kirchhoff's Voltage Law to Figure 2. Figure 3 is the representation of Figure 2 but represented in terms of resistance and inductance.

Figure 3 - One Line Diagram Representation of Converter, Impedance, and Grid

$$v_g - v_c = Ri_g + L \frac{di_g}{dt} \tag{4}$$

Equation(4) is the differential equation that represents Figure 3.

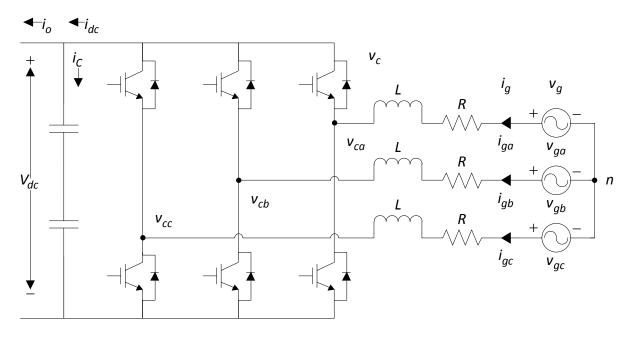

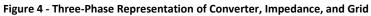

$$\begin{bmatrix} v_{ga} \\ v_{gb} \\ v_{gc} \end{bmatrix} - \begin{bmatrix} v_{ca} \\ v_{cb} \\ v_{cc} \end{bmatrix} = R \begin{bmatrix} i_{ga} \\ i_{gb} \\ i_{gc} \end{bmatrix} + L \frac{d}{dt} \begin{bmatrix} i_{ga} \\ i_{gb} \\ i_{gc} \end{bmatrix}$$

(5)

Equation(5) is the *abc* three-phase stationary frame representation of equation(4).

$$M_{1}\begin{bmatrix} v_{ga} \\ v_{gb} \\ v_{gc} \end{bmatrix} - M_{1}\begin{bmatrix} v_{ca} \\ v_{cb} \\ v_{cc} \end{bmatrix} = RM_{1}\begin{bmatrix} i_{ga} \\ i_{gb} \\ i_{gc} \end{bmatrix} + L\frac{d}{dt}(M_{1}\begin{bmatrix} i_{ga} \\ i_{gb} \\ i_{gc} \end{bmatrix})$$

(6)

$$\begin{bmatrix} \mathbf{v}_{g\alpha} \\ \mathbf{v}_{g\beta} \end{bmatrix} - \begin{bmatrix} \mathbf{v}_{c\alpha} \\ \mathbf{v}_{c\beta} \end{bmatrix} = R \begin{bmatrix} i_{g\alpha} \\ i_{g\beta} \end{bmatrix} + L \frac{d}{dt} \begin{bmatrix} i_{g\alpha} \\ i_{g\beta} \end{bmatrix}$$

(7)

Equations (6) and (7) are the result of the coordinate transformation from the *abc* three-phase stationary reference frame to the  $\alpha\beta$  two-phase stationary reference frame. This is done by multiplying the voltages and currents by the matrix  $M_1$  found in Appendix B: Coordinate Transformations.

$$M_{2}\begin{bmatrix} v_{g\alpha} \\ v_{g\beta} \end{bmatrix} - M_{2}\begin{bmatrix} v_{c\alpha} \\ v_{c\beta} \end{bmatrix} = RM_{2}\begin{bmatrix} i_{g\alpha} \\ i_{g\beta} \end{bmatrix} + LM_{2}\frac{d}{dt}\begin{bmatrix} i_{g\alpha} \\ i_{g\beta} \end{bmatrix}$$

(8)

$$\begin{bmatrix} v_{gd} \\ v_{gq} \end{bmatrix} - \begin{bmatrix} v_{cd} \\ v_{cq} \end{bmatrix} = R \begin{bmatrix} i_{gd} \\ i_{gq} \end{bmatrix} + L \frac{d}{dt} \begin{bmatrix} i_{gd} \\ i_{gq} \end{bmatrix} + L \omega \begin{bmatrix} 0 & -1 \\ 1 & 0 \end{bmatrix} \begin{bmatrix} i_{gd} \\ i_{gq} \end{bmatrix}$$

(9)

Equations (8) and (9) are the result of the coordinate transformation from the  $\alpha\beta$  two-phase stationary reference frame to the dq synchronous reference frame. The  $\omega Li_g$  term is a result of the coordinate transformation due to the derivative term [6, p. 147] with the derivation found in Appendix B: Coordinate Transformations.

$$v_{gd} - v_{cd} = Ri_{gd} + L\frac{di_{gd}}{dt} - \omega Li_{gq}$$

<sup>(10)</sup>

$$v_{gq} - v_{cq} = Ri_{gq} + L\frac{di_{gq}}{dt} + \omega Li_{gd}$$

(11)

Equations (10) and (11) are the result of separating the dq synchronous reference frame equation into separate equations.

$$\frac{di_{gd}}{dt} = \left(v_{gd} - v_{cd} - Ri_{gd} + \omega Li_{gq}\right)/L$$

(12)

$$\frac{di_{gq}}{dt} = \left(v_{gq} - v_{cq} - Ri_{gq} - \omega Li_{gd}\right) / L$$

(13)

Rearrangement of equations (10) and (11) into equations (12) and (13) leads to the conclusion that the derivative of either axes current is cross-coupled with both the d-axis and q-axis

currents. To simplify the controller design decoupling between the d-axis and q-axis components must be achieved as unsatisfactory dynamic performance would otherwise result [6, p. 147].

$$\mathbf{v}_{gd} - \mathbf{v}_{cd} = (\mathbf{s}\mathbf{L} + \mathbf{R})\mathbf{i}_{gd} - \omega\mathbf{L}\mathbf{i}_{gq} \tag{14}$$

$$v_{gq} - v_{cq} = (sL + R)i_{gq} + \omega Li_{gd}$$

<sup>(15)</sup>

Equations (14) and (15) represent the Laplace transformation of the synchronous frame equations (10) and (11) to move from the time domain to the frequency domain. Analysis in the time domain would present difficulties since the equations are non-linear.

$$i_{gd} = (v_{gd} - v_{cd} + \omega L i_{gq}) / (sL + R)$$

(16)

$$i_{gq} = (v_{gq} - v_{cq} - \omega L i_{gd}) / (sL + R)$$

(17)

Equations (16) and (17) represents the transfer functions of the system model that will be used in the inner current controllers.

#### **2.3. Current Controllers**

The current control methods for the voltage source converter can be generalized as either an on-off controller where the controller and modulation are combined or a controller with an open-loop PWM block. With an open-loop PWM block there are many different types of linear controllers that can be implemented such as proportional-integral, state feedback, resonant, and predictive as well as the additional benefit of utilizing many different types of open-loop modulators such as sinusoidal PWM, space vector PWM, and optimal PWM since the compensation for the current error feedback and the voltage modulation are separate parts [5, p. 116].

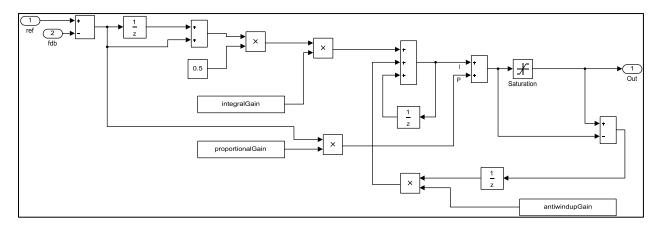

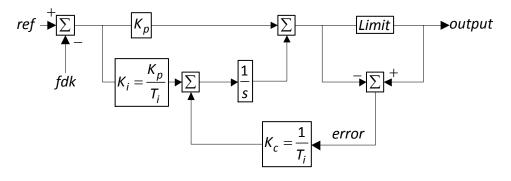

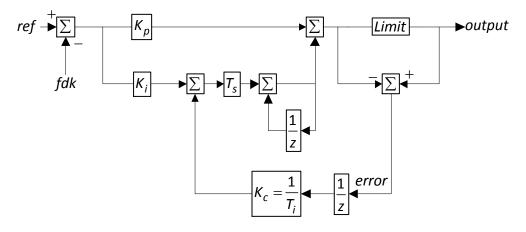

#### 2.3.1. Proportional-Integral Controller Model

For the PI controller, the proportional gain provides the high-frequency response while the integral gain ensures the output corresponds to the set-point in steady-state [7, p. 67], [8, p. 37]. The conversion of the PI controllers from the time domain to the frequency domain are represented in (18) and(19). In order to account for the difference in the desired and actual current a voltage reference is requested for the voltage source converter to generate [5].

$$\begin{aligned}

\mathbf{v}_{cd}^{*} &= K_{p,c} \left( i_{gd}^{*} - i_{gd} \right) + K_{i,c} \int \left( i_{gd}^{*} - i_{gd} \right) dt \\

&= K_{p,c} \left( i_{gd}^{*} - i_{gd} \right) + \frac{K_{i,c} \left( i_{gd}^{*} - i_{gd} \right)}{s} \\

&= \left( i_{gd}^{*} - i_{gd} \right) \left( K_{p,c} \frac{1 + sT_{i,c}}{sT_{i,c}} \right) \because T_{i,c} = \frac{K_{p,c}}{K_{i,c}} \\

\mathbf{v}_{cq}^{*} &= K_{p,c} \left( i_{gq}^{*} - i_{gq} \right) + K_{i,c} \int \left( i_{gq}^{*} - i_{gq} \right) dt \\

&= K_{p,c} \left( i_{gq}^{*} - i_{gq} \right) + \frac{K_{i,c} \left( i_{gq}^{*} - i_{gq} \right)}{s} \\

&= \left( i_{gq}^{*} - i_{gq} \right) \left( K_{p,c} \frac{1 + sT_{i,c}}{sT_{i,c}} \right) \because T_{i,c} = \frac{K_{p,c}}{K_{i,c}}

\end{aligned}$$

(19)

The transfer functions of PI controllers can be represented in the following forms in equation(20) and the derivation between the different forms can be found in Appendix D: Proportional-Integral Controller Forms.

$$G_{pi} = K_p + \frac{K_i}{s} = K_p \frac{1 + sT_i}{sT_i} = K_i \frac{\left(1 + s\frac{K_p}{K_i}\right)}{s} \because T_i = \frac{K_p}{K_i}$$

(20)

#### 2.3.2. Converter Model

The worst case execution time of the voltage source converter's computational device is represented in (21) as the sample period. The statistical delay of the modulator for the voltage source converter is represented in (22) as the average time required for the ability to generate the desired voltage [1, pp. 317,351], [9, pp. 118-119].

$$T_{mp} = T_s \tag{21}$$

$$T_{PWM} = 0.5T_s \tag{22}$$

$$T_d = T_{mp} + T_{PWM} = 1.5T_s \tag{23}$$

The voltage source converter transfer function in (24),(25), and (26) is modeled as a first order low pass filter with a bandwidth determined by the sum of the delays in (23) and gain due to modulation technique chosen [5, p. 147], [8, p. 35].

$$G_{converter} = \frac{K_{conv}}{1 + sT_d} \approx K_{conv} e^{-sT_d}$$

(24)

$$v_{cd} = \frac{K_{conv}}{1 + sT_d} v_{cd}^*$$

(25)

$$v_{cq} = \frac{K_{conv}}{1 + sT_d} v_{cq}^*$$

(26)

The cascaded representation [8, p. 17] of the PI Controller and voltage source converter transfer function is represented in (27) and(28).

$$v_{cd} = \frac{K_{conv}}{1 + sT_d} \underbrace{\left(i_{gd}^* - i_{gd}\right) \left(K_{p,c} \frac{1 + sT_{i,c}}{sT_{i,c}}\right)}_{v_{cd}^*}$$

$$v_{cq} = \frac{K_{conv}}{1 + sT_d} \underbrace{\left(i_{gq}^* - i_{gq}\right) \left(K_{p,c} \frac{1 + sT_{i,c}}{sT_{i,c}}\right)}_{v_{cq}^*}$$

(27)

#### 2.3.3. Feedforward and Disturbance Decoupling

By rearranging (14) and (15) the system transfer function can be represented in (29) and (30). Using rules from the block diagram representation of cascaded transfer functions [8, p. 17] the negative unity gain (inversion) indicated in the leftmost part of (29) and (30) can then be rearranged to reside on the output of the PI Controller transfer function. To achieve a controller design with decoupling the unwanted the d-axis and q-axis current components in the system transfer function should be treated as disturbances with the inverted d-axis or q-axis component added to the output of the PI Controller transfer function. This cancels out the effect of the d-axis or q-axis current disturbance represented in the system transfer function which can be derived using Mason's signal flow rules [8, p. 134]. Since the d-axis and q-axis grid voltage components from the system transfer functions are known, the feed-forward technique can be used to add this information to improve the command response of the current controller [8, p. 145] thereby allowing the voltage source converter excitation to respond only to corrections required to meet the desired d-axis or q-axis current reference.

$$-(v_{cd} - v_{gd} - \omega Li_{gq}) = (sL + R)i_{gd}$$

(29)

$$-(v_{cq} - v_{gq} + \omega Li_{gd}) = (sL + R)i_{gq}$$

(30)

$$v_{cd}^{*} = -\underbrace{\left(i_{gd}^{*} - i_{gd}\right)}_{PI \, Output} \left(K_{p,c} \frac{1 + sT_{i,c}}{sT_{i,c}}\right)}_{PI \, Output} + \underbrace{\omega Li_{gq} + v_{gd}}_{Decoupling \& Feedforward}$$

(31)

$$\mathbf{v}_{cq}^{*} = -\underbrace{\left(i_{gq}^{*} - i_{gq}\right)}_{Pl \, Output} \left(K_{p,c} \frac{1 + sT_{i,c}}{sT_{i,c}}\right)}_{Pl \, Output} \underbrace{-\frac{\omega Li_{gd} + v_{gq}}{Decoupling \&}}_{Feedforward}$$

(32)

# 2.3.4. Anti-Aliasing Filter Feedback Model

For the feedback model in the non-unity closed loop transfer function of the current controller a multiple feedback 2<sup>nd</sup> order, low pass analog filter implemented on the current measurement is modeled as a 1<sup>st</sup> order low-pass filter using the cut-off frequency of the 2<sup>nd</sup> order MFB filter [8, p. 29]. The filter helps in reducing gain near and above the resonant frequency while the cost is the phase lag it introduces and subsequently the reduced phase margin.

$$G_{feedback,i} = \frac{1}{1 + sT_{aaf}}$$

(33)

$$T_{aaf} = 2\pi f_{cut-off} \tag{34}$$

## 2.3.5. Per-Unit Representation

For simplification in the controller tuning methodology and selection of components (35) and (36) show the conversion of the d-axis and q-axis system transfer functions (14) and (15) to per-unit representation using Appendix A: Per Unit Values.

$$V_{b}\left(\mathbf{v}_{gd,pu} - \mathbf{v}_{cd,pu}\right) = \left(sL_{pu}L_{b} + R_{pu}Z_{b}\right)i_{gd,pu}I_{b} - \omega_{pu}\omega_{b}L_{pu}L_{b}i_{gq,pu}I_{b}$$

$$\mathbf{v}_{gd,pu} - \mathbf{v}_{cd,pu} = Z_{b}\left(\frac{sL_{pu}}{\omega_{b}} + R_{pu}\right)i_{gd,pu}\frac{I_{b}}{V_{b}} - \left(\omega_{pu}\omega_{b}\right)\left(\frac{L_{pu}Z_{b}}{\omega_{b}}\right)i_{gq,pu}\frac{I_{b}}{V_{b}}$$

$$\mathbf{v}_{gd,pu} - \mathbf{v}_{cd,pu} = \left(\frac{sL_{pu}}{\omega_{b}} + R_{pu}\right)i_{gd,pu} - L_{pu}i_{gq,pu}$$

(35)

$$V_{b}\left(v_{gq,pu} - v_{cq,pu}\right) = \left(sL_{pu}L_{b} + R_{pu}Z_{b}\right)i_{gq,pu}I_{b} + \omega_{pu}\omega_{b}L_{pu}L_{b}i_{gd,pu}I_{b}$$

$$v_{gq,pu} - v_{cq,pu} = Z_{b}\left(\frac{sL_{pu}}{\omega_{b}} + R_{pu}\right)i_{gq,pu}\frac{I_{b}}{V_{b}} + \left(\omega_{pu}\omega_{b}\right)\left(\frac{L_{pu}Z_{b}}{\omega_{b}}\right)i_{gd,pu}\frac{I_{b}}{V_{b}}$$

$$v_{gq,pu} - v_{cq,pu} = \left(\frac{sL_{pu}}{\omega_{b}} + R_{pu}\right)i_{gq,pu} + L_{pu}i_{gd,pu}$$

$$(36)$$

Equations (37) and (38) represent the conversion of the converter transfer function gain to the per-unit representation dependent upon the applied modulation technique chosen for the voltage source converter.

$$\begin{aligned}

\mathcal{K}_{conv,spwm,pu} &= \frac{\left(\frac{\sqrt{2}}{\sqrt{3}}\right) \left(\left(\frac{\sqrt{3}}{\sqrt{2}}\right) m_a \frac{V_{dc}}{2}\right)}{V_b} \\

&= \frac{\left(\frac{\sqrt{2}}{\sqrt{3}}\right) \left(\left(\frac{\sqrt{3}}{\sqrt{2}}\right) m_a \frac{2V_b V_{dc,pu}}{2}\right)}{V_b} \\

&= 1 \because m_a = 1, V_{dc,pu} = 1

\end{aligned}$$

$$\begin{aligned}

\mathcal{K}_{conv,pu} &= \frac{\left(\frac{\sqrt{2}}{\sqrt{3}}\right) \left(\frac{V_{dc}}{\sqrt{2}}\right)}{V_b} \\

&= \frac{\left(\frac{\sqrt{2}}{\sqrt{3}}\right) \left(m_a \frac{2V_b V_{dc,pu}}{\sqrt{2}}\right)}{V_b} \\

&= \frac{\left(\frac{\sqrt{2}}{\sqrt{3}}\right) \left(m_a \frac{2V_b V_{dc,pu}}{\sqrt{2}}\right)}{V_b} \\

&= \frac{2}{\sqrt{3}} \because m_a = 1, V_{dc,pu} = 1 \\

\approx 1.1547

\end{aligned}$$

(37)

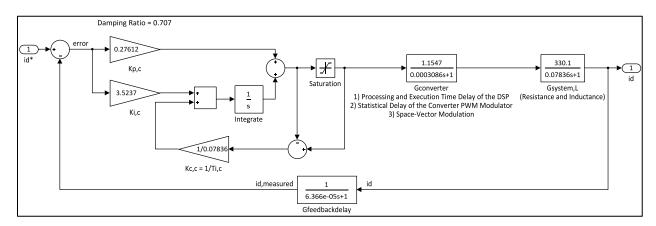

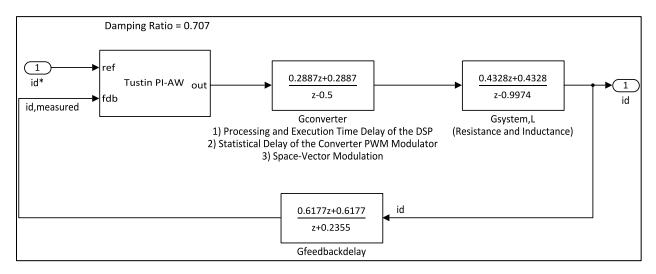

## 2.3.6. Block Diagram Representation of Transfer Functions

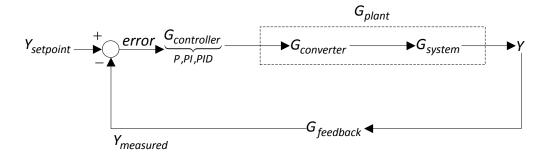

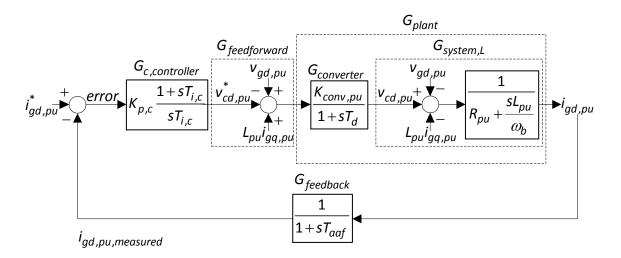

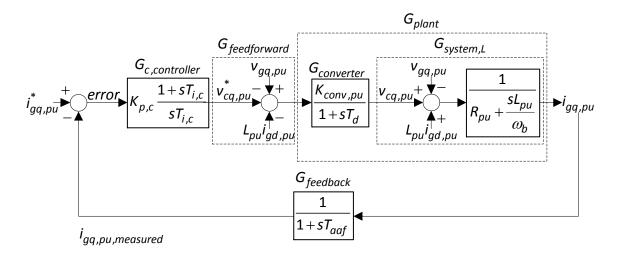

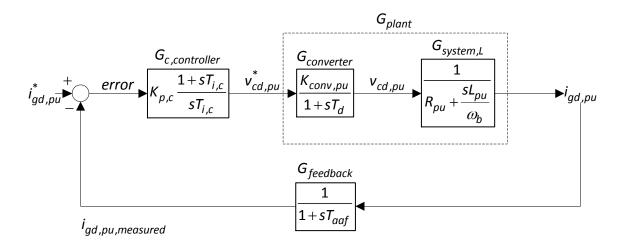

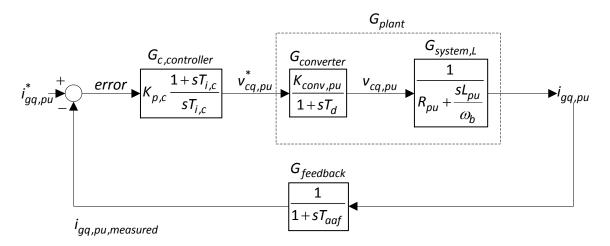

The combination of generic controller, converter, system, and feedback blocks is represented as a closed loop feedback diagram as shown in Figure 5. By substituting the respective d-axis and q-axis transfer functions for the controller, converter, system, and feedback into the blocks of Figure 5 the resultant Figure 6 and Figure 7 then represent the decoupled d-axis and q-axis current controllers for the voltage source converter. For development of the tuning method used on the current controllers Figure 6 and Figure 7 are

then simplified to Figure 8 and Figure 9 to represent the decoupled d-axis and q-axis current controllers in per-unit representation.

Figure 5 - Typical Closed-Loop Feedback System

Figure 6 - Decoupled Current Controller (d-axis)

Figure 7 - Decoupled Current Controller (q-axis)

Figure 8 - Simplified Representation of the Decoupled Current Controller (d-axis)

Figure 9 - Simplified Representation of the Decoupled Current Controller (q-axis)

#### 2.3.7. Modulus Optimum Tuning of Current Controller

Each block in the closed loop current controller contributes phase lag and gain to the overall response. When 180 degrees of phase lag is introduced into the controller, positive feedback will result. With positive feedback and unity gain through the loop the control system is classified as unstable. Finding the optimal values for the PI Controller parameters will mitigate this and other unstable scenarios for the control system. An optimization method is a robust technique for determining PI controller parameters. By utilizing the magnitude optimum tuning technique a frequency response of the current controller's reference to actual output will be as close to unity as possible for low frequencies [7, p. 166].

By evaluating the product of the forward path and feedback transfer functions of Figure 8 or Figure 9 results in the current controller open loop transfer function as in (39) [10, p. 6.6].

$$G_{cc,OL} = G_{pi,c}G_{converter}G_{system,L}G_{feedback,i}$$

$$= \left(K_{p,c}\frac{1+sT_{i,c}}{sT_{i,c}}\right) \left(\frac{K_{conv,pu}}{1+sT_d}\right) \left(\frac{\frac{1}{R_{pu}}}{1+sT_L}\right) \left(\frac{1}{1+sT_{aaf}}\right)$$

$$\approx \left(K_{p,c}\frac{1+sT_{i,c}}{sT_{i,c}}\right) \left(\frac{K_{conv,pu}}{1+s(T_d+T_{aaf})}\right) \left(\frac{\frac{1}{R_{pu}}}{1+sT_L}\right)$$

(39)

The system inductance is dominant pole. The poles introduced by the converter and feedback transfer functions are considered minor and are therefore approximated in the open loop transfer function with(40).

$$T_a = T_d + T_{aaf} :: T_L \gg T_d \& T_{aaf}$$

<sup>(40)</sup>

The magnitude optimum utilizes the dominant pole cancellation technique to mitigate the effect of the pole introduced by the system inductance with the zero of the PI controller with(41).

$$T_{i,c} = T_L ::$$

dominant pole cancellation (41)

Following the design procedure for magnitude optimum by evaluating the structure of (39) the proportional gain is specified in(42) [7, p. 171].

$$K_{p,c magnitude optimum} = \frac{R_{pu}T_L}{2T_a K_{conv.pu}}$$

(42)

Substituting (41) and (42) into (39) results in the simplified open loop current controller of (43).

$$G_{cc,OL} = \frac{\frac{1}{2T_a}}{s(1+sT_a)}$$

(43)

The closed loop current controller found in (44) when algebraically reduced can be recognized as the standard form of a second order transfer function depicted in (45) when ignoring the zero introduced by the feedback transfer function.

$$G_{cc,CL} = \frac{G_{pi,c}G_{converter}G_{system,L}}{1 + G_{pi,c}G_{converter}G_{system,L}G_{feedback,i}}$$

$$= \left(\frac{K_{p,c}K_{conv,pu}}{T_aT_LR_{pu}}\right) \frac{1 + sT_{aaf}}{s\left(\frac{1 + sT_a}{T_a}\right) + \left(\frac{K_{p,c}K_{conv,pu}}{T_aT_LR_{pu}}\right)}$$

$$= \left(\frac{K_{p,c}K_{conv,pu}}{T_aT_LR_{pu}}\right) \frac{1 + sT_{aaf}}{s^2 + \left(\frac{1}{T_a}\right)s + \left(\frac{K_{p,c}K_{conv,pu}}{sT_aT_LR_{pu}}\right)}$$

$$= \frac{1 + sT_{aaf}}{\omega_n^2}$$

(44)

Standard Form 2nd Order Transfer Function =

$$\frac{\omega_n^2}{s^2 + 2\zeta\omega_n + \omega_n^2}$$

(45)

The response of the standard form of a second order transfer function can be classified as overdamped, critically damped, and underdamped with  $\omega_n$  referred to as the undamped natural frequency and  $\zeta$  referred to as the damping ratio in (45) [10, p. 7.8]. A fast dynamic response for the current controller is desirable so (44) will reflect an underdamped second order transfer function. By using (46) a desirable phase margin and percent overshoot can be found for an underdamped second order transfer function.

$$0 \le \zeta < 1, the resulting oscillatory system response is underdamped

$$k = \sqrt{(1 - \zeta^2)}$$

Phase Margin = tan<sup>-1</sup> (  $\zeta / k$ )

Percent Overshoot =  $e^{-\zeta \pi / \sqrt{1 - \zeta^2}}$

(46)$$

By choosing the damping ratio defined in(47), as the modulus optimum method does, the underdamped response will provide the optimal rise and settling time for a low amount of

overshoot for the response of a second order transfer function. A larger damping ratio would negatively impact our settling and rise time, but reduce the overshoot. A smaller damping ratio would negatively impact the overshoot and settling time, but positively impact our rise time [10, p. 7.9].

$$\zeta = 0.707 \tag{47}$$

By rearranging the characteristic polynomial equation of (44) the relationships in (48) and (49) are found.

$$\omega_n = \frac{1}{2\zeta T_a} \tag{48}$$

$$\omega_n^2 = \frac{K_{p,c} K_{conv,pu}}{s T_a T_L R_{pu}}$$

(49)

By substituting (48) into (49) the relationship for the proportional gain is defined in (50) for a particular damping ratio and control system parameters.

$$K_{p,c} = \frac{R_{pu}T_L}{4\zeta^2 T_a K_{conv,pu}}$$

(50)

By substituting (50) into (44) the closed loop current controller can be further simplified to (51).

$$G_{cc,CL} = \frac{1 + sT_{aaf}}{4\zeta^2 T_a^2 s^2 + 4\zeta^2 T_a s + 1}$$

(51)

#### 2.4. Voltage Controller

The voltage source converter that maintains the DC Bus level is designed with multiple loop control [11, p. 16.24]. The voltage controller is the outer loop with the tuned current controller residing within. From the perspective of the voltage controller the inner current loop acts as a low pass filter [8, p. 52].

#### 2.4.1. Proportional-Integral Controller Model

The conversion of the PI controller from the time domain to the frequency domain is represented in(52). In order to account for the difference in the desired and actual dc bus voltage level a d-axis current reference is requested for the voltage source converter to generate [5].

$$i_{gd}^{*} = K_{p,v} \left( V_{dc}^{*} - V_{dc} \right) + K_{i,v} \int \left( V_{dc}^{*} - V_{dc} \right) dt$$

$$= K_{p,v} \left( V_{dc}^{*} - V_{dc} \right) + \frac{K_{i,v} \left( V_{dc}^{*} - V_{dc} \right)}{s}$$

$$= \left( V_{dc}^{*} - V_{dc} \right) \left( K_{p,v} \frac{1 + sT_{i,v}}{sT_{i,v}} \right)$$

(52)

#### **2.4.2.** Approximation of Current Controller Model

The zero due to the feedback in the closed loop current controller of (51) can be ignored since it wouldn't negatively affect the system until well beyond the bandwidth of the current controller [12, p. 600]. Using the damping ratio in (47) the second order transfer function of the closed loop current controller is approximated in (54) as a first order low pass filter [7, p. 55], [5, p. 131]. If the total impact of the anti-aliasing filter in the current controller is ignored then the relationship between the computational device sample time and bandwidth of the current controller is defined in(55) [1, pp. 215, 351].

$$G_{cc,CL} = \frac{1}{4\zeta^2 T_a^2 s^2 + 4\zeta^2 T_a s + 1} \approx \frac{1}{1 + s4\zeta^2 T_a}$$

(53)

$$G_{cc,1stOrdAppx} = \frac{1}{1 + s2T_a} \because \zeta = 0.707$$

(54)

$$T_{cc} = 2T_a \approx 3T_s$$

: anti-aliasing filter is ignored (55)

#### 2.4.3. Power Balance Model

To establish the power balance between the ac and dc side of the voltage source converter the relationship of dc voltage to d-axis current is required. Applying Kirchhoff's current law to Figure 4 the relationship between the phase currents, load current, and dc-link capacitor current is defined in (56) using the switch states of (57) [11, p. 11.7].

$$i_{C} + i_{o} = i_{dc} = S_{a}i_{ga} + S_{b}i_{gb} + S_{c}i_{gc} :: (S_{a} = 1, S_{b} = 0, S_{c} = 0) \text{ is } 1 \text{ of } 8 \text{ possible states}$$

(56)

$$S_x = 1$$

the upper IGBT of one leg in the converter is switched ON ( $x = a,b,c$ )

$S_x = 0$  the lower IGBT of one leg in the converter is switched ON ( $x = a,b,c$ ) (57)

The instantaneous power balance for the voltage source converter in the synchronous rotating *dq* frame neglecting any losses is expressed in(58) since the ac-side active power is equal to the dc-side power [1, p. 213].

$$v_{dc} \underbrace{C_{dc} \frac{dv_{dc}}{dt}}_{i_c} + v_{dc} i_o = v_{dc} i_{dc} = \frac{3}{2} \left\{ v_{gd} i_{gd} + v_{gq} i_{gq} \right\} \because P_{dc} = P_{ac}$$

(58)

Applying the small signal linearization to (58) leads to(59). The goal is to find the transfer function between the d-axis current and dc voltage so all perturbations including second-order signal perturbations are ignored resulting in (60) [1, p. 214].

$$(V_{dc} + \hat{v}_{dc})C_{dc} \frac{d(V_{dc} + \hat{v}_{dc})}{dt} + (V_{dc} + \hat{v}_{dc})(I_o + \hat{i}_o) = \frac{3}{2} \left\{ (V_{gd} + \hat{v}_{gd})(I_{gd} + \hat{i}_{gd}) + (V_{gq} + \hat{v}_{gq})(I_{gq} + \hat{i}_{gq}) \right\}$$

(59)

$$V_{dc}C_{dc}\frac{d\hat{v}_{dc}}{dt} + \hat{v}_{dc}I_{o} + V_{dc}I_{o} = \frac{3}{2} \left\{ V_{gd}I_{gd} + V_{gd}\hat{i}_{gd} + V_{gq}I_{gq} \right\}$$

(60)

Simplification of (60) considering (61) leads to(62).

$$V_{dc}I_{o} = \frac{3}{2} \left\{ V_{gd}I_{gd} + V_{gq}I_{gq} \right\}$$

(61)

$$V_{dc}C_{dc}\frac{d\hat{v}_{dc}}{dt} + \hat{v}_{dc}I_o = \frac{3}{2}\left\{V_{gd}\hat{i}_{gd}\right\}$$

(62)

Applying algebraic manipulation to (62) leads to the relationship of dc voltage to d-axis current in(63).

$$V_{dc}C_{dc}\frac{d\hat{v}_{dc}}{dt} + \hat{v}_{dc}I_{o} = \frac{3}{2}\left\{V_{gd}\hat{i}_{gd}\right\}$$

$$V_{dc}\left(C_{dc}\frac{d\hat{v}_{dc}}{dt} + \hat{v}_{dc}I_{o}\frac{1}{V_{dc}}\right) = \frac{3}{2}\left\{V_{gd}\hat{i}_{gd}\right\}$$

$$\sqrt{3}V_{gd}\left(C_{dc}\frac{d\hat{v}_{dc}}{dt} + \hat{v}_{dc}I_{o}\frac{1}{R_{o}I_{o}}\right) = \frac{3}{2}\left\{V_{gd}\hat{i}_{gd}\right\} \because V_{dc} \ge \sqrt{3}V_{gd}$$

$$\hat{v}_{dc}\left(sC_{dc} + \frac{1}{R_{o}}\right) = \frac{\sqrt{3}}{2}\hat{i}_{gd}$$

$$\frac{\hat{v}_{dc}}{\hat{i}_{gd}} = \frac{\sqrt{3}}{2}\frac{1}{sC_{dc}} + \frac{1}{R_{o}}$$

(63)

From a controller tuning perspective, the worst case stability standpoint of (63) simplifies to(64) during no load operation since the pole would reside on the imaginary axis [13, p. 711], [14, p. 103].

$$\frac{\hat{v}_{dc}}{\hat{i}_{gd}} = \frac{\sqrt{3}}{2} \frac{1}{sC_{dc}} \because R_o \to \infty \because I_o \to 0$$

(64)

## 2.4.4. Digital Filter Feedback Model

To ensure that the inner current loop is at least 5 times faster than the outer voltage loop a digital low pass filter in (65) is used on the voltage feedback to slow the system response down [14, p. 375], [8, p. 52] but without the introduction of unnecessary filtering that would lead to sluggish control [8, p. 16]. By setting the frequency in (66) to half of the computational device's update rate and examining the scenario of a step function applied to (65) leads to a delay of 6 sample periods to reach 95% of the input [1, p. 218].

$$G_{feedback,v} = \frac{1}{1 + sT_{lp}}$$

(65)

$$F_{lp} = 0.5F_s \tag{66}$$

## 2.4.5. Per-Unit Representation

For simplification in the controller tuning methodology (67) shows the conversion of the power balance transfer function (64) to per-unit representation using Appendix A: Per Unit Values.

$$V_{dc,pu} 2V_b sC_{dc} \hat{v}_{dc,pu} 2V_b + \hat{v}_{dc} V_{dc} = \frac{3}{2} \{ V_{gd} V_b \hat{i}_{gd} I_b \} \because V_{dc,b} = 2V_b$$

$$\underbrace{V_{dc,pu} 4V_b^2 sC_{dc} \hat{v}_{dc,pu}}_{=1} = \frac{3}{2} \underbrace{V_{gd,pu} V_b \hat{i}_{gd,pu} I_b}_{=1 \because VOC}$$

$$sC_{dc} \hat{v}_{dc,pu} = \frac{3}{8} \frac{1}{k_b} \hat{i}_{gd,pu}$$

$$\frac{\hat{v}_{dc,pu}}{\hat{i}_{gd,pu}} = \frac{3}{8} \frac{1}{sC_{dc} Z_b}$$

$$\frac{\hat{v}_{dc,pu}}{\hat{i}_{gd,pu}} = \frac{3}{8} \frac{1}{sC_{dc,pu} C_{b,dc} Z_b} \because C_{dc} = C_{dc,pu} C_{b,dc}$$

$$\frac{\hat{v}_{dc,pu}}{\hat{i}_{gd,pu}} = \frac{3}{8} \frac{1}{sC_{dc,pu} C_b Z_b} \because C_{b,dc} = \frac{3}{8} C_b$$

$$\frac{\hat{v}_{dc,pu}}{\hat{i}_{gd,pu}} = \frac{1}{sC_{dc,pu}} \frac{1}{Z_b \omega_b} \because C_b = \frac{1}{Z_b \omega_b}$$

$$G_{system,C} = \frac{\hat{v}_{dc,pu}}{\hat{i}_{gd,pu}} = \frac{1}{s\frac{C_{dc,pu}}{\omega_b}} \qquad (67)$$

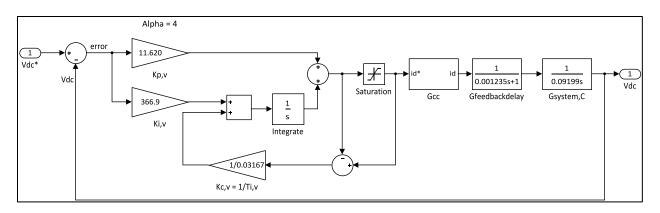

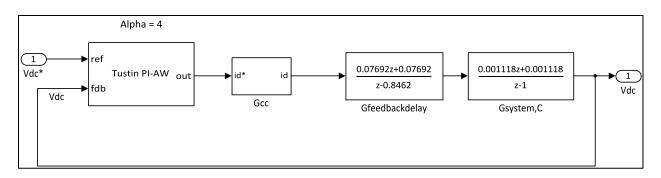

# 2.4.6. Block Diagram Representation of Transfer Functions

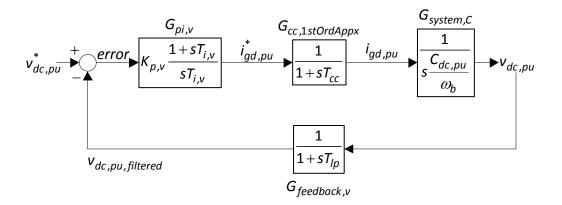

The non-unity closed loop feedback diagram for the per-unit representation of the voltage controller is shown in Figure 10. The 6 sample period delays introduced into the design of the voltage controller as a result of a step response with respect to the voltage feedback transfer function results in the desired slowdown of the system and Figure 10 can be further simplified to Figure 11 [15, pp. 758-759], [11, p. 16.26].

Figure 10 - Per Unit Voltage Controller

Figure 11 - Simplified Per Unit Voltage Controller

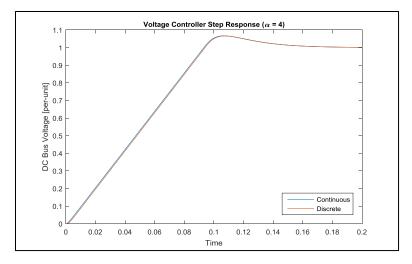

## 2.4.7. Symmetrical Optimum Tuning of Voltage Controller

By utilizing the symmetrical optimum tuning technique a cross-over frequency with the maximum amount of phase margin is obtained from the geometric mean between the approximated current controller with delay and PI controller frequencies that result in an optimum amount of damping for the voltage controller [16, pp. 85-87].

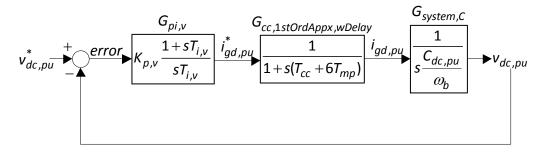

Evaluating the product of the forward path and feedback transfer functions of Figure 11 results in the voltage controller open loop transfer function as in(68) with the time constants simplified in (69) and (70).

$$G_{vc,OL} = G_{pi,v}G_{cc,1stOrdAppx,wDelay}G_{system,C}$$

$$= \left( K_{p,v} \frac{1 + sT_{i,v}}{sT_{i,v}} \right) \left( \frac{1}{1 + s(T_{cc} + 6T_{mp})} \right) \left( \frac{1}{s\frac{C_{dc,pu}}{\omega_b}} \right)$$

$$= \left( K_{p,v} \frac{1 + sT_{i,v}}{sT_{i,v}} \right) \left( \frac{1}{1 + sT_b} \right) \left( \frac{1}{sT_{cap}} \right)$$

$$T_b = T_{cc} + 6T_{mp}$$

(69)

$$T_{cap} = \frac{C_{dc,pu}}{\omega_b}$$

(70)

By first determining the integral component of the PI controller in (71) the cross-over frequency can then be determined in(72).

$$T_{i,v} = a^2 T_b$$

,  $a > 1$  (71)

$$\omega_d = \frac{1}{\sqrt{T_b T_{i,v}}} = \frac{1}{a T_b}$$

(72)

By evaluating the cross-over condition of the open loop transfer function of the voltage controller in (73) the gain component of the PI controller can be determined in(74).

$$\left|G_{vc,OL}(j\omega_d)\right| = 1 \tag{73}$$

$$K_{p,v} = \frac{T_{cap}}{\sqrt{T_b T_{i,v}}} = \frac{T_{cap}}{a T_b}$$

(74)

The open loop voltage controller in (68) can be further simplified to (75) by substitution of PI controller parameters defined in (71) and (74).

$$G_{vc,OL} = \left(\frac{1}{s^2 a^3 T_b^2}\right) \left(\frac{1 + sa^2 T_b}{1 + sT_b}\right)$$

(75)

The unity feedback closed loop voltage controller simplifies to(76).

$$G_{vc,CL} = \frac{G_{pi,v}G_{cc,1stOrdAppx,wDelay}G_{system,C}}{1 + G_{pi,v}G_{cc,1stOrdAppx,wDelay}G_{system,C}}$$

$$= \frac{\left(1 + sa^{2}T_{b}\right)}{s^{3}a^{3}T_{b}^{3} + s^{2}a^{3}T_{b}^{2} + sa^{2}T_{b} + 1}$$

(76)

By evaluating the denominator of the closed loop voltage controller a pole exists at (77) [17, p. 29] and with that knowledge by applying long polynomial division leads to the simplification of the closed loop voltage controller in(78).

$$S_{1} = -\frac{1}{aT_{b}}$$

$$G_{vc,CL} = \frac{\left(1 + sa^{2}T_{b}\right)}{\left(1 + saT_{b}\right)\left(s^{2}a^{2}T_{b}^{2} + sa^{2}T_{b} - saT_{b} + 1\right)}$$

$$= \frac{\left(1 + sa^{2}T_{b}\right)}{\left(1 + saT_{b}\right)\left(s^{2}a^{2}T_{b}^{2} + saT_{b}(a-1) + 1\right)}$$

$$\left(78\right)$$

$$\left(1 + saT_{b}\right)\left(s^{2}a^{2}T_{b}^{2} + saT_{b}(a-1) + 1\right)$$

$$\left(\frac{1}{\omega_{a}^{2}} - \frac{1}{\omega_{a}^{2}} - \frac{2\zeta}{\omega_{a}}\right)$$

The poles of the standard form of a second order transfer function (45) are represented in(79).

Poles of Standard Form 2nd Order TF =

$$-\zeta \omega_n \pm \sqrt{\zeta^2 \omega_n^2 - \omega_n^2}$$

(79)

The poles of the third order closed loop voltage controller (76) simplified to first and second order systems in (78) lead to the calculation of the poles in (80).

$$s_{1} = -\frac{1}{aT_{b}}$$

$$s_{2,3} = -\frac{a-1}{2}\frac{1}{aT_{b}} \pm \sqrt{\frac{(a-1)^{2}}{4}\frac{1}{a^{2}T_{b}^{2}} - \frac{1}{a^{2}T_{b}^{2}}}$$

$$= \frac{1}{aT_{b}} \begin{bmatrix} -\frac{a-1}{2} \pm \sqrt{\frac{(a-1)^{2}}{4} - 1} \end{bmatrix}$$

(80)

Evaluating (80) provides insight for practical values of a following the criteria defined in (71) for the symmetrical optimum tuning. With a > 1 and a < 3 one real and two complex poles exist with the selection of a impacting the damping ratio (81) which in turn determines the oscillatory part of the response.

$$\zeta = \frac{a-1}{2} \tag{81}$$

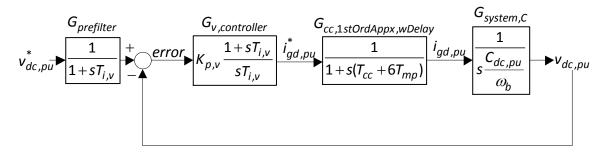

When  $a \ge 3$  the oscillatory response is removed since three real poles exist and the system can be further dampened by increasing a. Further evaluation of the open loop voltage controller of (75) identifies a double integrating term causing the step response of the closed loop voltage controller to exhibit significant overshoot. To eliminate this overshoot caused by the lead term of the PI Controller a corresponding low pass filter is inserted before the input to the closed loop voltage controller in Figure 12 [16, p. 87], [11, p. 16.26].

$$G_{prefilter} = \frac{1}{1 + sT_{i,v}}$$

(82)

Figure 12 - Simplified Per Unit Voltage Controller with Prefilter

#### 2.5. Active and Reactive Controller Models

The transfer of power between the grid and the voltage source converter in Figure 4 is represented with the *dq* synchronous reference frame active and reactive power equations of (83) and(84). In order for the voltage source converter to achieve the vector control method known as voltage oriented control the d-axis of the synchronous frame must be aligned to the grid voltage vector. With the d-axis of the synchronous frame aligned to the grid voltage vector the magnitudes will be equal to one another resulting in the q-axis of the synchronous frame equal to zero [6, p. 145]. Evaluation of (83) and (84) leads to the conclusion that the active power transferred is a result of controlling the d-axis of the synchronous frame current while the reactive power transferred is a result of controlling the q-axis of the synchronous frame current.

$$P_{g} = \frac{3}{2} \left( v_{gd} i_{gd} + v_{gq} i_{gq} \right)$$

=  $\frac{3}{2} v_{gd} i_{gd} \because v_{gq} = 0$  (83)

$$Q_{g} = \frac{3}{2} \left( v_{gq} i_{gd} - v_{gd} i_{gq} \right)$$

$$= -\frac{3}{2} v_{gd} i_{gq} \because v_{gq} = 0$$

(84)

#### 2.5.1. Open Loop Model

The voltage source converter that controls the power consumed and or supplied to the grid is designed with open loop control of the active and reactive power [18, p. 70]. In order for the PQ controllers to interface the *dq* current controllers (83) and (84) are simplified to per-unit representation in (85) and (86) using Appendix A: Per Unit Values.

$$\frac{3}{2}V_b I_b P_{g,pu} = \frac{3}{2}V_b v_{gd,pu} I_b i_{gd,pu}$$

$$P_{g,pu} = v_{gd,pu} i_{gd,pu}$$

(85)

$$\frac{3}{2}V_b I_b Q_{g,pu} = \frac{3}{2}V_b V_{gd,pu} I_b i_{gd,pu}$$

$$Q_{g,pu} = -V_{gd,pu} i_{gq,pu}$$

(86)

The per-unit open loop PQ controllers are represented in (87) and(88).

$$P_{g,pu}^* = v_{gd,pu} i_{gd,pu}^*$$

(87)

$$Q_{g,pu}^{*} = -v_{gd,pu} i_{gq,pu}^{*}$$

(88)

#### 2.6. Phase-Locked Loop

For voltage oriented control of the voltage source converter the grid voltage angle must be detected in order to align the d-axis of the synchronous frame to the grid voltage vector. With the coordinate transformation of the grid voltage from the *abc* three-phase stationary reference frame to the  $\alpha\beta$  two-phase stationary reference frame the grid voltage angle can then be detected in(89). However, any harmonic content present on the grid voltage may distort the measured angle so instead a phase locked loop is employed [6, pp. 144-145].

$$\theta_g = \tan^{-1} \frac{v_{g\beta}}{v_{g\alpha}} \tag{89}$$

The general concept of the phase-locked loop is to use a PI Controller to establish the grid voltage angle from the grid voltage vector. With the actual grid voltage angle detected, the transformation of the grid voltage vector to the  $\alpha\beta$  two-phase stationary reference frame is defined in (90) and (91) [19, p. 81].

$$v_{g\alpha} = v_g \cos \theta_g \tag{90}$$

$$\mathbf{v}_{g\theta} = \mathbf{v}_g \sin\theta_g \tag{91}$$

Substituting (90) and (91) into the coordinate transformation of the  $\alpha\beta$  two-phase stationary reference frame to the dq synchronous reference frame in Appendix B: Coordinate Transformations results in (92) and (93). Evaluating (93) shows that when the grid voltage angle is established the q-axis of the synchronous frame grid voltage is zero.

$$v_{gd} = \cos \theta_g v_{g\alpha} + \sin \theta_g v_{g\beta}$$

$$= v_g \left( \cos^2 \theta_g + \sin^2 \theta_g \right)$$

(92)

$$= v_g \because \cos^2 \theta_g + \sin^2 \theta_g = 1$$

$$v_{gq} = -\sin \theta_g v_{g\alpha} + \cos \theta_g v_{g\beta}$$

$$= v_g \left( -\sin \theta_g \cos \theta_g + \cos \theta_g \sin \theta_g \right)$$

(93)

$$= 0$$

The output of a PI controller represents the deviation control signal. Since a correct detection of the grid voltage angle results in zero for the q-axis of the synchronous frame grid voltage, it is used as the input to the PI Controller. The addition of the steady-state term to the PI Controller output represents the actual control signal instead of simply the deviation control signal which would result without the addition of the steady-state term [19, p. 91]. By adding the base grid frequency as the bias signal to the PI controller output deviation control signal calculated from the q-axis of the synchronous frame grid voltage the grid frequency is established in(94).

$$\omega_{g} = \underbrace{K_{p,p|l}\left(v_{gq}-0\right) + K_{i,p|l}\int\left(v_{gq}-0\right)dt}_{G_{p_{i,p|l}}} + 2\pi f_{b}$$

$$= K_{p,p|l}v_{gq} + \frac{K_{i,p|l}v_{gq}}{s} + 2\pi f_{g}$$

$$= v_{gq}\left(K_{p,p|l}\frac{1+sT_{i,p|l}}{sT_{i,p|l}}\right) + 2\pi f_{g} \because T_{i,p|l} = \frac{K_{p,p|l}}{K_{i,p|l}}$$

(94)

The result of the integration of grid frequency leads to the grid voltage angle in(95).

$$\theta_{g} = \int \omega_{g} dt$$

$$= \frac{\omega_{g}}{s}$$

(95)

The sampling delay of the computational device can be modeled as a first order low pass filter in (96) with a bandwidth determined by the sampling time of the computational device in (21) [20, p. 59].

$$G_{computational \, device} = \frac{1}{1 + sT_{mp}} \tag{96}$$

With the transfer functions for the controller, computational device, and integrator known the resultant diagram for the detection of the grid voltage angle using a phase-locked loop is represented in Figure 13.

Figure 13 - Phase-Locked Loop for Grid Voltage Angle Detection

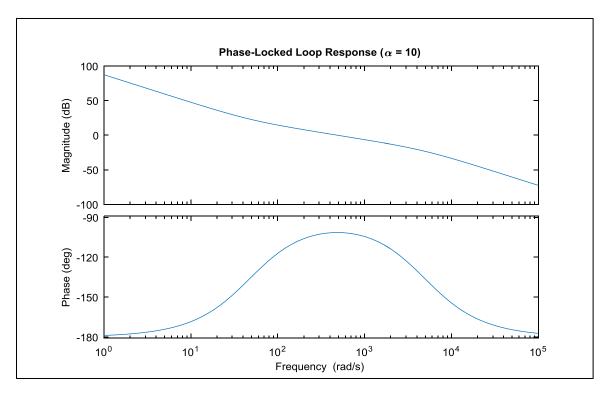

#### 2.6.1. Symmetrical Optimum Tuning of Phase-Locked Loop

By utilizing the symmetrical optimum tuning technique a cross-over frequency with the maximum amount of phase margin is obtained from the geometric mean between the computational device and PI controller frequencies that result in an optimum amount of damping for the phase-locked loop.

Evaluating the product of the forward path of Figure 13 results in the phase-locked loop transfer function as in(97).

$$G_{pll} = G_{pi,pll}G_{computational \,device}G_{integrator}$$

$$= \left(K_{p,pll}\frac{1+sT_{i,pll}}{sT_{i,pll}}\right) \left(\frac{1}{1+sT_{mp}}\right) \left(\frac{1}{s}\right)$$

(97)

Since the application of the phase-locked loop is for the electric grid the frequency should remain fairly constant which allows the bandwidth of the phase-locked loop to be designed with the maximum amount of phase margin in relation to the grid frequency in(98) [20, p. 60] to find the most robust phase-locked loop output. By establishing alpha in (99) the appropriate integral component of the PI controller is determined in(100).

$$\omega_{pll} = \omega_b$$

$$= \frac{1}{\sqrt{T_{mp}T_{i,pll}}} = \frac{1}{aT_{mp}}$$

(98)

$$a = \frac{1}{T_{mp}\omega_b} \tag{99}$$

$$T_{i,pll} = a^2 T_{mp} \tag{100}$$