# University of Wisconsin Milwaukee UWM Digital Commons

Theses and Dissertations

December 2012

# Multi-Level Medium Voltage Inverter for Dc Distributed Wind Farm to Establish Grid Interface and Provide Ancillary Support

Yogesh Popatlal Patel University of Wisconsin-Milwaukee

Follow this and additional works at: https://dc.uwm.edu/etd Part of the <u>Electrical and Electronics Commons</u>

#### **Recommended** Citation

Patel, Yogesh Popatlal, "Multi-Level Medium Voltage Inverter for Dc Distributed Wind Farm to Establish Grid Interface and Provide Ancillary Support" (2012). *Theses and Dissertations*. 203. https://dc.uwm.edu/etd/203

This Dissertation is brought to you for free and open access by UWM Digital Commons. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of UWM Digital Commons. For more information, please contact open-access@uwm.edu.

# MULTI-LEVEL MEDIUM VOLTAGE INVERTER FOR DC DISTRIBUTED WIND FARM TO ESTABLISH GRID INTERFACE AND PROVIDE ANCILLARY SUPPORT

by

Yogesh P. Patel

A Dissertation Submitted in

Partial Fulfillment of the

Requirements for the Degree of

Doctor of Philosophy

in Engineering

at

The University of Wisconsin-Milwaukee

December 2012

## ABSTRACT MULTI-LEVEL MEDIUM VOLTAGE INVERTER FOR DC DISTRIBUTED WIND FARM TO ESTABLISH GRID INTERFACE AND PROVIDE ANCILLARY SUPPORT

by

Yogesh P. Patel

The University of Wisconsin-Milwaukee, 2012 Under the Supervision of Professor Dr. Adel Nasiri

Wind energy has gained in popularity in recent years due to cost, security and environmental concerns associated with conventional energy sources like fossil fuels. However, the utilization of wind energy in power systems creates many technical and non-technical challenges that need to be addressed for successful integrations. The main technical issues related to wind energy are its uncertainty and variability and their impacts on stability, reliability and quality of the electric power. In systems with high wind energy penetrations, unlike conventional generations, sudden changes in active and/or reactive power demand cannot be supported by wind energy. This lack of demand support may create unwanted voltage and frequency variations in the grid. On the hand, the existing AC distributed wind farms have several drawbacks including complexity, higher cost, and lower efficiency.

In this dissertation, a medium voltage direct current (MVDC) distribution system for wind farms is investigated. The proposed system offers higher reliability, lower cost,

ii

higher efficiency and more importantly grid support. It also allows for easier integration of energy storage systems at DC level. Design, control, implementation, and testing of a three-level medium voltage inverter are presented. The inverter can provide active and reactive power support to the grid in case of frequency and voltage droops. Simulation and experimental results are presented to verify the viability of the proposed system and control techniques. © Copyright by Yogesh P Patel, 2012 All Rights Reserved

#### ACKNOWLEDGEMENTS

First and foremost, I would like to express my sincere gratitude towards my doctoral thesis advisor, Dr. Adel Nasiri, for his academic advising, guidance, support and understanding, without which this dissertation would have never be produced. Also, I would like to take this opportunity to thank the respected members of my dissertation committee: Dr. George Hanson, Dr. David Yu, Dr. Anoop Dhingra, and Dr. Ethan Munson for guidance during the research process that resulted in this dissertation and courses they taught which all found application in this dissertation. I also like to thank all my colleagues from the Laboratory for Power Electronics and Electric Drives at the University of Wisconsin Milwaukee, for their assistance on various issues and companionship throughout my Ph.D. studies. I thank David Kirschnik, Ahmed Sayed Ahmed, Brian Seibel, Steve Kaishain, Ranga Tallam, Lixiang Wei, Chris Sartler, Mark Phillips and Richard Lukaszewski for their invaluable help in modeling and experimental setup for the thesis. Finally, I thank to my family for their endless support, understanding, and tolerance for all time I had to be away, that this work required.

# TABLE OF CONTENTS

| 1.1 Introduction                                                  |

|-------------------------------------------------------------------|

| 1.2 Problem with offshore wind farm and its distribution          |

| 1.3 Uncertain availability of wind power and effect on the grid   |

| 1.4.MVDC distribution for wind applications                       |

| 2. Precharge                                                      |

| 2.1 Types of Precharge Circuits                                   |

| 2.2 Precharge sequence for propose novel AC precharge topology 11 |

| 2.3 Advantages of novel precharge circuit 12                      |

| 2.4 Novel DC precharge circuit                                    |

| 2.5 Simulation results                                            |

| 2.6 Conclusion 17                                                 |

| 3. LCL and Trap filter for VSI                                    |

| 3.1. Low harmonics requirements                                   |

| 3.2 Trap filter analytical model and design algorithm             |

| 3.2.1 Trap filter configuration                                   |

| 3.2.2 Trap filter design                                          |

| 3.3 LCL filter analytical model and design algorithm              |

| 3.3.1 LCL filter configuration                                    |

| 3.3.2 LCL filter design algorithm                                 |

| 3.4 Effect of the source impedance                                |

| 3.5 Passive damping for LCL filters                               |

| 3.6 Simulation and Experimental results                           |

| 3.6. 1 Simulation result of Trap filter                        | 38 |

|----------------------------------------------------------------|----|

| 3.6.2 Simulation result of LCL filter                          | 39 |

| 3.6.3 Experimental result Trap filter                          | 41 |

| 3.6.4 Experimental result LCL filter                           | 42 |

| 3.7 Comparison of Trap and LCL filters                         | 44 |

| 3.8 Conclusion                                                 | 44 |

| 4. Voltage source inverter                                     | 46 |

| 4.1 Introduction                                               | 46 |

| 4.2 Selection of topology                                      | 46 |

| 4.3 Three level NPC voltage source inverter                    | 49 |

| 4.3.1 Gate pulse generation for 3L NPC voltage source inverter | 51 |

| 4.4 Control technique for 3L NPC VSI                           | 54 |

| 4.4.1 Constant DC bus voltage control                          | 54 |

| 4.4.2 Active and reactive power control                        | 59 |

| 4.5. Simulation result                                         | 61 |

| 4.6. Experimental setup and control implementation             | 68 |

| 4.6.1 Experimental result                                      | 68 |

| 4.6.3 Experimental result                                      | 80 |

| 4.7. Conclusion                                                | 89 |

| 5. Energy efficient inverter for wind power application        | 90 |

| 5.1 Introduction                                               | 90 |

| 5.2 Power losses in LCL filter                                 | 91 |

| 5.2.1 Core loss                                                | 91 |

| 5.2.2 Copper loss                                                     |     |

|-----------------------------------------------------------------------|-----|

| 5.3 Power losses in VSI/VSC/CSC                                       |     |

| 5.3.1 Double pulse test setup                                         |     |

| 5.4 Power losses in DC link capacitor and miscellaneous loss          | 103 |

| 5.5 Efficiency and standby mode of operation                          | 104 |

| 5.6 Experimental result                                               | 105 |

| 5.7 Conclusion                                                        | 110 |

| 6. MVDC distribution system: frequency and voltage droop support      | 111 |

| 6.1. Overview of the grid standard                                    | 111 |

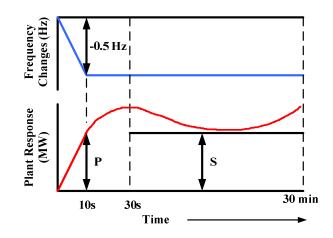

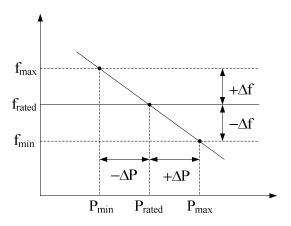

| 6.1.1. Active power requirement and frequency regulation              | 112 |

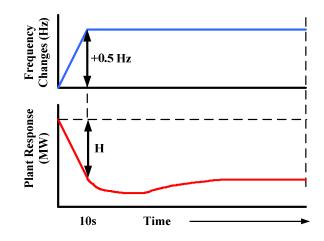

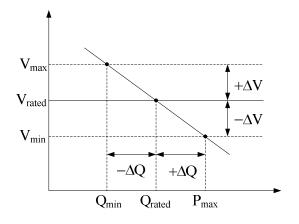

| 6.1.2. Reactive power requirement and voltage regulation              | 115 |

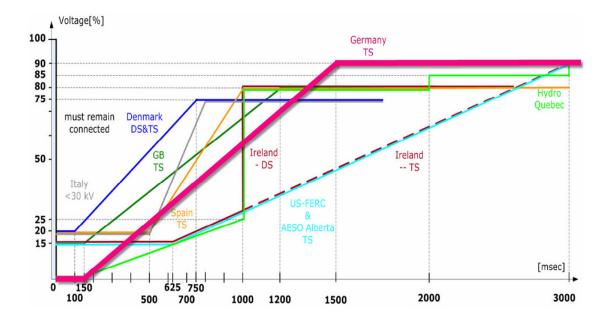

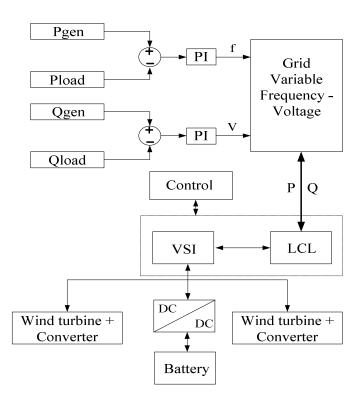

| 6.2 Medium Voltage DC distribution system for wind power applications | 119 |

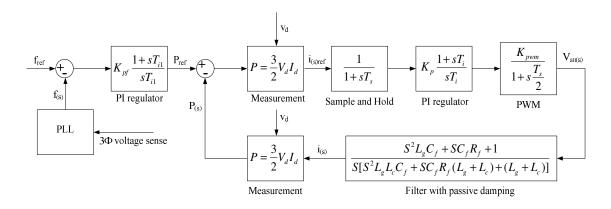

| 6.3. Frequency droop and voltage droop control                        | 123 |

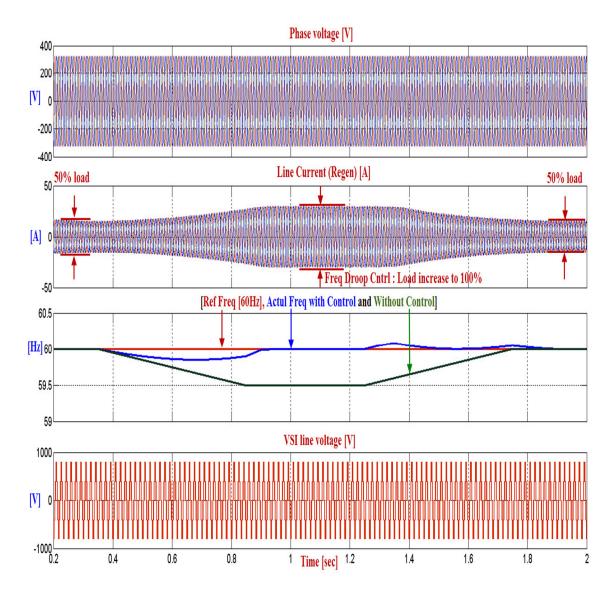

| 6.4. Simulation result                                                | 129 |

| 7. Conclusion                                                         | 152 |

| 8. References                                                         | 155 |

| APPENDIX A: LCL filter design algorithm                               | 161 |

| APPENDIX B: Trap filter design algorithm                              | 164 |

| APPENDIX C: LCL filter damping calculation                            | 168 |

| Curriculum Vitae                                                      | 171 |

# LIST OF FIGURES

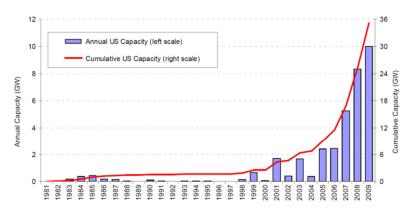

| Figure 1.1 Annual / cumulative installed capacity of wind power (US), Source NREL 1 |

|-------------------------------------------------------------------------------------|

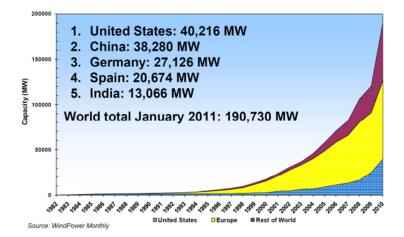

| Figure 1.2 Total installed wind power capacity, source Wind power 1                 |

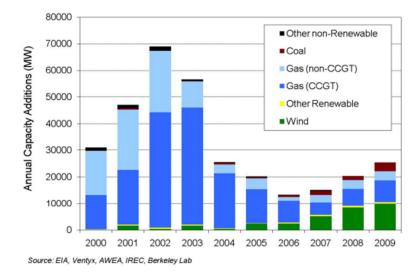

| Figure 1.3 Wind power annual capacity addition, source EIA 2                        |

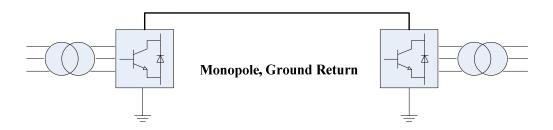

| Figure 1.4 DC distribution with monopole and ground return                          |

| Figure 1.5 DC distribution with monopole and metallic return                        |

| Figure 1.6 DC distribution with monopole and midpoint grounded                      |

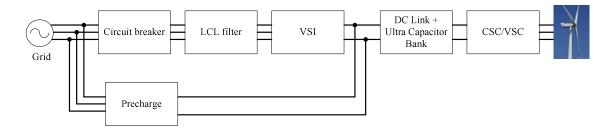

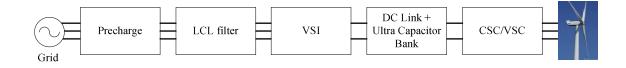

| Figure 1.7 Block diagram of proposed MVDC distribution system                       |

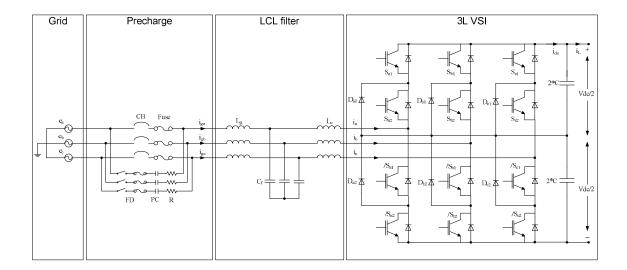

| Figure 2.1 Block diagram system with conventional AC precharge                      |

| Figure 2.2 Detail of the AC side precharge circuit                                  |

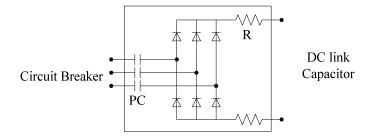

| Figure 2.3 Block diagram system with conventional precharge (DC side) 10            |

| Figure 2.4 Detail of the DC side precharge circuit 10                               |

| Figure 2.5 Block diagram of system with novel AC precharge 10                       |

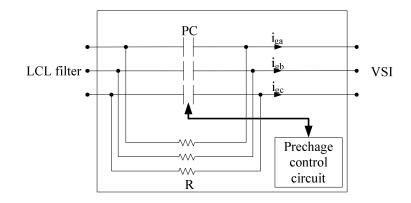

| Figure 2.6 Detail of the novel AC precharge circuit                                 |

| Figure 2.7 Block diagram of the power conversion system with DC precharge 13        |

| Figure 2.8 Detail of the DC precharge circuit                                       |

| Figure 2.9 Matlab Simulink model of AC precharge circuit 15                         |

| Figure 2.10 Simulation result of AC precharge                                       |

| Figure 2.11 Matlab Simulink model of DC precharge                                   |

| Figure 2.12 Simulation result of DC precharge 17                                    |

| Figure 3.1 3L NPC VSI with Trap filter                                              |

| Figure 3.2 Single phase equivalent circuit of VSI with TRAP filter                  |

| Figure 3.3 Block diagram of TRAP filter                               | . 23 |

|-----------------------------------------------------------------------|------|

| Figure 3.4 Bode plot of TF of Trap filter without damping             | . 26 |

| Figure 3.5 Bode plot of Trap filter with damping                      | . 27 |

| Figure 3.6 3L NPC VSI with LCL filter                                 | . 28 |

| Figure 3.7 Single phase equivalent circuit for VSI with LCL filter    | . 29 |

| Figure 3.8 Block diagram for the LCL filter                           | . 29 |

| Figure 3.9 Bode plot of LCL filter with different source impedance    | . 31 |

| Figure 3.10 VSI's connected at same PCC                               | . 32 |

| Figure 3.11Block diagram of LCL filter with series damping resistor   | . 33 |

| Figure 3.12 Block diagram of LCL filter with Cf1    [Cf2+Rf] damping  | . 34 |

| Figure 3.13 Block diagram of LCL filter with Cf+ [Lf    Rf] damping   | . 35 |

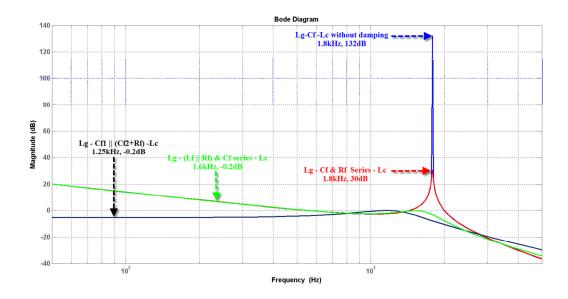

| Figure 3.14 LCL passive damping techniques comparison using bode plot | . 37 |

| Figure 3.15 LCL damping resistor switching circuit                    | . 37 |

| Figure 3.16 Simulation result of Trap filter phase voltage            | . 38 |

| Figure 3.17 Simulation result of Trap filter phase currents           | . 38 |

| Figure 3.18 Simulation result of Trap voltage and currents FFT        | . 39 |

| Figure 3.19 Simulation result of LCL filter phase voltage             | . 40 |

| Figure 3.20 Simulation result of LCL filter phase currents            | . 40 |

| Figure 3.21 Simulation result of LCL filter voltage and currents FFT  | . 41 |

| Figure 3.22 Trap filter full load phase currents                      | . 41 |

| Figure 3.23 Trap filter FFT of phase R voltage and phase current      | . 42 |

| Figure 3.24 LCL filter full load measurement of phase currents        | . 42 |

| Figure 3.25 LCL filter FFT of phase R voltage and phase current       | 43   |

| Figure 4.1 Classification for high power converters                        | 47 |

|----------------------------------------------------------------------------|----|

| Figure 4.2 2.2kV- 6.6kV rated IGBT from ABB                                | 48 |

| Figure 4.3 3-Level NPC topology for VSC/VSI with LCL filter                | 49 |

| Figure 4.4 Simulation model of 3L NPC gate pulse generator                 | 52 |

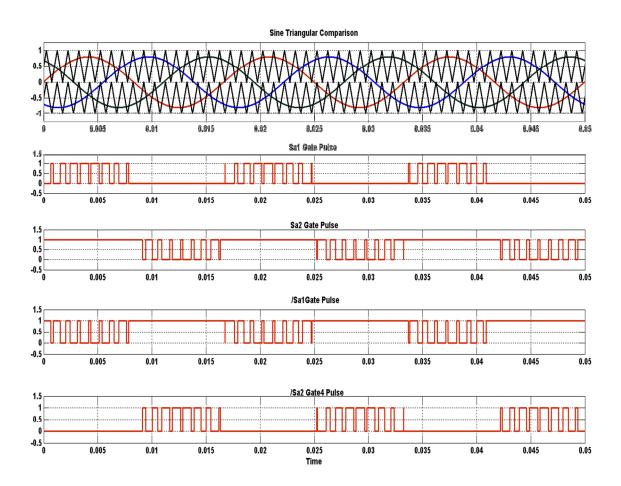

| Figure 4.5 Simulation result of carrier Vs control & pulse generation      | 52 |

| Figure 4.6 Single phase equivalent of 3L VSI with LCL filter               | 53 |

| Figure 4.7 Vector diagram of VSI system                                    | 55 |

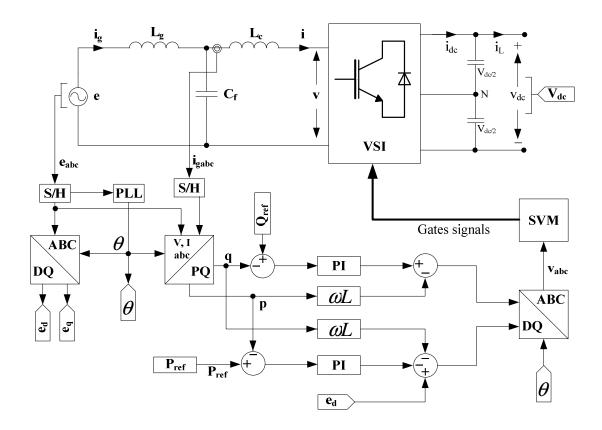

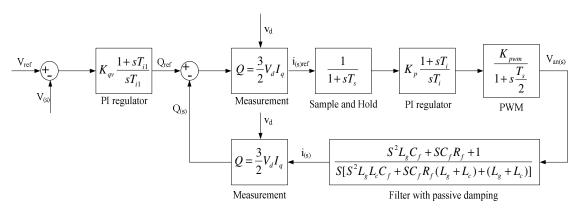

| Figure 4.8 Block diagram of VSI with LCL filter current control            | 57 |

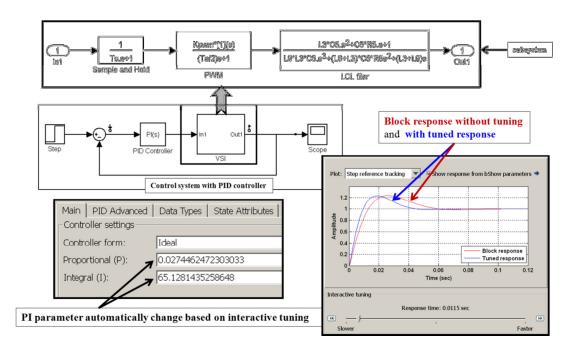

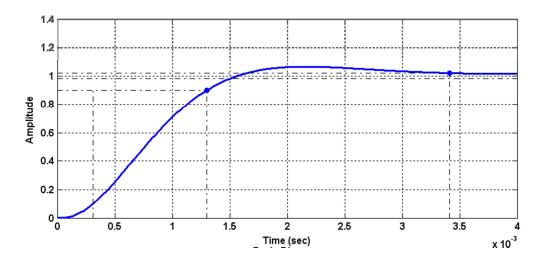

| Figure 4.9 Control loop analysis using control design toolbox              | 57 |

| Figure 4.10 Step response of VSI current control loop                      | 58 |

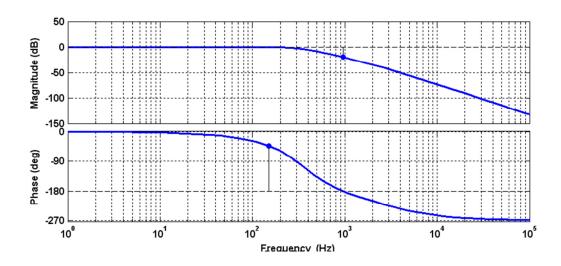

| Figure 4.11 Bode plot of the of VSI with LCL filter current control        | 58 |

| Figure 4.12 Control diagram of constant DC bus voltage control             | 59 |

| Figure 4.13 Control diagram of direct active/reactive power control        | 61 |

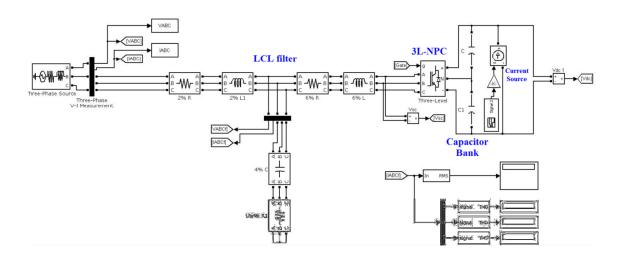

| Figure 4.14 3L NPC VSI with LCL filter model in Simulink                   | 62 |

| Figure 4.15 Constant DC bus control for 3L NPC VSI in Simulink             | 62 |

| Figure 4.16 Simulation result of constant DC bus control                   | 63 |

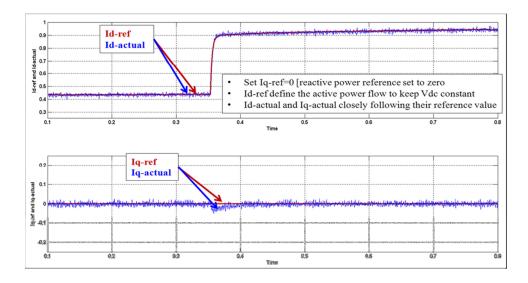

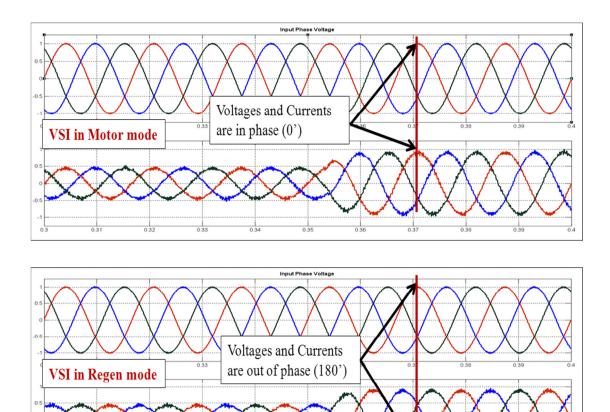

| Figure 4.17 Simulation result of reference and actual $I_d$ and $I_q$      | 63 |

| Figure 4.18 Simulation result of Motor and Regen mode of operation         | 64 |

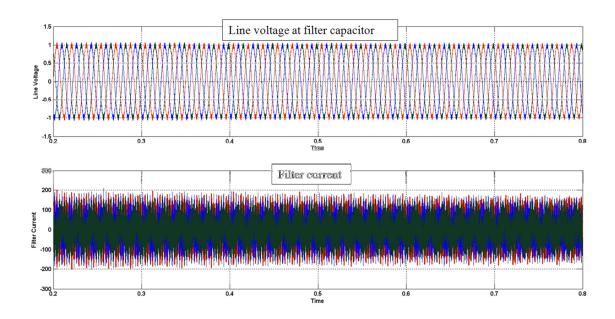

| Figure 4.19 Simulation result of filter capacitor line voltage and current | 65 |

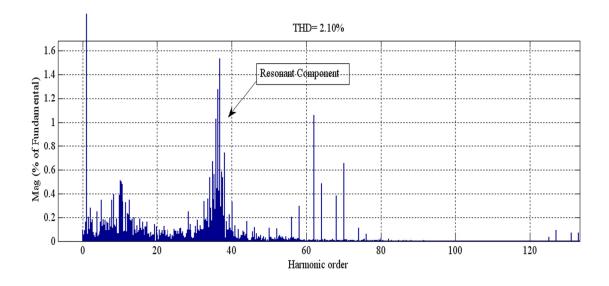

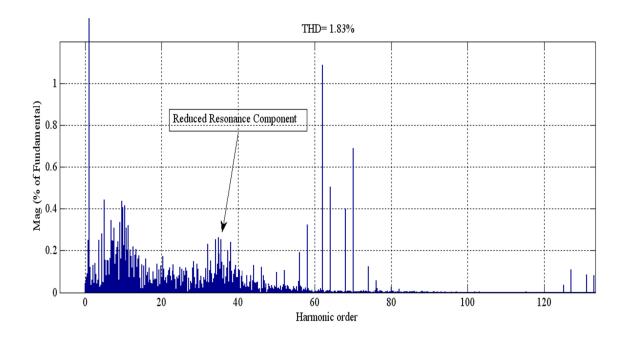

| Figure 4.20 FFT of the VSI line current without passive damping            | 65 |

| Figure 4.21 FFT of the VSI input current with passive damping              | 66 |

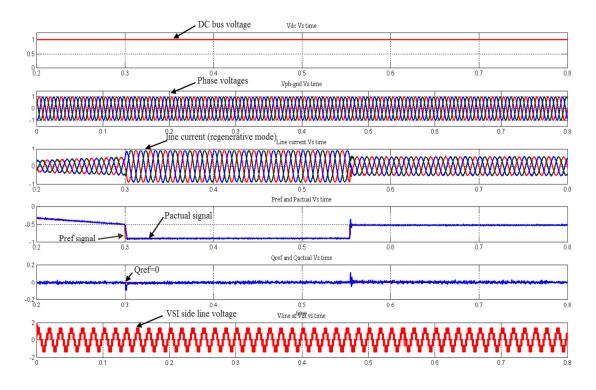

| Figure 4.22 Simulation result of active power control                      | 67 |

| Figure 4.23 Reference and actual active and reactive power                 | 67 |

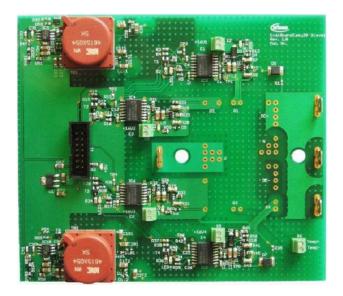

| Figure 4.24 GPDSP board with DSP TMS320F2812                                   | . 69 |

|--------------------------------------------------------------------------------|------|

| Figure 4.25 Spectrum digital XDS510 USB emulator                               | . 69 |

| Figure 4.26 Power Flex Frame-2 power structure                                 | . 70 |

| Figure 4.27 IGBT leg for 3L NPC VSI                                            | . 70 |

| Figure 4.28 IGBT leg for 3L NPC VSI                                            | . 71 |

| Figure 4.29 Gate drive board for 3L NPC VSI                                    | . 71 |

| Figure 4.30 3L NPC VSI with DC bus structure                                   | . 72 |

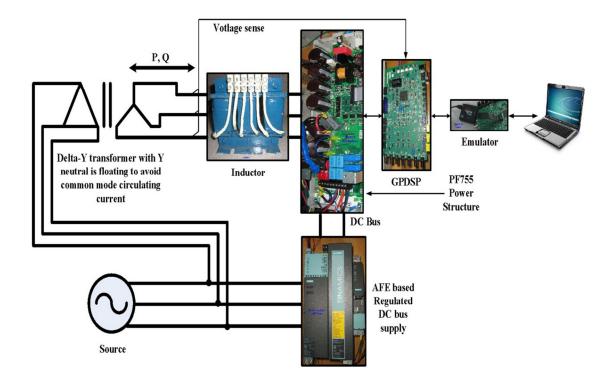

| Figure 4.31 Block diagram of 2L inverter setup                                 | . 73 |

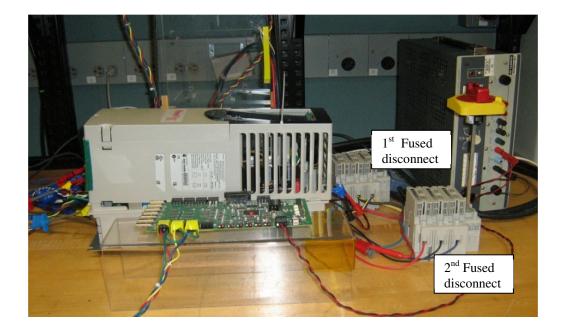

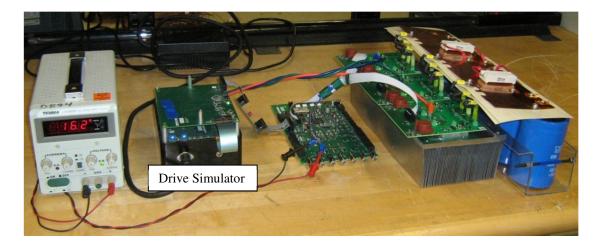

| Figure 4.32 Actual 2L inverter test setup                                      | . 74 |

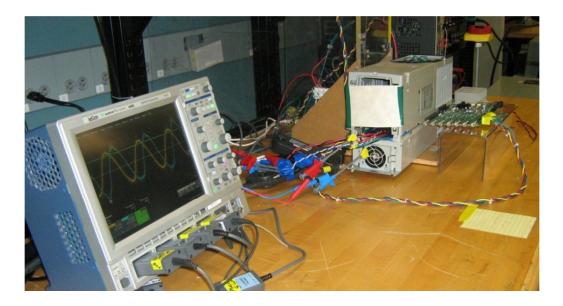

| Figure 4.33Voltage and current measurement setup                               | . 74 |

| Figure 4.34 3L NPC VSI interface with GPDSP and drive simulator                | . 75 |

| Figure 4.35 3L NPC VSI setup for gate pulse measurement                        | . 75 |

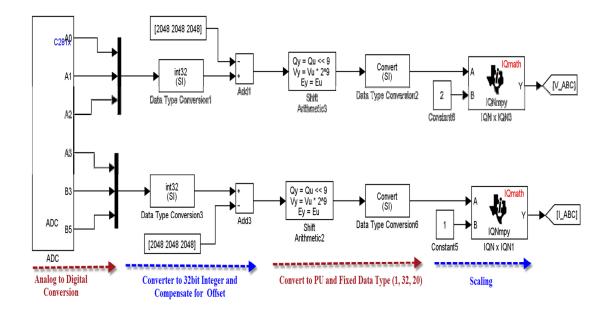

| Figure 4.36 ADC, data type conversion / scaling of voltage and current signals | . 76 |

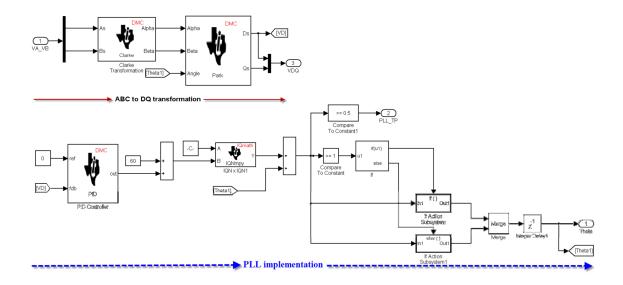

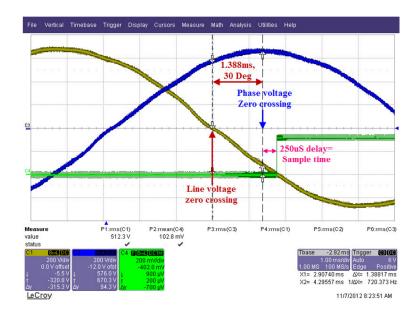

| Figure 4.37 PLL implementation in DSP TMS320F2812                              | . 77 |

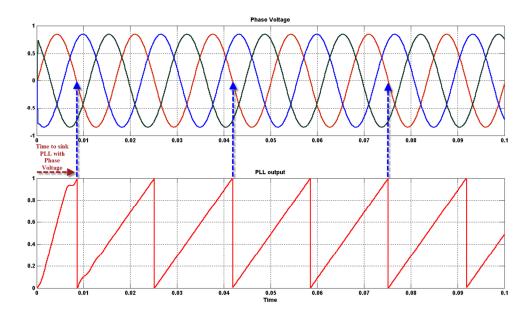

| Figure 4.38 PLL signal synchronized with phase voltage                         | . 77 |

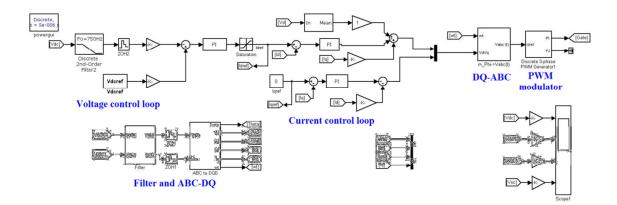

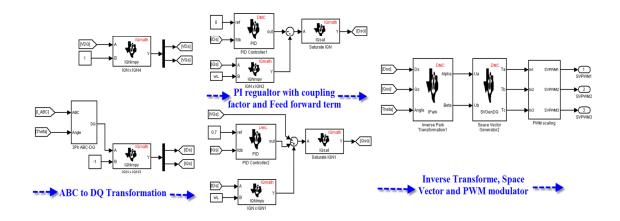

| Figure 4.39 Current regulator in DSP TMS320F2812                               | . 78 |

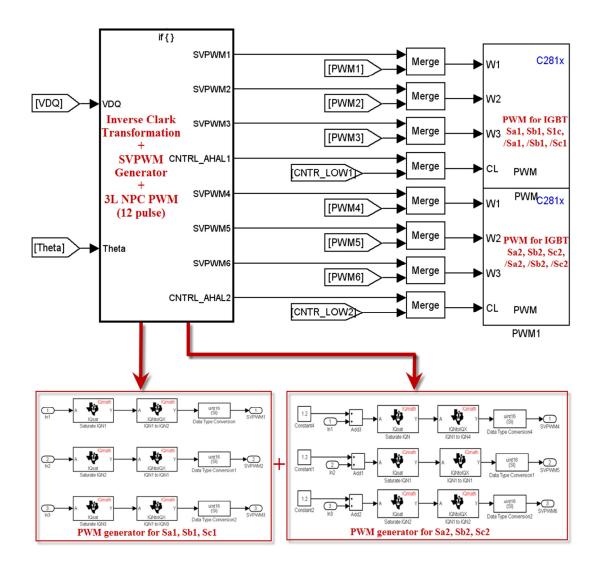

| Figure 4.40 6 pulse generators in Matlab for 3L NPC VSI                        | . 79 |

| Figure 4.41 Modified 2 pulses per phase for 3L NPC gate pulse generator        | . 80 |

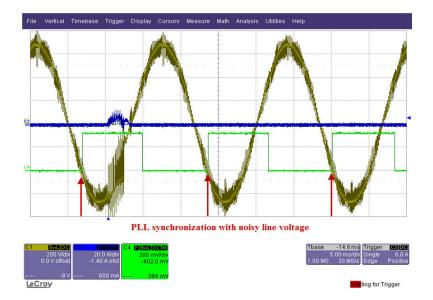

| Figure 4.42 Experimental result of PLL sync with phase voltage                 | . 81 |

| Figure 4.43 PLL synchronization with noisy line voltage                        | . 81 |

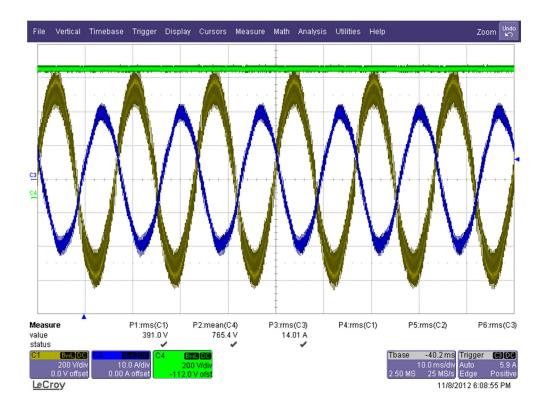

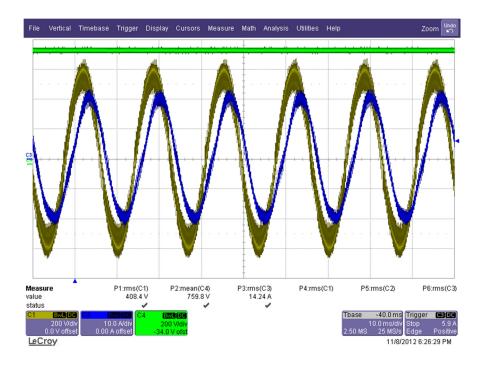

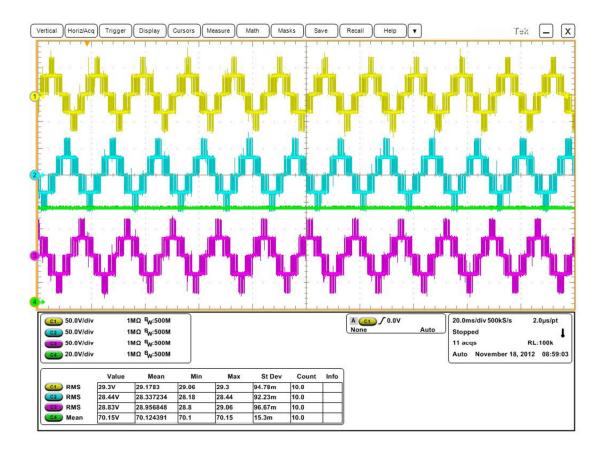

| Figure 4.44 Experimental result of 2L VSI in motor mode at full load           | . 82 |

| Figure 4.45 Experimental result of 2L VSI in Regen mode at full load           | . 83 |

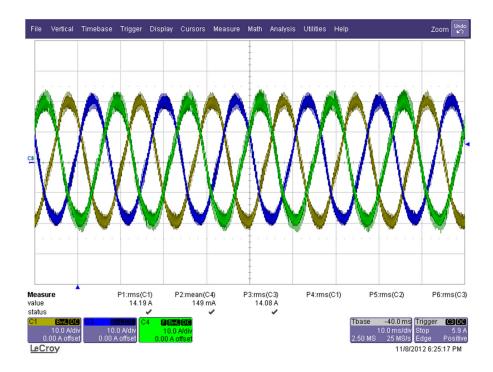

| Figure 4.46 3-phase current waveform in Regen mode at full load                | . 83 |

| Figure 4.47 FFT analysis of line voltage for 2L VSI                       | 84    |

|---------------------------------------------------------------------------|-------|

| Figure 4.48 FFT analysis of line current for 2L VSI                       | 85    |

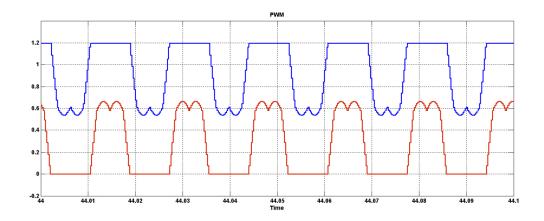

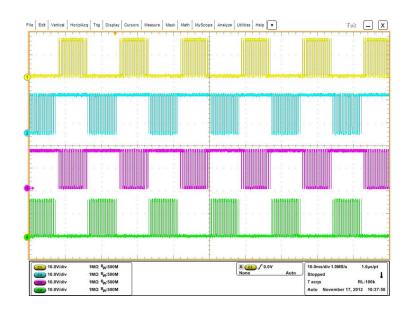

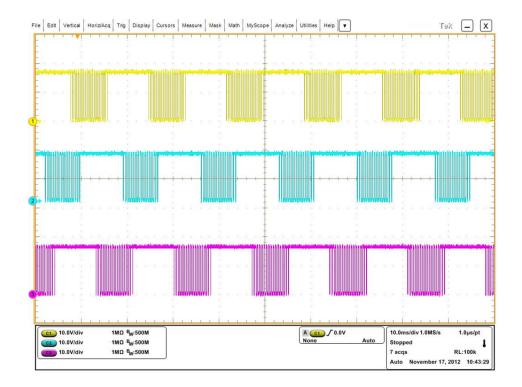

| Figure 4.49 Gate drive pulse pattern of one leg for 3L NPC                | 85    |

| Figure 4.50 Gate pulse pattern of 2 <sup>nd</sup> IGBT of Phase R, S, & T | 86    |

| Figure 4.51 3L NPC line voltage measurement at converter side             | 87    |

| Figure 4.52 3L NPC in motor mode: Voltage and current measurement         | 88    |

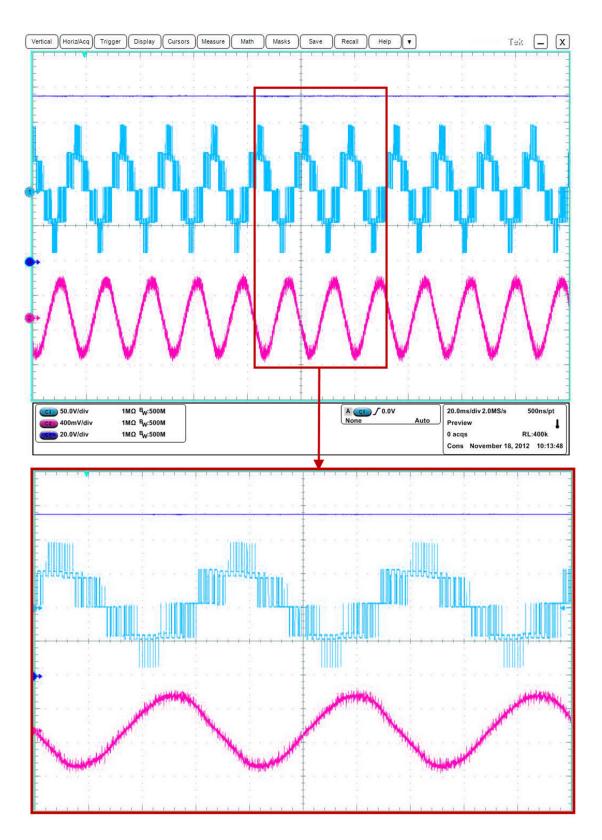

| Figure 5.1 Power conversion unit for wind power application               | 91    |

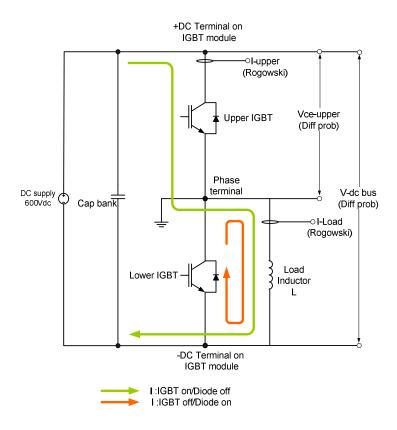

| Figure 5.2 Double pulse test circuit                                      | 96    |

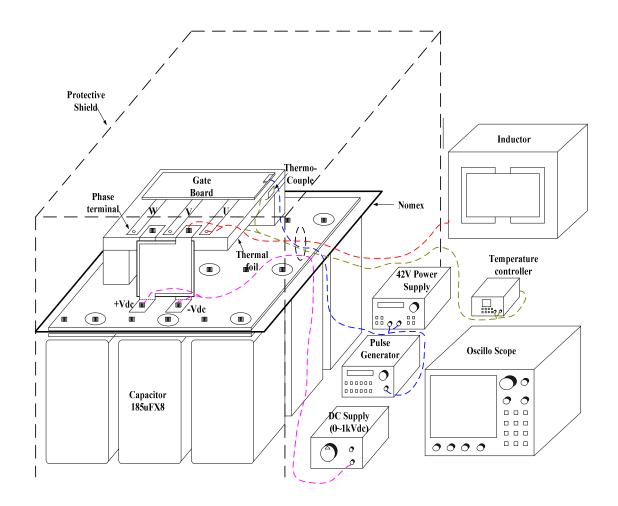

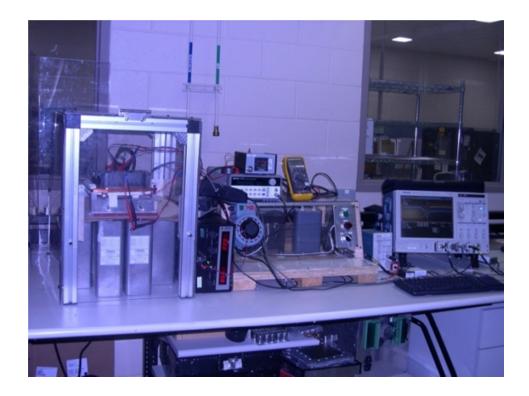

| Figure 5.3 Setup for double Pulse Test                                    | 97    |

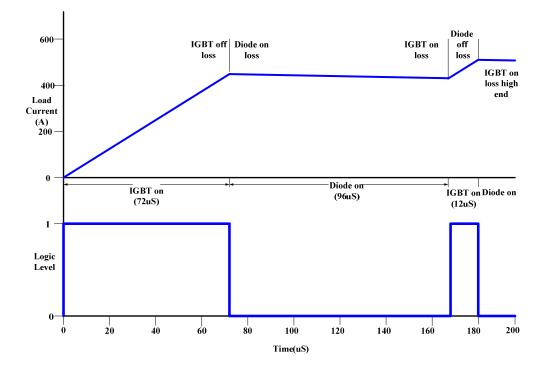

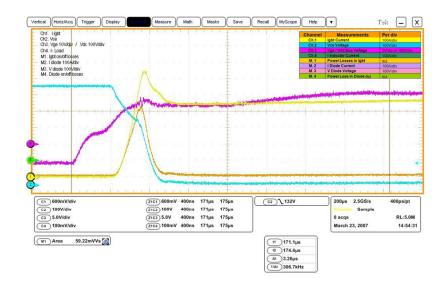

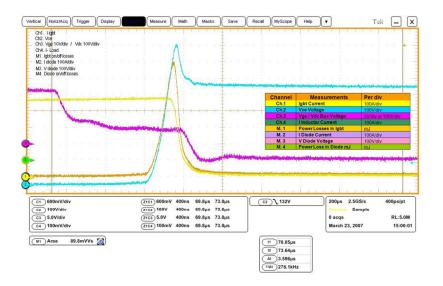

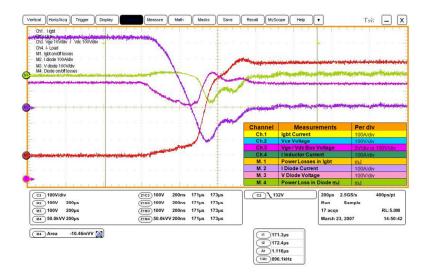

| Figure 5.4 Double pulse diagram                                           | 99    |

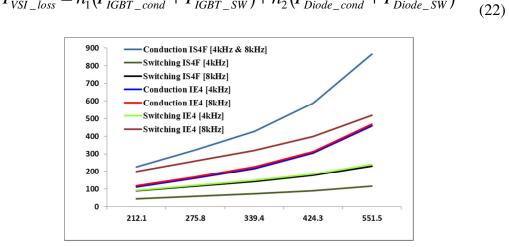

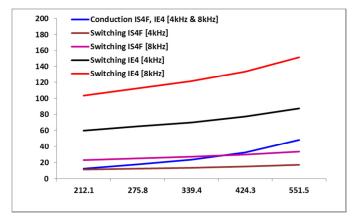

| Figure 5.5 IGBT conduction and switching losses for Si and SiC unit       | . 100 |

| Figure 5.6 Diode conduction and switching losses for Si and SiC unit      | . 100 |

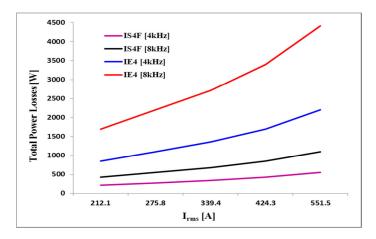

| Figure 5.7 Total power losses for Si and SiC unit                         | . 101 |

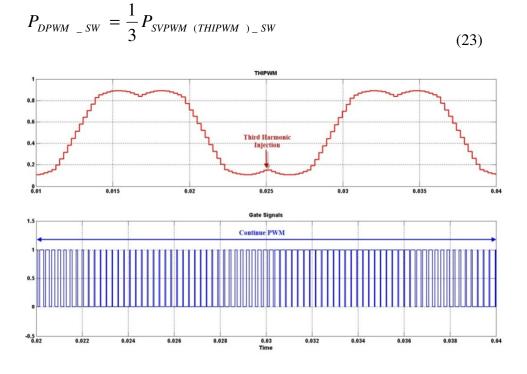

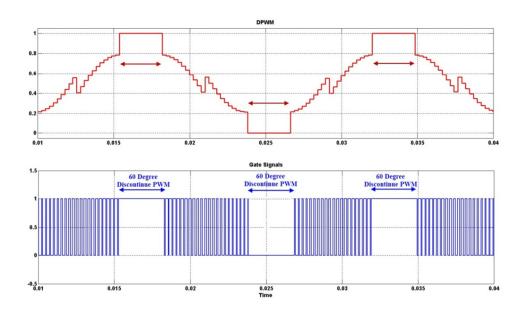

| Figure 5.8 THIPWM control signal and PWM gate pulse                       | . 102 |

| Figure 5.9 DPWM control signal and PWM gate pulse                         | . 102 |

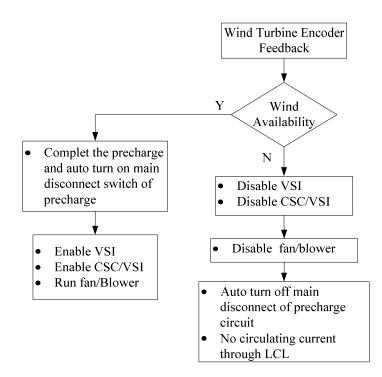

| Figure 5.10 Flow chart for standby mode of operation                      | . 105 |

| Figure 5.11 Actual double pulse test setup                                | . 106 |

| Figure 5.12 IGBT ON loss at 450A                                          | . 107 |

| Figure 5.13 IGBT OFF loss at 450A                                         | . 107 |

| Figure 5.14 Diode OFF loss at 450A                                        | . 108 |

| Figure 5.15 Input voltage and current waveform for 300Hp unit             | . 109 |

| Figure 6.1 Pri and Sec response requirement for frequency support         | . 113 |

| Figure 6.2 High frequency response requirements for grid                  | . 114 |

| Figure 6.3 Low voltage ride though chart, source NREL                              |

|------------------------------------------------------------------------------------|

| Figure 6.4 Proposed MVDC distribution system                                       |

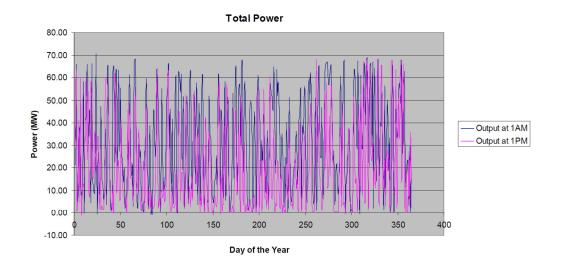

| Figure 6.5 Power profile of 72MW wind farm at 1AM & 1PM during a year 121          |

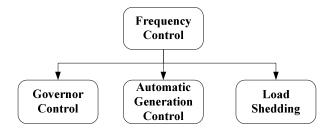

| Figure 6.6 Conventional frequency control techniques for grid 122                  |

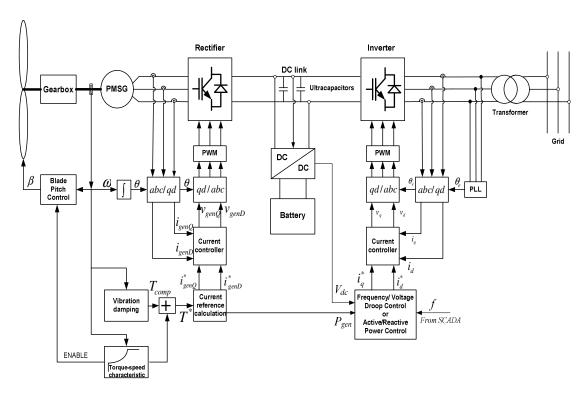

| Figure 6.7 Over view of MVDC system with frequency and voltage droop control 122   |

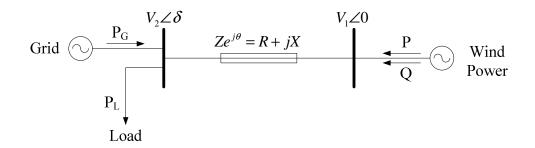

| Figure 6.8 Simplified model of MVDC interface system with two nodes 123            |

| Figure 6.9 Vector diagram of two node system                                       |

| Figure 6.10 Frequency Vs active power characteristics                              |

| Figure 6.11 Voltage Vs reactive power characteristics                              |

| Figure 6.12 Single phase equivalent block diagram of frequency droop control 127   |

| Figure 6.13 Single phase equivalent block diagram of the voltage droop control 127 |

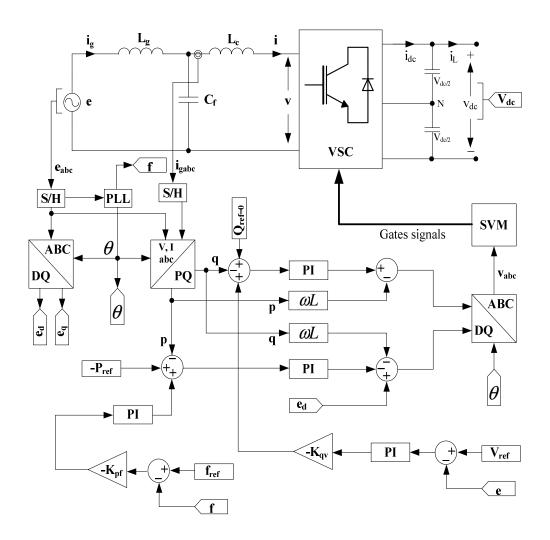

| Figure 6.14 Control diagram of VSI with Frequency and Voltage droop support 128    |

| Figure 6.15 Block diagram of the simulated system in Matlab Simulink 129           |

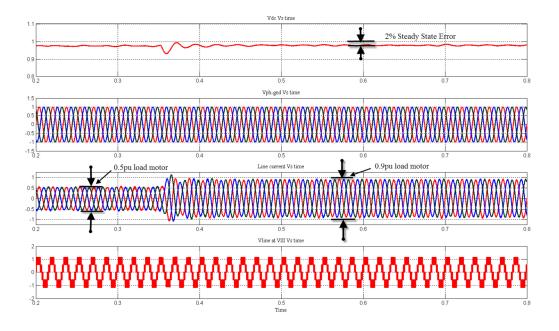

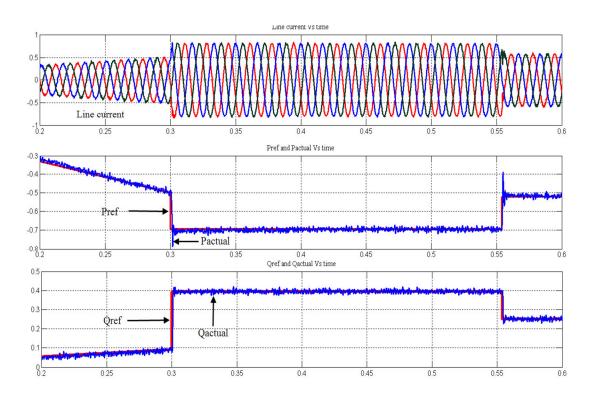

| Figure 6.16 Simulation results for frequency droop control                         |

| Figure 6.17 Simulation results for voltage droop control                           |

| Figure 6.18 Experimental setup for frequency and voltage droop control             |

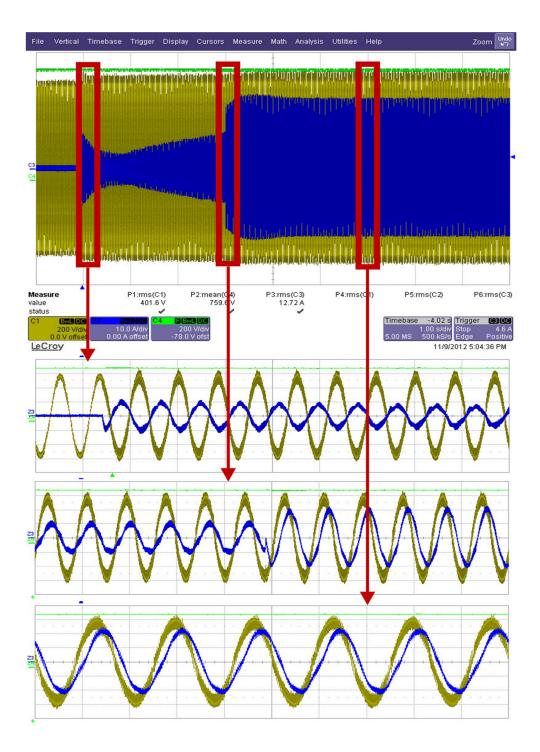

| Figure 6.19 Experimental result of VSI in Regen mode at no load                    |

| Figure 6.20 Experimental result of VSI in Regen mode at 25% to 100% load 135       |

| Figure 6.21 3Ph current in Regen mode at 25% to 100% load                          |

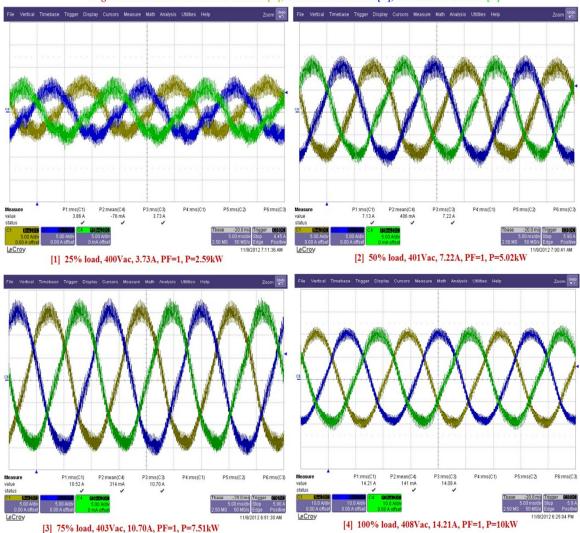

| Figure 6.22 Experimental result of VSI in Motor mode at 25% to 100% load 137       |

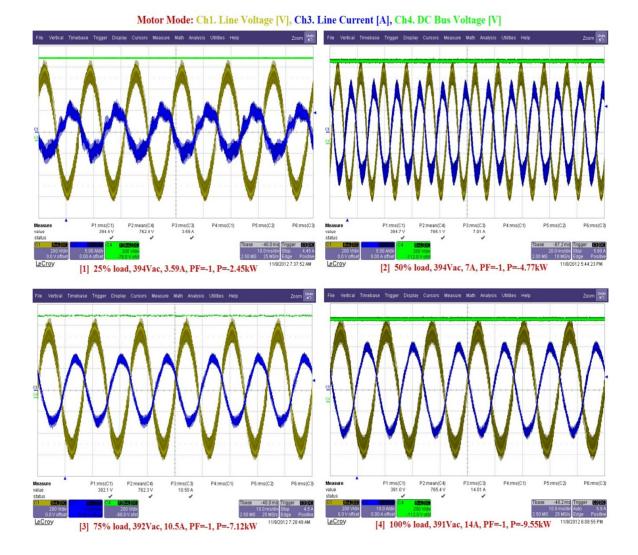

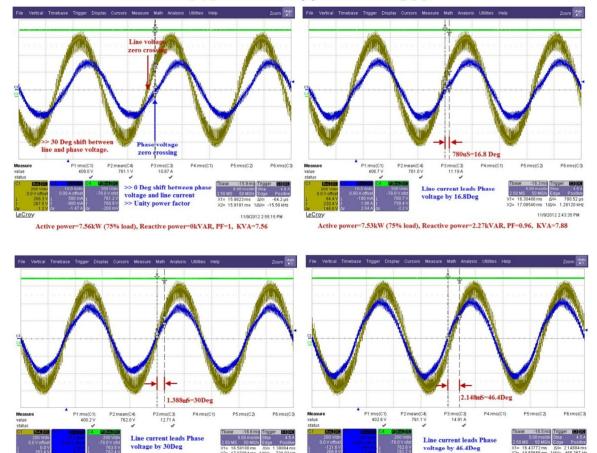

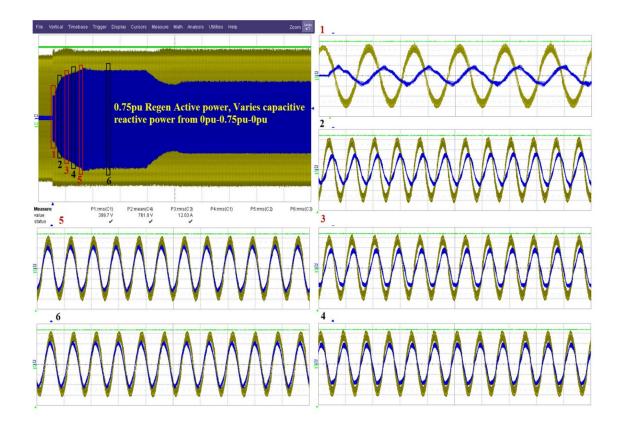

| Figure 6.23 Active power = 75% and variable reactive power (capacitive)            |

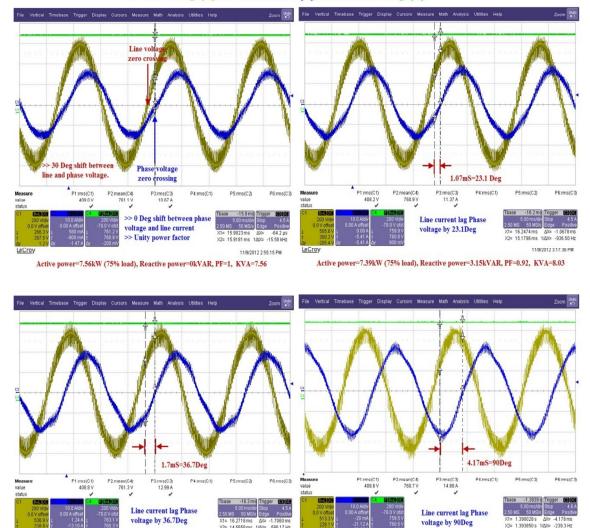

| Figure 6.24 Active power set to 75% and variable reactive power (inductive) 139    |

| Figure 6.25 Ramp and step change of active power reference                         |

| Figure 6.26 Active power 75%, reactive power ramp changes               | 141 |

|-------------------------------------------------------------------------|-----|

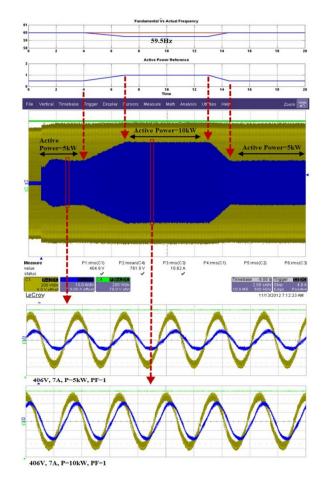

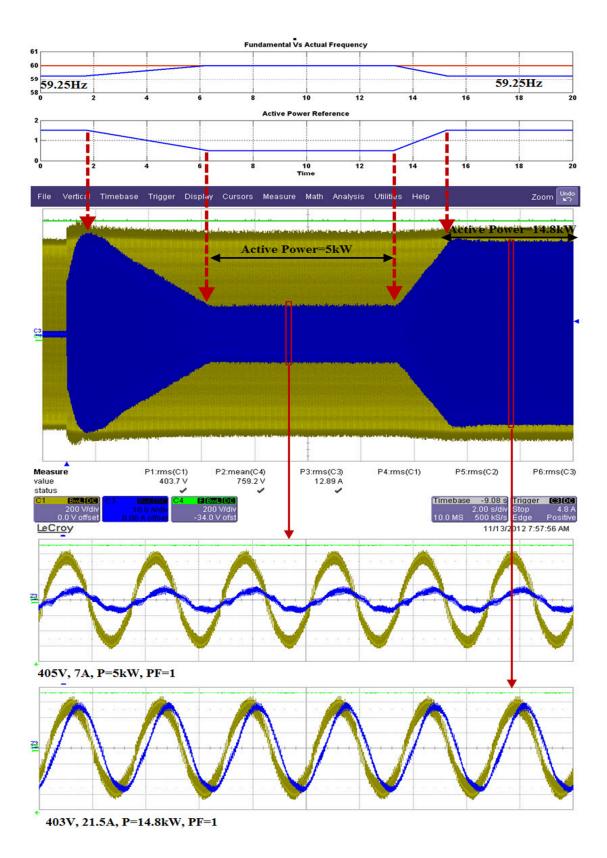

| Figure 6.27 Frequency droop support with 100% max load profile          | 142 |

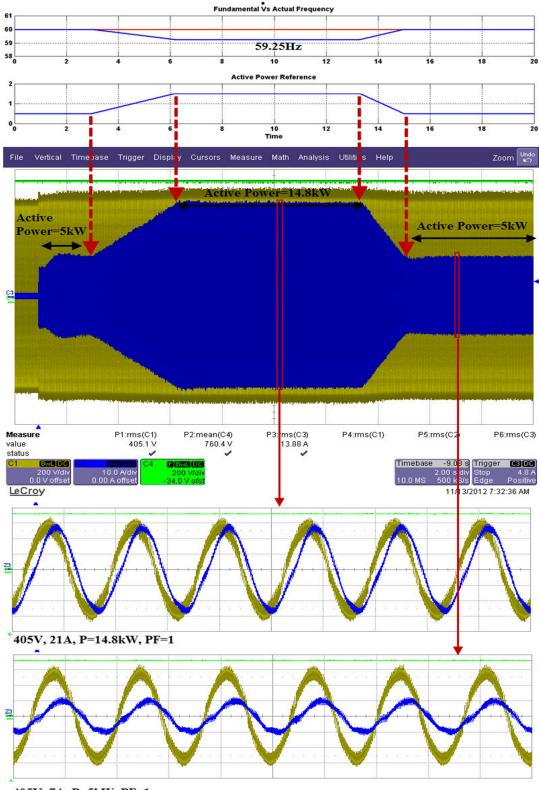

| Figure 6.28 Frequency droop support with 150% load profile 1            | 144 |

| Figure 6.29 Frequency droop support with 150% load profile 2            | 145 |

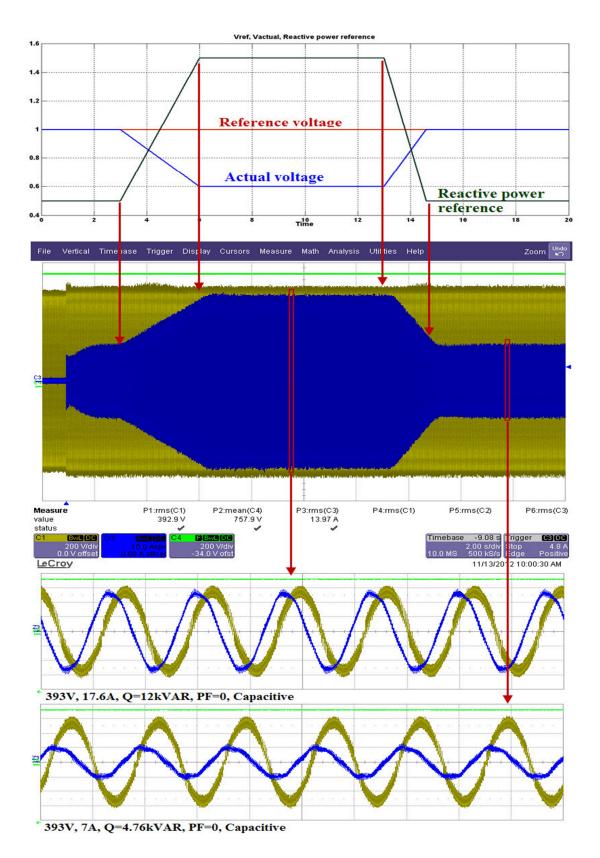

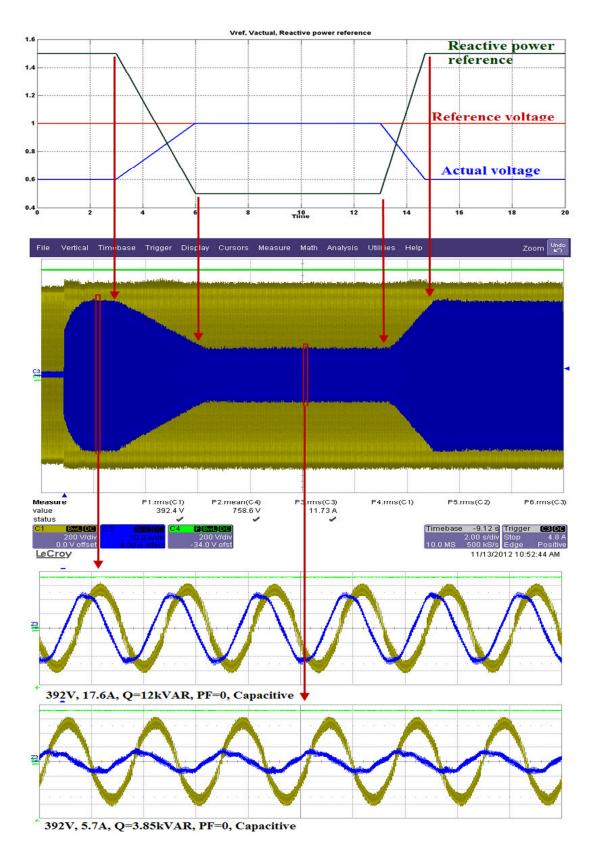

| Figure 6.30 Voltage droop support with 150% load profile 1              | 147 |

| Figure 6.31 Frequency droop support with 150% load profile 2            | 148 |

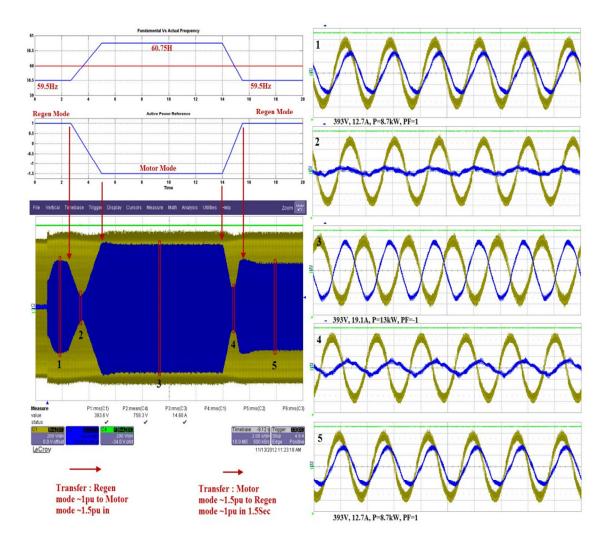

| Figure 6.32 Frequency droop support with Regen and Motor mode operation | 149 |

# LIST OF TABLES

| Table 2.1. AC precharge parameter use for simulation    15                |

|---------------------------------------------------------------------------|

| Table 2.2. DC precharge parameter for Simulink model                      |

| Table 3.1. IEEE 519 Voltage Distortion Limit.    20                       |

| Table 3.2. IEEE 519 Current Distortion Limit                              |

| Table 3.3. Trap filter parameters                                         |

| Table 3.4. LCL filter parameters                                          |

| Table 3.5. LCL passive damping technique comparison in terms of watt loss |

| Table 4.1. 3-Level NPC switching states (Phase a)    49                   |

| Table 5.1. Conditions for VSI watt loss measurement                       |

| Table 5.2. Power loss breakdown in LCL filter                             |

| Table 5.4. Measured efficiency for 300Hp unit at different load condition |

| Table 6.1 Operational frequency range requirement for different grid      |

| Table 6.2. Power factor requirements for different grid    117            |

| Table 6.3. Low voltage ride through requirement for different grid        |

## LIST OF ABBREVIATIONS

- DC Direct Current

- AC Alternating Current

- VSI Voltage Source Inverter

- VSC Voltage Source Converter

- CSC Current Source Converter

- LCL Inductor Capacitor Inductor filter

- NPC Neutral Point Clamp

- AGC Automatic Generator Controller

- PCC Point of Common Coupling

- MVDC Medium Voltage Direct Current

- HVDC High Voltage Direct Current

- LVRT Low Voltage Ride Through

- PMSG Permanent Magnet Synchronous Generator

- MPPT Maximum Power Point Tracking

- PLL Phase Locked Loop

- SVPWM Space-Vector Pulse Width Modulation

- DPWM Discontinue Pulse Width Modulation

- THIPWM Third Harmonic Injection Pulse Width Modulation

- ADC Analog to Digital Converter

- DFIG Doubly Fed Induction Generator

- PMSG Permanent Magnet Synchronous Generator

## **1.1 Introduction**

Renewable energy is increasingly popular over conventional energy. In particular, wind generation has become a substantial share of the total generation. As shown in figure 1.1, in the US alone 10GW wind power installation was added in 2009 with a cumulative capacity over 35GW. Figure 1.2 shows that world total wind power installation is over 190GW. Figure 1.3 shows the renewable energy installed capacity in 2009 is almost 40% of the total installed capacity [1].

Figure 1.1 Annual / cumulative installed capacity of wind power (US), Source NREL

Figure 1.2 Total installed wind power capacity, source Wind power

Figure 1.3 Wind power annual capacity addition, source EIA

The electric energy generation using wind turbines have been in the form of AC so far. This is because most of the wind turbine installations are land based. In addition existing machines, existing power conversion systems, control systems and protection scheme have been adapted in wind energy systems. Besides the onshore trend, offshore wind farms have also been continuing to grow rapidly. Some leading countries in the wind energy arena are focusing more on offshore technology. The main reasons for adopting offshore are lack of suitable onshore sites, installation of wind farms closer to load areas and the much better wind conditions of offshore sites. Sometimes, many of the large offshore wind farms are installed more than 50-60 miles away from the grid connection point. However, AC distribution through submarine cables seems to be less economical for distances about 50-60 miles due to issues related with high charging currents, reactive power and harmonics.

#### 1.2 Problem with offshore wind farm and its distribution

The trend in the wind power industry is the off shore wind farms. Off shore wind farm has its own challenges in terms of cost-effective installation and energy efficient power transfer. Generally offshore wind farms have back to back converters and transfer energy from the wind farm to the grid using three phase AC system. If overhead three phase AC system is used to transfer power from the wind farm to grid, the cost of the installation is very high. In addition to ecological and aesthetic considerations, there are more overhead faults compared to underground faults. If underwater three phase AC system is used in this case, there are higher reactive power requirement as well as being difficult to locate the fault. It is necessary to have a viable economical solution for offshore wind power integration to the gird.

#### 1.3Uncertain availability of wind power and effect on the grid

The grid is dominated by the synchronous machines. Synchronous machines have inertia. When there is sudden change in the active power demand, synchronous machine inertia will allow keeping the frequency of the grid within limits for short durations. It allows time for automatic generation system of the grid to react based on the change in demand. As more and more renewable energy resources are added to the grid, total inertial of the grid won't be dominated by the synchronous machines any more. Grid will be prone to frequency deviation by fluctuations of the load. The frequency deviation is severe enough and won't allow any time for automatic generation systems to react. It severely impacts the power system stability and in some cases it leads to power outages. In addition, the reactive power of the grid is generally supported by synchronous generator, synchronous condenser, static VAR compensator or shunt capacitor. The reactive power effect is localized and reactive power generation must be close to where it requires voltage support. Generally the wind power unit is located remotely and does not support any reactive power generation. When there is a sudden fluctuations of the reactive power demand, the grid voltage may collapse and lead to brownout conditions. Both of these conditions affect grid stability, reliability and quality.

#### **1.4.MVDC** distribution for wind applications

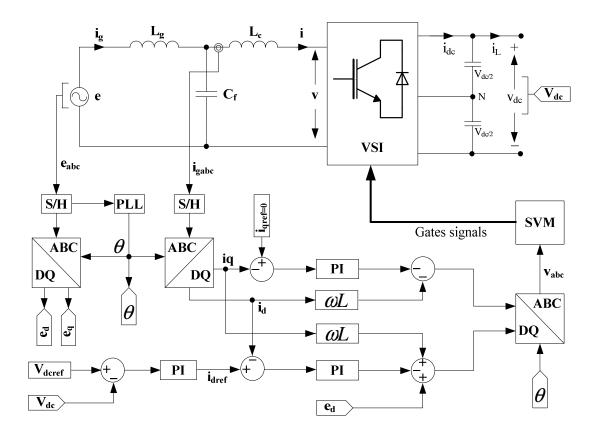

The solution for reactive power support is provided in [2]. The reactive power support is based on combination of the STATECOM (static synchronous compensator) and wind power. It did not address the issue of frequency support. Various references [3], [4] discussed the optimized algorithm to provide reactive power using the DFIG (Doubly Fed Induction Generator) to keep the grid voltage constant. It is machine specific and won't provide a generic solution which includes PMSG (Permanent Magnet Synchronous Generator). In addition, it did not mention about frequency support for the grid. Reference [5]-[7] discussed frequency support, but it always requires the availability of the wind power. There is no back up energy storage system available to support the frequency during off peak wind. Reference [9] is used the VSC-HVDC (High Voltage Direct Current) connected wind farm to support the frequency of the grid without any energy storage unit. In addition, it is very expensive to integrate the energy storage unit

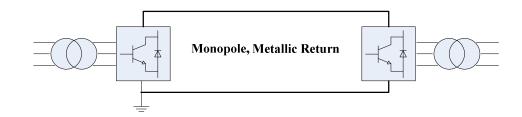

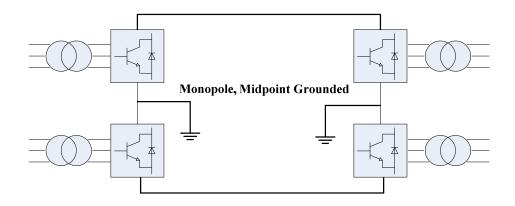

directly to the HVDC bus. The existing converter topologies and power modules easily support the MVDC system [8], [10], [13]. The bi-directional DC-DC converters are available [14] which allow integrating the energy storage systems with the MVDC bus. The MVDC power distribution systems offer several benefits over AC distribution system, such as lower losses and voltage drops, which allow to distribute power over longer distances and to interconnect remote offshore wind farms. With minor drawbacks there are many solutions for a cost effective control and protection of DC distribution system are presented in [13]. Particularly for offshore wind power applications, medium voltage direct current (MVDC) system is suitable from the size, cost and efficiency point of view over high voltage DC system (HVDC)[10]. MVDC distribution can be classified as monopole with ground return, monopole with metallic return or monopole with midpoint grounded. In the entire configuration there is significant cost advantage over the AC distribution. In addition there is no skin effect and minimum loss in the cables. Figures 1.4 to 1.6 show different DC distribution topologies. Added advantages of the DC distribution system are that PV can directly couple to the DC bus of the DC distribution system. Energy storage units and ultra-capacitor banks can be connected to the DC bus.

Figure 1.4 DC distribution with monopole and ground return

Figure 1.5 DC distribution with monopole and metallic return

Figure 1.6 DC distribution with monopole and midpoint grounded

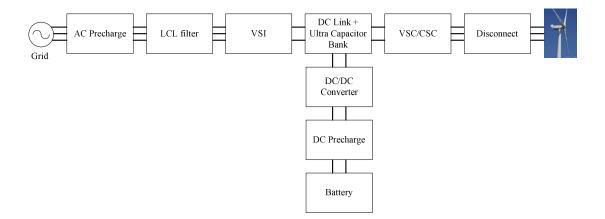

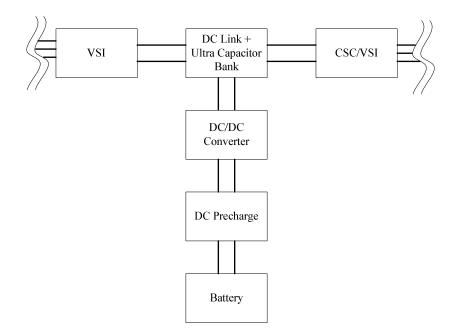

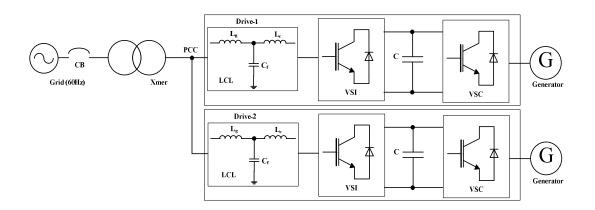

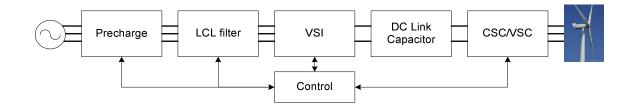

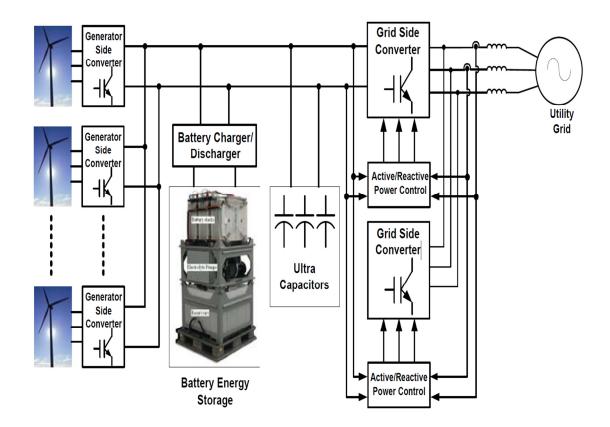

Figure 1.7 Block diagram of proposed MVDC distribution system

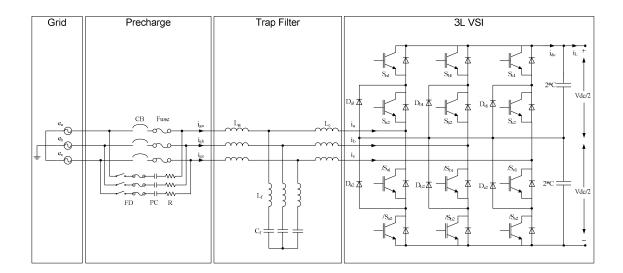

The block diagram of proposed DC distribution system for a wind farm is shown in figure 1.7. The wind farm connected to the MVDC link using CSC/VSC based converter and AC side disconnect switch. Energy storage, PV unit etc. can be interface with the

MVDC link using DC precharge and DC/DC converter. The MVDC link connects to the grid using VSI, LCL filter and AC precharge unit. The MVDC provides the cost effective distribution of the wind power. VSI based inverter can be controlled such a way that it provides frequency and voltage droop support to the grid.

In this thesis, a novel frequency and voltage droop support control strategy is presented which increases the stability and reliability of the grid. The VSI based 3L NPC topology to support the MVDC system is discussed in detail. An algorithm to provide optimized value of the LCL filter is discussed. It reduces the size, cost and power losses of the LCL filter. Novel precharge topologies (AC and DC) offer size and cost effective solutions. Energy efficient voltage source inverter with standby mode of operation during unavailability of wind is provided. The following chapter discusses the precharge for the voltage source inverter application.

#### 2. Precharge

The precharge circuit is used to reduce high inrush current to the DC link capacitor during startup of the VSI. The typical precharge circuit includes precharge resistors in parallel with the contactor. The precharge circuit can either connected to the AC side of the VSI or the DC side of the VSI. Different types of the conventional precharge circuits commonly used for the power conversion systems will be discussed in this chapter. The novel AC and DC precharge circuits are presented and compared with conventional precharge circuits. Precharge control sequences will be discussed in detail and verified using simulation results.

#### **2.1 Types of Precharge Circuits**

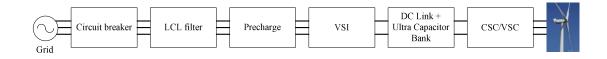

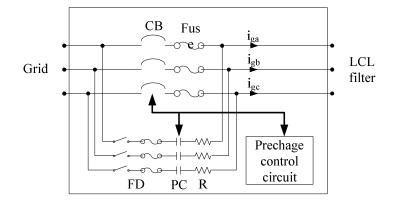

One of the commonly used precharge circuit is shown in figure 2.1 and 2.2 as below [15][17]. The circuit breaker (CB) is used for to isolate the system from the grid. The precharge circuit is connected between the LCL filter and the VSC. The precharge circuit consists of the precharge contactor (PC) in parallel with the resistor(R). The precharge contactor is rated for the full load current of the system. During start up, first turn on the circuit barker. The precharge contactor is normally open and the DC capacitor bank is charged through the resistor. The precharge controller turns on the contactor when the DC capacitor bank charges up to 90% of the peak grid line to line voltage. Once the precharge contactor turns on, precharge resistors are bypassed. The precharge resistors need not to be rated for a higher wattage rating because it just precharges the DC capacitor bank and after that there is minimum current flow through the precharge resistor. The disadvantages of this precharge are two full load rated components (circuit breaker and precharge contactor) are required. The LCL filter capacitor bank is not precharge through the precharge circuit and may be prone to damages from the inrush current.

Figure 2.1 Block diagram system with conventional AC precharge

Figure 2.2 Detail of the AC side precharge circuit

Another commonly used precharge circuit is shown in figure 2.3 and 2.4 as below [17]. The circuit breaker is used to isolate the main power structure from the grid. During start up, the circuit breaker is normally off. The DC capacitor bank is charged through the precharge contactor, rectifier and resistor. The precharge controller will wait until the DC capacitor bank charge up to 90% of the peak line to line voltage and then it will issue a command to close the circuit breaker. After the circuit breaker turns on, the precharge control will turn off the precharge contactor. The precharge contactor is not rated for the

full load rating of the system. The only disadvantage of this precharge is that the LCL filter capacitor is not precharged.

Figure 2.3 Block diagram system with conventional precharge (DC side)

Figure 2.4 Detail of the DC side precharge circuit

A novel precharge circuit for the power conversion system is shown in figure 2.5 and 2.6. The precharge circuit is between the grid and the LCL filter [16][18]. The precharge circuit consist of a circuit breaker, fused disconnect (FD), fuses, precharge contactor and resistors. The fused disconnect and the precharge contactor is not rated for full load. Only the main circuit breaker is rated for full load current.

Figure 2.5 Block diagram of system with novel AC precharge

Figure 2.6 Detail of the novel AC precharge circuit

The precharge resistor need to be rated for higher power rating because during the precharge mode it will carry the current to charge the DC capacitor bank as well as the circulating current through the LCL filter. It is also necessary to make sure the precharge resistor is in the circuit for a very short duration, till the DC bus is precharged. Once DC bus reaches 90% of the grid line to line voltage, it must turn on the main circuit breaker to avoid the LCL circulating current passing though the precharge resistor. This indirectly imposes the requirement of automatic precharge circuit instead of manual precharge.

#### 2.2Precharge sequence for propose novel AC precharge topology

### Precharge turn on sequence:

- Manually turn on the fused disconnect.

- The precharge control circuit turn on the precharge contactor

- LCL filter capacitor bank and DC link capacitor start recharging through fused disconnect, precharge contactor and resistor.

- When the DC link voltage reaches 90% of the peak line to line grid voltage, the precharge controller will turn on the circuit breaker.

- After the circuit breaker turns on, the precharge controller will turn off the precharge contactor.

- The precharge contactor always turns off after the precharge complete or after fault occurred, which prevents circulating current through the LCL filter.

## **Precharge turn off sequence:**

- Turn off the fused disconnect.

- Precharge controller detect the status of the fused disconnect.

- Precharge controller will turn off the VSC first and then open the circuit breaker.

# 2.3Advantages of novel precharge circuit

- Only one full rated current component is used, which leads to lower power loss and cost effective design.

- The precharge circuit serves dual purpose. 1) precharge 2) Means of disconnect of the power conversion unit from the grid and lockout / tagout operation.

- Precharge circuit precharge DC link capacitors as well as the LCL filter capacitors. It increases the life of the filter capacitors.

- In case of fault or normal turn off sequence, the precharge controller will turn off the inverter first and then issue an actuate command to turn of the circuit breaker.

These guarantees the no load makes and breaks operation of the circuit breaker. It reduces the maintenance and increases the life of the circuit breaker.

### 2.4Novel DC precharge circuit

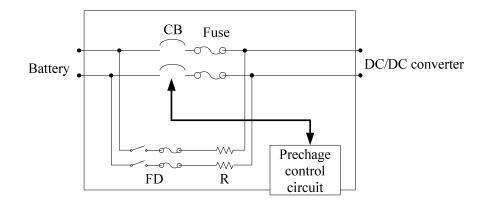

The derivate of the novel AC precharge technique is used for the DC precharge applications as shown in figure 2.7. The battery is connected to the DC/DC converter using the DC precharge circuit. The DC/DC converter is used to charge the battery and delivers energy back to the grid to support the frequency and voltage droop control.

Figure 2.7 Block diagram of the power conversion system with DC precharge

The DC precharge circuit diagram is shown in figure 2.8. The DC precharge circuit is similar to AC precharge as shown in figure 2.6. The only differences are the precharge contactor is not required and the precharge resistor is not rated for a higher power [19].

The fused disconnect turns on manually. The DC bus on DC/DC converter starts precharging through FD and the resistors. When the DC link capacitors are completely charged, the precharge controller turns on the circuit breaker. The DC precharge works as a precharge as well as the disconnect means in case of the maintenance. Same as the AC precharge, the DC precharge controller algorithm make sure that the CB always turns on and turns off at no load. Which reduces the size of DC rated circuit breaker and provides potentially cost saving solution for the MVDC system.

Figure 2.8 Detail of the DC precharge circuit

## **2.5Simulation results**

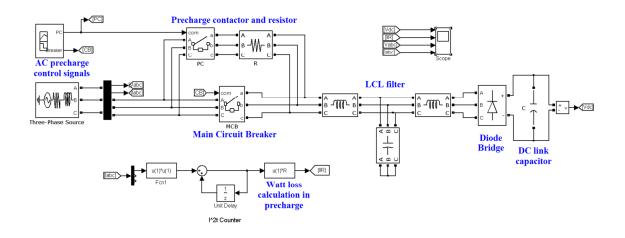

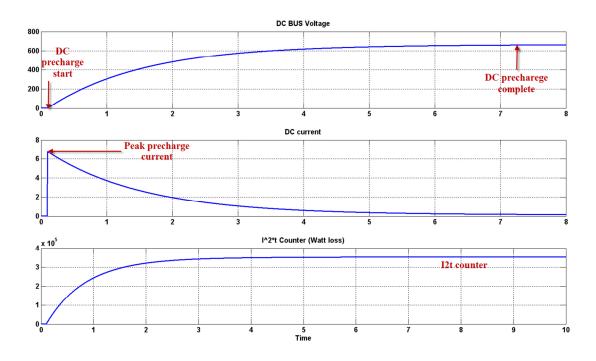

The simulation study of the AC precharge is performed using Matlab Simulink software. Figure 2.9 shows the Simulink model of an AC precharge. The AC precharge controller controls the ON and OFF sequence of the precharge contactor and main circuit breaker during the precharge operation. The precharge model parameters are shown in table 2.1 as below:

| AC precharge Parameters |        |

|-------------------------|--------|

| Input Voltage           | 480Vac |

| Total Power             | 200kW  |

| Bus Capacitance         | 60mF   |

| 3% Inductor             | 84uH   |

| 9% Inductor             | 254uH  |

| 5% Capacitor            | 415uF  |

| Precharge Resistor      | 2.50hm |

Table 2.1. AC precharge parameter use for simulation

Figure 2.9 Matlab Simulink model of AC precharge circuit

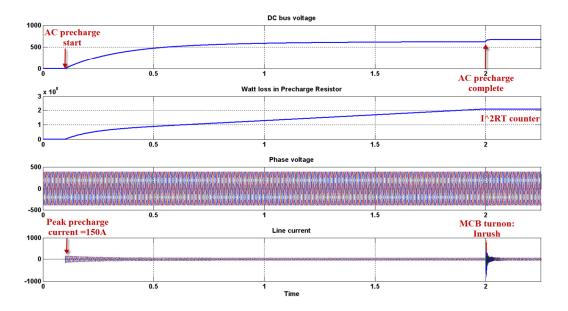

The simulation result of an AC precharge is shown in figure 2.10. The first waveform shows the DC bus capacitor charge up to 90% of the peak line voltage within 2 sec. Second waveform shows the i<sup>2</sup>tR counter for the precharge resistor, which determines the rating of the resistor. The line current waveform shows that when MCB is close, the capacitor bank will charge remaining 10% rapidly and around 1000A peak current pass through the circuit breaker.

Figure 2.10 Simulation result of AC precharge

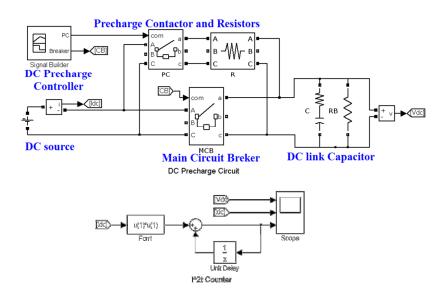

Figure 2.11 shows the Simulink model for DC precharge circuit. The Precharge contactor is not required in the DC precharge circuit. For the DC precharge application, one can select a higher precharge resistor value. The parameter for the DC precharge circuit is shown in table 2.2. Figure 2.12 shows the dc precharge simulation result.

Figure 2.11 Matlab Simulink model of DC precharge

| DC precharge parameters |           |

|-------------------------|-----------|

| DC bus voltage          | 678Vdc    |

| Bus Capacitance         | 15mF      |

| Cap ESR                 | 0.01040hm |

| Balancing Resistor      | 5000ohm   |

| Precharge Resistor      | 50ohm     |

Table 2.2. DC precharge parameter for Simulink model

Figure 2.12 Simulation result of DC precharge

# **2.6Conclusion**

The novel AC and DC precharge topologies are presented in this chapter. The proposed AC precharge topology precharges the DC link capacitor as well as LCL filter. Both AC and DC precharge have size and cost advantages. It reduces the maintenance and increase life of the switch gear. An automated AC and/or DC precharge topology enables standby mode of operation when wind is not available. In next chapter, the LCL and the Trap filter for VSI are discussed in detail including optimum design algorithm, effect of grid impedance and passive damping technique to reduce the resonance in the filters.

### **3.** LCL and Trap filter for VSI

This chapter presents two main filters widely used in industry for the three phase voltage source inverters. The filters are the Trap and the LCL. These filters are primarily used to reduce the switching frequency ripple and to meet the IEEE 519 THD requirements. The algorithms presented in this chapter provide optimized values of the inductors and capacitors for the Trap and LCL filters. The source impedance has significant effect on the resonance of the filters. The passive resonance damping techniques are presented in this chapter. The Trap and LCL filters for a 125kW voltage source inverter are designed using algorithm. The simulation and experimental results reveal the performance of the Trap and LCL filter. This chapter also compares the Trap and LCL filter results.

### **3.1.** Low harmonics requirements

Voltage source inverter connection to the grid contributes to harmonic distortion proliferating throughout the system. The IEEE Standard 519 established a basis for limits on system distortion. The IEEE 519 specifications for voltage and current harmonics are shown in Table 3.1 and 3.2. In many specifications the lowest number in table is used for all situations and little attention is paid to the  $I_{SC}/I_L$  ratio at PCC (point of common coupling). For a soft source ( $I_{SC}/I_L$ <20) the current distortion is less than 5% whereas for a stiff source ( $I_{SC}/I_L$ = 100-1000) the current distortion is less than 15%. Voltage source are connected to the grid using the reactors or filters and isolation transformers. The size of the isolation transformer defines the allowable distortion as per IEEE 519 as presented in [20]. Generally for medium to higher power applications, lower converter switching frequencies are selected to reduce switching losses. This results in smaller heat sinks and cooling fans. As a result, active converter size will be reduced and efficiency will be higher. The lower switching frequency requires a higher value of the input reactors to reduce the switching frequency ripple, which is very expensive and gives poor dynamic response. In addition, a reactor alone is not sufficient to meet the IEEE 519 requirements. Alternative solutions to these problems are to use either a Trap or a LCL filter instead of the line reactors as suggested in [20]-[22]. Trap and LCL filters are specifically design to reduce switching frequency ripple and provide lower total harmonic distortion.

| Bus Voltage at PCC     | Individual<br>Harmonic (%) | Total Harmonic<br>Distortion THD% |

|------------------------|----------------------------|-----------------------------------|

| 1.0kV and below        | 5.0                        | 8.0                               |

| 1.001kV through 69kV   | 3.0                        | 5.0                               |

| 69.001kV through 161kV | 1.5                        | 2.5                               |

| 161.001kV and above    | 1.0                        | 1.5                               |

| Maximum Harmonic Current Distortion in Percentage of IL |  |

|---------------------------------------------------------|--|

| Individual Harmonia Order (Odd Harmonias)               |  |

| Table 3.1 | <b>IEEE 519</b> | Voltage | Distortion | Limit |

|-----------|-----------------|---------|------------|-------|

|           |                 |         |            |       |

| Ν        | Maximum Harmonic Current Distortion in Percentage of IL                  |                 |               |           |       |      |  |

|----------|--------------------------------------------------------------------------|-----------------|---------------|-----------|-------|------|--|

|          | Indi                                                                     | vidual Harmonic | Order (Odd Ha | armonics) |       |      |  |

| Isc/IL   | <11                                                                      | 11<=h<17        | 17<=h<23      | 23<=h<35  | 35<=h | TDD  |  |

| <20      | 4.0                                                                      | 2.0             | 1.5           | 0.6       | 0.3   | 0.5  |  |

| 20<50    | 7.0                                                                      | 3.5             | 2.5           | 1.0       | 0.5   | 8.0  |  |

| 50<100   | 10.0                                                                     | 4.5             | 4.0           | 1.5       | 0.7   | 12.0 |  |

| 100<1000 | 12.0                                                                     | 5.5             | 5.0           | 2.0       | 1.0   | 15.0 |  |

| >1000    | 15.0                                                                     | 7.0             | 6.0           | 2.5       | 1.4   | 20.0 |  |

| Isc =me  | Isc =max short circuit current at PCC. IL=max demand load current at PCC |                 |               |           |       |      |  |

Table 3.2 IEEE 519 Current Distortion Limit

### 3.2 Trap filter analytical model and design algorithm

### **3.2.1 Trap filter configuration**

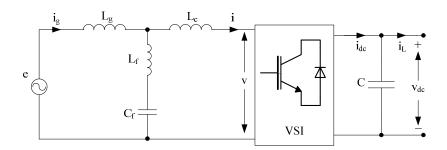

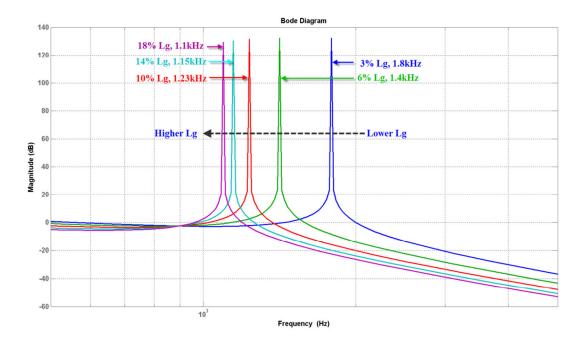

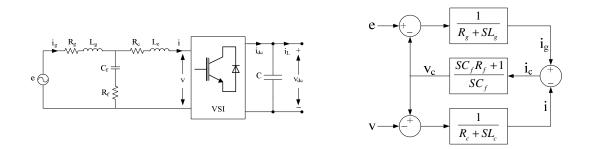

A Trap filter based 3L VSI is shown in figure 3.1. The filter name is based on its ability to trap the switching frequency components.  $L_g$  and  $L_c$  are grid side and VSI side inductances.  $L_g=L_t+L_1$ , where  $L_t$  is the inductance of the isolation transformer and  $L_1$  is inductance of the line side inductor.  $L_t$  is not required unless the application requires two converters connected in parallel on the same isolation transformer. In paralleling,  $L_t$  is used to reduce the circulating current between the two parallel units. The inductor  $L_f$  and the capacitor  $C_f$  are conned in Y configuration. The damping resistor R can be connected in series with the  $L_f$  and the  $C_f$  to damp the resonance. The resonance study and the novel techniques to mitigate the resonance are discussed later in this chapter.

The goal of the Trap filter is to reduce the switching frequency ripple and meet the IEEE 519, total harmonic distortion requirements. The  $L_f$  and  $C_f$  are tuned to the switching frequency of the 3L VSI [23]. The design of the Trap filter is critical because poor design results in lower attenuation of switching frequency components, resonant issues, higher cost, higher power losses, lower efficiency and inductor saturation. The Trap filter design limitations are the switching frequency of VSI, line frequency and the power rating of VSI. The isolation transformer to which the VSI is connected also plays an important role. It is necessary to consider the isolation transformer impedance in the Trap filter design.

Figure 3.1 3L NPC VSI with Trap filter

The higher the power rating of VSI, the lower the switching frequency used to reduce the switching losses. Usually the switching frequency for 100kW to 1MW VSC varies from 2 kHz to 6 kHz. It is very difficult to design the Trap filter with very low switching frequency because the resonance frequency of the filter must not approach the fundamental frequency as well as the switching frequency. In addition, the size and the cost of  $L_c$  will be higher. Isolation transformer impedance also contributes to the resonance frequency of the Trap filter. VSIs are connected to isolation transformers up to a maximum of 20 times rating, providing a wide bandwidth of resonance frequency. Also, the tolerance of  $L_c$  contributes to the bandwidth of resonance frequency. The cost of  $L_c$  is inversely proportional to allowable tolerances in the inductance value [26]-[28]. The single phase equivalent circuit of the Trap filter is shown in figure 3.2. The damping resistor is ignored in mathematical model.

Figure 3.2 Single phase equivalent circuit of VSI with TRAP filter

Figure 3.3 Block diagram of TRAP filter

$$\frac{i_g(s)}{e(s)} = \frac{S^2(L_fC_f + L_cC_f) + 1}{S^3(L_gL_2C + L_gL_fC_f + L_cL_fC_f) + S(L_g + L_c)}$$

(1)

$$\frac{i(s)}{v(s)} = \frac{S^2(L_f C_f + L_g C_f) + 1}{S^3(L_g L_2 C + L_g L_f C_f + L_c L_f C_f) + S(L_g + L_c)}$$

(2)

-. 7

The resonance frequency of the Trap filter with effect of isolation transformer impedance is given by:

$$\omega_{res} = \frac{1}{\sqrt{\frac{L_g + L_c}{L_g L_c C + L_g L_f C + L_c L_f C_f}}}}$$

(3)

The capacitor  $C_f$  and the inductor  $L_f$  are tuned such that the trap resonant frequency is equal to the switching frequency of the VSI.

$$\omega_{Trap} = \frac{1}{\sqrt{(L_f C_f)}} \tag{4}$$

The base impedance of the active converter system can be calculated as  $Z_{base} = \frac{V^2}{P}$  and

base inductance is  $L_{base} = \frac{Z_{base}}{2\pi f}$  and base capacitance is  $C_{base} = \frac{1}{2\pi f Z_{base}}$ , where P is power rating of active converter, V is line to line voltage and the f is fundamental frequency.

## 3.2.2 Trap filter design

The Trap filter design algorithm is based on keeping the resonant frequency of the Trap filter including the isolation transformer away from fundamental as well as switching frequency. The  $L_f$  and  $C_f$  are tuned to the switching frequency. Considering the variation in isolation transformer impedance and the tolerance of the inductor, the Trap filter algorithm is given as below.

- Switching frequency, fundamental frequency, active converter ratings are the input arguments.

- Calculate base impedance, base inductance and base capacitance.

- Based on ripple current requirements, design the converter side inductor *L<sub>c</sub>*, which is usually between 6-9% of base impedance as per [28][29].

- Select the inductor  $L_f$  which is small percentage of  $L_c$  and calculate the capacitor  $C_f$  based on the switching frequency requirements.

- Based on applications, consider the minimum and maximum rating of the isolation transformer to be used for the active converter, and find its impedance and inductance in terms of percentage of the base impedance and inductance.

- Vary the isolation transformer inductance in small steps from minimum to maximum and find the resonance frequency. The resonance frequency must fall between limit lines set per design requirements, which is usually<sup>13f</sup> < ω<sub>res</sub> < 0.6f<sub>sw</sub>, in order to reduce the resonance issue because of the low frequency or switching frequency harmonics. The f is fundamental frequency and F<sub>sw</sub> is the switching frequency.

- If the above condition does not satisfy, increase  $L_f$  in small steps and repeat steps 4-6 until it fulfills the above requirement.

- If there are multiple options available, select the option which gives highest attenuation to the switching frequency component.

It is important to keep low tolerance of  $L_f$  and  $C_f$ , which provides more predictable filtering for switching frequency components. The above algorithm is implemented in Matlab with rated power of 125kW, line voltage of 480Vrms, fundamental frequency f=60Hz, and switching frequency 4 kHz. The Trap filter component values are calculated in terms of base inductance and base capacitance. In this design we consider the size of the isolation transformer to vary from 125kVA to 3MVA. Typically isolation transformer impedance is 6%, which means if we connect 125kVA active converter to 3MVA transformer, then effective inductance in series with Trap filter is 0.6% of base inductance of the VSI. The program based on the above algorithm provides optimum value of inductors and capacitors. The transfer function of the Trap filter without damping resistor is given by

$$\frac{i_{(s)}}{e_{(s)}} = \frac{S^2 L_f C_f + 1}{S^3 (L_g L_2 C + L_g L_f C_f + L_c L_f C_f) + S(L_g + L_c)}$$

(5)

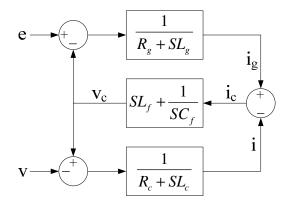

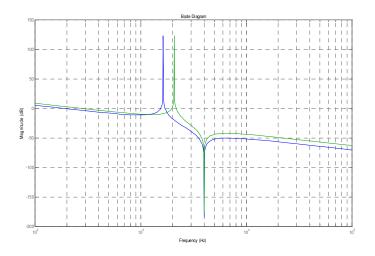

Figure 3.4 shows bode plot of the transfer function (TF) for minimum and maximum value of the isolation transformer inductance. For a minimum inductance equal to 0.6% of base inductance of active converter, the corresponding maximum resonance frequency is 2048Hz and gain is around 122dB, whereas for maximum inductance 6% of base inductance, corresponding minimum resonance frequency is 1633Hz and gain is around 122dB. Attenuation to switching frequency components (4 kHz) is around 180dB.

Figure 3.4 Bode plot of TF of Trap filter without damping

Transfer function of the Trap filter with damping resistor is as below.

$$\frac{\dot{i}_{(s)}}{e_{(s)}} = \frac{S^2 L_f C_f + S C_f R + 1}{S^3 (L_g L_c C_f + L_g L_f C_f + L_c L_f C_f) + S^2 (L_g + L_c) C_f R + S (L_g + L_c)}$$

(6)

Minimum and maximum resonance frequencies of Trap filter and attenuation for switching frequency components are shown in table 3.3 for R=0.01ohm resistor which is good approximation for ESR of capacitors and connection resistance. The corresponding bode plot for transfer function (6) is shown in figure 3.5. Various methods are proposed to damp the resonance in literature [28]-[29]. Table 3.3 shows the trap filter design parameters. It should be noted that with 6% source impedance, Trap filter provides 81dB attenuation to switching frequency components.

| 125k\ | 125kVA, 480Vrms, 60Hz Active converter with 4kHz switching frequency Trap filter design with R=0.010hm damping resistor |     |             |           |             |             |              |              |  |

|-------|-------------------------------------------------------------------------------------------------------------------------|-----|-------------|-----------|-------------|-------------|--------------|--------------|--|

| l     | Isolation transformer base inductance                                                                                   |     | Ls min=0.6% | Ls Max=6% | Ls min=0.6% | Lsmax =6%   |              |              |  |

| %L2   |                                                                                                                         | %L1 | %Lt         | %C        | Fres max Hz | Fres Min Hz | Atten max dB | Atten min dB |  |

|       | 9.0                                                                                                                     | 3.0 | 0.9         | 2.5       | 2048        | 1633        | -73.0        | -81.0        |  |

Table 3.3. Trap filter parameters

Figure 3.5 Bode plot of Trap filter with damping

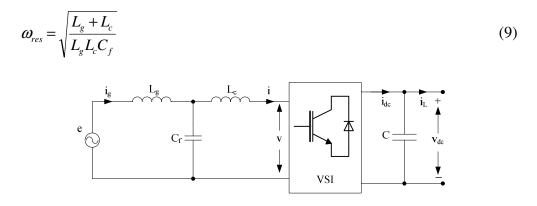

# 3.3 LCL filter analytical model and design algorithm

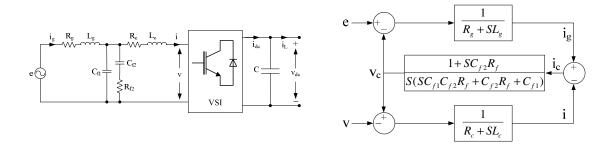

# 3.3.1 LCL filter configuration

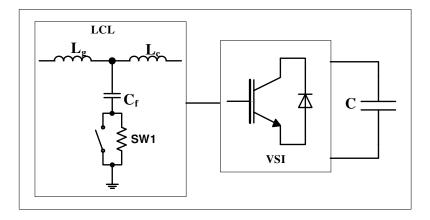

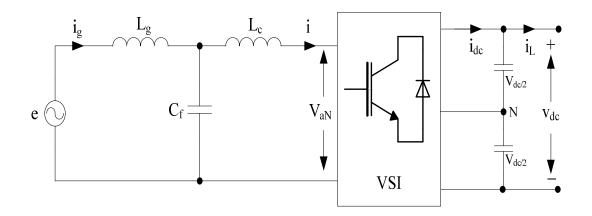

The LCL filter based 3L VSI is shown in figure 3.6. The  $L_g$  and  $L_c$  are grid side and VSI side inductances. Lg=L<sub>t</sub>+L<sub>1</sub>, where L<sub>t</sub> is the inductance of the isolation transformer and L<sub>1</sub> is inductance of the line side inductor. The capacitor  $C_f$  is connected in Y configuration.

Figure 3.6 3L NPC VSI with LCL filter

The Single phase equivalent circuit of the LCL filter is shown in figure 3.7. The damping resistor is ignored in mathematical model.

$$\frac{i_{g(s)}}{e_{(S)}} = \frac{S^2 L_c C_f + 1}{S[S^2 L_g L_c C_f + (L_g + L_c)]}$$

(7)

$$\frac{i_{(s)}}{v_{(S)}} = \frac{S^2 L_g C_f + 1}{S[S^2 L_g L_c C_f + (L_g + L_c)]}$$

(8)

The resonance frequency of LCL filter is given by

Figure 3.7 Single phase equivalent circuit for VSI with LCL filter

Figure 3.8 Block diagram for the LCL filter

## **3.3.2 LCL filter design algorithm**

The LCL filter design algorithm is also based on keeping the resonance frequency away from fundamental and switching frequency considering the variation in isolation transformer impedance and tolerance of the inductor. The algorithm is given as below:

- Switching frequency, fundamental frequency, VSI ratings are input arguments.

- Calculate base impedance, base inductance and base capacitance.

- Based on the ripple current requirement, design the converter side inductor, which is usually between 6-9% of base impedance as per [28][29].

- Select inductor L<sub>1</sub>, which is some percentage of L<sub>c</sub>. Total inductance should be less than 12% of base inductance in order to reduce the voltage drop across it. Also the cost of the inductor should be taken into consideration. Start with L<sub>c</sub>/L<sub>1</sub> ratio =3, as a good approximation.

- The capacitor decreases power factor. Generally, the maximum desired capacitor is around 5-6% of base capacitance [24]. Start the capacitance at 3% of base capacitance.

- Based on applications, consider the minimum and maximum rating of isolation transformers used for the active converter and find its impedance and inductance in terms of percentage of base impedance and inductance.

- Vary the isolation transformer inductance in small step from minimum to maximum and find the resonance frequency. Resonance frequency must fall between limit lines set as per design requirements which is <sup>13 f</sup> < ω<sub>res</sub> < 0.6 f<sub>sw</sub>.

- If the above condition does not meet the requirements, then increase  $C_f$  in small steps and repeat steps 6-7. If necessary reduce the  $L_c/L_1$  ratio and repeat steps 4-7.

- If there are multiple options available, select the option which gives highest attenuation to switching frequency component.

The above algorithm is implemented in Matlab. Using the same power rating as in the Trap filter section, the program gives us three different combinations. The values of highlighted row in table 3.4 are used for simulation and experiment purpose. Cost will be the driving factor for the selection of one of the combinations.

| 12  | 125kVA, 480Vrms, 60Hz Active converter with 4kHz switching frequency LCL filter Design with R=0.01ohm<br>damping resistor |     |    |             |             |              |              |  |

|-----|---------------------------------------------------------------------------------------------------------------------------|-----|----|-------------|-------------|--------------|--------------|--|

| lsc | Isolation transformer base inductance Ls min=0.6% Ls Max=6% Ls min=0.6% Lsmax =6%                                         |     |    |             |             |              |              |  |

| %   | L2                                                                                                                        | %L1 | %C | Fres max Hz | Fres Min Hz | Atten max dB | Atten min dB |  |

|     | 8                                                                                                                         | 3   | 6  | 1732        | 1201        | -35          | -46          |  |

|     | 9                                                                                                                         | 3   | 5  | 1789        | 1265        | -35          | -46          |  |

|     | 9                                                                                                                         | 3   | 6  | 1633        | 1155        | -37          | -47          |  |

Table 3.4. LCL filter parameters

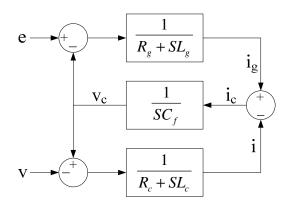

# **3.4 Effect of the source impedance**

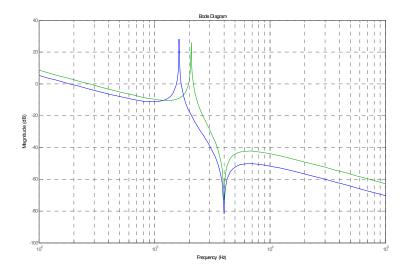

Figure 3.9 Bode plot of LCL filter with different source impedance

The source impedance has significant effects on the behavior of the Trap and LCL filter response. Bode plot of the LCL filter transfer function with different source impedance is shown in figure 3.9. It includes the source impedance as well as grid side inductance (3% L) of the LCL filter. One can observe that as source impedance increases, resonance frequency reduces [25]. If source is more than 20 times VSI rating then source

impedance is negligible compare to the grid side inductance. In this case the resonance frequency is 1.8 kHz. In contrary, if the VSI is connected to generator, in this case the source impedance is almost 5 times the grid side inductor of the LCL filter. The resonance frequency may drop to 1.1 kHz and the effective bandwidth of the control loop reduces significantly. If the control loop parameter is tuned based on just LCL filter without considering the source impedance, for any step change in load, VSI may go to the unstable mode. The information about source impedance is required for better tuning of the VSI control loop [30]-[32].

Figure 3.10 VSI's connected at same PCC

Even after considering the source impedance and tune the control loop of the VSI, there are some cases where the VSI control can't avoid resonance. One of the scenarios is shown in figure 3.10 where two drives are connected to the same PCC. One drive's switching frequency is overlapping to other drive's LCL resonance frequency. Active damping control techniques can be used to damp the resonance [33][34][40][41]. The active damping control algorithm is complex; it may pose additional issues if is not implemented properly. The only easy way to alleviate the problem is by adding passive damping circuit to the unit when a resonance is detected in the system. Passive damping of the LCL filter is discussed in detail later in this chapter.

### 3.5 Passive damping for LCL filters

The resonance of the LCL filter can be avoided by either an active damping or a passive damping technique. Passive damping is simple, easy to implement and guarantee work for all the time. Heat dissipation and space for the resistors are the only issues when dealing with the passive damping. Active damping requires complex control algorithm with higher sampling rate. Doesn't always guarantee work with all possible scenarios. Sometime active damping has adverse effects on overall control of the VSI. In this section, we will discuss possible topologies for the passive damping, its mathematical model and comparative result of the passive damping technique in terms of bode plot.

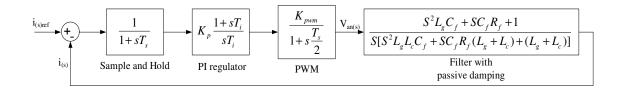

Figure 3.11Block diagram of LCL filter with series damping resistor

The simplest topology for the passive damping is series connected resistor  $R_f$  with filter capacitor  $C_f$ . The topology and a block diagram of LCL filter with series connected

resistor is shown in figure 3.11. The input and output admittances and transfer function are given by equations (10)-(12).

$$\frac{i_{g(s)}}{e_{(s)}} = \frac{S^2 L_c C_f + S C_f R_f + 1}{S[S^2 L_g L_c C_f + S C_f R_f (L_g + L_c) + (L_g + L_c)]}$$

(10)

$$\frac{i_{(s)}}{v_{(s)}} = \frac{S^2 L_g C_f + S C_f R_f + 1}{S[S^2 L_g L_c C_f + S C_f R_f (L_g + L_c) + (L_g + L_c)]}$$

(11)

$$\frac{i_{(s)}}{e_{(s)}} = \frac{SC_f R_f + 1}{S[S^2 L_g L_c C_f + SC_f R_f (L_g + L_c) + (L_g + L_c)]}$$

(12)

In order to reduce the heat dissipation in series connected resistor, another proposed topology is shown in figure 3.12. The filter capacitors are split in to two different capacitor banks. The  $C_{f1}$  is 4% capacitor bank and the  $C_{f2}$  is 1% capacitor bank. The damping resistor  $R_{f2}$  is connected in series with the  $C_{f2}$  capacitor bank. The block diagram of the passive damping technique is shown in figure 3.12. The mathematical model of the admittances and transfer function are given by equations (13)-(15).

Figure 3.12 Block diagram of LCL filter with Cf1 || [Cf2+Rf] damping

$$\frac{i_{g(s)}}{e_{(s)}} = \frac{S^3 L_c C_{f1} C_{f2} R_f + S^2 L_c (C_{f2} R_f + C_{f1}) + S C_{f2} R_f + 1}{S[S^3 L_g L_c C_{f1} C_{f2} R_f + S^2 L_g L_c (C_{f2} R_f + C_{f1}) + S C_{f2} R_f (L_g + L_c) + (L_g + L_c)]}$$

(13)

$$\frac{i_{(s)}}{v_{(s)}} = \frac{S^3 L_g C_{f1} C_{f2} R_f + S^2 L_g (C_{f2} R_f + C_{f1}) + S C_{f2} R_f + 1}{S[S^3 L_g L_c C_{f1} C_{f2} R_f + S^2 L_g L_c (C_{f2} R_f + C_{f1}) + S C_{f2} R_f (L_g + L_c) + (L_g + L_c)]}$$

(14)

$$\frac{i_{(s)}}{e_{(s)}} = \frac{S C_{f1} C_{f2} R_f + (C_{f2} R_f + C_{f1})}{S^3 L_g L_c C_{f1} C_{f2} R_f + S^2 L_g L_c (C_{f2} R_f + C_{f1}) + S C_{f2} R_f (L_g + L_c) + (L_g + L_c)}$$

(15)

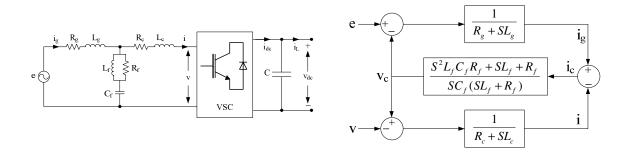

Another possible solution to reduce the heat dissipation in series connected resistor is shown in figure 3.13. The filter capacitor is series connected to parallel combination of a resistor and an inductor. The block diagram of this passive damping technique is shown in figure 3.13. The mathematical model of the transfer function and admittances are given by equations (16)-(18).

Figure 3.13 Block diagram of LCL filter with Cf+ [Lf || Rf] damping

$$\frac{i_{g_{(s)}}}{e_{(s)}} = \frac{S^{3}L_{c}L_{f}C_{f} + S^{2}C_{f}R_{f}(L_{c} + L_{f}) + SL_{f} + R_{f}}{S[S^{3}L_{g}L_{c}L_{f}C_{f} + S^{2}C_{f}R_{f}(L_{g}L_{c} + L_{g}L_{f} + L_{c}L_{f}) + SL_{f}(L_{g} + L_{c}) + R_{f}(L_{g} + L_{c})]}$$

(16)

$$\frac{i_{(s)}}{v_{(s)}} = \frac{S^{3}L_{g}L_{f}C_{f} + S^{2}C_{f}R_{f}(L_{g}L_{c} + L_{g}L_{f} + L_{c}L_{f}) + SL_{f} + R_{f}}{S[S^{3}L_{g}L_{c}L_{f}C_{f} + S^{2}C_{f}R_{f}(L_{g}L_{c} + L_{g}L_{f} + L_{c}L_{f}) + SL_{f}(L_{g} + L_{c}) + R_{f}(L_{g} + L_{c})]}$$

(17)

$$\frac{i_{(s)}}{e_{(s)}} = \frac{S^{2}L_{f}C_{f}R_{f} + SL_{f} + R_{f}}{S[S^{3}L_{g}L_{c}L_{f}C_{f} + S^{2}C_{f}R_{f}(L_{g}L_{c} + L_{g}L_{f} + L_{c}L_{f}) + SL_{f}(L_{g} + L_{c}) + R_{f}(L_{g} + L_{c})]}$$

(18)

For all the above topologies, bode plots analysis are performed. Figure 3.14 shows the bode plots of the different passive damping techniques with its configuration, resonance frequency and effective damping. It's quite obvious that without damping the LCL resonance peak can go as high as 132dB. With the series connected resistor (C-R), the resonance peak reduces to 30dB and attenuation at switching frequency component (4kHz) is maximum, For (C1||C2+R) and (C+L||R) topologies, the resonance peak remain same -0.2dB. The attenuation of switching frequency component is reduces significantly for (C1||C2+R) topology. The watt loss calculation table is shown below for 125kVA system. Table 3.5 shows that for configurations 1 and 3 the watt losses are very similar but very expensive to implement the configuration 3. The 2<sup>nd</sup> configuration provides lowest watt loss solution but implementation for delta configuration capacitor bank is very difficult from packaging point of view. Based on resonance damping, attenuation of switching frequency component, cost of implementation and packaging point of view topology 1 provides the best solution except heat dissipation, which can be easily solve by the energy efficient solution provided in next section.

|                                               | Result for 125kVA system |     |    |         |      |      |  |  |

|-----------------------------------------------|--------------------------|-----|----|---------|------|------|--|--|

| Configuration Value R C1 C2 / L IR (Amp) Watt |                          |     |    |         | Watt |      |  |  |

| 1                                             | C+R                      | 0.4 | 5% | -       | 15   | 90   |  |  |

| 2                                             | C1  C2+R                 | 8   | 4% | 1% (C2) | 2    | 32   |  |  |

| 3                                             | L  R +C                  | 0.5 | 5% | 2% (L)  | 13   | 84.5 |  |  |

Table 3.5. LCL passive damping technique comparison in terms of watt loss

Figure 3.14 LCL passive damping techniques comparison using bode plot

The energy efficient solution is shown in figure 3.15. The SW1 is in normally ON when there is no resonance, connects the filter capacitors in Y configuration without damping resistor. There is no additional watt loss across the resistor. When control system detects the resonance, SW1 allows putting the resistor in series with filter capacitor to help damping the LCL resonance.

Figure 3.15 LCL damping resistor switching circuit

## 3.6 Simulation and Experimental results

## 3.6.1 Simulation result of Trap filter

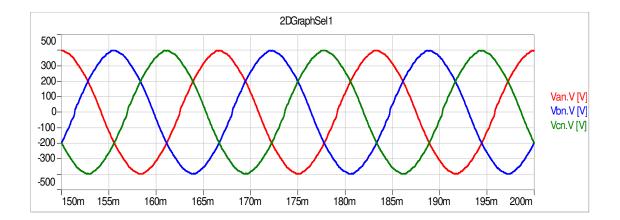

Voltage source inverter (125kW) connected to 2.5MVA 6% isolation transformer system is simulated using Simplorer software. The Trap filter inductors; capacitor and resistor values are shown in Table 3.3. Input phase to phase voltage and current waveforms are shown in figures 3.16 and 3.17.

Figure 3.16 Simulation result of Trap filter phase voltage

Figure 3.17 Simulation result of Trap filter phase currents

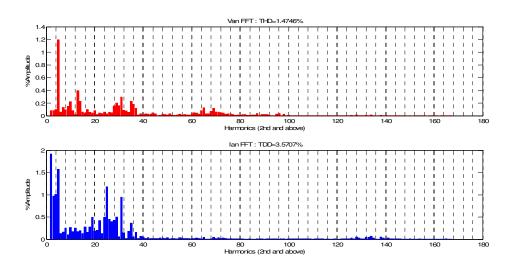

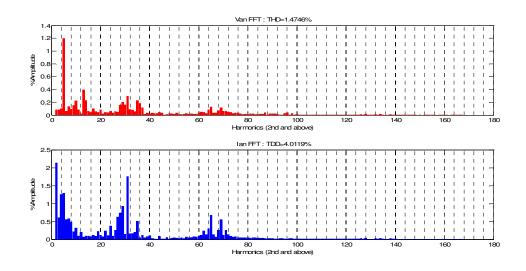

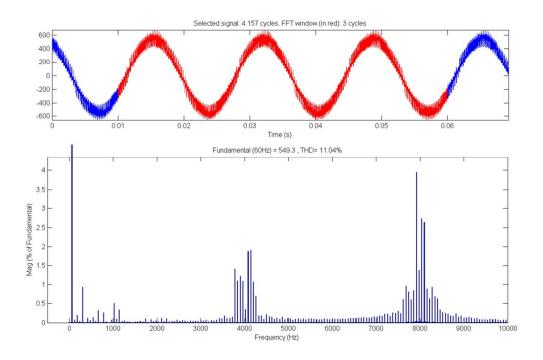

Phase to neutral voltage and phase current FFT are shown in figure 3.18. The THD of phase to neutral voltage is 1.4746% and the TDD is 3.5707%. There is minimum switching frequency component (4kHz) are observed in current FFT compare to 2<sup>nd</sup> order of switching frequency component (8kHz), this is because Trap filter is tuned for the 4kHz. Trap filter has minimum attenuation effect on 2<sup>nd</sup> and higher order harmonics of switching frequency components.

Figure 3.18 Simulation result of Trap voltage and currents FFT

## 3.6.2 Simulation result of LCL filter

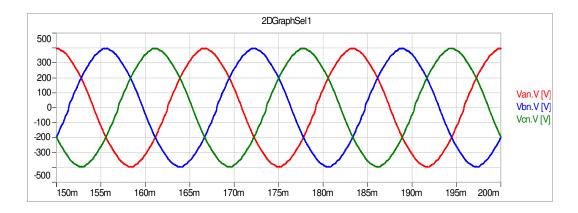

With the same setup as TRAP filter, the LCL system is simulated using Simplorer software. LCL filters inductors, capacitor and resistor values are shown in table 3.4. Input phase to phase voltage and current waveforms are shown in figure 3.19 and 3.20.

Figure 3.19 Simulation result of LCL filter phase voltage

Figure 3.20 Simulation result of LCL filter phase currents

The phase to neutral voltage and phase current FFT are shown in figure 3.21. The THD of phase to neutral voltage is 1.4746% and the TDD is 4.0119%. In phase current FFT graph, switching frequency components (4kHz) is very high compare to Trap filter. The  $2^{nd}$  and higher order harmonic components are attenuated significantly compare to Trap filter. It shows that LCL filter provides better attenuation for electro-magnetic interference at low frequency range (<500 kHz).

Figure 3.21 Simulation result of LCL filter voltage and currents FFT

## 3.6.3 Experimental result of Trap filter

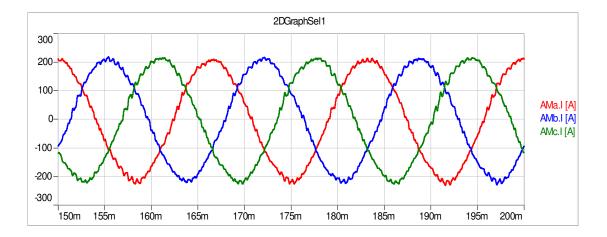

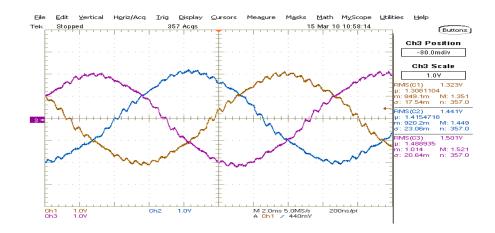

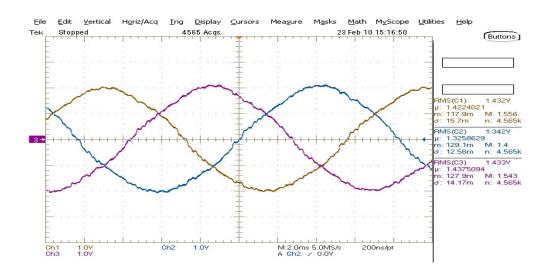

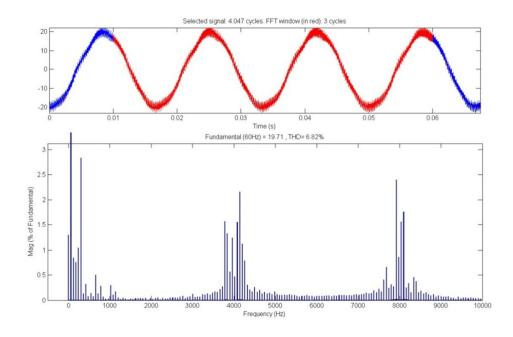

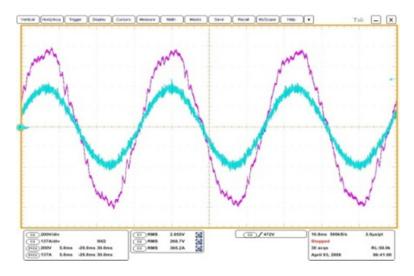

Figure 3.22 and 3.23 shows the experimental result of the 125kW active converter with Trap filter ran at full load and FFT analysis of phase voltage and line current of phase R. The measured voltage THD is 1.812% and the current TDD is 5.262%.

Figure 3.22 Trap filter full load phase currents

Figure 3.23 Trap filter FFT of phase R voltage and phase current

# 3.6.4 Experimental result LCL filter

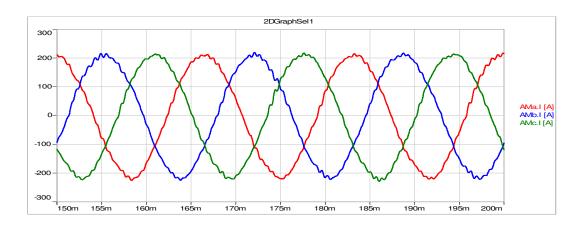

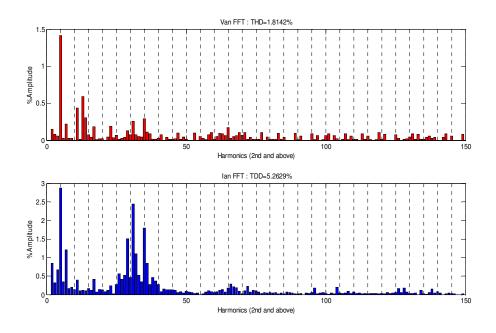

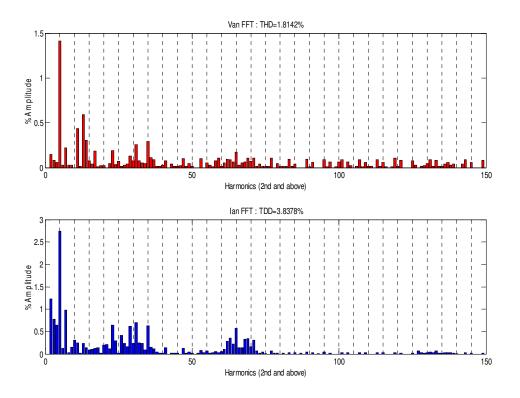

Figure 3.24 LCL filter full load measurement of phase currents

Figure 3.25 LCL filter FFT of phase R voltage and phase current

Figure 3.24 and 3.25 shows the experimental result of the 125kW active converter with LCL filter ran at full load and FFT analysis of phase voltage and the line current of phase R. The measured voltage THD is 1.814% and the current TDD is 3.837%. The attenuation of the switching frequency component (4 kHz) is not as high as Trap filter but the higher attenuation of the  $2^{nd}$  order switching frequency component (8 kHz) is achieved compare to Trap filter. The drive is connected to a 2.5MV transformer in both cases. The *I<sub>SC</sub>/I<sub>L</sub>* ratio is 139 which means it requires less than 15% current TDD to meet the IEEE standard 519 specification. The THD and the TDD results are higher than simulation results because the base line voltage measurements had higher fifth harmonic

components. The experimental results of TRAP and LCL filters show that both filters pass IEEE 519 requirements.

## 3.7 Comparison of Trap and LCL filters

The Trap filter provides better attenuation of the switching frequency components. It provides better performance for a generator as a source and during line dip conditions. The Trap filter is effective for audible noise reduction when it is connected to an isolation transformer. A 3% reactor could be optional depending upon application. The Trap filter has less attenuation at higher frequency. The Trap filter required very tight tolerance of the *LC* tuned circuit to effectively filter the switching frequency component. The cost of the *LC* tuned circuit will be higher. The LCL provides higher attenuation at higher frequency and will be effective in electromagnetic compliance. Higher L and C tolerance will be acceptable. The LCL is not as effective as Trap filter for switching frequency component filtering.

### 3.8 Conclusion

In this chapter the TRAP and the LCL filters mathematical models are discussed in detail. The optimum design algorithms for the TRAP and the LCL filters are presented. The effects of the grid impedance or isolation transformer are discussed in detail and used the information to design the TRAP and the LCL filters. The algorithms are implemented in MATLAB. The resonance issues with LCL filter are discussed in depth and different topologies for the passive resonance damping for the LCL filter are presented. The pros and cons of each passive damping topology are compared. The TRAP and the LCL filters for 125kW converters are designed using optimum design algorithm. The design has been tested in simulation and with an experimental setup. Simulation result as well as experimental result shows that both filters meet the IEEE 519 voltage THD and current TDD limits. In next chapter we will discussed the VSI for the MVDC application. Selection of a topology and the control algorithm is presented in detail.

#### 4. Voltage source inverter

### **4.1 Introduction**

With advancement in silicon technology, the higher voltage self-commutated switching devices are available in market, which enables to supports higher power medium voltage converters for the MVDC system. Depending up on the dc-link energy storage component, the medium voltage converters are classified into a current-source and voltage-source topologies. The voltage source inverters (VSI) are increasingly popular for the MVDC application. The VSI can be further classified in multiple topologies like multi-level converters, flying capacitors and cascade H-bridge [37]-[39]. The VSI operates with higher switching frequencies generally in range of 2 kHz – 4 kHz, reduces the input LCL filter size. This leads to reduce the overall size of the power conversion unit.

### **4.2 Selection of topology**

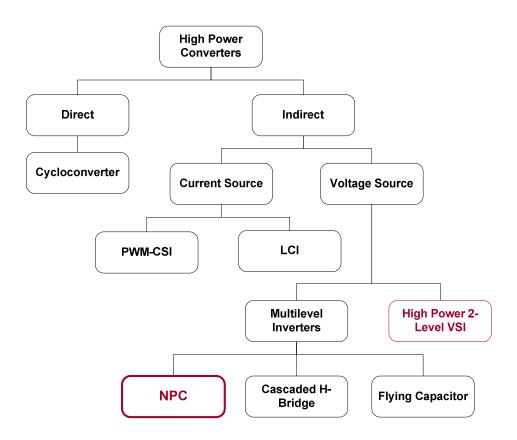

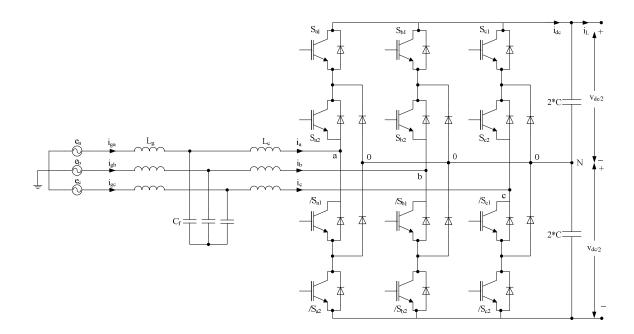

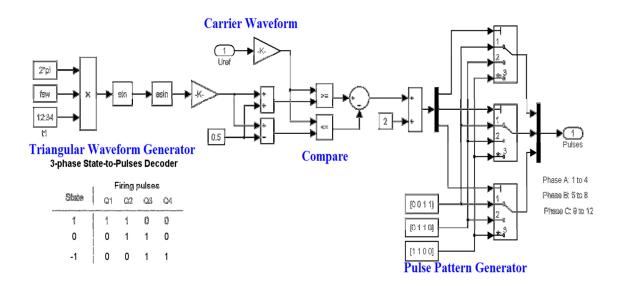

The high power converter classification is shown in figure 4.1. The cycloconverter is fall under the bi-direction conversion without DC link. The indirect conversion have DC link between the inverter and the converter. The current source converters have more harmonics and lower power factor compare to voltage source inverters. The voltage source inverters are further classified in to multi-level inverters and high power 2-Level inverters. The multi-level voltage source converters are classified

into three different categories like 3-level neutral point clamp (NPC), cascade H-bridge (CHB) and Flying capacitors. The control for the flying capacitor topology is complex compare to 3-level NPC converter. In addition, it's more expensive because low switching frequency makes clamping capacitor large and an excessive number of capacitors used for the clamping.

Figure 4.1 Classification for high power converters

The disadvantages of the cascade H-bridge are the separate dc sources and a nonstandard transformer. The 3-level NPC provides higher quality output voltage and current waveform results in reduced output filter size and cost compare to two level inverter. Only half of the DC bus voltage has to be switched leads to reduced switching losses

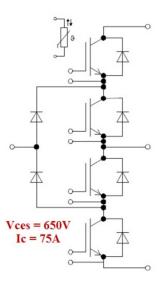

compare to 2-level inverter. The control loop is easy to implement. With the availability of IGBT modules of 3.3kV, 4.5kV and 6.6kV rating makes the 3-Level NPC topology very popular for MVDC (2.3kV-4.6kV) applications [37].

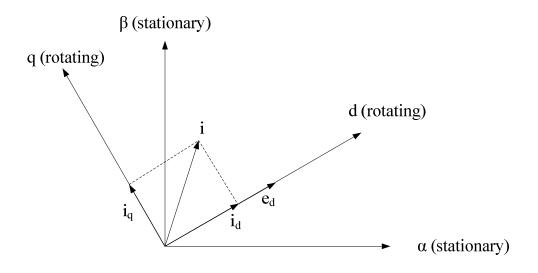

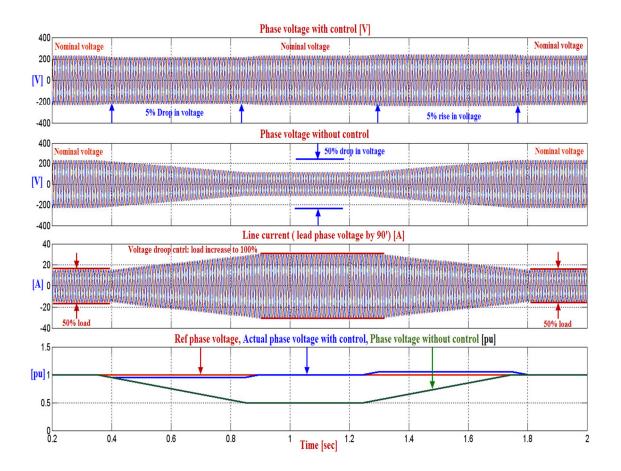

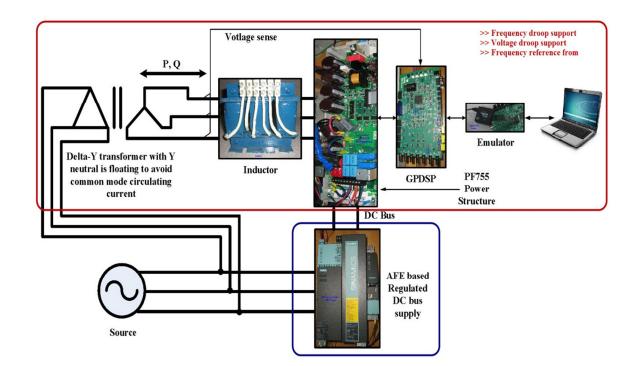

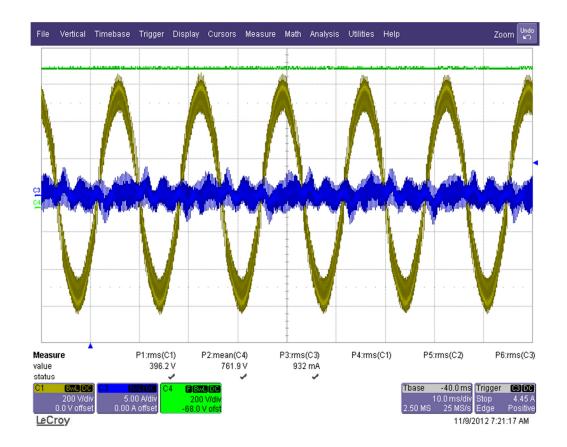

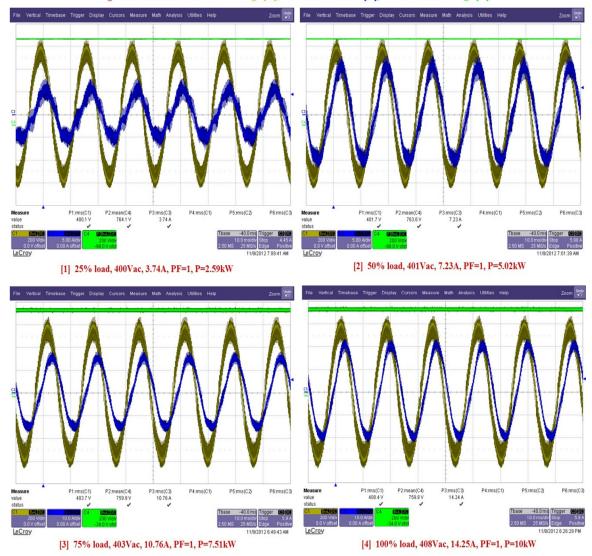

## Summary of the advantages of the 3L NPC as below: