## The University of Maine DigitalCommons@UMaine

**Electronic Theses and Dissertations**

Fogler Library

2001

# Asynchronous Validity Resolution in Sequentially Consistent Shared Virtual Memory

Jonathan Thomas

Follow this and additional works at: http://digitalcommons.library.umaine.edu/etd Part of the <u>Computer Sciences Commons</u>

**Recommended** Citation

Thomas, Jonathan, "Asynchronous Validity Resolution in Sequentially Consistent Shared Virtual Memory" (2001). *Electronic Theses and Dissertations*. 221. http://digitalcommons.library.umaine.edu/etd/221

This Open-Access Dissertation is brought to you for free and open access by DigitalCommons@UMaine. It has been accepted for inclusion in Electronic Theses and Dissertations by an authorized administrator of DigitalCommons@UMaine.

# ASYNCHRONOUS VALIDITY RESOLUTION IN SEQUENTIALLY CONSISTENT SHARED

### VIRTUAL MEMORY

By

Jonathan Thomas B.S. University of Vermont, 1995

M.S. University of Maine, 1998

#### A THESIS

Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy (in Computer Science)

> The Graduate School The University of Maine May, 2001

Advisory Committee:

James L. Fastook, Associate Professor of Computer Science, Advisor Larry Latour, Associate Professor of Computer Science Thomas Wheeler, Assistant Professor of Computer Science Thomas Wagner, Assistant Professor of Computer Science Fei Chai, Assistant Professor of Marine Sciences

## LIBRARY RIGHTS STATEMENT

In presenting this thesis in partial fulfillment of the requirements for an advanced degree at The University of Maine, I agree that the Library shall make it freely available for inspection. I further agree that permission for "fair use" copying of this thesis for scholarly purposes may be granted by the Librarian. It is understood that any copying or publication of this thesis for financial gain shall not be allowed without my written permission.

Signature:

Date:

## Asynchronous Validity Resolution in Sequentially Consistent Shared Virtual Memory

By Jonathan Thomas

Thesis Advisor: Dr. James L. Fastook

An Abstract of the Thesis Presented in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy (in Computer Science) May, 2001

Shared Virtual Memory (SVM) is an effort to provide a mechanism for a distributed system, such as a cluster, to execute shared memory parallel programs. Unfortunately, SVM has performance problems due to its underlying distributed architecture. Recent developments have increased performance of SVM by reducing communication. Unfortunately this performance gain was only possible by increasing programming complexity and by restricting the types of programs allowed to execute in the system.

Validity resolution is the process of resolving the validity of a memory object such as a page. Current SVM systems use synchronous or deferred validity resolution techniques in which user processing is blocked during the validity resolution process. This is the case even when resolving validity of false shared variables. False-sharing occurs when two or more processes access unrelated variables stored within the same shared block of memory and at least one of the processes is writing. False sharing unnecessarily reduces overall performance of SVM systems because user processing is blocked during validity resolution although no actual data dependencies exist.

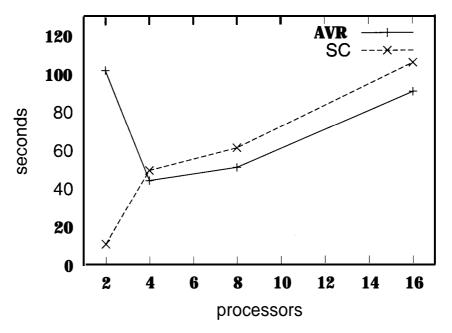

This thesis presents Asynchronous Validity Resolution (AVR), a new approach to SVM which reduces the performance losses associated with false sharing while maintaining the ease of programming found with regular shared memory parallel programming methodology. Asynchronous validity resolution allows concurrent user process execution and data validity resolution. AVR is evaluated by comparing performance of an application suite using both an AVR sequentially consistent SVM system and a traditional sequentially consistent (SC) SVM system. The results show that AVR can increase performance over traditional sequentially consistent SVM for programs which exhibit false sharing. Although AVR outperforms regular SC by as much as 26%, performance of AVR is dependent on the number of false-sharing vs. true-sharing accesses, the number of pages in the program's working set, the amount of user computation that completes per page request, and the internodal round-trip message time in the system. Overall, the results show that AVR could be an important member of the arsenal of tools available to parallel programmers.

### ACKNOWLEDGEMENTS

I would like to thank my wife, Kris, for her support of me and my Ph.D efforts. Although I am grateful for her understanding, patience, and tolerance for the many late nights that I worked, I am especially appreciative of her continuous support of my educational goals. I thank her for helping me finish my Bachelor's and for supporting me in the earning of both my Master's and Ph.D. degrees.

I would like to thank my parents, Tom and Judy Thomas, for support of my educational endeavors. Their support, among other things, allowed me to earn a Bachelor's, an educational foothold for my Master's and ultimately my Ph.D.

I would like to thank my advisor, James Fastook, for allowing me to pursue this problem, for supporting my work, and for offering invaluable insights when the problem seemed most difficult. I would like to thank my committee members, Larry Latour, Thomas Wheeler, Thomas Wagner, and Fei Chai for their guidance, willingness to help, and commitment. I thank Larry Latour and Tom Wheeler for their suggestions on transactions and software engineering. I am grateful to Tom Wagner for his help with my proposal and for helping me through the process. I thank Fei Chai for allowing me to be part of the University of Maine Beowulf Project. Without access to the Beowulf machine, this work may not have been possible.

I would like to thank the Computer Science Department for support of my graduate work and for starting the Ph.D. program. Particularly, I would like to thank George Markowsky for 17 years of relentless effort toward the evolution of the department and development of the new program. As the first Computer

Science Ph.D. student at The University of Maine, I am grateful for the efforts of the department in helping me navigate my graduate career.

## **TABLE OF CONTENTS**

| ACKNOWLEDGEMENTS | ii   |

|------------------|------|

| LIST OF TABLES   | viii |

| LIST OF FIGURES  | ix   |

## Chapter

| 1 INTRODUCTION |                               |    |

|----------------|-------------------------------|----|

| 1.1            | Shared Virtual Memory         | 4  |

| 1.2            | Cache Consistency             | 6  |

| 1.3            | Granularity and Fragmentation | 9  |

| 1.4            | Consistency Models            | 11 |

|                | 1.4.1 Sequential Consistency  | 12 |

|                | 1.4.2 Processor Consistency   | 13 |

|                | 1.4.3 Weak Consistency        | 13 |

|                | 1.4.4 Release Consistency     | 14 |

|                | 1.4.5 Entry Consistency       | 15 |

|                | 1.4.6 Scope Consistency       | 16 |

| 1.5   | Protocols                                          | 17 |

|-------|----------------------------------------------------|----|

|       | 1.5.1 Generalized SC Protocols                     | 17 |

|       | 1.5.2 Optimistic Protocol                          | 21 |

|       | 1.5.3 Reduced Granularity Protocols                | 22 |

|       | 1.5.4 Lazy Protocols                               | 23 |

|       | 1.5.5 Home-Based Protocols                         | 24 |

|       | 1.5.6 Adaptive Protocols                           | 25 |

| 1.6   | Architectural Support                              | 26 |

|       | 1.6.1 Broadcast and Multicast Protocols            | 26 |

|       | 1.6.2 Network Support and SMP Clusters             | 28 |

| 1.7   | Application Support                                | 29 |

|       | 1.7.1 Compiler Transformations and Instrumentation |    |

|       | 1.7.2 Transparency                                 |    |

| 1.8   | Thesis                                             | 32 |

| 1.9   | Contributions                                      |    |

| 2 ASY | NCHRONOUS VALIDITY RESOLUTION                      |    |

| 2.1   | Motivation and Background                          |    |

| 2.2   | Protocol                                           |    |

| 2.3   | System                                             | 41 |

|       | 2.3.1 Sequential Consistency                       | 42 |

|       | 2.3.2 AVR                                          | 45 |

|       | 2.3.3 Checkpointing                                | 46 |

|       | 2.3.4 Memory Mechanisms                            | 47 |

|               | 2.3.5 N       | Nessage Handling                  |    |

|---------------|---------------|-----------------------------------|----|

|               | 2.3.6 T       | Timers, Locks, and Barriers       |    |

|               | 2.3.7 E       | Dependency Checking and Rollbacks |    |

|               | 2.4 Correctn  | ess                               |    |

|               | 2.5 Limitatio | Dns                               |    |

|               | 2.6 Summar    | у                                 |    |

| 3             | PERFORM       | ANCE                              |    |

|               | 3.1 Experim   | ental Environment                 | 60 |

|               | 3.1.1 H       | Hardware Platform                 | 60 |

|               | 3.1.2 E       | Basic Operation Costs             | 61 |

|               | 3.2 Applicat  | ion Suite                         | 61 |

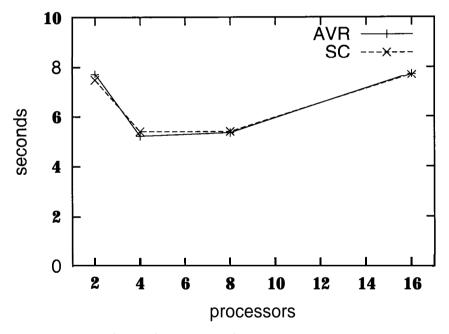

|               | 3.2.1         | Water                             | 64 |

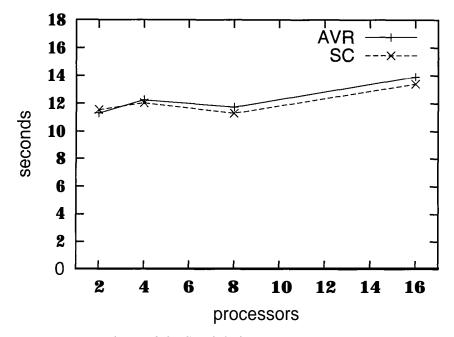

|               | 3.2.2         | Spatial                           | 64 |

|               | 3.2.3         | LU Decomposition                  |    |

|               | 3.2.4         | Raytrace                          | 65 |

|               | 3.2.5         | Volrend                           | 66 |

|               | 3.2.6         | FFT                               | 66 |

|               | 3.2.7         | Ocean                             | 67 |

|               | 3.2.8         | Radix                             | 67 |

|               | 3.2.9         | Matmul                            | 67 |

| 3.2.10 Jacobi |               | 68                                |    |

|               | 3.2.11        | Gauss                             | 68 |

|               | 3.2.12        | Diversity                         | 69 |

| 3.3 Results                   | 70    |

|-------------------------------|-------|

| 3.3.1 Timings                 | 70    |

| 3.3.2 Discussion              | 87    |

| 3.3.3 Validation of Claims    | 93    |

| 4 Conclusions and Future Work | 96    |

| 4.1 Conclusions               | 96    |

| 4.2 Future Work               | 97    |

| BIBLIOGRAPHY                  | . 100 |

| BIOGRAPHY OF THE AUTHOR       | . 108 |

## LIST OF TABLES

| 3.1 Application Sharing Patterns       | 62 |

|----------------------------------------|----|

| 3.2 Application Input Sizes            | 69 |

| 3.3 Water 4 CPU 100 Run Test Case Data | 70 |

| 3.4 Matmul 1024x1024 Timing Data       | 82 |

| 3.5 Matmul 1013x1013 Timing Data       | 82 |

# LIST OF FIGURES

| 1.1 Shared Memory Abstraction                            | 4    |

|----------------------------------------------------------|------|

| 1.2 Shared Virtual Memory[ 20]                           | 5    |

| 1.3 Validity Checking                                    | 7    |

| 1.4 False-Sharing                                        | 10   |

| 1.5 Consistency Models and Protocols (adapted from [20]) | . 11 |

| 1.6 Sequential Consistency                               | 12   |

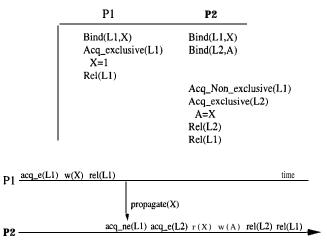

| 1.7 Release Consistency                                  | . 14 |

| 1.8 Entry Consistency                                    | 15   |

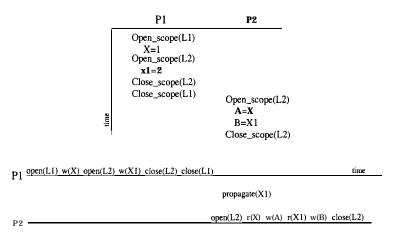

| 1.9 Scope Consistency                                    | 16   |

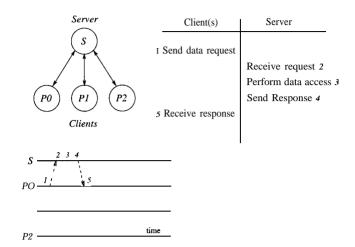

| 1.10 Central Server                                      | 18   |

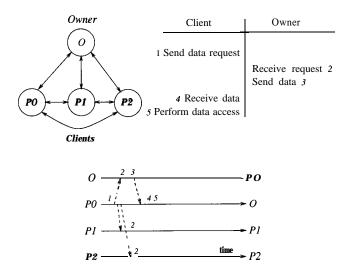

| 1.11 Migration                                           | 19   |

| 1.12 Read Replication                                    | 20   |

| 1.13 Full Replication                                    | 21   |

| 1.14 ToRiS: Optimistic Full Replication                  | 22   |

|                                                          | 40   |

| 2.1 Validity Resolution Interval                         | 40   |

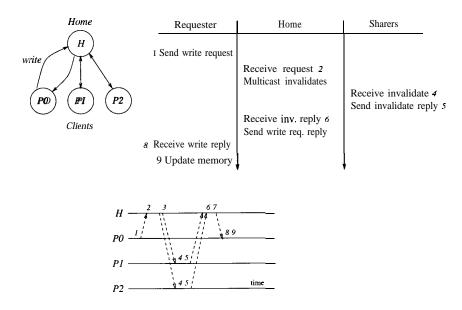

| 2.2 SC System.                                           | 42   |

| 2.3 Checkpointing                                        | 46   |

|                                                          |      |

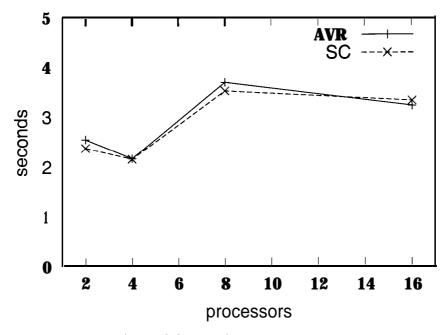

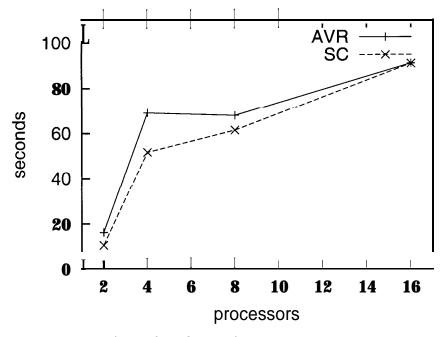

| 3.1 Water time vs. #processors                | 71   |

|-----------------------------------------------|------|

| 3.2 Spatial time vs. #processors              | . 72 |

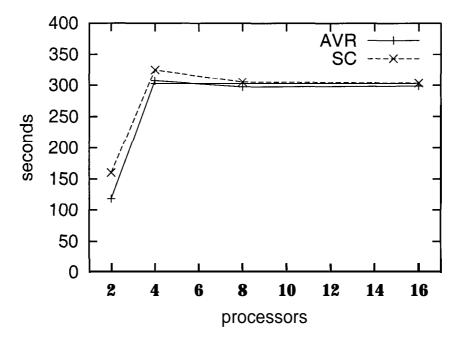

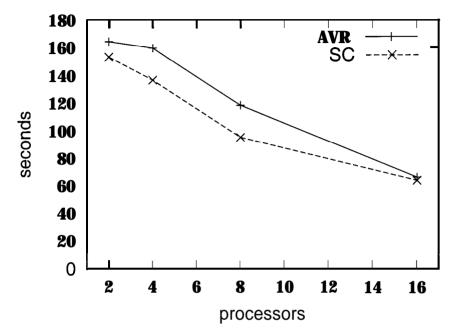

| 3.3 LU time vs. #processors                   | . 73 |

| 3.4 Raytrace time vs. #processors             | . 74 |

| 3.5 Volrend time vs. #processors              | . 76 |

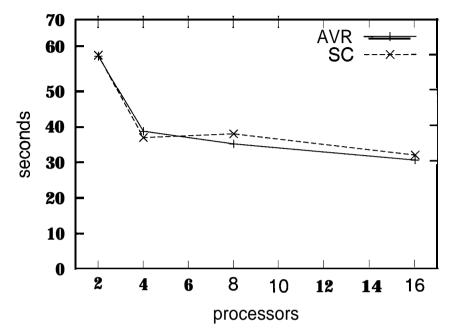

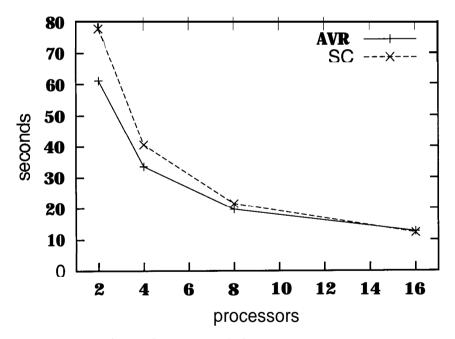

| 3.6 FFT time vs. #processors                  | 77   |

| 3.7 Ocean time vs #processors                 | . 78 |

| 3.8 Radix time vs. #processors                | . 79 |

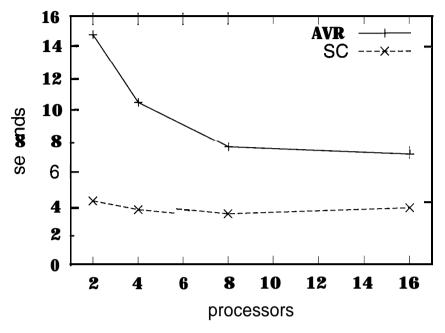

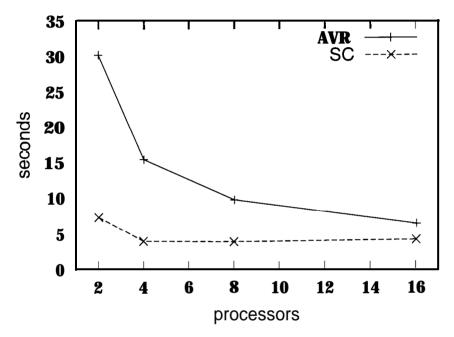

| 3.9 Matmul time vs. #processors               | 81   |

| 3.10 Jacobi time vs. #processors              | . 83 |

| 3.11 Gauss time vs. #processors               | 84   |

| 3.12 SC Resolution Interval                   | . 86 |

| 3.13 AVR Resolution Interval Without Rollback | . 87 |

| 3.14 AVR Resolution Interval with Rollback.   | . 89 |

# Chapter 1

# INTRODUCTION

Cluster based computing has become increasingly popular due to the availability of low cost off-the-shelf computer components. Advances in technology have allowed clusters composed of off-the-shelf hardware to perform similarly to expensive modern shared-memory supercomputers. Hence, clusters are attractive platforms for production and research. The problem is that clusters have a distributed-memory architecture and distributed-memory programming, i.e. message passing, is more difficult than shared-memory programming. In the distributed-memory programming paradigm, the programmer must manage data flow across processors by using explicit messaging constructs. In contrast, the shared-memory programming paradigm allows common areas of memory to be accessed by multiple processors, such that shared information can be passed by reference. Shared Virtual Memory (SVM) is an effort to provide a shared memory programming paradigm over a distributed memory architecture.

A memory consistency model of a shared-memory multiprocessor provides a formal specification of how the memory system will appear to the programmer, eliminating the gap between the behavior expected by the programmer and the actual behavior of the system [2]. Caching is a mechanism which serves to provide locality to a processing unit. A cache consistency model, sometimes called a cache coherence model, is a specification which ensures that the view of memory maintained across all caches allows the correct execution of programs. Shared Virtual Memory emulates shared memory cache consistency in a distributed memory system. A SVM employs a memory consistency model, such as Sequential Consistency (SC) [32], to ensure the proper execution of programs in the distributed system. Unfortunately, consistency in a distributed system has considerable performance costs. These costs are related to the number of messages required to synchronize distributed memories [12]. Consistency costs are a barrier to SVM performance since consistency maintenance occurs inline in relation to user processing. This means that a process must block while permission to a memory object is requested and received. The database community, when referring to transaction processing, classifies this process as synchronous validity checking if the permission request occurs inline before transaction processing. If the permission request is performed inline after transaction processing, it is called *deferred* validity checking. Synchronous validity checking is a pessimistic approach which has been observed to have a high cost of consistency [12]. Deferred validity checking works well with transactions, but has problems when applied to SVM. It requires extra effort on behalf of the programmer for correct program execution in SVM. Deferred validity checking in SVM requires global synchronization of memory accesses which introduces a performance bottleneck and limits the amount of parallelism in a program's execution.

This thesis proposes the use of asynchronous validity resolution (AVR) in sequentially consistent SVM. Asynchronous validity resolution is a semi-optimistic protocol, analogous to asynchronous validity checking, in which computation overlaps the communication request for memory access permission. Asynchronous validity resolution is of interest because it has the capability of reducing the effect of false-sharing. False-sharing occurs when two or more processors access variables located on the same block of memory and at least one of the processors is writing. Typically, the false-shared block of memory is an operating system level page structure. Asynchronous validity resolution allows a process to continue with computation using potentially invalid data while permission to access the memory location is sent and received. When access permission is received and the SVM determines that the data is false-shared, computation can continue. If the SVM determines that the data is not false-shared, the requesting process must rollback to the state at the time of the invalid memory access. Implementation of AVR involves time and storage space overhead. Process checkpointing, memory page comparisons, and rollbacks are required to be performed. Although this approach has substantial overhead, it improves the performance of sequential consistency SVM for some applications by reducing the negative performance effects that are inherent to the SVM design. Specifically, AVR increases performance for applications which have high ratio of false-shared to true-shared memory accesses and applications which perform a large amount of user computation relative to the time required for memory resolution.

## **1.1 Shared Virtual Memory**

Message passing and shared-memory are two parallel programming models that provide mechanisms for data to be shared among processes. The message passing model is the most versatile, because it can be used with both shared-memory multiprocessors and distributed systems. The caveat is that the message passing model is difficult to program, since the communication layer is visible to the programmer. The shared-memory paradigm, an extension of uniprocessor program-

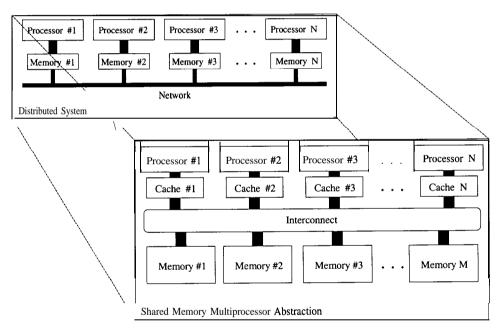

Figure 1.1: Shared Memory Abstraction

ming methodology, provides an intuitive and easy programming model. Unfortunately, the shared-memory model does not extend readily to distributed systems. Shared Virtual Memory is an effort to provide a shared memory programming model with message passing performance characteristics in a distributed environment.

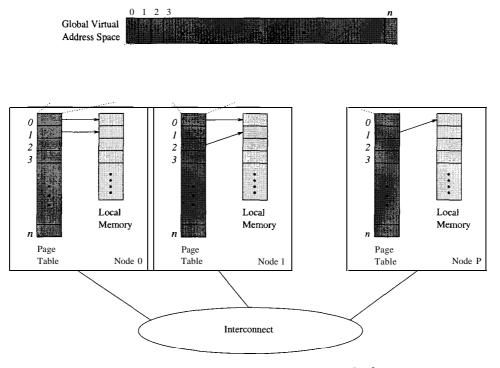

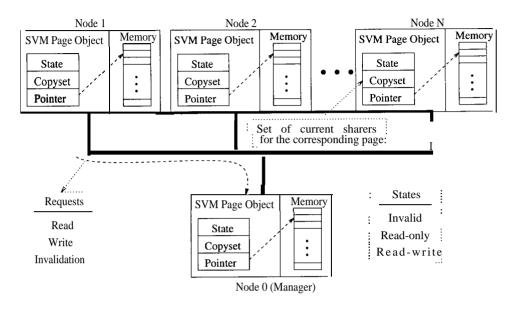

Figure 1.2: Shared Virtual Memory[20]

Shared Virtual Memory was first proposed in 1986 by Kai Li [35]. Shared Virtual Memory provides an abstraction of shared memory architecture (Figure 1.1) and emulates caching in cache-coherent multiprocessors [34]. In the cache-coherent multiprocessor architecture, caches provide local access to a global address space. In SVM, local memory acts as a cache of a global virtual address space. See Figure 1.2. Memory consistency is maintained by using consistency mechanisms, similar to those used in cache-coherent multiprocessors. Each node has a page table with an entry for each page of global virtual address space. Entries can either be valid or invalid. A valid entry signifies that the global page is cached in local memory and maps the global address to the address of the local cached page. An invalid entry signifies that the page has never been cached or

that the cached page is invalid. A page fault occurs when attempting to access an invalid page. The SVM system is responsible for memory consistency and must respond to page faults by fetching new copies of pages from remote sources.

The following sections outline some fundamental concepts of shared virtual memory such as caching and granularity. The later sections, starting with Section 1.4, provide an overview of the major advancements in the SVM field describing research efforts centered on memory consistency models, consistency protocols, architectural support mechanisms, and application support methodologies.

## **1.2 Cache Consistency**

Optimal multiprocessing in a shared memory system requires some mechanism, such as caching, to provide locality. Caching allows multiple processing units to concurrently access replicated shared memory objects. The cache consistency mechanism controls concurrent access to the shared memory objects such that the allowed order of memory operations provides for the correct execution of programs. The database community has dissected cache consistency into four main categories[12]. They are *invalid access prevention, write validity checking, write permission duration,* and *remote update action.*

*Invalid access prevention* denotes how the consistency algorithm maintains the caches. In detection based algorithms, the cache is validated before performing an operation. In avoidance based algorithms, the cache is maintained in an up-to-date state. Avoidance based algorithms tend to perform better in small systems. Their performance degrades as system size and number of messages increases. Clearly,

the use of a page table in an SVM is a detection based mechanism, since the entry in the page table is tested for validity. Pre-fetching is a type of avoidance, since it acts to cache pages before they are required for use.

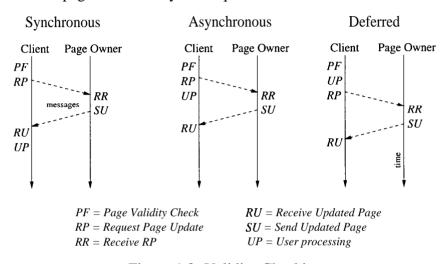

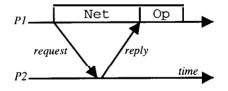

Figure 1.3: Validity Checking

Write validity checking is the process of obtaining write permission from the concurrency control, the server of the memory object. Write validity checking, as shown in Figure 1.3, has been subdivided into three categories called synchronous, asynchronous, and deferred. Synchronous Validity Checking means that the process obtains write permission prior to transaction processing. Deferred Validity Checking is the opposite of synchronous write declaration with write declaration occurring at the point when the transaction commits. Asynchronous Validity Checking is the process when write validity checking is referred to as pessimistic, while deferred validity checking is referred to as optimistic. The main disadvantage to the pessimistic approach is a higher cost of consistency than that of the optimistic approach [12]. The disadvantage of the optimistic approach is the

late detection of data conflicts which cause a transaction abort. In the database domain, the choice between synchronous and deferred methods is a trade-off in the number of messages sent and the transaction abort rate [12]. Asynchronous validity checking seeks to minimize the cost of consistency and to discover conflicts earlier in the transaction execution. Although programs usually are not described in terms of transactions, nearly all SVM systems use a process similar to synchronous validity checking where write permission is received before the write occurs. The system which this dissertation proposes is asynchronous validity resolution (AVR). AVR is different from asynchronous validity checking because AVR allows a program to use data that is marked as invalid while data validity resolution occurs. Additionally, AVR does not require a program to be broken into distinct transactions.

*Write duration* is the length of time for which write permission is given to a cached object. Write duration can be inter-transactional or *intratransactional*. Intertransactional write duration means that write permissions, unless revoked by the server, do not have to be reacquired for a series of transactions which use the same cached objects. Intratransactional write duration means that the cached object is only valid for the lifetime of the caching transaction. Write duration in SVM is defined by the pattern of sharing. Write permission usually only extends to the lifetime of the process with some type of writeback occurring at the end of execution.

*Remote update action* refers to how the updates are handled in the system. Propagation of the update means that the update is installed at each remote site. Invalidation means that old remote copies are marked as invalid. As the number of nodes in the system increases, the messages required for the propagation of updates degrades overall system performance considerably. In general, invalidation tends to perform much better than propagation, except in a fixed single-writer multiple-reader configuration [9]. Invalidation is typically used in SVM systems because the pattern of memory access in unknown and the cost of communication within the system is high. Invalidation makes page acquisition demand-based and minimizes unnecessary overhead for the writing process.

In distributed client-server transaction processing, avoidance based algorithms using deferred write declaration, intertransactional caching, and a dynamic update action perform better than other algorithms using different combinations of features. Although SVMs present a different environment than database transaction processing, SVMs may benefit from application of some of these cache consistency techniques.

## 1.3 Granularity and Fragmentation

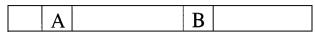

Granularity refers to the size of the shared memory blocks used in the system. Common granularities are byte, word, page or complex data type (object). Granularity size has many trade-offs and is an important issue, since it effects the overall performance of the system. Applications have inherent memory sharing patterns and memory access granularity determined by algorithm design. Use of an SVM with a mismatched granularity causes the program to have an induced memory sharing pattern [22]. Small granularity creates additional directory overhead and increased message traffic, but reduces the potential for false-sharing. False-sharing

Page of Memory

Figure 1.4: False-Sharing

occurs when two or more processes use disjoint sets of variables that are stored in the same block of memory and at least one of the processors is writing (see Figure 1.4). False-sharing is a cause of the ping-pong effect in which a page of memory is repetitively sent from one processor to another with only a minimal amount of work actually being done. False-sharing, in synchronous validity resolution, results in a process having to block on a page fault until an updated page is obtained. This burdens the system with unnecessary performance loss, since parallel processing cannot occur even though no actual sharing is taking place. Fragmentation occurs when a page is fetched in response to a fault on a single word of memory. Fragmentation breaks a processing unit's locality of reference. Locality of reference is the affinity for some working set of data objects. In general, large granularity has reduced directory overhead and provides locality of reference for a processing unit, but introduces a greater potential for false sharing.

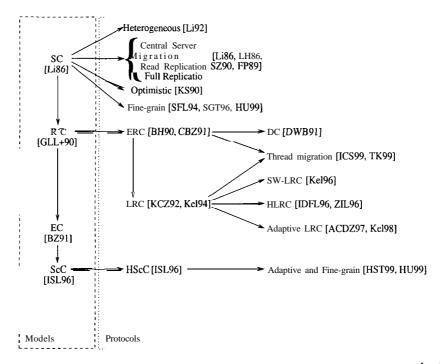

Figure 1.5: Consistency Models and Protocols (adapted from [20])

In practice, the choice of sharing size usually reflects what is implemented on the platform, typically a page of memory. Small granularities, such as words or cache lines, are rarely used due to high overhead except in systems with some hardware support. Many efforts in the SVM community have been aimed at reducing the negative effects of false sharing. These efforts will be discussed in later sections.

## **1.4 Consistency Models**

The consistency model is the underlying specification of how memory operations are handled in the system. It guarantees a consistent view of memory that matches programmer expectations. Figure 1.5 shows an abridged historical view of SVM research involving memory consistency models and protocols. Some of these models and protocols will be discussed in later sections.

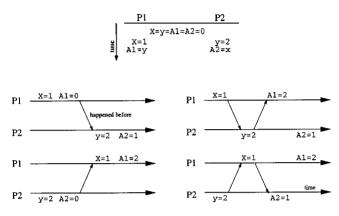

Figure 1.6: Sequential Consistency

#### **1.4.1 Sequential Consistency**

Strict consistency is a uni-processor consistency model which is the basis for sequential consistency, a multiprocessor consistency model. Strict consistency defines what most programmers intuitively expect: A read operation returns the value of the most recent write operation. Sequential Consistency (SC) is strict consistency applied to multi-programming. In SC, the result of any execution appears as some interleaving of the memory operations of the individual nodes when executed on a multi-threaded sequential machine. Figure 1.6 shows the possible outcomes in sequential consistency given a set of memory operations.

Sequential Consistency [32] was the first model used for SVM implementation [35]. SC is an extension of strict consistency that offers a simple parallel programming model which follows common uni-processor methodology. SC has barriers to performance, since every write can result in an invalidation and every read can result in a page fault. This means that the protocol overhead can be high relative to the computation.

#### **1.4.2 Processor Consistency**

In processor consistency, writes issued by an individual processor are seen in order by all processors. Writes by two different processors, however, can be seen differently. Processor consistency is weaker than SC because different processors can observe a different ordering of writes.

#### **1.4.3 Weak Consistency**

Weak Consistency (WC) methods allow caches to become inconsistent and utilize synchronization operations to define synchronization points within programs. Weak consistency was introduced by Adve and Hill [3] in 1990. Weak Consistency methods aggregate consistency events and perform coherence operations at specific user defined synchronization points within the program. The overall effect is that network traffic can be minimized in WC. Weak Consistency relies on the programmer to properly label programs with synchronization operations. These synchronization operations are fence operations that act to separate conflicting sets of memory operations. Synchronization operations are guaranteed to be sequentially consistent. Thus, by properly labeling a program, sequentially consistent execution can be enforced.

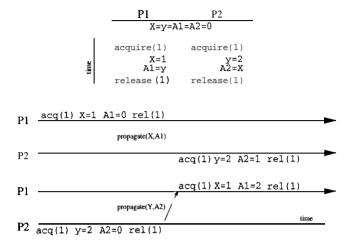

Figure 1.7: Release Consistency

#### **1.4.4 Release Consistency**

Release Consistency (RC) [14] is an effort to lower the cost of coherence. Release consistency is an extension of weak consistency which utilizes two types of synchronization operators: Acquire and *Release*. An Acquire operation is performed when a process wants access to a shared memory object. A Release operation is performed when a process "gives up" a shared memory object. These operations have two roles. The first is that of a barrier where synchronization of all shared data objects occurs. The second role is that of a lock. Acquires and Releases are guaranteed to be processor consistent. Figure 1.7 shows the two possible outcomes in a Release Consistent two processor execution. Note that variables in the two nodes are not made consistent unless synchronization operations are used.

RC reduces the frequency of coherence operations beyond that of Weak Consistency, because synchronization in RC only occurs between sharing processors. This reduces the negative effects of false sharing. The drawback is that in order to use RC, programs must be data-race free and be properly labeled, which means that the programmer must use explicit synchronization.

RC was the basis for Eager Release Consistency (ERC) [10] and Lazy Release Consistency (LRC) [25][26] protocols. ERC and LRC are described in Section 2.4.

Figure 1.8: Entry Consistency

### **1.4.5 Entry Consistency**

Entry Consistency (EC) [9] is a memory model which is more relaxed than Release Consistency. EC is more relaxed because it limits the data to which the synchronization is applied. In EC, there are two levels of synchronization. The first is identical to that of RC where global synchronization occurs. The second level provides a method for synchronization of a smaller set of data objects. In this level, the programmer explicitly binds data objects to synchronization variables. At the synchronization event, only the data which is bound to the synchronization variable is made consistent. The overall effect is a reduced message traffic which allows for greater performance with some types of data distributions. See Figure 1.8 for an example of Entry Consistency.

A negative aspect of EC is that it places a greater burden on the programmer than RC, since the programmer must explicitly associate data to synchronization variables.

## **1.4.6 Scope Consistency**

Scope Consistency (ScC) [23][20] is similar to entry consistency. In ScC, however, not all data objects need to be explicitly bound to synchronization variables. ScC

Figure 1.9: Scope Consistency

uses synchronization variables which define a scope, such that a data binding is achieved dynamically when write access to the data occurs within that scope. See Figure 1.9. The ScC model is less complex than EC to program, but is at least as complex as RC and in some cases more complex than LRC [20].

## **1.5** Protocols

#### **1.5.1 Generalized SC Protocols**

A protocol provides a global view of how the SVM system works. Stumm and Zhou [47] describe four general SC algorithms as central server, migration, read replication, and full replication. Although these algorithms were originally designed in the context of a sequentially consistent distributed shared memory model, they have been applied to other consistency models. Choice of an optimal algorithm for an SVM system will depend on a number of architectural and implementation features, such as amount of memory, per message communication costs, and computational ability. One negative aspect of SC protocols is the tendency for a ping-pong effect can be so severe that memory accesses are never allowed to complete [38]. A solution shown to address this problem is to assign each page a delta value, the minimum amount of time that the page must be resident [13]. The delta value is typically based on the amount of time the hardware requires to perform one memory operation. The four protocols are discussed below.

#### **Central Server**

The central server algorithm, shown in Figure 1.10, is based on client-server architecture. In this algorithm, a central node, sometimes called the home node, controls access to globally accessible memory. Caching does not occur in this algorithm. Instead messages that contain a request type and data are sent between the client and server. The server responds to a read request by sending the data

Figure 1.10: Central Server

at the requested location. A server responds to a write request by writing the data contained in the client message to the requested location. The ordering of operations can be provided by the natural sequencing produced by the interconnect or by a system of logical clocks. The central server algorithm has the obvious problem that the server performs all memory operations and can be a bottleneck to system performance.

#### Migration

In migration, data is shipped to the local memory of the accessing process. See Figure 1.11. Migration is a single-reader/single-writer protocol with at most one copy of each page in the system at any given time. When a process wants to access a page, it must query remote nodes for the location of the page. There are two mechanisms used to minimize the cost of the query. One is to store page directory information on a designated server. The other is to allow sharers to

Figure 1.11: Migration

store, as hints, some information about previously seen pages, such as the page's destination address. These hints can help to lower the cost of finding the page.

#### **Read Replication**

Read replication, shown in Figure 1.12, is a multiple-readers/single-writer protocol. In read replication, concurrent read access is allowed. Shared pages of memory can be replicated with read-only permission at each process. Only a single writer is allowed in the system. In order to keep the replicated copies consistent, an owning process must keep track of the state of the replicated copies. The owner must ensure that a page with write permission is invalidated before giving read or write permission to another process. Similarly, the owner must invalidate all read-only copies before giving write permission. Systems can either scatter or migrate ownership in the system to alleviate performance limitations.

Figure 1.12: Read Replication

#### **Full Replication**

Full replication, shown in Figure 1.13, is a multiple-readers/multiple-writers algorithm. It allows concurrent reads and writes. In full replication, a mechanism must be used to ensure a global ordering of operations. This can be accomplished by using an implementation based on system of distributed clocks or by using a server implementation similar to the central server algorithm. With a system of distributed clocks each node maintains its own updates. This can be costly with respect to message traffic. Using a centralized server introduces a bottleneck, since all write operations must be scheduled by the server.

Figure 1.13: Full Replication

## **1.5.2 Optimistic Protocol**

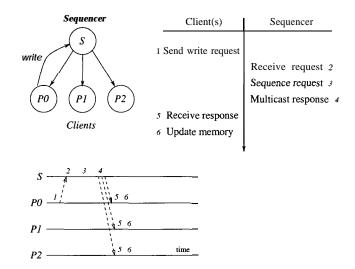

TORIS [31] is an optimistic central-server full replication algorithm. The primary components of TORIS are shown in Figure 1.14. TORIS defines a transaction to be a set of read and write operations bracketed by *begin-transaction* and *end- transaction* operations. Transactions are two-phase with active and commitment phases. A transaction is active after executing *begin- transaction* and before executing *end- transaction*. Memory operations of the transaction are logged during the active phase. The commitment phase begins at the point of the *end- transaction* operation. A sequence number *n* is assigned by the central server at the onset of the commitment phase. A transaction commit or abort marks the end of the commitment phase. A transaction *A* with sequence number n commits when no concurrently executing transaction with a sequence number smaller than *n* has modified any of the data that transaction *A* accessed. Transaction *A* aborts when the opposite occurs.

Figure 1.14: ToRiS: Optimistic Full Replication

TORIS differs from regular sequential consistency methods since it determines *a posteriori* if a transaction has accessed invalid data. Hence, TORIS uses deferred validity resolution. TORIS minimizes communication since consistency messages occur at the end of a transaction and not with each memory object access.

### **1.5.3 Reduced Granularity Protocols**

Much work has been done in the area of fine-grain SVM. Fine-grain approaches reduce the size of the shared object in an effort to reduce the amount of false sharing and fragmentation. Blizzard-S [43] and Shasta [45] are two fine-grain SVMs which function by first scanning executables for memory operations and then modifying the executables to include coherence and synchronization functionality. This approach has the advantage that source code is not always available and false sharing is eliminated, but has the disadvantage that there may be an increase in the number of messages required for synchronization.

Other efforts are aimed at reducing false sharing and message overhead. JIA-JIA [17] divides a shared page into blocks. A faulting processor is only required to fetch the invalid blocks and not the entire shared page. BOPS [41] adapts the shared object granularity to application requirements during program execution. MultiView [21] uses the concept of a view. A view is a region of shared memory. Views of different sizes can be used such that large and small granularity sharing is allowed in the system. Small views can be composed into larger views and large views can be decomposed into multiple small views, thus providing a sharing granularity best suited for the application.

#### **1.5.4 Lazy Protocols**

A release based protocol can be lazy in two respects. Lazy propagation means that the invalidations are propagated from one process to another on demand when the second process performs an Acquire operation. Lazy application means that invalidations are queued at the destination node and applied when the node performs its next Acquire operation. Lazy propagation minimizes coherence overhead since updates are sent to only those processes requiring the modifications. Lazy application can reduce the number of page misses which occur between the time invalidations are received and the next Acquire operation.

Eager Release Consistency (ERC) [6] [10] is a release consistent protocol which propagates updates as soon as they are made and applies updates as soon as they are received. ERC is not a lazy protocol, but was a basis for the development of other lazy protocols. Delayed consistency [11] eagerly propagates modifications, but uses lazy application. Lazy Release Consistency (LRC) [25] is a page-based multiple writer protocol that uses lazy propagation and lazy application. It minimizes network traffic by packaging each update as a *diff*, a comparison between new modified memory and old memory.

#### **1.5.5 Home-Based Protocols**

Home-based protocols utilize one or more central nodes for bookkeeping, performing page modifications, and servicing page requests. Home-based protocols have advantages. Home-based protocols minimize the amount of information that needs to be stored, since modifications can be applied immediately and discarded. In some circumstances, home-based protocols require fewer messages since requests from remote nodes can be serviced by one round trip to the home node. Another advantage of home-based protocols is that memory operations performed at the home node do not require remote data operations. There are two main disadvantages to home based systems. One is that home-based systems typically send an entire page even if the faulting process needs to modify a single word. The second is that assignment of homes can yield a wide range of performance.

Home-based Scope Consistency [23] and Home-based LRC [20][50] are two home-based protocols.

#### **1.5.6 Adaptive Protocols**

There are two main types of adaptive protocols. The first, Adaptive Writer Protocols, adapt between single writer and multiple writer protocols. Adaptive LRC [1] is a version of LRC which adapts on a per page basis between a single writer and multiple writer protocol. At runtime during a synchronization point, the sharing pattern of each page is examined. If write-write sharing is not detected, then the protocol switches from multiple-writer to single-writer for that page. Single writer LRC [27] eliminates the need for diffs and the extra coherence messages required with regular LRC.

The second type of adaptive protocols are Adaptive Migration Protocols. Adaptive Migration Protocols adaptively migrate homes or threads. These migration methods seek to optimize the amount of local operations, minimize the amount of network traffic, and load balance the system. JIAJIA [15], incorporates home migration into home-based scope consistency. It adaptively migrates home pages according to the application sharing pattern. Orion [39], is an adaptive home-based LRC SVM system which uses home migration and dynamic adaptation between write-invalidation and write-update protocols. Orion's dynamic write protocol adaptation is based on the collection of memory access information at the home nodes and aims at lowering network costs while providing high data availability. Write invalidate methods are generally less costly since messages are shorter. Write update methods have greater network costs, but minimize page misses.

Thread migration is a strategy for load balancing a distributed system. Migration of a thread from an overburdened node to an idle or minimally burdened node can boost overall performance. On the other hand, it may be beneficial to migrate sharing threads to the same node, such as a multiprocessor node, to take advantage of hardware and operating system memory management. This strategy also reduces the amount of network overhead between the two sharers. How to choose which threads to migrate to a location in a release consistent system is an active field of research. One approach is to minimize the total number of shared pages between any two nodes [48]. This is based on the idea that the amount of network traffic for maintenance is dependent on the number of sharers. Cohesion [33] is a thread-migratory SVM that incorporates this strategy. Additionally, in order to determine if migration of a thread to a remote node is beneficial, Cohesion determines the page-sharing pattern between the thread and all local threads and the page-sharing pattern between the thread and all threads on the remote node. If the number of local sharers is greater than the number of remote sharers, migration will not be beneficial.

# **1.6 Architectural Support**

#### **1.6.1 Broadcast and Multicast Protocols**

Use of broadcast or multicast capable network hardware devices and libraries minimizes network traffic because they replace multiple messages with a single message. Brazos [42] is an example of a Scope Consistent SVM which uses both a multicast and point-to-point communication protocol. Multicast, as Speight and Bennett [42] describe, does lead to two problems. The first problem is useless multicast traffic. In this situation, a process receives multicast updates for pages

they are no longer actively accessing. Upon receiving the updates, the process is interrupted, thereby reducing the amount of useful computation. Brazos minimizes the effect of useless multicast traffic with a copyset reduction algorithm. This algorithm involves a counter for each page that is decremented when a useless update is received. If the counter reaches zero, the process is removed from the sender's copyset at the next synchronization point. If the process accesses the data, the counter is reset. The value of the counter is configured based on an application-specific history mechanism.

The second problem is multicast conflicts. A multicast conflict occurs when a multicast update for a page arrives while waiting for a response to a request for updates. In this situation, there is an extra conflicting copy of an update. Brazos' solution to the multicast conflict problem is to store the duplicate updates and at the next barrier transfer the updates to the sending processor. For each page, the sending processor determines which nodes received useless updates. This set of nodes becomes the page's copyset. Subsequent updates are multicast to nodes only within the copyset.

The resolution of the two multicast-based problems helps Brazos provide a dynamic write protocol on a per page basis. When only one process has membership in the copyset of a particular page, the page is handled using a write-invalidation protocol. With two or more sharers, multicast is utilized and the page is handled using a write update protocol.

#### **1.6.2** Network Support and SMP Clusters

Network devices capable of performing memory operations are the basis for research in the area of remote operations. Coupled with high speed interconnects, these types of network interfaces can be used to improve performance of SVM systems. Digital's Memory Channel and the custom network interface of the SHRIMP [4] multicomputer are examples of memory-mapping communication devices. Automatic Update Release Consistency (AURC) [19] is a SVM system which has been used on the SHRIMP multicomputer. In AURC, the memory bus is monitored for write operations. These write operations are then automatically propagated in hardware to remote memory locations. Cashmere [29] is a similar system that uses memory channel. Cashmere does not use an automatic remote write mechanism like AURC. Instead, a remote write is performed on demand for each shared local write.

Use of Symmetric Multi-processor (SMP) nodes with SVM systems has appeared in recent work [7] [S]. These efforts are an attempt to capitalize on hardware coherence and synchronization while maintaining memory consistency across the entire cluster. The results of the work show that SMP nodes perform better than uniprocessor nodes and that increasing the size of the SMP nodes further increases performance.

# **1.7 Application Support**

#### **1.7.1** Compiler Transformations and Instrumentation

Compiler transformations are useful tools for providing transparency, reusabilty, and increased performance. Compiler modifications to source can reduce the amount of false sharing, the amount of synchronization, and overall performance of the system. Jeremiassen and Eggers [24] have used compile time data transformations to reduce the number of false-sharing misses in SVM systems. They have modified Parafrase-2, a source-to-source restructurer, to incorporate algorithms that reduce the amount of false sharing. Specifically, Parafrase-2 analyzes parallel source code, generates information about cross-processor memory reference patterns, identifies data structures that may be false shared at runtime, and transforms these data structures to eliminate false sharing. Two fundamental transformations are used. The first is to cluster together data that is accessed primarily by one processor. This ensures that a high degree of availability is maintained for data with processor locality. The second is to arrange data such that shared data structures with no processor locality do not fall in the same cache lines. This transformation minimizes the cost of coherency overhead for shared data.

There is substantial work in the area of synchronization-reducing compiler transformations. Barrier synchronization can be the worst form of synchronization because barriers are global in nature. Potential computation time is lost as processors already in a barrier become idle and wait for the slowest processor to enter the barrier. Also as computation is spread out across more processors, the frequency of barriers increases, thus decreasing the amount of useful computation. Han, Tseng, and Keleher [16] researched SVM barrier synchronization elimination for compiler-parallelization. The main thrust of their work is to utilize LRC and replace barriers with nearest-neighbor synchronization translations. Communication of memory coherence information in SVM systems often occurs within a barrier region. In some barriers, communication only takes place between neighboring processors. Nearest neighbor synchronization allows a process to synchronize with only those neighbor processes with which it communicates coherence information. In nearest neighbor replacement, a process sends a notification message to each of its neighbors. After the neighbors receive the notification and after the two processes have transfered any pending coherence information, the neighbors send a message in response to the notification. Receipt of responses from all the neighbors releases the process to continue computational work. Nearest neighbor replacements have the ability to balance the system by decreasing the amount of processor idle time. Another benefit of nearest neighbor replacements is the elimination of the serial bottleneck of global barrier managers.

Compiler Assisted Software DSM (CAS-DSM) [36] is a recent effort aimed at eliminating operating system involvement in segmentation violations. The majority of SVM systems rely on hardware mechanisms to detect local memory faults. These faults, in the form of segmentation violation signals (SEGV), are handled by costly operating system or SVM system SEGV handler routines. CAS-DSM instruments source code in a way that helps avoid the segmentation violation. In essence, CAS-DSM equips the source with aggressively optimized prefetch functionality. This is a sensible approach since the overhead required for testing for invalid data and possibly prefetching in user code is less than the overhead expense of the operating system or SVM SEGV handlers.

Another approach at the compiler level is the use of Aspect-Oriented Programming (AOP) [37]. Aspect-Oriented Programming [30] is a programming methodology where different aspects of a program, such as synchronization and memory management, are specified separately from the base program. Aspects are woven into a base program to create source that has aggregate functionality. Mentre, Metayer, and Priol's work proposes a base program consisting of a high level SVM abstraction and aspects consisting of different implementation choices. The aspects are transformed into automatons which can be dynamically loaded at runtime in order to optimize SVM performance for a particular application sharing pattern.

#### **1.7.2 Transparency**

Shasta [44] is a SVM system which tackles the problem of transparency. Shasta is a fine-grain SVM system that provides the tools to execute applications compiled for hardware shared-memory systems. These applications include a large number of commercial binaries that are available in the software market. Shasta transparently executes binaries by outfitting the binary code with appropriate memory coherence functionality. Shasta scans the binary executable for load and store operations and inserts code that checks during runtime whether the required data is local and in the proper state. Shasta minimizes the overhead of checks by recognizing that groups of memory operations can be satisfied by a single check. Memory checks eliminate operating system page fault resolution. Also, Shasta incorporates polling as a replacement for interrupt based SVM messaging. Interrupts are costly since they involve hardware and operating system layers. Shasta researchers have noted that two of the largest problems with this type of approach are the correct support of the instruction set architecture and the provision of operating system services, other than memory-management, in the distributed system.

# 1.8 Thesis

This dissertation is an evaluation of a new protocol called Asynchronous Validity Resolution. It centers around three claims:

- **Claim** 1.1 Asynchronous Validity Resolution (AVR) decreases the negative effects of false-sharing that are found in regular Sequential Consistency.

- **Claim** 1.2 Asynchronous Validity Resolution (AVR) does not require a different programming methodology than that of regular Sequential Consistency.

- **Claim 1.3** Asynchronous Validity Resolution (AVR) has best performance in loosely coupled systems that have relatively high communication costs.

False-sharing burdens processes with extra induced coherence costs. Reducing false-sharing by decreasing granularity is an obvious solution. Unfortunately, smaller granularity means more shared objects, more directory overhead, and

more message traffic. Also, in order to use hardware and operating system services, many Shared Virtual Memory sharing granularities are matched to the hardware and operating system page size requirements. Thus, use of small granularity may not be optimal, if hardware and operating system support is lost.

Some relaxed consistency protocols eliminate false sharing, but not without limitations. Programs with data races, such as chaotic programs, cannot be run on relaxed memory model SVM systems. Also, programs destined for execution on relaxed memory model systems must be written to include synchronization primitives. In some protocols, explicit binding of synchronization to variables is required. In other words, the implementation details of the memory consistency model have bubbled-up from lower levels into user application space. The programming methodology required by relaxed memory models is middle-ground between the traditional sequentially consistent shared memory parallel programming paradigm and the message passing programming paradigm. Sequentially Consistent shared memory parallel programming is an intuitive step from regular uni-processor programming methodology. Thus, it makes sense to study shared virtual memory in the context of sequentially consistent shared memory programming.

The traditional shared memory parallel programming paradigm is only available on sequentially consistent SVM systems and sequential consistency protocols suffer from high communication overhead and false sharing. Kreiger and Stumm [31] proposed an approach to this problem with TORiS. TORiS uses optimistic write declaration in a multiple-writer sequentially consistent protocol, requires the programmer to define transactions within the program, and sequences memory operations on a per transaction basis. TORiS uses transactions to define consistency events. This has two caveats. The first is that transactions larger than one memory operation disallow certain orderings of memory operations. The second is that TORiS suffers from the same programming complexity problem that is found with relaxed consistency models. Thus, TORiS doesn't offer a reduction in communication costs and false sharing while maintaining a sequentially consistent shared memory parallel programming paradigm.

SVM protocols, with the exception of TORiS, have used synchronous validity resolution techniques. Synchronous validity resolution techniques ensure that a page is valid before performing memory operations, but leave the faulting process in a blocked state while the page fault is resolved. Unfortunately if the page is false-shared, the process loses valuable computational time waiting for completion of indirectly related coherence operations. These coherence operations, such as write permission requests, can have considerable costs since they may involve a large number of sharers and a large number of messages. Current trends in hardware show that processor speeds are increasing relative to communication speeds, which suggests that the amount of computation lost due to blocking is also increasing. Overall, the amount of lost computation due to synchronous validity resolution can be substantial. Asynchronous Validity Resolution (AVR) is a new approach to the problem. AVR reduces the effects of false sharing by overlapping communication with computation. AVR is based on a read-replication sequential consistency protocol [40] and does not require explicit communication primitives, transaction boundary operations, or any other protocol programming constructs.

The base sequentially consistent protocol is a read-replication SVM protocol that is similar to an SGI Origin 2000 cache consistency protocol. As with all read-replication protocols, this protocol has a relatively high overhead on certain operations, such as a write request on a shared read-only page. In general, AVR provides the greatest benefit for write request operations on pages that are cached in read-only state on multiple remote nodes. These types of requests involve the greatest number of messages and highest overall network costs. High network costs allow more user operations to complete asynchronously. AVR also increases performance for write request operations on a pages cached in read-write state on a remote node. The success of AVR in an application is a function of the amount of false sharing in the application, the cost of SVM overhead, and the cost of coherence overhead.

# **1.9 Contributions**

The contributions of this dissertation are the design, implementation, and evaluation of asynchronous validity resolution protocol. The claims made in Section **1.8** are validated.

Claim 1.2 states that AVR does not require specialized programming methodology. This claim is validated by designing and implementing an AVR system which uses regular shared-memory programming methodology. A programming suite is then implemented using the AVR protocol.

Claim 1.1 and Claim 1.3 address the performance characteristics of AVR. Claim 1.1 states that AVR decreases the negative effects of false sharing that are found in regular sequential consistency while claim 1.3 states that AVR will have best performance in loosely coupled systems that have relatively high communication costs. These two claims are validated through a set of experiments and analysis of those experiments. AVR and SC are implemented in a modularized SVM, called CVM, which provides a control environment for testing protocols. A suite of applications is chosen for use as a test bed for performance analysis of AVR and SC.

The results show that four components influence the performance of AVR. They are the number of false-sharing vs. true-sharing accesses, the number of pages in the program's working set, the amount of user computation that completes per page access, and the round-trip message time. In order for AVR to outperform SC, the average round-trip message time must be greater than the average amount of time required to checkpoint and perform user computation. Additionally, the average amount of time to perform user computation must be longer than the average amount of time required to resolve the checkpoint. The amount of false-sharing and true-sharing, characteristics of program memory access patterns, also are factors of performance. True-sharing reduces performance in all SVM systems because it reduces the amount of parallelism. In AVR, however, true-sharing causes additional performance loss in the form of protocol overhead from processor rollbacks. False-sharing is the basis for performance gains in AVR, since the net effect of AVR is to allow different processors simultaneous access to false-shared pages. AVR performs well if the false-shared gains outweigh the true-shared losses. Overall, AVR met the expectations and satisfied the claims of the dissertation.

# Chapter 2

# ASYNCHRONOUS VALIDITY RESOLUTION

# 2.1 Motivation and Background

Sequential consistency (SC) was the basis for the first work in the SVM field. Sequential consistency is defined as follows:

A system is sequentially consistent if the global ordering of operations is such that each processor executes its operations in some sequential order and each processor views the operations of the other processors in some global sequential order as specified by the program.

In SC, any read operation returns the value of the most recent write operation as long as it doesn't violate program order. This global ordering requirement creates considerable consistency overhead in SVM systems. The problem is compounded by false sharing. False sharing occurs when unrelated memory accesses fall on a shared memory object, such as a page. False sharing means that consistency events are required for the memory object although there is no actual data sharing occurring.

Newer relaxed consistency models, such as Lazy Release Consistency, Entry Consistency, and Scope Consistency, have been used to provide improved performance over SC by reducing consistency overhead. Unfortunately, these newer memory models have two caveats: they cannot be used with programs that contain data races and they require more programming effort than SC.

In relaxed consistency (RC), synchronization defines consistency points. Memories are not consistent unless synchronization constructs (i.e. locks and barriers) are used. Hence, the requirement in RC that programs be data race free. Data races are often considered bugs, but are used for some programs including chaotic programs. The use of inconsistent memories in RC, allows RC protocols to reduce or eliminate false-sharing by performing page comparisons in a multiple writer configuration. In contrast to RC, SC allows programs with data races, but suffers from false sharing.

SC is an extension of the memory architecture and cache coherence mechanisms found in regular uni-processor machines. Likewise, the SC parallel programming paradigm is an extension of the programming methodology of regular uni-processor machines. SC programming is an intuitive step from traditional regular uniprocessor programming. In contrast, RC programming varies in difficulty. At a minimum, the RC programmer must use proper synchronization to provide consistency for shared variables. This is not substantially different from SC programming, except for some programs, such as those using task queues [26]. Recent RC methods require significantly more programming effort than SC because they require variables to be bound to synchronization variables. This programming methodology approaches the complexity required by message passing programming interfaces in which the programmer must specify the communication parameters.

Asynchronous Validity Resolution (AVR) is an extension of SC designed to improve performance by overlapping computation with communication. In AVR, a memory object is used by the user program while the SVM system simultaneously verifies the memory object's validity. AVR reduces the effects of consistency overhead, especially overhead related to false-sharing. AVR utilizes the programming methodology of regular SC. It allows data races and does not require explicit coherence operations.

# 2.2 Protocol

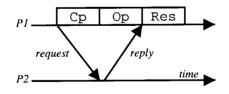

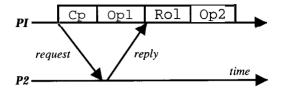

Asynchronous Validity Resolution is an extension of Sequential Consistency. AVR provides overlapped communication and computation while preserving Sequential Consistency. Overlapping communication and computation means that potentially invalid data is used while data validity is resolved. Data validity resolution occurs in shared virtual memory systems when a page fault occurs. From the application viewpoint, all memory is accessible. Use of potentially invalid memory by the application triggers a page fault by the operating systems and/or underlying hardware. Subsequently, a SVM fault handler routine is called which resolves the invalid access. Validity resolution is the process of sending a page request and receiving an updated page from another SVM node. SVM nodes may be either remote hosts or local threads in a SMP configuration. Current SVM systems use synchronous data validity resolution. In synchronous validity resolution a page request is sent by the SVM fault handler in response to a page fault, the SVM system waits until the reply to the page request is received, and then copies the newly received updated page into local memory. The SVM marks the page as valid and returns from the fault handler. User processing in synchronous validity resolution is blocked during the entire data validity resolution interval. AVR differs by allowing the fault handler to return and user processing to continue while data validity is resolved.

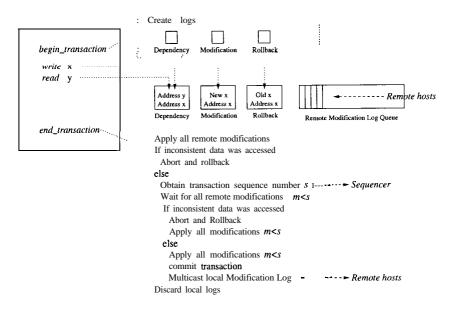

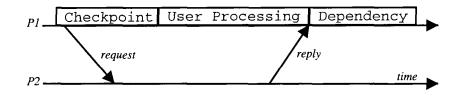

Figure 2.1: Validity Resolution Interval

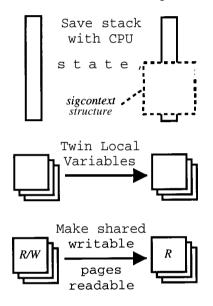

In AVR, the validity resolution interval has three phases as shown in Figure 2.1. The first phase includes the initial page fault, sending of the request message, and process checkpointing. The second phase is the phase in which user process-

ing on potentially invalid data occurs. The final phase is the period where user processing stops, the reply is received, and dependency checking occurs. The AVR configuration allows user processing to occur while messages are sent and received across the network. Dependency checking, the process of determining if valid data was used during the second phase of the resolution interval, is performed once an updated page is received. Dependency checking has two possible consequences: The first is that valid data was used which means that all operations that were performed are valid and the process can continue with user processing. The second is that invalid data was used which means that all operations performed are invalid and the user process must return, or rollback, to its state at the point of the original page fault. Valid data must be used in order to provide sequential consistency in the SVM system. Hence, the requirement for a process thread to rollback to a previous point in execution.

# 2.3 System

The AVR concept was implemented using a modularized application layer SVM system called the Coherent Virtual Machine (CVM) [28]. CVM is a library of functions which provide the functionality of a SVM. The structure of CVM allows SC and AVR to be tested in the same environment. The AVR protocol was incorporated into CVM and was developed for use with the Linux operating system on Intel hardware. The AVR implementation was based on an existing sequentially consistent protocol.

Figure 2.2: SC System

#### 2.3.1 Sequential Consistency

A memory page is an operating system level memory management structure. A page is the smallest sized memory block for which access can be controlled. Page size is platform dependent. The default for the Intel/Linux platform is 4096 bytes. SVM systems that are page based, such as CVM, must use page sizes that are a multiple of the platform dependent page size. Page based SVM systems mimic the cache architecture and mechanisms that are present in shared memory multiprocessors. Memory consistency in the distributed SVM system is analogous to cache coherency in the shared memory architecture. In CVM, memory consistency and local access permissions for shared memory are controlled by a memory consistency to make the distributed memories behave as a single physical memory. The CVM SC consistency module allows sequential execution of the user program in the

distributed system. It controls caching of shared pages and retrieval of updated pages from remote hosts. See Figure 2.2.

Pages are objects in the CVM implementation. Every node has a page object that corresponds to each page in the global shared memory address space. Page objects provide the additional implementation features necessary for physical pages in local memory to be consistent with their corresponding pages in remote nodes. A page object includes a pointer to the actual page in local memory, a copyset, an owner, a manager, and a state. The copyset is the set of nodes which have valid copies of the page in memory. The owner is the node that has the most recent valid copy of the page in local memory. The manager is the node that keeps track of the page's current owner and is determined in the setup routines before user processing. A valid copy of each page is present in the system at all times.

In the SC module implementation, each page exists in memory in a particular state which dictates the type of access allowed on the page. As shown in Figure 2.2, these states are invalid, read-only, or read-write. The read-only state marks the page as readable, but not writable. The page is readable and writable in the read-write state. In the invalid state, the page is not accessible. The invalid state implies that either the page has never been in local memory, has been written over with a different page due to space limitations, or was demoted from another state as a result of an incoming write request from a remote host. The SC system is a multiple-reader/single-writer system which means that multiple processes can simultaneously read from the same shared page, but only one process is allowed to write to a page at any given time.

A read or write operation performed by the user process triggers a page fault, if it operates on a memory location that does not have the required access permission. The SVM system responds to the page fault by sending a page request message to either the owner or the manager of the page. The faulting node is the requester. The requester can be the page's owner if and only if the page fault is a write fault and the page is cached in read-only state. If the requester is the manager of the page and not the owner, the request is sent to the owner. If the requester is not the manager, the request is sent to the manager. If the manager is not the owner, it forwards the request to the current owner of the page. The manager also changes the copyset for the page to show that the requester is now the owner of the page. This ensures that the manager always has the current copyset for the page and always knows which node is the owner. The current owner receives the request from the manager. It changes the copyset for the page and changes the local permissions for the page to reflect the request. The current owner replies to the requester by sending the page and a copy of the copyset. The current owner is now no longer the owner. The requester, once receiving the reply, copies the new page and the new copyset into memory and marks itself as the new owner of the page. The requester always becomes the owner, even when the page is read-only cached in multiple nodes. If the initial request is a read request, then the new owner returns to user processing with the page in a read-only state. If the initial request is a write request, the new owner sends invalidation messages to all nodes, excluding itself, listed in the page's copyset. The receivers of invalidations, mark the page as invalid, and reply with acknowledgement messages. Once all acknowledgment messages are received, the new owner changes the copyset to reflect the invalidations, marks the page as read-write and returns to user processing. If the initial page fault is a write fault and the faulting node is currently the owner of the page, the faulting node needs to only perform the invalidation phase of the fault resolution. Waiting for all invalidation replies ensures that all nodes have a consistent view of memory.

Messages are assigned sequence numbers to allow reliable communication such that messages sent between any two processes are guaranteed to arrive in the order that they are sent. Each page has a *delta* value and a message queue. The delta value is used to reduce the ping-pong effect that occurs in page-based SVM systems. It is the minimum amount of time that a page is required to be resident in memory and is used to ensure that at least one operation completes before a remote node can obtain access to the page. The message queue is used to delay incoming messages that request pages that are in their *delta* interval.

Data validity resolution in the SC implementation is pessimistic. User processing is blocked until the new page is copied into memory and the faulting node has received the appropriate reply messages to guarantee consistency.

## 2.3.2 A V R

The AVR implementation is based on the SC implementation. The main difference between the two protocols is that data validity resolution in AVR is optimistic and in SC it is pessimistic. AVR is optimistic because the user process is allowed to continue execution immediately after the request message is sent. It optimistically assumes that the data is valid. The benefit of an optimistic approach is enhanced performance due to overlapped computation and data validity resolution. The caveat to the approach is that the user process may use data which is invalid. Use of potentially invalid data requires mechanisms that allow for process checkpointing, process rollback, memory operation logging, message queueing, and page twin comparison. The AVR implementation utilizes these mechanisms in the SC framework. The sections below describe the implementation issues of AVR.

Figure 2.3: Checkpointing

# 2.3.3 Checkpointing

The use of potentially invalid data and the possibility of the user process having to return to a previous point in execution means that the protocol must checkpoint the user process state at the point of the initial invalid data access. The checkpoint is the saved process state which includes all the necessary information for the process to return from a point later in execution to a point previous in execution. See Figure 2.3. The necessary process state structures are the CPU registers, the

stack, the local variables, and the shared global variables (the SVM pages). The CPU registers are saved by saving the stack, and thus the *sigcontext* structure, from within the fault handler. The stack is copied into a static structure that grows to accommodate different size stacks. The local variables are saved by making twins. Shared global variables are contained in SVM pages. The process of making twins of SVM pages is not performed initially, but is deferred to the point of first access within the checkpointed interval. Initially each SVM page that currently has write permission is made readable such that writing to the page triggers a page fault. The page fault results in the execution of the segv handler which makes a twin of the page and sets the permission of the page to its original writable state. Thus, twins are only made for pages which are written during the checkpointed state. Twins do not need to be made for pages that have read-only permission, since reads do not modify variables. Handling of shared pages in this fashion means that the working set of pages can be minimized to only those which are modified, hence allowing remote access to unmodified pages to be granted.

## 2.3.4 Memory Mechanisms

The checkpoint page is a page for which the process does not have appropriate permission. Access of this page generates a page fault and causes delivery of a segv signal which is handled by the system's fault handler. The fault handler calls routines which send the update request message and perform checkpointing. After the request message is sent and the process is checkpointed, the handler uses *mprotect()* to set page access permissions for the checkpoint page. Access