Michigan Technological University Digital Commons @ Michigan Tech

Dissertations, Master's Theses and Master's Reports

2018

# Implementing Write Compression in Flash Memory Using Zeckendorf Two-Round Rewriting Codes

Vincent T. Druschke Michigan Technological University, vtdrusch@mtu.edu

Copyright 2018 Vincent T. Druschke

#### **Recommended Citation**

Druschke, Vincent T., "Implementing Write Compression in Flash Memory Using Zeckendorf Two-Round Rewriting Codes", Open Access Master's Report, Michigan Technological University, 2018. https://digitalcommons.mtu.edu/etdr/724

Follow this and additional works at: https://digitalcommons.mtu.edu/etdr Part of the <u>Data Storage Systems Commons</u>, and the <u>Theory and Algorithms Commons</u>

# $\begin{array}{c} \mbox{IMPLEMENTING WRITE COMPRESSION IN FLASH MEMORY USING ZECKENDORF\\ TWO-ROUND REWRITING CODES \end{array}$

By Vincent Druschke

A REPORT Submitted in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE In Computer Engineering

# MICHIGAN TECHNOLOGICAL UNIVERSITY \$2018\$

$\bigodot$  2018 V<br/>incent Druschke

This report has been approved in partial fulfillment of the requirements for the Degree of MAS-TER OF SCIENCE in Computer Engineering.

Department of Electrical and Computer Engineering

| Report Advisor:   | Dr. Saeid Nooshabadi   |

|-------------------|------------------------|

| Committee Member: | Dr. Roger Kieckhafer   |

| Committee Member: | Dr. Soner Onder        |

| Department Chair: | Dr. Daniel R. Fuhrmann |

# Contents

| Li | st of                                  | Figures                                                                                                                                                                                                               | vii                                                                   |

|----|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Li | st of                                  | Tables                                                                                                                                                                                                                | ix                                                                    |

| D  | efinit                                 | $\operatorname{tions}$                                                                                                                                                                                                | xi                                                                    |

| Li | st of                                  | Abbreviations                                                                                                                                                                                                         | xv                                                                    |

|    | bstra                                  | act                                                                                                                                                                                                                   | xvii                                                                  |

| 1  | <b>Intr</b><br>1.1<br>1.2              | roduction       Scope and Outline       Scope and Outline         Flash Memory Technology       Scope and Outline       Scope and Outline         1.2.1       Reading and Writing Flash Cells       Scope and Outline | <b>1</b><br>1<br>2<br>2                                               |

|    | 1.3                                    | 1.2.1       Reading and Writing Flash Cens         1.2.2       NAND and NOR Flash         Solid State Drives                                                                                                          | $\begin{array}{c} 2\\ 3\\ 4\\ 5\\ 6\end{array}$                       |

| 2  | <b>The</b><br>2.1<br>2.2<br>2.3<br>2.4 | e KS-Code       Primary Encodings         Primary Encodings       Secondary Encodings         2.2.1 Padding       Extended Fibonacci Series         Compression Performance       Secondary Encoding                  | 7<br>7<br>8<br>9<br>10<br>10                                          |

| 3  | Imp<br>3.1<br>3.2                      | Algorithms                                                                                                                                                                                                            | <b>13</b><br>13<br>14<br>14<br>15<br>16<br>17<br>18<br>18<br>19<br>20 |

|    | 3.3                                    | 3.2.3       Storage Performance         3.2.4       Parallelism         3.2.4       Parallelism         Software Implementation                                                                                       | 20<br>21<br>22<br>23<br>23<br>23<br>24                                |

|              | 3.4            | Hardware Implementation                                                                                                                     | 25        |

|--------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|              |                | 3.4.1 Primary Encodings and Padding                                                                                                         | 26        |

|              |                | 3.4.2 Secondary Encodings                                                                                                                   | 27        |

|              |                | 3.4.3 Packaging Module                                                                                                                      | 31        |

|              |                | 3.4.4 Hardware Synthesis Results and Performance                                                                                            | 32        |

| 4            | $\mathbf{Svs}$ | tem Integration Considerations                                                                                                              | 35        |

|              | 4.1            | Data Addressing                                                                                                                             | 35        |

|              |                | 4.1.1 File Systems and Clustering                                                                                                           | 36        |

|              |                | 4.1.2 Addressing Adaptations for Encoded Data                                                                                               | 36        |

|              | 4.2            | Data Storage                                                                                                                                | 36        |

|              |                | 4.2.1 Encodings and Page Alignment                                                                                                          | 37        |

|              |                | 4.2.2 Modifying Cluster Size                                                                                                                | 38        |

|              | 4.3            | Primary Encoding Storage                                                                                                                    | 38        |

|              |                | 4.3.1 Primary Encoding Aligned Storage                                                                                                      | 39        |

|              |                | 4.3.2 Unaligned Storage and Super-clustering                                                                                                | 40        |

|              | 4.4            | Storage Alignment for Secondary Encodings                                                                                                   | 42        |

|              |                | 4.4.1 Minimal Write Secondary Storage                                                                                                       | 43        |

|              |                | 4.4.2 Secondary Storage Space Management                                                                                                    | 43        |

|              | 4.5            | Coding Policy                                                                                                                               | 44        |

|              | -              | 4.5.1 Stale Cluster Detection                                                                                                               | 45        |

|              |                | 4.5.2 Padding Policy                                                                                                                        | 45        |

|              |                | 4.5.3 Secondary Encoding Policy                                                                                                             | 46        |

| 5            | Cor            | nclusion                                                                                                                                    | 49        |

| 0            | 001            |                                                                                                                                             | 10        |

| Re           | efere          | $nces \ldots \ldots$ | 51        |

| $\mathbf{A}$ | Imp            | plementation Source Code                                                                                                                    | <b>53</b> |

|              | A.1            | Software Implementation                                                                                                                     | 53        |

|              |                | A.1.1 FZcompress.h                                                                                                                          | 53        |

|              |                | A.1.2 FZcompress.c                                                                                                                          | 58        |

|              | A.2            | Hardware Implementation                                                                                                                     | 83        |

|              |                | A.2.1 FZCompressSeq.sv                                                                                                                      | 83        |

|              |                | A.2.2 FZEncodeWordSeq.sv                                                                                                                    | 87        |

|              |                | A.2.3 FZDecodeWordSeq.sv                                                                                                                    | 89        |

|              |                | A.2.4 FZPadWordSeq.sv                                                                                                                       | 90        |

|              |                | A.2.5 FZOverwriteSeq.sv                                                                                                                     | 92        |

|              |                | A.2.6 FZExtractSeq.sv                                                                                                                       | 95        |

# List of Figures

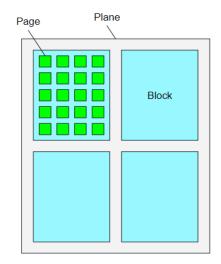

| 1.1          | A mock-up of the SSD's internal memory structure, with pages in green, blocks in blue, and the plane in gray                                                                                                                                                                                                                                                 | 5                          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2.1          | A Zeckendorf encoding $(F_{11}+F_4+F_1=243)$ (top) is padded (center), with additional separator bits underlined and extension bits boxed; the encoding is then overwritten with the number 19 (bottom), shown in bold.                                                                                                                                      | 9                          |

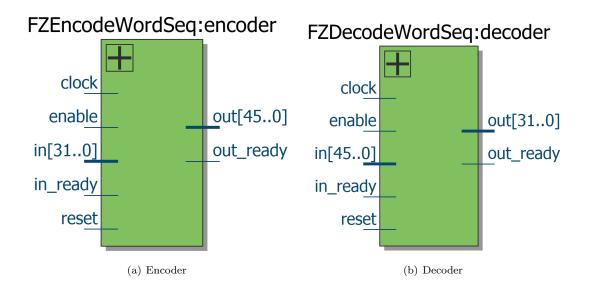

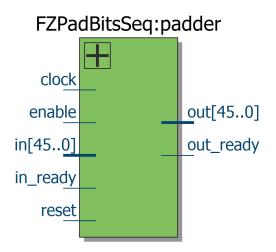

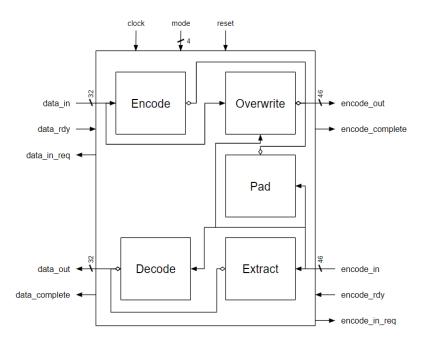

| 3.1          | Block diagrams of the encode and decode modules                                                                                                                                                                                                                                                                                                              | 26<br>26<br>26             |

| 3.2<br>3.3   | A block diagram of the pad module                                                                                                                                                                                                                                                                                                                            | 27                         |

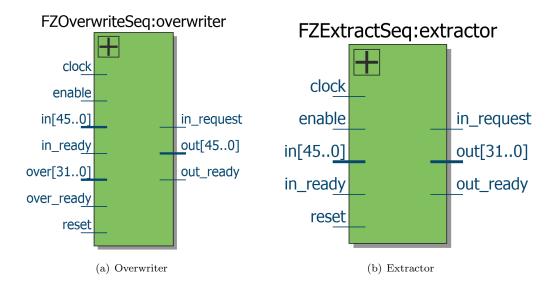

| 3.4          | module to I.       Block diagrams of the overwrite and extract modules         (a)       Overwriter         (b)       Extractor                                                                                                                                                                                                                              | 28<br>28<br>28<br>28<br>28 |

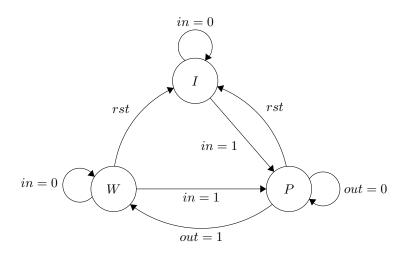

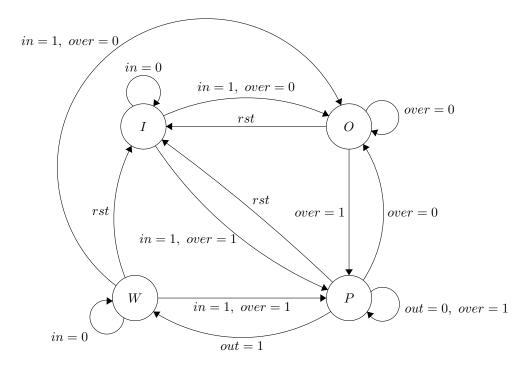

| 3.5          | State machine for the overwrite module. From initial state I, module transitions either<br>to O while awaiting secondary input, if data to overwrite has not been provided, or<br>to P to process the encoding. From P, transitions are either to W when an encoding<br>is complete or to O if data is exhausted beforehand. Resetting returns the module to |                            |

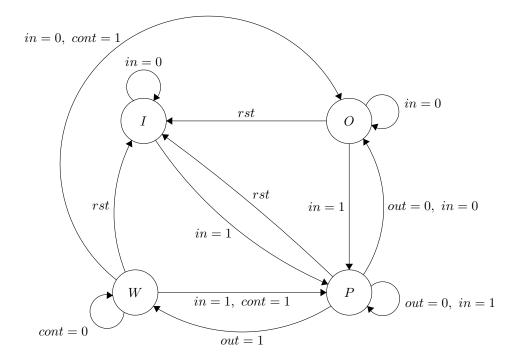

| 3.6          | I                                                                                                                                                                                                                                                                                                                                                            | 29                         |

| 9.7          | module to I                                                                                                                                                                                                                                                                                                                                                  | 30                         |

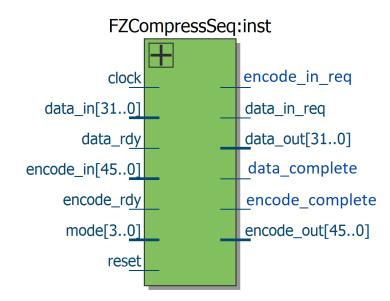

| $3.7 \\ 3.8$ | Block diagram for the packaging module                                                                                                                                                                                                                                                                                                                       | $\frac{31}{31}$            |

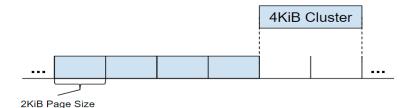

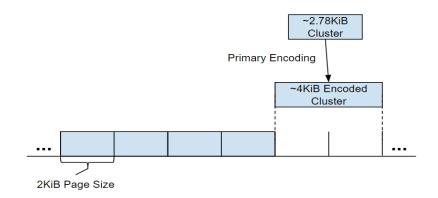

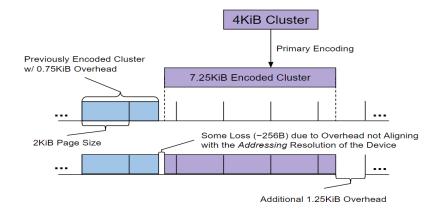

| $4.1 \\ 4.2$ | A page-aligned 4KiB cluster fits exactly within page boundaries for a 2KiB page size<br>Altering cluster size to match its <i>encoded</i> size guarantees correct page alignment, but                                                                                                                                                                        | 37                         |

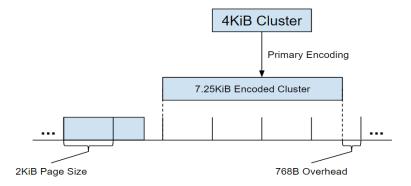

| 4.3          | requires significant changes to device file access                                                                                                                                                                                                                                                                                                           | 38                         |

| 4.4          | age space overhead to maintain alignment Storing to overhead space can reduce memory waste, but creates unaligned pattern of access; the file shown in purple now occupies 5 pages instead of the minimal 4,                                                                                                                                                 | 39                         |

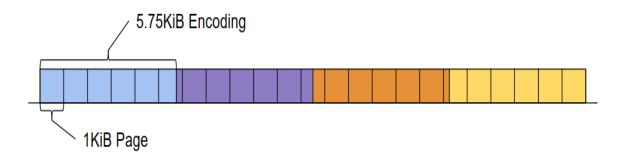

| 4.5          | requiring more access time to retrieve                                                                                                                                                                                                                                                                                                                       | 41                         |

| 1.0          | perfectly to a 1KiB page size                                                                                                                                                                                                                                                                                                                                | 42                         |

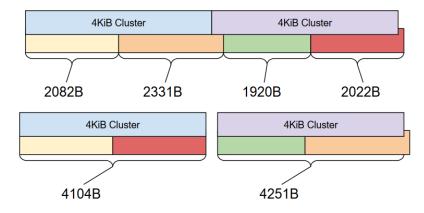

4.6 Two 4KiB file clusters are stored as secondary encodings over four primary encodings of degree 2 (each primary encoding represents 4KiB of data and occupies 5888B = 5.75KiB of flash memory). Top: secondary cluster data is overwritten onto padded primary encodings in no particular order (secondary storage capacity shown in bytes), with two clusters partially occupying a single encoding. Bottom: by selecting which encoding(s) to overwrite based on their capacity, it is possible to more efficiently store secondary data by minimizing overhead while keeping secondary data from overlapping on the same primary encoding.

44

# List of Tables

| 2.1 | Data Expansion Factor and Theoretical Min/ Max Compression for Encoding Degrees |    |

|-----|---------------------------------------------------------------------------------|----|

|     | 2 to 10 Inclusive                                                               | 11 |

| 3.1 | Average Write Compression for Varying File Type                                 | 24 |

| 3.2 | Write Compression Sample Variance                                               | 24 |

| 3.3 | Top-Level Circuit Modes                                                         | 33 |

| 3.4 | HDL Synthesis Results                                                           | 33 |

| 4.1 | Storage Overhead for Encoded 4KiB Cluster for Varying Degree and Page Size .    | 40 |

| 4.2 | Minimum Compression Ratio for Encoded 4KiB Cluster w/Storage Overhead           | 40 |

| 4.3 | Maximum Compression Ratio for Encoded 4KiB Cluster w/Storage Overhead           | 40 |

| 4.4 | Minimum Number of 4KiB Clusters Required for Perfect Page Alignment             | 42 |

# Definitions

#### block

The smallest unit of a flash memory that can be **erased**.

**cell** The smallest physical component of a memory from which a meaningful value can be interpreted.

#### cluster

A fixed-size portion of a file which constitutes the smallest logical unit of file storage.

#### compression ratio

Typically, the ratio of the amount of information bits stored in a given memory over the number of memory bits occupied. Specifically used here to refer to the ratio of the number of information bits stored over *multiple writes* to a given location in memory, *without* requiring an **erase** operation, over the number of memory bits accessed during those writes.

#### data bit

A single binary digit representing an arbitrary data value either in part or whole. In particular, refers to the m-1 bit(s) immediately proceeding a **sentinel bit** in a **primary encoding** which can be used to represent additional data in a **secondary encoding**, where m is the *encoding degree*.

#### encoding

Generally, can be used to refer to any way in which information is represented (for example, base-2 binary, the decimal numeral system, or even the English language can all be thought of as ways of encoding information). In the context of this report, refers to any data represented as either a **primary**, **secondary**, or **padded primary encoding**.

#### encoding degree

The series degree of the extended Fibonacci series used when generating a primary encoding. Can also be applied to padded primary encodings and secondary encodings, as this value has implications for the function and interpretation of these encoding types as well.

#### erase

To restore a **cell** from its **programmed** state back to its original or default value, which can vary according to the design of the memory.

#### extended Fibonacci series

A recursive series based on the classic Fibonacci series  $(A_0 = 1, A_1 = 2, A_n = A_{n-1} + A_{n-2})$ , where each element is based on the sum of the first previous element and the **m**th previous element, where **m** is the series **encoding degree**. This includes the classic Fibonacci series, whose degree is equal to 2.

#### extension bit

Any bits which proceed the m-1 data bits in an encoding but appear before the next separator bit.

#### flash memory

A digital memory whose method of storage is an array of FG-MOSFETS arranged into relatively large erase blocks such that the memory can be erased "in a flash."

#### KS-code

A type of two-round **rewriting code**, named after researchers Klein and Shaoira who first proposed its use, which uses **Zeckendorf sums** to produce a first-round encoding to which additional data can be subsequently written to in the second round of writing.

#### padded encoding

A primary encoding containing the maximum number of separator bits possible for a given initial state while still maintaining the properties of a **Zeckendorf sum** and the locations of the separator bits from the initial state.

#### padding scheme

A method of adding bits to a pre-existing binary string; in this case, particularly refers to the process of adding as many additional sseparator bits to a primary encoding as is possible without violating the properties of a Zeckendorf sum.

page The smallest unit of a flash memory that is physically accessible by the read/ write circuit.

#### primary encoding

A value or set of values encoded according to the binary representation of their **Zeckendorf** sums.

#### program

To alter a memory's **cells** from their default state, which can vary according to the design of the memory.

#### rewriting code

A state-based method of representing data such that the data can be altered in-place to represent some value other than its original value, typically while maintaining certain writing properties, such as not requiring bits to be **erased** in order to be updated.

#### secondary encoding

A primary encoding which has had its data bits set to represent additional information.

#### separator bit

A bit with a logical value of '1' in a **primary encoding** or **padded primary encoding**. Denotes the beginning of a set of data bits in a **secondary encoding** (although its value does not contribute to the value of the stored data in this case).

#### series degree

An integer which represents the number of prior series elements upon which an **extended Fibonacci series** depends.

#### solid-state memory

Any type of digital memory which does not use moving parts, and is able to represent data values through static electrical circuits alone.

#### standard encoding

The standard base-2 binary method of representing data values.

#### Zeckendorf encoding

A binary representation of a **Zeckendorf sum** wherein each bit position represents a member of an **extended Fibonacci series**, rather than a power of 2.

#### Zeckendorf sum

A summation of a subset of the elements in a given **extended Fibonacci series** in which each element in the series appears at most once and no elements which are within m-1 positions of

each other appear in the sum, where m is the *series degree* of the extended Fibonacci series being summed.

# List of Abbreviations

| API      | Application Programming Interface                               |

|----------|-----------------------------------------------------------------|

| ASIC     | Application-Specific Integrated Circuit                         |

| FGMOSFET | Floating-Gate Metal-Oxide-Semiconductor Field-Effect Transistor |

| FPGA     | Field Programmable Gate Array                                   |

| FTL      | Flash Translation Layer                                         |

| HDL      | Hardware Description Language                                   |

| IP       | Intellectual Property                                           |

| SSD      | Solid-State Drive                                               |

| WOM      | Write-Once Memory                                               |

### Abstract

Flash memory has become increasingly popular as the underlying storage technology for highperformance nonvolatile storage devices. However, while flash offers several benefits over alternative storage media, a number of limitations still exist within the current technology. One such limitation is that programming (altering a bit from its default value) and erasing (returning a bit to its default value) are asymmetric operations in flash memory devices: a flash memory can be programmed arbitrarily, but can only be erased in relatively large batches of storage bits called blocks, with block sizes ranging from 512K up to several megabytes. This creates a situation where relatively small write operations to the drive can potentially require reading out, erasing, and rewriting many times more data than the initial operation would normally require if that write would result in a bit erase operation. Prior work suggests that the performance impact of these costly block erase cycles can be mitigated by using a rewriting code, increasing the number of writes that can be performed on the same location in memory before an erase operation is required. This paper provides an implementation of this rewriting code, both as a software program written in C and as a SystemVerilog FPGA circuit specification, and discusses many of the additional design considerations that would be necessary to integrate such a rewriting code with current file storage techniques.

# 1. Introduction

Modern computing devices are rapidly adopting **flash memory** as a means of persistent data storage. Offering lower power requirements, smaller form-factors, and superior performance in comparison to "traditional" types of non-volatile memory, all at an increasingly competitive price per unit of storage, flash has become an attractive storage solution for both mobile computing and high-speed file access [1]. Unfortunately, due to the physical properties of the underlying technology and the constraints that these properties impose on flash memory architecture, these benefits also come with certain inherent limitations that can impact the performance and longevity of flash-based memories [2]; while the benefits to using flash technology in memory devices still far outweigh the potential caveats in doing so, circumventing or mitigating the effects of these limitations is nevertheless essential to maximizing its utility. The object of this report is to address one such limiting factor. specifically that flash memories are restricted in their ability to modify data values once written, by providing two novel implementations of a method of data coding. First proposed in prior work [3] as a potential method of circumventing the memory modification restrictions of flash, this report details the motivation, theory, and mechanics of this coding; its implementation and performance in both hardware and software; and its potential application to data storage on a flash-based mass storage device.

### 1.1 Scope and Outline

The chapters below cover a number of topics relating to the motivation for this work, i.e. the construction and mechanics of flash memories, in addition to detailing the theoretical background of the system of coding being implemented, but the scope of the implementation(s) itself is actually quite narrow. The goal in producing these implementations was simply to adapt the abstract methods of data rendering so described in order to successfully encode and decode some known data; it is important to note that, although the implementations detailed herein are complete in the sense that they are capable of applying the prescribed data transformations which constitute the aforementioned coding method, they do not themselves facilitate its primary function: to store and manage encoded data in flash memory such that memory performance is improved. Instead, these implementations are offered as the first piece of the puzzle in applying these data processes to flash storage devices, providing the necessary shuffling of bits to translate data to its encoded form for storage and back to a usable state once retrieved while leaving the tasks of figuring out where and how to store the encodings in a way that make sense to other devices; while these tasks are fairly straightforward in most systems, applying this coding system complicates things somewhat, as chapter 4 illustrates.

This chapter, chapter 1, explains the construction of flash memory, how it operates, and why such memories are subject to certain limitations. Chapter 2 summarizes the contents of [3] that detail the theoretical basis of the code being implemented, providing a high-level description of its function and purpose. Chapter 3 describes the implementations themselves, providing an overview of their operation from a user's perspective as well as some general insight into the logic by which they operate. As mentioned, chapter 4 discusses the application of this code to storing data, particularly in flash, and how the results of the encoding process are often at odds with the objective of maximizing memory performance. Finally, Chapter 5 concludes this report with a brief summary of the topics covered, the results and significance of the work, and what yet remains to be done.

## 1.2 Flash Memory Technology

As opposed to the magnetic storage devices commonly associated with mass data storage applications, flash memories are a form of electronic or **solid-state memory**, meaning that they are able to represent data purely through the use of electronic circuits, with no moving parts. In flash (and other solid-state memories), a **cell** - the most basic physical storage element in a memory from which a value can be meaningfully interpreted - is made up of just a single, specialized field-effect transistor called a floating gate transistor, or FG-MOSFET [4]. Floating gate transistors are built with two electrically isolated gates: a control gate (which functions as a normal transistor gate), and a "floating" gate that is insulated from both the control gate and the transistor substrate by two dielectric layers. By constructing the transistor in this way, charged particles (i.e. electrons) can then be induced onto the floating gate under specific conditions, altering the transistor's response to voltages on the control gate.

#### 1.2.1 Reading and Writing Flash Cells

FG-MOSFETs are charged via two primary mechanisms: hot-carrier injection and Fowler-Nordheim tunneling [4], [5]. To utilize hot-carrier injection, a high positive voltage is applied between the transistor control gate and its source, and a smaller positive voltage is then applied from drain to source. High current flows from the drain to the source, but some of the charge carriers in that current have enough energy to overcome the resistance of the oxide surrounding the floating gate and get trapped. Fowler-Nordheim tunneling takes a slightly different approach: instead of pulling a current through the transistor to induce charge carriers to move through the oxide (which can be destructive to the oxide material), Fowler-Nordheim uses a high positive voltage between the control gate and the transistor substrate to induce a high electric field in the transistor, causing some electrons to "tunnel" through the oxide and again embed themselves in the floating gate. In both cases, charge is removed via tunneling by charging the gate and the substrate with a voltage of opposite polarity to that used charging (i.e. a voltage drop from the substrate to the control gate).

The charges stored in the floating gate of an FGMOSFET modify the functioning of the underlying field effect transistor by increasing the threshold voltage required to cause it to conduct current. A negatively charged floating gate works to counteract the field induced by the positive control gate voltage, causing cells whose floating gates have been charged to conduct less current than they would otherwise when a voltage is applied to their control gates. This property can then be exploited to interpret logic values from the differently charged cells as follows: connect the source and drain terminals of the cell to a read circuit and apply a test voltage,  $V_{read}$ ; an uncharged cell will readily conduct current from its source to its drain when  $V_{read}$  is applied to its control gate, while a transistor that has been written to by having electrons stored on its floating gate will produce a proportionally lower current. A logic value can then be associated with each current level, usually 1 for high current and 0 for low current [5].

#### 1.2.2 NAND and NOR Flash

There are two common types of flash memory: NAND and NOR, named so for the way in which the operation of the cells of these memories resembles the operation of a NAND or a NOR logic gate, respectively [4]. In both NAND and NOR memories, cells are arranged in a grid, with each "row" defined by a common word line connected to the control gate of each cell in the row, and each "column" sharing a bit line which connects to the drain of one or more of the cells in the column. The key difference between NAND and NOR flash is that, in a NOR flash, each cell in a column connects to the bit line individually and in parallel, while NAND flash allows multiple cells to share a single connection to the bit line by wiring groups of them in series from source to drain, with only the first transistor in the series connecting to the bit line directly. Each cell (or group of cells) then has its remaining source terminal connected to a source line, which completes the read circuit.

To read a given row in a NOR flash, the word line for that row is energized to  $V_{read}$  while all other rows on the same bit are set to a lower voltage,  $V_{off}$ . If the floating gate of the cell(s) being read are not charged, current flows between the bit line and the source line(s) and the flash memory read circuit will interpret this as a logic 1; charged cells . NOR flash gets its name from the fact that this read operation resembles the operation of a NOR gate: if all gates on a bit line are open, the bit line voltage remains high (as the source line is typically connected to ground), but if a single gate conducts the bit line is pulled low [5].

Reading from a row in NAND is slightly less straightforward than in NOR flash due to the wiring of cells in series. To read from a NAND memory, the word line of the row to be read is again energized to  $V_{read}$ , but, in order for the entire series-cell group to conduct from their shared source line to the bit line, the rest of the cells in the group must also conduct. To accomplish this, the word lines which connect to the other cells in the group are set to some voltage,  $V_{on}$ , which is greater than  $V_{read}$ , forcing these cells to conduct regardless of their charge state. If the cell(s) in the row being read are uncharged, they will once again close when  $V_{read}$  is applied and the entire series of cells in each column will conduct from bit line to source line, causing a logic 1 to be interpreted. Otherwise, a charged gate will cause the series to fail to conduct, resulting in a read value of 0. As in a NAND gate, if all gates close the bit line will be pulled to ground, while a 0 on any of the series gates will allow the bit line to remain high [5].

NAND flash contains fewer connecting elements per cell than a comparable NOR flash, giving NAND-based flash designs a significant storage density advantage and making them smaller and cheaper to produce than a NOR memory of equivalent capacity [6]. NAND flash also benefits from faster write speeds compared to NOR flash. These two features make NAND flash the preferred memory type for flash-based file storage, where high capacity and the ability to quickly write data are higher priorities. By contrast, NOR flash offers faster random read times due to the fact that each cell is directly connected to a bit line; NAND flash offers similar *sequential* read performance (i.e. reads to consecutive rows in the same group), but is much slower to read randomly. Because of its ability to perform fast random access reads, is preferred for ROM-type storage and code execution, but is slower to program and erase, and is thus not suited for large-scale file data storage from either a cost or a performance standpoint. Because the focus of this report is on improving write performance for flash storage devices, our implementations are primarily applicable to NAND flash memories, although the principles still technically apply to both.

### **1.3** Solid State Drives

A secondary storage device that uses flash (particularly NAND flash) memory to store data is called a **solid state drive**, or SSD. The flash memory in an SSD is physically organized into a hierarchy of progressively larger units of storage according to the structural relationships between the cells therein. Flash memory cells are arranged, in order of increasing units of size, as follows: a group of cells connected by a common word line constitutes a **page**; a group of pages embedded in a common substrate constitutes a **block**; groups of blocks which share an independent set of accessing hardware are known as **planes**; and one or more planes connected to a single memory controller, which is responsible for interpreting and executing memory commands [7], [8]. Pages and blocks, in particular, are of special significance to the operation of the SSD due to the way cells are structured in these organizational units.

Because the word line is the component that is used to select a row of cells for reading or writing, all cells on the same word line are accessed at the same time when the word line is asserted. This makes page size a defining feature of the device architecture, as each read and write operation to an SSD must be facilitated at the hardware level in units of pages; not all of the cells of a page will necessarily have their values changed or transmitted back to the accessing device, but an operation on part of a page can occur no faster than the time it takes to access the whole page, so aligning access to page boundaries - reading or writing to one full page instead of two half-pages whenever possible, for example - is necessary for optimal drive performance. Chapter 4 discusses page size and its effects on storage performance in more detail.

All memories must be writable at least once to be given a meaningful value, but in order for a memory to be *re*writable, it must be capable of reversing this process as well. For a memory with some preferred initial state or value, the processes of altering and restoring this value to the cells of such a memory are known respectively as **programming** and **erasing**; in an SSD, programming a cell thus sets its value to 0 while erasing the cell returns its value to 1. Many memories, including magnetic storage devices, can be programmed and erased symmetrically, meaning that programming and erasing are roughly equivalent processes, only differing in the value they assign to a memory's cells [8]. This allows such memories to rewrite previously programmed memory locations in-place, directly programming and erasing cells as necessary without any additional steps. Flash memories, however, are *asymmetric* write devices; their cells can be programmed in pages, but can only be erased an entire block - usually 64 or 128 pages - at a time.

Erasing in blocks means that writes to occupied regions of the device can potentially be much slower than writes to "empty" drive space; if a write to just a single page in a block requires a 1 to be written where a 0 was previously, the SSD then has to make a copy of each page in the block that contains valid data before erasing the entire block, writing the new data to the page that was originally being accessed, then re-writing the saved page data back to all the pages that were copied out beforehand. These additional operations are all performed by the SSD memory controller and happen transparently to the accessing system, so an occasional read-erase-write cycle has fairly minimal impact on drive performance, but frequent writes of this type can severely reduce the average write speed of the device [9]. This block erase property is one of the main limitations of this technology, and is the primary motivation for this report.

#### 1.3.1 SSD Memory Management and the Flash Translation Layer

Fortunately, modern flash storage devices have a number of techniques at their disposal to reduce the occurrences of this worst-case behavior and avoid having to perform costly read-erase-write cycles: nearly all SSDs incorporate some form of address translation, called the flash translation layer (FTL), in order to abstract their physical memory from the logical addresses used to access the device [10] [11]. Essentially, the FTL allows the SSD to maintain a dynamic one-to-one or manyto-one association of logical storage addresses to physical pages in flash. This provides accessing devices with a consistent *logical* interface to the SSD (i.e. data written to address n will always be found at address n) while allowing the SSD memory controller a much greater degree of control over how data is managed physically.

Figure 1.1: A mock-up of the SSD's internal memory structure, with pages in green, blocks in blue, and the plane in gray

One advantage to this approach is that the SSD can process write requests intended to update some data already present at a given logical address by writing the new data to a **fresh** page, one that has not been written to since it was last erased, and updating the page association for that address in the address translation table. This method of writing allows the SSD to avoid having to erase blocks when storing modified data while providing seamless operation from the perspective of the accessing device. The previous page is then marked as **stale** to indicate that it no longer contains useful information and can be safely erased at a later time; one strategy used by SSD memory controllers is to try to group as many of these stale pages as possible into the same block to maximize the efficiency of each erase operation. Unfortunately, as more information is written to the drive and the number of unoccupied pages dwindles, the SSD is left with fewer possible pages in which to store modified data, increasing the likelihood of a read-erase-write cycle occurring. As a method of augmenting the SSDs own storage management abilities to further reduce the occurrence of block erase cycles at write time, a type of data encoding known as a **rewriting code** is proposed to enable restricted in-place modifications to data values in flash [3].

#### **1.3.2** Write-Once Memories and Rewriting Codes

The concept of rewriting codes was originally developed as a method of allowing multiple writes to write-once memories, or WOMs [12]. As the name implies, a WOM is a type of memory in which the act of programming a bit permanently and irreversibly alters the physical structure of the storage mechanism, meaning that this type of memory can usually only be practically written once: unaltered bits can still technically programmed, but programmed bits cannot be erased, making useful modifications to such memory unlikely at best without a methodology for organizing these bits. Rewriting codes are designed to do just that; by encoding information in such a way as to preserve a specific set of bits for future writes, these codes can enable arbitrary repeat writes to a storage medium without the need (or the ability) to erase bits. Apart from allowing limited re-use of physically limited write-once media, this concept can be extended to other memories such as flash; while not technically a WOM in and of itself, flash can be considered a type of quasi-WOM due to the relative difficulty of erasure on such a device.

To preserve a write-once memory for future writes, previously developed codes have taken advantage of sparse encoding techniques to spread out the information contained in a given value over a larger-than-normal memory area while ensuring that a certain number of the bits therein remain un-programmed [12], [13]; these sparsely encoded initial values can then be modified by writing to the preserved memory bits, thus "rewriting" that value in memory. Because they occupy more space in memory, rewriting codes generally present a trade-off between total storage volume (i.e. the amount of information that can be represented by the memory at a given instant) and number of possible rewrites for a given memory. At first glance, this would seem no better than just artificially limiting the amount of data that can be written to the memory at one time, thus ensuring that some memory regions will be available for additional writing without the need for a complex data coding process. However, apart from securing some number of additional writes by virtue of the way in which it represents information, the real benefit of a rewriting code is that it can actually allow more information to be written to the memory cumulatively over the total number of writes supported than would have been otherwise possible; even though each encoding, in and of itself, requires more memory to represent the same value, the total number of data bits it is able to represent over all writes should, ideally, be greater than the number of memory bits needed to store that encoding.

Because of this property, a rewriting code can be thought of as a type of compression algorithm, but instead of deriving its compression performance from the reduction of a single data object's memory footprint as much as possible for a single write, a rewriting code, as its name implies, attempt to maximize the utility of the memory over *multiple* writes. One obvious drawback to this approach is that, in many of these rewriting codes, the rewriting process is destructive to the existing data; whereas writing two data sets encoded using a traditional approach to data compression allows for the retrieval and decoding of both sets once written, a rewriting code typically only supports the retrieval of the most recently encoded values [12], [13]. However, it is also possible to use rewriting codes as "compression boosters," applying them in conjunction with other methods of data encoding to achieve a combined compression effect [3].

# 2. The KS-Code

Prior literature suggests the use of a particular rewriting code [3], which this report refers to as the **KS-code**, based on a method of representing integral values as a particular summation of the members of the Fibonacci series known a **Zeckendorf sum**. These sums hold certain properties that, when represented in binary, guarantee a particular arrangement for the represented data which can then be exploited to allow a second write "into" a previously stored value.

### 2.1 Primary Encodings

While there are infinitely many ways of arriving at a given integer by summing members of the Fibonacci series, two properties must be obtained in order for such a sum to be considered a Zeckendorf sum: first, no elements in the series may be repeated - each Fibonacci number can appear at most once in the sum; second, the sum must not contain any two *consecutive* Fibonacci numbers, as Zeckendorf sums are *minimal* sums of the Fibonacci series, and any two consecutive Fibonacci numbers can be represented more minimally by replacing them with the value of their sum, which is also a Fibonacci number by definition [14]. As an example, consider the number 29: while it is natural to think of this number as the sum of the numbers 20 and 9 in base-10, or even  $2^4 + 2^3 + 2^2 + 2^0$  in (base-2) binary, we can also represent this value, using Fibonacci numbers, as the sum of 21 and 8, which are the  $8^{th}$  and  $6^{th}$  numbers in the Fibonacci series, respectively. Zeckendorfs theorem posits that any integer can be uniquely represented as the sum of one or more non-consecutive members of the Fibonacci series [14], and it is this property of non-consecutiveness that forms the basis of the KS rewriting code.

Of course, when storing these encodings on a computer, there are still only two digital values with which to represent them, so how is this done efficiently? Fortunately, because Zeckendorf sums contain no repeat elements (i.e. it will never be necessary to count more than 1 of each Fibonacci number in the sum), these sums can be encoded as a simple binary sequence, where a 1 represents the presence of a given Fibonacci number in the sum, and 0 the absence. After all, the typical base-2 binary encoding, or **standard encoding**, merely represents the sum of a series of consecutive powers of two; by mapping each index of a string of binary digits to a member of the Fibonacci series rather than a power of two, a Zeckendorf sum can be represented in the binary numeral system, producing a **Zeckendorf encoding** [14]. Returning to the above example, the Zeckendorf encoding of 29 can be produced by examining the first 9 members of the Fibonacci series, which are (in descending order): 21, 13, 8, 5, 3, 2, 1, 1, and 0. Rewriting 29 as a Zeckendorf encoding, with its Zeckendorf sum members being 21 and 8, produces 21 \* 1 + 13 \* 0 + 8 \* 1 + 5 \* 0 + 2 \* 0 + 1 \* 0 (omitting the first two elements in the series, as the repeated 1 is unnecessary and the value of 0 is implied by an empty sum), or just 101000. More generally, it is possible to represent any Zeckendorf sum Z as the sum-product of a series of n bits, b, and the Fibonacci series F (again, omitting the first 0 and 1), or:

$$Z = \sum_{i=0}^{n-1} F_i b_i = F_{n-1} b_{n-1} + F_{n-2} b_{n-2} + \dots + F_0 b_0$$

$$F_0 = 1, F_1 = 2, F_i = F_{i-1} + F_{i-2} \text{ for } i \ge 2$$

(2.1)

The Zeckendorf sum of a given (non-negative) integer value can be calculated in linear time with respect to the size of the input value using a greedy algorithm [14]: for any number in the Fibonacci series that is less-than or equal to the input value, starting with the largest Fibonacci number that satisfies this condition, add that series element to the sum and subtract its value from the value of the input, then move on to the next smaller Fibonacci number and repeat this process with the remainder of the input value until that remainder becomes 0. Translating data from its standard form to this new Zeckendorf form constitutes the encoding portion of the first round of the KS-code, the product of which will be referred to as a **primary encoding**. A primary encoding can then be decoded by simply calculating the unsigned, base-2 integer sum of the series elements in the encoding.

### 2.2 Secondary Encodings

As the previous section alludes, Zeckendorf sums posses an important property for this rewriting code: each of these sums must, by definition, be composed of non-sequential members of the Fibonacci series. Applied to the binary encoded forms of such sums, this property implies that any two 1-bits in the binary string of such an encoding must be separated by at least one 0-bit; stated another way, it can be assumed that each 1 in an encoding will be followed by at least one 0 (with the notable exception of the last bit in the series). These leading 1s are referred to as **separator** bits, with the bit immediately following each separator being designated a data bit [3]. Note the significance of these so-called data bits: the primary encoding guarantees that each 1 is followed by a 0, so the values of these data bit in the primary encoding are initially implicit. As they have a fixed value of 0 and thus do not represent any value in the encoding, their only function in this case is to act as placeholders to denote the position of the "skipped" elements in the encoded series' summation. Once a primary encoding has been produced, the actual values of the data bits therein are essentially irrelevant to the interpretation of the Zeckendorf summation's value (as they can be inferred as 0's during the decoding of the encoded sum and skipped entirely), meaning that it is possible to alter the values of these bits without actually changing the interpretation of the initial encoding. Thus, for each separator bit that appears in a binary-encoded Zeckendorf sum, an additional bit of data can be stored by setting the corresponding data bit to the desired value. The process of writing to the data bits in a primary encoding constitutes the second round of the rewriting code, with the "re-written" primary encoding becoming a secondary encoding. Both data sets can still be retrieved from the encoding after a second-round write by scanning through the resulting secondary encoding and identifying the separator-data bit pairs; the separator bit can still be interpreted as a member of the Zeckendorf sum used to encode the primary data value, and the data bit represents one bit of the secondary data value. More to the point, because each data bit has the same value initially, it is possible to perform this secondary write operation without causing any bits to be erased.

Unfortunately, Zeckendorfs theorem only implies at least one 0-bit after each sentinel, meaning that no assumptions can be made about any possible additional bits based solely on the encoding itself, and it is for this reason that only one additional bit of data can be stored in the secondary encoding for each separator bit. More specifically, each separator-data bit pair in a primary encoding may or may not be followed by one or more 0-bits; if we were to use these bits for secondary data storage, setting any of these bits to a value of 1 would make them indistinguishable from another separator bit during decoding (as it can only be assumed that the *one* bit after each separator will not be another separator). These additional bits are called **extension bits**, and a source of performance loss for this rewriting code. Mitigating the deleterious effects of these extension bits on the overall compression performance of the encoding is key to maximizing the effectiveness of the rewriting code.

#### 2.2.1 Padding

While the ability to store multiple data values in a single Zeckendorf encoding can be potentially beneficial, this method of storage is highly inconsistent from a compression performance perspective: the total number of data bits which can be stored within the secondary encoding is entirely dependent on the data that was initially used to create the primary encoding. Again, secondary data can only be stored in the single bit immediately following each separator 1-bit in the encoding, so an encoding in which the Zeckendorf sum of the input value contains fewer elements (and thus fewer 1's) will have very little potential for secondary storage. In general, a binary-encoded Zeckendorf sum of length n can contain anywhere between 0 and  $\frac{n}{2}$  separator bits, with an encoding containing no 1's being the worst case (i.e. an encoded value of 0), and a pattern of alternating 1's and 0's (which corresponds to the largest encoded value possible for a given number of encoding bits) representing the optimal case for secondary encoding. To mitigate this uncertainty problem and minimize the number of extension bits present in the encoding, a **padding scheme** is added to the rewriting process to "insert" as many 1-bits into the encoding as possible (without violating the sparseness property) in order to maximize the number of data bits available for the secondary encoding [3]. Padding a primary encoding raises the lower bound on the number of data bits in the encoding from 0 to  $\frac{n}{3}$  for an n bit encoding: sets of three or more consecutive 0's in a bit string can accept an additional 1 without creating any adjacent 1's, but any pattern which contains just two consecutive 0's cannot be padded further without violating the all-important sparseness property, resulting in one separator bit (and thus one data bit) for every three bits in the worst case. The padding process is also irreversible, meaning whatever data value that was initially used to produce the primary encoding will be destroyed. As such, padding is only used to condition data which is no longer needed in order to maximize the utility of the data for storage in the secondary writing process. An illustration of the padding and secondary encoding process is shown in figure 2.1.

| 1 | 0 | 0        | 0 | 0        | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

|---|---|----------|---|----------|---|---|---|---|---|---|---|

| 1 | 0 | <u>1</u> | 0 | <u>1</u> | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | <u>1</u> | 0 | <u>1</u> | 0 | 0 | 1 | 1 | 0 | 1 | 1 |

**Figure 2.1:** A Zeckendorf encoding  $(F_{11} + F_4 + F_1 = 243)$  (top) is padded (center), with additional separator bits underlined and extension bits boxed; the encoding is then overwritten with the number 19 (bottom), shown in bold.

### 2.3 Extended Fibonacci Series

While the description and examples of the KS-code thus far have focused on summations of the classic Fibonacci series, the principles of the rewriting code described can be applied to any method of encoding with similar properties. Recall the Fibonacci series F, recursively defined as  $F_i$  =  $F_{i-1} + F_{i-2}$  with base cases  $F_1 = 2$  and  $F_0 = 1$ . By modifying this recursion, it is possible to create a related series which, when used to encode data in the same fashion as before (i.e. binaryencoded series sums), produce binary strings with variations of the sparseness property described above. In fact, the Fibonacci series belongs to an infinite set of recursive series whose members can be described generally as any series A with a **series degree** of m, denoted as  $A^{(m)}$ , such that  $A_i^{(m)} = A_{i-1}^{(m)} + A_{i-m}^{(m)}$ , with base cases  $A_i^{(m)} = i + 1$  for  $0 \le i < m$  [15]. This allows us to produce alternate primary encodings, based on any one of these  $A^{(m)}$  series for some fixed degree  $m \ge 2$ , <sup>1</sup> which posses the property that each 1-bit in the encoding will be followed by at least m-1Os (again with the exception of separator bits appearing in the final m-1 bits of the encoding). All such encodings remain compatible with the padding and secondary read/ write processes as applied to the Fibonacci (or  $A^{(2)}$ ) encoding scheme, but with additional data bits read and written after each separator. These extended Zeckendorf encodings can thus be used to fine-tune the overall compression algorithm by leveraging higher order encoding series to modify the sparseness properties of the primary encoding, which may prove to be advantageous for encoding different types of data or for different usage patterns.

### 2.4 Compression Performance

Like other rewriting codes, data encoded in the initial round of the KS-code is expanded, requiring more memory bits to represent than it would in its standard form; over both rounds of writing, the goal is to cumulatively write more bits of *information* than the number of memory bits written to, with the **compression ratio** of the encoding defined as the ratio of the total amount of information written over the number of memory bits used. In the example above, the number 29, which is a 5-bit value in its standard form, is represented as a 6-bit binary Zeckendorf sum, 101000, for a round-one expansion factor of  $\frac{6}{5} = 1.2$ ; this value can then be padded with an additional separator bit, to 101010, for a total of 3 secondary storage bits and an overall compression ratio once overwritten of  $\frac{5+3}{6} = 1.333$ . For a sufficiently large number of bits encoded, n, this expansion can be approximated by  $\frac{n}{\log_2(\phi)} \approx 1.44n$ , or an expansion of roughly 44% over the standard encoding [3]. However, like other rewriting codes, this particular method of representing data makes up for the reduction in immediate storage capacity with improvements to the overall "write capacity" of the memory: the first write will store n bits of information in 1.44n bits of memory as a primary encoding, then a first write will store *n* bits of information in 1.44*n* bits of memory as a primary encoding, encoded second write will allow re-use of up to half of these memory bits, for another  $\frac{1.44n}{2}$  information bits stored, resulting in a best case compression ratio of  $\frac{n+0.72n}{1.44n} = \frac{1.72}{1.44} \approx 1.194$ . Even in the worst case, where only one in *three* bits can store secondary data, it is still possible to store  $n + \frac{1.44n}{3}$  bits of information across the same 1.44*n* storage bits, yielding a compression ratio of  $\frac{n+0.48n}{1.44n} = \frac{1.48}{1.44}$ , or approximately 1.028. Thus, even in the worst case, the KS-code (with degree 2) still manages to store slightly more information bits over two writes than the number of storage bits that were used to represent that information.

<sup>&</sup>lt;sup>1</sup>An interesting observation: the series  $A^{(1)}$  actually represents the standard binary series, 1, 2, 4, 8, 16..., and so data represented by the standard binary encoding could be said to represent a particular sum of this variant of  $A^{(m)}$ .

Using a series of a higher degree incurs a higher initial storage space penalty: as degree increases, the resulting series tends to grow more slowly, requiring more bits to represent a given value. This data expansion can generally be described as a function of degree m according to  $n \log_{\phi_m}(2)$ , where n is the number of bits to be encoded and m represents the dominant root of the characteristic equation of the series Am, xm - xm - 1 - 1 = 0; as m increases,  $\phi_m$  asymptotically approaches 1, so the expansion factor,  $\log_{\phi_m}(2)$ , becomes increasingly large [3]. However, while the initial storage penalty is greater when compared to a lower encoding degree, a higher degree series can potentially offer better write compression overall due to the presence of additional secondary data bits; table 2.1 lists the minimum and maximum theoretical compression ratios for the first nine degrees of series encodings (starting with the Fibonacci series,  $A^{(2)}$ ), as well as their overall primary expansion factors.

|        | 00 10 11014      |        |        |

|--------|------------------|--------|--------|

| Degree | Expansion Factor | Min CR | Max CR |

| 2      | 1.440            | 1.0217 | 1.1957 |

| 3      | 1.813            | 0.9483 | 1.2069 |

| 4      | 2.151            | 0.8971 | 1.2206 |

| 5      | 2.465            | 0.8462 | 1.2051 |

| 6      | 2.763            | 0.8182 | 1.1932 |

| 7      | 3.047            | 0.7835 | 1.1856 |

| 8      | 3.321            | 0.7642 | 1.1698 |

| 9      | 3.587            | 0.7456 | 1.1667 |

| 10     | 3.846            | 0.7317 | 1.1545 |

Table 2.1

Data Expansion Factor and Theoretical Min/ Max Compression for Encoding Degrees 2 to 10 Inclusive

An interesting pattern to note: minimum compression ratios go down as series increases degree due to the greater possible number of extension bits as a proportion of the total number of bits in the encoding, but maximum compression ratio increases up to a point, peaking at approximately 1.221 for an encoding degree of 4, before the number of bits needed to represent the encoding begins to outgrow the amount of information being represented. For lower encoding degrees, this means that there is a trade-off between maximizing potential secondary storage in the best case and mitigating storage waste in the worst case. Our analysis is restricted to encoding degrees 2 to 10, inclusive, as it would appear that higher order series, at least in theory, offer no compression benefit, as a steady decline in both minimum and maximum performance is observed for degrees greater than 4. It is certainly possible that some use case exists for higher degree encodings in practice due to some as-yet unforeseen property of the data, but, in general, higher degree encodings seem to yield diminishing returns on potential compression performance.

# 3. Implementation

We developed two implementations to facilitate the encoding and decoding of data according to the KS-code: one as a set of software functions, the other a hardware logic circuit design. We wrote the software first as a "proof of concept," allowing us to become familiar with the KS-code and its mechanisms and to develop the initial sketches for a general set of coding algorithms. Later, the software became useful as a method of testing file data properties, as several test batches could be performed fairly quickly on various files to determine how the code fared in terms of compression performance for various files. This source code is provided here with a header file in addition to main execution logic, and can thus be compiled as either a standalone utility or as a software library.

The hardware shares many of the logical design cues from the software, and is based on the same general algorithms, relying on sequential, clocked logic to drive the state-based calculations that make up the KS-code. Although we recognize that hardware *cannot* be written as software, and despite the fact that the specific implementations do differ in some key aspects, many of the coding processes are nevertheless highly state dependent, lending themselves much more readily to sequential designs. In hardware, each coding function is implemented as a separate module, with the total set of modules being packaged together to form a single encoding unit which is capable of performing the full suite of coding tasks. We developed these modules using the SystemVerilog HDL, which afforded a convenient means by which to define and test a circuit specification that could then be distributed and synthesized for any platform, be it an FPGA or some ASIC design. Source code for both designs is available in appendix A.

### 3.1 Algorithms

This section provides pseudo-code representations of the algorithms developed in the course of this implementation, illustrating the basic logic used for each coding process. The hardware and software implementations both share this same logic design, and so these algorithms can be thought of as the "blueprints" for their design.<sup>1</sup> Each algorithm is described in terms of the function it performs within the context of the coding scheme, with a separate name given to describe each of the five fundamental operations thereof: creating a primary encoding; decoding a primary encoding; padding a primary encoding; creating a secondary encoding; and decoding a secondary encoding. These operations or processes are respectively referred to as "encoding", "decoding", "padding", "overwriting", and "extracting". The first three of these are self-explanatory; overwriting and extracting, however, are new terms used to distinguish the encoding and decoding processes used in the second round of this rewriting code's operation from those in the first, and are in a sense more descriptive as to what task these processes perform.

<sup>&</sup>lt;sup>1</sup>Specific implementation details, unless relevant to the content of this discussion, are omitted here for brevity and clarity. Implementation source code can be found in appendix A for complete details on how each of these algorithms are applied in their respective implementations.

Each of these algorithms relies on bit-wise access to at least one if its inputs or outputs, so it is important to note that such access in each of these algorithms is exclusively performed from most to least significant bit. Any access to a bit at a particular index should interpreted such that index 0 is the most significant, 1 is the next most significant, and so on.

#### 3.1.1 Encoding Algorithm

```

Encode(DATA_SET, DEG):

SERIES := {extended Fibonacci series of degree DEG}

ENCODE_SET := {}

while DATA_SET is not empty

DATA := next element in DATA_SET

ENCODING := 0 // Size in bits equal to length of SERIES

for each ELEMENT in SERIES in descending order

if DATA >= ELEMENT

subtract ELEMENT from DATA

set corresponding bit in ENCODING to 1

endif

endfor

append ENCODING to ENCODE_SET

endwhile

return ENCODE_SET

```

For each discrete data element, DATA, in a set of data elements, DATA\_SET, iteratively compare that element's value - interpreted as an unsigned integer - to the members of the extended Fibonacci series, SERIES, generated by degree, DEG, in descending order. If the value of the DATA is greater than or equal to that of the current ELEMENT in the SERIES, decrement the DATA value by the value of the ELEMENT and set the bit corresponding to ELEMENT in the ENCODING to 1; ENCODING bits correspond to SERIES elements such that the most significant bit in the ENCODING represents the largest element in the SERIES, the second most significant bit represents the second element, and so on. Continue this process until all SERIES elements have been considered, then append the resulting ENCODING to a list of encodings, ENCODE\_SET, and begin the process again with the next element in DATA\_SET until all elements in the set have been processed.

#### 3.1.2 Decoding Algorithm

```

Decode(ENCODE_SET, DEG):

SERIES := {extended Fibonacci series of degree DEG}

DATA_SET := {}

while ENCODE_SET is not empty

ENCODING := next element in ENCODE_SET

DATA := 0

```

```

for each BIT in ENCODING

if BIT == 1

add corresponding element of SERIES to DATA

endif

endfor

append DATA to DATA_SET

endwhile

return DATA

```

For each discrete encoding, ENCODING, in a set of encodings, ENCODE\_SET, iteratively examine each BIT in the ENCODING, starting with the most significant bit. If the BIT has a value of 1, add the value of the corresponding element in the Fibonacci series, SERIES, and generated by degree, DEG, to the DATA value being calculated. Continue until all bits in the ENCODING have been examined, then append the resulting DATA value to a list of data values, DATA\_SET, and begin the process again with the next encoding in ENCODE\_SET until all elements in the set have been processed.

#### 3.1.3 Padding Algorithm

```

Pad(ENCODE_SET, DEG):

PADDED_SET := {}

while ENCODE_SET is not empty

ENCODING := next element in ENCODE_SET

ZERO_COUNT := DEG - 1

for each BIT in ENCODING

if BIT == 0

add 1 to ZERO_COUNT

else

ZERO_COUNT := 0

endif

if ZERO_COUNT == (2*DEG - 1)

set the bit in ENCODING at DEG-1 positions prior to the \leftrightarrow

current BIT to 1

subtract DEG from ZERO_COUNT

endif

endfor

if ZERO_COUNT >= DEG

set bit in ENCODING at ZERO_COUNT - DEG positions from the \leftrightarrow

end of the ENCODING to 1

endif

append ENCODING to PADDED_SET

```

#### endwhile

return PADDED\_SET

For each discrete encoding, ENCODING, in a set of encodings, ENCODE\_SET, iteratively examine each BIT in the ENCODING, starting with the most significant bit. Count the number of consecutive bits in the encoding by incrementing a counter for every BIT value of 0, and reset the counter if the BIT value is 1. The counter is initialized to DEG-1 to allow padding a 1 within the first DEG bits of the encoding, as the bits prior to each individual encoding have no effect on their correctness. If the count of consecutive 0 bits reaches DEG\*2 - 1, pad this run of 0's by setting the bit located DEG-1 positions prior to the current BIT to 1, splitting the current string of 0's into two strings of DEG-1 0's separated by a 1, then set the counter to DEG-1 to reflect the reduction in the number of consecutive 0 bits. Continue until all bits in the ENCODING have been examined. Once the end of the encoding is reached, if the remaining count of consecutive 0's is still greater than or equal to DEG, place an additional 1 in the bit whose index matches this count, minus the degree DEG; this can be done due to the fact that there does not necessarily have to be a full DEG-1 0's after the final 1 bit in the encoding. Append the ENCODING to a list of padded encodings, PADDED\_SET, and begin the process again with the next encoding in ENCODE\_SET until all elements in the set have been processed.

#### 3.1.4 Overwriting Algorithm

```

Overwrite(ENCODE_SET, DATA_SET, DEG):

OVER_SET := {}

while ENCODE_SET is not empty

ENCODING := next element in ENCODE_SET

WRITE_BITS := 0

DATA_IDX := 0

for each BIT in ENCODING

if DATA_IDX == 0

if DATA_SET not empty

DATA := next element in DATA_SET

else

append ENCODING to OVER_SET

return OVER_SET

endif

endif

if WRITE_BITS > 0

set BIT to value of bit in DATA at DATA_IDX

decrement WRITE_BITS

increment DATA_IDX, wrapping to 0 on the last bit

else if BIT == 1

WRITE_BITS := DEG - 1

endif

endfor

```

```

append ENCODING to OVER_SET

endwhile

return OVER_SET

```

For each discrete encoding, ENCODING, in a set of encodings, ENCODE\_SET, iteratively examine each BIT in the ENCODING, starting with the most significant bit. Retrieve a data element, DATA, from a data set, DATA\_SET, on the first iteration and any subsequent iterations where the current DATA has been completely encoded. If the BIT value is 1, set a counter to one less than the degree, DEG, of the ENCODING. On subsequent iterations, if this counter is greater than zero, set the value of the current BIT in the ENCODING to one of the bits in DATA, starting with the most significant bit and continuing in order of decreasing significance in later iterations until the DATA has been completely encoded to the prior ENCODING. Decrement the counter after each bit written. Once every BIT in ENCODE has been examined, append ENCODE to a list of overwritten encodings, OVER\_SET, and begin the process again with the next element in ENCODE\_SET until all elements have been processed from either ENCODE\_SET or DATA\_SET.

#### 3.1.5 Extracting Algorithm

```

Extract(OVER_SET, DEG):

DATA_SET := {}

while OVER_SET is not empty

OVER := next element in OVER_SET

READ_BITS := 0

DATA_IDX := 0

DATA := 0

for each BIT in OVER

if READ_BITS > 0

if BIT == 1

set bit in DATA at DATA_IDX to 1

endif

decrement READ_BITS

increment DATA_IDX, wrapping to 0 on the last bit

if DATA_IDX == 0

append DATA to DATA_SET

clear value of DATA

endif

else if BIT == 1

READ_BITS := DEG - 1

endif

endfor

endwhile

return DATA_SET

```

For each discrete encoding, OVER, in a set of encodings, OVER\_SET, iteratively examine each BIT in OVER, starting with the most significant bit. If the BIT value is equal to 1, set a counter to DEG-1. On subsequent iterations, if this counter is greater than 0, copy the value of BIT to a decode value DATA, starting with the most significant bit, and decrement the counter. As long as the counter is greater than 0, the value of bit is ignored for the purposes of setting this counter to avoid misinterpreting data bits as separator bits in the secondary encoding. Once a DATA element has been filled with bits extracted from OVER, append it to a list of data elements, DATA\_SET. Once the end of an encoding, OVER, has been reached, retrieve the next encoding from OVER\_SET and continue extracting until all elements have been processed.

# 3.2 Encoding Unit Size and Performance Analysis