# Cleveland State University EngagedScholarship@CSU

**ETD** Archive

2009

# A Frequency Response Based Approach to DC-DC Control Loop Design

Jack Andrew Redilla Cleveland State University

Follow this and additional works at: https://engagedscholarship.csuohio.edu/etdarchive Part of the <u>Electrical and Computer Engineering Commons</u> How does access to this work benefit you? Let us know!

#### **Recommended** Citation

Redilla, Jack Andrew, "A Frequency Response Based Approach to DC-DC Control Loop Design" (2009). *ETD Archive*. 434. https://engagedscholarship.csuohio.edu/etdarchive/434

This Thesis is brought to you for free and open access by EngagedScholarship@CSU. It has been accepted for inclusion in ETD Archive by an authorized administrator of EngagedScholarship@CSU. For more information, please contact library.es@csuohio.edu.

# A FREQUENCY RESPONSE BASED APPROACH TO DC-DC CONTROL LOOP DESIGN

JACK ANDREW REDILLA

Bachelor of Electrical Engineering

Cleveland State University

August, 1989

Submitted in partial fulfillment of requirements for the degree

MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

at the

CLEVELAND STATE UNIVERSITY

December, 2009

This thesis has been approved for the Department of Electrical and Computer Engineering and the College of Graduate Studies by

Thesis Committee Chairperson, Dr. Zhiqiang Gao

Department/Date

Committee Member Dr. Dan Simon

Department/Date

Committee Member Dr. Lili Dong

Department/Date

Committee Member Dr. Charles Alexander

Department/Date

### ACKNOWLEDGMENTS

Thanks go out to my thesis chairperson and thesis advisor, Dr. Zhiqiang Gao. I am extremely thankful to him for his providing knowledge, guidance, and expertise in the area of control theory. Most of all I am thankful for his patience and persistence in support during the completion of this thesis.

I would like to thank Dr. Dan Simon for his patience and perseverance when helping me to improve the content of this thesis. I would like to thank Dr. Lili Dong and Dr. Charles Alexander for being part of my thesis committee and providing support and comments after reviewing my work. I would also like thank Adrienne Fox and Jan Basch for opening up the door to the controls lab when I forgot my key. In addition, I would like to thank my fellow students: Dan Raybold and Dave Avanesian and Qing Zheng for helping me in the controls lab. Finally, I would like to thank my children Gina and Ryan Redilla for the unknowing sacrifice during the completion of this thesis.

# A FREQUENCY RESPONSE BASED APPROACH TO DC-DC CONTROL LOOP DESIGN

#### JACK ANDREW REDILLA

## ABSTRACT

This thesis encompasses control theory, mathematical models and practical methods for developing high performance control loops for compact DC-DC power converters. In this research we compare an existing hardware control loop design developed through traditional empirical tuning methods to a control loop established by a proposed systematic design approach. To address the many problems of ad-hoc controller design for DC-DC converters, we develop a procedure utilizing tools from frequency domain analysis and loop shaping techniques. This design approach is used to ensure control loop stability and to verify improved loop performance. This systematic control loop design procedure can be utilized for future development work to create improved DC-DC converter control loops. Our goal is to turn the art of traditional empirical tuning into a science by creating a systematic process utilizing tools that can quantify and define DC-DC converter control loop performance.

Mathematical simulations are used to verify the control loop models before hardware verification. Finally we compare resulting performance of the control loop circuitry designed with the proposed approach to that of the empirical approach.

# TABLE OF CONTENTS

| ABSTRACT iv                                      |

|--------------------------------------------------|

| LIST OF TABLES                                   |

| LIST OF FIGURES ix                               |

| NOMENCLATURE xii                                 |

| CHAPTER I INTRODUCTION1                          |

| CHAPTER II DC-DC CONVERSION                      |

| 2. 1 DC-DC Conversion Background5                |

| 2. 2 Concepts and Criterion for Loop Stability7  |

| 2. 3 Phase and Gain Plots9                       |

| 2. 4 Time Domain Characteristics 12              |

| 2. 5 Time Response Simulation Example15          |

| CHAPTER III IMPROVING THE CONTROL PERFORMANCE 17 |

| 3. 1 Improving the Feedback Loop17               |

| 3. 2 DC-DC Converter Technology 18               |

| 3. 3 Converter Topology and Basic Operation19    |

| 3. 4 DC-DC Converter Control System 22           |

| 3. 5 Buck Converter Duty Cycle Versus Vout       |

|    | 3. 6 Error Amplifier and PWM Signal                            | 26   |

|----|----------------------------------------------------------------|------|

|    | 3. 7 Output LC Filter Characteristics and Bode Plots           | 28   |

|    | 3. 8 The Bode Plots                                            | 30   |

|    | 3. 9 The Linear Time Invariant Representation                  | 31   |

|    | 3.9.1 Averaged Model                                           | 35   |

|    | 3.9.2 The Linear Model                                         | 36   |

|    | 3. 10 Open Loop Phase and Gain Margin of the Buck Converter    | 39   |

|    | 3. 11 Frequency Compensation and Circuit Implementation        | . 41 |

|    | 3.11.1 Lag Compensation                                        | 41   |

|    | 3.11.2 Lead Compensation                                       | 46   |

|    | 3.11.3 Lead-lag Compensation                                   | 48   |

|    | 3. 12 Straight Line Approximation with Lead-lag Compensation   | 51   |

|    | 3. 13 From Transfer Function Verification to Hardware Test     | 52   |

|    | 3. 14 Developing the Transfer Function                         | 55   |

|    | 3. 15 The Systematic Design Process                            | 63   |

| CI | HAPTER IV AN EXAMPLE OF THE PROPOSED DESIGN PROCESS            | 69   |

|    | 4. 1 Applying the Lead-lag Compensation to the Existing Design | 69   |

|    | 4. 2 Selecting the Lead-lag Compensation Components            | 71   |

|    | 4. 3 Comparison of the Existing versus the Improved System     | 76   |

| 4. 4 Simulation Results Versus Lab Results | 77 |

|--------------------------------------------|----|

| CHAPTER V SUMMARY AND FUTURE RESEARCH      | 79 |

| REFERENCES                                 | 83 |

# LIST OF TABLES

| Table      |                                       | Page |

|------------|---------------------------------------|------|

| TABLE I:   | Time Response Equations               | 14   |

| TABLE II:  | Generic Design Component Parameters   | 40   |

| TABLE III: | Lag Design Component Parameters       | 45   |

| TABLE IV:  | Lead Design Component Parameters      | 47   |

| TABLE V:   | Lead-lag Design Component Parameters  | 50   |

| TABLE VI:  | Unimproved Converter Component Values | 59   |

| TABLE VII: | Improved Converter Component Values   |      |

# LIST OF FIGURES

| Figure                                                                        | Page |

|-------------------------------------------------------------------------------|------|

| Figure 1: State Space Averaging Model for a DC-DC Converter                   | 7    |

| Figure 2: DC-DC Converter Closed Loop Configuration                           | 10   |

| Figure 3: Phase and Gain Plots                                                | 11   |

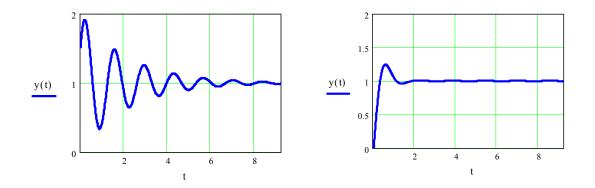

| Figure 4: Transient Response ( $z = 0.215$ )                                  | 15   |

| Figure 5: Transient Response (z=0.10)                                         | 16   |

| Figure 6: Transient Response ( $z = 0.5$ )                                    | 16   |

| Figure 7: DC-DC Converter Block Diagram                                       | 18   |

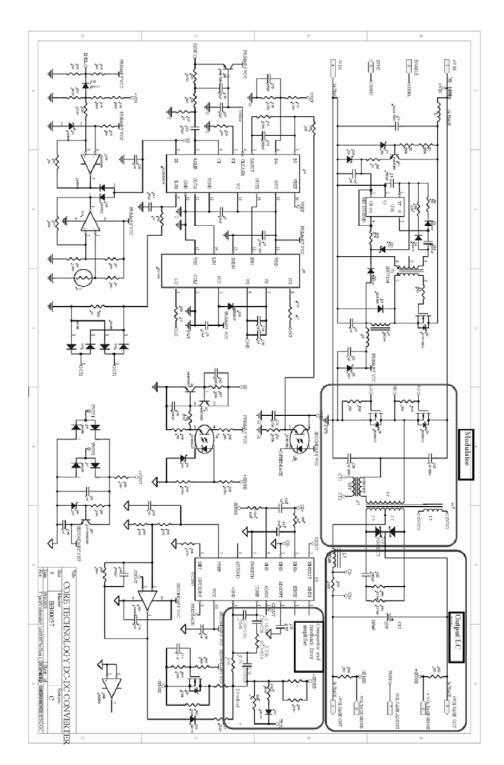

| Figure 8: Core Technology, Inc. Unimproved DC-DC Converter Schematic          | 20   |

| Figure 9: Unimproved LC Filter and Error Amplifier                            | 21   |

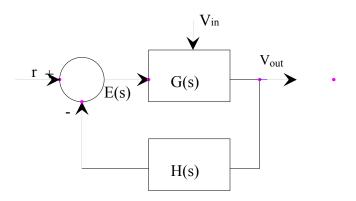

| Figure 10: Basic System Feedback Control Diagram                              | 23   |

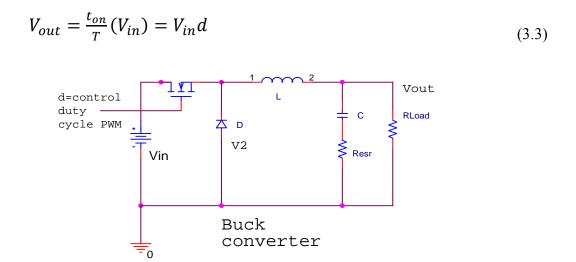

| Figure 11: Buck Converter Modeling Schematic                                  | 24   |

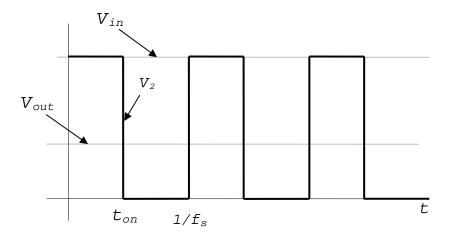

| Figure 12: Timing Diagram For ON/OFF Time for Power Flow                      | 25   |

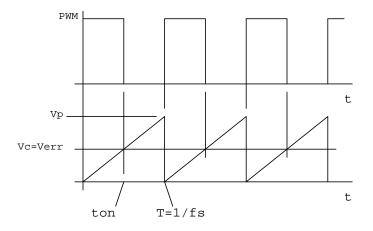

| Figure 13: Error Amplifier and Comparator to Generated PWM for the FET Drive. | 27   |

| Figure 14: Ramp, Verr and Generated PWM Signals for the FET Drive             | 27   |

| Figure 15: Output LC Filter                                                   |      |

| Figure 16: Phase and Gain Plots (Open Loop Plant)                             | 30   |

| Figure 17: Switched model Illustrating Mode 1 and 2                        | 32     |

|----------------------------------------------------------------------------|--------|

| Figure 18: Buck Topology Illustrating PWM Switched Model for Averaging Wav | eforms |

|                                                                            | 32     |

| Figure 19: PWM Switch Model and Corresponding Averaged Waveforms           | 33     |

| Figure 20: Resulting Averaged Model                                        | 35     |

| Figure 21: The Linearized Model of a Buck Converter                        | 36     |

| Figure 22: Generalized System Configuration for the Time Invariant Model   | 37     |

| Figure 23: Voltage Mode Control Flow Diagram                               | 37     |

| Figure 24: Generalized Control Law from Time Invariant Model               | 38     |

| Figure 25: Phase and Gain Plots                                            | 40     |

| Figure 26: Lag Compensated Error Amp                                       | 42     |

| Figure 27: Error Amp Lag Compensated Phase and Gain                        | 42     |

| Figure 28: Lag Compensated Gain Plot                                       | 45     |

| Figure 29: Lag Compensated Phase Plot                                      | 45     |

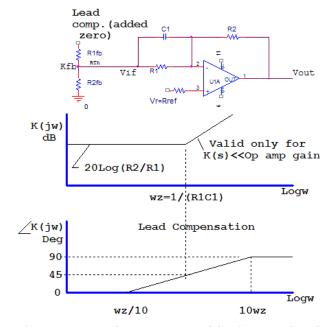

| Figure 30: Lead Compensated Error Amp with Phase and Gain Diagram          | 47     |

| Figure 31: Lead Compensated Gain                                           | 48     |

| Figure 32: Lead Compensated Phase                                          | 48     |

| Figure 33: Lead-lag Compensated Error Amp with Phase and Gain Diagram      | 49     |

| Figure 34: Error Amp Lead-lag Compensated Phase and Gain Plots             | 50     |

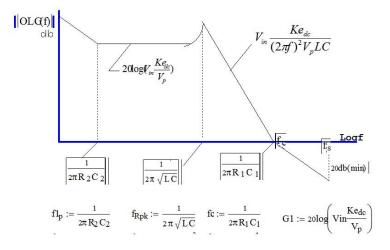

| Figure 35: Straight Line Approximations of Open Loop Gain Equations        | 51     |

| Figure 36: Feedback Elements in Schematic Form                   | 55 |

|------------------------------------------------------------------|----|

| Figure 37: Buck Converter Output LC Filter                       | 56 |

| Figure 38: The Existing Error Amplifier Design                   | 57 |

| Figure 39: Feedback Loop Flow Diagram                            | 58 |

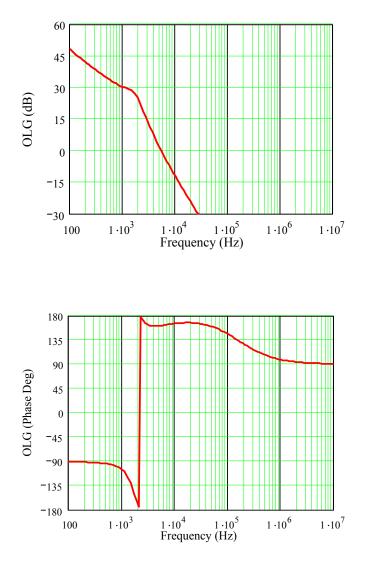

| Figure 40: Bode Plots for Existing Hardware Model                | 60 |

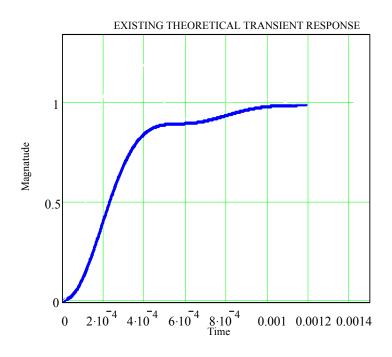

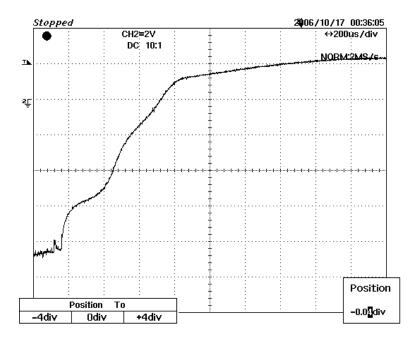

| Figure 41: Simulated Time Response of Existing Design            | 61 |

| Figure 42: Lab Results Transient Response from Existing Hardware | 62 |

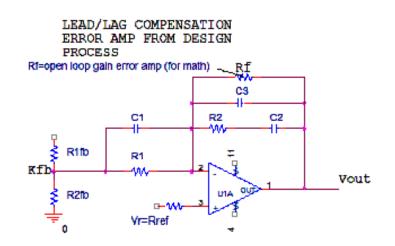

| Figure 43: Lead-lag Network Error Amp                            | 70 |

| Figure 44: Improved Feedback Configuration Schematic             |    |

| Figure 45: Improved Feedback Configuration Close-up              | 74 |

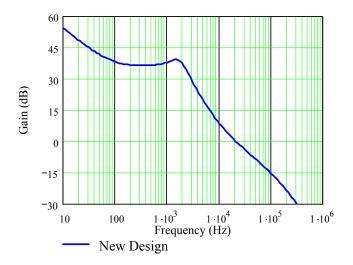

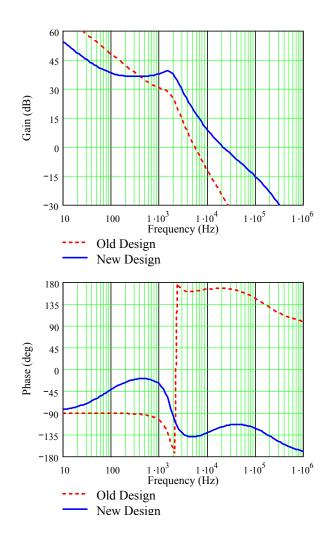

| Figure 46: Gain Plot of the Improved System                      | 75 |

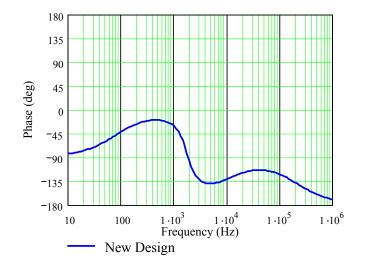

| Figure 47: Phase Plot of the Improved System                     | 75 |

| Figure 48: Comparison of Existing Versus Improved System         | 76 |

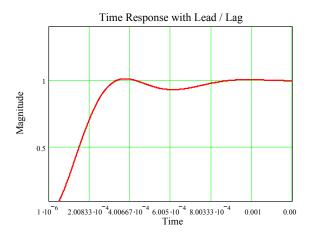

| Figure 49: Simulated Transient Response of Improved System       | 77 |

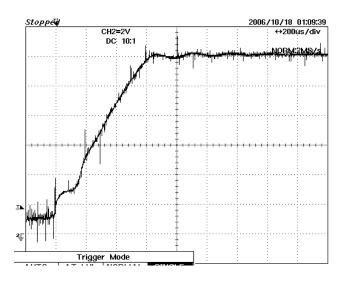

| Figure 50: Lab Transient Response of the Improved System         |    |

# NOMENCLATURE

- FET: Field Effect Transistor

- ESR: Equivalent Series Resistance

- PWM: Pulse Width Modulation

- CCM: Continuous Conduction Mode

- DCM: Discontinuous Conduction Mode

- OLG: Overall Loop Gain

- SSA: State Space Averaging

- OTC: One Time Constant

# CHAPTER I INTRODUCTION

Historically it has been difficult to determine the required feedback control loop parameters upon the initial design of a power converter. DC-DC converters have many control and power circuitry components which are misunderstood and difficult to characterize. These complex elements make the analysis of the control loop difficult. In most cases, at the start of a design, estimates of the control parameter values are determined. Many times these control parameters are based on years of experiences resulting in empirical tuning of the feedback elements. Once the hardware has been built and system dynamic testing begins, the long hours of painstaking and frustrating empirical tuning become a reality. This controller design problem may consume the majority of the effort in developing a DC-DC converter.

The goal of this research is to provide a systematic method to improve an analog controller for a DC-DC power converter. Currently, there are multiple methods used for

modeling power conversion systems such as DC-DC converters. A simulation package such as PSPICE® or SABER® can be used for this purpose. Additionally, Mathcad® can support this effort and make it easier to deal with the equations required to determine the time response of the DC-DC converter. Good models must be available in order to achieve good results. Many of the components within a DC-DC control loop system model do not exist and must be created by the user. This requires a deep understanding of the power components being evaluated. In order to obtain the results that closely match real world hardware, we must include some or all of the parasitics contained within the individual components that make up the converter. These components consist of diodes, FETS, capacitors, and inductors. Understanding the details of these components will allow us to determine what parasitics can be omitted to simplify the model without having much effect on the simulation results. By utilizing mathematical models we can develop a good understanding of each segment of the power converter as well as the effect that each segment has on the control system.

The motivation for this research comes from many years of utilizing empirical tuning methods for DC-DC converter control loops. The difficulty with this method is revealed by the painstaking non-systematic nature of the resulting lab work. This has resulted in the desire to create a systematic approach for defining and improving these control parameters. It is imperative we establish a mathematical systematic approach (a process) that can be easily utilized for developing control loops and establishing the resistive, inductive and capacitive component values for the DC-DC converter analog

controller. Having a process like this will dramatically reduce development costs as well as design time.

Improving the stability of the control loop and maximizing converter performance will be the key focus for our process. Utilizing new tools such as Mathcad® and Simulink® we can get a good look at how the system will perform in the real-world hardware. Of course our ultimate goal is to establish a means to effectively utilize these tools to accurately predict how DC-DC converter control loop will respond. We will discuss new and old methods that can be used to understand and feedback control system for DC-DC converters. We will also review some of the newer tools created that make it easier to work through some of the difficulties of the mathematical equations. This will be followed by reviewing some of the more traditional mathematical tools used to quantify the feedback loop stability and system transient response.

In order to fully understand the methods described in our process, we will first discuss the operating principles of DC-DC converters. We will review the DC-DC converter power topology first, then move on to the power flow, timing, small-signal analysis and finally the DC-DC output filter characteristics. Following this we then will describe our systematic approach for a voltage mode control loop design used to control a DC-DC buck converter.

After describing the difficulty with empirical tuning of control loops in the introduction of chapter I, the rest of this thesis is organized as follows. In Chapter II, we review the basic DC-DC converter operation as well as frequency domain and time domain characteristics of the DC-DC converters. We also review basic concepts and

tools such as Bode diagrams and the Laplace transform. In Chapter III we go on to develop the improvement process and describe the DC-DC converter hardware system containing the control loop. We then establish how to treat the non-linear dynamics of the converter so traditional mathematical tools for frequency domain analysis can be applied. We further discuss how to compensate the DC-DC converter error amplifier in order to ensure good stability and time response. These chapters will serve as the basis for our process of determining feedback component values that will ensure good DC-DC converter control loop performance. Finally we verify our mathematical approximation by comparing it to the lab data (scope plots) of the existing converter in order to ensure our approach and the mathematical model represent and produce results closely matching the real world hardware.

Finally, in Chapter IV, the proposed design process as applied to the existing DC-DC converter is evaluated by utilizing both the time domain and frequency domain analysis. This proposed process will be implemented utilizing both the mathematical model and the real hardware. The experimental data is used to compare the old design to the new one.

# CHAPTER II DC-DC CONVERSION

### 2.1 DC-DC Conversion Background

DC-DC converters are used to convert voltage up or down. A buck converter the a higher voltage on the input to a lower voltage on the output. A boost converter the voltage is shifted upward from the input. A buck-boost will regulate the output voltage even if the input voltage is below or above the output voltage set point. DC-DC converters are used in a variety of applications, however, systems such as battery systems or systems that contain a constant DC bus will utilize DC-DC converters to interface to downstream components that require a different voltage level.

In 1976, Fred C. Lee of Virginia Polytechnic Institute established a method for obtaining a small signal model for buck, boost and buck-boost converters.<sup>[6]</sup> By taking the transform of the loop components we can establish an independent transfer function of the individual blocks within the system. Combining these transfer functions we can

obtain the gain and phase plots <sup>[2], [3], [4]</sup> in the frequency domain. Also, if we apply the step function and take the inverse Laplace transform <sup>[2]</sup> and plot the resulting time domain function we can obtain the transient response of the system.

In the past, taking the inverse Laplace transform in this way was very difficult due to the complexity of each equation. With the use of Mathcad® taking the Laplace transform becomes a very simple task.

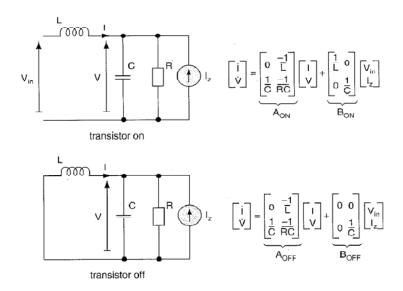

State space averaging, <sup>[1],[3],[13],[14]</sup> shown in Figure 1, is a technique proposed by Slobodan Cuk and R. D. Middlebrook<sup>[15]</sup> in 1976, and used very effectively in deriving models for power converters. This technique allows ideal components (FET switches) to be evaluated and weighted with a duty cycle value. This average is established over a single power cycle or a single period. The state space average equations are the equations of valid small signals around a nominal operating point. A key point in state space averaging is that we ignore terms with products of any two small signal perturbations and this makes the dynamic model linear.<sup>[10]</sup> Once again, time domain expressions can be obtained by taking the inverse Laplace transform of the transfer function equations. State space averaging is a great technique for developing mathematical models. Again, with new software programs such equations can be easily manipulated. For our purposes, we will simply create transfer function equations directly from the components within the system. These transfer function equation can be directly graphed in the frequency domain and the inverse Laplace transforms will be graphed in order to obtain the time response.

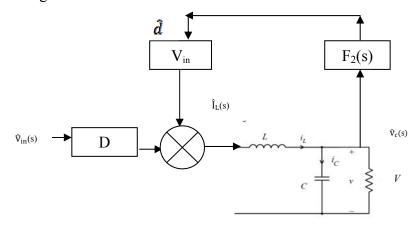

Figure 1: State Space Averaging Model for a DC-DC Converter

### 2. 2 Concepts and Criterion for Loop Stability

The concepts for defining the stability of a system used in this research are not necessarily novel; however, establishing a concise process by which all of these concepts can be utilized to improve a control loop for DC-DC converters is extremely valuable. We will attempt to create this approach to organize these concepts in a way that will be effective in DC-DC converter design. In addition, we will also develop an understanding of instability caused by certain elements within system control loop.

In the following paragraphs we discuss several key concepts relating to control loop system stability that are very important. It is imperative that we understand how the concepts apply to switched mode power conversion technology. This will help support our efforts in determining the best approach to identify a systematic approach to improving DC-DC converter control loop performance.

With voltage mode control the output LC filter shown in Figure 1 adds up to 180° phase lag to the feedback loop. The error amplifier has negative feedback therefore it adds 180° phase lag to the loop as well. The system must be compensated otherwise the feedback loop could be inherently unstable. Also, as the input voltage increases so will the loop gain of the system. This makes it harder to stabilize. Another difficult problem when implementing empirical tuning methods is obtaining lab measurements of the phase and gain margin. It is virtually impossible because the optimal point for AC signal injection is embedded inside the control chip and is not accessible. AC signal injection is a technique used to measure the system phase and gain by implementing a frequency sweep and observing the reduction in amplitude and phase shift at certain points within the system.

Finally, establishing the gain and phase <sup>[2], [3], [11]</sup> characteristics of each element within the control loop is difficult because the modulator, opto-isolator, and Field Effect Transistors in the power train are nonlinear elements and have bandwidth limiting characteristics.

The design process being developed is based on the concepts of the Nyquist stability criterion <sup>[2], [3], [6]</sup>. The following are well known Nyquist criterion concepts that apply to our voltage mode control system.

A simplified version of the Nyquist stability criterion can be used because the unity gain crossover occurs only once in the gain versus frequency plot. When evaluating the open loop gain we need to realize that if the open loop gain crosses the 0 dB (or unity) point only once, the system is stable if the crossover frequency point (unity or zero dB point) is less than the corresponding point where the phase plot crosses the -180° line. If the phase lag at the crossover frequency exceeds 180° phase shift, then the loop will oscillate at the crossover frequency. The phase margin <sup>[2], [3], [11]</sup> is commonly known as the amount by which the phase lag is less than the critical value of -180° at the crossover frequency  $f_c$  on the gain versus frequency plot. In addition, the gain margin <sup>[2], [3], [11]</sup> is the factor by which the gain is less than unity (0 dB) at the point when the phase plot reaches -180°. If the phase lag at  $f_c$  is only a few degrees less than 180° (small phase margin) the system will be stable but will have considerable overshoot and ringing at the crossover frequency  $f_c$ . If the phase margin of the system is at least 45°, the system will yield good response with little overshoot and no ringing. Finally, we should have at least 20 dB of gain margin when phase approaches -180°. In addition, at frequencies less than  $f_c$  the phase lag may be permitted to exceed 180° even though the open loop gain is greater than one. Understanding these items will support our efforts in identifying the best possible process for improving DC-DC converter control loop performance.

#### 2.3 Phase and Gain Plots

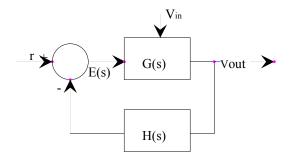

A generic feedback control loop used in DC-DC converters is shown in Figure 2.

Figure 2: DC-DC Converter Closed Loop Configuration

Let G(s)H(s) be the loop gain transfer function. A random particular example is

$$G(s)H(s) = \frac{1*10^{6}(s+10)}{(s^{2})(s+100)(s+1000)}$$

(2.1)

Converting this transfer function to the following form shown in Equation 2.2 and taking  $20*\log |G(s)H(s)|$  we can establish the logarithmic magnitude gain plot in dB.

$$|G(j\omega)H(j\omega)| = 20 * log | \left\{ \frac{100 * \left| 1 + \frac{j\omega}{10} \right|}{|(j\omega)^2| * \left| 1 + \frac{j\omega}{100} \right| + \left| 1 + \frac{j\omega}{1000} \right|} \right\} | dB$$

(2.2)

$$|G(j\omega)H(j\omega)| = 20 * log |(100)| + 20 * log |(1 + \frac{j\omega}{10})| - 40 *$$

$$log |(j\omega)| - 20 * |(1 + \frac{j\omega}{100})| - 20 * log |(1 + \frac{j\omega}{1000})| dB$$

(2.3)

The following form can be derived from the transfer function and used to establish the phase plot.

$$\phi_{G(j\omega)H(j\omega)} = \tan^{-1}(\frac{\omega}{10}) - \tan^{-1}(\omega^2) - \tan^{-1}(\frac{\omega}{100}) - \tan^{-1}(\frac{\omega}{1000})$$

(2.4)

We would like to use Bode plot information for ensuring a stable DC-DC feedback control system. In fact we can monitor the gain margin at the converter switching frequency to ensure that we have reduced the gain at that point to prevent instability. By providing at least 20 dB of gain margin at the converter switching frequency we can eliminate switching noise from being amplified by the control loop. As we explain later, we set the corner frequency of the output LC filter to approximately 1/10 of the converter switching frequency. This LC filter will inherently provide a negative -40 dB per decade of system gain roll-off, ensuring that the switching frequency noise will not be present in the system output.

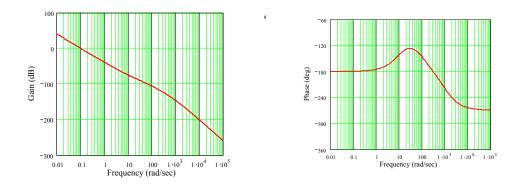

As stated previously, a phase margin of 45° yields good response with little overshoot and essentially no ringing. The Bode plots in Figure 3 illustrate a system that is nearly unstable. Later we illustrate how to compensate a system so we may improve the system stability, reduce overshoot and ringing.

Figure 3: Phase and Gain Plots

#### 2. 4 Time Domain Characteristics

For the purpose of analysis, it is important to represent the feedback loop mathematically. The following equation is called the closed loop transfer function and represents the system in Figure 2. Equation (2.5) and Figure 2 can be used to establish the frequency and time domain performance of the system. G(s) is typically considered the plant and H(s) is the compensator.

$$\frac{V_{out}}{r} = \frac{G(s)}{1 + G(s)H(s)} \tag{2.5}$$

The right side of this equation is typically a ratio of two polynomials. The roots of the numerator are called the zeros and roots of the denominator are called the poles. The denominator of the closed loop transfer function is called the characteristic function and setting the characteristic function equal to zero yields the characteristic equation. We use the characteristic equation to establish the stability of the overall system transfer function.

$$1 + G(s)H(s) = 0 (2.6)$$

The roots of the characteristic equation are used when determining the stability of the system. These roots can be real or complex. In the s-domain, if the roots are in the left-hand plane (left of the imaginary axis), then the feedback loop will be stable. If one or more of the roots lie in the right-hand plane (to the right of the imaginary axis) then the system will be unstable. If the roots lie on the imaginary axis and none in the right hand plane then the system will be marginally stable. In order to express the characteristic equation in the frequency domain the Laplace transform <sup>[2], [3]</sup> or transform tables can be used.

$$F(s) = \mathcal{L}\{f(t)\} = \int_{0^{-}}^{\infty} e^{-st} f(t) dt$$

(2.7)

To express the response of a system in the time domain, we can take the inverse Laplace transform of the following equation.<sup>[2], [3]</sup>

$$\mathcal{L}^{-1}\{F(s)\} = \frac{1}{2\pi} \int_{c-j\infty}^{c+j\infty} e^{st} F(s) ds = f(t)$$

(2.8)

By subjecting the closed loop transfer function to a step input and applying the inverse Laplace transform <sup>[3], [10]</sup> we can generate a time response of our DC-DC converter system. The following equations can be used to establish the time domain transient response of our second order system to a step response.

Consider the following transfer function

$$G(s) = \frac{(\omega_{a}^{2})}{s^{2} + 2z\omega_{a}s + (\omega_{a}^{2})} \qquad \qquad G(s) = \frac{100}{s^{2} + 2z\omega_{a}s + (\omega_{a}^{2})}$$

(2.9)

where z is the damping ratio <sup>[2], [5]</sup> and  $\omega_a$  is the natural frequency.

Applying a step input to the above system <sup>[10]</sup>, the output becomes

$$y(s) = \frac{100}{s(s^2 + 2z\omega_a s + \omega_a^2)}$$

(2.10)

its inverse Laplace transform is obtained as

$$y(t) = 1 - \frac{e^{-z(\omega_a t)}}{\sqrt{(1-z^2)}} \sin[\omega_a(\sqrt{(1-z^2)})t + \theta]$$

(2.11)

Clearly, when the damping ratio z decreases, the closed loop roots approach the imaginary axis and the response will become increasingly oscillatory.

The following quantities in Table I are used to characterize the time response plot of a second order system. It should be noted, as the damping ratio increases the system will oscillate less but may require more time to settle out. Let the following illustrate characteristics of the time response of a second order control system for a DC-DC converter.

| $OTC = 1/(z \omega_a)$                        | Time required for the output to reach 63% of the final value                                                                        | (2.12) |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------|

| $T_p = \frac{p}{\omega_a \sqrt{(1-z^2)}}$     | Peak Time                                                                                                                           | (2.13) |

| $T_s = \frac{4}{z\omega_a}$                   | Settling Time is the point after four time constants and defines the time where the response remains within 2% of the final output. | (2.14) |

| $M_{pt} = 1 + e^{-\frac{zp}{\sqrt{(1-z^2)}}}$ | Peak value of the time response overshoot                                                                                           | (2.15) |

| $PO\% = (M_{pt} - 1)100$                      | The percent overshoot is the maximum amount of overshoot of the time response.                                                      | (2.16) |

TABLE I: TIME RESPONSE EQUATIONS

The quantities in Table I will help us to evaluate and define the swiftness and other characteristics of the system time response. Another important note is that a third order system can be approximated by the dominant roots of the second order system as long as the real part of the dominant roots is less than 1/10 of the real part of the third root.

#### 2. 5 Time Response Simulation Example

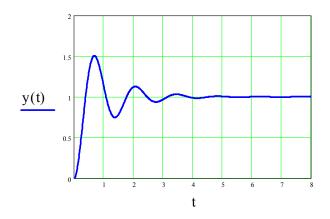

Below we plot the time response of a second-order plant to a step input. Changing the damping ratio will modify the system's response. The damping ratio <sup>[2], [5], [10]</sup> will affect the amount of overshoot and the quickness of the settling time. In this example we randomly pick the damping ratio z in order to illustrate the effect it has on the time response of the system. Let the damping ratio z = 0.215 and  $\omega_a = 4.631$ .

Figure 4: Transient Response (z = 0.215)

In Figure 4 it can be seen that the percent overshoot is PO = 50.083% and the amount of time required to get to that peak is  $T_p$ = 0.695 seconds. This plot also has a settling time of  $T_s$ =4.018 to come within +/- 2% of its final value. The damping ratio chosen can be adjusted based on the requirements of the system. In Figure 5, the damping ratio (z = 0.10) will cause more overshoot (P.O. = 72.929%) however will have a quicker peak time ( $T_p$ = 0.682 seconds) and a much longer time to settle out ( $T_s$  = 8.639) than in

the previous case. In Figure 6, with a damping ratio of (z=0.50) you can see that the overshoot is much less (P.O. = 16.309%) and requires less time to settle ( $T_s = 1.6$  seconds) however the peak time is much larger ( $T_p=0.725$ ).

Figure 5: Transient Response (z=0.10)

Figure 6: Transient Response (z = 0.5)

The most important concept to take from this is that the damping ratio and the natural resonant frequency of the system will play a key role in determining the system performance. Understanding how these items can affect the system performance will help us develop a good control loop design approach.

### **CHAPTER III**

### **IMPROVING THE CONTROL PERFORMANCE**

#### 3.1 Improving the Feedback Loop

In this chapter we will begin to develop the main portion of the design process to improve the selection of feedback control parameters for DC-DC converters. We will utilize figures, flow charts, schematics, equations and graphs to support the development of this design process.

The simulation model established will be tested by utilizing the component values from an existing Core Technology, Inc. compact DC-DC converter. Since this DC-DC converter control loop has been developed using empirical methods, it will also be used as a subject to be improved with the newly created design process. In the following chapters, we compare this empirical controller design with the new controller design based upon the proposed systematic design process. Comparisons will be made in both the time domain and the frequency domain and simulation results will be compared to lab results. To improve the empirically design controller we use the proposed design process to select feedback components then feed the values into our simulation model. Once we have improved the design using simulation, we implement the changes on the real hardware and then compare the simulations with the lab results.

### **3. 2 DC-DC Converter Technology**

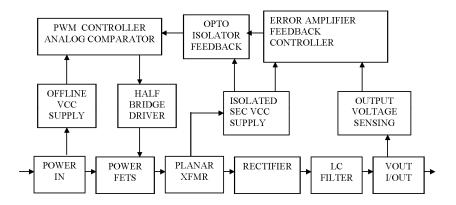

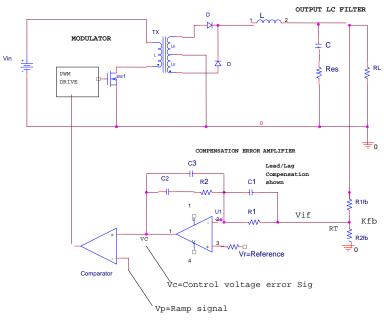

The targeted 200 watt DC-DC converter for control loop performance improvement was empirically developed and was based on previous knowledge and experience. The topology under consideration is a half bridge forward converter. See Figure 7, the DC-DC converter block diagram.

Figure 7: DC-DC Converter Block Diagram

Our task is to utilize our simulation model to compare the old and newly proposed design. We do this by inserting the component values from the empirically designed converter into our simulation tools to obtain baseline frequency and time domain responses. We can then utilize our proposed design process to obtain a new error amplifier configuration and component values. The new error amplifier configuration and component values derived from our proposed process will be inserted into the simulation tools to determine if the design will meet our performance requirements. If so, we can build new hardware. Comparing results from the new and old designs, we can quantify our improvement.

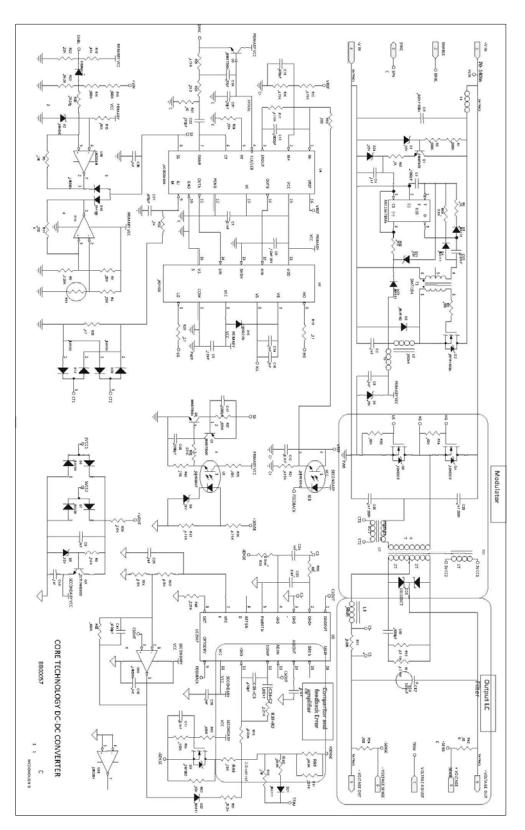

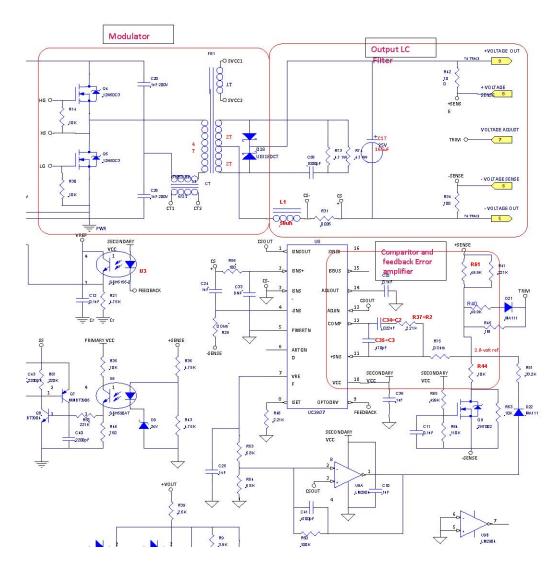

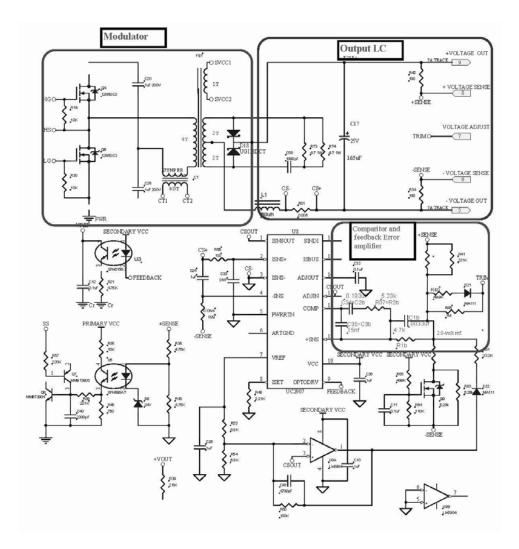

### 3.3 Converter Topology and Basic Operation

By evaluating the voltage control loop in the existing Core DC-DC converter we establish the motivation for developing the new design method. Obtaining lab results from this converter and comparing these results to our simulations will help us verify our model. The schematic diagram in Figure 8 and 9 can be used to describe basic converter operation. The primary power transfer occurs with the two active switches. These switches (FETs) transfer current back and forth through the main power transformer charging and discharging opposing capacitors C20 and C26. The control chip (U8) receives the  $V_c$  control signal via the opto-isolator (U3) from the secondary. The primary side control chip generates a ramp signal that intersects with the  $V_c$  control signal to terminate the pulse that drives the active switches. This signal that drives the active switches in an alternative fashion is called the PWM signal. This is the signal that is ultimately affected by the secondary compensation (the error amplifier) and the output voltage.

Figure 8: Core Technology, Inc. Unimproved DC-DC Converter Schematic

Figure 9: Unimproved LC Filter and Error Amplifier

On the secondary side, the power is transferred from the primary via the power transformer (T1) and down converted by a factor of 4 due to the center tapped secondary winding and a transformer turns ratio of 2/4 or 1/2. Once this square wave is generated on the secondary of the power transformer, it is rectified via the secondary ultra-fast

rectifiers (D18). This rectified square wave is then filtered and smoothed via the output LC (L1 and C17) filter. The remaining output ripple is highly dependent on the LC filter corner frequency and the equivalent series resistance (ESR) of the output capacitance (C17). The output voltage is divided down to establish a voltage equal to the reference into the compensating error amplifier. This will set the output voltage regulation point. This converter has an input voltage range of 70-Vdc to 140-Vdc and has an output regulation set point of 12 Vdc. The maximum output current is 16 amps.

### 3.4 DC-DC Converter Control System

The equations to determine gain and phase margins are intended to ensure smallsignal stability. In addition, these calculations are only intended to be applied to linear systems. In switch mode DC-DC converters, elements such as PWM circuitry and the effects from variations in output capacitor resistance (equivalent series resistance, ESR) are non-linear elements. We handle this problem by utilizing what we call small-signal analysis: the analysis of small perturbations around a large-signal operating point. The basic premise of our control system is that a bounded but uncontrolled source voltage is applied to the input of the system. Our system must accept this input voltage and then act to maintain a well controlled output voltage on the basis of a reference.

The difference between the output voltage measurement point and the reference produces an error voltage to be utilized by the controller to adjust the PWM signal in order to maintain a well-regulated output voltage. The goal of the controller design is to reduce this error voltage as close to zero as possible. In addition, it is important to reduce this error quickly. With negative feedback there is an inherent trade-off between system response time and system stability. The quicker we attempt to reduce the error voltage the greater the potential for instability. Our system feedback control can be summarized in the following flow diagram of Figure 10.

Figure 10: Basic System Feedback Control Diagram

The reference to output transfer function becomes

$$\frac{V_{out}}{r} = \frac{G(s)}{1 + G(s)H(s)} \tag{3.1}$$

In the frequency range where |G(s)H(s)| >>1, the transfer function is simplified as

$$\frac{V_{out}}{r} = \frac{1}{H(s)} \tag{3.2}$$

and is independent of G(s). This means that the closed loop gain is independent of input supply voltage, temperature effects and component variations. It is only dependent on

H(s) and the accuracy of the H(s) parameters. In general the system should be designed so that G(s) >> H(s) and G(s)H(s) >> 1 while still maintaining stability.

## 3. 5 Buck Converter Duty Cycle Versus Vout

Figure 11 is a standard switched mode DC-DC Buck converter <sup>[3]</sup>. The input voltage is switched via a FET (field effect transistor) at some fixed frequency and duty cycle. The switch will apply a square wave voltage to the output LC filter. The LC output filter then smoothes the output voltage which is a portion of the input voltage. The transfer function for this buck converter stage is

Figure 11: Buck Converter Modeling Schematic

$d = \frac{t_{on}}{T}$  is the small signal duty ratio.

The signals  $V_2$  and  $V_{out}$  are shown in Figure 12 and we assume the system is in the continuous conduction mode (CCM)<sup>[3]</sup> meaning that the current continuously flows through the inductor L, and does not drop to zero or less than zero. The current will flow through the inductor when the switch is closed and through the diode when the switch is open. Our analysis will be based on CCM operation because in CCM it is more difficult to achieve small-signal stability. Discontinuous mode <sup>[3]</sup> or DCM is another mode where the FET switch, the diode and the output power inductor all have zero current flowing. In this mode the control chips are designed to begin a power pulse at the beginning of each clock cycle even if the output filter inductor has zero current flowing. With inductor current at zero in discontinuous mode the system order is reduced to one, this makes the small-signal stability easier to obtain. Also, with the exception of hysteric controlled converters all other PWM type converters essentially have similar small-signal behavior.

Figure 12: Timing Diagram For ON/OFF Time for Power Flow

### 3. 6 Error Amplifier and PWM Signal

With voltage mode control the PWM signal is generated as shown in Figure 13 and Figure 14. It can be seen that the width of the PWM signal is generated at the point in time where the control chip generated saw-tooth (or ramp) signal crosses the output voltage from the error amplifier. In addition, it illustrates that the ramp signal starts at zero and extends linearly to a maximum voltage  $V_p$ . A minimum duty cycle will result as the error signal gets very close to zero and will approach 100% width as the error signal increases to  $V_p$ . The duty cycle of the modulator can be determined as  $\frac{V_{err}}{V_p}$ . For an isolated buck converter, we reference the duty cycle to the secondary of the power transformer. The gain of the modulator is then computed as  $K_{mod} = \frac{V_{out}}{V_{err}} = \frac{V_{in}}{V_p}$  and the duty cycle can be shown to be

$$d = t_{on} f_s = \frac{V_{err}}{V_p} \tag{3.4}$$

Ideally our system is completely linear and the output of the error amplifier  $V_{err}$  is a DC voltage and is not affected by the ESR variation in the output capacitor. In real life there is always a slightly triangular oscillation riding on *Verr*, due to the *Resr* (in the output filter capacitor) at the converter switching frequency <sup>[12], [13]</sup>. The *Resr* can cause large signal switching instability. This is what makes the phase margin at the converter switching frequency a main issue in the controller design.

Figure 13: Error Amplifier and Comparator to Generated PWM for the FET Drive

Figure 14: Ramp, Verr and Generated PWM Signals for the FET Drive

This type of oscillation caused by the output filter capacitor *Resr* is called sub-harmonic oscillations. Although the converter may regulate at the correct output voltage, these oscillations will show up riding on the output voltage. The amplitude of these oscillations will depend on the output LC filter components.

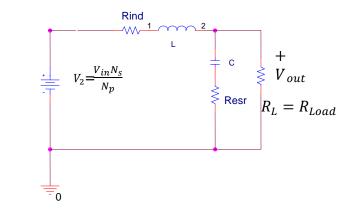

### 3.7 Output LC Filter Characteristics and Bode Plots

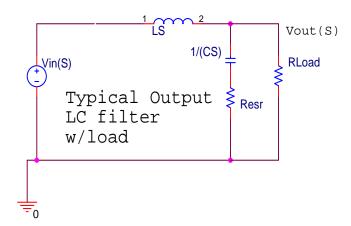

Figure 15 shows an output LC filter for a buck converter. The process of deriving the transfer function and ultimately establishing frequency and time domain characteristic plots requires the use of the Laplace transform. First, the components are converted into impedances in the frequency domain. The transfer function  $V_{\alpha t}/V_{in}$  will be used for the frequency response of the loaded LC filter.

Figure 15: Output LC Filter

The following LC filter transfer function representing the open loop characteristics of our system plant can be evaluated by our model. Next we establish phase and gain plots of this portion or our control system. This equation will be needed to define the overall system loop response.

$$\frac{V_{out}(s)}{V_{in}(s)} = \frac{1/LC}{(s^2 + \frac{s}{R_LC} + \frac{1}{LC})}$$

(3.5)

where  $R_L = R_{LOAD}$ .

The two poles of the transfer function are

$$p_1 = -\alpha + j\omega$$

, and  $p_2 = -\alpha - j\omega$  where

$\alpha = \frac{1}{2R_L C}$ ,  $j = \sqrt{-1}$

(3.6)

For these types of filters (lightly damped),  $\omega_d = \sqrt{\left(\frac{1}{LC}\right)} - \alpha^2$ . However, for the natural

resonant (peak) frequency we can use the approximation of

$$\omega_d = \sqrt{\left(\frac{1}{LC}\right)} \tag{3.7}$$

If  $s = j\omega$ , we see that the transfer function contains complex numbers and will have a real part and an imaginary part. The amplitude of the complex number is the square root of the sum of the squares of the real and imaginary parts. In addition, the phase is the inverse tangent of the ratio of the imaginary part to the real part. This transfer function can be described in terms of magnitude and phase as a function of frequency. We do this by plotting the gain in dB and the phase in degrees versus the log of frequency. These are, of course, the Bode plots and allow easy visualization of the system characteristics as they relate to system stability.

From the derived transfer function the following can be determined: the gain is equal to one and the phase is zero for  $\omega$  much less than  $\sqrt{1/(LC)}$  and the gain will be equal to  $R_L\sqrt{C/L}$  while the phase is equal to 90° for  $\omega = \sqrt{1/(LC)}$  (the resonant peak

frequency). The gain slope is equal to  $-1/(\omega^2 LC)$  and the phase is  $-180^\circ$  for  $\omega$  much greater than  $\sqrt{1/(LC)}$ .

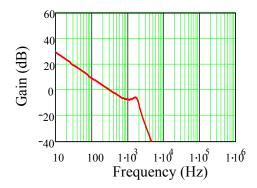

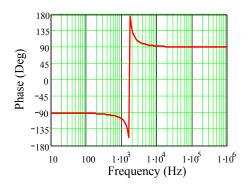

### 3.8 The Bode Plots

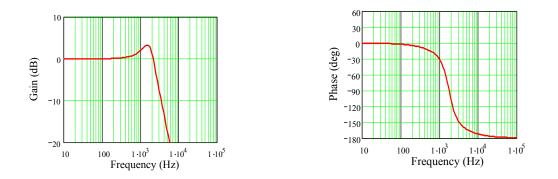

The Bode plots in Figure 16 are of the output LC shown in Figure 15 and described by Equation 3.5. They contain values  $R_L$ =0.75 ohms, C=165 µf, L=50 µh.

Figure 16: Phase and Gain Plots (Open Loop Plant)

The gain of the LC filter is unity at low frequencies and contains a resonant peak at  $f = f_{peak} = 1.75$  KHz. The slope becomes -40 dB per decade (called a -2 slope because it is proportional to  $\frac{1}{\omega^2}$ ). The phase changes from zero to -180° in two decades starting at approximately one decade prior to the resonant peak change to -180° at approximately one decade after the resonant peak.

#### 3.9 The Linear Time Invariant Representation

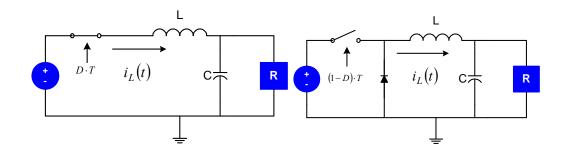

Shown in Figure 17 and 18 is the PWM (pulse width modulation) switch model similar to the model of a BJT (bipolar junction transistor). Note that the active devices (FETs) of the DC-DC converter are discontinuous in their operation. In order to use frequency domain techniques to investigate stability, transient response, settling time and external load disturbances, the averaging method is used. <sup>[3]</sup> <sup>[7],[13],[12]</sup> By analyzing the system in this way, we can evaluate DC-DC converter control loop performance based on its Bode plots. We can use the averaging technique for switching power converters because the switching rate is very fast with respect to the rate of change of other system variables. This method gives excellent accuracy providing the system bandwidth is 1/10 of the converter switching frequency and it works fairly well up to 1/3 of the switching frequency. Of course it can be used up to the 1/2 the switching frequency and this would be the theoretical limit due to the Nyquist sampling criterion. <sup>[1],[2],[6][9]</sup>

The linear time invariant PWM model allows us to ignore the nonlinear dynamics in describing the relationship between the average terminal voltage and currents. The schematic of Figure 17 shows the two modes of operation: Mode-1 when the switch (FET) is closed (for time DT) and Mode-2 when the switch is open (for time (1-D)T. Later we combine these two modes and replace the active devices with a DC-transformer containing a turns-ratio representing the duty cycle or duty ratio D. For our purposes this theoretical transformer can pass both DC and AC voltage.

Figure 17: Switched model Illustrating Mode 1 and 2

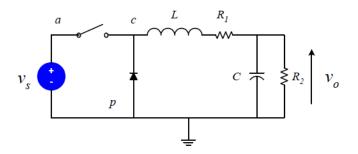

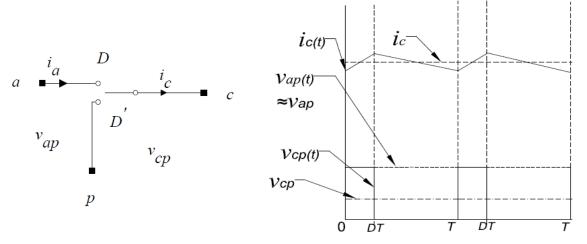

Figure 18 illustrates the buck topology under consideration and defines the terminals of the PWM switch model, a (active), p (passive) and c (common).

Figure 18: Buck Topology Illustrating PWM Switched Model for Averaging Waveforms

With a simple equivalent circuit model of the PWM switch as shown in Figure 19, we can now represent the relationship between the average terminal values (considered as DC) and the small-signal perturbations (considered ac) affecting the system. We are able to do this because in our model they are extremely small with respect to the averaged or DC values due to the system's inability to change much during one or even several duty cycles. Because the changes are so small, we can remove the non-linear small signal perturbations by ignoring the products of any two small signal variables. The PWM switch model can be used with any topology because the following terminal currents and

voltages largely remain invariant. The instantaneous currents  $i_a(t)$  and  $i_c(t)$  and the instantaneous terminal voltages  $v_{ap}(t)$  and  $v_{cp}(t)$ , are shown in Figure 19. Also, the averaged current in the active terminal  $i_a$  is related to the averaged current in the common terminal  $i_c$  by a simple relationship where  $d(t)(same \ as \ d)$  is the instantaneous change in the duty cycle represented in Equation 3.8. We can drop the time function notation for simplicity, however the time dependent nature of these expressions is understood. In addition,  $\hat{d}$  is the ac or small signal perturbation or the small change in the average duty ratio D and requires  $(\hat{d}/D) \ll 1$ . Therefore d can be used to determine the average current  $i_a$  shown in Equation 3.9 and the average terminal voltages show in Equation 3.10.

$$d(t) = D + \hat{d} \tag{3.8}$$

$$i_a = di_c \tag{3.9}$$

$$v_{cp} = dv_{ap} \tag{3.10}$$

Figure 19: PWM Switch Model and Corresponding Averaged Waveforms

In the signal diagram of Figure 19 the average current is represented by  $i_c$  while the actual instantaneous current is shown as  $i_c(t)$ . The same notation is used for  $v_{ap}$  and  $v_{cp}$ . The instantaneous terminal voltages always have the same shape.

All terminal voltages are also perturbed in this manner.

$$v_{ap} = V_{ap} + \hat{v}_{ap} \tag{3.11}$$

$$v_{cp} = V_{cp} + \hat{v}_{cp} \tag{3.12}$$

Using the perturbations representation as described above it follows that

$$(V_{ap} + \hat{v}_{ap}) = (\hat{v}_{cp} + V_{ap} D)/(D + \hat{d}) \text{ (Note:} V_{cp} = V_{ap} D)$$

$$(V_{ap} + \hat{v}_{ap})(D + \hat{d}) = V_{ap} D + \hat{v}_{cp}$$

$$\hat{v}_{ap} D + \hat{v}_{ap} \hat{d} + V_{ap} \hat{d} + V_{ap} D = V_{ap} D + \hat{v}_{cp}$$

Since  $V_{cp} = DV_{ap}$  and ignoring the product of any two small signal perturbations (or the second order effects) such as  $\hat{v}_{ap}\hat{d}$  it follows that

$$\hat{v}_{ap}D = \hat{v}_{cp} - V_{ap} \hat{d}$$

$$\hat{v}_{ap} = \hat{v}_{cp}/D - V_{ap} \hat{d}/D$$

(3.13)

By performing the same process on the current we obtain

$$\hat{\imath}_a = I_c \ \hat{d} + D \ \hat{\imath}_c \tag{3.14}$$

### **3.9.1 Averaged Model**

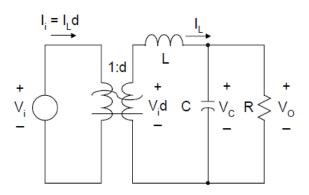

Figure 20 shows the averaged switched circuit model <sup>[7],[3]</sup> and illustrates the DCtransformer schematically after combining the two switched conditions. The duty cycle variable *d* represents the turn ratio of the hypothetical DC transformer. With this model the primary current becomes  $I_L d$  and the secondary voltage is  $V_i d$ . This DC transformer will allow us to create the averaged continuous model.

Figure 20: Resulting Averaged Model

Neglect the hat or second order terms due to their insignificance

$$\mathbf{v}_i = \mathbf{V}_i + \widehat{\mathbf{v}}_i, \quad \mathbf{i}_L = \mathbf{I}_L + \widehat{\mathbf{i}}_L, \quad \mathbf{d} = \mathbf{D} + \widehat{\mathbf{d}} \text{ then}$$

$$\mathbf{V}_{i}\mathbf{d} \approx (\mathbf{V}_{i} \cdot \hat{\mathbf{v}}_{i}) (\mathbf{D} + \hat{\mathbf{d}}) = \mathbf{V}_{i}\mathbf{D} + \mathbf{V}_{i}\hat{\mathbf{d}} + \hat{\mathbf{v}}_{i}\mathbf{D} + \hat{\mathbf{v}}_{i}\hat{\mathbf{d}} \approx \mathbf{V}_{i}\mathbf{D} + \mathbf{V}_{i}\hat{\mathbf{d}} + \hat{\mathbf{v}}_{i}\mathbf{D}$$

(3.15)

because  $\hat{v}_i \hat{d}$  is negligible. From Figure 21 and Equation 3.15, it can be shown that the product of  $v_i d$  is linearized about the operating point,  $V_i D$

#### **3.9.2 The Linear Model**

As previously described, to obtain a linear model we need to define the small signal parameters based on a large signal operating point <sup>[3], [7]</sup>. Mathematically this linearization involves separating each variable into its DC and AC components. In the linearized model of Figure 21 we can see the averaged duty cycle being used along with the addition of the primary incremental change in current in  $I_L \hat{d}$  and the incremental change in voltage on the secondary  $V_i \hat{d}$ . Because our equations will contain the product of two small signal variables, the system will still have some non-linearity. However, as previously mentioned we can ignore the products of any two small signal variables because they are extremely small with respect to our averaged operating points. In general, the linear approximations work well as long as the small signal amplitudes are small enough not to "rail" the duty cycle full-on or full-off for multiple cycles.

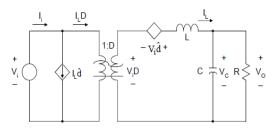

Figure 21: The Linearized Model of a Buck Converter

If we apply the generalized control law to the linearized power <sup>[3], [7], [12]</sup> circuit in Figure 22 a flow diagram can be derived. This flow diagram will help illustrate how  $\hat{d}(s)$  the transformed control variable, varies as a function of converter elements affecting the control loop.

Figure 22: Generalized System Configuration for the Time Invariant Model

From the flow diagram in Figure 22 it can be seen that the inductor current, output voltage, and the input voltage variables can each affect the system control variable  $\hat{d}(s)$ .

$$d(s) = -F_1(s) \hat{i}_L(s) - F_2(s) \hat{v}_c(s) + B(s) \hat{v}_{in}(s)$$

(3.16)

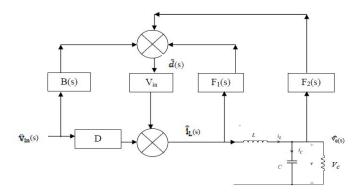

For purposes of completeness, feed forward control is also shown. However, it will not be used in our analysis of the voltage mode control. In Figure 23 we show the complete buck converter flow diagram and eliminate the items which do not contribute to the voltage mode control.

Figure 23: Voltage Mode Control Flow Diagram

For voltage mode control  $F_1(s)$   $\hat{i}_L(s) = 0$ , B(s)  $\hat{v}_{in}(s) = 0$ , and  $F_2(s) = \frac{K(s)}{V_p}$ . Therefore the system open loop transfer function can be defined as

$$\hat{\mathbf{d}}(\mathbf{s}) = -\mathbf{F}_2(\mathbf{s})\,\hat{\mathbf{v}}_c(\mathbf{s}) \tag{3.17}$$

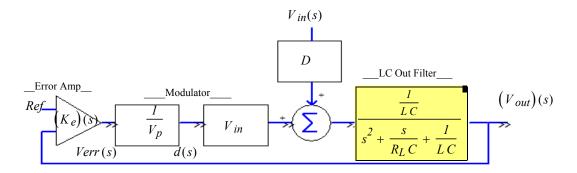

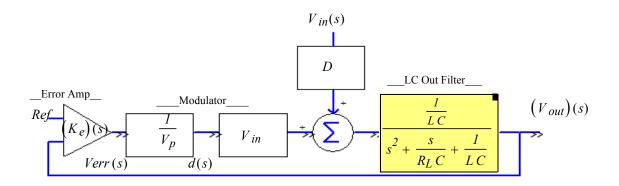

A more detailed flow diagram which can illustrate the individual components within the control loop can be seen in Figure 24. Included are the values within the functional blocks in order to help describe how each part of the system affects the control signal.

Figure 24: Generalized Control Law from Time Invariant Model

The overall open-loop gain is the product of the individual gains around the control loop of the system (the error amplifier, the modulator, etc.). That is

$$G(s)H(s) = \frac{\frac{V_{in}K(s)}{V_pLC}}{s^2 + \frac{s}{R_LC} + \frac{1}{LC}}$$

(3.18)

Equation 3.18 illustrates the basic DC-DC buck converter system's transfer function. It is important to note that this transfer function is independent of the duty cycle D and is dependent on the DC input voltage  $V_{in}$ . Thus the open loop gain function is dependent on the DC operating point. Another interesting point is that the output load resistance shows up in the second term of the denominator. It would seem that if the load resistance goes to infinity, the system would become unstable, but as previously discussed; the DC converter will go into DCM discontinuous mode. When this occurs, the system will become a first order system and becomes easier to stabilize. Additionally, the error amplifier negative feedback causes an inherent -180° phase shift and can cause our system to go unstable at 180° rather than 360°. It is for this reason that we review the gain margin at the -180° point on the Bode plots.

#### 3. 10 Open Loop Phase and Gain Margin of the Buck Converter

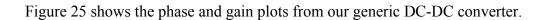

In the following example we will use real world values chosen from a generic design similar to the design under consideration. These values are shown in Table II below and we use them to obtain the gain and phase plots. We can insert them into the open loop transfer function and use this function to derive the Bode plots so we may obtain the gain and phase margin.

| Variable = Value        | Variable = Value                                                                  |

|-------------------------|-----------------------------------------------------------------------------------|

| $V_P = 2$ Volts         | $C = 540 \ uf$                                                                    |

| $R_L=0.5 Ohms$          | L = 16  uf                                                                        |

| $f_s = 100 \text{ KHz}$ | $V_{in} = 12$ Volts                                                               |

| $K_{err} = 5.6$         | $s = j2 \pi f$                                                                    |

| $K(s) = R_2/R_1$        | $G(s)H(s) = \frac{\frac{V_{in}K(s)}{V_pLC}}{s^2 + \frac{s}{R_LC} + \frac{1}{LC}}$ |

TABLE II: GENERIC DESIGN COMPONENT PARAMETERS

Figure 25: Phase and Gain Plots

Our example shown in Figure 25 is close to being unstable with at best  $5^{\circ}$  of phase margin which is not acceptable. We will use these tools (Bode plots) to define the robustness of the control loop.

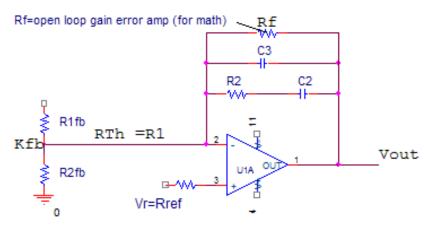

#### 3. 11 Frequency Compensation and Circuit Implementation

The system we have just analyzed in the previous plots would be viewed as nearly unstable due to the lack of phase margin at the crossover frequency. In this case, the system would experience a lot of ringing under any external disturbance.

Obviously we need to provide some frequency compensation. We will now shape the open loop transfer function to provide adequate gain and phase margins to ensure a stable system with good transient response. This is accomplished by applying a lead, a lag, or a Lead-lag network to the error amplifier. Determining the proper network and components within that network is our challenge. In the next section, we describe each compensation network in order to help us determine how to apply them.

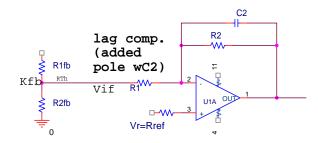

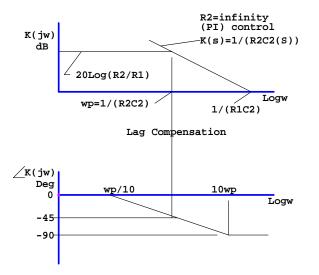

#### **3.11.1 Lag Compensation**

Based on the initial run of the phase and gain plots we need to reduce the gain at lower frequencies so when the system loop reaches the unity gain point there will be a phase margin of at least 45°. This is achieved by rolling off the gain of the error amplifier with local feedback around the error amp as shown in Figure 26. With the addition of  $C_2$ we now have the amplifier gain of

$$K(s) = \frac{-V_{out}(s)}{V_{in}(s)} = \frac{R_2}{R_1(1+R_2C_2s)}$$

(3.19)

This allows the same DC gain; however, we add a pole at frequency

$$\omega_p = 1/(R_2 C_2) \tag{3.20}$$

As previously discussed this single pole compensation method is called lag compensation <sup>[2],[3],[11],[12],[15]</sup>. This causes the phase shift to change from zero degrees at 1/10 of the corner frequency to -90° at 10 times the corner frequency. Shown in Figure 27 is the lag compensated error amplifier.

Figure 26: Lag Compensated Error Amp

Figure 27: Error Amp Lag Compensated Phase and Gain

The amplitude of the compensated error amplifier gain in dB will add to the amplitude of the control loop. The error amplifier phase adds to the overall phase lag. The phase lag compensation becomes a proportional integral control with  $R_2=\infty$ .

We now use straight line approximations <sup>[3],[12],[15]</sup> of the transfer function to gain insight and to pick the filter components. The lag compensating straight line transfer function (Equation 3.21) dictates the value of the gain below the resonant frequency and produces a negative slope of 20 dB per decade.

$$\frac{V_{in}}{\left(2\pi \cdot f \cdot V_p \cdot R_1 \cdot C_2\right)} \tag{3.21}$$

Beyond the resonant peak Equation 3.22 defines the shape of the gain plot and produces a negative slope of 40 dB per decade.

$$\frac{V_{in}}{\left(2\pi \cdot f\right)^3 \cdot V_p \cdot R_1 \cdot C_2 \cdot L \cdot C}$$

(3.22)

The resonant frequency where the gain will peak is

$$G_{fpk} = \frac{V_{in}}{2\pi f V_p R_1 C_2} R_L \sqrt{C/L}$$

(3.23)

At a particular frequency (the resonant frequency) the output filter capacitor and inductor reactances are equal in magnitude but opposite in sign and exhibit minimum impedance. This is common for series LC circuits. When this occurs we call this the resonant frequency. To achieve a 6 dB gain margin at  $f_{pk}=1.71$  KHz we can set the gain at the peak point ( $G_{fpk}$ ) equal to  $\frac{1}{2}$  yielding a  $R_1C_2$  product of (.00324). We then pick  $R_1 = 167$ K ohms and  $C_2 = 0.02 \, uf$  to make  $R_1C_2$  product close to (.00324),

$$R_1 C_2 = \frac{V_{in}}{2\pi f V_p(G_{fpk})} R_L \sqrt{C/L}$$

(3.24)

resulting in  $R_1C_2 = 3.24x10^{-3}$ .

The unity gain crossover frequency has been reduced and will now be less than 300 Hz which is about an order of magnitude below the resonant frequency. It is important to note that the gain margin of 6 dB was based on the resonant peak. The resonant peak is dependent on the output load value. So, if we were to decrease the load, this would also decrease the gain margin. We could use the smallest load before the converter would go into the discontinuous mode. While the phase margin would be -90°, the dominant pole has reduced the system bandwidth to a point where the transient response would be very poor. In addition, the low frequency gain has been reduced. The lag compensator contributed -90° phase shift. The output LC filter contributes another

-180° of phase shift. Equation 3.25 can be used to establish the phase and gain plot illustrating the characteristics of the lag network. This transfer function appears to be like the previous *OLG* transfer function. However, it contains the addition of  $C_2$  in the  $K_e(s)$  term.

$$OLG(s) = \frac{\frac{V_{in} \cdot K_e(s)}{V_p \cdot L \cdot C}}{(s)^2 + \frac{s}{R_L \cdot C} + \frac{1}{L \cdot C}}$$

(3.25)

Table III shows the values utilized for the Lag compensation error amplifier. Figure 28 and Figure 29 illustrate the resulting phase and gain margin. For a 6 dB gain in margin at the resonant peak we can set the  $G_{fpk}$ =0.5. As mentioned before we do this to obtain an  $R_1C_2$  product.

| TABLE III. LAG DESIGN COMPONENT PARAMETERS                                         |                                                                                                                        |  |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|

| Variable = Value                                                                   | Variable = Value                                                                                                       |  |

| $V_P = 2$ Volts                                                                    | $C = 540 \ uf$                                                                                                         |  |

| $R_L=0.5 Ohms$                                                                     | L = 16  uf                                                                                                             |  |

| $f_s = 100 \text{ KHz}$                                                            | $V_{in} = 12$ Volts                                                                                                    |  |

| $K_{err} = 5.6$                                                                    | $C_2 = 0.021 \ uf$                                                                                                     |  |

| G <sub>Rpeak</sub> =1.713 KHz                                                      |                                                                                                                        |  |

| $R_{ampOL} = 1E9 Ohms$                                                             | $R_1 = 167K Ohms$                                                                                                      |  |

| $s = j2 \pi f$                                                                     | $V_{out} = 5 Volts$                                                                                                    |  |

| $K(s) = \frac{R_2}{\left[R_1 \cdot \left(1 + R_2 \cdot C_2 \cdot s\right)\right]}$ | $OLG(s) = \frac{\frac{V_{in} \cdot K_e(s)}{V_p \cdot L \cdot C}}{(s)^2 + \frac{s}{R_L \cdot C} + \frac{1}{L \cdot C}}$ |  |

TABLE III: LAG DESIGN COMPONENT PARAMETERS

Figure 28: Lag Compensated Gain Plot

Figure 29: Lag Compensated Phase Plot

In Figures 28 and 29 it can be seen that the lag compensation has moved the unity gain point to a lower frequency allowing a phase margin of approximately 90°. However, the DC gain could be higher as well as the gain margin (approximately 5 dB) where the phase approaches 180° is not acceptable based on our criteria for our stable system. We can now explore the lead compensation network.

#### 3.11.2 Lead Compensation

Using a lead network <sup>[2],[3],[11],[12],[15]</sup> is another method of compensation. We can increase the phase by adding a lead capacitor  $C_I$  in parallel with the input resistor (on the negative terminal) of the error amp (see Figure 30). This will introduce a zero into the system transfer function. The addition of the lead capacitor will increase the gain; however, if we set the break frequency  $f_{brk}=1/(R_IC_I)$  of the zero to be the same as the crossover frequency, we can increase the phase margin by 45°. It is important to note that pure lead compensation is physically unrealizable since the gain cannot continue to rise indefinitely due to the limitations in the open loop amplifier gain bandwidth. Obviously the gain-bandwidth of the operational amplifier used with lead compensation must be much higher than that required for lag compensation. The following is the transfer function for the lead compensated error amplifier.

$$K_{e}(s) = \frac{R_{2} \cdot (1 + R_{1} \cdot C_{1} \cdot s)}{R_{1}}$$

(3.26)

$C_1$  is determined from  $C_1 = \frac{1}{(\omega_z \cdot R_1)}$  where  $\omega_z$  is the break frequency.

Figure 30 and 31 illustrate how the addition of  $C_1$  increases the system gain at higher frequencies.

Figure 30: Lead Compensated Error Amp with Phase and Gain Diagram

Table IV shows the values derived in the lead compensator and the corresponding effects on the Bode plots.

| Component                                                    | Value                                                                                                                  |  |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|

| $V_P = 2$ Volts                                              | $C = 540 \ uf$                                                                                                         |  |

| $R_L=0.5 Ohms$                                               | L = 16 uf                                                                                                              |  |

| $f_s = 100 \text{ KHz}$                                      | $V_{in} = 12$ Volts                                                                                                    |  |

| $K_{err} = 5.6$                                              | $C_2 = 0.021 \ uf$                                                                                                     |  |

| $G_{Rpeak} = 1.713 \ KHz$                                    | $C_1 = 58.8 \ nf$                                                                                                      |  |

| $R_{ampOL} = 1E9 Ohms$                                       | $R_1 = 167 \text{ KOhms}$                                                                                              |  |

| $s = j2 \pi f$                                               | $V_{out} = 5$ Volts                                                                                                    |  |

| $K_e(s) = \frac{R_2 \cdot (1 + R_1 \cdot C_1 \cdot s)}{R_1}$ | $OLG(s) = \frac{\frac{V_{in} \cdot K_e(s)}{V_p \cdot L \cdot C}}{(s)^2 + \frac{s}{R_L \cdot C} + \frac{1}{L \cdot C}}$ |  |

TABLE IV: LEAD DESIGN COMPONENT PARAMETERS

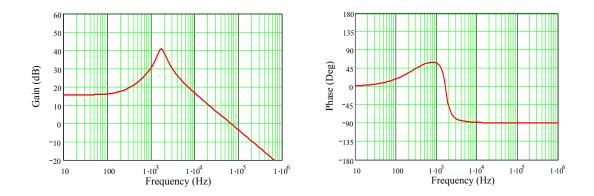

Figure 31: Lead Compensated Gain

Figure 32: Lead Compensated Phase

It can be seen from Figure 31 that the lead compensation has increased the gain at the higher frequencies. However, the problem here is that the DC gain dropped dramatically. We get the benefit of higher gain at the higher frequency but there is a consequence of low DC gain, which can cause DC error. Combining the lead and the lag compensation, we can obtain the benefits of both as shown in the following section.

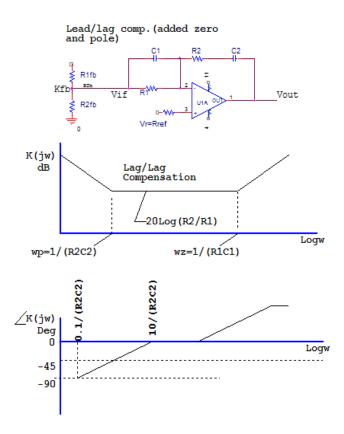

### 3.11.3 Lead-lag Compensation

It is possible to combine both lead and lag networks to achieve better performance. The goal with the this type of compensation <sup>[2],[3],[11],[12],[15]</sup> is to achieve low DC error and high bandwidth for a quick responding system. The new error amplifier configuration is shown in Figure 33. This configuration shows the insertion of one capacitor  $C_1$  in parallel with the input resistor while inserting another capacitor  $C_2$  in series with the feedback resistor  $R_2$ . By shaping the frequency characteristics of the error amplifier in this manner we can achieve high gain at low frequencies and provide acceptable phase margin at the crossover point.

Figure 33: Lead-lag Compensated Error Amp with Phase and Gain Diagram The Lead-lag error amplifier gain is:

$$K_{e}(s) = \frac{\left(\frac{1}{C_{2} \cdot s} + R_{2}\right)}{\left(\frac{1}{C_{1} \cdot s} + R_{1}\right)}$$

(3.27)

Table V shows the values used in order to derive the Bode plots.

| Component                                                                                            | Value                                                                                                                  |  |

|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|

| $V_P = 2$ Volts                                                                                      | $C = 540 \ uf$                                                                                                         |  |

| $R_L=0.5 Ohms$                                                                                       | L = 16  uf                                                                                                             |  |

| $f_s = 100 \text{ KHz}$                                                                              | $V_{in} = 12$ Volts                                                                                                    |  |

| $K_{err} = 5.6$                                                                                      | $C_2 = 0.021 \ uf$                                                                                                     |  |

| $G_{Rpeak} = 1.713 \ KHz$                                                                            | $C_1 = 15  pf$                                                                                                         |  |

| $R_{ampOL} = 1E9 Ohms$                                                                               | $R_1 = 10.5K Ohms$                                                                                                     |  |

| $s = j2 \pi f$                                                                                       | $R_2 = 59K Ohms$                                                                                                       |  |

| $K_e(s) = \frac{\left(\frac{1}{C_2 \cdot s} + R_2\right)}{\left(\frac{1}{C_1 \cdot s} + R_1\right)}$ | $OLG(s) = \frac{\frac{V_{in} \cdot K_e(s)}{V_p \cdot L \cdot C}}{(s)^2 + \frac{s}{R_L \cdot C} + \frac{1}{L \cdot C}}$ |  |

TABLE V:LEAD-LAG DESIGN COMPONENT PARAMETERS

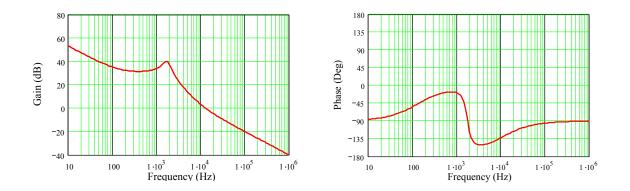

Figure 34: Error Amp Lead-lag Compensated Phase and Gain Plots

It is shown in Figure 34 that we can obtain a substantial improvement with this type of Lead-lag compensation network. As shown, at the crossover frequency we have obtained 45° of phase margin. This meets our criteria for a very stable control loop. In

addition we have obtained excellent gain (approximately 55 dB) at low frequency reducing the possibility of DC error that may have occurred with a non-compensated (approximately 30 dB gain at DC) or a lead only compensated (approximately 20 dB gain at DC) system. This is extremely important because this analysis has shown that by combining the networks we can improve system performance with the addition of only two capacitors to the error amplifier.

#### 3. 12 Straight Line Approximation with Lead-lag Compensation

Figure 35 shows a straight-line approximation of the open loop gain plot illustrating a few critical points of the DC-DC converter. The Lead-lag components contained within the system feedback loop are included in the plot.

Figure 35: Straight Line Approximations of Open Loop Gain Equations

It can be seen from the above diagram at the lower frequency that  $V_{in}(K_e/V_p)$  dictates the shape of the gain plot. At the higher frequencies  $V_{in}/((2\pi f)^2 V_p LC)$  dictates the shape of the gain plot by producing a negative slope of -40 dB/decade. At the resonant frequency the gain will peak and is defined by

$$G_{fpk} = V_{in} \frac{K_{err}}{V_{in}} \left( R_L \sqrt{C/L} \right)$$

(3.28)

A commonly used rule of thumb is, the slope of the gain response as it crosses the unity-gain (0 dB) axis is not more the 20 dB per decade (-6 dB per octave), and the phase margin should be greater than or equal to 45°. Also, the recommended gain margin should be (-6 dB to 12 dB) as the phase reaches 180°. Finally a recommended phase margin of 45 to 60° will ensure good stability properties and transient response. We should also be aware that phase shift causing instability can be attributed to other system details such as time delays in the FET drive system, or hold time in a sampling system. There is also a potential for op-amp and other component parasitics that can cause phase lags. All of these factors indicate the importance of having a generous phase margin.

### 3. 13 From Transfer Function Verification to Hardware Test

In this section we derive the transfer function for the existing DC-DC converter and the error amplifier employing a Lead-lag compensator. This transfer function is then used to simulate our new design. After successful testing with our simulation method, we can test the actual hardware and compare the simulation results to the actual lab results. This will provide verification for our simulation model as well as our design method.

Our existing DC-DC converter topology is a half bridge forward converter with an input voltage ranging from 70 Vdc to 140 Vdc. The output is 12 Vdc and there is a transformer isolating the primary from the secondary. The feedback loop contains an analog opto-isolator and is used to provide the analog feedback signal from the secondary across the isolation barrier back to the primary. This signal that is produced on the primary side (input side of the converter transformer) is the signal that is used as the control signal to intersect the ramp for termination of the PWM pulse that drives the primary side switches. For simplicity, the opto-isolator is not shown in our control loop and is assumed not to cause any non-linearity or bandwidth limitations. Our goal is to proceed and use a systematic method to determine if it is possible to improve the existing control loop bandwidth transient response and stability. This will be accomplished in the following manner:

a) Derive the existing phase, gain and transient response plots from the schematic of our existing converter.

b) Obtain frequency and transient plots of the actual hardware and compare the theoretical results to the real hardware results.

c) Derive the transfer functions of the improved design; determine the corresponding error amp components; obtain the gain, phase and transient plots of the new transfer function and compare this to the previous design.

d) Insert the newly obtained components into the existing converter and obtain the real hardware results. Compare these to the result from the original design.