## University of New Orleans ScholarWorks@UNO

University of New Orleans Theses and Dissertations

**Dissertations and Theses**

5-20-2005

# Design and Implementation of an Universal Lattice Decoder on FPGA

Swapna Kura University of New Orleans

Follow this and additional works at: https://scholarworks.uno.edu/td

#### **Recommended Citation**

Kura, Swapna, "Design and Implementation of an Universal Lattice Decoder on FPGA" (2005). *University of New Orleans Theses and Dissertations*. 236. https://scholarworks.uno.edu/td/236

This Thesis is protected by copyright and/or related rights. It has been brought to you by ScholarWorks@UNO with permission from the rights-holder(s). You are free to use this Thesis in any way that is permitted by the copyright and related rights legislation that applies to your use. For other uses you need to obtain permission from the rights-holder(s) directly, unless additional rights are indicated by a Creative Commons license in the record and/or on the work itself.

This Thesis has been accepted for inclusion in University of New Orleans Theses and Dissertations by an authorized administrator of ScholarWorks@UNO. For more information, please contact scholarworks@uno.edu.

### DESIGN AND IMPLEMENTATION OF AN UNIVERSAL LATTICE DECODER ON FPGA

A Thesis

Submitted to the Graduate Faculty of the University of New Orleans in partial fulfillment of the requirements for the degree of

Master of Science in The Department of Electrical Engineering

by

Swapna Kura

B.Tech J.N.T.U, 2001

May 2005

## ACKNOWLEDGEMENTS

I would like to express my special thanks to Dr. Jing Ma for being my advisor throughout my thesis research. I appreciate her patience, guidance and supervision of my work which helped me in progressing in right path.

I acknowledge Dr. Bhaskar Kura for his support throughout my graduate program without which it would have been impossible for me to get thru my master's degree. His patience, guidance and insight served as invaluable assets in both my personal and academic lives.

I would also express my sincere thanks to Dr. Xinming Huang and Dr. Edit Bourgeois for their willingness to serve as members in my thesis committee.

I would express my heartfelt thanks to my parents and all family members. Their blessings and love were always with me and encouraged me in stepping forward in life.

I would thank my colleagues for being eager and prompt enough to help me when I needed them. Finally, I would like to thank all my friends and cousins for their encouragement and motivation.

# **GLOSSARY OF ABBREVIATIONS**

- MIMO Multiple Input Multiple Output

- FPGA Field Programmable Gate Arrays

- PLD Programmable Logic Device

- ASIC Application Specific Integrated Circuit

- IC Integrated Chip

- SOC System-On-Chip

- FSM Finite State Machine

- AWGN Additive White Gaussian Noise

- PAM Pulse Amplitude Modulation

- BER Bit Error Rate

- ML Maximum Likelihood

- DSP Digital Signal Processor

- VHDL Very High speed integrated Description Language

- RTL Register Transfer Level

- ISE Integrated Software Environment

# TABLE OF CONTENTS

| 1 INTRODUCTION             |                                     |   |

|----------------------------|-------------------------------------|---|

| 1.1 Motivations and Bac    | kground                             | 1 |

| 1.2 Research Objective     |                                     |   |

| 1.3 Contribution of Thes   | is                                  |   |

| 1.4 Organization of Thes   |                                     |   |

| 2 FPGAs and MIMO Chan      | nels                                | 6 |

| 2.1 MIMO Channels          |                                     | 6 |

| 2.2 Field Programmable     | Gate Array (FPGA)                   |   |

| 3 Sphere Decoding Algorit  | hm                                  |   |

| 3.1 The Sphere Decoder     |                                     |   |

|                            | ihood Criterion                     |   |

| _                          | Sphere Decoder                      |   |

|                            |                                     |   |

| C C                        |                                     |   |

| 3.3 Decoding Procedure     |                                     |   |

| 3.4 High Level Simulation  | on of the Sphere Decoding Algorithm |   |

| 3.5 Decoder Architecture   | e Scheduling                        |   |

|                            | Algorithm                           |   |

|                            |                                     |   |

|                            | quare Root Algorithm                |   |

|                            | ng Algorithm                        |   |

|                            |                                     |   |

|                            | coding Algorithm<br>odifications    |   |

|                            |                                     |   |

| 4.2 Decoding Procedure     |                                     |   |

| 4.3 High Level Description | ion of the improved Sphere decoder  |   |

| 4.4 Decode Architecture    | Scheduling                          |   |

| 4.5 Hardware-Software      | Scenario                            |   |

| 4.6                                    | Simulation Results                       | 42                   |

|----------------------------------------|------------------------------------------|----------------------|

| 4.7                                    | Data Dependency                          | 43                   |

| 5 FP                                   | GA Based Architecture Design             | 46                   |

| 5.1                                    | Lattice Decoder Architecture             | 46                   |

| 5.2                                    | Parallel Structure                       | 47                   |

| 5.3                                    | VLSI Design Flow                         | 52                   |

| 5.4                                    | Design Optimization                      | 54                   |

| 6 RE                                   | ESULTS                                   | 57                   |

| 6.1                                    | Experimental Setup                       | 57                   |

| 6.2                                    | Pre-Processing Results                   | 57                   |

| 6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3 | <ul> <li>3.2 Synthesis Results</li></ul> | 58<br>60<br>62<br>67 |

| 6.4                                    | Conclusions                              | 70                   |

|                                        | RENCES                                   |                      |

# LIST OF FIGURES

| Figure 2.2: Virtex-II FPGA architecture [Chris]       10         Figure 3.1: Flowchart of a Sphere decoding algorithm [Viterbo 1999]       14         Figure 3.2: Flowchart of a Sphere decoding algorithm showing states       22         Figure 3.3: Input and Output pins for original sphere decoder       24         Figure 3.4: The FSM diagram of Sphere decoding algorithm       26         Figure 4.1: Flow chart of improved algorithm showing states       39         Figure 4.2: Flow chart of an improved algorithm showing states       39         Figure 4.3: Input and Output pins for improved sphere decoder       40         Figure 5.1: Dependency graph of the Sphere decoding algorithm       43         Figure 5.2: The hardware architecture of improved sphere decoding algorithm       46         Figure 5.3: An example of improved sphere decoding algorithm (a) Sequential implementation       6         (b) Parallel-Pipeline implementation       49         Figure 5.4: Design flow for an FPGA.       52         Figure 5.5: Workspace of Project Navigator       53         Figure 5.6: RTL schematic of parallel-pipeline implemented sphere decoder generated by Xilinx       56         Figure 6.1: Bar chart showing the simulations times of each states in both algorithms       59         Figure 6.2: Xilinx Virtex-II 1000 FPGA Device Description       61         Figure 6.3: BER vs. Eb/No (dB) for an uncoded system using o | Figure 2.1: A MIMO system. (a) MIMO Transmitter. (b) MIMO receiver                         | 7      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------|

| Figure 3.1: Flowchart of a Sphere decoding algorithm [Viterbo 1999]       14         Figure 3.2: Flowchart of a Sphere decoding algorithm showing states       22         Figure 3.3: Input and Output pins for original sphere decoder       24         Figure 3.4: The FSM diagram of Sphere decoding algorithm       26         Figure 4.1: Flow chart of improved algorithm showing states       39         Figure 4.2: Flow chart of an improved algorithm showing states       39         Figure 4.3: Input and Output pins for improved sphere decoder       40         Figure 5.1: Dependency graph of the Sphere decoding algorithm       43         Figure 5.2: The hardware architecture of improved sphere decoding algorithm       46         Figure 5.3: An example of improved sphere decoding algorithm (a) Sequential implementation       49         Figure 5.4: Design flow for an FPGA       52         Figure 5.5: Workspace of Project Navigator       53         Figure 5.6: RTL schematic of parallel-pipeline implemented sphere decoder generated by Xilinx       56         Figure 6.1: Bar chart showing the simulations times of each states in both algorithms       59         Figure 6.2: Xilinx Virtex-II 1000 FPGA Device Description       61         Figure 6.3: BER vs. Eb/No (dB) for an uncoded system using original and improved algorithms       59                                                                                | Figure 2.2: Virtex-II FPGA architecture [Chris]                                            | 10     |

| Figure 3.2: Flowchart of a Sphere decoding algorithm showing states       22         Figure 3.3: Input and Output pins for original sphere decoder       24         Figure 3.4: The FSM diagram of Sphere decoding algorithm       26         Figure 4.1: Flow chart of improved algorithm showing states       39         Figure 4.2: Flow chart of an improved algorithm showing states       39         Figure 4.3: Input and Output pins for improved sphere decoder       40         Figure 4.4: Overview of the complete system       42         Figure 5.1: The hardware architecture of improved sphere decoding algorithm       43         Figure 5.2: The hardware architecture of parallel-pipeline improved sphere decoding algorithm       46         Figure 5.3: An example of improved sphere decoding algorithm (a) Sequential implementation       (b) Parallel-Pipeline implementation         (b) Parallel-Pipeline implementation       49         Figure 5.4: Design flow for an FPGA       52         Figure 5.5: Workspace of Project Navigator       53         Figure 5.6: RTL schematic of parallel-pipeline implemented sphere decoder generated by Xilinx ISE 6.2i       56         Figure 6.1: Bar chart showing the simulations times of each states in both algorithms       59         Figure 6.3: BER vs. Eb/No (dB) for an uncoded system using original and improved algorithms       59                                                  | Figure 3.1: Flowchart of a Sphere decoding algorithm [Viterbo 1999]                        | 14     |

| Figure 3.3: Input and Output pins for original sphere decoder       24         Figure 3.4: The FSM diagram of Sphere decoding algorithm       26         Figure 4.1: Flow chart of improved algorithm showing states       39         Figure 4.2: Flow chart of an improved algorithm showing states       39         Figure 4.3: Input and Output pins for improved sphere decoder       40         Figure 4.4: Overview of the complete system       42         Figure 5.1: The hardware architecture of improved sphere decoding algorithm       43         Figure 5.2: The hardware architecture of parallel-pipeline improved sphere decoding algorithm       46         Figure 5.3: An example of improved sphere decoding algorithm (a) Sequential implementation       49         Figure 5.4: Design flow for an FPGA       52         Figure 5.6: RTL schematic of parallel-pipeline implemented sphere decoder generated by Xilinx       53         Figure 6.1: Bar chart showing the simulations times of each states in both algorithms       59         Figure 6.2: Xilinx Virtex-II 1000 FPGA Device Description       61         Figure 6.3: BER vs. Eb/No (dB) for an uncoded system using original and improved algorithms       59                                                                                                                                                                                                                         |                                                                                            |        |

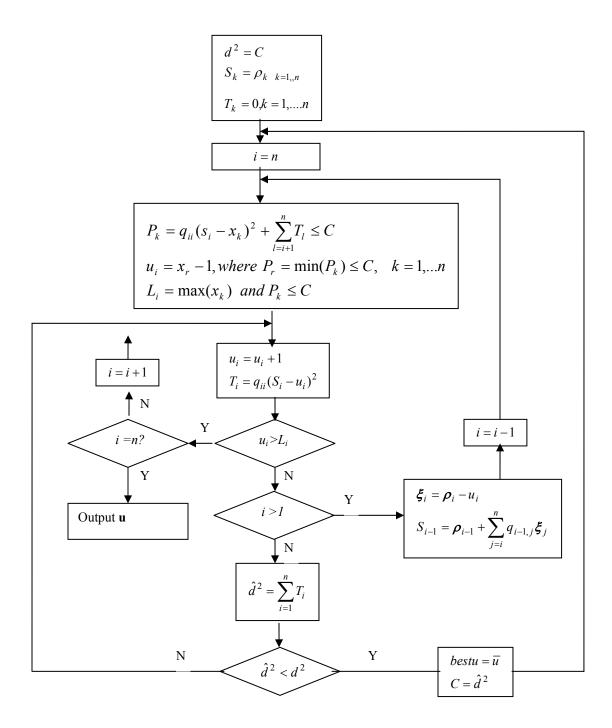

| Figure 4.1: Flow chart of improved algorithm       35         Figure 4.2: Flow chart of an improved algorithm showing states       39         Figure 4.3: Input and Output pins for improved sphere decoder       40         Figure 4.4: Overview of the complete system       42         Figure 5.1: The hardware architecture of improved sphere decoding algorithm       43         Figure 5.2: The hardware architecture of parallel-pipeline improved sphere decoding algorithm       46         Figure 5.3: An example of improved sphere decoding algorithm (a) Sequential implementation       49         Figure 5.4: Design flow for an FPGA.       52         Figure 5.5: Workspace of Project Navigator       53         Figure 5.6: RTL schematic of parallel-pipeline implemented sphere decoder generated by Xilinx       1SE 6.2i         56       Figure 6.1: Bar chart showing the simulations times of each states in both algorithms.       59         Figure 6.3: BER vs. Eb/No (dB) for an uncoded system using original and improved algorithms       50                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                            |        |

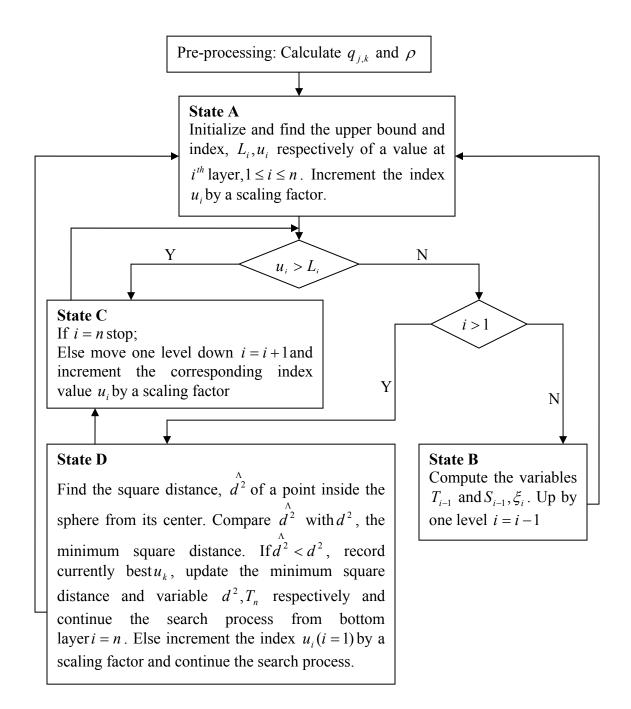

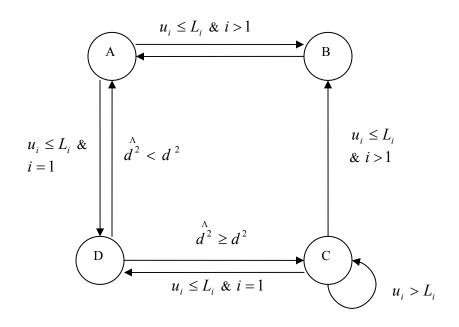

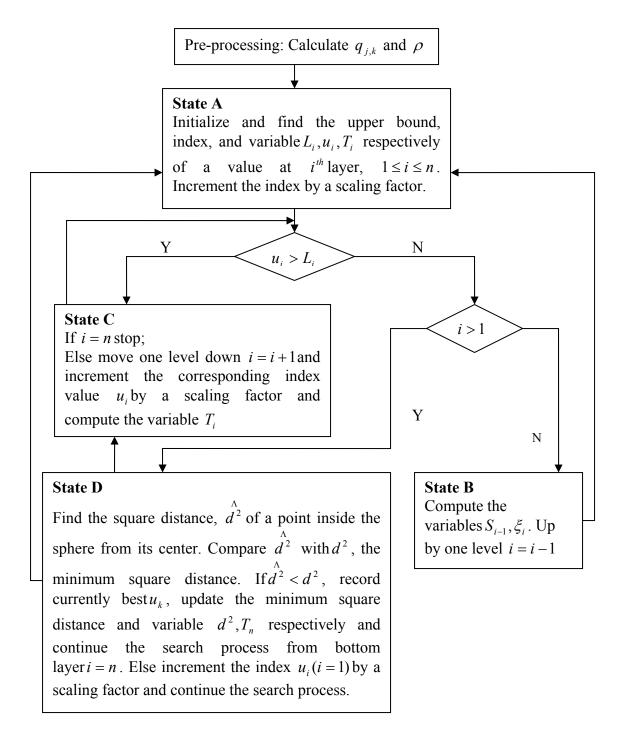

| Figure 4.2: Flow chart of an improved algorithm showing states39Figure 4.3: Input and Output pins for improved sphere decoder40Figure 4.4: Overview of the complete system42Figure 4.5: Dependency graph of the Sphere decoding algorithm43Figure 5.1: The hardware architecture of improved sphere decoding algorithm46Figure 5.2: The hardware architecture of parallel-pipeline improved sphere decoding algorithm48Figure 5.3: An example of improved sphere decoding algorithm (a) Sequential implementation49(b) Parallel-Pipeline implementation49Figure 5.4: Design flow for an FPGA.52Figure 5.5: Workspace of Project Navigator53Figure 5.6: RTL schematic of parallel-pipeline implemented sphere decoder generated by Xilinx56Figure 6.1: Bar chart showing the simulations times of each states in both algorithms59Figure 6.2: Xilinx Virtex-II 1000 FPGA Device Description61Figure 6.3: BER vs. Eb/No (dB) for an uncoded system using original and improved algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Figure 3.4: The FSM diagram of Sphere decoding algorithm                                   | 26     |

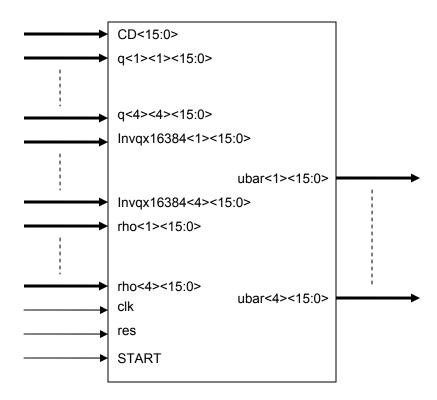

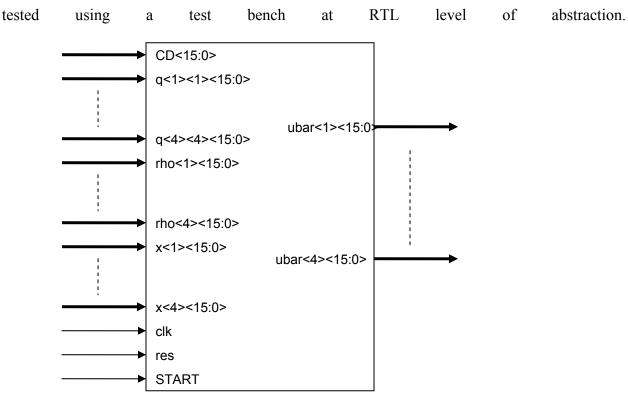

| Figure 4.3: Input and Output pins for improved sphere decoder       40         Figure 4.4: Overview of the complete system       42         Figure 4.5: Dependency graph of the Sphere decoding algorithm       43         Figure 5.1: The hardware architecture of improved sphere decoding algorithm       46         Figure 5.2: The hardware architecture of parallel-pipeline improved sphere decoding algorithm       46         Figure 5.2: The hardware architecture of parallel-pipeline improved sphere decoding algorithm       48         Figure 5.3: An example of improved sphere decoding algorithm (a) Sequential implementation       49         Figure 5.4: Design flow for an FPGA.       52         Figure 5.5: Workspace of Project Navigator       53         Figure 5.6: RTL schematic of parallel-pipeline implemented sphere decoder generated by Xilinx       56         Figure 6.1: Bar chart showing the simulations times of each states in both algorithms       59         Figure 6.2: Xilinx Virtex-II 1000 FPGA Device Description       61         Figure 6.3: BER vs. Eb/No (dB) for an uncoded system using original and improved algorithms       59                                                                                                                                                                                                                                                                                    |                                                                                            |        |

| Figure 4.3: Input and Output pins for improved sphere decoder       40         Figure 4.4: Overview of the complete system       42         Figure 4.5: Dependency graph of the Sphere decoding algorithm       43         Figure 5.1: The hardware architecture of improved sphere decoding algorithm       46         Figure 5.2: The hardware architecture of parallel-pipeline improved sphere decoding algorithm       46         Figure 5.2: The hardware architecture of parallel-pipeline improved sphere decoding algorithm       48         Figure 5.3: An example of improved sphere decoding algorithm (a) Sequential implementation       49         Figure 5.4: Design flow for an FPGA.       52         Figure 5.5: Workspace of Project Navigator       53         Figure 5.6: RTL schematic of parallel-pipeline implemented sphere decoder generated by Xilinx       56         Figure 6.1: Bar chart showing the simulations times of each states in both algorithms       59         Figure 6.2: Xilinx Virtex-II 1000 FPGA Device Description       61         Figure 6.3: BER vs. Eb/No (dB) for an uncoded system using original and improved algorithms       59                                                                                                                                                                                                                                                                                    | Figure 4.2: Flow chart of an improved algorithm showing states                             | 39     |

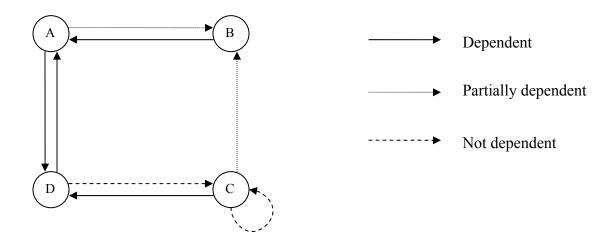

| Figure 4.5: Dependency graph of the Sphere decoding algorithm       43         Figure 5.1: The hardware architecture of improved sphere decoding algorithm       46         Figure 5.2: The hardware architecture of parallel-pipeline improved sphere decoding algorithm       48         Figure 5.3: An example of improved sphere decoding algorithm (a) Sequential implementation       49         Figure 5.4: Design flow for an FPGA.       52         Figure 5.5: Workspace of Project Navigator       53         Figure 5.6: RTL schematic of parallel-pipeline implemented sphere decoder generated by Xilinx       56         Figure 6.1: Bar chart showing the simulations times of each states in both algorithms.       59         Figure 6.2: Xilinx Virtex-II 1000 FPGA Device Description       61         Figure 6.3: BER vs. Eb/No (dB) for an uncoded system using original and improved algorithms       61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                            |        |

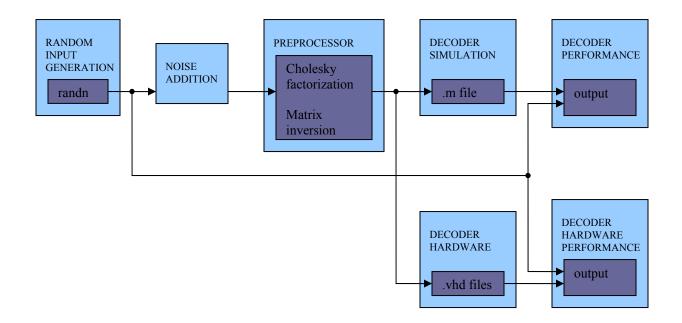

| Figure 4.5: Dependency graph of the Sphere decoding algorithm       43         Figure 5.1: The hardware architecture of improved sphere decoding algorithm       46         Figure 5.2: The hardware architecture of parallel-pipeline improved sphere decoding algorithm       48         Figure 5.3: An example of improved sphere decoding algorithm (a) Sequential implementation       49         Figure 5.4: Design flow for an FPGA.       52         Figure 5.5: Workspace of Project Navigator       53         Figure 5.6: RTL schematic of parallel-pipeline implemented sphere decoder generated by Xilinx       56         Figure 6.1: Bar chart showing the simulations times of each states in both algorithms       59         Figure 6.2: Xilinx Virtex-II 1000 FPGA Device Description       61         Figure 6.3: BER vs. Eb/No (dB) for an uncoded system using original and improved algorithms       61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 4.4: Overview of the complete system                                                | 42     |

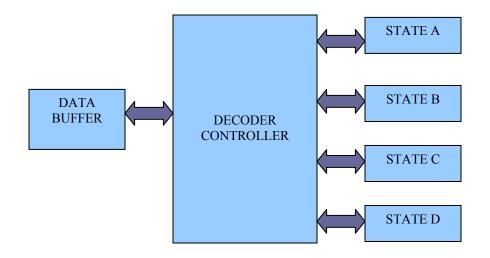

| Figure 5.2: The hardware architecture of parallel-pipeline improved sphere decoding algorithm       48         Figure 5.3: An example of improved sphere decoding algorithm (a) Sequential implementation       49         (b) Parallel-Pipeline implementation       49         Figure 5.4: Design flow for an FPGA.       52         Figure 5.5: Workspace of Project Navigator       53         Figure 5.6: RTL schematic of parallel-pipeline implemented sphere decoder generated by Xilinx       56         Figure 6.1: Bar chart showing the simulations times of each states in both algorithms       59         Figure 6.2: Xilinx Virtex-II 1000 FPGA Device Description       61         Figure 6.3: BER vs. Eb/No (dB) for an uncoded system using original and improved algorithms       61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                            |        |

| 48         Figure 5.3: An example of improved sphere decoding algorithm (a) Sequential implementation         (b) Parallel-Pipeline implementation         49         Figure 5.4: Design flow for an FPGA.         52         Figure 5.5: Workspace of Project Navigator         53         Figure 5.6: RTL schematic of parallel-pipeline implemented sphere decoder generated by Xilinx         ISE 6.2i         56         Figure 6.1: Bar chart showing the simulations times of each states in both algorithms         59         Figure 6.2: Xilinx Virtex-II 1000 FPGA Device Description         61         Figure 6.3: BER vs. Eb/No (dB) for an uncoded system using original and improved algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 5.1: The hardware architecture of improved sphere decoding algorithm                | 46     |

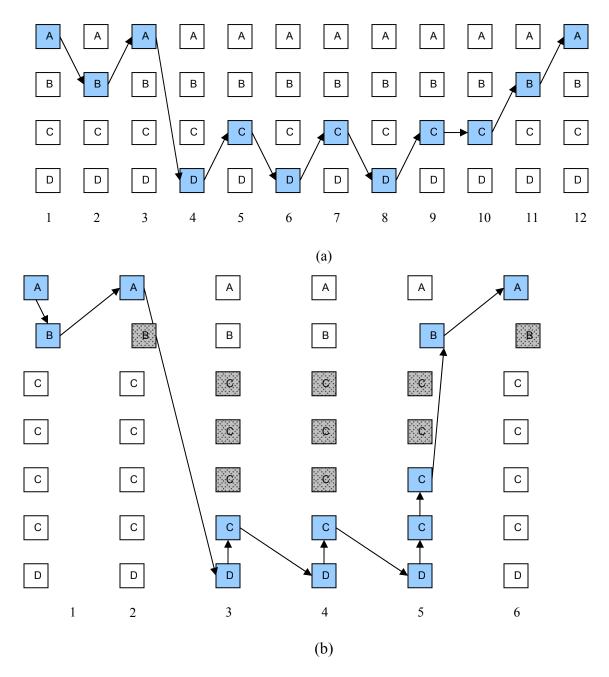

| Figure 5.3: An example of improved sphere decoding algorithm (a) Sequential implementation       49         (b) Parallel-Pipeline implementation       49         Figure 5.4: Design flow for an FPGA       52         Figure 5.5: Workspace of Project Navigator       53         Figure 5.6: RTL schematic of parallel-pipeline implemented sphere decoder generated by Xilinx       56         Figure 6.1: Bar chart showing the simulations times of each states in both algorithms       59         Figure 6.2: Xilinx Virtex-II 1000 FPGA Device Description       61         Figure 6.3: BER vs. Eb/No (dB) for an uncoded system using original and improved algorithms       61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Figure 5.2: The hardware architecture of parallel-pipeline improved sphere decoding algor  | ithm   |

| (b) Parallel-Pipeline implementation49Figure 5.4: Design flow for an FPGA.52Figure 5.5: Workspace of Project Navigator53Figure 5.6: RTL schematic of parallel-pipeline implemented sphere decoder generated by Xilinx56ISE 6.2i56Figure 6.1: Bar chart showing the simulations times of each states in both algorithms59Figure 6.2: Xilinx Virtex-II 1000 FPGA Device Description61Figure 6.3: BER vs. Eb/No (dB) for an uncoded system using original and improved algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                            | 48     |

| Figure 5.4: Design flow for an FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Figure 5.3: An example of improved sphere decoding algorithm (a) Sequential implementation | ation  |

| Figure 5.5: Workspace of Project Navigator       53         Figure 5.6: RTL schematic of parallel-pipeline implemented sphere decoder generated by Xilinx       56         ISE 6.2i       56         Figure 6.1: Bar chart showing the simulations times of each states in both algorithms       59         Figure 6.2: Xilinx Virtex-II 1000 FPGA Device Description       61         Figure 6.3: BER vs. Eb/No (dB) for an uncoded system using original and improved algorithms       61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (b) Parallel-Pipeline implementation                                                       | 49     |

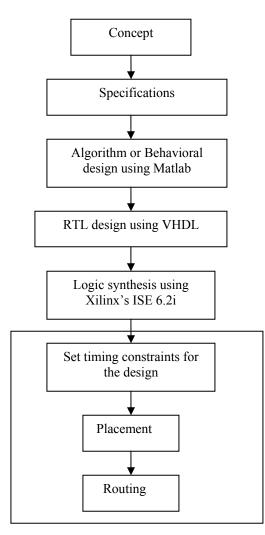

| <ul> <li>Figure 5.6: RTL schematic of parallel-pipeline implemented sphere decoder generated by Xilinx ISE 6.2i</li> <li>Figure 6.1: Bar chart showing the simulations times of each states in both algorithms</li> <li>59</li> <li>Figure 6.2: Xilinx Virtex-II 1000 FPGA Device Description</li> <li>61</li> <li>Figure 6.3: BER vs. Eb/No (dB) for an uncoded system using original and improved algorithms</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Figure 5.4: Design flow for an FPGA                                                        | 52     |

| ISE 6.2i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Figure 5.5: Workspace of Project Navigator                                                 | 53     |

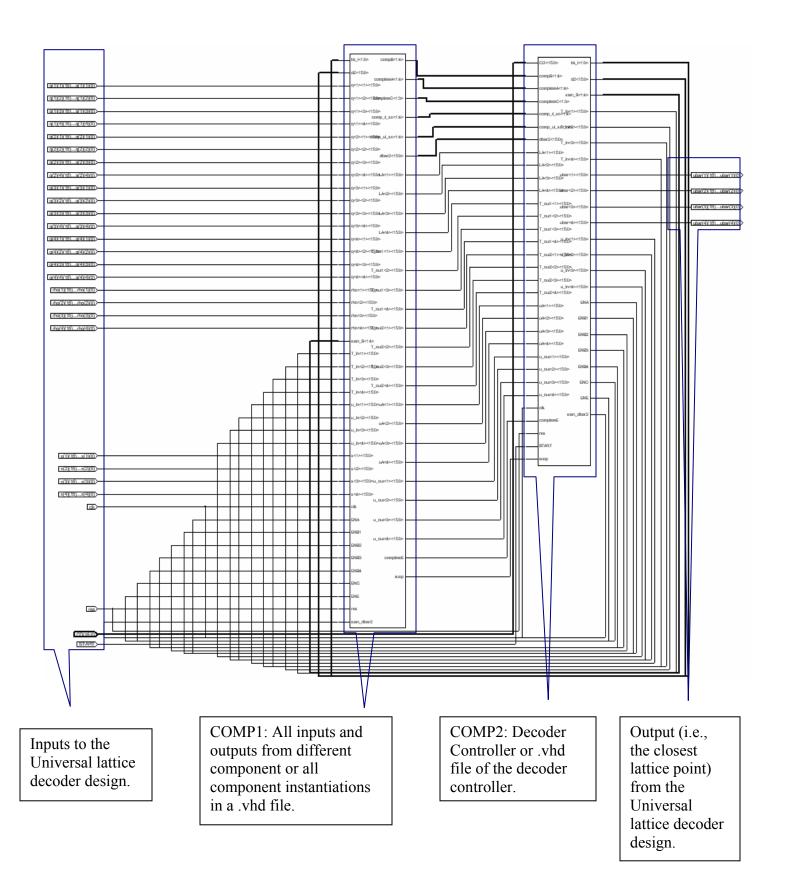

| ISE 6.2i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Figure 5.6: RTL schematic of parallel-pipeline implemented sphere decoder generated by 2   | Xilinx |

| Figure 6.2: Xilinx Virtex-II 1000 FPGA Device Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                            |        |

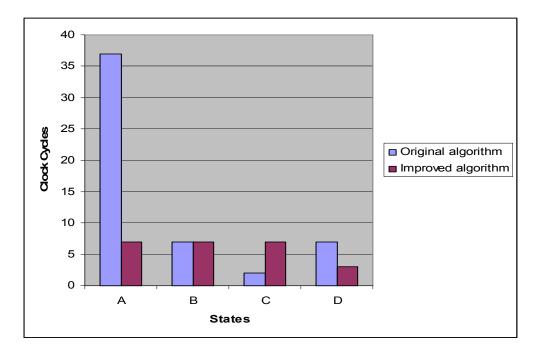

| Figure 6.3: BER vs. Eb/No (dB) for an uncoded system using original and improved algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 6.1: Bar chart showing the simulations times of each states in both algorithms      | 59     |

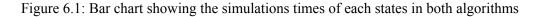

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 6.2: Xilinx Virtex-II 1000 FPGA Device Description                                  | 61     |

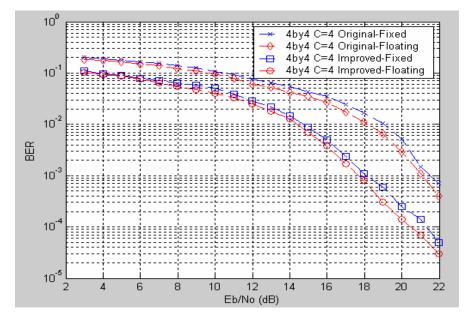

| 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Figure 6.3: BER vs. Eb/No (dB) for an uncoded system using original and improved algori    | ithms  |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                            | 67     |

# LIST OF TABLES

| Table 3.1: Pin descriptions for the decoder controller of the original sphere decoding alg | gorithm   |

|--------------------------------------------------------------------------------------------|-----------|

|                                                                                            |           |

| Table 3.1: Simulation Times of each state in original algorithm                            |           |

| Table 4.1: Pin descriptions for the decoder controller of the improved sphere decoding a   | algorithm |

|                                                                                            |           |

| Table 4.2: Simulation Times of each state in improved algorithm                            |           |

| Table 5.1: Sequence of states for an example of improved algorithm at 6dB SNR              |           |

| Table 6.1: Average number of state visits in sequential implementation at 20 dB            | 60        |

| Table 6.2: Average number of state visits in parallel-pipeline implementation at 20 dB     | 60        |

| Table 6.3: Synthesis results of m=n=4 MIMO system                                          | 61        |

| Table 6.4: Sequence of state in Sequential procedure                                       |           |

| Table 6.5: Sequence of state in Parallel-Pipeline procedure                                |           |

| Table 6.6: Comparison of decoding rate at 20 dB.                                           |           |

| Table 6.7: Comparison between FPGA and DSP implementation at 20 dB                         |           |

## ABSTRACT

In wireless communication, MIMO (multiple input multiple output) is one of the promising technologies which improves the range and performance of transmission without increasing the bandwidth, while providing high rates. High speed hardware MIMO decoders are one of the keys to apply this technology in applications. In order to support the high data rates, the underlying hardware must have significant processing capabilities. FPGA improves the speed of signal processing using parallelism and reconfigurability advantages.

The objective of this thesis is to develop an efficient hardware architectural model for the universal lattice decoder and prototype it on FPGA. The original algorithm is modified to ensure the high data rate via taking the advantage of FPGA features. The simulation results of software, hardware are verified and the BER performance of both the algorithms is estimated. The system prototype of the decoder with 4-transmit and 4-receive antennas using a 4-PAM (Pulse amplitude modulation) supports 6.32 Mbit/s data rate for parallel-pipeline implementation on FPGA platform, which is about two orders of magnitude faster than its DSP implementation.

## **1 INTRODUCTION**

## 1.1 Motivations and Background

Although wireless technologies have been around for a while, there has been a recent and rapid surge in the evolution of new standards that enable and accelerate the convergence of telecommunications and IP networking to provide new multimedia services. To keep up with the demands of wireless network services, the capacities of systems are increased. The most brute-force approach to increasing wireless data rate is to use more frequency channels to increase modulation rate [Jones 2003]. This "channel bonding" approach will not meet the needs of wireless network consumers for the following reasons: First, while channel bonding increases data rate, it decreases the transmission range for the same transmit power. Second, channel bonding robs channels from other systems that operate nearby.

MIMO (multiple input multiple output) antenna technology is considered as one of the solutions to support the wireless network services. It essentially multiplies data throughput, with a simultaneous increase in range and reliability, without consuming any extra frequency spectrum [Jones 2003]. The multi-antenna wireless communication systems are capable of providing data transmission at potentially very high rates. Furthermore, to secure high reliability of the data transmission, special attention has to be given to the receiver design. The data streams are separated at the receiver using algorithms that rely on estimates of all channels between each transmitter and each receiver. The low complexity suboptimal detection algorithm for MIMO signals was the Vertical Bell Labs Layered Space-Time (VBLAST) algorithm. This is an iterative cancellation method that depends on computing a matrix inverse to solve the zero-

forcing function [Jones 2003]. While the iterative detection can increase receiver sensitivity, there are substantial problems with a real implementation.

The optimal detection strategy for a MIMO receiver is to perform a maximum-likelihood search over all possible transmitted symbol sets. ML decoding is equivalent to finding the closest lattice point to the received point in a lattice constellation. ML detection at the receiver becomes an essential part in high-performance MIMO communication systems [Burg 2004]. Thus, ML decoding algorithms and their architecture are active research areas in wireless communication that motivated the research in MIMO systems.

For decoding the lattices with no regular structure at the receiver follows two main branches. Pohst [Pohst 1981] in 1981 examined lattice points lying inside a hyper sphere, whereas Kannan in 1983 used a rectangular parallelepiped. Both methods later appeared in revised and extended versions. Pohst method is intended as practical tool while Kannan's is a theoretical tool. In [Viterbo 1999], a technique referred to as the "sphere decoding" (based on the Fincke-Pohst algorithm) was proposed for lattice code decoding [Eriksson 2002]. This performs a bounded distance search among the lattice points falling inside the sphere centered at the received point.

The sphere decoder provides the maximum-likelihood estimate of the transmitted signal sequence with complexity comparable, at high signal-to-noise ratios (SNRs), to VBLAST nulling/canceling algorithm [Bertrand 2003]. It is later stated that sphere decoding often significantly outperforms heuristic nulling and canceling. Developing an efficient sphere decoder with reduced complexity has received significant attention due to its applications to wireless communications as in [Viterbo 1999]. However, most modifications suggested are well suited for implementations using DSPs, for example BLAST system [Adjoudani 2003]. In the VBLAST

algorithm the front end of the receiver is implemented on FPGA whereas actual decoder function is implemented on a DSP processor.

As the performance requirements of today's communication systems are outstripping the capabilities of general-purpose DSP processors, the need for DSP implementations to seek hardware solution arises [Dan 2004]. FPGAs provide an ideal platform for DSP implementation, combining the reprogrammability, architectural flexibility, and support of parallelism. FPGA-based hardware platforms also meet the critical requirements such as processing speed, time-to-market, system integration etc. Due to the significant processing capabilities of FPGAs, high data rates are ensured for signal processing applications implemented on FPGAs. With advanced FPGA architectures such as the Xilinx Virtex-II devices, a new hardware alternative is available for DSP implementations combining all the benefits of DSP processors with the performance advantages of ASICs [Dan 2004].

The key advantages of FPGAs when compared to DSP implementations include performance, integration, and customization. Because of this, an FPGA-based solution of a highperformance DSP system will typically have fewer devices than a processor-based one resulting in less power consumption, lower overall cost, and significantly less board area [Kevin 2003]. Due to the support of parallelism, FPGAs achieve huge gains in performance compared to DSP implementations. The computational throughput is also at least an order of magnitude higher with FPGA platforms.

Comparing to ASICs, FPGAs are reprogrammable and when combined with HDL design flow can greatly reduce the design and verification cycle. In addition to this, increased time-tomarket demands, low FPGA development costs, and FPGA capacities well in excess of million gates are increasing the number of applications of FPGAs in programmable form [ED 2000].

3

## 1.2 Research Objective

The main objective of this thesis is to develop an efficient architecture of a sphere decoder simulated in VHDL and prototype it on device technology of XILINX VirtexII-1000 FPGA platform. The architectural model deploys the parallelism offered by FPGA and ensures the high data rate of the MIMO system.

### 1.3 Contribution of Thesis

The main contribution in this thesis is the design and implementation of an universal lattice decoder on FPGA. Firstly, the functionality of original sphere decoding algorithm is examined using Matlab simulations. Then a VHDL model is developed for core decoder function and simulated at RTL level of abstraction using Mentor Graphics' Modelsim SE 5.8a. Based on the simulation results, we observed that the original sphere decoder is not feasible for parallelpipeline implementation. Modifications are applied to the original algorithm and as a result an improved form of universal lattice decoder is proposed. Functionality testing procedure similar to that of original algorithm is carried out for the improved algorithm. Based on the data dependency analysis, a parallel-pipeline architectural model is developed for the improved sphere decoding algorithm. Both sequential and parallel-pipeline architectural models are developed in VHDL and are simulated at RTL level of abstraction. All the hardware architectural models are prototyped on a XC2V1000-6FF896C, a device technology of Xilinx VirtexII-1000 FPGA platform. BER performance of original and improved sphere decoding algorithms is compared for both fixed point and floating point simulations. For a 4-transmit and 4-receive antennas system using 4-PAM transmitted signals, a decoding throughput of 6.32

Mbits/s is achieved. The performances of FPGA and DSP implementations are compared. The details of the results are presented in Chapter 6.

## 1.4 Organization of Thesis

Chapter 2 introduces FPGA and MIMO channels. Their concepts and features are explained in detail. Chapter 3 describes the original sphere decoding algorithm. It also discusses the data flow path by partitioning the algorithm into various states. Eventually the Finite state machine (FSM) design is proposed, state transitions are discussed and simulation times for each state are also presented. Chapter 4 presents the modifications applied to the original algorithm by avoiding square root. Thus, an improved sphere decoding algorithm is developed. In addition, data dependency analysis of the improved sphere decoder is discussed. Chapter 5 gives the detail description of the FSM design for the improved sphere decoder. Also, the parallel-pipeline structure of sphere decoding algorithm is described, and the design optimization techniques are presented. Finally Chapter 6 gives the experimental results obtained during the thesis research.

## 2 FPGAs and MIMO Channels

This chapter gives a brief introduction of FPGA and MIMO channel. A detail description explaining the basic concept, features is also given.

#### 2.1 MIMO Channels

The ever increasing demands of multimedia services have led to high speed wireless communications with much higher data rates. Multiple transmit and receive antennas are most likely the dominant solution in future broadband wireless communication systems as they are the key technology to produce high rates.

MIMO systems consist of an array of transmit and receive antennas combined in such a way that the quality (bit error rate) or the rate (Bit/sec) of the communication is improved [Gesbert 2005]. Use of multiple transmit and/or receive antennas produce enormous gain in spectral efficiency by exploiting a rich multi-path fading environment and increased the system capacity without requiring an increase in the transmit power or bandwidth of the system. These channels also provide radio-link reliable communication when multiple users are sharing the spectrum by reducing the fading environments which is sometimes possible through the use of diversity technique. The spatial diversity in the MIMO systems is to send the signals that carry the same data through different paths. Due to this multiple independently faded replicas of the same data symbol can be obtained at the receiver end and hence more reliable reception is achieved. If the path gains between individual transmit-receive antenna pairs fade independently, the channel matrix well conditioned with high probability such that multiple parallel spatial channels are created [Zheng 2003]. The spatial multiplexing of the MIMO system which helps in achieving high data rates is to split a single data stream into multiple sub-streams, and each of

these independent sub-streams is transmitted in parallel through those spatial channels with same frequency. In wireless channels the data streams transmitted from multiple transmit antennas can be separated, thus leading to the parallel data paths. Under these conditions, the capacity of the radio channel grows linearly with the number of antennas used either at the transmitter or receiver. The scattering of signals, which interferes with one another in a single-antenna system, if exploited properly can enhance, rather than degrade the transmission accuracy and huge channel capacities are intended to achieve [Garrett 2002]. Multi-path propagations can make the output of receiver antenna to be equal to a linear combination of the multiple transmitted data streams. Thus with sophisticated coding at the transmitter and substantial signal processing at the receiver, the MIMO channel can be provisioned for higher data rates [Love 2004].

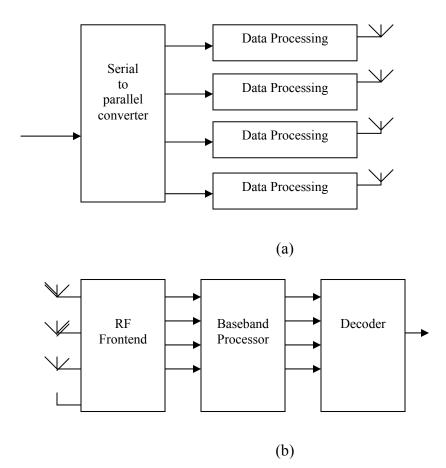

Figure 2.1: A MIMO system. (a) MIMO Transmitter. (b) MIMO receiver

Figure 2.1 shows a schematic representation of this multiple input multiple output (MIMO) system [Adjoudani 2003]. The complexity of the MIMO systems is involved in designing an optimal receiver for the system. The optimal receiver is a maximum-likelihood sequence detector and is computationally complex due to system parameters like number of antennas and type of constellation used. Therefore the optimal detection strategy is to equivalent to performing a maximum-likelihood search over all possible transmitted symbol vectors. When there is a perfect knowledge of channel state information at the receiver the sphere decoding algorithm is considered as the maximum likelihood decoder.

There are two typical lattice decoding algorithms. One is the Pohst strategy based algorithm [Viterbo 1999]. This tries to find lattice points inside a sphere of given radius. Another is the Schnorr-Euchner strategy based algorithm [Eriksson 2002]. This method divides the lattice into hyper-planes and starts the search for the closet point in the nearest hyper-plane.

## 2.2 Field Programmable Gate Array (FPGA)

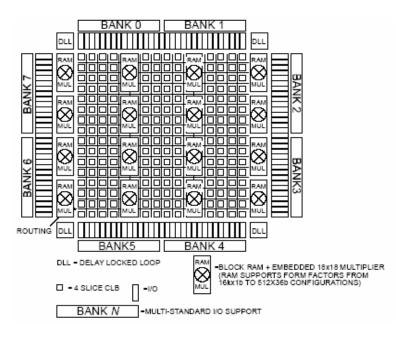

FPGA is an integrated circuit that contains configurable (programmable) logic blocks and interconnects between these blocks. In other words, it is a general purpose chip which can be reconfigured any number of times to carry out specific hardware functions. It provides an opportunity of instantaneous changes in designing and debugging. It allows for system reuse, parallel design and SOC design. This is the result of combinatorial features of PLD and ASIC. PLD is a digital IC that can be programmed by the user to perform a wide variety of logical operations. ASIC is an IC product customized to perform specific functions to a particular system or application. Like PLD, FPGA is completely prefabricated and contain special features for customization. FPGA is subclass of ASIC which can be reprogrammable. Designs started in FPGA can be migrated to ASICs. A comparison between ASIC, FPGA, and DSP implementations of the any decoder shows that the performance of FPGA-based designs lean more toward that of ASICs but retain flexibility more like DSP [Gregory 1999]. ASICs provide the most optimized hardware implementation of an algorithm. Using a dedicated ASIC for each mode of radio leads to a very large silicon area. DSPs have excellent programmability but cannot handle the complex algorithms at the required speeds with reasonable power consumption. FPGAs on the other hand use hardware reconfiguration, which allows implementation of complex high-speed algorithms [Srikanteswara 2003]. Compared to FPGA implementation, DSP implementations require low cost and less development time. But once an efficient architecture is developed and the parallelism of the algorithm is explored, FPGAs can be used to significantly improve the speed of the signal processing or wireless communication systems. Thus, FPGA is considered as an ideal platform for performing the computationally complex operations for reasons of performance, power consumption and configurability. Compared to DSP chip, parallelism is an additional feature in FPGA. The architecture of the Xilinx Virtex-II FPGA is shown in Figure 2.2. The device is organized as an array of logic elements and programmable routing resources used to provide the connectivity between the logic elements, FPGA I/O pins and other resources such as on-chip memory, delay lock loops and embedded hardware multipliers.

Figure 2.2: Virtex-II FPGA architecture [Chris]

The FPGA resources of particular interest to the signal processing engineer are configurable dual-port block memories, distributed memory, and the multiplier array [Xilinx 2003]. The multiplier array is composed of 18x18-bit precision multipliers for addressing advanced sign al processing applications. The smallest Virtex-II device provides a modest 4 multipliers while the largest supplies an impressive 192 multipliers [Chris].

## 3 Sphere Decoding Algorithm

This chapter describes the Pohst's lattice point enumeration algorithm [Viterbo 1999] widely known as sphere decoding, and also called universal lattice decoding. The data flow path and state transition details are elaborated. High level description of the algorithm and decoder architecture scheduling are also elucidated. The FSM diagram is shown. The table showing the processing time taken by each state is presented.

## 3.1 The Sphere Decoder

In digital communications, lattice codes generate signal constellations for high rate transmission. The high-rate data streams and spatial multiplexing leave MIMO technology as the most desirable option in communication systems. The complexity of MIMO systems is involved in designing a MIMO receiver. For designing a MIMO receiver, a ML decoding is employed. ML decoding of a arbitrary lattice code used over an additive white Gaussian noise (AWGN) channel is equivalent to finding the closest lattice point to the received point. To reduce the complexity of an exhaustive search procedure, the bounded distance search among the lattice points is formulated. Therefore, for decoding the optimal receiver output of these MIMO systems, Pohst's enumeration based sphere decoding algorithm searches for the closest lattice point to the received point within the sphere with radius  $\sqrt{C}$ . The center point i.e., the signal or vector at the receiver is known before hand. The choice of C is very crucial to the speed of the algorithm. In practice the choice of C can be adjusted according to the noise variance so that the probability of a decoding failure reported is negligible. The complexity of the algorithm is independent of the lattice dimension size, which is very useful for high data rate transmission [Viterbo 1999]. Pohst first proposed the strategy for enumerating all the lattice points within the sphere with a certain radius in [Pohst 1985]. Then it was introduced into the field of digital communications for the first time in [Viterbo 1993] and further analyzed in [Viterbo 1999].

#### 3.1.1 Maximum-Likelihood Criterion

Considering a MIMO system with m transmit and n receive antennas, and a perfect knowledge of channel state information is known at the receiver then the maximum likelihood decoding requires minimization of metric

$$\sum_{i=1}^{n} ||r_i - x_i||^2 \quad \forall \text{ valid lattice points.} \qquad \text{Equation (3-1)}$$

Where, r = uM + V, the received vector. When the data streams interfere with each other in the channel and is distorted by an AWGN component *V* then, the resultant is the received vector. *u* is the transmitted signal.

*M* is the channel matrix which generates the lattice.

V is the AWGN noise vector with zero mean and  $N_0$  variance.

x is the information symbol vector mapped into the output vector which is the received vector r. Thus x is considered as one of the transmitted lattice code points.

The representation of lattice points is given as  $\{x = uM\}$  where  $u = \{u_1, u_2, ..., u_n\}$  is the integer component vector, and *M* is the channel transfer matrix which generates the lattice  $\Lambda$  structure. Any lattice  $\Lambda$  is given as the combination of set of basis vectors represented by  $v = \{v_1, v_2, ..., v_n\}$

If  $v_i = (v_{i1}, v_{i2}..., v_{ib})$ , i = 1..., n, and *b* is the dimension of the lattice then the generator matrix *M* of the lattice  $\Lambda$  is defined as

$$M = \begin{pmatrix} v_{11} & \cdots & v_{1b} \\ \vdots & & \vdots \\ v_{n1} & \cdots & v_{nb} \end{pmatrix}$$

The same lattice structure  $\Lambda$  can have any number of generator matrices. For example the matrix of the form M' = TM, where T is an integer orthogonal matrix  $(\det(T) = \pm 1)$ , is also the generator matrix of the lattice  $\Lambda$ . Assuming matrix M to be non-singular square matrix i.e., n = b, the Gram matrix of the lattice  $\Lambda$  is given by

$$G = MM^{T} = \begin{pmatrix} g_{11} & \cdots & g_{1b} \\ \vdots & & \vdots \\ g_{b1} & \cdots & g_{bb} \end{pmatrix}$$

The elements of the matrix G are the Euclidean square products of the pairs of vectors of the lattice basis.

#### 3.1.2 ML Decoding In Sphere Decoder

The lattice decoding algorithm attempts to minimize the metric in Equation (3-1) but employs the bounded distance search procedure. Thus it searches through the points of lattice that are falling inside the sphere of radius  $\sqrt{C}$  and centre at the received point.

Thus, sphere decoding problem is to solve

$$\min_{x \in \Delta} \| r - x \| = \min_{w \in r - \Delta} \| w \|$$

Equation (3-2)

So we search for the shortest vector w in the translated lattice  $r - \Lambda$  in the *n*-dimensional Euclidean space  $R^n$ . We write

$$x = uM \text{ with } u \in z^n$$

$$r = \rho M \text{ with } \rho = (\rho_1, \rho_2 \dots \rho_n) \in R^n$$

$$w = \xi M = \sum_{i=1}^n \xi_i v_i \text{ with } \xi = (\xi_1, \xi_2, \dots, \xi_n) \in R^n \text{ and } \xi_i = \rho_i - u_i, i = 1, \dots, n$$

Where,  $\rho$  and  $\xi$  are real vectors.

$\rho = rM^{-1}$  i.e.,  $\rho$  is equal to the matrix product of the received vector r, and the inverse of generator matrix  $M^{-1}$ .  $\xi$  defines the translated coordinated axes in sphere of the integer component vectors u of the cubic lattice  $Z^n$

## 3.2 Flow-Chart

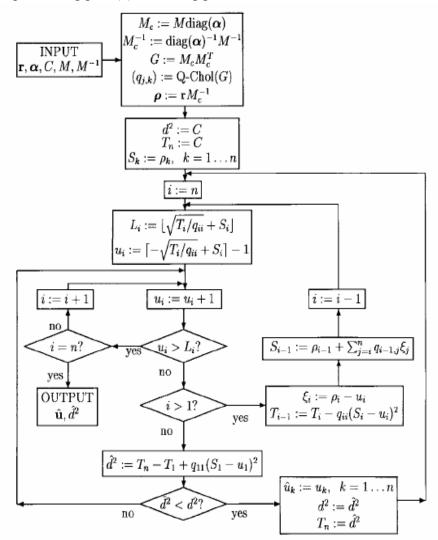

The flow chart showing of a Lattice decoding algorithm [Viterbo 1999] or a Universal lattice decoder is shown in Figure 3.1. The lattice decoding algorithm can be divided into two parts (1) Pre-processing part (2) Decoding part.

Figure 3.1: Flowchart of a Sphere decoding algorithm [Viterbo 1999]

#### 3.2.1 Pre-Processing

The pre-processing stage of the sphere decoding algorithm involves the complex computations like Cholesky decomposition of the Gram matrix G, finding inverse and transpose of generator matrix M. The resultant matrices are passed to the decoding part where they are further exploited to carry on other computations, thereby reducing the complexity of the decoding part. The variables and specialized functions used at this stage are described in detail below.

An inverse matrix of the lattice generator matrix is computed. Another important function carried out in the preprocessing stage in the algorithm is the Cholesky factorization of the Gram matrix G. Gram matrix is equal to the product of lattice generator matrix M and its transpose,

$G = MM^T$  yields  $G = R^T R$  where, R is the upper triangular matrix.

From the algorithm  $(q_{i,k})$  is the element of Cholesky factor matrix.

#### 3.2.2 Decoding

In the decoding part, the integer component of lattice point vector u closest to the transmitted signal constellation x is found as an output when the Cholesky factor matrix  $(q_{j,k})$ , the square radius of the sphere C and the received vector with respect to lattice  $\rho$  are taken as inputs.

Considering the metric properties of the lattice, we can say that the minimum squared Euclidean distance between any two points of lattice equals the minimum of the quadratic form  $Q(\xi)$ .

$$Q(\xi) = \xi G \xi^{T} = \xi M M^{T} \xi^{T}$$

Equation (3-2)

If the lattice point being searched is within the sphere with square radius *C* and centered at the received point then

$$\|w\|^2 = Q(\xi) = \xi M M^T \xi^T = \sum_{i=1}^n \sum_{j=1}^n g_{ij} \xi_i \xi_j \le C$$

Equation (3-3)

Thus the sphere of square radius *C* and centered at the received point is transformed into an ellipsoid centered at origin of the new coordinate system defined by  $\xi$ .

Cholesky factorization yields  $G = R^T R$ , where *R* is an upper triangular matrix. By further analyzing the above equations we get

$$Q(\xi) = \xi R^T R \xi^T = \left\| R \xi \right\|^2 = \sum_{i=1}^n (r_{ii}\xi_i + \sum_{j=i+1}^n r_{ij}\xi_j)^2 \le C$$

Equation (3-4)

Substituting  $q_{ii} = r_{ii}^2$  and  $q_{ij} = r_{ij} / r_{ii}$  for i = 1, ..., n, j = i + 1, ..., n, we can write (3-4) as follows

$$Q(\xi) = \sum_{i=1}^{n} q_{ii} (\xi_i + \sum_{j=i+1}^{n} q_{ij} \xi_j)^2 \le C$$

Equation (3-5)

We find the equations of the border of the ellipsoid to estimate the upper and lower bounds of the integer component value  $u_i$  at the  $i^{th}$  layer. Therefore the ranges for the integer component value at  $i^{th}$  layer are given by

$$\begin{bmatrix} -\sqrt{\frac{1}{q_{ii}}} \left( C - \sum_{l=i+1}^{n} q_{ll} (\xi_{l} + \sum_{j=l+1}^{n} q_{lj} \xi_{j})^{2} \right) + \rho_{i} + \sum_{j=i+1}^{n} q_{ij} \xi_{j} \end{bmatrix} \le u_{i} \le \left[ \sqrt{\frac{1}{q_{ii}}} \left( C - \sum_{l=i+1}^{n} q_{ll} (\xi_{l} + \sum_{j=l+1}^{n} q_{lj} \xi_{j})^{2} \right) + \rho_{i} + \sum_{j=i+1}^{n} q_{ij} \xi_{j} \end{bmatrix}$$

Equation (3-6)

Thus the upper bound,  $L_i$  and the index,  $u_i$  are simplified as follows

$L_{i} = \left\lfloor \sqrt{T_{i} / q_{ii}} + S_{i} \right\rfloor$ Equation (3-7)  $u_{i} = \left\lceil -\sqrt{T_{i} / q_{ii}} + S_{i} \right\rceil - 1$ Equation (3-8) Where, the variables  $S_i$  and  $T_i$  are written as

$$S_i(\xi_{i+1},\ldots,\xi_n) = \rho_i + \sum_{l=i+1}^n q_{il}\xi_l$$

Equation (3-9)

$$T_{i-1} = T_{i-1}(\xi_i \dots \xi_n) = C - \sum_{j=l+1}^n q_{lj} \xi_j = T_i - q_{ii} (S_i - u_i)^2$$

Equation (3-10)

Thus the variables  $S_i$ ,  $T_i$  and one of the outputs of the pre-processing part  $q_{ii}$  are used to determine and recursively update the values of bounds.

The index  $u_i$  is initially fixed at the lower bound and incremented in steps until it exceeds the upper bound of that layer. Search procedure starts at the bottom layer i.e., at i = 4 and continues switching the layers step by step by checking various conditions at each layer until it reaches the top layer and a valid lattice point vector is reported. When the vector inside the sphere is found, its square distance from the center is computed which is given by

This value is compared to the minimum square distance  $d^2$  (initially set equal to *C*) found so far in the search. If it is smaller then we have a new candidate closest point and new value for  $d^2$  updated with  $d^2$ . Thus the search continues like this until all the vectors inside the sphere are tested.

If no point in the sphere is found the sphere is declared empty and the search fails. In this case the squared radius C must be increased and the search is restarted. Thus finally we search the lattice point closest to received point.

The advantage of this method is that we never test the vectors which are present outside the sphere.

## 3.3 Decoding Procedure

The original sphere decoding algorithm performs step-by-step procedure as follows,

The inputs are  $C, \rho, Q$  and output is  $u^{\Lambda}$

Step 1. (Initialization)

Set  $i = n, T_n = C, d^2 = C$  (current sphere square radius) and

$$S_k = \rho_k, k = 1....n$$

**Step 2**. (Bounds on index  $u_i$ )

Compute the upper and lower bounds. Assign the upper bound to  $L_i$  and the lower bound to index  $u_i$  initially. Thus

$$L_{i} = \left[\sqrt{T_{i} / q_{ii}} + S_{i}\right]$$

$$u_{i} = \left[-\sqrt{T_{i} / q_{ii}} + S_{i}\right] - 1$$

Step 3. (Natural spanning of the interval)

Increment the index  $u_i$  by one step, i.e.,  $u_i = u_i + 1$

If  $u_i \le L_i$  and i > 1, i.e., the index is within the range and layer is not the top layer then go to Step 5, else if  $u_i \le L_i$  and i = 1, i.e., the index of the top layer is within the bound then go to Step 6, else if  $u_i > L_i$  go to Step 4.

Step 4. (Increase *i*: move one level down)

If i = n terminate, i.e., the end of the search procedure is reached and closest lattice point to received point is found, else set i = i + 1, i.e., the search procedure goes one level down in the hierarchy, and go to Step 3.

Step 5. (Decrease *i*: move one level up)

Let

$$\xi_i = \rho_i - u_i$$

$S_{i-1} = \rho_{i-1} + \sum_{l=i}^n q_{i-1,l} \xi_l$

$T_{i-1} = T_i - q_{ii} (S_i - u_i)^2$

$i = i - 1$  and go to Step 2.

The variables needed to recursively update the lower and upper bounds are computed at this step and the search procedure goes one layer up in the hierarchy to re-compute the upper bound and index  $u_i$ .

#### Step 6. (A valid point is found)

Compute  $d^2 = C - T_1 + q_{11}(S_1 - u_1)^2$ , the square distance of the vector found from the center. Then compare this value to the minimum square distance  $d^2$  i.e., If  $d^2 < d^2$  then save the lattice point,  $\overset{\Lambda}{u}_k = u_k$ , k = 1...,n and reduce the search area by assigning the minimum square distance value  $d^2$  with  $\overset{\Lambda}{d^2}$  and the variable  $T_n$  at the bottom layer with  $\overset{\Lambda}{d^2}$  and again set i = n.

Then go to Step 2 repeat the whole process once again. Else go to Step 3, where the index value  $d^2 = d$ ,  $T_n = d$  $u_i$  at each layer is incremented and the search procedure continues as mentioned.

## 3.4 High Level Simulation of the Sphere Decoding Algorithm

Before actually carrying out the implementation of the sphere decoding algorithm in the next section, which is the main concern of our thesis, it was felt necessary to visualize the functionality and working of the sphere decoder. Therefore the whole algorithm, including both

pre-processing and decoding parts is initially developed in Matlab for simulating at behavioral level. The complete system is brief below:

• Generation of Lattice generator matrix based on normally distributed random numbers generated using MATLAB function "randn"

• Generating the upper triangular matrix by Cholesky decomposing of the gram matrix.

• After the input information to the decoder is ready, sphere decoding algorithm which finds the closest lattice point is simulated using Matlab. Its functionality is verified by comparing the obtained lattice point with the transmitted signal constellation vector.

The functionality of the decoder is verified at high level of abstraction and behavior of the decoder design is simulated using Matlab. Thus preliminary information of outputs is obtained. After ensuring the functionality of the decoder design, the corresponding hardware architecture is planned.

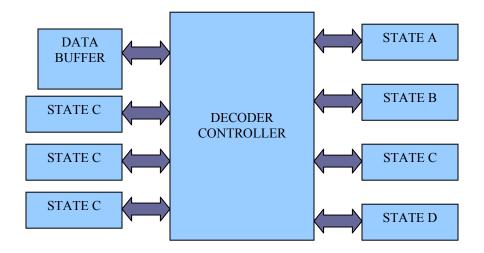

#### 3.5 Decoder Architecture Scheduling

The hardware architectural model of Sphere decoder is planned in accordance with the simulated version. Each of the operations like calculating the bounds, calculating variables needed to update the bounds, spanning of index at each level and finding the Euclidean distance of a point from the received point are dealt in separate blocks. Different components are designed for specific set of operations at each block. Each of these blocks are designed in VHDL and tested for their functioning with the help of stand alone test benches and different sets of data. Digital circuit designs are invariable faced with the need to design circuits that perform specific sequence of operations, for example controllers used to control the operation of other circuits [Smith 1997]. Thus the decoder controller is designed for the original sphere decoding