CONF-8510194 - -10

Presented at the Second International Accelerator Controls Workshop, Los Alamos, New Mexico October 7-10, 1985

BNL--37310

DES∪ 005055

JAN 1 6 1935

# STATUS OF THE NATIONAL SYNCHROTRON LIGHT SOURCE UPGRADE

B. B. Culwick & J. D. Smith Brookhaven National Laboratory, Upton N.Y. 11973

The demands for real-time control, data acquisition and display from accelerators of the National Synchrotron Light Source have exceeded the capabilities of the computer control system designed in 1978. In January 1985, a workshop on control systems was held at Brookhaven, one of the purposes of which was to provide impetus and design goals for an upgrade of the NSLS control system. The resulting design is described and its status reported.

## 1. The Original System.

The NSLS control system was originally designed using dual "supermini" computers, Data General S-250's, connected symmetrically via a high speed bus to a star configuration store and forward message network.[1,2] The arms of the star are serial links connected to 64 Intel Multibus 8-bit 8080 type microprocessors which coordinate the monitoring and control of the four accelerators in the project. The system performance was adequate to allow development and commissioning of the accelerators and is in full use today. Recently, the NSLS has become a fully operational complex with design brightness and performance levels met or exceeded in the storage rings.

Currently the system is considered inadequate because:

- a) Some accelerator parameters are more dynamic than originally envisaged; for example, the storage ring trim magnets are continuously adjusted during changes in beam energy.

- b) Many real-time displays updated about once per second, are desired to provide operators with a current description of the accelerator status. For example, 60 X-ray vacuum pressures are read, converted from log format, averaged and plotted versus time.

- c) More complex signal processing algorithms are desired to represent beam parameters, etc. The beam current is read up to 100 times per second, converted to floating point, calibrated and a least squares fit done at rates up to once per second.

- d) The real-time requirements on the S-250's result in poor response time to operator requests at the consoles.

- e) There is a requirement to implement modelling programs which exceed the storage space of the 16-bit minicomputers.

The limitations which have been identified as constraining expansion are:

- f) The 64k byte address space of the S-250's permits only very modest programs to reside in the logical address space and limits the operating system and application organization.

- g) The serial links are relatively slow but cannot be speeded up usefully with the present microprocessors and message network processors.

- h) In most cases devices are addressed one per network message which produces excessive overhead in the operating system and serial links.

- i) The microprocessors are coded in assembly language which is unsuited for higher level signal processing and cumbersome.

#### 2. The Workshop.

The January 1985 workshop presented a general review of activities in the accelerator control field but, specifically for the benefit of the NSLS, addressed questions relevant to an upgrade of the present system. Apart from specific topics, 5 systems more or less relevant to the requirements of the NSLS were described. These were:

## a) Los Alamos Proton Storage Ring.

This system has a central VAX computer with peripheral LSI lls. Equipment is interfaced via CAMAC. The operator workstations are provided via a high speed graphics display processor interfaced to the VAX. Hardware and soft-ware collect data peripherally and make it available via a memory data pool to application programs in the VAX. Powerful operator access facilities are available in the Control Room.

## b) Berkeley Superhilac System.

This is a small, fast system using many compatible microprocessors and concentrating on the use of hardware to reduce system software demands. There is no mainframe computer and no operating system. A central data pool approach makes accelerator data available to many processes.

## c) Fermi National Accelerator Laboratory.

## 1) Linac System.

This system uses a network of microprocessors to collect and store data locally. The network permits any node to request any data in the system and performance is defined to permit a 15 Hz update of parameters. All parameters are collected and maintained at the remote locations but a dynamic subset of parameters is provided to operator consoles for further processing.

## 2) Main Ring System.

This is a very extensive and powerful system corresponding to the complexity of the operations requirements. High speed buses make the accelerator data available to consoles at the canonical 15 Hz data rate. Large control computers are used for development and coordination and to manage the network transactions. Each operator console is supported by a dedicated processor and display hardware. The console processor is compatible with the central processors providing cross compilers and utility functions. Additional operator stations can readily be added and only increase the data bus load since they are supported by their own computer and display.

#### d) Stanford Linear Collider System.

This is another large system using a high speed network to communicate between micros and a central VAX. The hardware interface is in CAMAC but most modules are SLAC designs. The operator COW/CALF consoles allow flexible user access to the data pool in the VAX and remote stations for debugging, etc.

### e) Los Alamos Meson Production Facility Upgrade.

This project was defined to replace a SEL 8400 system with a VAX. It provides some important lessons for the NSLS; the project was long, expensive and ultimately hindered by the effort to retain existing hardware. An important point is that the accelerator hardware interface became a serious limitation but was not significantly modified because of operational and other restrictions.

## 3. Workshop Conclusions and Plans for the NSLS Upgrade.

Several conclusions regarding desirable objectives of the NSLS upgrade were reached as a result of the presentations and discussions at the workshop. These include:

- a) The VAX is a very popular, successful and almost universal computer.

- b) Powerful networks are needed to support a distributed control system. Few systems now in operation use standard networks but these are increasingly available.

- c) A data pool of accelerator parameters is a very effective way to make data available to multiple applications processes.

Objectives considered desirable for the NSLS system are:

- d) Increased monitoring of hardware performance making on-line use of diagnostic tests. These might include monitoring for magnet shorts, excessive ripple in supplies, etc.

- e) Processing of data to real units, floating point parameters and complete data reduction in the front end processors. This would include signal averaging, fitting of data and calibration, conversions, etc.

- f) Correlation of parameters in a universal fashion independent of their source to allow sophisticated monitoring procedures to operate continually at a high rate.

- g) Creation of a data pool of converted and derived parameters accessible to multiple processors.

- h) The existing system must continue to operate during the upgrade period. While this is essential, it must not be allowed to constrain the hardware design. In this sense the upgrade is more in the nature of a replacement than a modification.

- i) Design of the system for high reliability and ability to withstand single point failures without significant degradation of performance.

#### 4. The System.

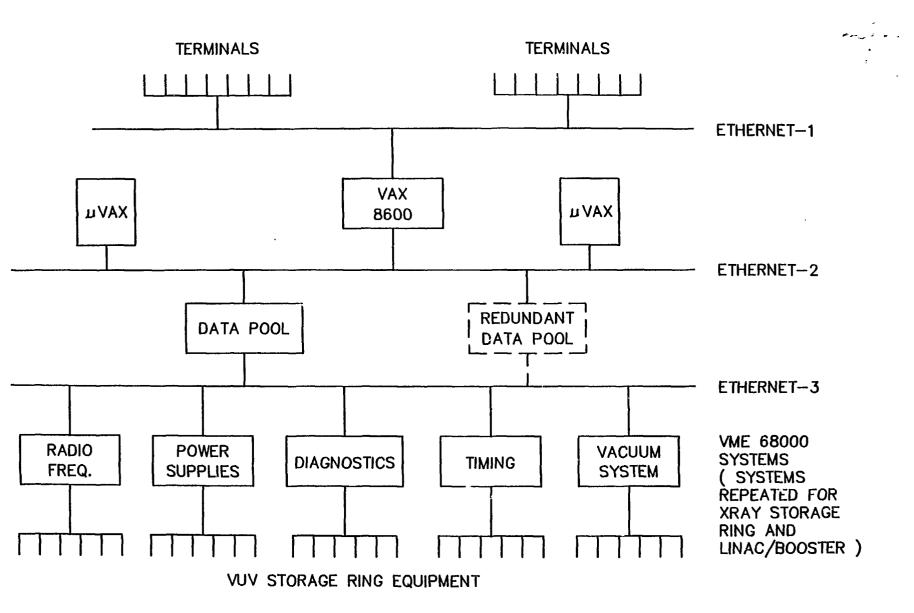

Figure 1 is a block diagram outline of the chosen system. Key functions adopted are: use of a central VAX computer, extensive use of ETHERNET links for communications, a universally accessible data pool outside any of the general purpose processors and powerful local systems to interface to the accelerator hardware.

DISCLAIMER

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of th-United States Government or any agency thereof.

## a) Central Computer.

We have selected a VAX 8600 for the central computer. We believe that this powerful processor is easily justified for a system with an expected life of over 10 years. We will use it as our principal managerial, development and utility facility but delegate all repetitive operations to more dedicated processors. While we greatly admire the facilities of a VAX cluster we are unable to fund such a purchase at this time and will await developments over the next few years to decide if an extension to the VAX facility is desirable.

## b) Workstations.

We propose to develop an operator workstation on a Micro Vax II.

Recognizing that this processor cannot perform the functions of a central facility, it is neverless code and operating system compatible with the VAX 8600 and likely to be the predecessor of even more powerful systems.

#### c) Communications.

Ethernet will be used at three or more levels in the system. The terminal communications will be implemented via a terminal server operating over Ethernet to the VAX. The VAX and operator workstations will communicate with the data pool via Ethernet. The coordinating microprocessors will report to the data pool over Ethernet. We have not yet defined the interface between the sub-system microprocessors and device dedicated microprocessors because of conflicts between "dumb" hardware needing only read/write operations and micro supported hardware justifying message transfer.

## d) Microprocessors.

The VME/68000 combination has been selected as the microprocessor system to be used to implement all but the VAX processors. This choice was guided by the wide acceptance of the hardware, the bus format, and the availability of powerful processors with large address space. These features permit one to have a large data pool, a high level language and fast floating point operations in the microprocessors.

## 5. System Elements.

#### a) Central Computer.

This will serve as the general purpose, code management, data base and development system for the control system. Modelling programs running in real-time or pseudo real-time to, for example, adjust the storage ring parameters in response to powering an undulator will be supported by this computer. Such models will also permit accelerator developments to be closely coupled to the accelerator hardware. Note that, in this implementation we will have no redundancy at this level but the accelerators can be operated without the VAX 8600 and software development activities can be supported by other VAX's at Brookhaven to some degree.

The VAX 8600 will perform the function of permanently saving a historical data record. This has become a very important function of the existing computers. There is constant demand for the recording of more parameters at a faster rate, and there is quick complaint from Operations when this function fails. The large number of beam lines requires changes in beam line status to be displayed and recorded for management purposes. We must also record beam current, vacuum status, accumulated ampere—hours, etc.

#### b) Data Pool.

This will consist of a large VME/68000 system with multiple ETHERNET driver modules. It will provide a wide bandwidth access to the data pool from operator workstations and VAX users. All readings and commands will be transmitted via this unit which will also provide access protection and a transaction record or audit trail of control procedures and error logging. All data in the data pool will be available at the level of physical units and in floating point format for analog parameters. A provision for raw data in the data pool is possible but we are inclined to restrict the data to its reduced form. Most dynamic parameters will be updated at a rate of 10 per second. Low rates may be used for slowly varying parameters and a buffer scheme for data acquired on user requests will be developed. A redundant system will be required for this unit which will probably operate passively until needed actively to bypass a failure of the primary system.

## c) Subsystem Microprocessors.

These will be VME/68000 systems interfaced by Ethernet. They will be coded in FORTRAN using a cross compiler on the VAX which can produce VAX or 68000 code. Extensive hardware monitoring will be provided and as much data reduction as is possible within the given system will be performed at this level. Floating point processing will be performed here to facilitate high resolution devices, variable gain, etc. and to allow fitting and correlation algorithms to be implemented. Data base parameters will be required for much of this activity so that the relevant data base entries, device names, etc. will be retained in the sub-system microprocessors. Some decisions on the interface to the physical hardware of the acelerator remain to be made. There is a desire for a serial system but some questions about utilizing intelligence in device hardware have yet to be answered. It is intended to limit the number of sub-systems for the accelerators but with duplication for each storage ring and probably the Booster/Linac system. This is necessary to provide access for maintenance and modification.

## d) Device Structures.

We propose to define devices at a low level in the subsystem microprocessors with device types defined as analog setpoint, analog readback, bit input, bit output, bit field in, bit field out, etc. Derived parameters will be named appropriate to their function.

#### e) User Access.

The Control Room operators will access the system via micro VAX's. We expect to provide extensive graphics, windows and interactive devices for this purpose. Software of this type is now becoming available on the micro Vax workstations. Other user access will be via IBM personal computers interfaced to the VAX 8600 where equivalent code will be run. With care much of the micro VAX and VAX 8600 code can be shared to promote efficiency and compatibility. For real-time debugging of systems and other special purposes a processor using BASIC or some other interpreter may be connected to a sub-system microprocessor and operate locally.

## f) Communication Link Usage.

As is evident in Figure 1, there are three Ethernets in the system. While these could be a single cable, we wish to separate them logically and physically to promote discipline and conserve bandwidth. Thus Ethernet 1 is used for VAX terminal access, Ethernet 2 is used for dynamically varying data pool access from the workstations. The data rate on this link is a function of workstation update rate and display complexity. We estimate that with update rates of 3 to 10 per second and typical data block sizes the peak rate will be about 300 kbits/s. Ethernet 3 is used for repetitive data pool update and access for repetitive displays. This link will be determinate and can be heavily loaded. We anticipate a data rate of 1 Mbit/s. We could reduce this rate by "report-on-change" strategies in some of the microprocessors. Repetitive displays will be implemented on the subsystem microprocessors or in dedicated processors connected to Ethernet 3. Arcnet may be considered as an alternative to the Ethernet 3 network for the micro-to-micro interface.

#### 6. Status.

Orders have been placed for the VAX and some initial 68000 systems for development. Operating systems for the 68000 are being reviewed. The first Ethernet system has been installed. A detailed software schedule is being prepared. The implementation is scheduled to take 2 years. The hardware, communications and system software should be in place by the first quarter of 1987. The application software should be converted to the VAX during the following year.

#### Acknowledgment.

We would like to thank the accelerator control community for their advice, help and criticism at the NSLS workshop and elsewhere which have been invaluable in developing the ideas for this system.

Research carried out under the auspices of the U.S.D.O.E.

#### References.

- [1] K. Batchelor, B.B. Culwick, J. Goldstick, J. Sheehan and J. Smith, IEEE Trans. on Nucl. Sci. 26, 3387 (1979).

- [2] E. Bozoki, B.B. Culwick and J.D. Smith, IEEE Trans. on Nucl. Sci. 28, 2183 (1981).

FIG. 1- BLOCK DIAGRAM OF THE NSLS SYSTEM UPGRADE