# SOME TRANSISTOR SMALL SIGNAL EQUIVALENT CIRCUIT CALCULATIONS

ARPAD BARNA

MARCH 28, 1961

SYNCHROTRON LABORATORY

CALIFORNIA INSTITUTE OF TECHNOLOGY

**PASADENA**

#### CALIFORNIA INSTITUTE OF TECHNOLOGY

Synchrotron Laboratory Pasadena, California

SOME TRANSISTOR SMALL SIGNAL EQUIVALENT CIRCUIT CALCULATIONS

Arpad Barna March 28, 1961

Supported in part by the U.S. Atomic Energy Commission Contract No. AT(11-1)-68

## Contents

|     | Introduction                             | p. 2  |

|-----|------------------------------------------|-------|

| I   | Basic Equivalent Circuits                | p. 2  |

| II  | Some Typical Transistor Parameter Values | p. 2  |

| III | Grounded Emitter Configuration           | p. 5  |

| IV  | Grounded Base Configuration              | p. 5  |

| V   | Grounded Collector Configuration         | p. 12 |

| VI  | Emitter Degenerated Configuration        | p. 26 |

#### Introduction

Transient responses, input and output impedances have been derived for the use of the circuit designer. A hybrid equivalent circuit was assumed to be correct and has been used as the basis of the derived relationships.

Grounded emitter, grounded base, grounded collector and emitter degenerated configurations are discussed.

#### I Basic Equivalent Circuits

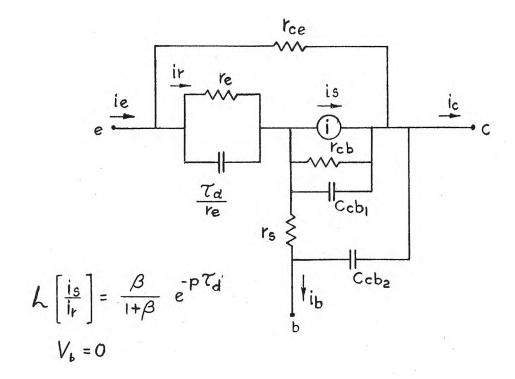

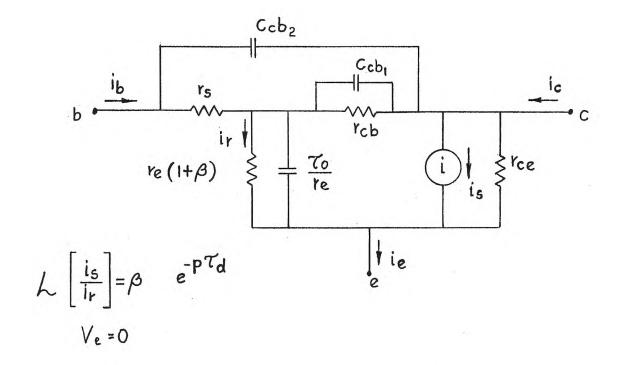

A small signal emitter input transistor equivalent circuit for diffused base transistors, for times larger than  $\tau_0$  is shown in Fig. 1.1. The corresponding base input circuit is in Fig. 1.2.

In both circuits

$$r_e = \frac{kT}{qI_{eDC}} \approx \frac{25 \text{ mv}}{I_{eDC}}$$

and

$$\tau_o = \tau_\alpha + \tau_d$$

.

#### II Some Typical Transistor Parameter Values

| Transistor | $\tau_{\alpha}$ nsec | T<br>o<br>nsec | rs<br>ohms | β <sub>o</sub> | Ccb*<br>pF | at Vcb<br>Volts |

|------------|----------------------|----------------|------------|----------------|------------|-----------------|

| 2N 1500    | 0.25                 | 0.5            | 5          | 75             | 2.5        | 3               |

| 2N 1742    |                      | 0.2            | 8          | 50             | 1.5        | 12              |

$$^*C_{cb} = Ccb_1 + C_{cb2}$$

Theoretical value for Ccb:

$$C_{cb} \cong C_{stray} + \frac{k_1}{v^n}$$

where  $n = \frac{1}{3}$  to  $\frac{1}{2}$

FIGURE 1.1

Emitter input small signal equivalent circuit.

FIGURE 1.2

Base input small signal equivalent circuit.

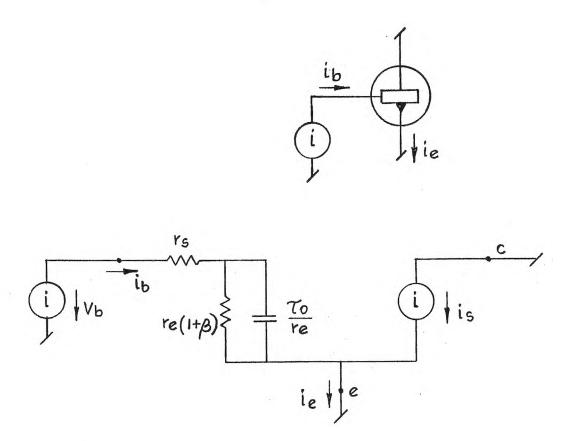

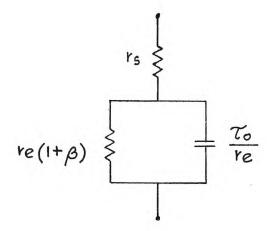

#### III Grounded Emitter Configuration (Fig. 3.1)

$$L\left[\frac{i_c}{i_b}\right] = \frac{\beta}{1 + p\tau_o \beta} e^{-p\tau_d}$$

and for the input impedance (Fig. 3.2):

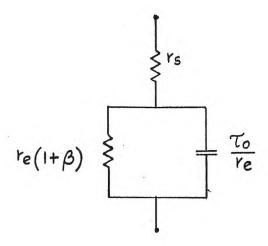

$$L\left[\frac{V_{b}}{i_{b}}\right] = r_{s} + \frac{r_{e}(1+\beta)}{1+p\tau_{o}(\beta+1)} \cong r_{s} + \frac{\beta_{re}}{1+p\tau_{o}\beta} \quad (\text{for } \beta \gg 1)$$

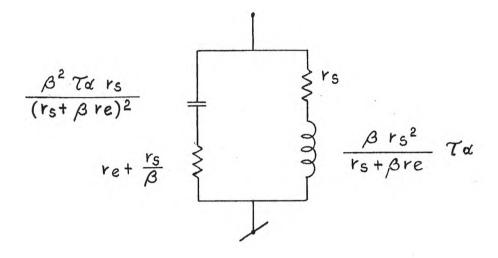

## IV Grounded Base Configuration (Fig. 4.1.1)

#### 4.1 Current transfer and input impedance.

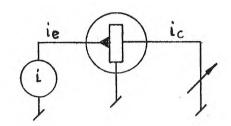

Conditions: Current source input; short circuited output;  ${\rm C_{cb}} = 0; \; {\rm r_{ce}} >\!\!\!> {\rm r_{s}} + {\rm r_{e}}. \; \; {\rm Using \; the \; emitter \; input \; circuit, \; we \; get \; for \; the \; current \; transfer: }$

$$L\left[\frac{i_c}{i_e}\right] = \frac{\beta}{1+\beta} \frac{1}{1+pr_\alpha} e^{-pr_d}$$

and the input impedance of Fig. 4.1.2.

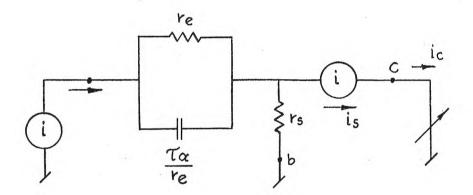

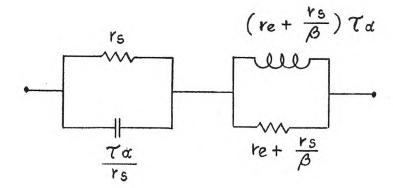

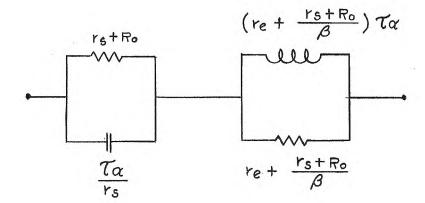

4.2 Grounded base configuration with resistive input impedance.

If we load the input with a network of Fig. 4.2.1, the resulting impedance will have a resistive value of

$$\frac{r_{\rm s}(r_{\rm e}+r_{\rm s}/\beta)}{r_{\rm s}(1+\frac{1}{\beta})+r_{\rm e}} \qquad ({\rm for}\ r_{\rm e}\gg r_{\rm s}/\beta) \quad . \label{eq:rs}$$

Or if we insert a series network of Fig. 4.2.2, the resulting resistance will be

$$Z = r_e + r_s \frac{1+\beta}{\beta} \cong r_e + r_s$$

(for  $\beta \gg 1$ ).

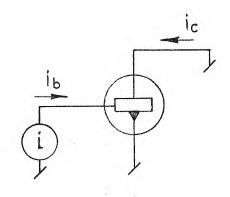

FIGURE 3.1

Grounded emitter stage.

FIGURE 3.2

Input impedance of a grounded emitter stage.

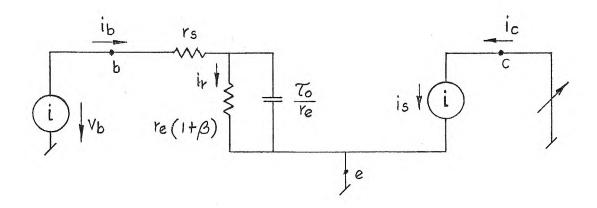

FIGURE 4.1.1

Grounded base stage.

FIGURE 4.1.2

Input impedance of a grounded base stage.

FIGURE 4.2.1

Parallel compensating network for the input of a grounded base stage.

FIGURE 4.2.2

Series compensating network for the input of a grounded base stage.

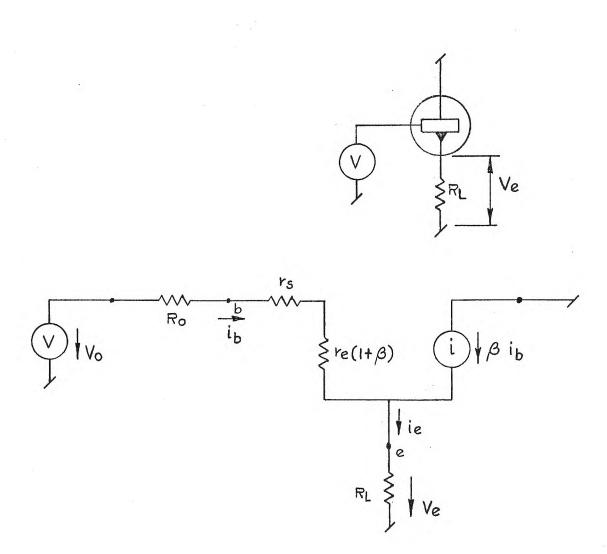

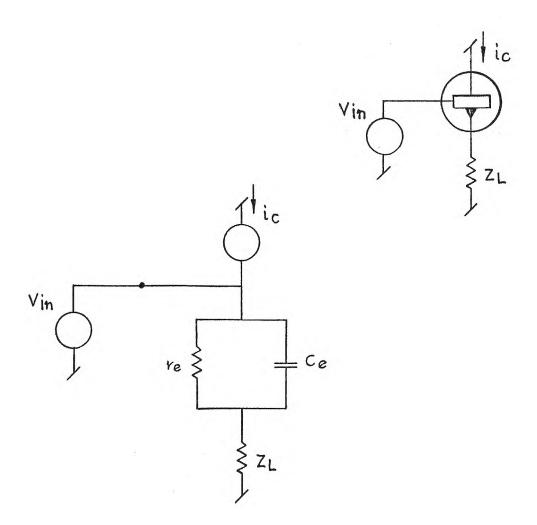

#### V Grounded Collector Configuration (Fig. 5.1.1)

#### 5.1 Current transfer and input impedance.

Conditions: Current source input; short circuited output;  $^{\text{C}}_{\text{cb2}} = 0 \; ; \; ^{\text{C}}_{\text{cb1}} \ll \tau_{\text{o}}/\beta r_{\text{e}} \; ; \; r_{\text{cb}} \gg \beta r_{\text{e}} \; . \; \text{Using the base input circuit, we get for the current transfer:}$

$$L\left[\frac{i_{e}}{i_{b}}\right] = \frac{\beta}{1 + pr_{o}\beta} e^{-pr_{d}} + 1$$

and obtain the input impedance of Fig. 5.1.2.

#### 5.2 DC voltage transfer (Fig. 5.2.1).

Conditions:  $r_{cb} \gg \beta r_e$ ;  $r_{ce} \gg R_o$ ;  $t \gg \beta \tau_o$ . Using the base input circuits, we get for the voltage transfer:

$$\frac{V_{e}}{V_{o}} = \frac{1}{1 + \frac{r_{e} + \frac{R_{o} + r_{s}}{1 + \beta}}{R_{T_{e}}}}$$

and for the input resistance (Fig. 5.2.2):

$$R_{in} = R_o + r_s + (r_e + R_L)(1 + \beta) \cong R_o + r_s + \beta(r_e + R_L)$$

(for  $\beta \gg 1$ )

$$R_{\text{out}} = \frac{-V_{\text{o}}}{i_{\text{e}}} = r_{\text{e}} + \frac{R_{\text{o}} + r_{\text{s}}}{1 + \beta} \cong r_{\text{e}} + \frac{R_{\text{o}} + r_{\text{s}}}{\beta} \qquad \text{(for } \beta \gg 1\text{)}$$

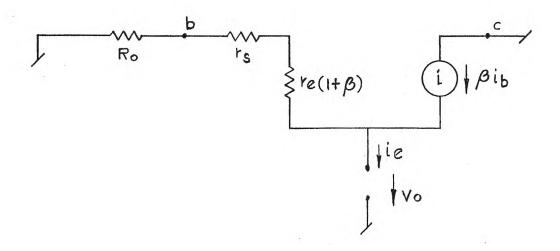

Thus, we obtain the DC equivalent circuit of Fig. 5.2.3.

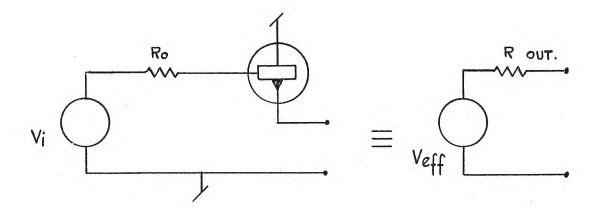

## 5.3 Transient response for step voltage input (Fig. 5.3.1).

Conditions: Resistive source impedance (R<sub>o</sub>); parallel RC load;  $C_{\rm cb}$  = 0;  $r_{\rm ce} \gg R_{\rm o}$ ;  $\beta \gg 1$ . Using the emitter input circuit, we get:

$$L\left[\frac{v_{L}}{v_{in}}\right] = \frac{1 + p \tau_{\alpha}}{\frac{R'_{o}}{R_{L}} (p \tau_{o})^{2} + \frac{r_{e}}{R_{L}} (1 + \frac{k}{c}) p \tau_{o} + \frac{r_{e}^{2}}{R_{O} R_{L} c}}$$

where

$$R_{o}' = R_{o} + r_{s}$$

$$1 + \frac{R_{L}}{R_{o}'} \frac{\tau_{\alpha}}{\tau_{o}}$$

$$1 + \frac{R_{L}}{R_{e}} + \frac{R_{o}'}{\beta r_{e}}$$

$$c = \frac{c_{L} r_{e}^{2}}{r_{o} R_{o}'} \frac{1}{1 + \frac{r_{e} + R_{o}'/\beta}{R_{L}}}$$

The response for a step voltage input will be free of ringing if the roots of the denominator are real:

$$(1+\frac{k}{c})^2 \ge \frac{4}{c}$$

or  $c^2 + c \left[2k - 4\right] + k^2 \ge 0$ .

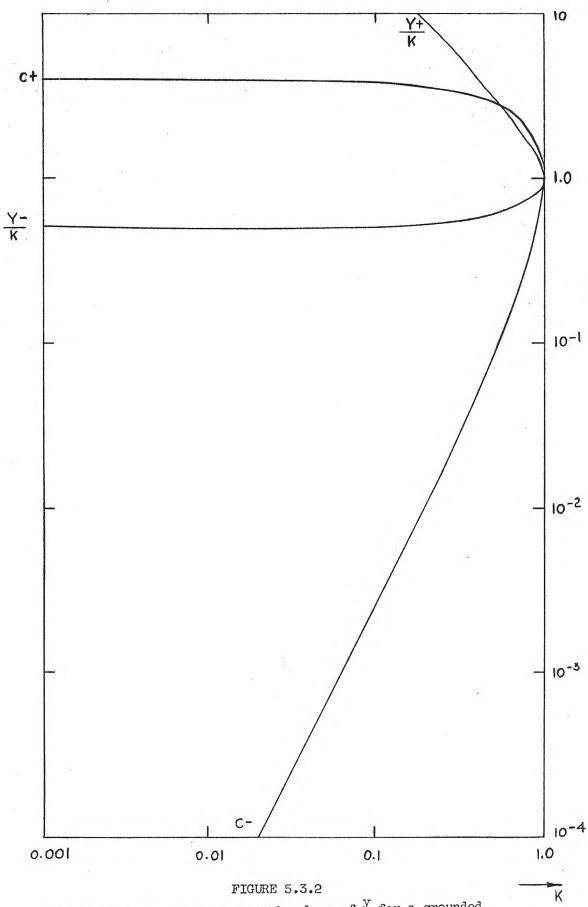

This represents a parabola, where  $C_{-} < C < C_{+}$  leads to ringing. These critical values of C,  $C_{+} = 2 - k + 2 \sqrt{1 - k}$ , are plotted on Fig. 5.3.2. Using either of these critical values, the response:

$$L\left[\frac{V_L}{V_{in}}\right] = \text{const.} \frac{1}{1 + pr^*}$$

where

$$\tau^* = \tau_0 \frac{\frac{R_0'}{r_e}}{\frac{2}{1 + \frac{k}{c}}} = \tau_0 \frac{\frac{R_0'}{r_e}}{\frac{r_e}{r_e}} y = \frac{y}{k} \frac{\frac{1 + \frac{R_L}{R_0'}}{\frac{R_0'}{r_e} + \frac{R_L}{R_0'}}}{\frac{R_0'}{r_e} + \frac{1}{\beta}}$$

FIGURE 5.1.1

Grounded collector stage.

FIGURE 5.1.2

Input impedance of a grounded collector stage.

FIGURE 5.2.1

DC conditions for a grounded collector stage.

## FIGURE 5.2.2

DC input impedance of a grounded collector stage.

FIGURE 5.2.3

DC equivalent circuit of a grounded collector stage.

FIGURE 5.3.1

Grounded collector stage.

$$\beta \gg \frac{R_o'}{r_e + R_T}$$

$$\frac{\tau^*}{\tau_o} \cong \frac{\frac{R_o' + R_L \frac{\tau_\alpha}{\tau}}{r_o}}{\frac{y}{k}}$$

Values of  $\frac{y}{k}$  as functions of k, y, corresponding to c = c, y to c = c are plotted on Fig. 5.3.2. Furthermore,

$$C_{L} \pm = (C \pm) \frac{\tau_{o} R_{o}'}{r_{e}^{2}} \left(1 + \frac{R_{o}' + \beta_{re}}{\beta R_{L}}\right)$$

for  $k \ll 1$

$$c_{2} \cong \frac{k^{2}}{4}$$

$$\frac{Y}{k} \cong 0.5$$

For  $k \ge 1$  the response is always free of ringing.

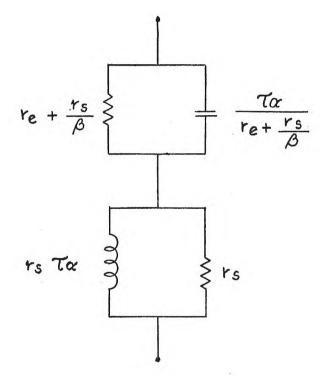

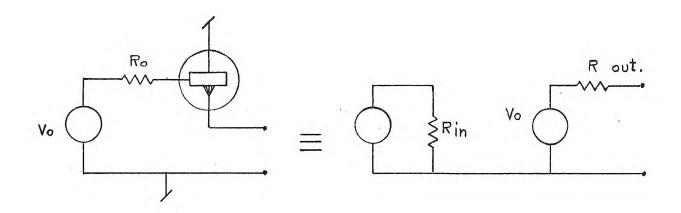

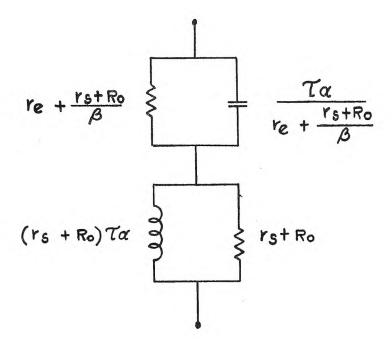

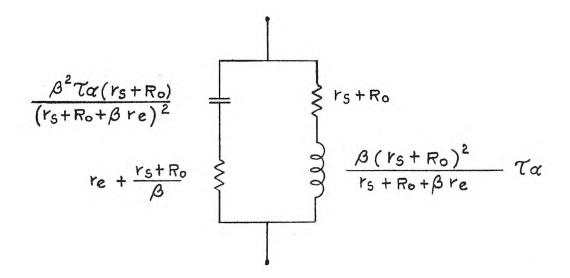

## 5.4 Grounded collector configuration with resistive output impedance.

Conditions:  $C_{cb} = 0$ ;  $r_{ce} >> R_{o}$ ; resistive source impedance (Fig. 5.4.1). The output impedance thus is as in Fig. 5.4.2.

If we load the output with a network of Fig. 5.4.3, the resulting impedance will be resistive. Or if we insert a series network of Fig. 5.4.2, the output impedance will be resistive:

$$Z = r_e + (r_s + R_o) \left(\frac{1+\beta}{\beta}\right) \cong r_e + r_s + R_o \quad \text{(for } \beta \gg 1\text{)}$$

Critical load capacitances and values of  $\frac{y}{k}$  for a grounded collector stage.

## FIGURE 5.4.1

Equivalent circuit of a grounded collector stage with resistive output impedance.

FIGURE 5.4.2

Output impedance of a grounded collector stage.

FIGURE 5.4.3

Parallel compensating network for the input of a grounded collector stage.

FIGURE 5.4.4

Series compensating network for the input of a grounded collector stage.

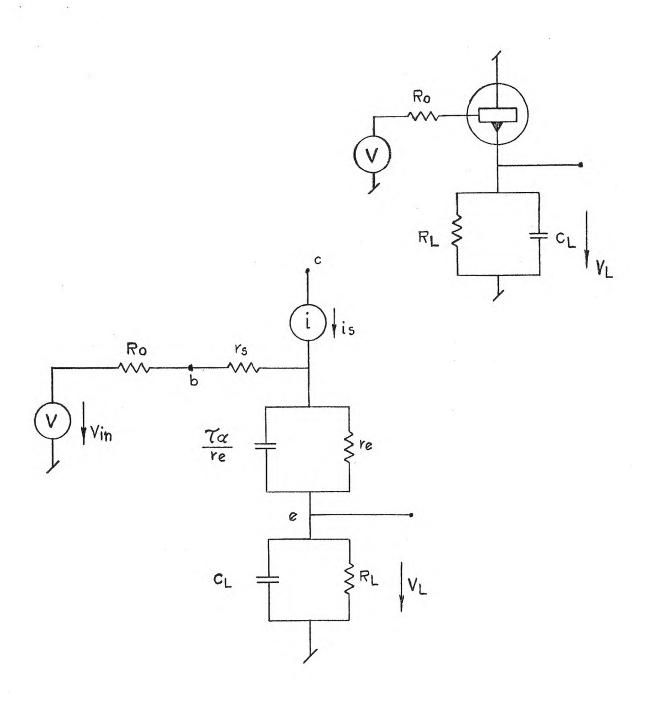

#### VI Emitter Degenerated Configuration (Fig. 6.1)

Conditions: Voltage source input, short circuited output,  ${\bf r_s} = {\bf 0}$ . Using the emitter input equivalent circuit, we get for the transconductance:

$$L\left(\frac{ic}{V_{in}}\right) = \frac{\alpha}{r_{e} + R_{L}} e^{-p\tau_{o}}$$

and obtain the input impedance of Fig. 6.2.

FIGURE 6.1

Emitter degenerated stage.

$$(\beta+1)(r_e+R_L)$$

$=$   $\frac{\tau_o}{r_e+R_L}$

#### FIGURE 6.2

Input impedance of a critically damped emitter degenerated stage.

#### References

- R. D. Middlebrook: An Introduction to Junction Transistor Theory.

- W. Shockley: Electrons and Holes in Semiconductors.

- J. G. Linvill: Lumped Models of Transistors and Diodes (PIRE June 1958).

- C. G. Thornton, J. B. Angell: Technology of Micro-alloy Diffused Transistors (PIRE June 1958).

Publications on Philco MADT Transistors.