## Electron-beam-induced current measurements in silicon-on-insulator films prepared by zone-melting recrystallization

E. W. Maby, a) H. A. Atwater, a) and A. L. Keiglerb)

Massachusetts Institute of Technology, Cambridge, Massachusetts 02139

N. M. Johnson

Xerox Palo Alto Research Center, Palo Alto, California 94304

(Received 5 May 1983; accepted for publication 10 June 1983)

Enhanced diffusion of arsenic along grain boundaries and subboundaries in zone-recrystallized silicon-on-insulator films has been measured by electron-beam-induced current analysis of lateral pn junctions fabricated in the films. A four-hour diffusion at 1100 °C resulted in protrusions of arsenic at the junction edges which measured approximately 3–5  $\mu$ m along the grain boundaries and only 1–2  $\mu$ m along the subboundaries. The results suggest that under more ordinary thermal processing conditions, field-effect transistors with channel lengths greater than about 1.5  $\mu$ m can be randomly positioned with respect to the more numerous subboundaries, but grain boundaries should be avoided.

PACS numbers: 73.40.Lq, 61.70.Ng, 66.30.Jt, 81.10.-h

Zone-melting recrystallization by means of a movablestrip heat source can produce continuous device-worthy silicon films over thermally oxidized silicon when a suitable encapsulation layer is present to prevent silicon agglomeration. 1-5 The films consist of large grains, typically 1 mm wide and extending the length of the zone scan, which are seeded from a transition region where solidification begins.<sup>2,5</sup> Individual grains contain subboundaries, typically 25  $\mu$ m apart, which are generally parallel to one another and to the direction of motion of the molten zone. The subboundaries consist of linear arrays of dislocations with angular deviations of the order of one degree or less; they originate at the interior corner of the solid-liquid interface during recrystallization.<sup>5,6</sup> Large-angle grain boundaries can be eliminated by seeding from the silicon substrate beneath the silicon dioxide layer<sup>7,8</sup> or by appropriate patterning of the silicon film prior to recrystallization. The subboundaries are more difficult to control; however, entrainment techniques which force the subboundaries to be positioned at specific regular intervals have been reported.6

In a previous letter, 10 the electrical characteristics of both grain boundaries and subboundaries were examined by fabricating large (92 $\times$ 375  $\mu$ m), phosphorus-doped (1 $\times$ 10<sup>17</sup> cm<sup>-3</sup>) resistors which were either parallel or perpendicular to the line defects. One or more transversely oriented grain boundaries provided significant ( $\sim 15\%$ ) bulk conductivity degradation; whereas, an average of 20 subboundaries provided only marginal (~0.15%) bulk conductivity degradation. The surface conductivity at the interface between the silicon film which contained the resistors and the silicon dioxide below could be modulated by using the silicon substrate as a gate electrode. Transversely oriented grain boundaries induced peculiar "kinks" in the turn-on characteristics of these "upside-down" depletion-mode field-effect transistors. The influence of subboundaries on surface conductivity could not be detected. These results suggest that

grain boundaries must be avoided when considering the placement of field-effect transistors on zone-recrystallized silicon-on-insulator films and that the degradation of electrical properties due to subboundaries can be ignored.

As the dimensions of field-effect transistors fabricated on zone-recrystallized silicon-on-insulator films are reduced, another potential problem arises, i.e., the enhanced diffusion of dopant impurities during high-temperature processing along line defects which form a connective path between source and drain. This phenomenon shortens the effective channel length of the transistor and ultimately leads to an abrupt increase in subthreshold leakage current. Enhanced diffusion of arsenic along grain boundaries in laser-recrystallized silicon-on-insulator films was shown to be significant when channel lengths are less than 3  $\mu$ m, given a source-drain anneal at 900 °C for 90 min. <sup>11</sup>

In an earlier study,  $^{12}$  enhanced diffusion of arsenic along grain boundaries in the vicinity of lateral pn junctions fabricated in laser-recrystallized silicon films was measured by electron-beam-induced current (EBIC) analysis, and the results were compared with scanning-electron-beam voltage-induced contrast as a check for measurement consistency. A five-hour arsenic diffusion at  $1000\,^{\circ}\text{C}$  resulted in protrusions of arsenic at the junction edges extending up to  $5\,\mu\text{m}$  along the grain boundaries. The different lengths of the protrusions suggested significant variations in the microstructures or diffusivities of the grain boundaries.

This letter presents the results of EBIC analysis of lateral pn junctions fabricated in zone-recrystallized siliconon-insulator films. In recognition of the electrical and crystallographic differences between grain boundaries and subboundaries, particular effort has been made to compare the enhanced diffusion along the two types of line defect. Earlier work suggested a difference in diffusion characteristics, <sup>13</sup> but the measurements were by a less accurate procedure in which the arsenic-rich regions of the lateral pn junctions were preferentially etched. If minimal diffusion along subboundaries could be demonstrated, it would further justify the random placement of devices with respect to the

482

a) Department of Electrical Engineering and Computer Science.

b) Department of Materials Science and Engineering.

subboundaries, thereby simplifying the processing requirements associated with zone-recrystallized silicon-on-insulator films.

Prior to recrystallization, samples were prepared by oxidizing (100) n-type silicon wafers at 1100 °C to obtain a silicon dioxide thickness of 0.5  $\mu$ m. The thermal oxide was sequentially coated with a 0.5-\mu m-thick layer of low pressure chemical vapor deposition (LPCVD) polycrystalline silicon, a 2.0-\mum-thick layer of CVD silicon dioxide, and a  $0.03-\mu m$ -thick layer of sputtered silicon nitride. The details of the zone-melting recrystallization procedure have been reported elsewhere. 1-5 Briefly, the sample was placed within an argon ambient on a graphite strip which was resistively heated to 1000 °C. A movable upper strip, approximately 1 mm above the sample and 1 mm wide, was resistively heated until the polycrystalline silicon film melted, and the molten zone was moved across the sample at a speed of approximately 1 mm/s. After recrystallization, the silicon dioxide and silicon nitride encapsulation layers were removed in concentrated hydrofluoric acid. The silicon film was implanted with a fluence of  $2 \times 10^{12}$  cm<sup>-2</sup> boron at 70 keV. The boron was uniformly redistributed throughout the silicon film at a later point in the process sequence to yield a concentration of  $4 \times 10^{16}$  cm<sup>-3</sup>.

In order to distinguish the subboundaries from the grain boundaries, the films were decorated by a regular matrix of anisotropically etched pits. <sup>14</sup> These were prepared by depositing a 0.4- $\mu$ m-thick layer of CVD silicon dioxide over the silicon film and then etching 5- $\mu$ m-diam holes on 50- $\mu$ m center spacing. The exposed silicon was etched in a potassium hydroxide solution until square pits revealed the local crystallographic orientations throughout the film. As in other experiments, <sup>1-5</sup> the texture of the film was (100).

The fabrication of lateral pn diodes began with the opening of large (up to  $2 \times 2$  mm) holes in the silicon dioxide which had been used to define the matrix of etch pits. The holes defined the diode emitter  $(n^+)$  regions and were implanted with a fluence of  $1 \times 10^{15}$  cm<sup>-2</sup> arsenic at 150 keV. The implant was annealed at 1100 °C for 10 min in dry oxygen to form a thin silicon dioxide cap and then for 4 h in dry nitrogen to exacerbate the degree of enhanced diffusion which was expected along the grain boundaries. The silicon dioxide over the diode emitter regions was removed following the anneal. Aluminum was deposited over the sample and then defined to form contact pads which were slightly recessed from the junction edges. The fabrication process concluded by etching the silicon dioxide which remained over the silicon film.

After processing, the samples were mounted on headers and aluminum wires were bonded to the diode  $n^+$  contact pads. There was no direct electrical contact available to the diode p regions (field); the diodes were connected back-to-back in pairs without an applied bias voltage. A JSM-50 (Japanese Electron Optics Limited) scanning electron microscope was used for the EBIC analysis. With a 5-keV electron beam, the EBIC resolution was presumed to be consistent with that established in Ref. 12, approximately 0.5  $\mu$ m.

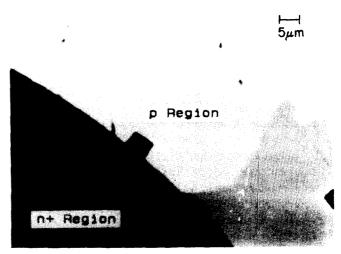

Many grain boundaries were located near the transition region of the zone-recrystallized film. A typical EBIC image

FIG. 1. EBIC image in the vicinity of a lateral pn junction which is intersected by grain boundaries. The large dark square which extends from the diode  $n^+$  region is an anisotropically etched pit used to determine grain orientations in the recrystallized silicon film. A second dark square at the right indicates that a grain boundary is located between the two squares, and the misorientation of the squares indicates that the angle of the grain boundary is approximately 20°. Note the large protrusions where the grain boundaries intersect the junction edge.

from this region is shown in Fig. 1. The arsenic protrusions extend approximately  $3-5 \mu m$  from the edge of the lateral pn junction. A protrusion length is assumed to be roughly equal to a diffusion length  $(Dt)^{1/2}$ , where D is the coefficient of line

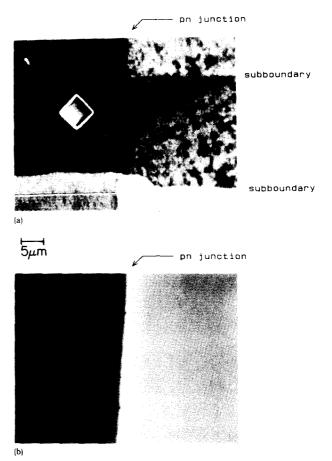

FIG. 2. (a) Secondary electron image in the vicintity of a lateral pn junction which is intersected by subboundaries. The distinct contrast is due to preferential electron channeling. (b) Corresponding EBIC image. Note the small protrusions along the subboundaries.

defect diffusion and t is the diffusion time. From this relation, the coefficient for arsenic diffusion along a grain boundary at 1100 °C is about  $1 \times 10^{-11}$  cm<sup>2</sup>/s. The value which was estimated in Ref. 12 for the case of arsenic diffusion at 1000 °C was also about  $1 \times 10^{-11}$  cm<sup>2</sup>/s. If the enhanced diffusion which brings about the transistor failure mode of Ref. 11 is assumed to correspond to a diffusion length of 1.5  $\mu$ m for an arsenic diffusion time of 90 min at 900 °C, the estimated coefficient of grain boundary diffusion for this case is approximately  $4 \times 10^{-12}$  cm<sup>2</sup>/s. Since these particular estimates vary as the square of a diffusion length and yet are comparable to within a factor of 2, the degree of enhanced arsenic diffusion along grain boundaries appears to be weakly dependent upon temperature over the range of 900-1100 °C. This conclusion is not consistent with that of earlier work<sup>15</sup> in which the enhanced diffusion of arsenic along grain boundaries in laser-recrystallized silicon-on-insulator films suggested a thermal activation energy of about 2.3 eV.

The EBIC analysis in the vicinity of subboundaries suggests a lesser degree of enhanced arsenic diffusion. Figure 2(a) shows two subboundaries separating regions of distinctly different contrast. The contrast results from preferential electron channeling along certain crystalline orientations.<sup>5</sup> The corresponding EBIC image of Fig. 2(b) shows small protrusions at the subboundary locations which extend approximately 1  $\mu$ m beyond the lateral pn junction edge. The protrusion lengths were sometimes greater along other subboundaries within the sample, but in no case did a protrusion extend more than about  $2\mu m$ . For a nominal protrusion length of 1.5  $\mu$ m, the estimated coefficient of arsenic diffusion along subboundaries has the approximate value of  $1 \times 10^{-12}$  cm<sup>2</sup>/s, roughly one order of magnitude less than for the grain boundaries. Under more ordinary processing conditions, the subboundary diffusion length scales downward by a factor of 2 as the diffusion time is reduced to one hour, and some degree of scaling can be expected as the diffusion temperature is reduced. These results suggest that field-effect transistors can be randomly positioned with respect to the subboundaries provided that channel lengths are greater than about  $1.5 \, \mu m$ .

In the work at MIT, E. W. Maby was supported by the Defense Advanced Research Projects Agency, contract N0014-C-80-0622, and H. A. Atwater was supported by the Department of Energy, contract DE-AC02-80-ER13019.

- <sup>1</sup>E. W. Maby, M. W. Geis, Y. L. Le Coz, D. J. Silversmith, R. W. Mountain, and D. A. Antoniadis, IEEE Electron Device Lett. EDL-2, 241 (1981).

- <sup>2</sup>M. W. Geis, H. I. Smith, B-Y. Tsaur, J. C. C. Fan, E. W. Maby, and D. A. Antoniadis, Appl. Phys. Lett. 40, 158 (1982).

- <sup>3</sup>R. F. Pinizotto, H. W. Lam, and B. L. Vaandrager, Appl. Phys. Lett. 40, 388 (1982).

- <sup>4</sup>T. J. Stultz and J. F. Gibbons, Appl. Phys. Lett. 41, 186 (1982).

- <sup>5</sup>M. W. Geis, H. I. Smith, B-Y. Tsaur, J. C. C. Fan, D. J. Silversmith, and R. W. Mountain, J. Electrochem. Soc. 129, 2812 (1982).

- <sup>6</sup>M. W. Geis, H. I. Smith, D. J. Silversmith, R. W. Mountain, and C. V. Thompson, J. Electrochem. Soc. 130, 1178 (1983).

- <sup>7</sup>B-Y. Tsaur, J. C. C. Fan, M. W. Geis, D. J. Silversmith, and R. W. Mountain, Appl. Phys. Lett. 39, 561 (1981).

- <sup>8</sup>J. C. C. Fan, B-Y. Tsaur, R. L. Chapman, and M. W. Geis, Appl. Phys. Lett. 41, 186 (1982).

- <sup>o</sup>H. A. Atwater, H. I. Smith, and M. W. Geis, Appl. Phys. Lett. 41, 747 (1982).

- <sup>10</sup>E. W. Maby and D. A. Antoniadis, Appl. Phys. Lett. 40, 691 (1982).

- <sup>11</sup>K. K. Ng, G. K. Celler, E. I. Povilonis, R. C. Frye, H. J. Leamy, and S. M. Sze, IEEE Electron Device Lett. EDL-2, 316 (1981).

- <sup>12</sup>N. M. Johnson, D. K. Biegelsen, and M. D. Moyer, Appl. Phys. Lett. 38, 900 (1981).

- <sup>13</sup>H. W. Lam, R. F. Pinizzotto, S. D. S. Malhi, and B. L. Vaandrager, Appl. Phys. Lett. 41, 1083 (1982).

- <sup>14</sup>K. A. Bezjian, H. I. Smith, J. M. Carter, and M. W. Geis, J. J. Electro-chem. Soc. 129, 1848 (1982).

- <sup>15</sup>H. Baumgart, H. J. Leamy, L. E. Trimble, C. J. Doherty, and G. K. Celler, MRS Symposium on *Grain Boundaries in Semiconductors*, edited by H. J. Leamy, G. E. Pike, and C. H. Seager (North-Holland, New York, 1982), p. 311