Theses & Dissertations

http://open.bu.edu

Boston University Theses & Dissertations

#### 2017

# High performance communication on reconfigurable clusters

https://hdl.handle.net/2144/27045 Boston University

# BOSTON UNIVERSITY COLLEGE OF ENGINEERING

Dissertation

## HIGH PERFORMANCE COMMUNICATION ON RECONFIGURABLE CLUSTERS

by

## JIAYI SHENG

B.S., Fudan University, 2012

Submitted in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

2017

© 2017 by JIAYI SHENG All rights reserved

## Approved by

First Reader

Martin C. Herbordt, Ph.D. Professor of Electrical and Computer Engineering

Second Reader

Michel Kinsy, Ph.D. Assistant Professor of Electrical and Computer Engineering

Third Reader

Ayse K. Coskun, Ph.D. Associate Professor of Electrical and Computer Engineering

Fourth Reader

Adrian Caulfield, Ph.D. Principal Research Hardware Development Engineer Microsoft Research

Step after step the ladder is ascended.

George Herbert

#### Acknowledgments

First and foremost, I want to thank my advisor, Prof. Martin Herbordt. During our five-year collaboration, he has offered me limitless help on my research. I feel respected because he has understood every single detail in my projects. I feel motivated because he has helped me come up with numerous brilliant research ideas. I feel touched because he has been thoughtful to my personal life. I feel honored and proud to have him as my Ph.D. advisor in my life.

I also want to thank other members in my dissertation defense committee. Prof. Michel Kinsy has helped me describe technical part of my dissertation more clearly and precisely. Prof. Ayse Coskun has assisted me to organize the big picture of my dissertation. Dr. Adrian Caulfield not only has offered invaluable three-month guidance in summer 2016, but also has helped me address several technical issues in my dissertation.

I sincerely thank my collaborators at the University of Florida, Prof. Alan George, Prof. Herman Lam, and Dr. Abhijeet Lawande. Without their substantial work on Novo-G#, I would not have my dissertation. Especially, I want to thank Dr. Abhijeet Lawande. During the five years, he has provided me all sorts of help including emails, documentation, code sharing, and even remote control to allow me to reproduce his work on the BU side. His assistance is one of the fundamental factors in my dissertation.

I am grateful to my supervisors at MediaTek, Inc, Dr. Yuan Lin and Dr. Henry Cox. I feel fortunate to spend two fantastic summers with them. Dr. Henry Cox is considerate and kind. He could always motivate and thrill me even if I made mistakes. Dr. Yuan Lin is sharp and wise. He could steer me in the right directions and provide me better research ideas.

I would also like to appreciate other professors at Boston University that help me

grow and make progress. I thank Prof. Douglas Densmore, Prof. David Starobinski, and Prof. Richard West for their remarkable classes. I thank Prof. Roscoe Giles for his great advice when I was his teaching assistant.

I am also grateful to my current CAAD lab mates, Chen Yang, Qingqing Xiong, Ahmed Sanaulah, and Rushi Patel. They gave me plenty of research advice and collaboration. I also want to thank the alumni including Tiansheng Zhang, Hao Chen, Chao Chen, Jie Meng, Raphael Landaverde, Hansen Zhang, and Ben Humphries for their help and encouragement.

Finally, I want to thank my family for their unconditional and limitless support on my Ph.D. career. My dear maternal grandpa passed away in my Ph.D. fourth year. I did not have the chance to go back to see him. I hope my Ph.D. degree could make him smile in paradise.

The research that forms the basis of this dissertation has been partially funded by NSF grants #CNS-1405695 and #CCF-1618303/7960, and through a grant from Microsoft Research.

## HIGH PERFORMANCE COMMUNICATION ON RECONFIGURABLE CLUSTERS

### JIAYI SHENG

Boston University, College of Engineering, 2017

Major Professor: Martin C. Herbordt, PhD Professor of Electrical and Computer Engineering

#### ABSTRACT

High Performance Computing (HPC) has matured to where it is an essential third pillar, along with theory and experiment, in most domains of science and engineering. Communication latency is a key factor that is limiting the performance of HPC, but can be addressed by integrating communication into accelerators. This integration allows accelerators to communicate with each other without CPU interactions, and even bypassing the network stack. Field Programmable Gate Arrays (FPGAs) are the accelerators that currently best integrate communication with computation. The large number of Multi-gigabit Transceivers (MGTs) on most high-end FPGAs can provide high-bandwidth and low-latency inter-FPGA connections. Additionally, the reconfigurable FPGA fabric enables tight coupling between computation kernel and network interface.

Our thesis is that an application-aware communication infrastructure for a multi-FPGA system makes substantial progress in solving the HPC communication bottleneck. This dissertation aims to provide an application-aware solution for communication infrastructure for FPGA-centric clusters. Specifically, our solution demonstrates application-awareness across multiple levels in the network stack, including low-level link protocols, router microarchitectures, routing algorithms, and applications.

We start by investigating the low-level link protocol and the impact of its latency variance on performance. Our results demonstrate that, although some link jitter is always present, we can still assume near-synchronous communication on an FPGAcluster. This provides the necessary condition for statically-scheduled routing. We then propose two novel router microarchitectures for two different kinds of workloads: a wormhole Virtual Channel (VC)-based router for workloads with dynamic communication, and a statically-scheduled Virtual Output Queueing (VOQ)-based router for workloads with static communication. For the first (VC-based) router, we propose a framework that generates application-aware router configurations. Our results show that, by adding application-awareness into router configuration, the network performance of FPGA clusters can be substantially improved. For the second (VOQbased) router, we propose a novel offline collective routing algorithm. This shows a significant advantage over a state-of-the-art collective routing algorithm.

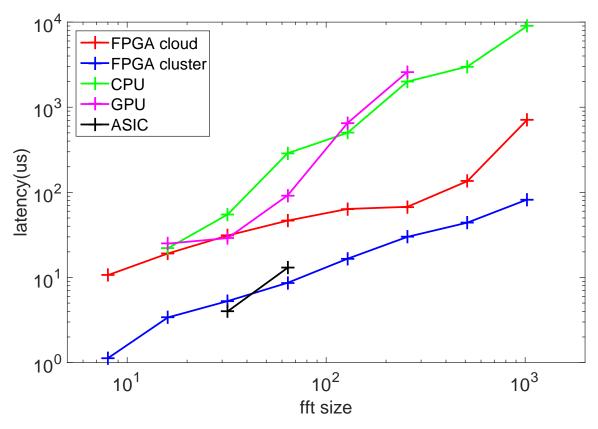

We apply our communication infrastructure to a critical strong-scaling HPC kernel, the 3D FFT. The experimental results demonstrate that the performance of our design is faster than that on CPUs and GPUs by at least one order of magnitude (achieving strong scaling for the target applications). Surprisingly, the FPGA cluster performance is similar to that of an ASIC-cluster. We also implement the 3D FFT on another multi-FPGA platform: the Microsoft Catapult II cloud. Its performance is also comparable or superior to CPU and GPU HPC clusters. The second application we investigate is Molecular Dynamics Simulation (MD). We model MD on both FPGA clouds and clusters. We find that combining processing and general communication in the same device leads to extremely promising performance and the prospect of MD simulations well into the us/day range with a commodity cloud.

## Contents

| 1        | Intr | roduct | ion                                                 | 1  |

|----------|------|--------|-----------------------------------------------------|----|

| <b>2</b> | Bac  | kgrou  | nd and Context                                      | 12 |

|          | 2.1  | Backg  | round                                               | 12 |

|          | 2.2  | Previo | ous Work Related to Contributions                   | 13 |

|          |      | 2.2.1  | Previous FPGA Clusters and Interconnection Networks | 14 |

|          |      | 2.2.2  | Previous Work on FPGA System/User Interfaces        | 19 |

|          |      | 2.2.3  | Previous Work of Router Architectures               | 20 |

|          |      | 2.2.4  | Previous Work of Routing Algorithms                 | 24 |

|          |      | 2.2.5  | Previous Work on Applications on FPGA Clusters      | 26 |

| 3        | Tar  | get Sy | stem Architecture and Implementation                | 29 |

|          | 3.1  | Design | n Choices of Multi-FPGA Systems                     | 29 |

|          | 3.2  | Backg  | round of Novo-G                                     | 31 |

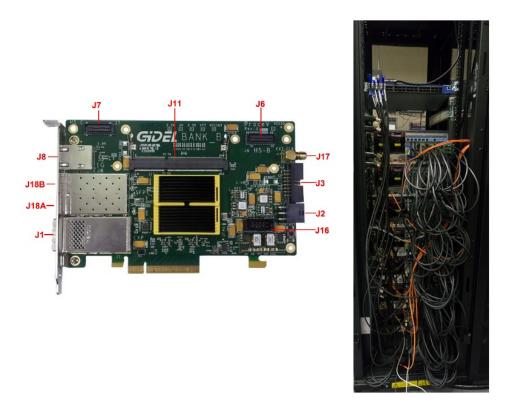

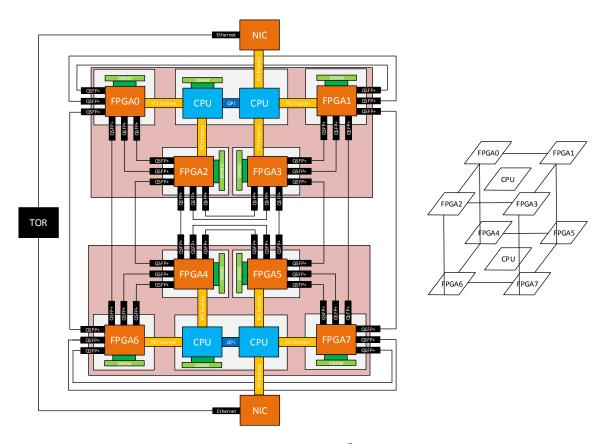

|          | 3.3  | Archit | Secture of Novo-G#                                  | 32 |

|          | 3.4  | Invest | igation of MGT Link Connections                     | 33 |

|          |      | 3.4.1  | Introduction of MGT link Protocol                   | 33 |

|          |      | 3.4.2  | Problem of Link Latency Variances and Clock Jitters | 35 |

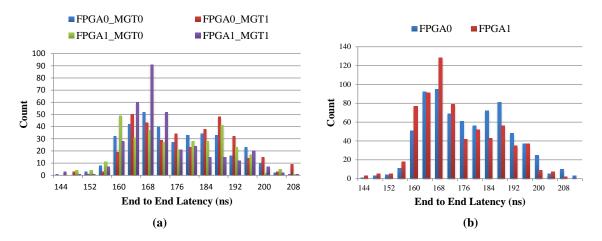

|          |      | 3.4.3  | Latency and Jitter Measurements                     | 37 |

|          |      | 3.4.4  | Variation of Communication Latencies                | 37 |

|          |      | 3.4.5  | Measurement of Clock Jitter                         | 40 |

|          |      | 3.4.6  | Case Study: 3D FFT                                  | 41 |

|          |      | 3.4.7  | Discussion                                          | 42 |

| 4 | Net  | work . | Architecture, Part 1: Router Design and Flow Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 44  |

|---|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | 4.1  | Backg  | round and Assumptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 44  |

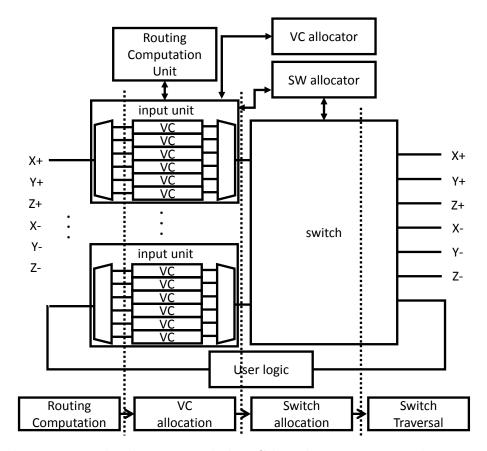

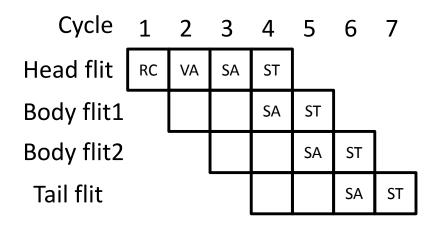

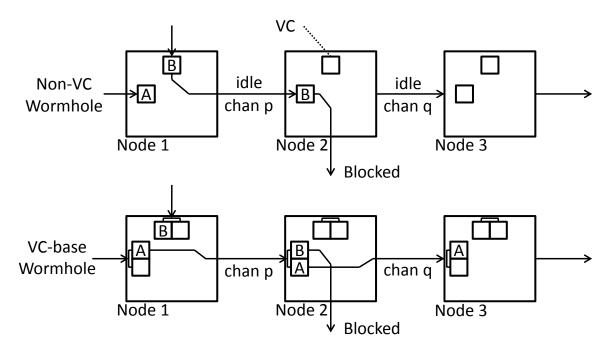

|   | 4.2  | Worm   | hole VC-based Router on FPGA Cluster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 46  |

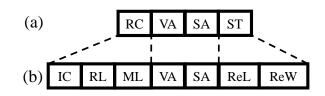

|   |      | 4.2.1  | Classic Wormhole VC-based Router Microarchitecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 47  |

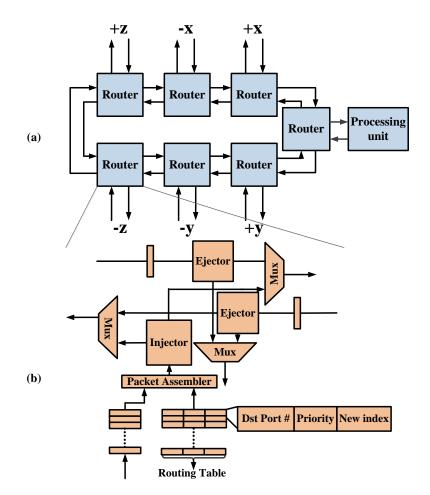

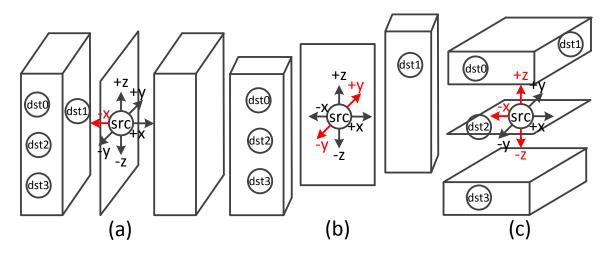

|   |      | 4.2.2  | Proposed VC-based Router on Novo-G# $\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdo$ | 49  |

|   | 4.3  | Propo  | sed Statically-scheduled Collective Acceleration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|   |      | Route  | r on Novo-G#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 62  |

|   |      | 4.3.1  | Table-based Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 62  |

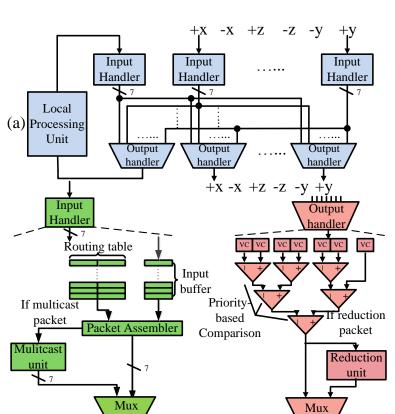

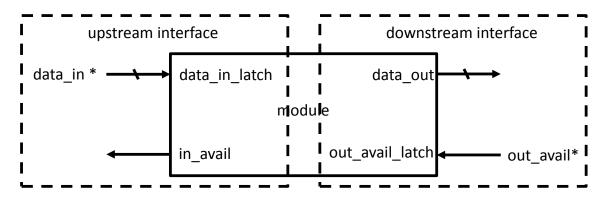

|   |      | 4.3.2  | Router Microarchitecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 64  |

| 5 |      |        | Design, Part 2: Routing Algorithms and Switch Arbitra-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|   | tion | Polic  | ies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 70  |

|   | 5.1  | Imple  | mented Routing Algorithms and Switch Arbitration Policies for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|   |      | Unica  | st workloads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 71  |

|   |      | 5.1.1  | Implemented Routing Algorithms in Proposed VC-based Router                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 71  |

|   |      | 5.1.2  | Implemented Switch Arbitration Policies in Proposed VC-based                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|   |      |        | Router                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 75  |

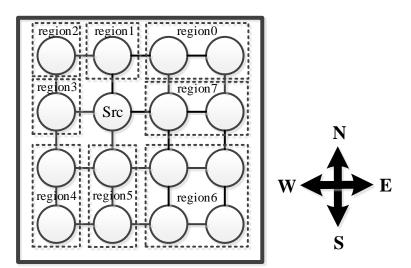

|   |      | 5.1.3  | Proposed Application-ware Framework to Generate Optimal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|   |      |        | Router Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 76  |

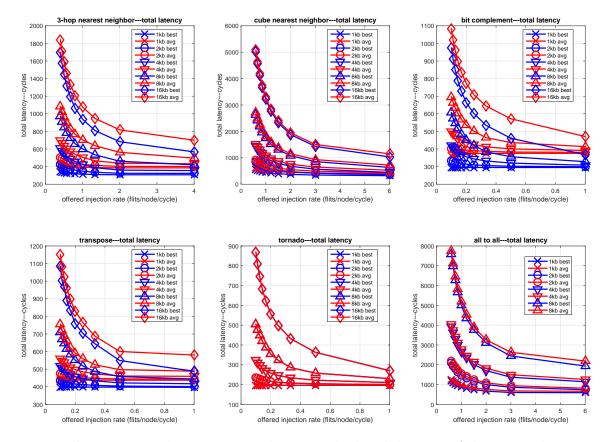

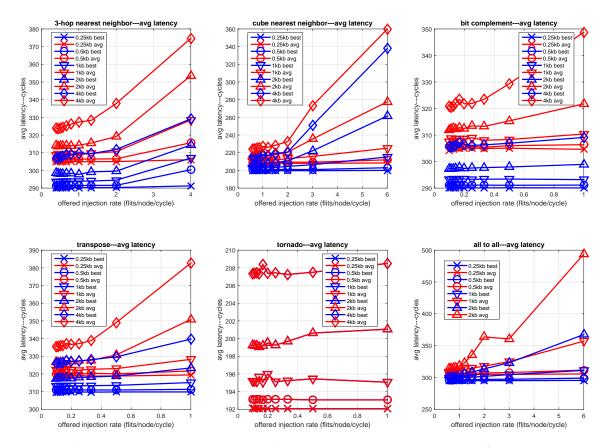

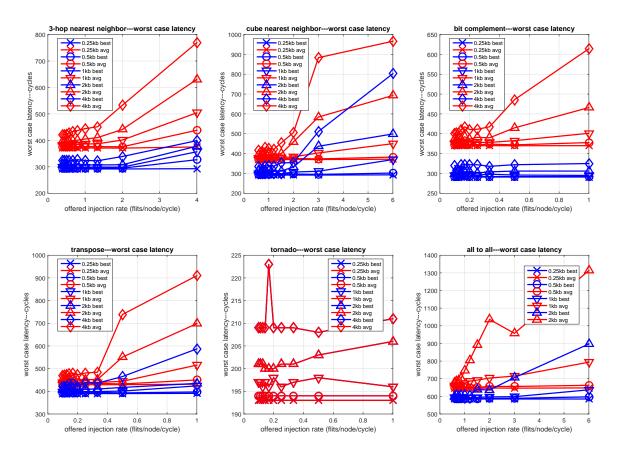

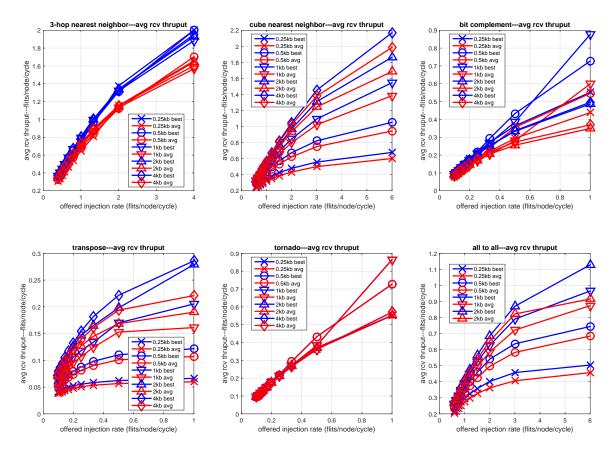

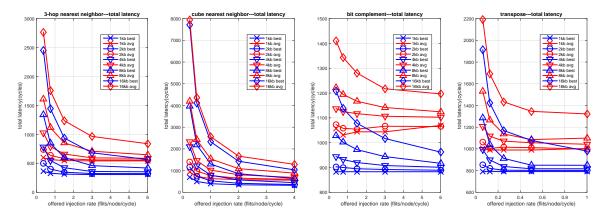

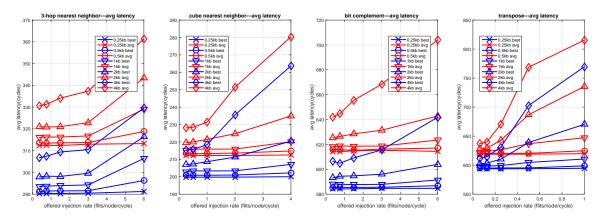

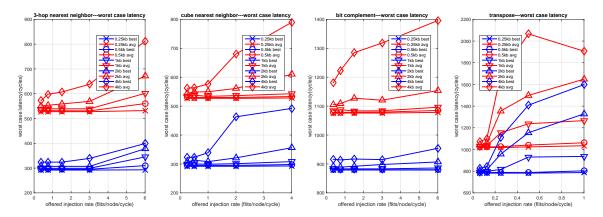

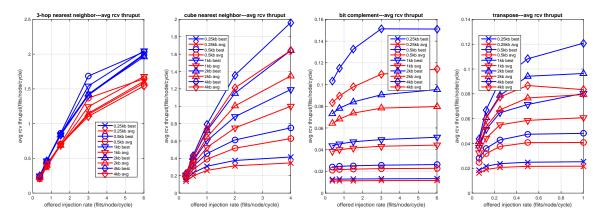

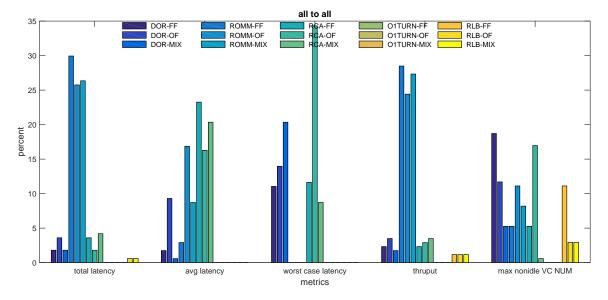

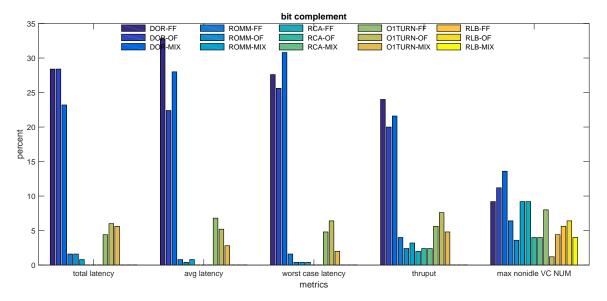

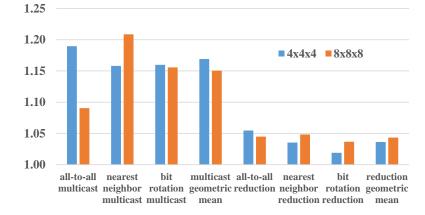

|   |      | 5.1.4  | Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 81  |

|   |      | 5.1.5  | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 91  |

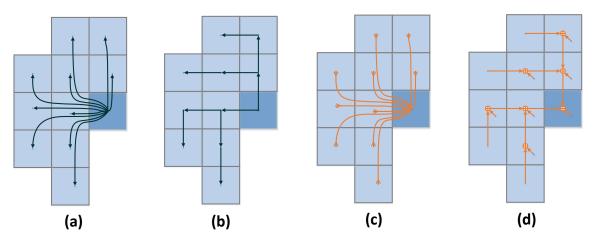

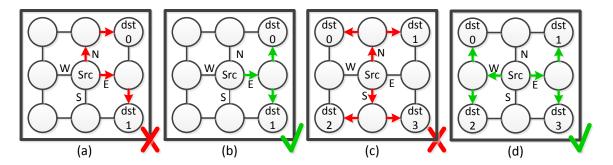

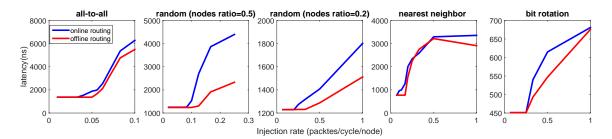

|   | 5.2  | Propo  | sed Offline Collective Routing Algorithm in Proposed VOQ Router                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 92  |

|   |      | 5.2.1  | Algorithm Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 95  |

|   |      | 5.2.2  | Algorithm Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 99  |

|   |      | 5.2.3  | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 106 |

| 6 | 3D   | FFT o  | on FPGA clusters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 107 |

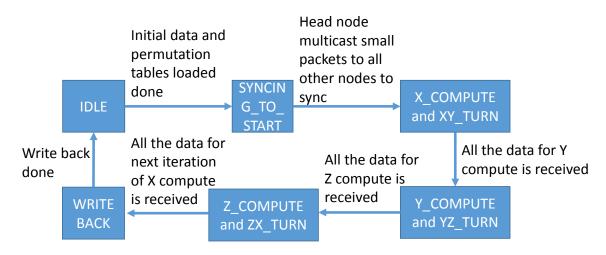

|   | 6.1  | 3D FI  | T Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 107 |

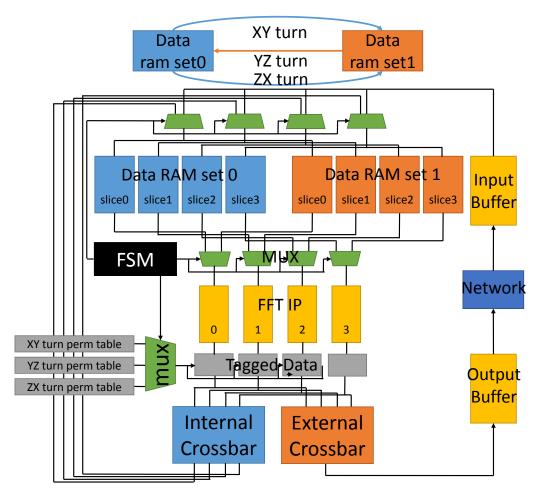

|   | 6.2 | Impler | mentation                                                                                      | 109 |

|---|-----|--------|------------------------------------------------------------------------------------------------|-----|

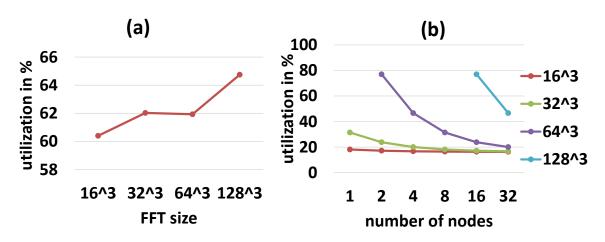

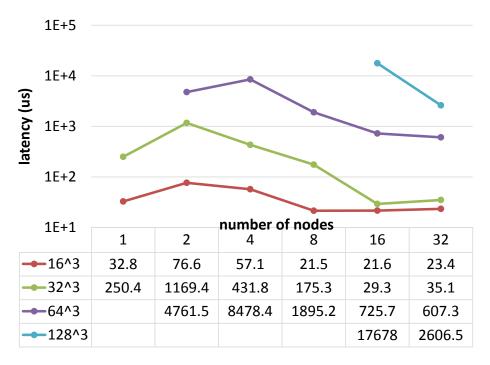

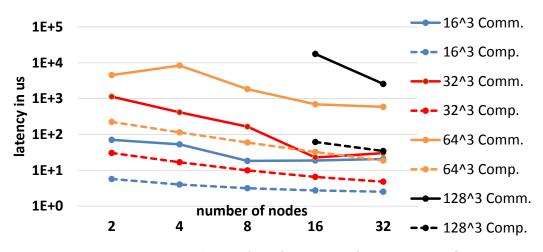

|   | 6.3 | Experi | imental Results                                                                                | 112 |

|   | 6.4 | Discus | sion $\ldots$ | 114 |

| 7 | 3D  | FFT a  | nd Implications for MD on FPGA Cloud                                                           | 116 |

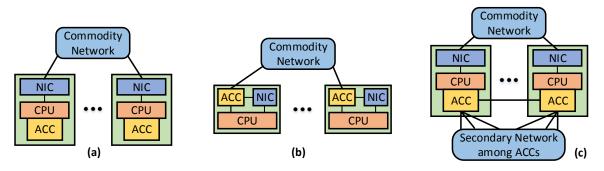

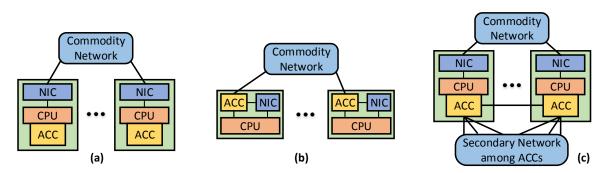

|   | 7.1 | FPGA   | -centric Clouds and Clusters                                                                   | 117 |

|   |     | 7.1.1  | Catapult II                                                                                    | 119 |

|   |     | 7.1.2  | Novo-G#                                                                                        | 121 |

|   |     | 7.1.3  | Methods                                                                                        | 122 |

|   | 7.2 | FFTs   | and Molecular Dynamics                                                                         | 122 |

|   |     | 7.2.1  | FFT and FPGAs                                                                                  | 122 |

|   |     | 7.2.2  | MD, FPGAs, and Strong Scaling                                                                  | 123 |

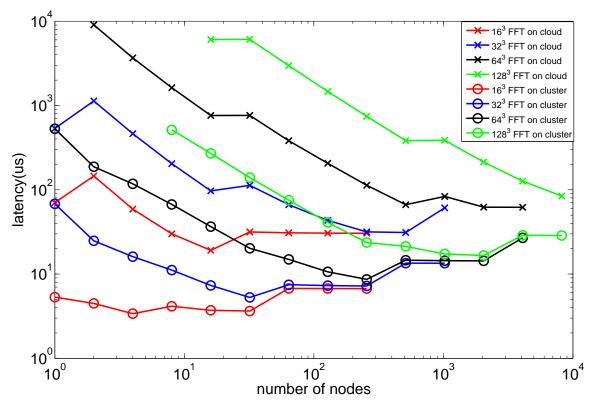

|   | 7.3 | 3D FF  | T on Catapult II and Novo-G# $\ldots$                                                          | 124 |

|   |     | 7.3.1  | 3D FFT on Catapult II                                                                          | 124 |

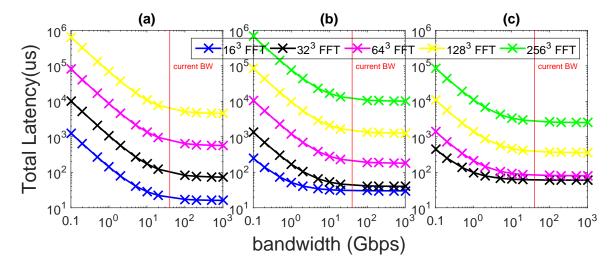

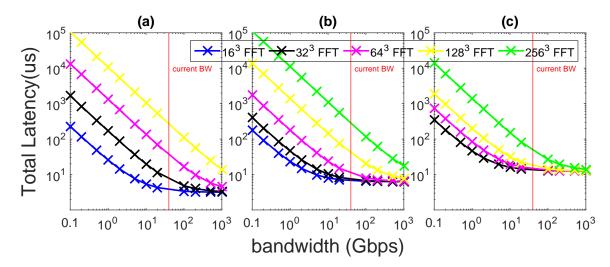

|   |     | 7.3.2  | 3D FFT Models for Catapult II and Novo-G#                                                      | 128 |

|   | 7.4 | Optim  | izing Performance with Contraction                                                             | 134 |

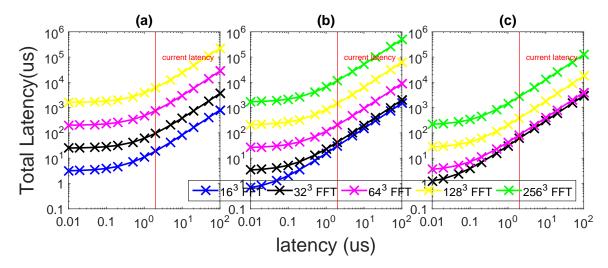

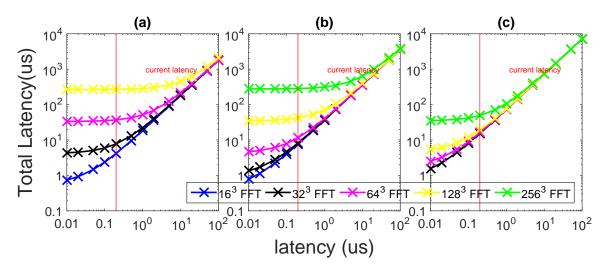

|   |     | 7.4.1  | Contraction Model                                                                              | 134 |

|   |     | 7.4.2  | Contraction Results                                                                            | 137 |

|   | 7.5 | MD St  | trong Scaling                                                                                  | 138 |

|   |     | 7.5.1  | Models for MD performance estimation                                                           | 138 |

|   |     | 7.5.2  | Evaluation                                                                                     | 142 |

|   | 7.6 | Discus | sion and Future Work                                                                           | 145 |

| 8 | Con | clusio | n and Future Work                                                                              | 147 |

|   | 8.1 | Conclu | usion                                                                                          | 147 |

|   | 8.2 | Future | e Work                                                                                         | 149 |

|   |     | 8.2.1  | Future Work on Inter-FPGA Links                                                                | 149 |

|   |     | 8.2.2  | Future Work on Inter-FPGA Communication Middleware                                             | 150 |

| Curriculum Vitae |                                   | 177 |

|------------------|-----------------------------------|-----|

| References       |                                   | 153 |

| 8.2.4            | Future Work on Applications       | 151 |

| 8.2.3            | Future Work on Routing Algorithms | 151 |

## List of Tables

| 3.1 | The comparison of characteristics between Interlaken and SerialLite III                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | The physical Characteristics of the Interlaken IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39  |

| 3.3 | The mean and variance of link latencies. All times in $ns. \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 41  |

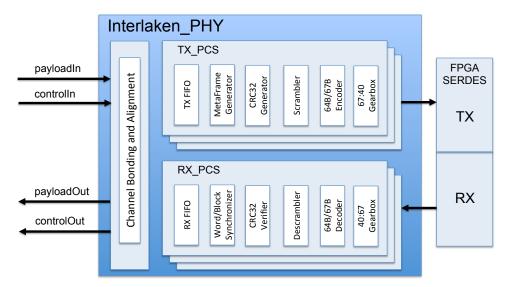

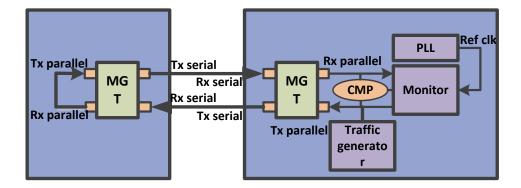

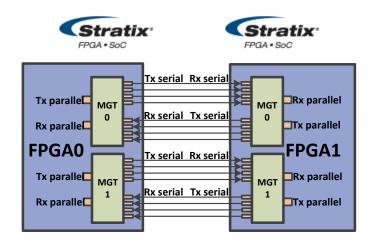

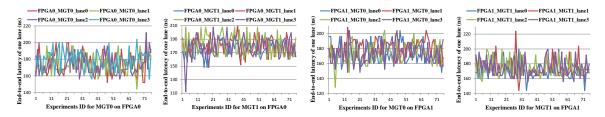

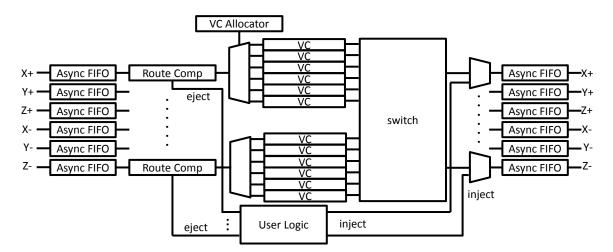

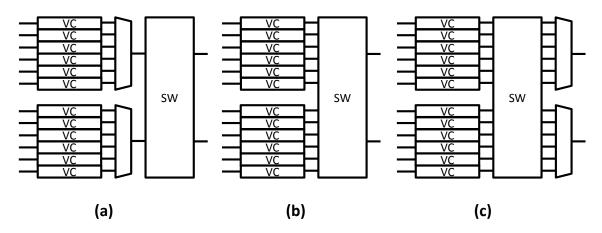

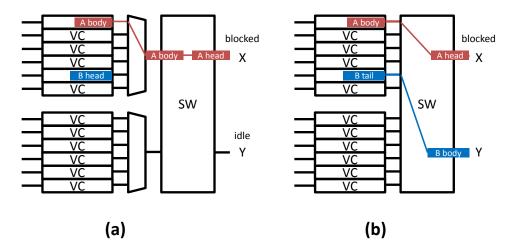

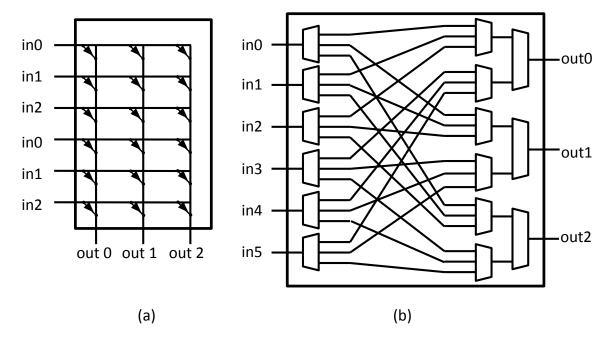

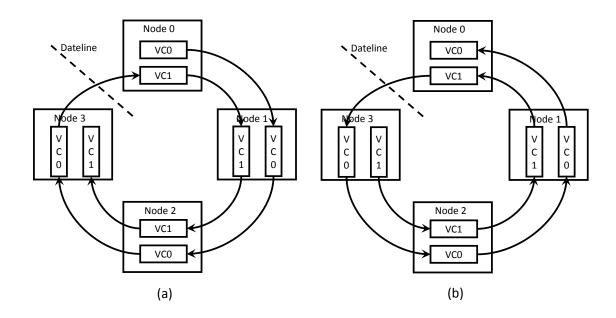

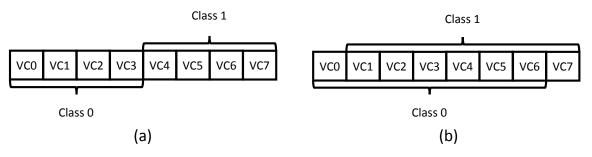

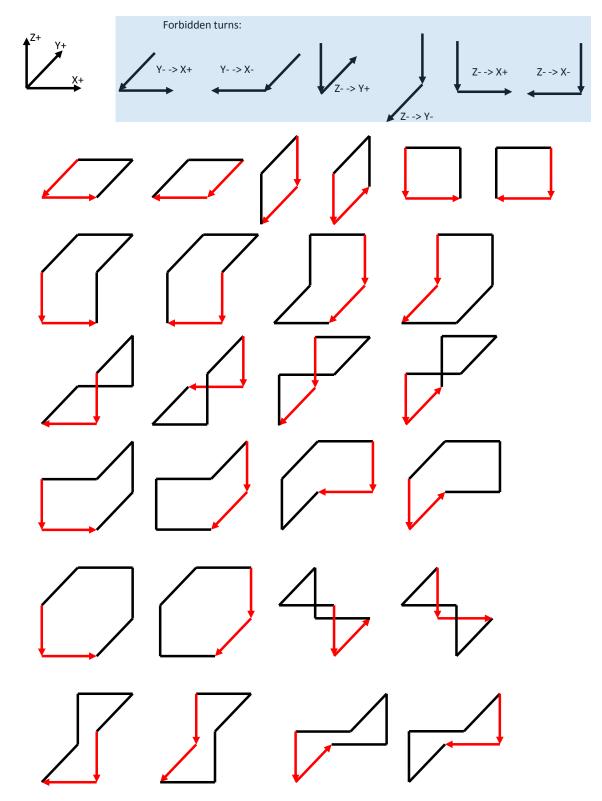

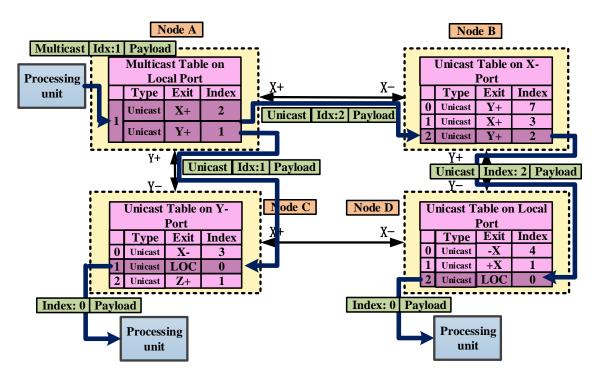

| 3.4 | The clock jitter over four ProceV boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 41  |