## **Syracuse University**

## **SURFACE**

Dissertations - ALL **SURFACE**

December 2018

## Efficient machine learning: models and accelerations

Zhe Li Syracuse University

Follow this and additional works at: https://surface.syr.edu/etd

Part of the Engineering Commons

#### **Recommended Citation**

Li, Zhe, "Efficient machine learning: models and accelerations" (2018). Dissertations - ALL. 989. https://surface.syr.edu/etd/989

This Dissertation is brought to you for free and open access by the SURFACE at SURFACE. It has been accepted for inclusion in Dissertations - ALL by an authorized administrator of SURFACE. For more information, please contact surface@syr.edu.

#### **ABSTRACT**

One of the key enablers of the recent unprecedented success of machine learning is the adoption of very large models with millions of parameters (i.e., weights). The larger-scale model tend to enable the extraction of more complex high-level features, and therefore, lead to a significant improvement of the overall accuracy. On the other side, the layered deep structure and large model sizes also demand to increase computational capability and memory requirements. In order to achieve higher scalability, performance, and energy efficiency for deep learning systems, two orthogonal research and development trends have attracted enormous interests. The first trend is the acceleration while the second is the model compression. The underlying goal of these two trends is the high quality of the models to provides accurate predictions. In this thesis, we address these two problems and utilize different computing paradigms to solve real-life deep learning problems.

To explore in these two domains, this thesis first presents the cogent confabulation network for sentence completion problem. We use Chinese language as a case study to describe our exploration of the cogent confabulation based text recognition models. The exploration and optimization of the cogent confabulation based models have been conducted through various comparisons. The optimized network offered a better accuracy performance for the sentence completion. To accelerate the sentence completion problem in a multi-processing system, we propose a parallel framework for the confabulation recall algorithm. The parallel implementation reduces runtime, improves the recall accuracy by breaking the fixed evaluation order and introducing more generalization, and

maintains a balanced progress in status update among all neurons. A lexicon scheduling algorithm is presented to further improve the model performance.

As deep neural networks have been proven effective to solve many reallife applications, and they are deployed on low-power devices, we then investigated the acceleration for the neural network inference using a hardware friendly computing paradigm, stochastic computing. It is an approximate computing paradigm which requires small hardware footprint and achieves high energy efficiency. Applying this stochastic computing to deep convolutional neural networks, we design the functional hardware blocks and optimize them jointly to minimize the accuracy loss due to the approximation. The synthesis results show that the proposed design achieves the remarkable low hardware cost and power/energy consumption.

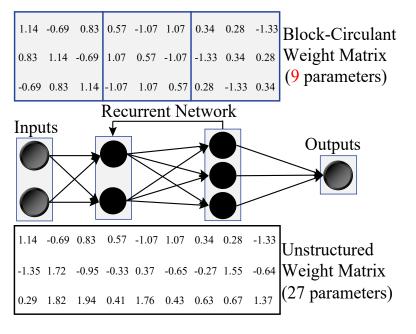

Modern neural networks usually imply a huge amount of parameters which can not be fit into embedded devices. Compression of the deep learning models together with acceleration attracts our attention. We introduce the structured matrices based neural network to address this problem. Circulant matrix is one of the structured matrices, where a matrix can be represented using a single vector, so that the matrix is compressed. We further investigate a more flexible structure based on circulant matrix, called block-circulant matrix. It partitions a matrix into several smaller blocks and makes each submatrix to be circulant. The compression ratio is controllable. With the help of Fourier Transform based equivalent computation, the inference of the deep neural network can be accelerated with high energy efficiency on the FPGAs. We also offer the optimization for the training algorithm for block circulant matrices based neural networks to obtain a high accuracy after compression.

## EFFICIENT MACHINE LEARNING: MODELS AND ACCELERATIONS

by

### Zhe Li

B.S., Beijing University of Posts and Telecommunications, 2012

M.S., Syracuse University, 2014

### Dissertation

Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electrical and Computer Engineering

Syracuse University December 2018 Copyright © Zhe Li 2018 All Rights Reserved

#### **ACKNOWLEDGEMENTS**

During my graduate career, I received help from many people, without whom this dissertation could not have been finished.

First of all, I would like to express my most sincere gratitude to my advisor, Dr. Qinru Qiu, who recognized me and offered me the chance of doctorate study on December, 2012 when I hesitated whether to move a step forward in the academia and needed a guidance. She provided comprehensive support all the way through the completion of this degree. Secondly, I am also thankful to Dr. Roger Chen, who recognized me and recommended me to seek the doctorate degree when I was a master student in his class. He offered me such opportunity to re-consider my career path. My sincere gratitude also goes to my close collaborator, Dr. Yanzhi Wang, without whom I could not have achieved so much. I learned a lot from his advice and enjoyed the journey we went on together. I would like also to show my appreciation to my committee members, Dr. Sucheta Soundarajan, Dr. Mustafa C., Dr. Lixin Shen for their valuable feedbacks. I would like to extend my deepest thanks to all my collaborators, Dr. Bo Yuan, Dr. Ji Li, Dr. Jian Tang, Dr. Xue Lin, Siyu Liao, Caiwen Ding, Ao Ren, Ruizhe Cai, Shuo Wang. I would like to thank all my labmates: Dr. Qiuwen Chen, Dr. Khadeer Ahmed, Wei Liu, Jianwei Cui, Amar Shrestha, Yilan Li, Haowen Fang and Ziyi Zhao. Your support, company and friendship are the treasures during my years in Syracuse.

Finally, I would like to express my everlasting appreciation to my family, who accompanied, encouraged, and supported me in this difficult journey. Without their trusts and constant love, I would never be able to achieve this much. This thesis is dedicated to my wife Lei Zhang, my baby girl Vivian Li, and my parents, Shengzhang Li and Honglei Zou.

## TABLE OF CONTENTS

| A  | Acknowledgements                              |                                                                                                                                                                                                                                                                                                                                         |                                                    |  |

|----|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|

| Ta | ble o                                         | Contents                                                                                                                                                                                                                                                                                                                                | V                                                  |  |

| Li | st of                                         | Tables                                                                                                                                                                                                                                                                                                                                  | i                                                  |  |

| Li | List of Figures                               |                                                                                                                                                                                                                                                                                                                                         |                                                    |  |

| 1  | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5       | <ul><li>1.5.2 Deep Convolutional Neural Network</li></ul>                                                                                                                                                                                                                                                                               | 33<br>33<br>33<br>33<br>34<br>35<br>10<br>11<br>11 |  |

|    | 1.6                                           | e e e e e e e e e e e e e e e e e e e                                                                                                                                                                                                                                                                                                   | 16                                                 |  |

| 2  | <b>Cog</b> 2.1 2.2                            | Formulation of Chinese Completion using Cogent Confabulation 2.2.1 Processing the training text                                                                                                                                                                                                                                         | 19<br>22<br>22<br>22                               |  |

|    | <ul><li>2.3</li><li>2.4</li><li>2.5</li></ul> | Training and Recall Algorithm with Case Study  2.3.1 Knowledge Link Weighting  Evaluations  2.4.1 Necessity of incorporating segmentation labels and circular Knowledge Base  2.4.2 Analysis of mutual information  2.4.3 Quantified Knowledge Link Weighting scheme  2.4.4 Confabulation model optimization  2.4.5 Qualitative Results | 25<br>25<br>25<br>25<br>31<br>34<br>36<br>42<br>42 |  |

| 3  | Para<br>ulat<br>3.1<br>3.2<br>3.3             | Introduction                                                                                                                                                                                                                                                                                                                            | 43<br>43<br>43<br>48<br>48                         |  |

|   |       | 3.3.2   | Lexicon Level Parallelization                              | 50         |

|---|-------|---------|------------------------------------------------------------|------------|

|   |       | 3.3.3   | Lexicon scheduling for intermittent pruning                | 52         |

|   | 3.4   | Exper   | imental Results                                            | 54         |

|   | 3.5   | Concl   | usion                                                      | 61         |

| 4 | Hig   | hly-Sca | alable Deep Convolutional Neural Network using Stochas     | 5 <b>-</b> |

|   | tic ( | Compu   | ting                                                       | 62         |

|   | 4.1   | Introd  | luction                                                    | 62         |

|   | 4.2   |         | ed Works                                                   |            |

|   | 4.3   | Overv   | view of DCNN Architecture and Stochastic Computing         | 67         |

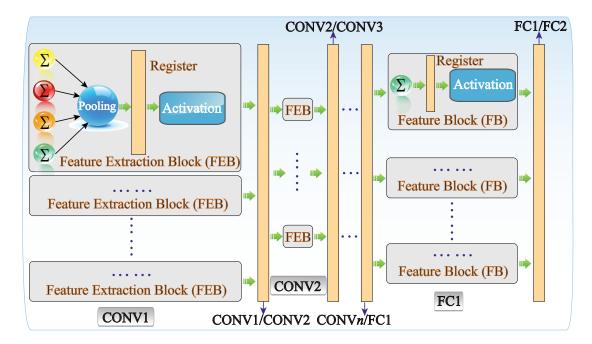

|   |       | 4.3.1   | DCNN Architecture Decomposition                            | 67         |

|   |       | 4.3.2   | Stochastic Computing (SC)                                  | 68         |

|   |       | 4.3.3   | Application-level vs. Hardware Accuracy                    | 71         |

|   | 4.4   | Desig   | n for Function Blocks and Feature Extraction Blocks        | 72         |

|   |       | 4.4.1   | Inner Product/Convolution Block Design                     | 72         |

|   |       | 4.4.2   | Pooling Block Designs                                      | 76         |

|   |       | 4.4.3   | Activation Function Block Designs                          |            |

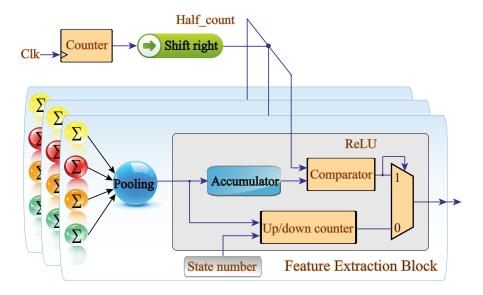

|   |       | 4.4.4   | Feature Extraction Block Designs                           | 84         |

|   | 4.5   | Furth   | er Optimization for Function Blocks and Feature Extraction |            |

|   |       | Blocks  | s in HEIF                                                  |            |

|   |       | 4.5.1   | Transmission Gate Based Multiplication                     |            |

|   |       | 4.5.2   | APC Optimization                                           |            |

|   |       | 4.5.3   | Weight Storage Optimization                                |            |

|   |       | 4.5.4   | Pipeline Based DCNN Optimizations                          |            |

|   | 4.6   | Overa   | ıll Evaluation                                             |            |

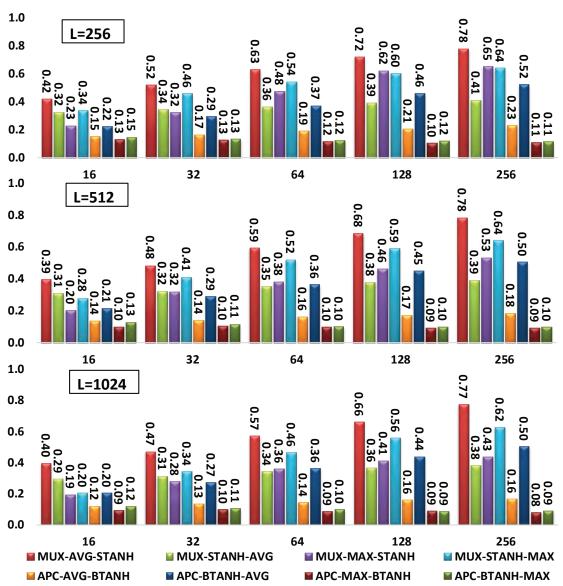

|   |       | 4.6.1   | Optimization Results on Feature Extraction Blocks          |            |

|   |       | 4.6.2   | Overall Results on the DCNNs                               |            |

|   | 4.7   | Concl   | usion                                                      | 108        |

| 5 |       |         | Efficient Recurrent Neural Networks using Structured Com   |            |

|   |       |         | echniques on FPGAs                                         | 111        |

|   |       |         | luction                                                    |            |

|   | 5.2   |         | ed Work                                                    |            |

|   | 5.3   |         | rured Compression                                          |            |

|   |       | 5.3.1   | Block-Circulant Matrix                                     |            |

|   |       | 5.3.2   | Inference and Training Algorithms                          |            |

|   |       | 5.3.3   | Alternating Direction Method of Multipliers (ADMM)         |            |

|   |       |         | Based Training                                             | 121        |

|   | 5.4   |         | Model Design Exploration: A software view                  |            |

|   | 5.5   |         | Acceleration                                               |            |

|   |       | 5.5.1   | FFT/IFFT Decoupling                                        |            |

|   |       | 5.5.2   | Datapath and Activation Quantization                       |            |

|   |       | 5.5.3   | Operator Scheduling                                        |            |

|   |       | 5.5.4   | Performance and Resource Models                            | -135       |

|    | 5.6                  | Hardware Design                                 | 136 |  |

|----|----------------------|-------------------------------------------------|-----|--|

|    |                      | 5.6.1 E-RNN Hardware Architecture               | 136 |  |

|    |                      | 5.6.2 PE Design                                 | 137 |  |

|    |                      | 5.6.3 Compute Unit (CU) Implementation          | 138 |  |

|    | 5.7                  | Experiment Evaluation                           | 143 |  |

|    | 5.8                  | Conclusion                                      | 148 |  |

| 6  | Con                  | clusion and future work                         | 149 |  |

|    | 6.1                  | Conclusion                                      | 149 |  |

|    | 6.2                  | Future Directions                               | 150 |  |

|    |                      | 6.2.1 Applying Structure Matrices to DCNN       | 150 |  |

|    |                      | 6.2.2 Accelerating structured matrices on GPGPU | 151 |  |

| Bi | bliog                | graphy                                          | 152 |  |

| Bi | Biographical Data 10 |                                                 |     |  |

## LIST OF TABLES

| 2.1  | Penn Treebank tag list                                             | 21  |

|------|--------------------------------------------------------------------|-----|

| 2.2  | Comparison of non-circular and circular model                      | 31  |

| 2.3  | Knowledge link grouping.                                           | 35  |

| 2.4  | Example of confabulated sentences                                  | 41  |

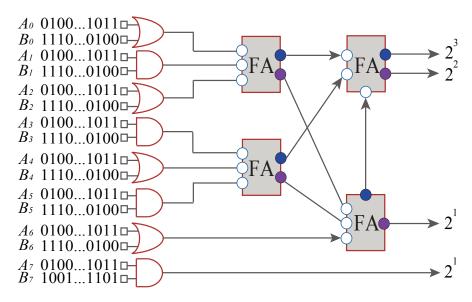

| 4.1  | Absolute Errors of OR Gate-Based Inner Product Block               | 74  |

| 4.2  | Absolute Errors of MUX-Based Inner Product Block                   | 74  |

| 4.3  | Relative Errors of the APC-Based Compared with the Conven-         |     |

|      | tional Parallel Counter-Based Inner Product Blocks                 | 76  |

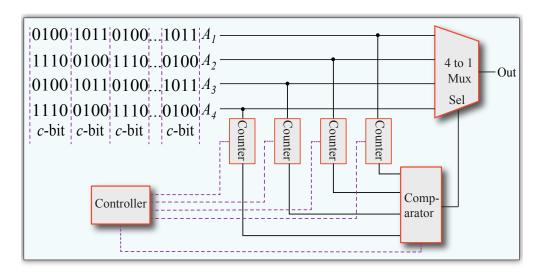

| 4.4  | Relative Result Deviation of Hardware-Oriented Max Pooling         |     |

|      | Block Compared with Software-Based Max Pooling                     | 79  |

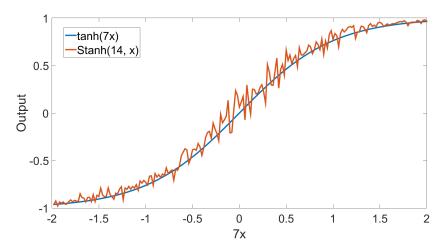

| 4.5  | The Relationship Between State Number and Relative Inaccu-         |     |

|      | racy of Stanh                                                      | 80  |

| 4.6  | The designs of FEBs and corresponding optimization functions.      | 88  |

| 4.7  | Comparison of inner-product blocks before and after optimiza-      |     |

|      | tion using 1024-bit-stream                                         | 93  |

| 4.8  | Hardware performance of FEBs with the different input sizes us-    |     |

|      | ing 1024-bit-stream w/ and w/o pipeline based optimization         | 99  |

| 4.9  | Comparison among various hardware-based and software-              |     |

|      | based DCNNs                                                        | 102 |

| 4.10 | Comparison among Various SC-DCNN Designs Implementing              |     |

|      | LeNet 5                                                            | 106 |

| 4.11 | Application-level performance and hardware cost of LeNet-5         |     |

|      | implementation using the proposed HEIF                             | 106 |

| 4.12 | Comparison with existing hardware platforms for handwritten        |     |

|      | digit recognition using the MNIST [27] dataset                     | 107 |

| 4.13 | List of existing hardware platforms for image classification using |     |

|      | (part of) the AlexNet [63] on ImageNet [26] dataset                | 108 |

|      | ·                                                                  |     |

| 5.1  | Comparison among LSTM based RNN models                             |     |

| 5.2  | Comparison among GRU based RNN models                              | 125 |

| 5.3  | Comparison of two selected FPGA platforms                          | 143 |

| 5.4  | Detailed comparisons for different (LSTM and GRU) RNN de-          |     |

|      | signs on FPGAs (ours, ESE, and C-LSTM)                             | 144 |

|      |                                                                    |     |

## LIST OF FIGURES

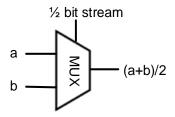

| 1.1  | Stochastic multiplication using: (a) unipolar encoding (b) bipolar encoding                                                                                                                   | $\epsilon$ |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.2  | Scaled addition in stochastic computing                                                                                                                                                       | 7          |

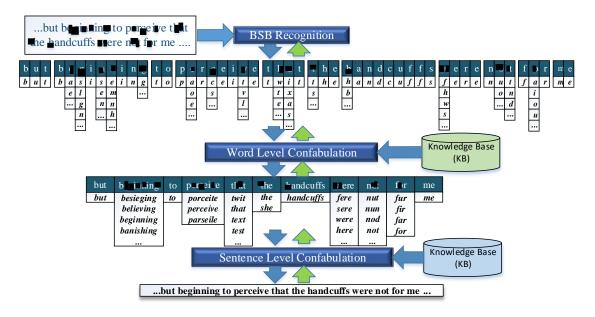

| 1.3  | Overall architecture of the ITRS models and algorithmic flow                                                                                                                                  | 11         |

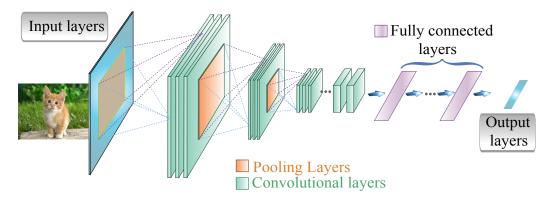

| 1.4  | General DCNN architecture                                                                                                                                                                     | 12         |

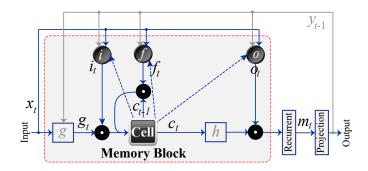

| 1.5  | An LSTM based RNN architecture.                                                                                                                                                               | 13         |

| 1.6  | A GRU based RNN architecture                                                                                                                                                                  | 14         |

| 2.1  | Lexion Structure of confabulation model                                                                                                                                                       | 26         |

| 2.2  | Lexion Structure of confabulation model (Any arrow is from source lexicon to target lexicon. Orange arrows represents                                                                         |            |

|      | Knowledge Links from observable lexicons to unobservable or<br>partially observable lexicons; Green arrows represents Knowl-<br>edge Links between lexicons in same level; Blue arrows repre- |            |

|      | sents Knowledge Links from unobservable or partially observ-                                                                                                                                  |            |

|      | able lexicons to observable lexicons)                                                                                                                                                         | 27         |

| 2.3  | Recall accuracy of sentence confabulation model with/without                                                                                                                                  |            |

|      | segmentation label                                                                                                                                                                            | 30         |

| 2.4  | Mutual information trend chart for 4 kinds of Knowledge Links.                                                                                                                                | 32         |

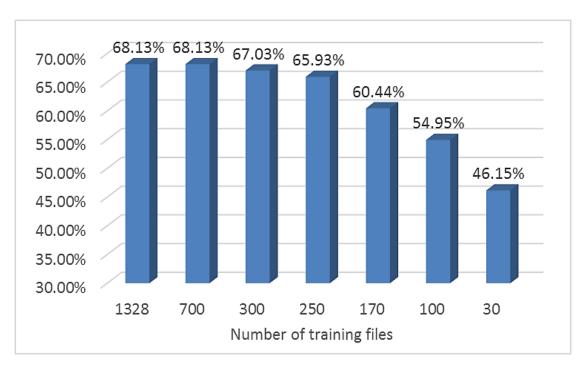

| 2.5  | Recall accuracy of different training set size                                                                                                                                                | 33         |

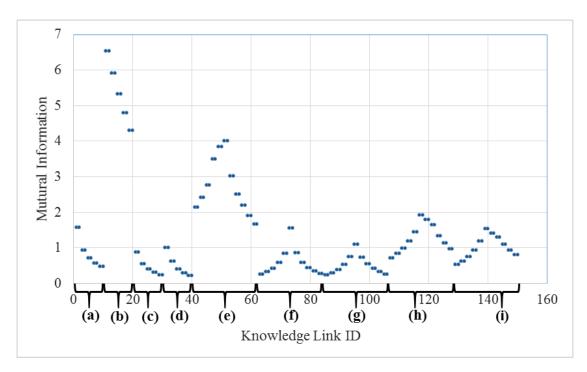

| 2.6  | Knowledge Links' mutual information                                                                                                                                                           | 34         |

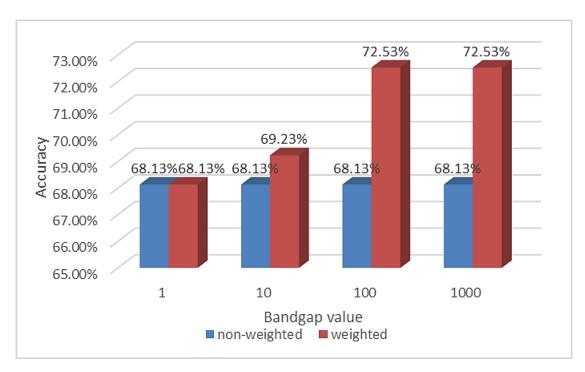

| 2.7  | Recall Accuracy of basic confabulation model of different bandgap value with/without weighting                                                                                                | 36         |

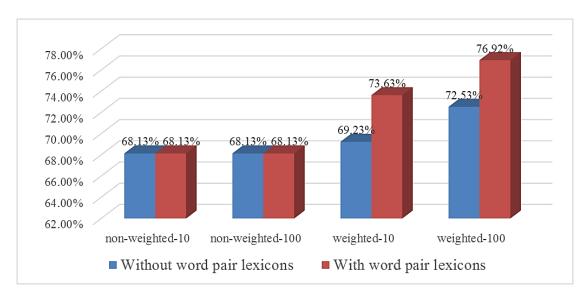

| 2.8  | Recall Accuracy of confabulation model with/without word                                                                                                                                      |            |

|      | pair lexicons (non-weighted-10 represents recall accuracy with                                                                                                                                |            |

|      | bandgap value of 10 and without weighting scheme; non-                                                                                                                                        |            |

|      | weighted-100 represents recall accuracy with bandgap value of 100 and without weighting scheme; Weighted-10 represents re-                                                                    |            |

|      | call accuracy with bandgap value of 10 and weighting scheme;                                                                                                                                  |            |

|      | Weighted-100 represents recall accuracy with bandgap value of                                                                                                                                 |            |

|      | 100 and weighting scheme)                                                                                                                                                                     | 37         |

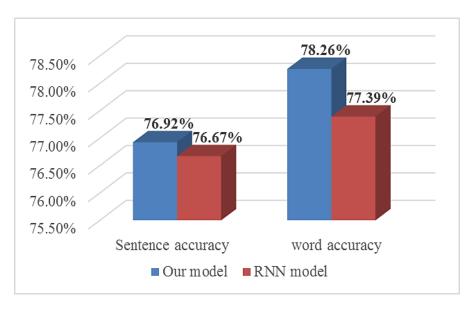

| 2.9  | Recall accuracy between different models(sentence accuracy is                                                                                                                                 |            |

|      | evaluated by the amount of sentences recalled identically to orig-                                                                                                                            |            |

|      | inal sentences; word accuracy is evaluated by the amount of                                                                                                                                   |            |

| 2.10 | missing Chinese charaters recalled identically to the original)                                                                                                                               | 38         |

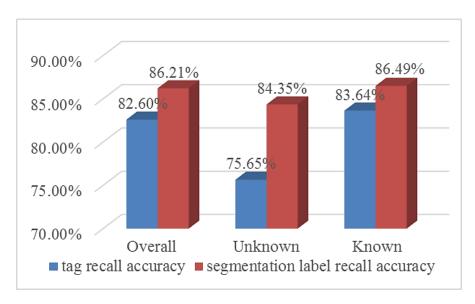

| 2.10 | Recall accuracy of tags and segmentation labels(Overall denotes accuracy for all characters in sentences; Unknown denotes accu-                                                               |            |

|      | racy for unknown missing characters, Known denotes accuracy                                                                                                                                   |            |

|      | for known characters)                                                                                                                                                                         | 39         |

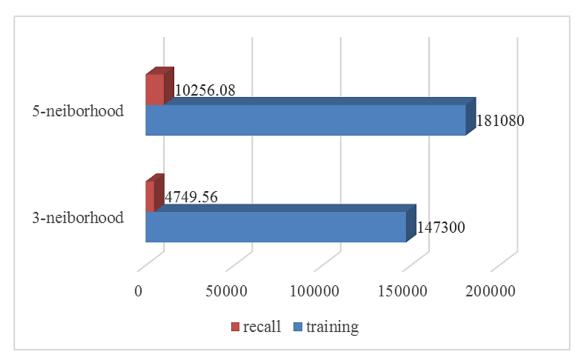

| 2.11 | Training time and recall time of different KL structure                                                                                                                                       | 40         |

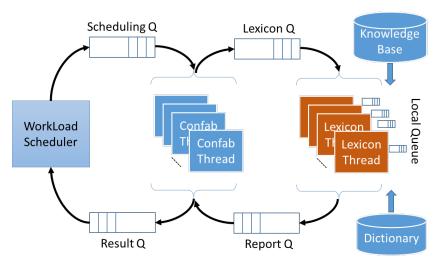

| 3.1  | Intuitive parallel confabulation architecture                                                                                                                                                 | 49         |

| 3.2  | Parallel confabulation architecture on lexicon level                 | 50  |

|------|----------------------------------------------------------------------|-----|

| 3.3  | Sentence lexicon model example                                       | 55  |

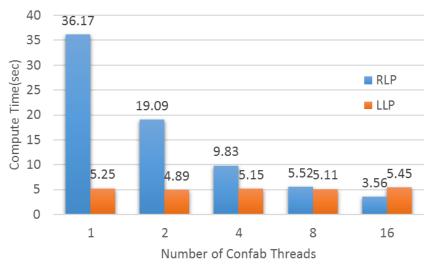

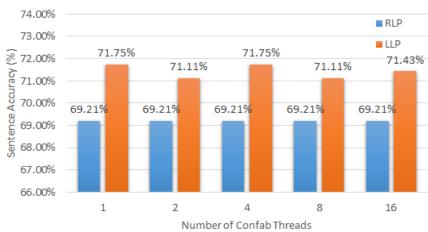

| 3.4  | Compute time for RLP and LLP w/o intermittent pruning                | 56  |

| 3.5  | Sentency accuracy for RLP and LLP w/o intermittent pruning .         | 57  |

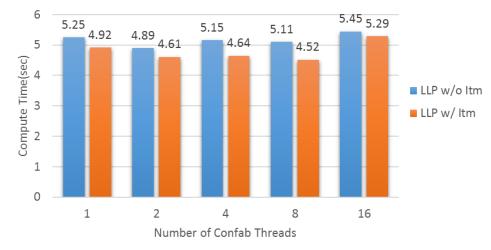

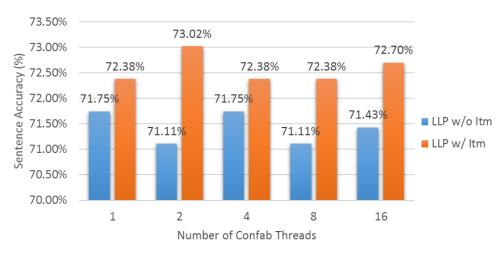

| 3.6  | Compute time for LLP w/o and w/ intermittent pruning                 | 58  |

| 3.7  | Sentency accuracy for LLP w/o and w/ intermittent pruning            | 58  |

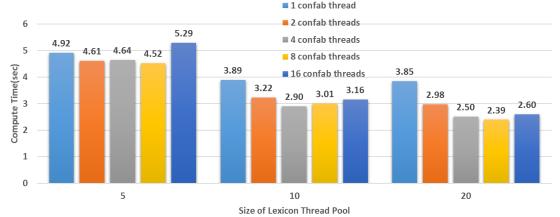

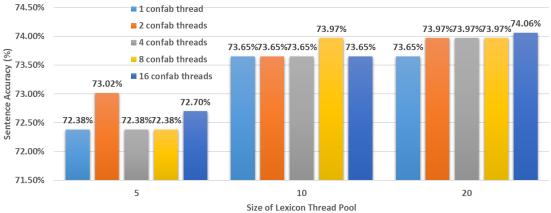

| 3.8  | Compute time for LLP w/ intermittent pruning for different lex-      |     |

|      | icon thread pool sizes                                               | 59  |

| 3.9  | Sentence accuracy for LLP w/ intermittent pruning with differ-       |     |

|      | ent lexicon thread pool sizes                                        | 59  |

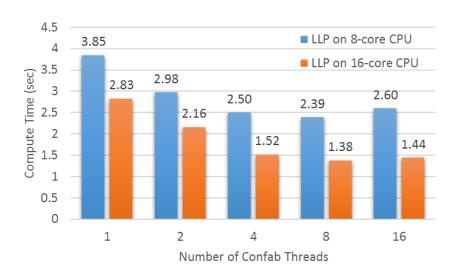

| 3.10 | Compute time for LLP w/ intermittent pruning on 8-core CPU           |     |

|      | machine and 16-core CPU machine with 20 lexicon threads              | 60  |

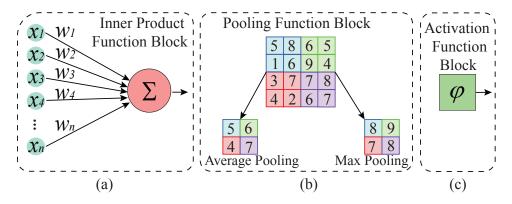

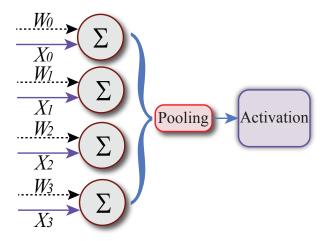

| 4.1  | Three types of basic operations (function blocks) in DCNN. (a)       |     |

|      | Inner Product, (b) pooling, and (c) activation                       | 68  |

| 4.2  | Stochastic multiplication. (a) Unipolar multiplication and (b)       |     |

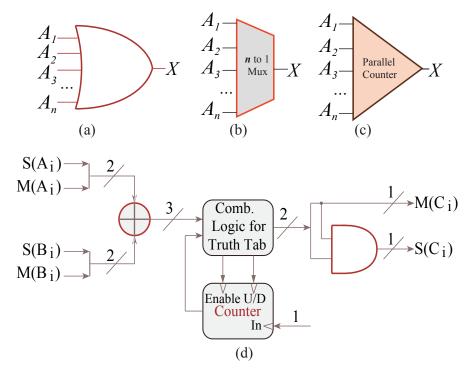

|      | bipolar multiplication                                               | 71  |

| 4.3  | Stochastic addition. (a) OR gate, (b) MUX, (c) APC, and (d) two-     |     |

|      | line representation-based adder                                      | 71  |

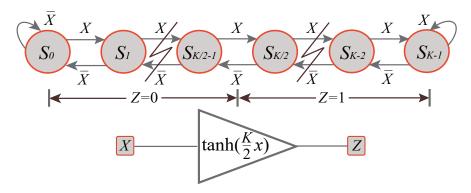

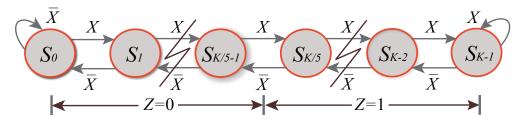

| 4.4  | Stochastic hyperbolic tangent                                        | 72  |

| 4.5  | 16-bit Approximate Parallel Counter                                  | 75  |

| 4.6  | The Proposed Hardware-Oriented Max Pooling                           | 79  |

| 4.7  | Output comparison of Stanh vs tanh                                   | 80  |

| 4.8  | Diagram of the proposed ReLU block                                   | 82  |

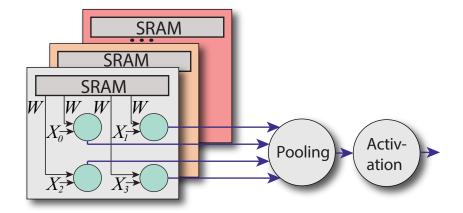

| 4.9  | The structure of a feature extraction block                          | 85  |

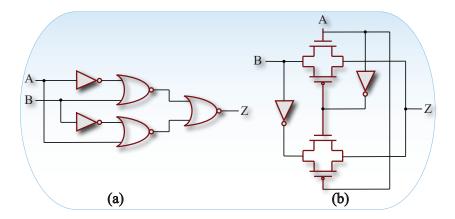

| 4.10 | Structure of optimized Stanh for MUX-Max-Stanh                       | 86  |

| 4.11 | XNOR gate implementations. (a) Static CMOS design, (b) Trans-        |     |

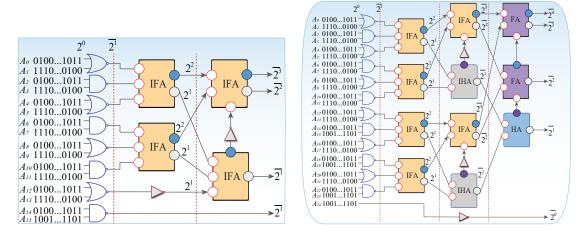

|      | mission gate design                                                  | 90  |

| 4.12 | (a) Redesigned 16-input APC structure, (b) Redesigned 25-input       |     |

|      | APC structure                                                        | 91  |

| 4.13 | Filter-Aware SRAM Sharing Scheme                                     | 95  |

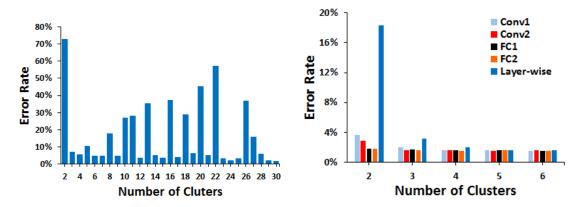

| 4.14 | Application-level error rates for (a) clustering through all layers, |     |

|      | (b) clustering within each layer and layer-wise clustering           | 97  |

| 4.15 | Two-tier pipeline design in the framework                            | 98  |

| 4.16 | Imprecision for Optimized FEBs with bit-stream length $L =$          |     |

|      | 256, 512, 1024                                                       | 101 |

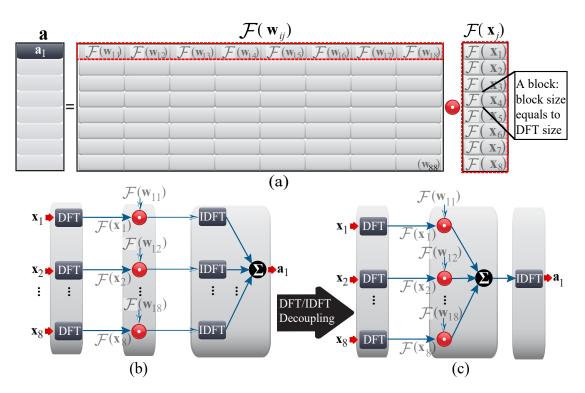

| 5.1  | Block-circulant matrices for weight representation                   | 118 |

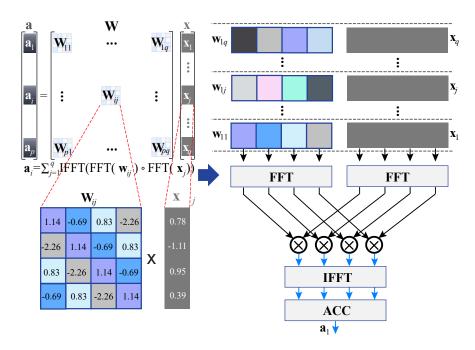

| 5.2  | An illustration of FFT-based calculation in block-circulant matrix   |     |

|      | multiplication                                                       | 119 |

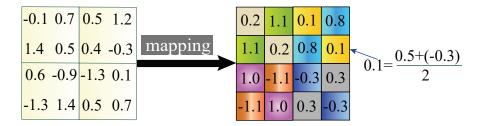

| 5.3  | Euclidean mapping for a $4 \times 4$ matrix with block size of 2     | 123 |

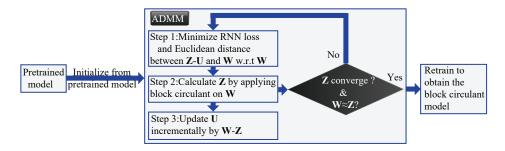

| 5.4  | The overall procedure of ADMM-based structured matrix training.      |     |

| 5.5  | An illustration of the (a) circulant convolution operator; (b) its   |     |

|      | original implementation; (c) and the optimized implementation.       | 129 |

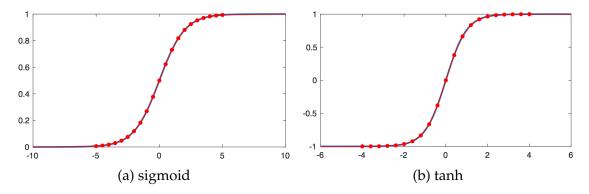

| 5.6  | Piece-wise linear activation functions                          | 131 |  |

|------|-----------------------------------------------------------------|-----|--|

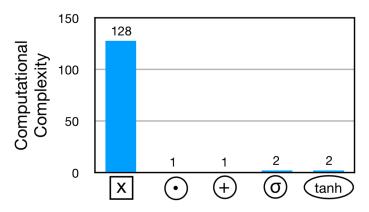

| 5.7  | Computational complexity of LSTM operators                      |     |  |

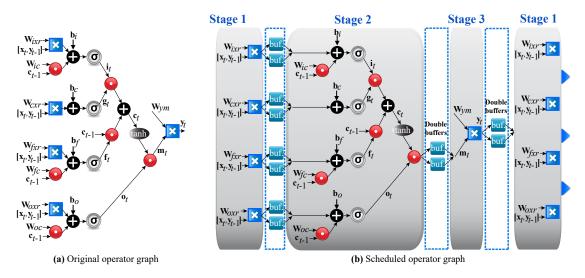

| 5.8  | Illustration of operator scheduling on data dependency graph.   |     |  |

|      | The circle represents the element-wise operator, and the square |     |  |

|      | represents the circulant convolution operator                   | 132 |  |

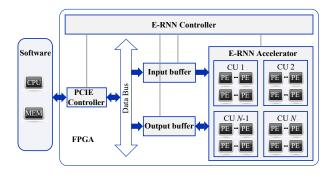

| 5.9  | The overall E-RNN hardware architecture                         | 137 |  |

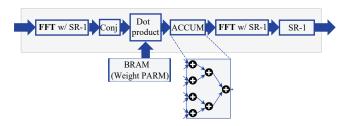

| 5.10 | The PE design in FPGA implementation                            | 138 |  |

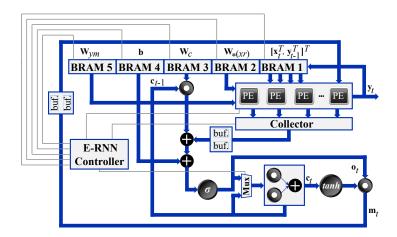

| 5.11 | One compute unit (CU) with multiple processing elements (PEs)   |     |  |

|      | of LSTM                                                         | 139 |  |

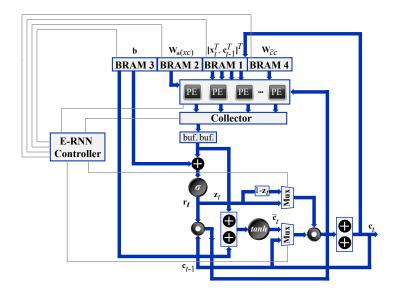

| 5.12 | A compute unit (CU) with multiple processing elements (PEs) of  |     |  |

|      | GRU                                                             | 140 |  |

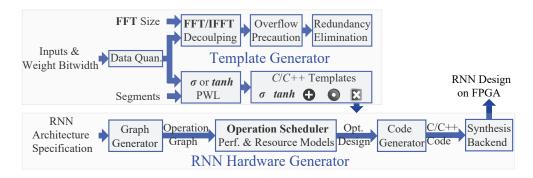

| 5.13 | Overview of high level synthesis framework                      | 141 |  |

#### CHAPTER 1

#### INTRODUCTION

From the end of the first decade of the 21st century, neural networks have been experiencing a phenomenal resurgence thanks to the big data and the significant advances in processing speeds. Large-scale deep neural networks (DNNs) have been able to deliver impressive results in many challenging problems. For instance, DNNs have led to breakthroughs in object recognition accuracy on the ImageNet dataset [26], even achieving human-level performance for face recognition [117]. Such promising results triggered the revolution of several traditional and emerging real-world applications, such as self-driving systems [51], automatic machine translations [22], drug discovery and toxicology [13]. As a result, both academia and industry show the rising interests with significant resources devoted to investigation, improvement, and promotion of deep learning methods and systems.

In this chapter, we discuss the motivation of the study. Then we introduce the basics of three computing paradigms for machine learning models especially deep learning models. Applications of different learning systems are introduced. Finally, the contributions of the thesis are reviewed.

### 1.1 Motivation

Machine learning technology benefits many aspects of modern life: web searches, e-commerce recommendations, social network content filtering, etc. [67]. Unfortunately, the conventional machine learning techniques were restricted due to the lack of ability to automatically extract high-level features.

These features traditionally have been extracted by well-engineered manual feature extractors. *Deep learning* methods have taken advantage of the architecture of multi-level representations to learn very complex functions [67]. Here, each representation is obtained from a slightly less abstract level through the transformation based on a simple non-linear module. Deep learning significantly enhances the machine learning capability using learning from data by these multiple layers for different features without human involvement.

Due to the deep structure, the performance of deep learning model highly relies on the capability of hardware resources. From high performance server clusters [25, 14] to *General-Purpose Graphics Processing Units (GPGPUs)* [54, 9], parallel accelerations of *deep neural networks (DNNs)* are widely used in both the academic and industry. Recently, hardware acceleration for DNNs has attracted enormous research interests on *Field-Programmable Gate Arrays (FPGAs)* [138, 89, 93]. Nevertheless, there is a trend of embedding DNNs into lightweight embedded and portable systems, such as surveillance monitoring systems [52], self-driving systems [51], unmanned aerial systems [87], and robotic systems [62]. These scenarios require very low power & energy consumptions and small hardware footprints. Besides, cell phones [67] and wearable devices [41] equipped with hardware-level neural network computation capability require the radical reduction in power & energy consumptions and footprints.

This thesis mainly addresses the inference acceleration and model compression for modern machine learning models. The acceleration also implies an energy-efficient system that enables the models to run on low-power devices. Meanwhile, effective modeling and training optimization for specific applications are proposed to maintain a good accuracy. We investigate three com-

puting paradigms to explore the efficient machine learning model acceleration. The first one, Cogent Confabulation is an application oriented acceleration research, which is introduced in Chapter 2 and Chapter 3. The second computing paradigm in this thesis is Stochastic Computing, which is more general to neural networks, is described in Chapter 4. The last computing paradigm is the structured matrices based neural network acceleration and model compression, which is presented in Chapter 5.

## 1.2 Cogent Confabulation

Inspired by human cognitive process, cogent confabulation [47] mimics human information processing including Hebbian learning, correlation of conceptual symbols and recall action of brain. Based on the theory, the cognitive information process consists of two steps: learning and recall. The confabulation model represents the observation using a set of features. These features construct the basic dimensions that describe the world of applications. Different observed attributes of a feature are referred as symbols. The set of symbols used to describe the same feature forms a lexicon and the symbols in a lexicon are exclusive to each other. In learning process, matrices storing posterior probabilities between neurons of two features are captured and referred as the knowledge links (KL).A KL stores weighted directed edges from symbols in source lexicon to symbols in target lexicon. The  $(i, j)^{th}$  entry of a KL, quantified as the conditional probability  $P(s_i|t_i)$ , represents the Hebbian plasticity of the synapse between  $i^{th}$  symbol in source lexicon s and  $j^{th}$  symbol in target lexicon t. The knowledge links are constructed during learning process by extracting and associating features from the inputs and collection of all knowledge links in the model forms its knowledge base (KB). During recall, the input is a noisy observation of the target. In this observation, certain features are observed with great ambiguity, therefore multiple symbols are assigned to the corresponding lexicons. The goal of the recall process is to resolve the ambiguity and select the set of symbols for maximum likelihood using the statistical information obtained during the learning process. This is achieved using a procedure similar to the integrate-and-fire mechanism in biological neural system. Each neuron in a target lexicon receives an excitation from neurons of other lexicons through KLs, which is the weighted sum of its incoming excitatory synapses. Among neurons in the same lexicon, those that are least excited will be suppressed and the rest will fire and become excitatory input of other neurons. Their firing strengths are normalized and proportional to their excitation levels. As neurons gradually being suppressed, eventually only the neuron that has the highest excitation remains firing in each lexicon and the ambiguity is thus resolved. Let l denote a lexicon,  $F_l$  denote the set of lexicons that have knowledge links going into lexicon *l*, and *S*<sub>*l*</sub> denote the set of symbols that belong to lexicon *l*. The excitation of a symbol *t* in lexicon *l* is calculated by summing up all incoming knowledge links:

$$el(t) = \sum_{k \in F_l} \{ \sum_{s \in S_k} [el(s) \ln(\frac{P(s|t)}{p_0})] + B \}, t \in S_l$$

(1.1)

where the function el(s) is the excitation level of the source symbol s. The parameter  $p_0$  is the smallest meaningful value of  $P(s_i|t_j)$ . The parameter B is a positive global constant called the bandgap. The purpose of introducing B in the function is to ensure that a symbol receiving N active knowledge links will always have a higher excitation level than a symbol receiving (N-1) active knowledge links, regardless of their strength. As we can see, the excitation level of a symbol is actually its log-likelihood given the observed attributes in other lexicons.

## 1.3 Stochastic Computing

Deviated from the conventional binary computing (referred as *conventional computing*), *stochastic computing* (*SC*) represents any number using a stream of bits. Here the value of real number x in the unit interval is interpreted by the ratio of bit-1 in the entire bit-stream, i.e., P(X = 1). For instance, the 8-bit sequence 00100101 containing three 1s denotes  $x = P(X = 1) = \frac{3}{8} = 0.375$ . Since each bit has the same weight, number representation in stochastic computing is unary and hence enables different interpretations for the same value. Besides this unipolar coding format [34], bipolar coding format [34] is another popular number representation scheme in stochastic computing. In the scenario of bipolar coding, the relationship between x and P(X = 1) becomes  $P(X = 1) = \frac{x+1}{2}$ , which enables the stochastic representation for negative number. Notice that for either unipolar or bipolar coding format, the represented number ranges in [0, 1] or [-1, 1]. To represent a number beyond this range, a pre-scaling operation [135] or integer bit-stream based representation [6] can be used to relax this constraint.

A major advantage of stochastic computing is its ultra-low hardware cost: Many complicated arithmetic functions can now be implemented with very simple logic circuits. For instance, as shown in Figure 1.1, the real multiplication can be performed with an **AND** gate in the unipolar coding form since

$$c = P(C = 1)$$

$$= P(A = 1)P(B = 1)$$

$$= ab$$

Figure 1.1: Stochastic multiplication using: (a) unipolar encoding (b) bipolar encoding.

or with an XNOR gate in bipolar coding form since

$$c = 2P(C = 1) - 1$$

$$= 2[P(A = 1)P(B = 1) + P(A = 0)P(B = 0)] - 1$$

$$= 2[P(A = 1)P(B = 1) + (1 - P(A = 1))(1 - P(B = 1))] - 1$$

$$= (2P(A = 1) - 1)(2P(B = 1) - 1)$$

$$= ab.$$

Another example is regarding the adder, which can be simply implemented with a multiplexer (see Figure 1.2) in the scenario of stochastic computing, for

$$c = P(C = 1)$$

$$= \frac{1}{2}(P(A = 1) + \frac{1}{2}P(B = 1))$$

$$= \frac{1}{2}(a + b).$$

Additionally, the addition in the bipolar form uses this multiplexer as well, since

$$c = 2P(C = 1) - 1$$

$$= 2\left[\frac{1}{2}(P(A = 1) + \frac{1}{2}P(B = 1)] - 1\right]$$

$$= \frac{1}{2}[2P(A = 1) - 1) + (2P(B = 1) - 1)]$$

$$= \frac{1}{2}(a + b).$$

In general, such significant saving in hardware resource makes stochastic computing circuits well-suited for the area-constrained applications, such as

Figure 1.2: Scaled addition in stochastic computing.

signal sensing and processing in wearable devices. Besides, the abundant budget on area offers immense design space in optimizing hardware performance in terms of power, latency and speed via efficient trade-offs between area and those metrics, thereby implying the potential application of stochastic computing in large-scale systems that requires massive parallelism for basic computing units.

Another advantage of stochastic computing is its inherent error-resilience. By nature, the redundant representation of stochastic computing translates to the strong capability for tolerating transient error and soft error (bit-flipping) since each bit has the same weight in bit-stream. For instance, as reported in [97, 85, 134], compared to their conventional computing counterparts, the stochastic digital signal processing component shows much better error-resilience capability, which is attractive for the emerging noise-rich deep nanoscale CMOS era.

### 1.4 Structured Matrices based Neural Networks

In general, a circulant matrix  $\mathbf{W} \in \mathbb{R}^{n \times n}$  [94] is defined by a vector  $\mathbf{w} = (w_1, w_2, \dots, w_n)$  as the following:

$$\mathbf{W} = \begin{bmatrix} w_1 & w_n & \dots & w_3 & w_2 \\ w_2 & w_1 & w_n & & w_3 \\ \vdots & w_2 & w_1 & \ddots & \vdots \\ w_{n-1} & & \ddots & \ddots & w_n \\ w_n & w_{n-1} & \dots & w_2 & w_1 \end{bmatrix}.$$

(1.2)

From equation (1.2) it is seen that an n-by-n circulant matrix only has n parameters because of its strong structure. Clearly, when such structure is imposed to the weight matrices of DNNs, the required space cost for storing the weights is immediately reduced from  $O(n^2)$  to O(n).

Besides the advantage on low space cost, the use of circulant matrices as weight matrices can also lead to low computational complexity for both inference and training, which are described as below:

**Inference:** The dominating computation during the forward propagation in the inference is the matrix-vector multiplication (**Wx**). According to [94], when **W** is a circulant matrix, **Wx** can be performed as below:

$$\mathbf{a} = \mathbf{W}\mathbf{x} = \text{IDFT}(\text{DFT}(\mathbf{w}) \circ \text{DFT}(\mathbf{x})), \tag{1.3}$$

where  $\circ$  denotes the element-wise multiplication; DFT( $\cdot$ ) denotes the Discrete Fourier transform; and IDFT( $\cdot$ ) denotes the inverse Discrete Fourier transform. Notice that since the computational complexity of n-point DFT/IDFT is only  $O(n \log n)$ , the computational complexity of DNN inference can achieve order-of-magnitude reduction (from  $O(n^2)$  to  $O(n \log n)$ ).

**Training:** For backward propagation in the training, recall that its key procedure is to perform the chain rule-based calculation for the gradient of loss function L with respect to the weight vector  $\mathbf{w}$  as below:

$$\frac{\partial L}{\partial \mathbf{w}} = \frac{\partial L}{\partial \mathbf{a}} \frac{\partial \mathbf{a}}{\partial \mathbf{w}},\tag{1.4}$$

where  $\frac{\partial L}{\partial \mathbf{a}}$  is the gradient back-propagated from the subsequent layer. Notice that in the scenario that **W** is a square circulant matrix, as indicated in [18],  $\frac{\partial \mathbf{a}}{\partial \mathbf{w}}$  is a circulant matrix defined by the vector  $\mathbf{x}' = (x_1, x_n, x_{n-1}, \dots, x_2)$ . Therefore, according to [94], equation (1.4) can be simplified as below:

$$\frac{\partial L}{\partial \mathbf{w}} = \text{IDFT}(\text{DFT}(\frac{\partial L}{\partial \mathbf{a}}) \circ \text{DFT}(\mathbf{x}')), \tag{1.5}$$

where 1 is a column vector full of ones. In addition, the gradient of input x which is back-propagated to the previous layer, should be calculated as:

$$\frac{\partial L}{\partial \mathbf{x}} = \frac{\partial L}{\partial \mathbf{a}} \frac{\partial \mathbf{a}}{\partial \mathbf{x}}.$$

(1.6)

Notice that here  $\frac{\partial \mathbf{a}}{\partial \mathbf{x}}$  is also a circulant matrix that is defined as  $\mathbf{w}' = (w_1, w_n, w_{n-1}, \dots, w_2)$ . Hence equation (1.6) can also be simplified as below:

$$\frac{\partial L}{\partial \mathbf{x}} = \text{IDFT}(\text{DFT}(\frac{\partial L}{\partial \mathbf{a}}) \circ \text{DFT}(\mathbf{w}')). \tag{1.7}$$

From equation (1.5) and (1.7) it is seen that, when **W** is a circulant matrix, the updating scheme for the gradients of **w** and **x**, as the key part of DNN training, can also be calculated using DFT/IDFT, thereby rendering order-of-magnitude reduction in computational cost for training (from  $O(n^2)$  to  $O(n \log n)$ ).

## 1.5 Applications

We applied the above three computing paradigms on three applications as below. To be specific, cogent confabulation is applied on the module for the *In*-

telligent Text Recognition System (ITRS); Stochastic Computing is applied on the deep convolutional neural networks (DCNNs) and structured matrices based neural network is used to train the Recurrent Neural Networks (RNNs) for automatic speech recognition (ASR).

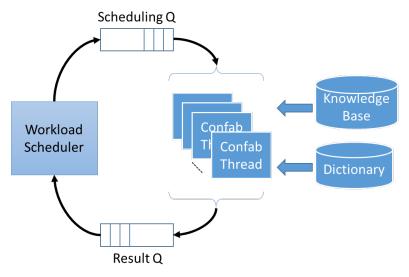

## 1.5.1 Intelligent Text Recognition System

In a recent development, the cogent confabulation model was used for sentence completion [47, 101]. Trained using a large amount of literature, the confabulation algorithm has demonstrated the capability of completing a sentence (given a few starting words) based on conditional probabilities among the words and phrases. We refer these algorithms as the "association" models. The brain inspired signal processing flow could be applied to many applications. A proof-of-concept prototype of context-aware Intelligence Text Recognition system (ITRS) is developed on high performance computing cluster [100]. As shown in Figure 1.3, the lower layer of the ITRS performs pattern matching of the input image using a simple non-linear auto-associative neural network model called Brain-State-in-a-Box (BSB) [4]. It matches the input image with the stored alphabet. A race model is introduced that gives fuzzy results of pattern matching. Multiple matching patterns will be found for one input character image, which is referred as ambiguity. The upper layer of the ITRS performs information association using the cogent confabulation model [47]. It enhances those BSB outputs that have strong correlations in the context of word and sentence and suppresses those BSB outputs that are weakly related. In this way, it selects characters that form the most meaningful words and sentences.

Figure 1.3: Overall architecture of the ITRS models and algorithmic flow.

## 1.5.2 Deep Convolutional Neural Network

Deep Convolutional Neural Networks (DCNN) are biologically inspired variants of *multi-layer perceptrons* (*MLPs*) by mimicking the animal visual mechanism [50]. Thus, a DCNN has special sets of neurons only connected to a small receptive field of its previous layer rather than fully connected. Besides an input layer and an output layer, a general DCNN architecture consists of a stack of *convolutional layers*, *pooling layers*, and *fully connected layers* shown in Figure 1.4. Please note that some special layers like normalization or regularization are not the focus in this thesis.

1) A convolutional layer is associated with a set of learnable filters (or kernels) [68], which are activated when specific types of features are found at some spatial positions in the inputs. Filter-sized moving windows are applied to the inputs to obtain a set of feature maps by calculating the convolution of the filter and inputs in the moving window. Each *convolutional neuron*, representing one

Figure 1.4: General DCNN architecture.

pixel in a feature map, takes a set of inputs and corresponding filter weights to calculate their inner-products.

2) After extracting features using convolution, a subsampling step can be applied to aggregate statistics of these features to reduce the dimensions of data and mitigate over-fitting issues. This subsampling operation is realized by a pooling neuron in pooling layers, where different non-linear functions can be applied, such as max pooling, average pooling, and L2-norm pooling. Among them, max pooling is the dominating type of pooling in state-of-the-art DC-NNs due to the higher overall accuracy and convergence speed. The activation functions are non-linear transformation functions, such as Rectified Linear Units (ReLU) f(x) = max(0, x), hyperbolic tangent (tanh) f(x) = tanh(x) or f(x) = |tanh(x)|, and sigmoid function  $f(x) = \frac{1}{1+e^{-x}}$ . Among them, the ReLU function is the dominating type in the (large-scale) DCNNs due to i) the lower complexity for software implementation; and ii) the reduced vanishing gradient problem [37]. These non-linear transformations are conducted somewhere before the inputs of the next layer, ensuring that they are within the range of [-1, 1]. Usually, a combination of convolutional neurons, pooling neurons and activation functions forms a feature extraction block (FEB) to extract high-level

Figure 1.5: An LSTM based RNN architecture.

abstraction from the input images or previous low-level features.

*3)* A fully connected layer is a normal neural network layer with its inputs fully connected with its previous layer. Each *fully connected neuron* calculates the inner-product of its inputs and corresponding weights.

# 1.5.3 Recurrent Neural Networks based Automatic Speech Recognition

## Long short-term memory (LSTM)

Modern large scale Automatic Speech Recognition (ASR) systems take advantage of LSTM-based RNNs as their acoustic models. An LSTM model consists of large matrices which is the most computational intensive part among all the steps of the ASR procedure. We focus on a representative LSTM model presented in [109] whose architecture is shown in Figure 1.5. An LSTM-based RNN accepts an input vector sequence  $\mathbb{X} = (\mathbf{x}_1; \mathbf{x}_2; \mathbf{x}_3; ...; \mathbf{x}_T)$  (each of  $\mathbf{x}_t$  is a vector corresponding to time t) with the output sequence from last step  $\mathbb{Y}^{T-1} = (\mathbf{y}_0; \mathbf{y}_1; \mathbf{y}_2; ...; \mathbf{y}_{T-1})$  (each of  $\mathbf{y}_t$  is a vector). It computes an output sequence

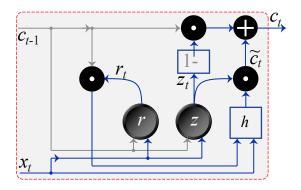

Figure 1.6: A GRU based RNN architecture.

$\mathbb{Y} = (\mathbf{y}_1; \mathbf{y}_2; \mathbf{y}_3; ...; \mathbf{y}_T)$  by using the following equations iteratively from t = 1 to T:

$$\mathbf{i}_{t} = \sigma(\mathbf{W}_{ix}\mathbf{x}_{t} + \mathbf{W}_{ir}\mathbf{y}_{t-1} + \mathbf{W}_{ic}\mathbf{c}_{t-1} + \mathbf{b}_{i}), \tag{1.8a}$$

$$\mathbf{f}_t = \sigma(\mathbf{W}_{fx}\mathbf{x}_t + \mathbf{W}_{fr}\mathbf{y}_{t-1} + \mathbf{W}_{fc}\mathbf{c}_{t-1} + \mathbf{b}_f), \tag{1.8b}$$

$$\mathbf{g}_t = \sigma(\mathbf{W}_{cx}\mathbf{x}_t + \mathbf{W}_{cr}\mathbf{y}_{t-1} + \mathbf{b}_c), \tag{1.8c}$$

$$\mathbf{c}_{t} = \mathbf{f}_{t} \odot \mathbf{c}_{t-1} + \mathbf{g}_{t} \odot \mathbf{i}_{t}, \tag{1.8d}$$

$$\mathbf{o}_t = \sigma(\mathbf{W}_{ox}\mathbf{x}_t + \mathbf{W}_{or}\mathbf{y}_{t-1} + \mathbf{W}_{oc}\mathbf{c}_t + \mathbf{b}_o), \tag{1.8e}$$

$$\mathbf{m}_t = \mathbf{o}_t \odot \mathbf{h}(\mathbf{c}_t), \tag{1.8f}$$

$$\mathbf{y}_t = \mathbf{W}_{vm} \mathbf{m}_t, \tag{1.8g}$$

where symbols **i**, **f**, **o**, **c**, **m**, and **y** are respectively the input gate, forget gate, output gate, cell state, cell output, and projected output [109]; the  $\odot$  operation denotes the point-wise multiplication, and the + operation denotes the point-wise addition. The **W** terms denote weight matrices (e.g.  $\mathbf{W}_{ix}$  is the matrix of weights from the input vector  $\mathbf{x}_t$  to the input gate), and the **b** terms denote bias vectors. Please note  $\mathbf{W}_{ic}$ ,  $\mathbf{W}_{fc}$ , and  $\mathbf{W}_{oc}$  are diagonal matrices for peephole connections [36], thus they are essentially a vector. As a result, the matrix-vector multiplication like  $\mathbf{W}_{ic}\mathbf{c}_{t-1}$  can be calculated by the  $\odot$  operation.  $\sigma$  is the logistic activation function and **h** is a user defined activation function. Here we use

hyperpolic tangent (tanh) activation function as h.

In the above equations, we have nine matrix-vector multiplications (excluding peephole connections which can be calculated by  $\odot$ ). In one gate/cell,  $\mathbf{W}_{*x}\mathbf{x}_t + \mathbf{W}_{*r}\mathbf{y}_{t-1}$  can be combined/fused in one matrix-vector multiplication by concatenating the matrix and vector as  $\mathbf{W}_{*(xr)}[\mathbf{x}_t^T, \mathbf{y}_{t-1}^T]^T$ . Furthermore, the four gate/cell matrices can also be concatenated and calculated through one matrix-vector multiplication as  $\mathbf{W}_{(ifco)(xr)}[\mathbf{x}_t^T, \mathbf{y}_{t-1}^T]^T$ . In this way, we can compute the above equations with only two matrix-vector multiplications, i.e.  $\mathbf{W}_{(ifco)(xr)}[\mathbf{x}_t^T, \mathbf{y}_{t-1}^T]^T$  and  $\mathbf{W}_{ym}\mathbf{m}_t$ .

#### Gated recurrent units (GRU)

The GRU is a variation of the LSTM as introduced in [20]. It combines the forget and input gates into a single "update gate". It also merges the cell state and hidden state, and makes some other changes. The architecture is shown in Figure 1.6. Similarly, it follows equations iteratively from t = 1 to T:

$$\mathbf{z}_t = \sigma(\mathbf{W}_{zx}\mathbf{x}_t + \mathbf{W}_{zc}\mathbf{c}_{t-1} + \mathbf{b}_z), \tag{1.9a}$$

$$\mathbf{r}_{t} = \sigma(\mathbf{W}_{rx}\mathbf{x}_{t} + \mathbf{W}_{rc}\mathbf{c}_{t-1} + \mathbf{b}_{r}), \tag{1.9b}$$

$$\tilde{\mathbf{c}}_t = \mathbf{h}(\mathbf{W}_{\tilde{c}x}\mathbf{x}_t + \mathbf{W}_{\tilde{c}c}(\mathbf{r}_t \odot \mathbf{c}_{t-1}) + \mathbf{b}_{\tilde{c}}), \tag{1.9c}$$

$$\mathbf{c}_t = (1 - \mathbf{z}_t) \odot \mathbf{c}_{t-1} + \mathbf{z}_t \odot \tilde{\mathbf{c}}_t \tag{1.9d}$$

where symbols  $\mathbf{z}$ ,  $\mathbf{r}$ ,  $\tilde{\mathbf{c}}$ ,  $\mathbf{c}$  are respectively the update gate, reset gate, reset state, and cell state; the  $\odot$  operation denotes the point-wise multiplication, and the + operation denotes the point-wise addition. The  $\mathbf{W}$  terms denote weight matrices (e.g.  $\mathbf{W}_{zx}$  is the matrix of weights from the input vector  $\mathbf{x}_t$  to the reset gate).  $\sigma$  is the logistic activation function and  $\mathbf{h}$  is a user defined activation function. Here

we use tanh activation function as h. Note that a GRU has two gates (update and reset), while an LSTM has three gates (input, forget, output). GRUs do not have the output gate that is present in LSTMs. Instead, the cell state is taken as the output. The input and forget gates are coupled by an update gate z, and the reset gate r is applied directly to the previous cell state.

In the above set of equations, we have six matrix-vector multiplications. In the reset and update gates,  $\mathbf{W}_{*x}\mathbf{x}_t + \mathbf{W}_{*c}\mathbf{c}_{t-1}$  can be combined/fused in one matrix-vector multiplication by concatenating the matrix and vector as  $\mathbf{W}_{*(xc)}[\mathbf{x}_t^T, \mathbf{c}_{t-1}^T]^T$ . Furthermore, the reset and update gate matrices can also be concatenated and calculated through one matrix-vector multiplication as  $\mathbf{W}_{(rz)(xc)}[\mathbf{x}_t^T, \mathbf{c}_{t-1}^T]^T$ . In this way, we compute the above equations with three matrix-vector multiplications, i.e.  $\mathbf{W}_{(rz)(xc)}[\mathbf{x}_t^T, \mathbf{c}_{t-1}^T]^T$ ,  $\mathbf{W}_{\tilde{c}x}\mathbf{x}_t$ , and  $\mathbf{W}_{\tilde{c}c}(\mathbf{r}_t \odot \mathbf{c}_{t-1})$ .

### 1.6 Contributions

This thesis studies the inference acceleration for modern machine learning models with high accuracy performance. We investigate three computing paradigms to explore the efficient machine learning model acceleration. The organization and contributions of this thesis are concluded as the following.

1. Cogenet confabulation based models on the text recognition system have been investigated and optimized in [77, 98, 99] to offer the state-of-the-art quality. In Chapter 2, we used Chinese language sentence completion problem as a case study to describe our exploration on the cogent confabulation based text recognition models. The exploration and optimization

- of the cogent confabulation based models have been conducted through various comparisons.

- 2. In Chapter 3, we develop a multi-processing system for cogent confabulation models on sentence completion problems [78]. We propose a parallel framework for the confabulation recall algorithm. The parallel implementation reduced runtime, improve the recall accuracy by breaking the fixed evaluation order and introducing more generalization, and maintain a balanced progress in status update among all neurons. A lexicon scheduling algorithm was presented to further improve the model performance.

- 3. In Chapter 4, the Stochastic Computing (SC) based efficient inference framework for the deep convolutional neural networks (DCNNs) are designed [104, 79, 70]. We firstly describe how we apply the stochastic computing paradigm to DCNNs followed by a detailed partitioning of DCNN components [71, 136, 72]. The joint optimizations among the DCNN components are discussed from the perspective of SC [103, 80, 76, 75]. Finally we propose the hardware-level optimization on the complete SC based system. The synthesis results have shown that our proposed framework achieves remarkable low hardware cost and low power and energy consumption. The comparisons with latest peer works are provided.

- 4. In Chapter 5, we introduced the structured matrices based acceleration of the neural network. Inspired by previous work [18], we propose block-circulant matrices [140] based weight matrices formatting, where a weight matrix is partitioned into several blocks each of which is a circulant matrix. A circulant matrix can be represented using a single vector so that the matrix is compressed. In this way, the compression of the weight matrix is controllable. With the help of Fourier Transform based equivalent compu-

tation, the inference of the deep neural network can be accelerated energy efficiently on the FPGAs [124, 74]. We also offer the optimization for the training algorithm for block circulant matrices based neural networks to obtain a high accuracy after compression.

5. Finally in Chapter 6, the works contributing this thesis are reviewed and summarized. Potential directions to improve the studies are proposed.

#### **CHAPTER 2**

## COGENT CONFABULATION ASSISTED CHINESE SENTENCE COMPLETION

### 2.1 Introduction

As an important part of text recognition, sentence completion and prediction, which stands for the capability of filling missing words in an incomplete sentence, has attracted much attention. The first step of sentence completion is syntactic parsing of the input text. Among different languages, Chinese is a great challenge due to its linguistically isolating. Each Chinese character generally corresponds to exactly one morpheme and multiple semantic meanings. Moreover, there has been a strong tendency in the Chinese language family over the last 2000 years for single morpheme words to develop into compounds of two or more morphemes [120], which makes Chinese language linguistically more flexible and complex. All of the above makes Chinese sentence completion extremely difficult.

In our previous research [102, 100, 101, 132], a cogent confabulation based sentence completion framework is developed. A sentence is represented by a set of lexicons corresponding to its words, word pairs, and part-of-speech tags. The conditional probability between neighboring lexicons are learned from training corpus. During recall, the missing information (including unknown word and part-of-speech tags for both unknown and given words) is selected that maximizes the likelihood of observed information (i.e. those words already given in the input sentence). Due to the difference between linguistic structures, this framework has to be modified for Chinese sentences. First of all, each Chinese

character, which is represented as a 3-byte UTF-8 code, is analogy to an English word. In the rest of the chapter, we use character and word interchangeably, as they are the same in Chinese. Secondly, the part-of-speech tagging of Chinese is usually associated with each multi-character compound. Correct segmentation is essential to syntactic parsing of the sentence.

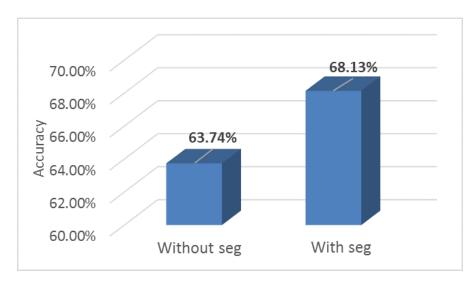

We improve previous cogent confabulation model and apply it to Chinese sentence completion. Besides integrating parts-of-speech (POS) tagging that identifies the function of each word, in the Chinese sentence confabulation, segmentation label for multi-character compound is added, which identifies word compound consisting of  $1 \sim 4$  Chinese characters. This work focuses on developing, optimizing and evaluating a confabulation model for Chinese sentence completion with high accuracy. It has three major contributions:

- 1. We extend the original sentence confabulation model to consider linguistic properties of Chinese language. Segmentation labels and beginning of sentence markers are specifically added to the model. *Knowledge links (KL)* are shared to reduce complexity and improve performance as well. Experiment results shows that the extended Chinese sentence confabulation model achieve 76.9% sentence recall accuracy with reduced memory and computing complexity.

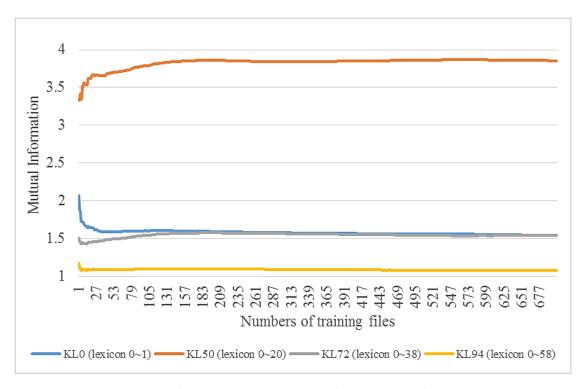

- 2. We analyze the mutual information between source and target lexicons of each knowledge link in the confabulation model and assign weight to these knowledge links accordingly. Compared to the original model, the model with weighted knowledge link has 9% higher recall accuracy.

- 3. The mutual information of KLs is also exploited to find the best training set size, which gives the best trade-offs between training effort and recall

Table 2.1: Penn Treebank tag list.

| Tag | Function                            | Examples                            |

|-----|-------------------------------------|-------------------------------------|

| VA  | Predicative Adjective               | 很(very), 雪白(snow white),            |

| VC  | Copula                              | (be), (not be),                     |

| VE  | 有 (have) as the main verb           | 有(have), 没有(have not), 无(not have), |

| VV  | Other verb                          | 想(want to), 走(walk), 喜欢(like),      |

| NR  | Proper Nouns (location, newspaper,) | 北京(Beijing), 纽约时报(New York Times),  |

| NT  | Temporal Nouns                      | 一月(Janurary), 汉朝(Han Dynasty),      |

| NN  | All other Nouns                     | 书(book), 房子(house),                 |

| PN  | Pronoun                             | 我(I), 你(you), 这(this),              |

|     |                                     |                                     |

accuracy.

## 2.2 Formulation of Chinese Completion using Cogent Confabulation

## 2.2.1 Processing the training text

Our training text is segmented and tagged using Standford Part-of-speech (POS) tagger [39]. It is one of the most matured Natural Language Processing software based on probabilistic tagging systems. First, the Chinese training sentences are segmented using Stanford Chinese word Segmenter, which is based on a linear-chain *conditional random field (CRF)* model. The tool partitions sentence into compound words consisting of single or multiple Chinese characters. And then Stanford POS Tagger takes segmented sentence as input and assigns a part-of-speech tag to each compound. Stanford POS Tagger for Chinese Language exploits 33 word level Chinese tags specified by the Penn Treebank Tagging System [129]. Table. 2.1 lists some examples of these Tags. The information of POS tags and segments will be built into the knowledge

base during training. However, the POS tagger cannot be used to process sentences with missing words. Therefore during recall, we cannot use POS tagger for syntactic analysis. Our solution is to rely on the confabulation model to recall the segments and tags during the same time when the missing words are filled in. The basic idea is to assume that all tags and segment partitions are possible at the beginning, and gradually eliminate the ambiguity during the recall process. This approach is feasible since the number of tags and possible segment partitions is limited. Our experimental results show that considering tags and segmentations at the same time helps to improve the accuracy of sentence completion.

### 2.2.2 Chinese Sentence Confabulation

### Basic confabulation framework

Inheriting from original sentence confabulation framework [101], we assume that the maximum length of a sentence is 20 words and sentence with more than 20 words will be truncated. We pad the sentence that has less than 20 words with special character [`] to represent the end of a sentence. Anything beyond the end of sentence will be ignored during training and recall.

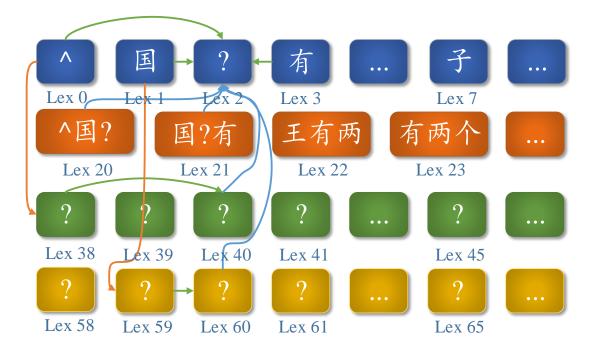

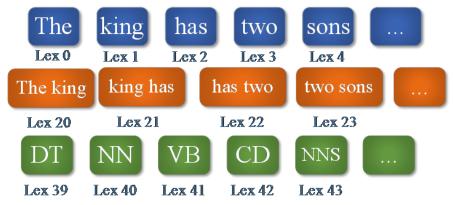

Original Sentence confabulation framework has two levels of lexicons – word and word pair. Lexicons 0 to 19 correspond to single English word at location 0 to 19 in a sentence. Lexicons 20 to 38 correspond to 19 word pairs combining word from lexicon 0  $\sim$  19 and its right adjacent neighbor. Each lexicon stores tremendous number of symbols (words or word pairs) that appears in the corresponding location.

In original framework, a KL is created between any two lexicons. In training process, we build all KL matrices to form knowledge base. And during recall, observed symbols will be set active in each lexicon. When there is no ambiguity in observation, only one symbol in a lexicon will be set active. Multiple symbols in the same lexicon will be set active because of ambiguous observation. They are referred as candidates. When a lexicon is not observable, all possible symbols will be set active to indicate the highest ambiguity. The excitation level of each candidate in the lexicon with ambiguity will be calculated and the symbols that is least excited will be suppressed. This procedure repeats until there is only one symbol left in each lexicon.

#### Chinese sentence confabulation model

Each Chinese character is encoded using 3 bytes of UTF-8 code. As mentioned before, we regard each Chinese character as a "word" and they occupy the word level lexicons in the confabulation framework. Modern Chinese language is based on word compound, which consists of 1 ~ 4 single Chinese characters. These word compounds are not delimited, however, they can be found with the help of tools, such as the Stanford POS tagger. We label each Chinese character based on its position in a word compound, and refer this as segmentation label. For example, in a two character word compound 书籍(book),书(book)is located at the first position of the two character word compound, therefore, it is marked as 1IN2, and 籍(book)is marked as 2IN2. In this work, ten segmentation labels are used. They are: 1IN1, 1IN2, 2IN2, 1IN3, 2IN3, 3IN3, 1IN4, 2IN4, 3IN4, and 4IN4. Please note that segmentation label is only needed in Chinese sentence confabulation. This is a major difference between Chinese and western

languages. In the next section, we will show the necessity of including segmentation label in the confabulation model.

In the improved confabulation model, new lexicons are created for tags and segmentation labels. Moreover, instead of having lexicons for two adjacent words, we create lexicons for three adjacent words in order to adapt to semantic compounds of multiple Chinese characters. Therefore, lexicons in the new confabulation model can be divided into four levels: lexicons  $0 \sim 19$  correspond to single Chinese word; lexicons  $20 \sim 37$  correspond to Chinese word triplets; lexicons  $38 \sim 57$  correspond to POS tags and lexicons  $58 \sim 77$  correspond to segmentation labels.

The original sentence confabulation framework has a knowledge link between any two lexicons. Therefore, the size of knowledge base increases exponentially with the number of lexicons. In this way,  $78 \times 77 = 6006$  KLs will be generated for the Chinese sentence confabulation model, which takes tremendous resources. To reduce the complexity of our computational model, two actions are jointly taken. First is to share KL matrix between lexicons that have the same relative position in sentence. For example, the distance from lexicon 0 to lexicon 1 is the same as the distance from lexicon 1 to lexicon 2, so the KLs between  $0 \sim 1$  and  $1 \sim 2$  are merged and shared.

The second action is to only create KLs between lexicons within N-neighborhood in the same lexicon level or across lexicon levels. In [88], experimental results show that considering words with low correlation in speech recognition making the performance poor. Empirically, Five-neighborhood is a best trade-off for accuracy and complexity. Therefore, we only generate knowledge links between two lexicons whose horizontal distance is within -5 to 5.

We refer to the new sentence confabulation model with these two changes as circular model as the knowledge links are circulated among lexicons.

Segmented and tagged training text is used during training. Characters, tags and segment labels are placed in corresponding lexicons. KLs are established not only between two lexicons in the same level, but also between lexicons in different levels, as long as their distance is less than 5. However, there is no KL between tag and segmentation label lexicons, because tags and segments are derivatives of the Chinese characters, and Stanford tools are not able to ensure 100% accuracy in tagging. Keeping KL between tag and segment lexicons will introduce noise in the confabulation procedure. A test sentence with missing characters will be given during recall. For those lexicons that are partially observable, a set of candidates that compliant with the partial observation is activated. If a lexicon is completely unobservable, then all possible symbols are activated as potential candidates. Since the test sentence originally is provided without tags and segmentation labels, the confabulation model automatically activates all tags and segmentation labels as possible candidates for each tag and segmentation label lexicon respectively.

# 2.3 Training and Recall Algorithm with Case Study

Given the confabulation model, the training and recall procedures are developed. The training process establishes knowledge base on tagged and segmented text. Taking following sentence "国  $\pm$ #NN (The king) 有#VE (has) 两#CD个#M (two) 儿子#NN (sons)" as example, the corresponding tagged and segmented training text is as follows, and the confabulation model constructed

Figure 2.1: Lexion Structure of confabulation model.

based on the training text is given in Figure 2.1.

As shown in Figure 2.1, a special symbol [^] is assigned to the first lexicon in each level. Those words that frequently appear at the beginning of a sentence will have strong link with this special symbol. The indication of beginning of sentence is especially important for circular model, because its knowledge base only contains relative position information. The beginning of sentence symbol acts as anchors that provide absolute position information. We can also see from Figure 2.1 that the sentence is extended to 20 characters that are symbols assigned to lexicons 0 to 19 respectively. Those 20 characters will generate 18 three-word triplets and be assigned to lexicons  $20 \sim 37$ , 20 tags and 20 segmentation labels will enter lexicons  $38 \sim 57$  and lexicons  $58 \sim 77$  respectively. At the end of training, the system will calculate the symbol to symbol conditional probability to fill in the KL matrix entry. For example,  $P("||\mathbf{E}|"|^*\mathbf{E}")$  will be stored as an entry in the KL connecting lexicons 1 and 2, and  $P("||\mathbf{E}|"|"NN")$  will be stored as an entry in the KL connecting lexicons 1 and 39.

During recall, sentences with missing characters will be given. Taking the same sentence in Figure 2.1 as example, Figure 2.2 gives a simple explanation

Figure 2.2: Lexion Structure of confabulation model (Any arrow is from source lexicon to target lexicon. Orange arrows represents Knowledge Links from observable lexicons to unobservable or partially observable lexicons; Green arrows represents Knowledge Links between lexicons in same level; Blue arrows represents Knowledge Links from unobservable or partially observable lexicons to observable lexicons).

how the model works. Assume that the third character " $\pm$ (king)" is partially observable, and the ambiguous observation gives two candidates: "' $\pm$ (king)" and " $\pm$ (labor)". Symbols in lexicons are activated according to the observation. Hence lexicon 2 has two symbols " $\pm$ (king)", " $\pm$ (labor)" activated. And since no tags and segmentation labels are provided for the test sentence, all tags and segmentation labels are activated in tag and segmentation label lexicons. The lexicons with only one candidate are regarded as known lexicons and others are regarded as unknown lexicons. Through KLs, active symbols in source lexicons will excite candidate symbols in target lexicons. Each candidate's excitation level is calculated based on equation 1.1. The least excited one is eliminated from candidate list and others are set to be active. It is noted that

no matter a source lexicon is known or not, as long as its candidates are set to be active, the active symbols will always excite the symbols in unknown lexicons. In this example, [^] in lexicon 0 will excite tag candidates in lexicon 38, and active symbols in lexicon 38 will then excite tag candidates in lexicon 40, while the active symbols in lexicon 40 excite candidates, " $\pm$ (king)", " $\pm$ (labor)" respectively in unknown lexicon 2. This procedure iterates so that unknown character will be determined gradually by eliminating weak candidates in unknown tag lexicons, segmentation lexicons and word triplet lexicons. Finally only one candidate is left in each lexicon and the candidate will be chosen as the most likely result and " $\pm$ (king)" is recalled for the missing character.

# 2.3.1 Knowledge Link Weighting

In the basic confabulation model, the excitation level of a candidate is the sum of contributions from active symbols in other lexicons. Intuitively, however, different source lexicons do not contribute equally to a target lexicon. For example, the lexicon right next to an unknown word obviously gives more information in determining the unknown word than the lexicon that is five words away. This motivates us to weight KL's contribution during recall.

The basic idea is to weight the contribution of each KL based on the *Mutual information (MI)* [133] between its source and target lexicons. Mutual information of two random variables is a measure of variables' mutual independence. In our work, mutual information is calculated as

$$I(A; B) = \sum_{b \in B} \sum_{a \in A} p(a, b) \log(\frac{p(a, b)}{p(a)p(b)})$$

(2.1)

where A is the source lexicon and a represents symbols in A; B is the target

lexicon and b represents symbols in B. p(a,b) is the joint probability of symbol a and b; p(a) and p(b) are the margin probability of symbol a and b respectively. I(A;B) is nonnegative. The value of I(A;B) will increase when the correlation of symbols in lexicon A and B get stronger. Because each knowledge link has its source and target lexicons, in the rest of the chapter when we say the MI of a KL we refer to the MI of the source and target lexicons of that KL.

#### 2.4 Evaluations

In this section, we compare the performance of different models and show how the analysis of mutual information can help to improve the efficiency of the confabulation modeling and recall. We train the Chinese confabulation model with a corpus of 10 sets of collected fairy and folk tales. We choose Chinese version of worldwide fairy tales such as Hans Christian Andersen's Fairytales, Grimm's Fairy Tales and also Chinese folk tales, because those works use vivid and common language, which will lead to a statistically meaningful knowledge base. The training set includes 364,709 sentences and 3,232,600 words, and is chunked into 1328 small files with equal size. The test document includes 91 sentences extracted from elementary school textbook on Chinese language art. Each test sentence has  $1 \sim 4$  randomly picked missing Chinese words. For each missing word,  $2 \sim 5$  possible candidates will be given. Accuracy is measured as the rate of successfully confabulated sentences, which must be identical to the original sentences.