#### **Syracuse University**

### **SURFACE**

Dissertations - ALL **SURFACE**

December 2015

## Design of a High Capacity, Scalable, and Green Wireless Communication System Leveraging the Unlicensed Spectrum

Mohammad Riaz Khawer Syracuse University

Follow this and additional works at: https://surface.syr.edu/etd

Part of the Engineering Commons

#### **Recommended Citation**

Khawer, Mohammad Riaz, "Design of a High Capacity, Scalable, and Green Wireless Communication System Leveraging the Unlicensed Spectrum" (2015). Dissertations - ALL. 393. https://surface.syr.edu/etd/393

This Dissertation is brought to you for free and open access by the SURFACE at SURFACE. It has been accepted for inclusion in Dissertations - ALL by an authorized administrator of SURFACE. For more information, please contact surface@syr.edu.

## **Abstract**

The stunning demand for mobile wireless data that has been recently growing at an exponential rate requires a several fold increase in spectrum. The use of unlicensed spectrum is thus critically needed to aid the existing licensed spectrum to meet such a huge mobile wireless data traffic growth demand in a cost effective manner. The deployment of Long Term Evolution (LTE) in the unlicensed spectrum (LTE-U) has recently been gaining significant industry momentum. The lower transmit power regulation of the unlicensed spectrum makes LTE deployment in the unlicensed spectrum suitable only for a small cell. A small cell utilizing LTE-L (LTE in licensed spectrum), and LTE-U (LTE in unlicensed spectrum) will therefore significantly reduce the total cost of ownership (TCO) of a small cell, while providing the additional mobile wireless data offload capacity from Macro Cell to small cell in LTE Heterogeneous Networks (HetNet), to meet such an increase in wireless data demand. The U.S. 5 GHz Unlicensed National Information Infrastructure (U-NII) bands that are currently under consideration for LTE deployment in the unlicensed spectrum contain only a limited number of 20 MHZ channels. Thus in a dense multi-operator deployment scenario, one or more LTE-U small cells have to co-exist and share the same 20 MHz unlicensed channel with each other and with the incumbent Wi-Fi.

This dissertation presents a proactive small cell interference mitigation strategy for improving the spectral efficiency of LTE networks in the unlicensed spectrum. It describes the scenario and demonstrate via simulation results, that in the absence of an explicit interference mitigation

mechanism, there will be a significant degradation in the overall LTE-U system performance for LTE-U co-channel co-existence in countries such as U.S. that do not mandate Listen-Before-Talk (LBT) regulations. An unlicensed spectrum Inter Cell Interference Coordination (usICIC) mechanism is then presented as a time-domain multiplexing technique for interference mitigation for the sharing of an unlicensed channel by multi-operator LTE-U small cells. Through extensive simulation results, it is demonstrated that the proposed usICIC mechanism will result in 40% or more improvement in the overall LTE-U system performance (throughput) leading to increased wireless communication system capacity.

The ever increasing demand for mobile wireless data is also resulting in a dramatic expansion of wireless network infrastructure by all service providers resulting in significant escalation in energy consumption by the wireless networks. This not only has an impact on the recurring operational expanse (OPEX) for the service providers, but importantly the resulting increase in greenhouse gas emission is not good for the environment. Energy efficiency has thus become one of the critical tenets in the design and deployment of Green wireless communication systems. Consequently the market trend for next-generation communication systems has been towards miniaturization to meet this stunning ever increasing demand for mobile wireless data, leading towards the need for scalable distributed and parallel processing system architecture that is energy efficient, and high capacity. Reducing cost and size while increasing capacity, ensuring scalability, and achieving energy efficiency requires several design paradigm shifts.

This dissertation presents the design for a next generation wireless communication system that employs new energy efficient distributed and parallel processing system architecture to achieve these goals while leveraging the unlicensed spectrum to significantly increase (by a factor of two) the capacity of the wireless communication system. This design not only significantly reduces the upfront CAPEX, but also the recurring OPEX for the service providers to maintain their next generation wireless communication networks.

## Design of a High Capacity, Scalable, and Green Wireless Communication System Leveraging the Unlicensed Spectrum

By

#### Mohammad R. Khawer

B.E. N.E.D. University of Engineering & Technology, Karachi, Pakistan, 1992M.S. Syracuse University, New York, U.S., 1995

#### **DISSERTATION**

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer and Information Science and Engineering (CISE)

Syracuse University

December 2015

Copyright © Mohammad R. Khawer 2015 All Rights Reserved "If you can dream - and not make dreams your master;

If you can think - and not make thoughts your aim;

If you can meet with Triumph and Disaster

And treat those two impostors just the same;"

- Rudyard Kipling, "A Father's Advice to his Son"

To my family, and the loving memory of my father, late Dr. Mohammad Ilyas

Akhter, who taught and inspired me to remain steadfast in the face of

adversity

## Acknowledgement

I would like to express my deepest and everlasting gratitude to all my teachers and mentors who were extremely kind and generous with their time and knowledge, without which I would not be where I am today.

To my advisor Professor Jian Tang, who continuously provided me with guidance and support, my greatest appreciation and thanks for his thought provoking insights and guidance that helped me tremendously in completing this dissertation work.

My deepest appreciation also goes to Professor Chilukuri K. Mohan (former Department Chair of EECS), and Dr. Nancy Cantor (former Chancellor of Syracuse University) for their help, and guidance in accomplishing this milestone.

I would like to thank my dissertation & research committee for their time, effort, consideration, and support in this entire endeavor.

I would also like to acknowledge the following Alcatel-Lucent colleagues for their guidance and support: Feng Han, Mugur Abulius, Lina So, and Shriram K. Easwaran.

My final and deepest gratitude goes to my parents, wife, kids, and siblings who stood by me with their love and encouragement without which nothing would have been possible. I dedicate this dissertation to you all.

## **Contents**

| Α  | bstrac                                                                  | t            |                                                                        | i   |  |

|----|-------------------------------------------------------------------------|--------------|------------------------------------------------------------------------|-----|--|

| С  | opyrig                                                                  | ht           |                                                                        | V   |  |

| Α  | cknow                                                                   | ledg         | ement                                                                  | vii |  |

| Li | st of F                                                                 | igure        | es                                                                     | X   |  |

| 1  | Introduction                                                            |              |                                                                        |     |  |

|    | 1.1 Bac                                                                 |              | ckground and Motivations                                               | 11  |  |

|    | 1.2 Rel                                                                 |              | ated Work and Literature Gap                                           | 13  |  |

|    | 1.3                                                                     | Cor          | ntributions and Claims of Originality                                  | 20  |  |

|    | 1.4                                                                     | Dis          | sertation Outline                                                      | 24  |  |

| 2  | Interference Mitigation for the LTE Networks in the Unlicensed Spectrum |              |                                                                        |     |  |

|    | 2.1                                                                     | Introduction |                                                                        |     |  |

|    | 2.2                                                                     | Sys          | stem Model and Problem Description                                     | 29  |  |

|    |                                                                         |              | icensed Spectrum Inter Cell Interference Coordination (usICIC)         | 33  |  |

|    | 2.3                                                                     | .1           | Overview                                                               | 33  |  |

|    | 2.3                                                                     | .2           | Workflow of the Proposed usICIC Mechanism                              |     |  |

|    | 2.4 Per                                                                 |              | formance Evaluation                                                    |     |  |

|    | 2.4.1                                                                   |              | Simulation Setup                                                       | 41  |  |

|    | 2.4.2                                                                   |              | Simulation Scenarios                                                   | 43  |  |

|    | 2.4.3                                                                   |              | Comparative Analysis of the Simulation Results                         | 45  |  |

| 3  |                                                                         |              |                                                                        |     |  |

|    | 3.1                                                                     | Use          | e of Open source Real Time Operating System (RTOS)                     | 50  |  |

|    | 3.2                                                                     | Use          | e of a Multicore processor                                             | 52  |  |

|    | 3.2.1                                                                   |              | Supervised Asymmetric Multi-Processing (S-AMP) Configuration           | 54  |  |

|    | 3.2.2                                                                   |              | Symmetric Multi-Processing (SMP) Configuration                         | 55  |  |

|    | 3.2.3                                                                   |              | Deterministic Symmetric Multi-Processing (D-SMP) Configuration         | 57  |  |

|    | 3.3 Por                                                                 |              | tability and Scalability Considerations                                | 59  |  |

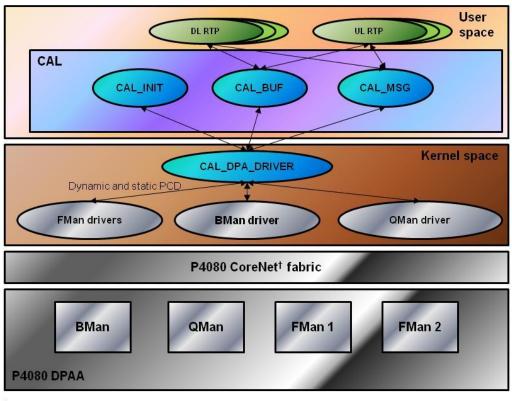

|    | 3.3.1                                                                   |              | Core Abstraction Layer (CAL)                                           | 61  |  |

|    | 3.4                                                                     | App          | olication Server Recovery Mechanism                                    | 64  |  |

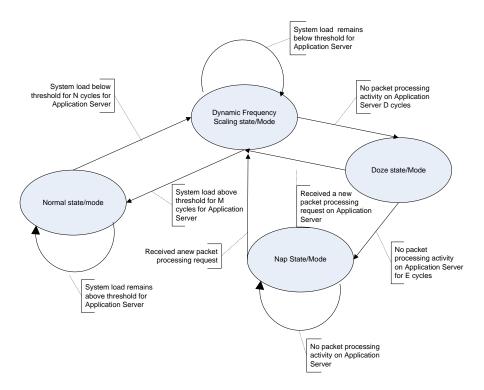

|    | 3.5                                                                     | Ene          | ergy Efficiency Considerations                                         | 67  |  |

|    | 3.5.1                                                                   |              | Energy Efficiency as a result of significant reduction in device coun- | t68 |  |

|    | 3.5.2                                                                   |              | Energy Efficiency as a result of Multicore Dynamic Power Control       | 69  |  |

|    | 3.5.3                                                                   |              | Energy Efficiency as a result of Disabling the LTE-U Service           | 75  |  |

| 3.6 |                                                                                                   | Testing and Performance Validation Considerations |                                                                             |     |  |  |  |

|-----|---------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------|-----|--|--|--|

| 4   | Co                                                                                                | Conclusions                                       |                                                                             |     |  |  |  |

| 4.1 |                                                                                                   | Со                                                | nclusions and Summary                                                       | 81  |  |  |  |

|     | 4.2                                                                                               | Fu                                                | Future Research Directions                                                  |     |  |  |  |

| 5   | Ap                                                                                                | Appendix                                          |                                                                             |     |  |  |  |

|     | 5.1 Appendix A – VxWorks                                                                          |                                                   | pendix A – VxWorks                                                          | 86  |  |  |  |

|     | 5.2 Appendix B – Open Source Linux with PREEMPT_RT                                                |                                                   | 87                                                                          |     |  |  |  |

|     | 5.3                                                                                               | Ap                                                | pendix C - Critical Section of Code, and software locks                     | 89  |  |  |  |

|     | 5.4                                                                                               | Ap                                                | pendix D – P4080 BMAN Initialization                                        | 92  |  |  |  |

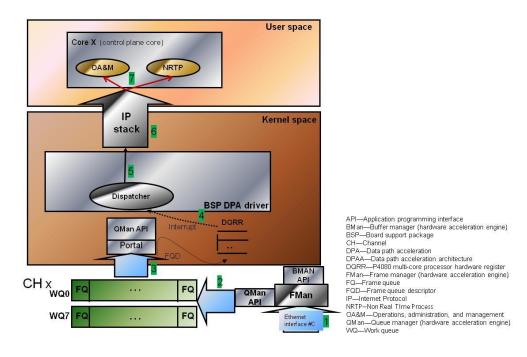

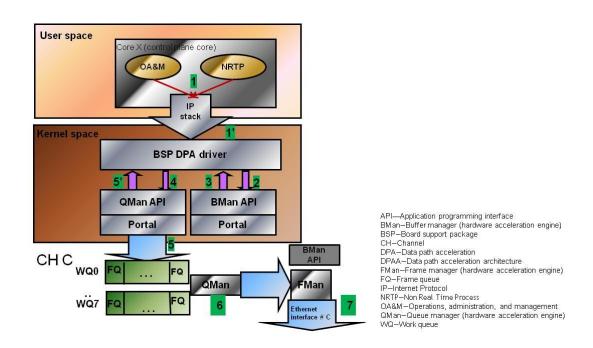

|     | 5.5 Appendix E – Standard P4080 DPAA configuration for IP packet process using the Protocol Stack |                                                   |                                                                             |     |  |  |  |

|     | 5.5.1                                                                                             |                                                   | Ingress Control Plane IP Packet processing                                  | 95  |  |  |  |

|     | 5.                                                                                                | 5.2                                               | Egress Control Plane IP Packet processing                                   | 96  |  |  |  |

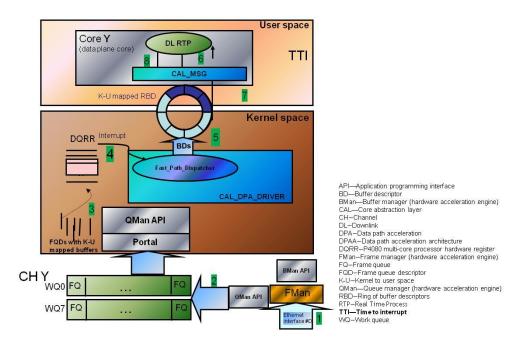

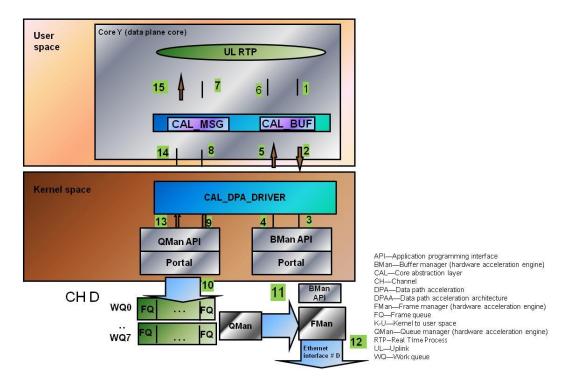

|     | 5.6<br>the F                                                                                      | •                                                 | pendix F – P4080 DPAA configuration for IP packet processing col Stack [36] | •   |  |  |  |

|     | 5.6                                                                                               | 5.1                                               | Ingress Data Plane IP Packet processing                                     | 98  |  |  |  |

|     | 5.6                                                                                               | 5.2                                               | Egress Data Plane IP Packet processing                                      | 101 |  |  |  |

|     | 5.7                                                                                               | Ap                                                | pendix G – P4080 QMAN Configuration [37]                                    | 103 |  |  |  |

| 6   | Bil                                                                                               | oliogr                                            | oliography105                                                               |     |  |  |  |

| 7   | Ab                                                                                                | Abbreviations, Acronyms, and Terms113             |                                                                             |     |  |  |  |

| 8   | Cı                                                                                                | Curriculum Vitae116                               |                                                                             |     |  |  |  |

# **List of Figures**

| Figure 1: Single Operator LTE-U Deployment Scenario in a Wireless HetNet     | 28  |

|------------------------------------------------------------------------------|-----|

| Figure 2: TCSAT Gating Cycle for LTE-U Channel Sharing with Wi-Fi            | 30  |

| Figure 3: Multi-Operator LTE-U Co-channel Interference Scenario              | 31  |

| Figure 4: Event Trace Diagram for the proposed usICIC Mechanism              | 35  |

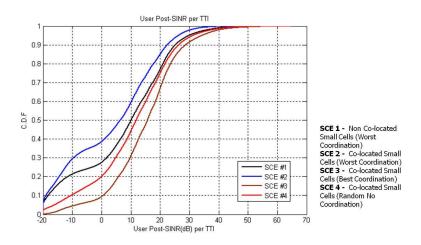

| Figure 5: LTE-U SINR Distribution Comparison                                 | 45  |

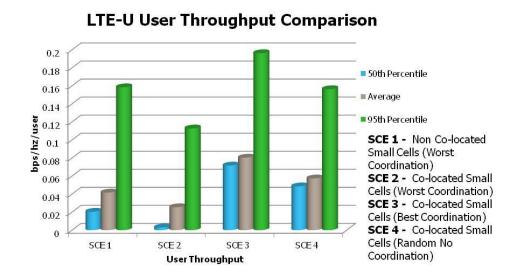

| Figure 6: LTE-U User Throughput Comparison                                   | 46  |

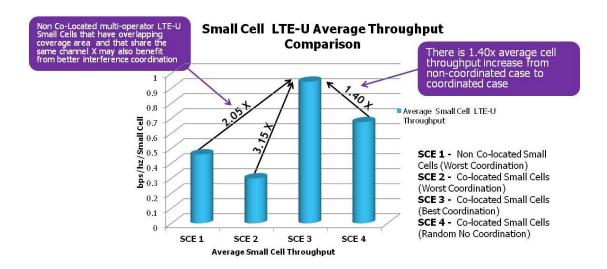

| Figure 7: LTE-U Small Cell Average Throughput Comparison                     | 47  |

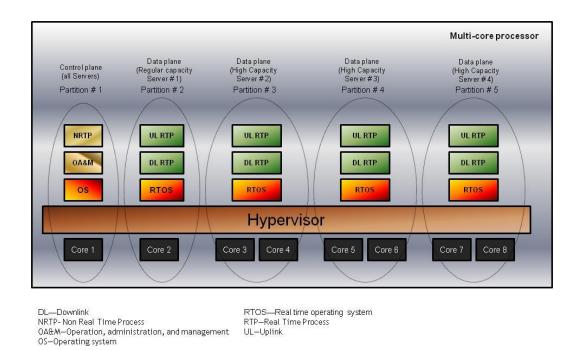

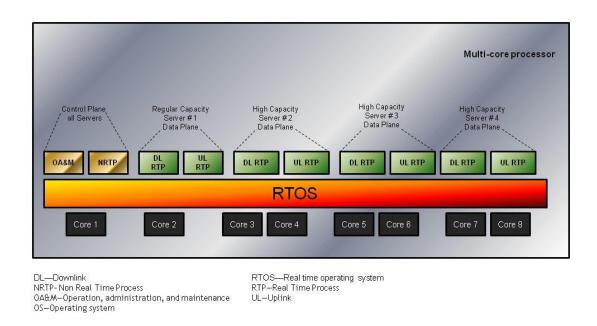

| Figure 8: Supervised Asymmetric Multi-Processing (S-AMP) Configuration       | 54  |

| Figure 9: Symmetric Multi-Processing (SMP) Configuration                     | 56  |

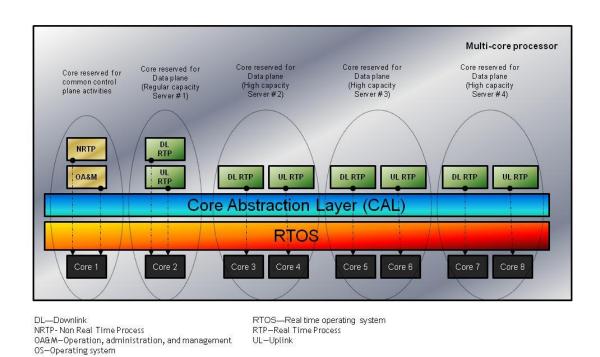

| Figure 10: Deterministic Symmetric Multi-Processing (D-SMP) Configuration    | 57  |

| Figure 11: Core Abstraction Layer Functional Architecture                    | 62  |

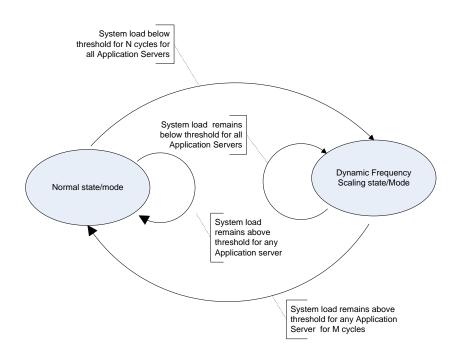

| Figure 12: DPC State machine for the dedicated data plane cores              | 71  |

| Figure 13: DPC State machine for the shared control plane core               | 75  |

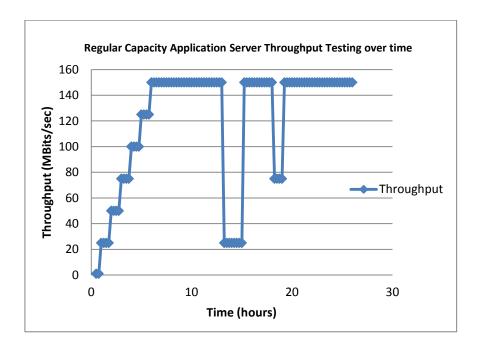

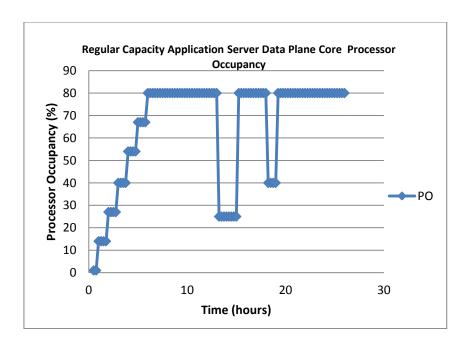

| Figure 14: Throughput Testing Rate over a Period of Time                     | 78  |

| Figure 15: Processor Occupancy Load Corresponding To Throughput Rate         | 79  |

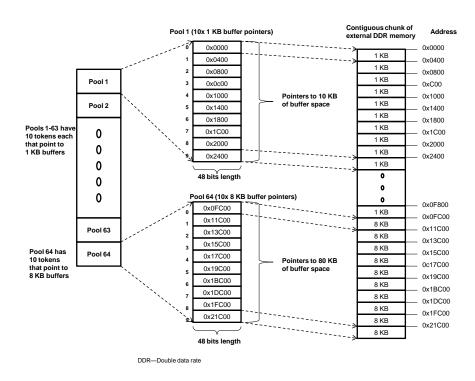

| Figure 16: P4080 BMAN Buffer Pool Seeding                                    | 93  |

| Figure 17: Ingress Control Plane IP Packet processing using Protocol Stack   | 96  |

| Figure 18: Egress Control Plane IP packet Processing using the Protocol Stac | k97 |

| Figure 19: Ingress Data Plane IP Packet Processing                           | 101 |

| Figure 20: Egress Data Plane IP Packet Processing                            | 103 |

# Chapter 1

## 1 Introduction

## 1.1 Background and Motivations

The ever increasing demand for mobile wireless data requires system design that is low cost, high capacity, flexible, scalable, and energy efficient with smaller size or foot print for building the next generation wireless communication systems. Even though the demand for mobile wireless data is increasing exponentially in recent years, but it is not translating into proportional increase in revenue for the service providers. It is therefore imperative for the service providers to look for energy efficient system design solutions that are aimed at reducing the average cost per bit of mobile wireless data transmitted by leveraging the unlicensed spectrum, to reduce the upfront capital expanses (CAPEX), and the recurring operational expenses (OPEX) for the wireless communication systems.

The use of unlicensed spectrum to aid the available licensed spectrum, allow a significant reduction in the total cost of ownership (TCO) of the wireless communication system for the service provider by increasing the overall system capacity in a cost effective manner. The licensed spectrum is not only limited, but extremely costly typically of the order of multi-billion dollars for each market segment that adds significantly to the upfront CAPEX for the service provider while deploying a wireless communication network.

The actual size or foot print of the wireless communication system has a direct impact on the recurring site leasing cost for the service provider for

the location where the wireless communication system is physically mounted or deployed. The overall power consumption of the wireless communication network is another key aspect of the recurring OPEX for the service providers, as tens of thousands of wireless communication systems are deployed to meet the ever growing mobile wireless data demand. These are some key design aspects that are driving the market trend towards system miniaturization using scalable distributed and parallel processing architecture that is low cost, high capacity, and energy efficient.

This dissertation presents in chapter 2, the research work related with improving the spectral efficiency of LTE networks in the unlicensed spectrum using a proactive small cell interference mitigation mechanism. More specifically an unlicensed spectrum Inter Cell Interference Coordination (usICIC) mechanism is presented, that significantly enhance the overall LTE-U system performance, and capacity for the wireless communication system.

This dissertation also presents in chapter 3, the research work related with system design using a new scalable distributed and parallel processing architecture that significantly reduce the device count by a factor of 14 to reduce the overall power consumption of the wireless communication system while providing higher system capacity (by a factor of two) by leveraging the unlicensed spectrum. It also employs a dynamic power control mechanism to continuously modules the clock speed of the individual processing cores of the multi-core processor used in the design, throughout the day depending upon the traffic load, in an attempt to reduce the power consumption to make the system even more energy efficient. Additionally while handling low traffic demand, the LTE-U service, and the radios corresponding to the unlicensed 5

GHz band may be completely turned off by the new design to achieve even higher energy efficiency.

Thus, the research work presented in this dissertation facilitate the design for building a commercial grade high capacity, scalable, and Green wireless communication system that leverages the unlicensed spectrum to reduce the upfront CAPEX, and the recurring OPEX for the service providers.

## 1.2 Related Work and Literature Gap

In this section, we describe below the state of the art related work and discuss the literature gap for the two research areas presented in the dissertation:

## Interference mitigation for the LTE networks in the unlicensed spectrum

The LTE and Wi-Fi coexistence in the unlicensed spectrum has been studied recently. In [6], the benefits of deploying LTE in the unlicensed spectrum and its potential co-existence with Wi-Fi were discussed. In [8], the need for proper co-existence mechanisms was explored to enable Wi-Fi, and LTE co-existence in the unlicensed spectrum. In [9], a Wi-Fi, and LTE co-existence mechanism that consisted of blanking some LTE subframes to improve Wi-Fi performance was discussed. In [10], the performance of LTE and Wi-Fi was compared in the unlicensed spectrum to demonstrate that in general, LTE outperforms Wi-Fi in similar scenarios. In [11], the use of LTE UL power control was presented to improve LTE and Wi-Fi coexistence. In [12], the performance of LTE and WLAN in a shared frequency band was evaluated. The study demonstrated that the

co-existence has a negative impact on WLAN system performance but it was reasoned that the severity of the impact can be controlled by restricting LTE activities. [12] Called for more careful co-existence mechanism studies to address this issue. [5] [24]-[27] provided in-depth analyses for LTE and Wi-Fi co-existence using carefully designed Carrier Sense Adaptive Transmission (CSAT) gating cycle mechanism for LTE-U transmissions in the unlicensed spectrum. These work that were done under the umbrella of the LTE-U Forum [23] demonstrated via simulation results that the CSAT mechanism will allow LTE to be a fair neighbor to Wi-Fi while sharing the same unlicensed channel by ensuring that the performance of the Wi-Fi AP is no worse than when it shares the same channel with another Wi-Fi AP.

The difference between the work presented in this dissertation and the other research works has been that the other research works have not studied and performed analysis for multi-operator LTE-U co-existence in the unlicensed spectrum while sharing the same unlicensed channel. The LTE-U Forum work [25]–[27] assumed that for the multi-operator LTE-U deployment scenario, the two LTE-U small cells will use different channels in the unlicensed spectrum. Since there are a limited number of channels in the 5 GHZ unlicensed spectrum, the probability of two LTE-U small cells sharing the same unlicensed channel in a dense multi operator deployment scenario is very high. We have demonstrated via detailed LTE system level simulations that overall system performance degrades significantly when two LTE-U Small cells share the same unlicensed channel without any CSAT gating cycle coordination. We have proposed

an unlicensed spectrum Inter Cell Interference Coordination (usICIC) mechanism to allow the multi-operator LTE-U small cells to negotiate orthogonal (non-overlapping) CSAT gating cycles for their respective LTE-U transmissions while sharing an unlicensed channel to drastically improve (by 40% or more) the overall LTE-U system performance as validated by the simulation results. This work has resulted in one IEEE publication [45], and one LTE-U Forum technical contribution [46].

Interference migration has been studied in the context of cognitive radios. In [28], the authors surveyed the fundamental capacity limits and associated transmission techniques for different wireless network design paradigms using cognitive radios. Power allocation strategies were proposed in [29], which could be employed for the coexistence of one or more cognitive radios with a primary radio where the cognitive radios transmit in a spectrum allocated to the primary radio. In [30], the authors proposed an underlay spectrum sharing policy for a point-to-point link of cognitive radios to leverage uplink spectrum resource of the primary network, and demonstrated that such an uplink band sharing mechanism could enhance the throughput performance of point-to-point link, while the interference to the primary users could be regulated under the allowed level decided by the primary users. In [47], the authors studied the green cognitive mobile networks with small cells in the smart grid environment. Unlike most existing studies on cognitive networks, where only the radio spectrum is sensed, their proposed cognitive networks sense not only the radio spectrum environment, but also the smart grid environment, based on which power allocation and interference management for multimedia

communications are performed to significantly reduce the operational expenditure and CO2 emissions.

Unlike cognitive radios, the LTE-U small cell operates in the unlicensed spectrum where there is no concept of the primary user. Upon detecting another node's (Wi-Fi or LTE-U) presence on the unlicensed channel, the LTE-U small cell does not necessarily switch its operation to another unlicensed channel, but rather attempts to co-exist with the other nodes and share the unlicensed channel in TDM fashion.

Interference mitigation has been an important area of research for the licensed spectrum as well. In [48], the authors have concluded that Inter Cell Interference Coordination (ICIC) must be effectively used to reduce the mutual interference of edge users in heterogeneous network (Het-net), where the interference scenario becomes more complicated They analyzed the limitation of traditional ICIC, and proposed a novel ICIC method based on User' position for the improvement of the downlink ICIC efficiency. In [49], the authors presented a decentralized subcarrier collision arbitrating algorithm among adjacent cells, and proved it to be distributed and collision free. Based on this algorithm, the authors proposed an ideal synchronous ICIC method and a more practical asynchronous ICIC method, which utilized the information exchange capability among adjacent cells provided by the new systems. In [50], the authors have analyzed the limitation of the traditional ICIC method, and proposed an improved priority based ICIC method in order to improve the efficiency in LTE-Advanced systems.

Interference mitigation in the licensed spectrum is mainly focused on enhancing the cell edge spectrum efficiency, and deals with the same operator cells in a wireless HetNet. In the unlicensed spectrum since the same channel is being shared by multiple operator's LTE-U Small Cell, the interference mitigation has to be achieved by coordination across the Small Cells of multiple operator such as our proposed usICIC mechanism, that enhances the system performance not just for the edge users, but rather for all the users that are within the overlapping coverage area of the multi-operator LTE-U Small Cells.

#### High Capacity, Scalable, and Energy Efficient Design

A multi-core processor is typically used to replace several individual processors for a high performance embedded distributed, and parallel processing system architecture design. A lot of research work has been published that evaluated the two possible multi-core processing configurations, and highlighted the superiority of asymmetric multi-processing (AMP) configuration that has deterministic execution behavior but lacks scalability, over non deterministic but scalable symmetric multi-processing (SMP) configuration, while designing high performance embedded distributed, and parallel processing systems. In [51], the characteristics and implementation of asymmetric multi-processing (AMP) framework in humanoid robot is discussed. The proposed framework was used to replace computer network as the high level processing unit for the humanoid robot that was designed to perform object localization based on visual and auditory information. In this AMP framework, a multi-core

computer was divided into several smaller virtual machines that owned a part of the physical resources including processing core, memory and input/output (I/O) devices. Each virtual machine executed a guest operating system (OS) and dedicated applications. Xen paravirtualization technology was used to conveniently manage these guest operating systems. In [52], the authors provided a discussion on the issues related with the design of embedded multi-processor systems, with the focus on DSP-based systems. Issues that were discussed in this paper included indicators of when applications would scale into multi-core processors designs, Central Processing Unit (CPU) benchmarking, partitioning and the applicability of symmetric multi-processing (SMP) and asymmetric multi-processing (AMP) architectures on embedded DSP based multiprocessor design. In [53], the authors presented the case that embedded appliances such as high end cell phones require not only high but also a performance guarantee. The performance. demonstrated a performance guarantee framework using asymmetric multi-processing (AMP) approach using a multi-core processor, and backed it by providing evaluation results to show that the framework improved the performance guarantee while maintaining software compatibility. In [54], the authors provided a detailed study of the performance issues associated with symmetric multi-processing (SMP) configuration on a multi-core processor. These issues included memory bandwidth restrictions for memory intensive applications; the use of software locks by existing SMP operating system to manage complex shared data structures. In [55], the authors highlighted the fact that writing

parallel software effectively for embedded systems is not an easy task. The authors believed that a new approach was needed to maximize the performance speed-up, and proposed a layered top-down model for parallel embedded software, based on their pattern language for high-performance computing. Several case studies were developed to demonstrate the strength of the proposed model and in one such case study a telecommunication system was migrated from a naive symmetric multi-processing (SMP) setup to an asymmetric multi-processing (AMP) set-up to demonstrate the performance enhancements.

The difference between the work presented in this dissertation, that has also resulted in an IEEE publication [40], and the other published research works has been that prior to our research work there was no precedence of combining the non real time control plane, and the real time sensitive data planes of one or more application servers of a wireless communication system on a single partition comprising of one or more processing cores of a multi-core processor, to be served by a single instance of an open source real time operating system. Our proposed new high performance distributed and parallel processing system configuration for multi-core processors that we called "Deterministic Symmetric Multiprocessing (D-SMP)" configuration, provides the desired deterministic execution behavior of the AMP configuration while offering the equally desired scalability feature of the SMP configuration where the number of processor partitions and consequently the number of operating system instances do not vary with the number of application servers configured in the system. We have also demonstrated in this dissertation how our

proposed D-SMP configuration may be used for the design of a commercial grade high capacity next generation wireless communication system.

## 1.3 Contributions and Claims of Originality

The material presented in this dissertation has so far resulted in two IEEE publications [40] [45], LTE-U Forum technical contribution [46], and several patent applications. Our specific contributions towards each of the research work presented in this dissertation are as follow:

## Interference mitigation for the LTE networks in the unlicensed spectrum

Our contribution (IEEE publication [45], LTE-U Forum technical contribution [46]) for this research work is summarized as follows:

- We present the LTE and Wi-Fi co-existence mechanism as proposed by LTE-U Forum [23], and define the deployment scenario that will result in overall degraded LTE-U system performance as a result of multi-operator LTE-U co-channel co-existence in non-LBT regions.

- We propose an unlicensed spectrum Inter Cell Interference Coordination (usICIC) mechanism to significantly improve the overall LTE-U system performance for multi-operator LTE-U co-channel coexistence in non LBT regions.

- We demonstrate by extensive simulation results that the proposed usICIC mechanism will result in 40% or more improvement in overall LTE-U system performance.

The LTE-U service and the associated radios corresponding to the 5 GHz unlicensed spectrum may be opportunistically turned off to make the communication system energy efficient while dealing with low traffic demand.

#### High Capacity, Scalable, and Energy Efficient Design

An IEEE publication [40] presents the research work related with the new scalable distributed and parallel processing system architecture that may be employed in designing the next generation Green wireless communication system. This research work encompasses the following design artifacts:

- For the very first time in the history of wireless industry, the control plane, and the time sensitive data planes of all configured application servers including the ones leveraging the unlicensed spectrum are consolidated under a single Deterministic-SMP partition comprising of all the cores of a multicore processor, and being served by a single open source real time operating system (RTOS) instance. A patent [33] has been granted by the U.S. patent office for this radical and innovative design idea.

- To design a communication system of varying sizes the choice of the multicore processor with more or less cores may vary depending upon the specific communication system capacity, and cost targets. Thus software portability becomes an important design consideration especially for the application software. The Core abstraction layer (CAL) has been introduced that abstracts or hides the hardware

- specific details from the application software to address this design goal.

- In a single partition Deterministic-SMP configuration the control plane (non-real time threads/processes) and the data plane (real time threads/processes) share the same operating system instance even though they are bound to run on different cores. In such a configuration, a system software lock taken by a non-real-time process or thread on one core may cause a latency spike for a real time thread or process waiting for that lock to be released on a different core. Thus there was a need for a custom Lock-less Zero copy Buffer management service as an alternative to the native RTOS buffer management service provided by the open source RTOS, to meet the performance criteria essential for commercial deployment.

- The protocol stack of the chosen RTOS SMP Linux with PREEMPT\_RT is not designed to be 100% guaranteed lock-less. This may result in serious performance implications for the time sensitive process or threads of the application server running on the data plane cores to use the Linux protocol stack to send or receive TCP/UDP IP packets. Since the non real time processes, and threads of the control plane also use this protocol stack, the performance implication in an SMP environment result from the fact that a spinlock taken by a non-real-time process or thread on one core (such as found on the control plane core) may cause an unbounded latency spike or busy waiting for a real time thread or process waiting for that lock to be released on a different core (such as found on the data plane core). These

unbounded latency spikes are handled well by the control plane applications (OA&M etc), but result in the breakdown of the data plane applications that have very stringent real time performance requirements. Thus there was a need for a custom lock-less zero copy messaging service in a multicore SMP environment for use by the real time process or threads running on the data plane cores to send or receive TCP/UDP IP packets without the use of the SMP Linux protocol stack.

- A performance optimization scheme on the data plane cores was needed that significantly reduced the number of interrupts, and the resulting context switch overheads on the data plane cores. This enhancement increased the processing capabilitites of the application servers on the data plane cores for increased system capacity.

- High system availability is a key performance criterion required for the commercial deployment. Since multiple application servers share the same multicore processor, the recovery mechanism for a failed application server could no longer use a processor reboot. An elaborate application server recovery mechanism has thus been defined, that performs application server recovery without affecting the other operational configured application servers in the communication system that shared the same single partition D-SMP configuration. A patent [38] has been granted by the U.S. patent office for this design artifact.

- This design drastically reduces the device count used in wireless communication systems by a factor of 14 to make it energy efficient.

Additionally a method and system for dynamic power control has been defined that further reduces the power consumption of the multicore processor by up to 30% throughout the day by modulating the clock speed of the individual cores and operating them at less than maximum clock speed depending upon the system load on each configured application server.

#### 1.4 Dissertation Outline

The rest of the dissertation is organized as follows:

In chapter 2, we present our research work related with improving the spectral efficiency of LTE networks in the unlicensed spectrum using a proactive small cell interference mitigation mechanism. The technical content of this chapter has been captured in a research paper [45] that has been accepted for publication in an upcoming edition of the IEEE Transactions on Wireless communications. This chapter describes our proposed unlicensed spectrum Inter Cell Interference Coordination (usICIC) mechanism for enhancing the overall LTE-U system performance by 40% or more.

In Chapter 3, we present the research work that deals with defining a distributed and parallel processing system design that leverages the unlicensed spectrum, and results in a low cost, high capacity, flexible, scalable, and energy efficient architecture for building the next generation communication systems. A number of viable system designs are presented, and the rationale behind the chosen and the rejected design are discussed in this chapter. This chapter also discusses the portability, scalability, application server recovery, and energy efficiency considerations associated with the proposed system design.

In chapter 4, a discussion on the conclusion and summary for the dissertation research works, and future research directions are presented.

In Chapter 5, a number of appendixes with supporting information have been provided. Appendix A provides some high level information about the industry leading real time operating system VxWorks. **Appendix B** provides some high level information about Open Source Linux with PREEMPT RT. **Appendix C** provides some high level information about Critical Section of Code, and software locks. **Appendix D** provides a discussion on the multicore processor P4080 hardware acceleration engine Buffer Manager (BMAN) buffer Initialization. Appendix E provides a discussion on the multicore processor P4080 Data Path Acceleration Architecture (DPAA) configuration for IP packet processing using the Protocol Stack as defined by the Board Support package (BSP) provided by the OS vendor. Appendix F provides a discussion on the multicore processor P4080 Data Path Acceleration Architecture (DPAA) configuration for IP packet processing without using the Protocol Stack by augmenting the Board Support package (BSP) provided by the OS vendor. Appendix G provides a discussion on the multicore processor P4080 hardware acceleration engine Queue Manager (QMAN) configuration.

Chapter 6 provides a list of the references used in this dissertation.

Chapter 7 provides a list of the abbreviations, acronyms, and terms used in this dissertation.

# Chapter 2

## 2 Interference Mitigation for the LTE Networks in the Unlicensed Spectrum

#### 2.1 Introduction

The demand for mobile wireless data is growing at an exponential rate in recent years. Industry is preparing for what is being labeled as the 1000x data traffic growth in the coming years. To meet such a stunning demand a several fold increase in spectrum [15] [16] is needed. The use of unlicensed spectrum is thus critically needed to aid the existing licensed spectrum to meet such a huge mobile wireless data traffic growth demand in a cost effective manner. Currently the unlicensed 5 GHZ band is used by Wi-Fi [13] [18]-[22] capable devices such as smart phones, laptops and tablet PCs. Wi-Fi 802.11 n/ac protocols are suitable for interference free environment, but offer unpredictable Quality of Service (QoS) and degraded performance in interference limiting environment, which are considered far inferior to those offered by licensed cellular wireless technologies such as LTE [14] [17] that offers higher spectral efficiency [10].

The support for LTE in the unlicensed 5 GHZ band where it has to coexist with Wi-Fi, and where the LTE carrier is transmitted according to the lower transmit power requirements of the unlicensed spectrum, makes it suitable only for Small Cell deployments. A small cell utilizing LTE-L (LTE in licensed spectrum), and LTE-U (LTE in unlicensed spectrum) will therefore significantly reduce the total cost of ownership (TCO) of the small cell for the service provider. LTE-U capable small cell will have a lower cost per bit of wireless data transmitted, while providing the additional mobile wireless data offloading capacity from Macro Cell to small cell in LTE Heterogeneous Networks (HetNet).

LTE-U is a solution developed based on 3GPP LTE Rel-10/11/12, with implementation-based approach at the eNodeB to properly address the coexistence issue. This solution applies to regions such as U.S., Korea, and India that do not mandate Listen-Before-Talk (LBT) regulations. To harmoniously co-exist with the incumbent Wi-Fi, LTE-U employs channel selection and LTE-U ON/OFF period in a carrier sense adaptive transmission (CSAT) duty cycle co-existence mechanism to share the unlicensed channel in TDM manner with Wi-Fi and other operators' LTE-U deployments. The LTE-U Technical Specifications were defined and published in March 2015 by the LTE-U Forum that includes as key participating members Verizon, Alcatel-Lucent, Ericsson, LG Electronics, Qualcomm Technologies, and Samsung. The commercial deployment of LTE-U based solution is expected to happen during the second half of 2016.

The basic mode of LTE operations in the unlicensed spectrum is the Supplemental Downlink (SDL) [5]. In this mode of operations the Best Effort (BE) user data in downlink is carried over the unlicensed secondary carrier also known as SCell. All control and uplink user data is carried over the anchor primary LTE licensed carrier also known as PCell. The licensed PCell and the unlicensed SCell are employed by the small cell, and the User Equipments (UEs) in the Carrier Aggregation (CA) mode.

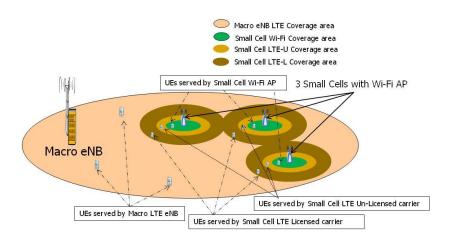

Figure 1 depicts the single operator wireless HetNet deployment scenario comprising of a Macro Cell, and three Wi-Fi, and LTE-U capable small cells. Wi-Fi coverage area is uplink (UL) limited due to the lower device uplink transmit power requirement in the unlicensed spectrum. On the other hand, LTE-U transmission is Supplemental Downlink (SDL) only, and all uplink control and critical data is transmitted via the anchor licensed LTE-L carrier (PCell), thereby increasing the LTE-U effective coverage area relative to the Wi-Fi coverage area for the same small cell.

Figure 1: Single Operator LTE-U Deployment Scenario in a Wireless HetNet

The limited number of available 20 MHZ channels in the 5 GHZ unlicensed spectrum will therefore require channel sharing among Wi-Fi APs, and LTE-U small cells in a dense multi operator deployment scenario.

Studies have been published [5]-[7] to demonstrate not only the viability of LTE deployment, but also its harmonious co-existence with Wi-Fi in the unlicensed spectrum. The published LTE and Wi-Fi coexistence performance studies [5] [6] [9] [11] have demonstrated that using carefully designed co-existence mechanism, LTE can be a fair neighbor to Wi-Fi that

does not degrade the Wi-Fi AP performance more than when the Wi-Fi AP share and co-exist with another Wi-Fi AP on the same unlicensed channel.

However, none of the published literature has so far examined the impact on the overall LTE-U system performance due to the interference resulting from multi-operator LTE-U channel sharing. In this dissertation, we study this key aspect, and quantify and highlight the need for an explicit interference mitigation mechanism for multi-operator LTE-U channel sharing for countries such as U.S., that do not mandate the LBT requirements for operations in the unlicensed spectrum.

The rest of the chapter is organized as follows. In Section 2.2, we present the system model and problem description for multi-operator LTE-U co-channel co-existence scenario that employs the LTE and Wi-Fi coexistence mechanism in the unlicensed spectrum as proposed by the LTE-U Forum. In Section 2.3 we present our proposed usICIC mechanism for enhancing multi-operator LTE-U co-channel co-existence scenario performance. In Section 2.4, we provide performance evaluation by describing the simulation setup, scenarios, results, and the corresponding analysis.

## 2.2 System Model and Problem Description

As part of the technical specifications released for the deployment of LTE-U, the LTE-U Forum [23] has proposed CSAT [5] [24] [25] to be used as the non LBT co-existence mechanism for the harmonious co-existence of LTE with Wi-Fi in the unlicensed spectrum. The CSAT mechanism allows the LTE-U small cell share an unlicensed channel with Wi-Fi in a Time-Division-Multiplexing (TDM) manner. In this adaptive transmission scheme, the LTE-U

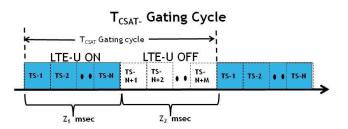

small cell employs a transmission gating cycle  $T_{CSAT}$  with a LTE-U ON/OFF duty cycle (Figure 2) to co-exist with Wi-Fi APs in a fair manner on the same unlicensed channel. The  $T_{CSAT}$  gating cycle is divided into Transmission Time Interval (TTI) or timeslots, each of which is a millisecond or sub-frame wide. Thus N timeslots or sub-frames for LTE-U ON ( $Z_1$  msec), and another M timeslots or sub-frames for the LTE-U OFF ( $Z_2$  msec) pattern (Figure 2). For the case of  $T_{CSAT}$  gating cycle with 50% duty cycle, N = M.

Figure 2: TCSAT Gating Cycle for LTE-U Channel Sharing with Wi-Fi

The CSAT mechanism works well for LTE and Wi-Fi co-existence, because the co-channel Wi-Fi backs off during the LTE-U ON transmission period of the T<sub>CSAT</sub> gating cycle due to the Carrier Sense Multiple Access (CSMA) nature of its Medium Access Control (MAC) layer. By using an appropriate duty cycle (e.g., 50%) for the CSAT transmission gating cycle (T<sub>CSAT</sub>), LTE-U small cell ensures that it leaves at least 50% of the channel for Wi-Fi use thereby ensuring a proper TDM sharing of the channel with Wi-Fi. However, an uncoordinated use of CSAT transmission gating cycle does not work well for multi-operator LTE-U small cells co-channel co-existence scenario, mainly because none of the LTE-U small cells sharing the channel backs off to each other's LTE-U transmissions during their respective LTE-U ON period of the gating cycle. This situation is exacerbated when each of

them use overlapping  $T_{CSAT}$  gating cycles for their LTE-U operations. If there is no coordination between multi-operator LTE-U small cells for the use of the LTE-U transmission gating cycle  $T_{CSAT}$  for co-channel LTE-U co-existence, it will result in overall degraded LTE-U system performance. The two LTE-U small cells that are either co-located or non-co-located with overlapping coverage area may each independently select an overlapping LTE-U transmission gating cycle. This will result in severe interference to their LTE-U users in the overlapping coverage area of the two LTE-U small cells for the duration of the overlapped LTE-U transmission gating cycle.

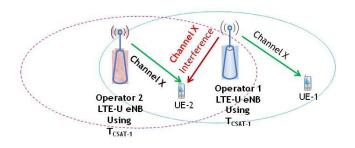

Figure 3: Multi-Operator LTE-U Co-channel Interference Scenario

Figure 3 depicts such a multi-operator LTE-U small cell deployment scenario, where Operator 1 LTE-U small cell and operator 2 LTE-U small cell each select the same unlicensed 5 GHZ Channel X and also use non-coordinated overlapping LTE-U transmission gating cycle for their LTE-U SDL operations. UE-1 is being served by operator 1 LTE-U small cell, and UE-2 is being served by operator 2 LTE-U small cell. The Operator 1 LTE-U small cell SDL transmission to UE-1 will result in interference to UE-2 during its simultaneous SDL operations with its serving Operator 2 LTE-U small cell for

the duration of the overlapped LTE-U T<sub>CSAT</sub> gating cycle, and will subsequently impact the LTE-U system throughput performance.

Let's denote  $\mathbf{S}_{i,j,k,t}$  as the received signal power at the  $i^{th}$  user from its serving LTE-U small cell j, of operator k at TTI t of the  $T_{CSAT}$  gating cycle, and  $\mathbf{N}_{thermal}$  is the thermal noise at  $i^{th}$  user. Let's use  $\mathcal{O}(t)$  to denote the set of interfering nodes (Wi-Fi or LTE-U) transmitting during a TTI t of the  $T_{CSAT}$  gating cycle on the unlicensed channel X. A node I is part of the interfering nodes set  $\mathcal{O}(t)$  only if it is transmitting at TTI t. The aggregate interference  $\mathbf{I}_{i,j,k,t}$  or the received signal power from the interfering nodes I in set  $\mathcal{O}(t)$  at the  $I^{th}$  user that is being served by LTE-U small cell I of operator I at TTI I can be represented by  $\sum_{t \in \mathcal{O}(t)} I_{i,j,k,t,t}$ .

Instantaneous signal to interference plus noise (SINR) ratio [24] for a given TTI t reflects instantaneous received signal powers from different transmitting nodes. Unlike Wi-Fi, LTE-U SINR distribution is independent of decoding. Thus, the SINR for the t user served by LTE-U small cell t of operator t for a TTI t is defined by:

$$SINR_{i,j,k,t} = \frac{S_{i,j,k,t}}{N_{thermal} + \sum_{l \in \emptyset(t)} I_{i,j,k,l,t}} \qquad ----- (1)$$

Thus for the multi-operator LTE-U co-channel interference scenario depicted in Figure 3, the higher interference level  $\mathbf{I}_{i,j,k,t}$  during the overlapping portion of the LTE-U ON period of the  $\mathbf{T}_{CSAT}$  gating cycle of the nearby LTE-U small cells will result in lower  $SINR_{i,j,k,t}$ , leading to degraded LTE-U system performance.

To address this co-channel LTE-U interference issue, and to enhance the overall LTE-U system performance (throughput gains) in non-LBT unlicensed spectrum, there is a need for an explicit LTE-U Inter Cell Interference Co-ordination mechanism. We present such a mechanism in the next section that will facilitate the coordination and usage of orthogonal non-overlapping LTE-U transmission gating cycles between adjacent multi-operator small cells that co-exist on the same unlicensed channel X (e.g., channel 149 in the 5GHZ band), for their LTE-U SDL operations.

# 2.3 Unlicensed Spectrum Inter Cell Interference Coordination (usICIC) Mechanism

#### 2.3.1 Overview

The main goal of our proposed usICIC mechanism is to reduce the inter-cell interference and enhance the overall system performance for the multi-operator LTE-U co-channel co-existence scenario. When two or more LTE-U small cells with overlapping coverage area, share an unlicensed channel for their respective LTE-U SDL operations, the usICIC mechanism enables them to negotiate with each other, over the backhaul X2 eNodeB signaling interface [3], the use of non-overlapping CSAT transmission gating cycle of appropriate duty cycle. Thus, when one LTE-U small cell is transmitting during its LTE-U ON period of the CSAT transmission gating cycle, the other LTE-U small cells sharing the same channel will be quiet (or OFF) leading to significant reduction in interference ( $\mathbf{I}_{i,j,k,t}$ ) to their users ( $\mathbf{f}^{th}$  user of serving small cell  $\mathbf{f}$  of operator  $\mathbf{K}$  at TTI  $\mathbf{f}$  of the CSAT gating cycle) throughout the overlapping coverage area of the LTE-U small cells.

When the LTE-U transmission gating cycles of two co-located or nearby multi-operator small cells that share the same channel X, is perfectly aligned, it will result in the worst case interference for LTE-U co-channel co-existence scenario. However, when the small cells employ orthogonal non-overlapping LTE-U transmission gating cycle via an inter cell coordination mechanism such as uslCIC it will result in the best case interference mitigation scenario for multi operator LTE-U co-channel co-existence.

Since the small cells of different operators will not be time synchronized across the same sub-frame boundary, during the CSAT gating cycle coordination process the adjacent small cells will also establish the start of each other's transmission gating cycle relative to their own sub-frame boundaries in an attempt to achieve as orthogonal a transmission gating cycles as possible with minimum overlap. For the non-coordinated scenario that does not employ usICIC mechanism, the level of LTE-U transmission gating cycle overlap between the two small cells will be a random distribution between the worst case (perfectly aligned and completely overlapping) and best case (orthogonal non-overlapping) scenarios. Consequently, the actual interference level and the resulting LTE-U system performance will be somewhere within the two extreme boundary conditions of worst case, and best case co-ordination scenarios.

#### 2.3.2 Workflow of the Proposed usICIC Mechanism

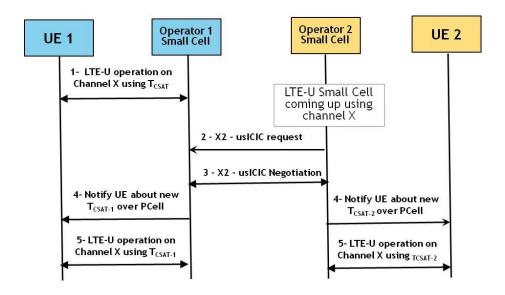

Figure 4 depicts the event trace diagram of our proposed usICIC mechanism with high level description for each step involved in the usICIC mechanism.

Figure 4: Event Trace Diagram for the proposed usICIC Mechanism

- In Step 1, operator 1 small cell is performing LTE-U SDL operations with UE 1 on unlicensed channel X (e.g., channel 149 in the 5GHZ band).

- In **Step 2**, as operator 2's small cell starts to initiate its LTE-U operations, its channel selection algorithm picks channel X for its LTE-U operations. Upon detecting the presence of other operator (operator 1) LTE-U small cell on the same channel X, operator 2 small cell initiates the uslCIC request with Operator 1 small cell over the backhaul eNodeB X2 signaling interface.

- In Step 3, the two small cells then exchange relevant information (such as number of Wi-Fi AP nodes presence on the channel X, number of LTE-U small cell nodes presence on Channel X, the timing information to notify

each other about the start of their sub-frame boundaries etc) over the backhaul X2 eNodeB signaling interface, to negotiate and determine as orthogonal a T<sub>CSAT</sub> gating cycle as possible of appropriate duration for their LTE-U operations to share the channel X in time domain.

- In **Step 4**, the two small cells notify their respective serving UEs about the beginning and end of the negotiated LTE-U ON period of the CSAT gating cycle from step 3, by the activation/deactivation of the unlicensed secondary carrier (SCell) using existing 3rd Generation Partnership Project (3GPP) standards based MAC (Medium Access control) channel element signaling over the primary carrier that is anchored in the licensed spectrum (PCell). This allows the UEs to know when to expect the LTE-U SDL transmission (LTE-U ON period of the T<sub>CSAT</sub> gating cycle) form their serving LTE-U small cell.

- In Step 5, the two small cells initiate their LTE-U SDL operations with their respective users (UEs) while causing minimal to no interference to each other's LTE-U SDL operations with users in their overlapped coverage area.

If channel X is only shared by two LTE-U small cells, the negotiated orthogonal (non-overlapping) T<sub>CSAT</sub> gating cycles for the two LTE-U small cells cannot use the entire 100% time duration of channel X. Some portion of the channel usage time has to be left free of any LTE-U activity to allow a nearby Wi-Fi AP to sneak in, and share the channel as well. In such a case, the number of nodes sharing channel X will change from 2 to 3 (Two LTE-U small cells, and one Wi-Fi AP). This change in channel node usage will trigger another round of uslCIC negotiations between the two LTE-U small cells that

would result in the two LTE-U small cells using orthogonal CSAT gating cycle that use one third of the available channel time.

The uslCIC mechanism applies equally for the scenario where the same unlicensed channel is shared by more than two LTE-U small cells, such as the case where an unlicensed channel is shared e.g., by three LTE-U small cells, and a Wi-Fi AP. Using the uslCIC mechanism the three LTE-U small cells may each negotiate the use of their respective orthogonal non overlapping CSAT gating cycle that use one fourth of the available channel time, while leaving 25% of the channel time exclusively for use by the Wi-Fi AP, thereby reducing interference for all nodes sharing the unlicensed channel.

The goal of our proposed interference mitigation usICIC mechanism is to minimize  $\mathbf{I}_{i,j,k,t}$  by reducing the interference caused by two or more co-channel LTE-U small cells to each other's LTE-U SDL operations. The use of the orthogonal non- overlapping CSAT transmission gating cycle by each co-existing LTE-U small cell on the same unlicensed channel will result in better SINR distribution, which will lead to higher user (50<sup>th</sup> percentile, Average, 95<sup>th</sup> percentile) and small cell system throughputs on the unlicensed carrier. The improvement in SINR distribution results from the fact that when one LTE-U small cell j is transmitting during a TTI t of its LTE-U ON transmission gating cycle, the other LTE-U small cells that share the same unlicensed channel X, will not be simultaneously transmitting, and will thus not cause interference to the users served by the LTE-U small cell j of operator k.

The uslCIC handshake mechanism is triggered only when a new LTE-U small cell starts to share an unlicensed channel with another LTE-U small cell, or if there is a change in the number of nodes sharing the unlicensed channel.

Therefore, once the orthogonal CSAT duty cycle duration, and start, and end time is negotiated, the LTE-U small cell may continue to use it for its LTE-U SDL transmission. If there is a change in the CSAT duty cycle duration, and start, and end time as a result of a new usICIC handshake mechanism that is being done in parallel with the on-going LTE-U SDL transmissions, the LTE-U small cell will start using the new settings once they become available after the successful conclusion of the new usICIC handshake mechanism.

The SINR distribution, user (50<sup>th</sup> percentile, Average, 95<sup>th</sup> percentile) and small cell average throughput are the three key performance indicators (KPIs) that we have utilized in our LTE system level simulations to evaluate the performance of our proposed usICIC mechanism for the multi-operator LTE-U co-channel co-existence scenario.

The LTE-U small cells average throughput is dependent upon Channel Resource Utilization [24], Channel Loading [24], and Channel Congestion [24] metrics. Better SINR distribution resulting from the use of our proposed usICIC mechanism will result in better channel conditions so the small cell will be able to complete its LTE-U SDL transmissions to its UEs much faster, thereby reducing the channel loading and congestion metrics and improving the LTE-U small cell average throughput.

Channel Congestion metric  $C_{j,k}$  for the LTE-U small cell j of operator k, is a function of the Channel Resource Utilization  $U_{j,k}$  and Channel Loading  $L_{j,k}$ , and is defined as follows:

$$C_{j,k} = 1 - \left(\frac{U_{j,k}}{L_{j,k}}\right)$$

----- ( 2)

If T is the set of TTIs over a given period of time, such that

$$T = \{t_1, t_2, ..., t_n\}$$

----- (3)

Let  $\mathbf{v}$  denote the set of users served by LTE-U small cell j of operator k within its coverage area of the 5GHz unlicensed spectrum. Then the Channel Resource utilization  $\mathbf{U}_{j,k}$  for the LTE-U small cell j of operator k is defined as the fraction of time the LTE-U small cell is transmitting to one of its users in set v over the unlicensed channel v. It is thus represented as follows:

$$U_{j,k} = \left(\frac{\sum_{t} 1(P_{j,k,t})}{T}\right)$$

----- ( 4)

Where the indicator function 1 ( $P_{j,k,t}$ ) is defined as follows:

$$\mathbf{1}(P_{j,k,t}) = \begin{cases} 1 & \text{If small cell } j,k \text{ is transmitting in TTI } t \\ 0 & \text{If small cell } j,k \text{ is Not Transmitting in TTI } t \end{cases}$$

LTE-U small cell unlicensed Channel Loading  $L_{j,k}$ , may be defined as the fraction of the time LTE-U small cell j of operator k has data to transmit (non empty queues) to its users defined by set  $\mathbf{v}$  within its coverage area. Let  $\mathbf{q}_{j,t}$  be the size of the queue for the  $i^{th}$  user in the set  $\mathbf{v}_{j,k}$  at Transmission Time Interval (TTI) t.

An indicator function  $\mathbf{1}(\mathbf{v}_{i,t})$  is defined on the set  $\mathbf{v}$  such that the value of the indicator function is 1, if the small cell j of operator k has a non empty queue at TTI t for its  $i^{th}$  user or element of user set  $\mathbf{v}$ . The value of the indicator function  $\mathbf{1}(\mathbf{v}_{i,t})$  will otherwise be 0.

$$1 (v_{i,t}) = \begin{cases} 1 & \text{if } q_{i,t} > 0 \text{ at TTI } t \\ 0 & \text{if } q_{i,t} = 0 \text{ at TTI } t \end{cases}$$

----- (6)

Then, the Channel Loading  $L_{j,k}$  over the unlicensed 5 GHZ unlicensed spectrum for each LTE-U small cell j of operator k may therefore be represented as follows:

So using equations (2) - (7), the overall congestion metric of an unlicensed channel is defined as follows:

$$C_{j,k} = 1 - \left(\frac{\sum_{t} 1(P_{j,k,t})}{\sum_{t} \sum_{i \in U} 1(U_{i,t})}\right)$$

----- (8)

The LTE-U small cell continues to monitor the channel conditions (Wi-Fi activity, number of co-existing Wi-Fi, and LTE-U Small Cell) of other unlicensed channels during its LTE-U OFF period of the CSAT transmission gating cycle. This is done to identify a candidate set of unlicensed channels to switch the LTE-U operation if the current unlicensed channel condition continues to yield degraded system performance. Thus by monitoring the Congestion metric  $C_{j,k}$  in addition to the system throughput, the LTE-U small cell may easily decide when to switch its LTE-U operations to an alternative cleaner unlicensed channel if the degraded system performance persists for a pre-defined period of time. Additionally the small cell may utilize these metrics to determine when to turn its LTE-U SDL operations off while dealing with light traffic that could easily be handled by the licensed LTE carrier. This opportunistic turning off of the small cell LTE-U SDL operations [24] will make it a fair neighbor to other nodes sharing the unlicensed channel, because by doing so it makes the unlicensed channel available to other transmitting nodes to use completely.

#### 2.4 Performance Evaluation

In this section, we present the simulation setup, scenarios, results, and the corresponding analysis.

# 2.4.1 Simulation Setup

We performed LTE system level simulations that were based on the scenario #1 of 3GPPTR 36.872 [4]. The MATLAB based LTE system level simulator employed for this simulation work has been developed in Bell Labs, Alcatel-Lucent, which provides LTE protocol stack support at the PHY (layer 1), and the MAC (layer 2) with complete scheduling functions. All Simulation parameters and assumptions are summarized in Table 1.

The Simulations employed two operators, one small cell per operator, and 30 users per operator in 21 macro cell layout with Inter Site Distance (ISD) of 500 meters. Three carriers were employed in the simulation: 2 licensed carriers at 2GHz (one licensed carrier or PCell per operator), and 1 unlicensed carrier SCell for LTE-U SDL operations with a bandwidth of 10 MHz at 5GHz (shared by the small cells of two operators). One transmit and one receive antenna configuration was used at each small cell with transmit power of 30 dBm used for licensed carrier (PCell) and 24 dBm for unlicensed carrier (SCell).

In the LTE system level simulation, the 21 macro cell layout was achieved by 7 macro cell sites, with 3 sectors per site. Within each of these 21 macro cells coverage areas a cluster of small cells was deployed. In each cluster, one small cell was deployed for each operator, so that there were two small cells per macro cell cluster for evaluating the performance of a multi-

operator unlicensed spectrum Inter Cell Interference coordination (usICIC) mechanism.

**Table 1**: Simulation Parameters & Assumptions

| Parameter                                         | Value                                                                                                                                                                 |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Layout                                            | 21 Macro Cells layout                                                                                                                                                 |

| Macro Cell Inter Site Distance (ISD)              | 500 m                                                                                                                                                                 |

| Number of Licensed Carriers                       | 2 (2 GHz for licensed carriers)                                                                                                                                       |

| Number of Unlicensed Carrier                      | 1 (5 GHz for unlicensed carrier)                                                                                                                                      |

| LTE-U System Bandwidth                            | 10 MHz                                                                                                                                                                |

| Number of Operators                               | 2                                                                                                                                                                     |

| Number of small cell Clusters Per Macro Cell      | 1                                                                                                                                                                     |

| Number of Small Cells Per<br>Operator per cluster | 1                                                                                                                                                                     |

| Number of UEs                                     | 30 per macro cell per operator                                                                                                                                        |

| UE Dropping                                       | 2/3 UEs randomly and uniformly dropped within the clusters, 1/3 UEs randomly and uniformly dropped throughout the macro cell coverage area that contained the cluster |

| Tx Power on Unlicensed                            | 30 dBm over licensed carrier, and 24 dBm over unlicensed carrier                                                                                                      |

| Cell Selection or Association<br>Criteria         | Reference Signal Received Power (RSRP) based on the licensed carrier                                                                                                  |

| Antenna Configuration                             | 1Tx, 1 Rx                                                                                                                                                             |

| Traffic Model                                     | Full Buffer                                                                                                                                                           |

| LTE-U T <sub>CSAT</sub> Duty Cycle                | 50%                                                                                                                                                                   |

| LTE-U ON Period                                   | 100 msec                                                                                                                                                              |

| LTE-U OFF Period                                  | 100 msec                                                                                                                                                              |

The simulation employed 30 UEs for each operator's Small cell dropped within each of the 21 macro cell coverage area. Two-thirds of these UEs were randomly and uniformly dropped within the cluster, and the remaining one-third UEs were randomly and uniformly dropped throughout the macro cell coverage area that contained the cluster. Cell selection or association was based on the licensed carrier reference signal received power (RSRP) criteria. A full buffer traffic model was employed in the simulation to ensure that the

small cell utilized the entire duration of its LTE-U ON period of its T<sub>CSAT</sub> transmission gating cycle. For performance evaluation, two types of multi-operator small cell layouts within a macro cell cluster were considered:

- Non co-located multi operator small cells that were 80 meters apart.

- Co-located multi operator small cells that were 3 meters apart.

#### 2.4.2 Simulation Scenarios

Four scenarios were simulated to evaluate the performance of our proposed uslCIC mechanism compared to the non coordinated case using the three key performance indicators (SINR distribution, user throughput, and small cell average throughput). In each scenario the T<sub>CSAT</sub> gating cycle with 100 msec LTE-U ON, and 100 msec LTE-U OFF intervals (i.e. 50% duty cycle) was employed. In this section, we first describe the simulation scenarios, and then provide simulation results and comparison analysis of the three key performance indicators for the four scenarios, to highlight and quantify the LTE system performance enhancements achieved by our proposed uslCIC mechanism.

- Scenario # 1 (Worst Coordination) Non Co-Located small cells Non Co-Located (80 meters apart) Multi-operator LTE-U small cells sharing the same unlicensed channel X, and using the same fully time aligned T<sub>CSAT</sub> gating cycle for their LTE-U SDL transmission.

- Scenario # 2 (Worst Coordination) Co-Located small cells Multioperator Co-located (3 meters apart) LTE-U small cells sharing the same unlicensed channel X, and using the same fully time aligned overlapping T<sub>CSAT</sub> gating cycle for their LTE-U SDL transmission.

- Scenario # 3 (Best Coordination) Co-Located small cells Multioperator Co-located (3 meters apart) LTE-U small cells sharing the same unlicensed channel X and employing our proposed usICIC mechanism to use orthogonal non overlapping T<sub>CSAT</sub> gating cycle for their LTE-U SDL transmission.

- Scenario # 4 (Random No Coordination) Co-Located small cells Multi-operator co-located (3 meters apart) LTE-U small cells sharing the same unlicensed channel X, and using randomly partially aligned overlapping T<sub>CSAT</sub> gating cycle for their LTE-U SDL transmission. Typically the small cells of two operators are not time synchronized and aligned on the same sub-frame boundary. So in the case of non coordinated multi-operator small cells (Scenario #4), the level of T<sub>CSAT</sub> gating cycle (LTE-U ON interval) overlap will be a random distribution between [0,...,100] msec. Therefore, for Scenario #4 (Random No Coordination case), the simulations were repeated 10 times with randomly generated T<sub>CSAT</sub> overlapping gating cycle patterns for each simulation run, and the LTE-U performance averaged across these 10 runs to achieve statistically meaningful result.

#### 2.4.3 Comparative Analysis of the Simulation Results

The LTE-U SINR distributions comparison for the four simulated scenarios is shown in Figure 5. Scenario #3 (Co-Located small cells - Best Coordination using our proposed usICIC mechanism) has the best SINR distribution that is even better than that of Scenario #1 (Non Co-located small cells), where the cells were non co-located, and thus had smaller overlapping LTE-U coverage area that limited the impact of interference each small cell LTE-U transmissions would have caused to their respective users. This highlights the fact that the multi-operator small cells that are either co-located or non co-located, and share the same channel X with overlapping coverage area for their LTE-U SDL operations will benefit with better LTE-U SINR distribution leading to improved overall LTE-U system performance from using our proposed uslCIC mechanism.

Figure 5: LTE-U SINR Distribution Comparison

The LTE-U user throughput (50<sup>th</sup> percentile, Average, and 95<sup>th</sup> percentile) comparison for the four simulated scenarios is shown in Figure 6. Scenario #3 (Co-Located small cells – Best Coordination that employed our proposed uslCIC mechanism) has the best user throughput results, and

demonstrate that the use of our proposed usICIC mechanism will result in substantial LTE-U system performance enhancement.

Figure 6: LTE-U User Throughput Comparison