## **Syracuse University**

## **SURFACE**

Dissertations - ALL **SURFACE**

8-2014

## EARLY PERFORMANCE PREDICTION METHODOLOGY FOR MANY-**CORES ON CHIP BASED APPLICATIONS**

Boray S. Deepaksubramanyan Syracuse University

Follow this and additional works at: https://surface.syr.edu/etd

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Deepaksubramanyan, Boray S., "EARLY PERFORMANCE PREDICTION METHODOLOGY FOR MANY-CORES ON CHIP BASED APPLICATIONS" (2014). Dissertations - ALL. 162.

https://surface.syr.edu/etd/162

This Dissertation is brought to you for free and open access by the SURFACE at SURFACE. It has been accepted for inclusion in Dissertations - ALL by an authorized administrator of SURFACE. For more information, please contact surface@syr.edu.

## **ABSTRACT**

Modern high performance computing applications such as personal computing, gaming, numerical simulations require application-specific integrated circuits (ASICs) that comprises of many cores. Performance for these applications depends mainly on latency of interconnects which transfer data between cores that implement applications by distributing tasks. Time-to-market is a critical consideration while designing ASICs for these applications. Therefore, to reduce design cycle time, predicting system performance accurately at an early stage of design is essential. With process technology in nanometer era, physical phenomena such as crosstalk, reflection on the propagating signal have a direct impact on performance. Incorporating these effects provides a better performance estimate at an early stage. This work presents a methodology for better performance prediction at an early stage of design, achieved by mapping system specification to a circuit-level netlist description.

At system-level, to simplify description and for efficient simulation, SystemVerilog descriptions are employed. For modeling system performance at this abstraction, queueing theory based bounded queue models are applied. At the circuit level, behavioral Input/Output Buffer Information Specification (IBIS) models can be used for analyzing effects of these physical phenomena on on-chip signal integrity and hence performance.

For behavioral circuit-level performance simulation with IBIS models, a netlist must be described consisting of interacting cores and a communication link. Two new netlists, IBIS-ISS and IBIS-AMI-ISS are introduced for this purpose. The cores are represented by a macromodel automatically generated by a developed tool from IBIS models. The generated IBIS models are employed in the new netlists. Early performance prediction methodology maps a system specification to an instance of these netlists to provide a better performance estimate at an early stage of design. The methodology is *scalable* in nanometer process technology and can be *reused* in different designs.

# EARLY PERFORMANCE PREDICTION METHODOLOGY FOR MANY-CORES ON CHIP BASED APPLICATIONS

By

Boray S. Deepaksubramanyan B.E., University of Pune, 2003 M.S., Syracuse University, 2006

#### **DISSERTATION**

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Syracuse University August 2014

## Copyright © 2014 Boray S. Deepaksubramanyan All rights reserved

# ACKNOWLEDGMENTS

To family, for family.

For me, it is "Tea Machine."

People.

# TABLE OF CONTENTS

| A  | Acknowledgments |               |                                                  | iv |

|----|-----------------|---------------|--------------------------------------------------|----|

| Li | st of ]         | <b>Fables</b> |                                                  | ix |

| Li | List of Figures |               |                                                  | X  |

| 1  | Intr            | oductio       | n                                                | 1  |

|    | 1.1             | Introd        | uction and Motivation                            | 1  |

|    | 1.2             | Systen        | n Modeling and Simulation Overview               | 4  |

|    |                 | 1.2.1         | System-Level Simulation                          | 4  |

|    |                 | 1.2.2         | Circuit-Level Simulation                         | 4  |

|    |                 | 1.2.3         | Performance Metrics of Interest                  | 5  |

|    | 1.3             | Outlin        | e                                                | 5  |

| 2  | Why             | Early         | Performance Prediction?                          | 8  |

|    | 2.1             | Introd        | uction                                           | 8  |

|    | 2.2             | ASIC          | Design Flow and Relevant Simulation Tools        | 9  |

|    |                 | 2.2.1         | Simulation Tools                                 | 10 |

|    | 2.3             | IBIS N        | Models for Behavioral SI Simulation              | 13 |

|    |                 | 2.3.1         | Generating an IBIS File                          | 14 |

|    |                 | 2.3.2         | SPICE to IBIS Tool                               | 15 |

|    | 2.4             | Higher        | r-Level System Specification                     | 17 |

|    |                 | 2.4.1         | Computational Models to Describe System Behavior | 18 |

|   |      | 2.4.2            | Specifying Communication - Protocol Modeling              | 20 |

|---|------|------------------|-----------------------------------------------------------|----|

|   | 2.5  | Summ             | ary - Need for Early Performance Prediction               | 24 |

| 3 | A M  | lethod to        | o Generate Models of Circuits Specified by IBIS Models    | 25 |

|   | 3.1  | Introdu          | action                                                    | 25 |

|   | 3.2  | Backg            | round on Moment Matching                                  | 26 |

|   |      | 3.2.1            | Asymptotic Waveform Evaluation and Obtaining System Poles | 26 |

|   |      | 3.2.2            | Reduced Pole Approximation                                | 28 |

|   |      | 3.2.3            | Delay Metrics Based on Distribution Function              | 30 |

|   |      | 3.2.4            | Moment Matching Background                                | 30 |

|   | 3.3  | Weibul           | ll Distribution Function as a Regression Function         | 31 |

|   |      | 3.3.1            | Weibull c.d.f. Based Regression                           | 33 |

|   | 3.4  | IBIS M           | Models Based Macromodel Generation Method                 | 35 |

|   | 3.5  | Impler           | mentation and Results                                     | 42 |

|   | 3.6  | Propos           | sed Model Generation Method                               | 43 |

|   | 3.7  | Summ             | ary                                                       | 44 |

| 4 | A To | ool for F        | Behavioral Signal Integrity Analysis                      | 46 |

|   | 4.1  | 4.1 Introduction |                                                           | 46 |

|   | 4.2  | Factors          | s Affecting Link Performance                              | 47 |

|   |      | 4.2.1            | Jitter Taxonomy                                           | 48 |

|   |      | 4.2.2            | Jitter Models                                             | 49 |

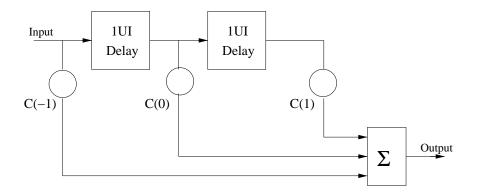

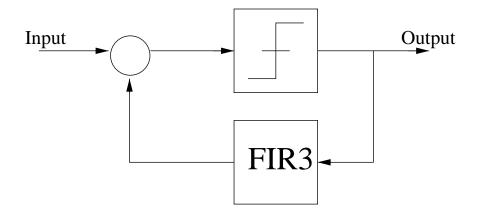

|   |      | 4.2.3            | Utilizing Equalizers to Minimize ISI                      | 51 |

|   |      | 4.2.4            | Crosstalk Analysis                                        | 53 |

|   | 4.3  | Netlist          | s for On-Chip Link Analysis                               | 54 |

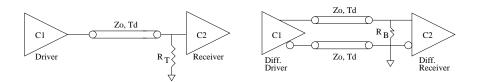

|   |      | 4.3.1            | Interconnect Topologies                                   | 55 |

|   |      | 4.3.2            | IBIS-ISS Netlist                                          | 57 |

|   |      | 133              | IRIS_AMI_ISS Netlist with Fauglizers                      | 57 |

|   | 4.4                               | PCI E                                                                              | xpress Protocol and Netlists                | 58                                           |

|---|-----------------------------------|------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------|

|   |                                   | 4.4.1                                                                              | PCIe PHY Layer                              | 59                                           |

|   |                                   | 4.4.2                                                                              | PCI Express Jitter Budget                   | 59                                           |

|   |                                   | 4.4.3                                                                              | IBIS-AMI-ISS Netlist for PCIe Spec          | 60                                           |

|   | 4.5                               | Simula                                                                             | ation-Based Performance Estimation at PHY   | 61                                           |

|   |                                   | 4.5.1                                                                              | Efficient Topology Selection                | 62                                           |

|   |                                   | 4.5.2                                                                              | Efficient Topology Selection Algorithm      | 63                                           |

|   | 4.6                               | Autom                                                                              | nated Behavioral On-Chip Link Analysis      | 64                                           |

|   |                                   | 4.6.1                                                                              | Experimental Setup                          | 64                                           |

|   |                                   | 4.6.2                                                                              | Netlist Generation Template                 | 65                                           |

|   |                                   | 4.6.3                                                                              | Behavioral Link Analysis Method             | 66                                           |

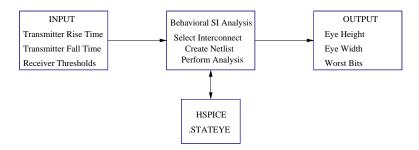

|   |                                   | 4.6.4                                                                              | Behavioral Link Analysis Tool               | 67                                           |

|   |                                   | 4.6.5                                                                              | Implementation                              | 68                                           |

|   | 4.7                               | Summ                                                                               | ary                                         | 71                                           |

| 5 | Earl                              | y Perfo                                                                            | rmance Prediction Methodology               | 73                                           |

|   |                                   |                                                                                    |                                             |                                              |

|   | 5.1                               | Introd                                                                             | action                                      | 73                                           |

|   | <ul><li>5.1</li><li>5.2</li></ul> |                                                                                    | action                                      |                                              |

|   |                                   |                                                                                    |                                             | 74                                           |

|   |                                   | Systen                                                                             | Modeling and Specification                  | 74                                           |

|   |                                   | System 5.2.1                                                                       | Modeling and Specification                  | 74<br>74<br>75                               |

|   |                                   | System 5.2.1 5.2.2 5.2.3                                                           | Modeling and Specification                  | 74<br>74<br>75<br>77                         |

|   | 5.2                               | System 5.2.1 5.2.2 5.2.3                                                           | Modeling and Specification                  | 74<br>74<br>75<br>77<br>78                   |

|   | 5.2                               | <ul><li>System</li><li>5.2.1</li><li>5.2.2</li><li>5.2.3</li><li>Perform</li></ul> | Modeling and Specification                  | 74<br>74<br>75<br>77<br>78                   |

|   | 5.2                               | 5.2.1<br>5.2.2<br>5.2.3<br>Perfor<br>5.3.1<br>5.3.2                                | Modeling and Specification  System Modeling | 74<br>74<br>75<br>77<br>78<br>78<br>81       |

|   | 5.2                               | 5.2.1<br>5.2.2<br>5.2.3<br>Perfor<br>5.3.1<br>5.3.2                                | Modeling and Specification  System Modeling | 74<br>74<br>75<br>77<br>78<br>78<br>81<br>82 |

|   | 5.2                               | 5.2.1<br>5.2.2<br>5.2.3<br>Perfor<br>5.3.1<br>5.3.2<br>Early 1                     | Modeling and Specification  System Modeling | 74<br>74<br>75<br>77<br>78<br>81<br>82<br>83 |

| 5.5 Implementation |     |                                                | 87 |

|--------------------|-----|------------------------------------------------|----|

|                    |     | 5.5.1 System-Level Template                    | 88 |

|                    |     | 5.5.2 Circuit-Level Template                   | 88 |

|                    |     | 5.5.3 Tool Components                          | 89 |

|                    | 5.6 | Summary                                        | 89 |

| 6                  | Con | lusion                                         | 91 |

|                    | 6.1 | Summary                                        | 91 |

|                    | 6.2 | Conclusions                                    | 92 |

|                    |     | 6.2.1 Features of Early Performance Prediction | 93 |

| A                  | EEP | PM Tool                                        | 94 |

# LIST OF TABLES

| 3.1 | Performance parameters, 22nm   | 43 |

|-----|--------------------------------|----|

| 3.2 | Performance parameters, 16nm   | 43 |

| 4.1 | PCI Express Jitter Budget [45] | 60 |

| 4.2 | PCI Express Jitter Budget      | 60 |

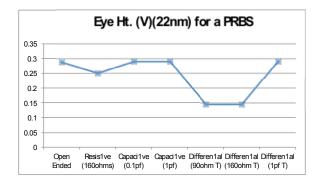

| 4.3 | Results: 22nm                  | 70 |

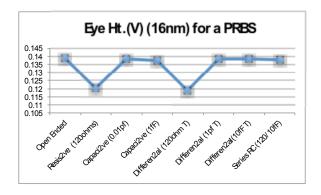

| 44  | Results: 16nm                  | 70 |

# LIST OF FIGURES

| 1.1 | Generic Many-Core ASIC Structure                                        | 2  |

|-----|-------------------------------------------------------------------------|----|

| 2.1 | ASIC Design Flow Overview                                               | 11 |

| 2.2 | Early Performance Prediction - Mapping System Spec. to Behavioral IBIS- |    |

|     | ISS Netlist                                                             | 12 |

| 2.3 | Structure of IBIS Models                                                | 13 |

| 2.4 | Setup to Obtain V/I Data                                                | 15 |

| 2.5 | Setup to obtain V/t Data                                                | 16 |

| 2.6 | Typical transient response waveform from generated IBIS file            | 16 |

| 2.7 | S2IBIS tool flow                                                        | 17 |

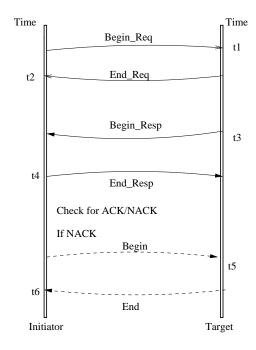

| 2.8 | TLM Two-Phase Protocol                                                  | 22 |

| 2.9 | TLM Four-Phase Protocol                                                 | 22 |

| 3.1 | Weibull c.d.f. for different parameter values                           | 32 |

| 3.2 | Typical IBIS model V/t Rising Waveform                                  | 35 |

| 3.3 | IBIS Component Characterization                                         | 36 |

| 3.4 | Inverter: V/t rising waveform                                           | 37 |

| 3.5 | Weibull c.d.f.                                                          | 37 |

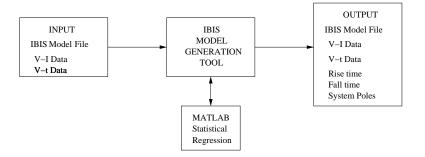

| 3.6 | IBIS Model Generation Tool                                              | 41 |

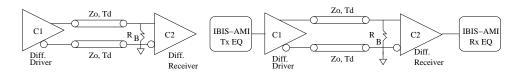

| 4.1 | Circuit-level Behavioral Link Analysis with Generated IBIS Models       | 50 |

| 4.2 | Block Diagram 3-tap FIR Filter                                          | 51 |

| 43  | Block Diagram 3-tan FIR Filter                                          | 53 |

| 4.4         | Presented Netlists for Serial Link Topologies                     | 55 |

|-------------|-------------------------------------------------------------------|----|

| 4.5         | Serial Link Netlist With Equalization                             | 58 |

| 4.6         | Results for 16nm Process Technology for Various T-line Topologies | 71 |

| 4.7         | Results for 22nm Process Technology for Various T-line Topologies | 71 |

|             |                                                                   |    |

| 5.1         | Communication Protocol                                            | 77 |

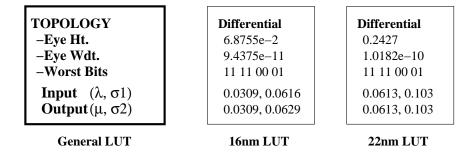

| 5.2         | Look Up Table: General Structure and Examples                     | 87 |

|             |                                                                   |    |

| <b>A</b> .1 | Snapshot of Early performance prediction tool                     | 95 |

## CHAPTER 1

## Introduction

## 1.1 Introduction and Motivation

Rapid advancement in process technology has allowed multiple cores to be integrated on integrated circuits. Current microprocessors consist of multiple on-chip cores with central processing (CPU) and graphics processing (GPU) cores integrated on the same die. As technology advances further into nanometer process technology allowing more transistors to be fabricated on-chip, many-core based processors, application specific integrated circuits (ASICs) with added functionality are becoming essential to meet performance goals while maintaining the power budget. These cores may be homogeneous (same size, type) or heterogeneous as described in [1]. Considering the current processors/systems trends, a future with many heterogeneous cores can be envisioned, each performing different functionality to implement complex applications.

These cores are interconnected through a highly efficient interconnect network. Selecting appropriate interconnect network topology considering on-chip constraints is an active research and development topic. Knowledge of many well-researched domains such as high performance computing, parallel systems, on-chip networks, ASIC system design is required for creating products that can execute multiple high intensity applications concur-

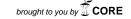

Fig. 1.1: Generic Many-Core ASIC Structure

rently for a real-world user experience. Recent examples of technology advancement include many-integrated cores (MIC) on a chip [14] that utilizes multiple cores on processors for fast computations required by concurrent applications. This many-core "co-processor" supplements the core processor in high performance computing applications.

For the applications mentioned above that have high computing needs and perform multiple functionalities requiring high amounts of data transfer, communication delay between cores is the main performance bottleneck as the application tasks is distributed to a few cores. And with process technology in nanometer era, evaluating signal integrity has become critically important to meet the performance requirement as eventually, it is the VLSI chip that has to perform the required functionality. System performance, defined primarily by latency at the system-level is therefore a function of circuit-level, layout-level issues. Therefore, physical phenomena affecting signal integrity (SI) such as reflections due to impedance mismatch, intersymbol interference and crosstalk between adjacent wires that transport data from one core to another must be accounted for to obtain a more accurate measure of system performance.

Early performance prediction methodology, the contribution of this work incorporates signal reliability information at an early stage of design. As these factors are more pronounced in nanometer process technology, and predicted to worsen with technology ad-

vancement according to the International Technology Roadmap for Semiconductors (ITRS) [2] [23], a **scalable** prediction method is essential. The developed methodology is scalable in nanometer technology.

Consider a generic many-core ASIC design as shown in Figure 1.1. Each core in the figure is tasked to perform specific functions for each application. A set of these cores would have dedicated memory and Input/Output (interconnect) units to transfer the result of tasks' computation. The performance of the chip depends mainly on the overall time taken for data transfer over interconnects. Studying the factors affecting interconnect performance is neccessary at an early stage of chip design. The design flow for processors and ASICs is a multi-phase process comprising of multiple steps. And in each phase, the system is designed with reference to the performance requirements. Computer-aided analysis or simulation of these complex systems is undertaken at each phase by selecting a suitable model of the system at that abstraction level to study various metrics required by the user.

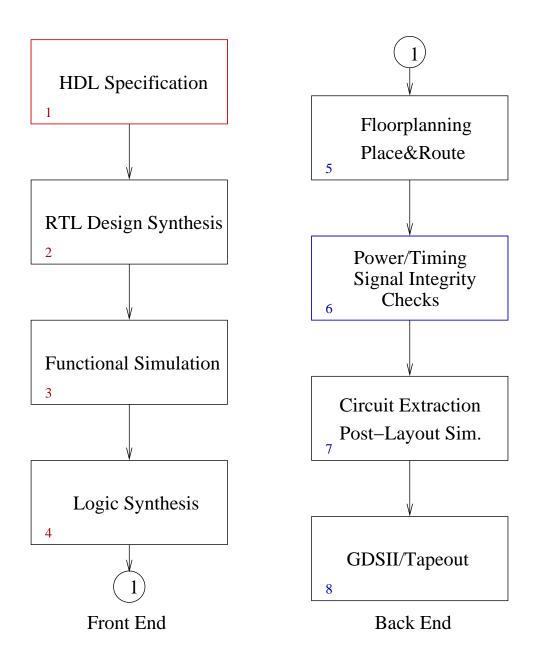

To study ASIC performance at the system-level, a C-like higher-level specification language is employed to simplify system description and perform efficient simulation. With factors affecting signal integrity as the main issues in evaluating system performance at the circuit-level, for behavioral simulation at this abstraction level, Input/Output Buffer Information Specification (IBIS) model description is used. To accurately estimate performance at an early phase of design (i.e. at the system-level), knowledge of circuit-level issues that impact performance is required. The goal of the presented work is to provide this circuit-level process technology dependent information at an early stage of design. This is achieved by mapping the system description to its equivalent circuit-level IBIS models based netlist (the generated IBIS-ISS netlist and created "IBIS-AMI-ISS" netlist). An overview of simulation models used at system- and circuit-levels of abstraction that are utilized in this work is presented below.

## 1.2 System Modeling and Simulation Overview

## 1.2.1 System-Level Simulation

At the system-level, to efficiently model and simulate modern integrated circuits, higher-level description languages have been developed to simplify system description and to aid fast simulations. HDLs such as SystemC and SystemVerilog are good examples. A complete system, such as the one shown in Figure 1.1, that consists of sub-systems performing different functions can be specified for fast simulation and early analysis with these description languages. Several work in recent years have added SystemC, SystemVerilog capabilities to efficiently specify and simulate such systems. In this work, system is specified with C-like SystemVerilog HDL constructs [18]. To allow higher level specification and performance modeling, communication links are modeled using the transaction-level modeling (TLM) paradigm.

## 1.2.2 Circuit-Level Simulation

At the circuit-level, SI analysis involves studying the effects of these phenomena on signal quality at the receiver end. Three types of electrical simulation tools are used to perform SI analysis; SPICE based circuit simulators, Electromagnetic (EM) simulators and Behavioral simulators. Circuit simulators solve differential equations corresponding to various circuit elements to predict current and voltage at different nodes of the circuit. EM simulators solve Maxwell's equations and simulate electric and magnetic fields at different locations. Both simulation methods are very accurate but computationally slow [19].

Behavioral simulators, on the other hand, use precompiled tabulated data to simulate voltages and currents. Therefore, they are accurate and computationally faster than circuit and EM simulators. Input/Output Buffer Information Specification (IBIS) models are used for behavioral SI simulations. IBIS models contain non-linear electrical characteristics of the input and output pins of a component. They do not include transistor-level

implementation details. Therefore, these models preserve intellectual property (IP) and are computationally very fast. Since IP is protected, IBIS models can be re-used in different designs. It can also be used at an early stage of design process as there is no need for circuit specifics.

## 1.2.3 Performance Metrics of Interest

In this application domain of interest, with the focus on interconnect performance, the main system-level performance metric evaluated is latency and to an extent throughput. Latency is defined as the amount of time (or number of clock cycles) needed to transfer data from source to destination. This performance metric is impacted by physical layer factors such as crosstalk and reflection on the communication link. The study of the impact of these physical phenomena is the main focus of early performance prediction methodology. Another performance metric is throughput, though isn't the focus in this work. System throughput is defined as the rate at which data is transferred from source to destination. The importance of a particular metric is application specific. For applications considered in this work, transmission latency is the primary performance metric of focus.

## 1.3 Outline

For systems with many processing cores on a chip, low energy and high performance is required to sustain the dramatic development in processor and ASICs over the past four decades [1]. From an architect's perspective, a good knowledge of performance bounds/estimates at an early stage is important to make accurate decisions. For these bounds/estimates to be accurate, the architect would require a good knowledge of circuit-level issues that would impede performance. Early performance prediction method is a contribution in this direction. Evaluating system performance accounting for factors affecting signal integrity would provide a more realistic and accurate estimate of overall

performance at early phase of design cycle.

#### **Contributions**

Due to increasing design complexity, it is critical to analyze the functionality accurately at an early stage of design process. Computer-aided analysis or simulation tools are used for this purpose. ASIC and microprocessor design flow consists of multiple levels of abstractions and at each level, simulation tools have been developed for comprehensive analysis. At each abstraction layer, different groups of engineers are involved in design and verification of the system and work independently from one other. To reduce the overall design time, it is therefore beneficial to develop a method that provides a better prediction of system performance by factoring the physical phenomena affecting signal quality. This would aid in meeting time-to-market requirements. The developed early performance prediction method is a contribution in this direction. The following are the contributions of this work:

- 1. A tool to generate macromodel for a circuit specified by behavioral IBIS models

- 2. A knowledge-based method for behavioral SI analysis with generated macromodel

- Creation of IBIS-ISS netlist based on IBIS-Interconnect subcircuit specification (IBIS-ISS).

- Creation of IBIS-AMI-ISS netlist, that enhances the IBIS-ISS standard to incorporate IBIS Algorithmic Modeling Interface (AMI).

- 3. Early performance prediction method that maps a system specification to the generated netlist to obtain a better performance estimate at an early stage of design.

#### Dissertation Overview

The remainder of this document is organized as follows: Chapter 2 describes the need for early performance prediction methodology. First, general ASIC design flow is described

with various design phases. The developed early performance prediction method is outlined with the phases in design flow along with future trends in perspective. Simulation spec. and models at both system-level and circuit-level are discussed with focus the reliability of transferred signal. Chapter 3 presents a method to generate a macromodel of a circuit specified by IBIS models. The method, based on moment matching method is discussed. Chapter 4 presents a knowledge-based tool to perform behavioral signal integrity analysis with IBIS models. The tool incorporates the generated IBIS models discussed in previous chapter to create two new netlists, IBIS-ISS and IBIS-AMI-ISS netlist. A knowledge-based template is created to perform behavioral statistical eye analysis using the new netlists that contain surveyed transmission line models for interconnects. Peripheral Component Interface (PCI) Express (PCIe) protocol is employed for this work. Chapter 5 presents the early performance prediction methodology. A higher-level C-like specification of the system is mapped to an instance of the created netlist. Mathematical model applied for performance modeling and estimation is discussed. Finally, Chapter 6 concludes the work with a discussion on the usefulness of the developed methodology.

## CHAPTER 2

## WHY EARLY PERFORMANCE

## PREDICTION?

## 2.1 Introduction

This chapter presents an overview of ASIC design flow and simulation tools to provide the reader a perspective on the developed early performance prediction methodology. Multicore and many-core integrated circuits are the computing engines in a wide range of systems/applications such as laptops, smartphones, tablets, gaming consoles, vehicles, aeronautics and so on. Each of these systems perform specific functions tailored to the required application. For example, modern microprocessors integrate CPU cores and GPU cores on the same die along with internal memory. The trend is to integrate more of these cores for highly efficient computing and are used in simulation of various high-performance applications and graphics (gaming softwares). A very recent example is the reporting of detailed simulation of the human heart, now possible with new IBM Blue Gene computing system [15]. This ASIC chip comprises of multiple cores (16 cores) performing computation along with dedicated on-chip memory, all managed by a layered interconnect fabric.

Designing and ensuring the proper operation of these ASICs is a complex task and is

handled by a series of steps. This chapter begins by an overview of the IC design flow from concept to tapeout. Each phase of design comprises of multiple intermediate steps optimized for user specified constraints such as power, timing, area etc. At each level of abstraction, comprehensive simulation is performed for validation and verification of functionality. Behavioral simulation method is of particular focus in this work and is discussed at both system spec. level and circuit level. IBIS models are widely used for performing behavioral signal integrity simulations at the circuit-level. IBIS models are discussed in detail in the subsequent sections. A good understanding of these behavioral models is required for the development of IBIS based behavioral serial link performance analysis tool presented in Chapter 3.

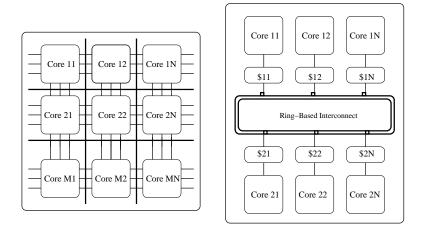

In the following section, background in system-level modeling with a higher-level specification language is introduced. Basic models of computation that are used for this work are discussed. A C-like description for modeling communication protocols is also described. These hardware descriptions are developed to simplify system specification and reduce simulation time. This spec. is provided as input to the early prediction method. Both system-level spec. and IBIS models background are presented with the design flow (Figure 2.1) in perspective. The goal is to motivate the need for early performance prediction method. The developed methodology itself is presented in Chapter 5.

## 2.2 ASIC Design Flow and Relevant Simulation Tools

ASIC design flow from specification to tapeout is discussed briefly, with a reference flow shown in Figure 2.1. System is first specified at a higher-level (behavioral-level) of abstraction in hardware oriented languages (HDLs) such as SystemVerilog, SystemC and other C-extensions to simplify complex ASIC design descriptions. These descriptions are *synthesized* to a gate-level netlist by modern synthesis tools in an automated fashion (mentioned here, but not the focus of this work). The synthesis process itself comprises of

multiple intermediate steps with optimizations for power, timing, area as per the requirements of the application (steps 1 through 4). The goal of back-end ASIC design flow (steps 4 through 8) is to map the generated netlist to standard cells for each component that is available as a library. A series of steps are performed to obtain an optimized final layout, which is converted to GDSII format and sent for fabrication. The focus here is on the simulation aspect of the flow. Depending on the spec., the required components' standard cells are invoked and interconnected to obtain final layout. In nanometer era, interconnect performance dictates overall system performance for applications discussed in Chapter 1. Therefore, many of the tools developed to automate the ASIC design flow at each phase of front-end design and back-end design specifically focus on timing and signal integrity aspects to meet performance requirement.

## 2.2.1 Simulation Tools

At each design phase, comprehensive simulations are performed to verify the functionality and ensure the correctness of design. System specification in higher-level languages allow fast simulations of systems as they simplify system description by abstracting relevant information. At behavioral level (system-level), simulation tools have been developed for (early) performance analysis. Similarly, mature gate-level and circuit-level simulation tools are available that analyze synthesized designs and ensure correct working of design. Examples include Cadence Spectre, Synopsys HSPICE and others. For fast behavioral signal integrity simulations with IBIS models at the circuit-level (or layout level), simulation tools exists such as Mentor Graphics Hyperlynx, Cadence Sigrity and so on. These simulations are performed at a later phase of design cycle (Step 6). Since custom ASIC design involves the use of standard cells, IBIS models for each of the cells would also be available.

From a system designer or architect's perspective, system-level simulations provide valuable understanding of the system to be designed. However, the accuracy of the models is critical for a good estimate of the system performance. A useful contribution would be

Fig. 2.1: ASIC Design Flow Overview

Fig. 2.2: Early Performance Prediction - Mapping System Spec. to Behavioral IBIS-ISS Netlist

to provide the architect with simulation information from later phase of design (at lower abstraction level) during system-level simulation phase. This would necessitate the need for process tech. dependent mapping at an early stage of design to improve the prediction accuracy and lead to first-time-correct implementations. The presented work is a step in this direction.

To appreciate early performance prediction methodology, a good understanding of specification and modeling at different abstraction levels is needed. The reader would recognize that the specification and models are vary significantly as the abstraction levels discussed in this work represent different domains in electrical engineering and computer engineering. The following section describes these models (specifications) in detail. Figure 2.2 shows the mapping of models at different abstraction level that forms the crux of *early prediction methodology*.

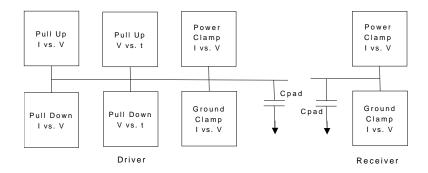

Fig. 2.3: Structure of IBIS Models

## 2.3 IBIS Models for Behavioral SI Simulation

This section describes the Input/Output Buffer Information Specification (IBIS) models in detail. IBIS is a behavioral specification (ANSI/EIA standard) that describes the non-linear electrical characteristics of the input and output pins of a component through tabulated Voltage-Current (V/I) and Voltage-time (V/t) data. IBIS models were introduced by Intel Corporation in early 1990s to aid signal integrity simulations by allowing interoperability of models between vendors. Unlike SPICE, IBIS models do not include transistor-level implementation details and thus preserves intellectual property (IP). This allows for faster simulation than SPICE. IBIS models can be created either manually by extracting V/I and V/t data or using automation tool such as S2IBIS. Both manual procedure and the automation tool to create IBIS models are discussed.

Figure 2.3 shows the structure of the input pin (receiver) and output pin (driver) of an IBIS file. The driver consists of a pull-up device (with V/I, V/t data) and a pull-down device (with V/I, V/t data). Behavioral simulation with IBIS models involves analyzing effects of impedance mismatch, crosstalk and reflections on an electrical signal propagating on a wire modeled as a transmission line from the driver to receiver. IBIS models are used mainly in signal integrity simulation of printed circuit boards.

In this work, IBIS models are used for on-chip signal integrity simulations. To be able to use the IBIS models to perform processor performance simulations in an automated manner, a macromodel needs to be generated from the IBIS model with estimates of per-

formance parameters; for example the signal rise time.

Using the V/t data, each component is characterized by the poles (transfer function) of the specific component at a particular technology node and its edge rate (rise and fall times). Manual procedure to extract V/I and V/t data is discussed next. This is followed by a brief discussion on the automated tool. The generated IBIS files form the input to the proposed model generation tool described in Chapter 3.

## 2.3.1 Generating an IBIS File

The procedure for generating data to create IBIS model file is described here. Steps for extracting voltage-current and voltage-time data of a component is discussed. The ANSI/EIA IBIS Specification [7] outlines the procedure to obtain V/I and V/t data [10].

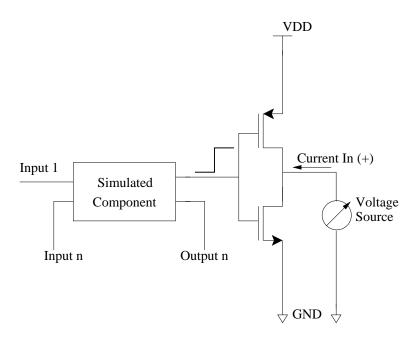

## Extracting V/I Data

To construct the V/I curves for the output pin, the first step is to understand the working of the component and determine how to put the component's output to logic low and logic high states. For this, a transistor-level netlist of the component is provided. Once the component is placed at a particular output state, the output pin is connected to an independent voltage source, as shown in Figure 2.4. The simulator is set to DC analysis mode. The current flow into the pad is then measured as the source is swept across a range from -VDD to 2VDD. Separate curves are generated for pull-up and pull-down devices by setting the output of the component to logic low and high respectively [10]. The steps are repeated for each component.

## Extracting V/t Data

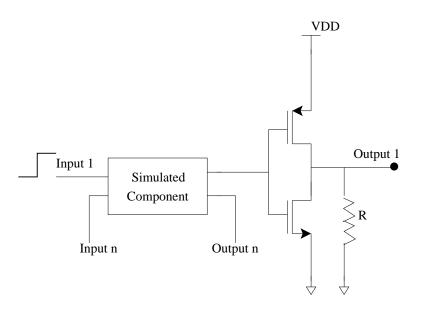

Next, the procedure to generate tabulated transient response (voltage-time data) is described. To obtain V/t (rise time and fall time) curves for each output pin, the simulator is set to transient analysis mode [10]. A signal with appropriate slew rate is applied at the

Fig. 2.4: Setup to Obtain V/I Data

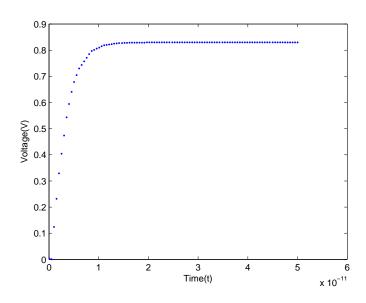

input of the simulated component as shown in Figure 2.5. V/t tables are created when the output is driving into a test load, typically a  $50\Omega$  resistor that is connected to the appropriate supply [10], as described in Figure 2.5. The test load can be selected or specified by the user. The test load used to generate the V/t tables must be described in the model. If the automation tool, discussed next, is used to generate IBIS data, then the test load must be specified in the user defined .s2i file. The signal integrity simulation tool will use this information from the model to reconcile the output waveform to reflect the behavior when driving the actual system load. Figure 2.6 shows a typical rising V/t waveform obtained from an IBIS file.

## 2.3.2 SPICE to IBIS Tool

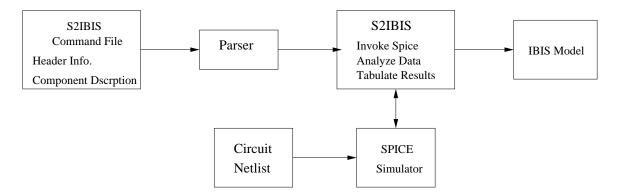

Spice to IBIS conversion tool (S2IBIS) is a platform independent tool that converts a SPICE netlist of a component (circuit) to its IBIS model. The tool was developed at North Carolina State University [9]. Figure 2.7 shows the block diagram of S2IBIS tool flow [12]. The tool consists of a command file that contains the header information and user defined description

Fig. 2.5: Setup to obtain V/t Data

Fig. 2.6: Typical transient response waveform from generated IBIS file

Fig. 2.7: S2IBIS tool flow

of the component. This command file (Example: example.s2i) has to be edited by the user and details of the Spice netlist file, the (technology) model file, supply voltage and other parameters are incorporated. The S2IBIS tool accepts this information through a parser and invokes a SPICE simulator to analyze data and extract relevant V/I and V/t data. Acceptable SPICE simulators include HSPICE, SPICE2, SPICE3. Finally, the data is stored into a file in the standard IBIS model format. For this work, IBIS-AMI (IBIS versions 5 and 6) models are created manually with specific information required for this academic work as S2IBIS generates models upto IBIS version 3. IBIS version 5 onwards support Algorithmic Modeling Interface (AMI).

With the understanding of data generation method for IBIS models, a method to generate macromodels of circuits specified by IBIS models is presented in Chapter 3. In the following section, system specification background is reviewed with focus of the presented work.

## 2.4 Higher-Level System Specification

As complexity of integrated circuits increases, there arises a need to describe these systems at a higher level of abstraction to simplify system description and improve simulation time. For specifying systems at this higher abstraction level (above RTL), called system-level, new hardware description languages [16] [62] have been developed. The most prominent

ones are SystemVerilog and SystemC. System-level languages provide constructs/facilities of computation and communication of the system to be modeled separately. SystemVerilog HDL [18] (IEEE 1800 Standard) builds on the existing, widely used Verilog HDL by adding new constructs that allows simplification of complex system descriptions. These include separate description of processing elements (cores) and the intercommunication between them, allowing abstract description of interfaces. Similarly, SystemC [16] (IEEE 1666 standard) on the other hand has been built ground-up with C++ programming language.

SystemVerilog, SystemC allow users to specify systems at a higher level of abstraction (above RTL, Verilog/VHDL). At the higher-level, system functionality is effectively described with minimal information of lower-level details. This allows for faster and more efficient simulation of modern systems. SystemVerilog comprises of extensions over Verilog HDL with specific constructs for interconnect description (interface), allowing the specification at system-level, where separation of computation and communication is required. SystemC on the other hand, has been built ground up. It is basically a set of classes built over the standard C++ programming language with the addition of timing and concurrency constructs. This allows hierarchical description of hardware components and ease of extensibility. During the course of this work, both have been studied, but SystemVerilog constructs have been used to develop early performance prediction methodology.

## 2.4.1 Computational Models to Describe System Behavior

Models of computation (MOC) relevant for modeling many-core ASICs have been defined and implemented over the past years. These MOCs have been implemented in SystemC and are available as part of standard libraries [54] [59]. Of the MOCs implemented, bounded process network is of particular interest along with timed synchronous dataflow. These MOCs can be specified in a similar way using SystemVerilog as well. This work started with SystemC, however SystemVerilog has been used for system specification.

#### Bounded Kahn Process Network (BKPN)

BKPN MOC consists of computational process nodes connected by unidirectional FIFO channel. BKPN implementation in SystemC is available as part of heterogeneous computation model library [54]. Both unbounded and bounded KPN are implemented with bounded FIFO channel with buffer size N, where  $1 < N < \infty$ . The behavior of BKPN is given by [54]:

#### Rules for communication:

- 1. Communication via bounded FIFO's  $(1 < N < \infty)$ . Size of the buffer is fixed.

- 2. Blocking read and write implementation. Read until fifo empty, write until buffer is full

- 3. No data can be written when buffer is full. No read access when buffer is empty

*Rules for computation*: Computation is through continuous mapping. That means, a token is produced only after consuming some tokens to perform a computation

#### Synchronous Dataflow

Timed synchronous dataflow (TSDF) MOC is implemented for example in the SystemC-AMS standard [59]. It is based on the synchronous dataflow model of computation with sampling at discrete time stamps. TSDF model is well suited for work focusing on signal processing applications. The rules that describe the behaviour of a TSDF MOC are given below:

## Rules for communication:

- 1. Tokens transferred at a rate specified by the user.

- 2. Communication through the HetSC  $uc\_arc\_seq$  FIFO channel implementation.

## Rules for computation:

- 1. Computation is through continuous mapping.

- 2. Functional relation.

- 3. Input arc is read first to produce the output arc.

## 2.4.2 Specifying Communication - Protocol Modeling

To simulate detailed communication protocols such ARM AMBA, Intel PCI Express at a higher level of abstraction, transaction-level modeling (TLM) method has been developed over the past decade. TLM provides mechanisms for modeling behavior of the communication link with predefined and user defined tasks and functions. The most recent version of standardized TLM, TLM 2.0 has been incorporated into SystemC [58] specification language. TLM is a concept that isn't specific to a particular description language and can be specified in other system-level languages such as SystemVerilog. The modeling of interconnects with TLMs using SystemVerilog is discussed in subsequent chapters.

#### Transaction Level Modeling

Transaction level modeling (TLM) [62] specifies modeling communication between processes as a sequence of transactions. The previous section highlighted computation models for higher-level component specification. TLM allows behavioral description and modeling of interconnection between processes. It provides means to abstract communication interface between the components using tasks and/or functions. By raising the abstraction level, significant simulation speedup is achieved while studying the system behavior. TLMs can be purely at the software level, or at the hardware level by abstracting the notion of time. They can be described in any system-level description language.

TLM 2.0, defined and adopted by Open SystemC Initiative (OSCI) defines two coding styles to specify protocols at different modeling abstractions; loosely-timed (LT) TLM and approximately-timed TLM. In loosely-timed model an abstract notion of timing (if any)

is provided. Approximately-Timed model contains more detailed timing information as compared to LT model. The level of timing detail could be an integer number or could be clock cycle count accurate, but not clock cycle-accurate. Loosely-timed (LT) modeling approach is suitable for early software-level analysis. Approximately-timed (AT) models on the other hand are very useful for hardware performance modeling and analysis at an early phase of the design process. Therefore, approximately-timed modeling approach has been referenced to model the communication between components in this work. The protocol model itself is briefly discussed below in general. In this discussion, a point-to-point producer-consumer transaction model is considered with producer referenced as the initiator and consumer as the target.

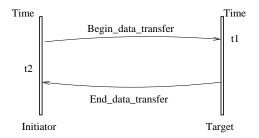

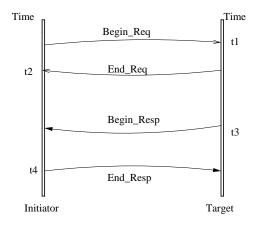

## Two-Phase and Four-Phase AT TLM Approach

Modeling interconnect protocol for performance prediction requires a level of timing detail. OSCI TLM2 describes two base protocol specifications with different timing phases. They are categorized as two-phase AT modeling and four-phase AT modeling approaches. Two phase AT implementation consists of two phases (timing points) to model the protocol. For this work, a combination of two-phase and four-phase AT protocol has been used to model the communication protocol at the transaction level, with PCIexpress protocol specification as a reference. Both two-phase and four-phase AT TLM models are used for this work. All timing phases are non-blocking calls. The two timing phases of 2-phase AT protocol are:

- 1. (Begin) Request Initiator to target

- 2. (End) Response Target to initiator

The four timing phases of the 4-phase AT protocol are:

- 1. Begin Request (Beg-Req)- Start of transaction from initiator to target

- 2. End Request (End-Req) Acknowledgement from the target to initiator

Fig. 2.8: TLM Two-Phase Protocol

Fig. 2.9: TLM Four-Phase Protocol

- 3. Begin Response (Beg-Rsp) Begin the transaction from target to initiator

- 4. End Response (End-Rsp) End of transaction from initiator to target

The timing information at each phase of the protocol can be specified explicitly by the **wait()** statement or implicitly by noting the time taken by each step in the protocol. Figure 2.9 shows a typical implementation of the protocol. Using the AT-TLM coding style and the two-phase, four-phase base protocol model, communication interfaces can be modeled at different timing abstraction levels.

Specifically, to model the interaction between cores in a many-core based systems, functional and architects TLM abstraction views are useful. The architects view transaction level model is well suited for architectural exploration, performance modeling and estimation at early stage of design. Timing information is specified as an integer at this abstract level and can be refined to clock cycle count accurate. Therefore, this view is referenced while specifying the interconnect functionality in this work. A typical system

description would consist of the instruction followed by its delay specification for performance analysis. A set of function calls are described for modeling the communication aspect. Open Cores Protocol - IP (OCP-IP), provides detailed description of various TLM views that includes functional view, programmers view and verification view for different research and development group. Chapter 5 provides code snippets used in this work as examples of functional and architectural view specification and modeling style.

## Communication/Interface Channels

During the initial phase of this work, SystemC based modeling and specification was studied. Although not used directly, the following paragraph summarizes some advances that are applicable with other HDLs. To broaden the usage of system-level HDLs (SystemC in this work) for efficient simulation, *converter channels* as means for connecting dissimilar models of computation have been developed in [51]. These adaptable channels are required to connect heterogeneous models of computation due to their dissimilar behavior. Of particular interest for this work is the connection between a BKPN MOC and TSDF MOC. BKPN model has an abstract notion of time. Conversion to TSDF is essentially a process of adding more detailed timing information. Considering the behavior of TSDF, the timing information is essentially discretized. Similarly, interfaces for other computation models are developed.

This work utilizes SystemVerilog based TLM as the language builds upon widely used Verilog HDL and newer constructs defined in the IEEE 1800 standard are particularly useful for research and development in this work. Authors in [105] provide a set of SystemVerilog snippets that model asynchronous communication between two systems. In similar work, a handshaking protocol based interface spec. is provided that can be used in async comm. These facilities can be used as an input specification for the developed early prediction method.

## 2.5 Summary - Need for Early Performance Prediction

The goal of this chapter was to provide the reader a perspective of the need for early performance prediction, the contribution of this work. In this context, the VLSI design flow overview was first presented highlighting the main steps from HDL specification to final tapeout. Each phase of the design flow in itself comprises of multiple steps that perform specific functions to meet the requirements. During each design phase, simulation plays an indispensable role providing valuable feedback to the tool (and user) and several tools exist that perform accurate simulation (Examples: SPICE, ModelSim). This work focusses on mapping system description used at two different abstraction levels for efficient simulation to obtain a better estimate of performance.

Specifically, a methodology for early performance prediction that aids an architect or system designer to better predict system performance at an early stage of design is developed. The method maps a SystemVerilog based system spec. (used for efficient simulation) to the generated IBIS models based netlist. This work is useful because it aims to reduce the design cycle time by providing a more accurate estimate at an early design phase, aiding faster time-to-market requirement. Aspects related to early performance prediction are discussed in subsequent chapters. The next chapter describes the model generation tool development. Given an IBIS file of a circuit, the tool estimates the system performance parameters and generates the macromodel.

# CHAPTER 3

# A METHOD TO GENERATE MODELS OF CIRCUITS SPECIFIED BY IBIS MODELS

#### 3.1 Introduction

At the circuit-level, behavioral signal integrity simulations are performed with IBIS models as discussed in Chapter 1. A serial link has to be represented by a netlist to employ signal integrity simulation tools to evaluate performance. For the serial link, rise time and fall time information of the signal is required. This infomation needs to be extracted from IBIS model file. This chapter describes methods for generating models of a circuit specified by IBIS model file. The developed model generation method generates a macromodel that comprises of the estimates of poles, rise time and fall time of the specified circuit, described in detail in this section. For the model generation tool to estimate the aforementioned parameters, the data must first be fitted to a mathematical model. Then the model parameters can be determined. Using circuit and systems theory, the model parameters are used to obtain the macromodel. In this work, Weibull cumulative distribution function (WCDF) has been selected as the regression function. With this regression function, regression analysis is performed on the IBIS V/t data. Moment matching method is then employed to obtain

the system poles.

The remainder of the chapter is organized as follows: Section 3.2 discusses the background on moment matching method applied for estimating system poles. Section 3.3 describes the selected mathematical model, the Weibull distribution function and previous work on development of Weibull delay metric based on the distribution function. This would motivate the reason for using Weibull distribution function for this work. Section 3.4 presents a method to generate a macromodel of a circuit specified by IBIS models. The method is summarized as a pseudocode for reference. Section 3.5 provides the results and implementation details. This is followed by another method for macromodel generation. Due to "human" constraints, this hasn't been implemented, however the method itself is well documented. Section 3.6 summarizes the developed method.

# 3.2 Background on Moment Matching

## 3.2.1 Asymptotic Waveform Evaluation and Obtaining System Poles

Asymptotic waveform evaluation is a general technique for simulation of large linear(ized) circuits [28]. In AWE, a form of Pade's approximation is employed to approximate a system transfer function to a reduced order model. Once the AWE model is developed, it can be reused for different applications. Consider a lumped linear time-invariant (LTI) system. This system can be described by the following state equation:

$$\dot{\mathbf{x}} = \mathbf{A}\mathbf{x} + \mathbf{B}\mathbf{u} \tag{3.1}$$

Here,  $\mathbf{u}$  is a generic input excitation vector and  $\mathbf{x}$  is an n-dimensional state vector. The solution for this is the following homogeneous equation [28]:

$$\dot{\mathbf{x}_h} = \mathbf{A}.\mathbf{x_h} \tag{3.2}$$

The Laplace transform for the above equation is:

$$X_h(s) = (sI - A)^{-1}x_h(0)$$

(3.3)

The equation above can be approximated by expanding it as a Taylor series about s = 0, shown below.

$$X_h(s) = -A(I + A^{-1}s + A^{-2}s^2 + .....)x_h(0)$$

(3.4)

Now, the transfer function of this system in terms of circuit moments  $(m_{ci})$  can be expressed as follows:

$$H(s) = m_{c0} + m_{c1}s + m_{c2}s^2 + m_{c3}s^3 + \dots {3.5}$$

Here, the generalized circuit moments are defined as:

$$m_{ci} = \frac{(-1)^i}{i!} \int_0^\infty t^i e^{-st} dt, \quad i = 0, 1, 2...$$

(3.6)

The circuit moments can be obtained by comparing Equations 3.4 and 3.5 as it follows from the definition of Laplace transform:

$$X(s) = \int_0^\infty x(t).e^{-st}dt = \sum_{k=0}^\infty \frac{(-1)^k}{k!} s^k \int_0^\infty t^k.e^{-st}dt$$

(3.7)

These time-domain circuit moments are now matched to a lower order frequency domain function in poles and residue form (Pade's approximation):

$$H(s) = \sum_{l=0}^{q} \frac{k_l}{s - p_l}$$

(3.8)

As many circuit moments from the equation above can be matched to a lower order model.

Note:

AWE method for timing analysis uses Pade's approximation to evaluate the lower order model. The idea of Pade's approximation is to approximate a transfer function H(s) by an order-limited rational function  $H_q(s)$ , where q is the order.

$$H_q(s) = \frac{1 + b_1 s + b_2 s^2 + \dots + b_n s^n}{1 + a_1 s + a_2 s^2 + \dots + a_n s^m}$$

(3.9)

where, n = m - 1.

To obtain a  $q^{th}$  order reduced model of an  $n^{th}$  order system, 2q circuit moments are required. Pade's approximation then converts these 2q moments into a  $q^{th}$  order reduced model. Poles and residues can be calculated using the steps outlined in [28].

#### 3.2.2 Reduced Pole Approximation

In [29], the authors present a *two-pole approximation* that is derived from the first three moments of the impulse response of the circuit/system. The system transfer function is approximated to the first three moments of the impulse response. Based on these circuit moments, two system poles are obtained by a set of equations. The first two poles are approximated/calculated to the first three moments using the following equations [29]:

$$p_1 = -\left(\frac{m_{c2}}{m_{c3}}\right) \tag{3.10}$$

$$p_2 = p_1 \cdot \left( \frac{m_{c0} \cdot m_{c2} - m_{c1}^2}{m_{c1} \cdot m_{c3} - m_{c2}^2} \right)$$

(3.11)

where,  $m_{ci}$ , i = 0, 1, 2, ... are the circuit moments.

The approximate residues can be obtained from the two poles and three circuit moments [29]. The approximate poles above are derived with the aid of AWE, discussed earlier in this chapter. The transfer function for a given system can be approximated by a reduced

order model based on Pade's approximation, the denominator can be further approximated by considering coefficients of 's' upto the second order. In [28], it was shown that the ratio of successive moments asymptotically approaches to the value of the dominant pole, i.e.,

$$p_1 = \lim_{j \to \infty} \left( \frac{m_{cj}}{m_{c(j+1)}} \right) \tag{3.12}$$

To obtain two poles, the first three moments of the circuit are required. They can be calculated by the following set of equations: The ratio of two successive poles in terms of circuit poles,  $\frac{p_j}{p_{j+1}}$  can be expressed as below [29]:

$$p_{2} = p_{1} \cdot \left( \frac{1 + \frac{k_{2}}{k_{1}} \cdot (\frac{p_{1}}{p_{2}})^{j+1} + \frac{k_{3}}{k_{1}} \cdot (\frac{p_{1}}{p_{3}})^{j+1} + \dots + \frac{k_{n}}{k_{1}} \cdot (\frac{p_{1}}{p_{n}})^{j+1}}{1 + \frac{k_{2}}{k_{1}} \cdot (\frac{p_{1}}{p_{2}})^{j+2} + \frac{k_{3}}{k_{1}} \cdot (\frac{p_{1}}{p_{3}})^{j+2} + \dots + \frac{k_{n}}{k_{1}} \cdot (\frac{p_{1}}{p_{n}})^{j+2}} \right)$$

(3.13)

Assuming that the given circuit has been approximated to 'N' poles, the  $j^{th}$  moment is related to poles and residues by the following expression:

$$m_{cj} = \sum_{i=1}^{N} \frac{k_i}{(p_i)^{j+1}} \tag{3.14}$$

The detailed derivation of the equations above are given in [29]. The same equations can be used to obtain additional poles of the system from higher order moments. The presented pole approximation method has been applied to estimate the poles of the system in the developed model generation method to be described in the next section. In [36], the authors present a method to obtain delay and slew metrics based on the first three circuit moments. The application is for interconnects modeled as RC trees and more accurately estimating the delay values for near end and far end nodes. In the following section, a survey of delay metrics proposed based on various probability distributions is discussed in some detail.

#### 3.2.3 Delay Metrics Based on Distribution Function

For circuits modeled as RC model, delay metrics have been proposed that define and calculate delay metrics based on probability distribution functions. Delay metrics based on the Gamma, Weibull, Lognormal and Beta distribution functions have been reported in earlier work. Weibull distribution function based delay metric is of particular interest as it has been applied in this work.

#### 3.2.4 Moment Matching Background

Moment matching method involves matching the circuit moments to the central moments of a selected distribution function. Several works explore this method in various domains. Here, this method along with regression, estimates the poles of a circuit specified by tabulated simulated data value, a contribution [38].

Recall that the transfer function of an LTI system in terms of circuit moments  $(m_{ci})$  is given by:

$$H(s) = m_{c0} + m_{c1}s + m_{c2}s^2 + m_{c3}s^3 + \dots {(3.15)}$$

Circuit moments are defined as:

$$m_{ci} = \frac{(-1)^i}{i!} \cdot \int_0^\infty t^i \cdot e^{-st} dt, \quad i = 0, 1, 2...$$

(3.16)

The central moments for a particular distribution function or p.d.f. are given in [32]. The goal here is to match these to the circuit moments given by Equation 3.16. From the above equations, matching the circuit moments and moments of a distribution, we obtain the following relations:

$$m_{c1} = -m_1 (3.17)$$

$$m_{c2} = 2!.m_2 - m_1^2 (3.18)$$

$$m_{c3} = -3!.m_3 + 3m_1m_3 - 2m_2^2 (3.19)$$

Based on this, the relation between circuit moments  $(m_{ci})$  and central moments  $(\mu_i)$  can be obtained. Weibull distribution function is specifically applied in this work. To obtain the macromodel, WCDF is used as the regression function. This is discussed in the following section.

# 3.3 Weibull Distribution Function as a Regression Function

Weibull distribution function is often used in reliability engineering. There are two models of Weibull distribution function; two parameter and three parameter. For the presented work, two-parameter Weibull distribution function has been used and will therefore be the focus of the following paragraphs. A two-parameter Weibull probability density function (WPDF) with parameters ' $\alpha$ ' and ' $\beta$ ' is defined as:

$$P(t) = \alpha . \beta^{\alpha} . t^{\alpha - 1} . e^{-(t/\beta)^{\alpha}}$$

(3.20)

Where, t > 0 and  $\alpha$ ,  $\beta > 0$ .

Parameter ' $\alpha$ ' is known as shape parameter.

Parameter ' $\beta$ ' is known as scale parameter.

The Weibull cumulative distribution function (WCDF) is defined as:

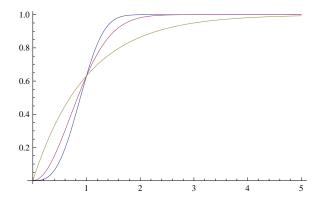

Fig. 3.1: Weibull c.d.f. for different parameter values

$$F(t) = 1 - e^{-(\frac{t}{\beta})^{\alpha}} \tag{3.21}$$

For  $\alpha$  < 1,  $\alpha$  = 1 and  $\alpha$  > 1, three basic shapes of WCDF can be obtained as shown in Figure 3.5.

It can be seen from Figure 3.5 that the WCDF is able to model various waveform shapes that a circuit modeled as RC network can take for a step (or ramp) input. Important properties of the distribution function are well catalogued and given below. The *mean*, *variance* and *skewness* of Weibull distribution function is given by:

$$\mu = \beta . \Gamma(1 + \theta) \tag{3.22}$$

$$\sigma^2 = \beta^2 \cdot (\Gamma(1+2\theta) - \Gamma^2(1+\theta))$$

$$\sigma = \sqrt{\beta^2 \cdot (\Gamma(1+2\theta) - \Gamma^2(1+\theta))}$$

(3.23)

$$\gamma = \frac{(2.\Gamma(1+1\theta)^3 - 3\Gamma(1+1\theta)\Gamma(1+2\theta) + \Gamma(1+3\theta))}{(-\Gamma(1+1\theta)^2 + \Gamma(1+2\theta))^{3/2}}$$

(3.24)

where,  $\theta = 1/\alpha$

Moment matching technique involves matching the moments of a selected distribution to the moments of the underlying circuit. Since, the simulation data is provided, first regression is required before applying moment matching. The details of this methodology is

discussed in the next section.

#### 3.3.1 Weibull c.d.f. Based Regression

The mathematical background required for model generation methodology is discussed in this section. Regression analysis is first performed with IBIS data to regression coefficients. Using the estimated value of these coefficients, moment matching method is applied to obtain the estimated poles, rise time and fall time of the specified circuit. The steps for the presented methodology is described in detail below. Weibull distribution function is reviewed as it is the selected regression function in this work. Then, regression analysis with Weibull distribution function is described.

Regression Function: Two parameter Weibull distribution function was introduced in the previous chapter. Here, the key properties are provided for reference. As was noted earlier, Weibull based delay metric is computationally fast and relatively accurate. The p.d.f., c.d.f., mean and variance of a Weibull distribution with parameters ' $\alpha$ ' and ' $\beta$ ' are given by:

$$P(t) = \alpha . \beta^{\alpha} . t^{\alpha - 1} . e^{-\left(\frac{t}{\beta}\right)^{\alpha}}$$

(3.25)

$$F(t) = 1 - e^{-(\frac{t}{\beta})^{\alpha}}$$

(3.26)

$$\mu = \beta.\Gamma(1+\theta) \tag{3.27}$$

$$\sigma^{2} = \beta^{2}.(\Gamma(1+2\theta) - \Gamma^{2}(1+\theta))$$

(3.28)

Where, t > 0 and  $\alpha$ ,  $\beta > 0$ , and  $\theta = 1/\alpha$ .

The Gamma function [110] is given by:  $\Gamma(t) = \int_0^\infty y^{x-1}.e^{-y}dy$ . Regression analysis is performed on IBIS model file by fitting the Weibull CDF to the transient analysis data. The rise and fall times are obtained with the estimated values of ' $\alpha$ ' and ' $\beta$ '. Then, applying moment matching technique, system poles are determined (estimated). Depending on the application, these parameters can be utilized to obtain other parameters. Detailed

discussion follows.

Regression Analysis: Ordinary least square regression method has been applied for this work with Weibull c.d.f. as the regression function due to its simple functional form and ability to fit various waveform shapes. For this function, least square regression analysis is performed as follows. Consider the WCDF, reproduced below:

$$F(t) = 1 - e^{-(\frac{t}{\beta})^{\alpha}}$$

(3.29)

If we take the natural logarithm on both sides of the equation above, we get:

$$\ln F(t) = \ln[1 - e^{-(t/\beta)^{\alpha}}]$$

$$\ln F(t) = \ln(1) - \ln(e^{-(t/\beta)^{\alpha}})$$

$$\ln F(t) = (t/\beta)^{\alpha}$$

Taking natural logarithm again,

$$\ln . \ln F(t) = \ln (t/\beta)^{\alpha}$$

$$\ln . \ln F(t) = \alpha . \ln(t - \beta)$$

$$\ln . (\ln F(t)) = \alpha . \ln(t) - \alpha . \ln(\beta)$$

(3.30)

Equation 3.30 above is now of the form of a linear regression line,  $y = \beta_0.x + \beta_1$ , where  $y = \ln .(\ln F(t))$ ,  $\beta_0 = \alpha$  and  $\beta_1 = -\alpha.\ln(\beta)$ . Least square regression can be performed on Equation 3.30 following the steps outlined earlier. The estimated values of ' $\alpha$ ' and ' $\beta$ ', ' $\alpha$ ' and ' $\beta$ ' respectively, are then used for obtaining the system poles, rise time and fall time of the circuit specified by IBIS model generated by the model generator. The model generation method is discussed next.

Fig. 3.2: Typical IBIS model V/t Rising Waveform

#### 3.4 IBIS Models Based Macromodel Generation Method

This section describes the implemented model generation tool. The model generator accepts IBIS voltage-time data as input and generates the estimated values of rise time, fall time and poles of the system. The methodology consists of two steps: macromodeling and parameter estimation. In the next chapter, this work is applied to aid early performance prediction.

*Macromodeling*: A macromodel is an approximation of an unknown function [24] [25]. Constructing a macromodel consists of the following steps: *data generation* and *regression*. IBIS model data generation and formatting steps were described in detail in Chapter 2. Regression is performed on the tabulated data in IBIS models. Regression analysis involves computing the coefficients of the selected functional form. In this work, Weibull cumulative distribution function has been used as the regression function. This is because it can fit various waveform shapes of the Voltage-time (V/t) curves of an IBIS model obtained with transient analysis of circuits as shown in Figure 3.2. The regression method applied here is discussed next.

Weibull c.d.f. Based Macromodel: The Weibull cumulative distribution function (WCDF), with parameters ' $\alpha$ ' and ' $\beta$ ' is given as:

$$F(t) = 1 - e^{-(\frac{t}{\beta})^{\alpha}} \tag{3.31}$$

#### Component

- -Technology

- -Rise time (tr)

- -Fall time (tf)

- -Component Perf. Parameters

Fig. 3.3: IBIS Component Characterization

The key statistical characteristics, mean  $(\mu)$ , variance $(\sigma^2)$  and skewness  $(\gamma)$  of the distribution function are given in terms of the Gamma function  $(\Gamma(t))$  in Equation 3.27 and Equation 3.28.

Advantages of Weibull c.d.f. as Macromodel:

- 1. The parameters of Weibull distribution function can be calculated relatively easily as they are based on the Gamma function.

- 2. A simple model can be obtained as two parameters are sufficient for regression.

A typical V/t rising waveform obtained from an IBIS file is shown in Figure 3.2. As can be seen, the rising transient response waveform is a monotonically increasing curve. Therefore, the data-set can be fitted to a distribution function. In addition to being monotonically increasing, the data set is also positively skewed. Due to these characteristics, Gamma distribution, Beta distribution [34] and Weibull distribution functions may be used as the regression function. Each of these distribution functions along with associated delay and slew metrics were discussed in background work. Weibull c.d.f (WCDF) is selected as the macromodel as the parameters of WCDF are based on the Gamma function, which can be calculated quickly and accurately. In addition, Weibull c.d.f takes a simple functional form. Figure 3.5 shows the Weibull c.d.f. waveform for different values of its parameters  $\alpha$  and  $\beta$ .

By changing the values of ' $\alpha$ ' and ' $\beta$ ' of WCDF, various rising and falling waveform data of IBIS models (examples include Figures 3.2 and 3.4) can be fitted. In the developed model generation tool, regression analysis is performed over V/t data of an IBIS file by

Fig. 3.4: Inverter: V/t rising waveform

Fig. 3.5: Weibull c.d.f.

fitting the data to a Weibull CDF and obtaining the estimated values of its parameters  $\hat{\alpha}$ ,  $\hat{\beta}$ . With this information, the mean and variance of the distribution is estimated from Equations 3.36 and 3.37. Once the parameters are estimated, rise and fall times can be obtained directly by solving Equation 3.29 for the 20% delay value and 80% delay value. Solving Equation 3.29 for time  $t_{\phi}$  and substituting F(t) to be ' $\phi$ ' as in [20], we get:

$$t_{\phi} = \beta . \ln(1/(1-\phi))^{\theta} \tag{3.32}$$

The 20% and 80% delay points on the waveform can be calculated by substituting  $\phi = 0.2$  and  $\phi = 0.8$  respectively in the above equation.

$$t_{0.2} = \beta . \ln(1/(1 - 0.2))^{\theta} = \beta . \ln(0.125)^{\theta}$$

(3.33)

$$t_{0.8} = \beta . \ln(1/(1 - 0.8))^{\theta} = \beta . \ln(5)^{\theta}$$

(3.34)

Therefore, the slew (rise time and fall time) values can be obtained by subtracting Equation 3.33 from Equation 3.34. The estimated value of rise time and fall time through the proposed method are more accurate as the recorded data provided in IBIS file is the analog output of a digital pin.

Parameter Estimation: Once the rise and fall times are estimated, the next step of the model generation tool is estimating poles of the component or circuit that the IBIS file represents. Consider that the simulated component in Figure 2.2 from Chapter 2 is a CMOS inverter. When a step input is applied to the inverter, it's output goes low, the pull-up section of the output buffer is activated and rising waveform is obtained. Similarly, pull-down section of the output buffer is activated when input of inverter is logic low. The V/I curves for the output buffer is obtained with transistors fully on as discussed previously [10]. The steps for parameter estimation are discussed below.

1. Moment Matching: After obtaining the coefficients of the regression function, rise time and fall time were estimated. The next step of model generation is to estimate the poles of the circuit. The key idea applied here is *moment matching*, a technique where the moments of the selected distribution function are matched to the moments of the circuit. The underlying circuit is assumed to be modeled as an RC circuit.

It has been shown that the impulse response of a RC circuit can be modeled by a probability density function [20] as it meets the following requirements:

$$h(t) > 0 \,\forall t$$

$$\int_0^\infty h(t)dt = 1 \tag{3.35}$$

It is well known that the integral of the impulse function is the step function. The step response of an LTI system would therefore be a cumulative distribution function. The key step in moment matching technique is to match the mean, variance, skewness and

other higher order central moments of a selected distribution function to the moments of the impulse response of the circuit. Since Weibull distribution function is used here, it's mean and central moments are matched to the circuit moments. Moment matching equations are given below:

$$\mu = -m_{c1} \tag{3.36}$$

$$\sigma^2 = 2m_{c2} - m_{c1}^2 \tag{3.37}$$

The next step to relate component transient response and its moments is to match the circuit moments of the simulated component (VLSI inverter) to the mean and variance of the proposed macromodel (Weibull CDF). Matching Equation 3.27 to Equation 3.36 and Equation 3.28 to Equation 3.37, the following relationship is obtained between the circuit moments and the mean and central moments of the Weibull distribution function:

$$m_{c1} = -\beta.\Gamma(1+\theta) \tag{3.38}$$

$$2.m_{c2} - m_{c1}^{2} = \beta^{2}.(\Gamma(1+2\theta) - \Gamma^{2}(1+\theta))$$

$$m_{c2} = 0.5.\beta^{2}.(\Gamma(1+2\theta) - \Gamma^{2}(1+\theta) + \Gamma^{2}(1+\theta))$$

$$m_{c2} = \frac{1}{2}\beta^{2}.(\Gamma(1+2\theta))$$

(3.39)

Similarly, higher order circuit moments can be obtained by matching them to higher order central moments of Weibull distribution function. Once the circuit moments are calculated, as many system poles as required can be estimated.

2. Estimating Poles: Once the circuit moments are calculated, poles of the transfer function of the circuit can be obtained by matching the transfer function to a reduced order Pade's approximation as discussed in the previous chapter [28]. Approximate poles are calculated in this work using the *three moments approximation* method [36], discussed in previous chapter, for a LTI system described by a reduced order transfer function, the first two poles are approximated with the first three circuit moments by the following equation:

$$p_{1} = -\left(\frac{m_{c2}}{m_{c3}}\right)$$