## **Syracuse University**

## **SURFACE**

Electrical Engineering and Computer Science -Dissertations

College of Engineering and Computer Science

5-2013

## Transparent and Precise Malware Analysis Using Virtualization: From Theory to Practice

Lok Kwong Yan Syracuse University

Follow this and additional works at: https://surface.syr.edu/eecs\_etd

Part of the Computer Sciences Commons

#### **Recommended Citation**

Yan, Lok Kwong, "Transparent and Precise Malware Analysis Using Virtualization: From Theory to Practice" (2013). Electrical Engineering and Computer Science - Dissertations. 332. https://surface.syr.edu/eecs\_etd/332

This Dissertation is brought to you for free and open access by the College of Engineering and Computer Science at SURFACE. It has been accepted for inclusion in Electrical Engineering and Computer Science - Dissertations by an authorized administrator of SURFACE. For more information, please contact surface@syr.edu.

## ABSTRACT

Dynamic analysis is an important technique used in malware analysis and is complementary to static analysis. Thus far, virtualization has been widely adopted for building fine-grained dynamic analysis tools and this trend is expected to continue. Unlike User/Kernel space malware analysis platforms that essentially co-exist with malware, virtualization based platforms benefit from *isolation* and *fine-grained instrumentation* support. Isolation makes it more difficult for malware samples to disrupt analysis and fine-grained instrumentation provides analysts with low level details, such as those at the machine instruction level. This in turn supports the development of advanced analysis tools such as dynamic taint analysis and symbolic execution for automatic path exploration.

The major disadvantage of virtualization based malware analysis is the loss of semantic information, also known as the *semantic gap* problem. To put it differently, since analysis takes place at the virtual machine monitor where only the raw system state (e.g., CPU and memory) is visible, higher level constructs such as processes and files must be reconstructed using the low level information. The collection of techniques used to bridge semantic gaps is known as Virtual Machine Introspection.

Virtualization based analysis platforms can be further separated into emulation and hardware virtualization. Emulators have the advantages of flexibility of analysis tool development and efficiency for fine-grained analysis; however, emulators suffer from the transparency problem. That is, malware can employ methods to determine whether it is

executing in an emulated environment versus real hardware and cease operations to disrupt analysis if the machine is emulated. In brief, emulation based dynamic analysis has advantages over User/Kernel space and hardware virtualization based techniques, but it suffers from semantic gap and transparency problems.

These problems have been exacerbated by recent discoveries of anti-emulation malware that detects emulators and Android malware with two semantic gaps, Java and native.

Also, it is foreseeable that malware authors will have a similar response to taint analysis.

In other words, once taint analysis becomes widely used to understand how malware operates, the authors will create new malware that attacks the imprecisions in taint analysis implementations and induce false-positives and false-negatives in an effort to frustrate analysts.

This dissertation addresses these problems by presenting concepts, methods and techniques that can be used to transparently and precisely analyze both desktop and mobile malware using virtualization. This is achieved in three parts. First, precise heterogeneous record and replay is presented as a means to help emulators benefit from the transparency characteristics of hardware virtualization. This technique is implemented in a tool called V2E that uses KVM for recording and TEMU for replaying and analysis. It was successfully used to analyze real-world anti-emulation malware that evaded analysis using TEMU alone. Second, the design of an emulation based Android malware analysis platform that uses virtual machine introspection to bridge both the Java and native level semantic gaps as well as seamlessly bind the two views together into a single view is presented. The core introspection and instrumentation techniques were implemented in a new analysis platform called DroidScope that is based on the Android emulator. It was

successfully used to analyze two real-world Android malware samples that have cooperating Java and native level components. Taint analysis was also used to study their information ex-filtration behaviors. Third, formal methods for studying the sources of false-positives and false-negatives in dynamic taint analysis designs and for verifying the correctness of manually defined taint propagation rules are presented. These definitions and methods were successfully used to analyze and compare previously published taint analysis platforms in terms of false-positives and false-negatives.

# TRANSPARENT AND PRECISE MALWARE ANALYSIS USING VIRTUALIZATION: FROM THEORY TO PRACTICE

by

## Lok Kwong Yan

B.S. Polytechnic University, 2004M.S. Polytechnic University, 2004

Dissertation

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in

Computer & Information Science and Engineering

Syracuse University May 2013  $\ \ \, \bigcirc \ \,$  Copyright 2013

Lok Kwong Yan

All Rights Reserved

To my grandfather, my parents, my wife, son and daughter.

#### ACKNOWLEDGMENTS

I would like to express my sincerest gratitute to the people who made this dissertation possible.

To my advisor, Dr. Heng Yin, whose vision, expertise and attention to detail not only guided my research and kept me on track, but also showed me the importance of being a balanced researcher. You taught me that communication is just as important as the research work itself and that I should strive to do my best in both areas.

To my Master's advisor and friend, Dr. Nasir Memon. You introduced me to computer security and planted the seed that has grown into this dissertation. My career would have been completely different without your initial and continued support and encouragement.

To my labmates, Aravind, Mu, Manju, Eknath, Qian, Andrew and Xunchao. Not to undermine your help in refining my ideas, conducting research and gathering data, but what I appreciate most are the social interactions with you. Our more mundane, non-technical conversations helped relieve the many stresses of working in an academic research lab.

To my previous supervisor at the Air Force Research Laboratory, Information Directorate, Mr. Duane Gilmour, who understood the importance of dedicating time towards research and was instrumental in ensuring that I had the time to do so.

Most important of all, to my wife Victoria. This dissertation would not have been possible without your behind-the-scenes support. Taking care of our infant son while

balancing all of your other responsibilities must have been more difficult and stressful than my research. For that, I am forever indebted to you.

## TABLE OF CONTENTS

|    |            |         |                                         | Page |  |  |  |  |  |  |  |  |  |  |

|----|------------|---------|-----------------------------------------|------|--|--|--|--|--|--|--|--|--|--|

| Al | BSTR       | ACT     |                                         | i    |  |  |  |  |  |  |  |  |  |  |

| LI | ST O       | F TAB   | LES                                     | xiii |  |  |  |  |  |  |  |  |  |  |

| LI | ST O       | F FIGU  | JRES                                    | xiv  |  |  |  |  |  |  |  |  |  |  |

| 1  | Intro      | duction | 1                                       | 1    |  |  |  |  |  |  |  |  |  |  |

| 2  | Background |         |                                         |      |  |  |  |  |  |  |  |  |  |  |

|    | 2.1        | Virtua  | lization                                | 8    |  |  |  |  |  |  |  |  |  |  |

|    |            | 2.1.1   | Hardware Virtualization                 | 11   |  |  |  |  |  |  |  |  |  |  |

|    |            | 2.1.2   | The QEMU Emulator                       | 14   |  |  |  |  |  |  |  |  |  |  |

|    |            | 2.1.3   | The Kernel Based Virtual Machine (KVM)  | 17   |  |  |  |  |  |  |  |  |  |  |

|    | 2.2        | Dynan   | nic Malware Analysis                    | 19   |  |  |  |  |  |  |  |  |  |  |

|    |            | 2.2.1   | Transparency                            | 22   |  |  |  |  |  |  |  |  |  |  |

|    | 2.3        | Andro   | id                                      | 23   |  |  |  |  |  |  |  |  |  |  |

|    |            | 2.3.1   | Android Malware Analysis                | 26   |  |  |  |  |  |  |  |  |  |  |

|    | 2.4        | Taint . | Analysis                                | 29   |  |  |  |  |  |  |  |  |  |  |

|    |            | 2.4.1   | Challenges                              | 32   |  |  |  |  |  |  |  |  |  |  |

|    |            | 2.4.2   | Noninterference                         | 35   |  |  |  |  |  |  |  |  |  |  |

|    | 2.5        | Summ    | ary                                     | 37   |  |  |  |  |  |  |  |  |  |  |

| 3  | Mak        | ing Em  | ulators Transparent                     | 39   |  |  |  |  |  |  |  |  |  |  |

|    | 3.1        | Introd  | uction                                  | 39   |  |  |  |  |  |  |  |  |  |  |

|    | 3.2        | Design  | Goals & Approach                        | 41   |  |  |  |  |  |  |  |  |  |  |

|    |            | 3.2.1   | Design Goals                            | 42   |  |  |  |  |  |  |  |  |  |  |

|    |            | 3.2.2   | Architecture                            | 43   |  |  |  |  |  |  |  |  |  |  |

|    |            | 3.2.3   | Precise Heterogeneous Record and Replay | 44   |  |  |  |  |  |  |  |  |  |  |

|    | 3.3        | Transı  | parent Recorder                         | 48   |  |  |  |  |  |  |  |  |  |  |

|     |           |                                                          | Page |

|-----|-----------|----------------------------------------------------------|------|

|     | 3.3.1     | Mediating Recording Realm                                | 48   |

|     | 3.3.2     | Basic Scheme                                             | 50   |

|     | 3.3.3     | Other Inputs                                             | 53   |

|     | 3.3.4     | Optimizations                                            | 54   |

|     | 3.3.5     | Bridging the Semantic Gap                                | 56   |

|     | 3.3.6     | Shadow Time Stamp Counter                                | 56   |

|     | 3.3.7     | Implementation                                           | 57   |

| 3.4 | Precis    | e Replayer                                               | 60   |

|     | 3.4.1     | Dynamic Binary Translation and QEMU                      | 61   |

|     | 3.4.2     | Changes for Precise Replay                               | 61   |

|     | 3.4.3     | Example Walk-through                                     | 64   |

|     | 3.4.4     | Implementation                                           | 65   |

| 3.5 | Evalua    | ation                                                    | 66   |

|     | 3.5.1     | Study of Existing Anti-emulation Attacks                 | 66   |

|     | 3.5.2     | Analyzing Malware on Existing Malware Analysis Platforms | 69   |

|     | 3.5.3     | Analyzing Real world Malware with V2E                    | 69   |

|     | 3.5.4     | Recorder Performance                                     | 73   |

| 3.6 | Discus    | ssion                                                    | 74   |

| 3.7 | Concl     | usion                                                    | 75   |

| Emu | ılation-l | based Android Malware Analysis                           | 77   |

| 4.1 | Introd    | luction                                                  | 77   |

| 4.2 | Archit    | secture                                                  | 78   |

| 4.3 | Instru    | mentation Interface                                      | 81   |

|     | 4.3.1     | Basic Instrumentation                                    | 81   |

|     | 4.3.2     | Application Programming Interfaces                       | 83   |

|     | 4.3.3     | Instrumentation Optimization                             | 85   |

|     | 4.3.4     | Taint Analysis                                           | 86   |

| 4.4 | Bridgi    | ing the Semantic Gaps                                    | 87   |

|     | 4.4.1     | Reconstructing the OS-level View                         | 87   |

4

|   |     |         |                                                           | Page |

|---|-----|---------|-----------------------------------------------------------|------|

|   |     | 4.4.2   | Reconstructing the Dalvik View                            | 91   |

|   |     | 4.4.3   | Symbol Information                                        | 100  |

|   | 4.5 | Plugir  | ns                                                        | 101  |

|   |     | 4.5.1   | Sample Plugin                                             | 101  |

|   |     | 4.5.2   | Analysis Plugins                                          | 102  |

|   | 4.6 | Evalua  | ation                                                     | 104  |

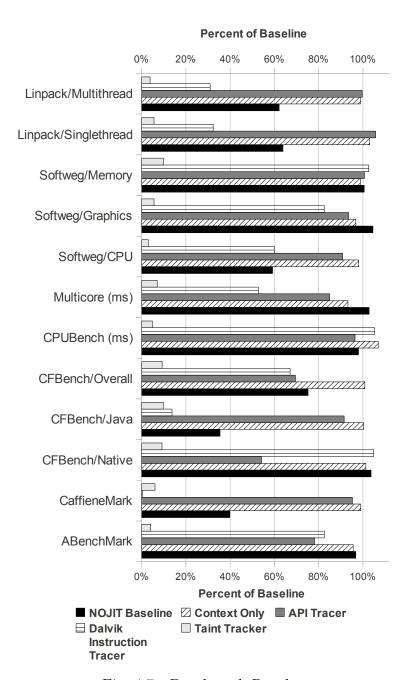

|   |     | 4.6.1   | Performance                                               | 105  |

|   |     | 4.6.2   | Analysis of DroidKungFu                                   | 108  |

|   |     | 4.6.3   | Analysis of DroidDream                                    | 114  |

|   | 4.7 | Discus  | ssion                                                     | 117  |

|   | 4.8 | Concl   | usion                                                     | 118  |

| 5 | Und | erstand | ling Dynamic Taint Analysis                               | 119  |

|   | 5.1 | Introd  | luction                                                   | 119  |

|   | 5.2 | Forma   | al Foundation                                             | 121  |

|   |     | 5.2.1   | Noninterference                                           | 122  |

|   |     | 5.2.2   | Taint Propagation Policies                                | 130  |

|   |     | 5.2.3   | Over- and Under-tainting                                  | 131  |

|   | 5.3 | Source  | es of Over- and Under-tainting                            | 132  |

|   |     | 5.3.1   | Over-tainting Due to Taint-granularity: Observation 5.2.1 | 133  |

|   |     | 5.3.2   | Analysis-granularity and Over-tainting: Observation 5.2.2 | 135  |

|   |     | 5.3.3   | Other Sources of Over- and Under-tainting                 | 138  |

|   | 5.4 | Gener   | eating an Accurate Policy for x86                         | 142  |

|   |     | 5.4.1   | Stage 1: Behavioral Definitions                           | 143  |

|   |     | 5.4.2   | Stage 2: General Information Flow                         | 145  |

|   | 5.5 | Result  | ts                                                        | 146  |

|   |     | 5.5.1   | Interpretation of Results                                 | 148  |

|   |     | 5.5.2   | Comparing With Previously Published Policies              | 152  |

|   |     | 5.5.3   | Refining Memcheck's Special Rules                         | 154  |

|   |     | 5.5.4   | Taint- and Analysis-granularity                           | 158  |

|    |                    |        |         |     |      |       |      |      |      |      |      |     |     |     |     |    |  |  |  |   |  | Page |

|----|--------------------|--------|---------|-----|------|-------|------|------|------|------|------|-----|-----|-----|-----|----|--|--|--|---|--|------|

|    |                    | 5.5.5  | ARM     | and | Dalv | /ik ] | Leve | el T | Tain | ting | g iı | ı D | roi | idS | coj | ре |  |  |  | • |  | 159  |

|    | 5.6                | Discus | sion .  |     |      |       |      |      |      |      |      |     |     |     |     |    |  |  |  | • |  | 162  |

|    | 5.7                | Conclu | usion . |     |      |       |      |      |      |      |      |     |     |     |     |    |  |  |  |   |  | 164  |

| 6  | Sum                | mary   |         |     |      |       |      |      |      |      |      |     |     |     |     |    |  |  |  |   |  | 165  |

| LI | LIST OF REFERENCES |        |         |     |      |       |      |      | 167  |      |      |     |     |     |     |    |  |  |  |   |  |      |

| V] | ТА                 |        |         |     |      |       |      |      |      |      |      |     |     |     |     |    |  |  |  |   |  | 177  |

## LIST OF TABLES

| Tabl | le                                                                                                                                                                                                                            | Page |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.1  | Operations and Corresponding Solutions                                                                                                                                                                                        | 48   |

| 3.2  | Survey of Emulation Detection Techniques                                                                                                                                                                                      | 67   |

| 3.3  | Analyzing Real-world Emulation-Resistant Malware with V2E                                                                                                                                                                     | 70   |

| 4.1  | Summary of DroidScope APIs                                                                                                                                                                                                    | 84   |

| 5.1  | Flow Type Results for x86 Instructions Flow Types: (U)p, (D)own, (I)n-place, (A)ll-around, (S)pecial, (N)ot-Supported, (S)pecial, (E)ax is tainted in cmpxchg, * - Zeroing Idiom, Boldface - Generated Policy is more precise |      |

| 5.2  | Summary of refined policies                                                                                                                                                                                                   | 156  |

| 5.3  | Summary of new rules using SMT2 prefix notation                                                                                                                                                                               | 158  |

## LIST OF FIGURES

| Figu | re                                                                                                                                                                                                                                                                                                     | Page |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

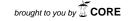

| 1.1  | A high level architectural diagram of an emulation based dynamic malware analysis platform                                                                                                                                                                                                             | 3    |

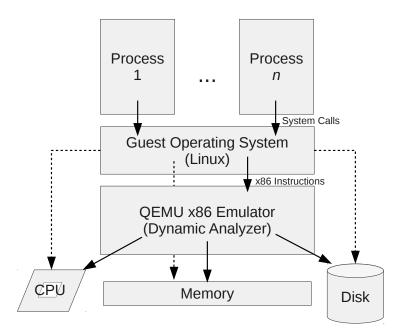

| 2.1  | Computer System Architecture [21]                                                                                                                                                                                                                                                                      | 8    |

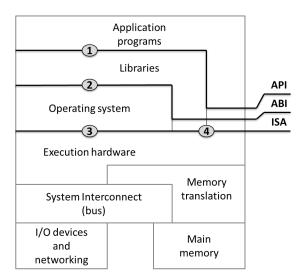

| 2.2  | Process VM [21]                                                                                                                                                                                                                                                                                        | 9    |

| 2.3  | System VM [21]                                                                                                                                                                                                                                                                                         | 10   |

| 2.4  | System Virtual Machine using KVM and QEMU                                                                                                                                                                                                                                                              | 17   |

| 2.5  | Memory translation in QEMU without KVM (a) and with KVM and TDP (b)                                                                                                                                                                                                                                    | 18   |

| 2.6  | Overview of Android System                                                                                                                                                                                                                                                                             | 24   |

| 2.7  | Control-flow tainting example                                                                                                                                                                                                                                                                          | 33   |

| 3.1  | Architecture Overview                                                                                                                                                                                                                                                                                  | 44   |

| 3.2  | adore_root_filldir                                                                                                                                                                                                                                                                                     | 49   |

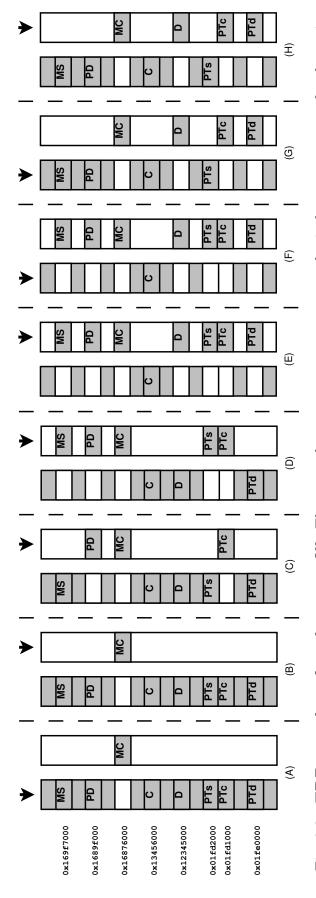

| 3.3  | <b>TDP</b> snapshots for adore_root_fill. The two columns represent two guest physical memory spaces for the main realm and the recording realm respectively. A shaded block represents a present page, while a blank block indicates an absent page. The arrow on top signifies which realm is active |      |

| 4.1  | DroidScope Overview                                                                                                                                                                                                                                                                                    | 79   |

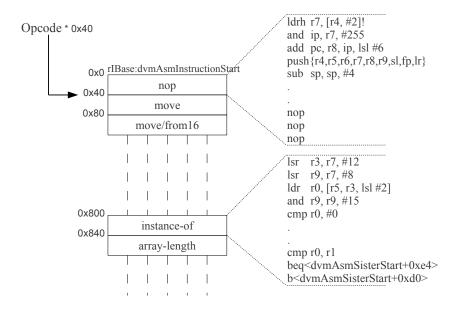

| 4.2  | Dalvik Opcode Emulation Layout in mterp                                                                                                                                                                                                                                                                | 92   |

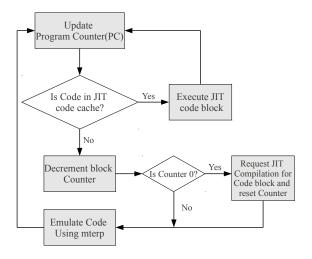

| 4.3  | High Level Flowchart of $mterp$ and JIT                                                                                                                                                                                                                                                                | 94   |

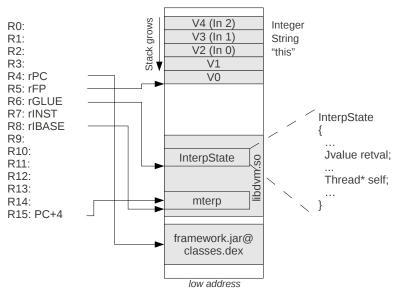

| 4.4  | Dalvik Virtual Machine State                                                                                                                                                                                                                                                                           | 97   |

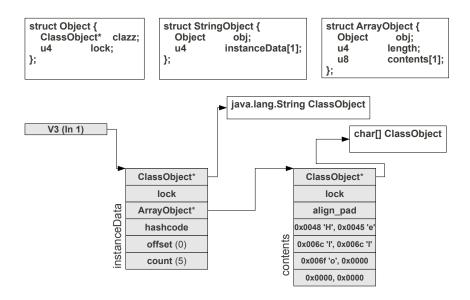

| 4.5  | String Object Example                                                                                                                                                                                                                                                                                  | 98   |

| 4.6  | Sample code for Dalvik Instruction Tracer                                                                                                                                                                                                                                                              | 102  |

| 4.7  | Benchmark Results                                                                                                                                                                                                                                                                                      | 106  |

| 4.8  | getPermission Pseudocode                                                                                                                                                                                                                                                                               | 109  |

| 4.9  | Annotated adbd trace                                                                                                                                                                                                                                                                                   | 112  |

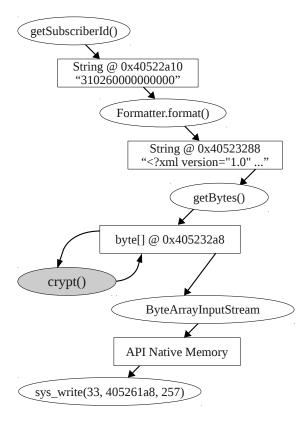

| 4.10 | Taint Graph for Droid Kung Fu                                                                                                                                                                                                                                                                          | 113  |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                            | Page |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.11 | Taint Graph for DroidDream                                                                                                                                                                                                                                                                                                                                                                                                    | 115  |

| 4.12 | Excerpt of Dalvik Instruction Trace for DroidDream. A Dalvik instruction entry shows the location of the current instruction in square brackets, the decoded instruction plus the values of the virtual registers in parenthesis. A taint log entry is indented and shows tainted memory being read or written to. The memory's physical address is shown in parenthesis and the total bytes tainted is represented by "len." | 116  |

| 5.1  | SMT2 Definition for ror dst, imm8                                                                                                                                                                                                                                                                                                                                                                                             | 144  |

| 5.2  | BAP IL for ror %eax, \$0x2                                                                                                                                                                                                                                                                                                                                                                                                    | 144  |

| 5.3  | SMT2 Definition and Test for add dst, src                                                                                                                                                                                                                                                                                                                                                                                     | 145  |

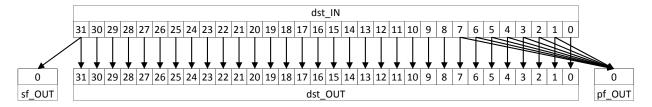

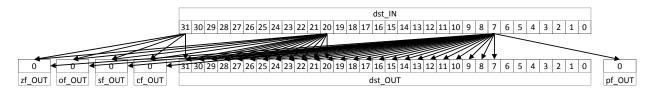

| 5.4  | Information flows of dst in the or instruction                                                                                                                                                                                                                                                                                                                                                                                | 148  |

| 5.5  | Information flow of bits 7, 20 and 31 of dst in sbb                                                                                                                                                                                                                                                                                                                                                                           | 149  |

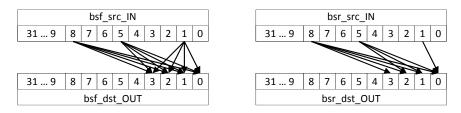

| 5.6  | Comparison between bsf and bsr                                                                                                                                                                                                                                                                                                                                                                                                | 150  |

| 5.7  | Pseudocode for cmpxchg (flags are omitted)                                                                                                                                                                                                                                                                                                                                                                                    | 151  |

| 5.8  | Comparison between Memcheck logic and SMT2 code for verifying AND $$                                                                                                                                                                                                                                                                                                                                                          | 155  |

| 5.9  | ARM Emulation code for basic mterp operations (binop.S)                                                                                                                                                                                                                                                                                                                                                                       | 160  |

## 1. INTRODUCTION

It is estimated that malware (malicious software) costs United States consumers \$2.3 billion and led to the replacement of 1.3 million personal computers (PCs) in 2010 [1]. Cybercrime, fueled by malware, was also estimated to have had a world-wide financial impact of \$118 billion [2] in the same year. As adoption of mobile platforms increased, so has the prevalence of mobile malware. According to McAfee, approximately 450 mobile malware samples, 400 of which target the Android platform, were identified in the 4th quarter of 2011 [3]. This is a 3.5x increase from the 3rd quarter and is expected to grow in 2012 [4]. The increase in the number of malware samples is also accompanied with new forms of fraud. lookout, a mobile security firm, has pointed out that "the most prevalent Toll Fraud malware family [FakeInst] has netted an approximate \$10 million for its makers" from September 2011 to June 2012 [5].

To mitigate the impacts of malware, anti-virus companies and researchers have used static and dynamic analysis tools to understand malware behavior so that countermeasures can be developed. In a survey of dynamic malware analysis techniques and tools, Egele et al. described the differences between static and dynamic analysis tools and outlined five dynamic analysis techniques (Function Call Monitoring, Function Parameter Analysis, Information Flow Tracking, Instruction Trace and Autostart Extensibility Points) that have been implemented using three different strategies (User/Kernel Space, Emulator and Virtual Machine) [6]. Of the techniques, taint analysis and instruction tracing provide the

most detailed information; however, there are limitations. The effectiveness of taint analysis is limited by the *precision* of taint propagation rules and while it is trivial to generate an instruction trace in an emulator, emulators lack *transparency* (and thus can be detected and evaded), and introduce *semantic gaps*.

This dissertation addresses these limitations and shows a fine-grained dynamic malware analysis platform that is transparent and supports precise taint analysis is feasible. The thesis is transparent malware analysis platforms with precise taint tracking rules can be realized using virtualization technologies. Three arguments are used to support this hypothesis: hardware virtualization can be used to make emulation transparent, semantic gaps can be bridged and the precision of taint propagation rules can be formally analyzed.

Transparency Emulators are designed to imitate the behavior of another system. For example, the CPU emulator in QEMU [7,8] is capable of emulating x86, ARM and other CPU architectures on top of different host architectures (e.g., x86 on x86 and x86 on ARM). If the CPU emulator is perfect, then the imitated behavior exactly mirrors that of a real hardware CPU and the emulator is considered *transparent*. However, transparency is difficult to achieve in practice due to emulation bugs, different CPU models and errata [9–12].

This dissertation proposes precise heterogeneous record and replay (PHRR) as a new technique to make emulation based dynamic analysis more transparent. The key idea is to separate a malware's execution from the analysis task. The malware is allowed to execute in a hardware virtualized environment where the above mentioned transparency issues due to emulation do not exist since execution takes place on a real CPU. The execution is

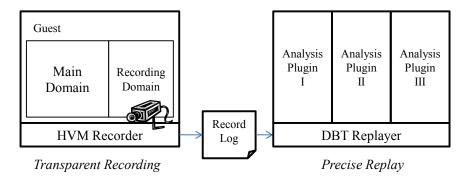

Fig. 1.1.: A high level architectural diagram of an emulation based dynamic malware analysis platform.

recorded such that all inputs and any potentially deviant behavior between the emulator and the real CPU are logged. In this manner, the emulator can better imitate the real CPU during analysis. Precise heterogeneous record and replay is implemented in a tool called V2E that uses the Kernel Based Virtual Machine (KVM) [13] as the recorder and TEMU [14–16] as the replayer. The details are presented in Chapter 3.

Semantic Gaps The semantic gap problem arises when analysis takes place at a lower abstraction layer than the analysis target resulting in a loss of higher level details. Take the emulation based dynamic analysis platform depicted in Figure 1.1 as an example. The solid arrows in the figure represent the interfaces between the different abstraction layers. Processes use *system calls* to interact with the operating system and the operating system uses x86 instructions to access hardware resources. These x86 instructions are emulated,

meaning the emulator mediates all accesses to hardware resources by the guest operating system and executes the guest instructions on its behalf. If emulation was not used, then the operating system will have direct access to the resources (dashed arrows).

It is clear from the figure that system calls are the interfaces between processes and the operating system, and not between the operating system and the emulator. Hence, an analyzer situated at the emulator that seeks to log all system calls made by "Process 1" will have difficulties. Since the emulation layer can only access the raw CPU and memory states, the concept of a process (an operating system construct) is limited to the value of the CR3 register, which contains the physical address of the top level page table. Also, the concept of Linux system calls is limited to the int 0x80 instruction that is used to invoke system calls. Additionally, while the CR3 values can be used to distinguish between different processes, specific information such as which CR3 value represents "Process 1" is not available at the emulation layer. To retrieve this information, and thus bridge the semantic gap, researchers have proposed Virtual Machine Introspection (VMI) techniques that can identify and interpret specific data structures from raw memory [17–19]. While these techniques have proven useful for bridging the semantic gap between the emulator and the guest operating system, Android, a mobile platform, has multiple gaps that must be bridged.

Unlike traditional desktop systems where applications run directly on top of the operating system, Android applications run in a Java Virtual Machine - known as the Dalvik Virtual Machine - and use JNI (Java Native Interface) to interface with native libraries. Consequently, Android malware can contain Java and native components that cooperate to achieve a common goal. Therefore, there are two levels of semantic

information that must be reconstructed in order to adequately analyze Android malware. First is the native level that includes the Linux kernel and second is the Java level that is interpreted using the DVM.

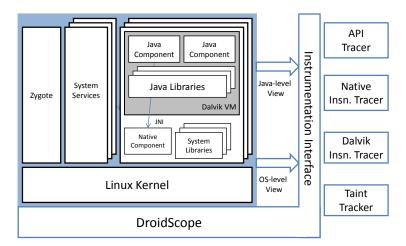

Bridging these two gaps involves understanding the different kernel data structures used to store pertinent information (e.g., processes) and the data structures and logic of the DVM (e.g., Java objects). These details along with the design of a new emulation analysis platform that seamlessly binds the two views together so that a sample's Java execution, native execution and interactions between them can be studied are presented in Chapter 4. These ideas are implemented in a new analysis tool name DroidScope, which is also discussed in the same chapter.

Precise Taint Analysis Dynamic taint analysis is designed to track information flows through data items of interest and is a key binary analysis technique [6]. In taint analysis, data items are labeled as "tainted" or "untainted" and this taint (label) is propagated from data item to data item as the program being analyzed is executed. The rules that determine when and how taint is to propagate are defined in a taint propagation policy.

Taint analysis is supported by both V2E, through TEMU, and DroidScope.

The propagation policies have been widely researched with different design patterns that vary taint-granularity (e.g., byte versus bit tainting [both TEMU and DroidScope labels taint per byte of data]), analysis-granularity, (e.g., propagating through ARM instructions like DroidScope or an Intermediate Representation [IR] like TEMU), and special case support (e.g., TEMU has a special rule to propagate taint through the bit shift operations without introducing false-positives while DroidScope does not). The

relationships between these design parameters and the accuracy (a measure of false-negatives) and precision (a measure of false-positives) of taint analysis are analyzed in Chapter 5 using formal methods.

In particular, a formal model of dynamic taint analysis is defined based on the concept of information flow or noninterference [20]. The model is then used to prove that propagating taint at the byte-level can introduce false-positives when compared to propagating taint at the bit-level and similarly, propagating taint through an IR can introduce false-positives when compared to propagating taint through the native instruction the IR is used to emulate. Methods for automatically generating a default policy without false-negatives and for determining the accuracy and precision of manually defined taint propagation rule are also presented.

Summary In short, this dissertation presents concepts, techniques, methods and proofs that can be used to design and build transparent and precise malware analysis platforms. DroidScope illustrates that emulation based fine-grained binary analysis can be performed on both mobile and desktop malware by bridging the two semantic gaps in Android, V2E shows that emulators can be made more transparency using hardware virtualization, and Chapter 5 provides insights into the fundamental sources of imprecision in dynamic taint analysis designs and methods for building and verifying precise taint propagation rules and taint analysis platforms.

The rest of the dissertation is organized as follows. Background information on malware analysis, virtualization, and taint analysis is presented in Chapter 2. V2E and DroidScope are presented in Chapters 3 and 4 respectively. The formal model for understanding the

relationship between dynamic taint analysis implementations and precision, and its application towards analyzing the precision of previously published taint analysis implementations are presented in Chapter 5. Chapter 6 summarizes the results. Future work is discussed throughout the dissertation.

## 2. BACKGROUND

#### 2.1 Virtualization

Virtualization is a computing concept where a device, component, or system is simulated for use by another device, component or system. To clarify the concept, Smith and Nair [21] state that "a discussion of [Virtual Machines] is also a discussion about computer architecture in the pure sense of the term." Then "architecture, as applied to computer systems, refers to a formal specification of an interface in the system" that can be implemented using multiple abstraction layers, each with its own interface (i.e., sub-architecture).

Fig. 2.1.: Computer System Architecture [21]

Fig. 2.2.: Process VM [21]

For example, a notional computer system architecture is depicted in Figure 2.1 [21]. While the computer system architecture consists of many different interfaces, four are notable. The Instruction Set Architecture (ISA) divides the hardware and software layers. It is further separated into the privileged system ISA (3) and unprivileged user ISA (4). The Application Binary Interface (ABI) is used by user programs to access system resources directly using the user ISA and indirectly using the system call interface (2). Finally, the Application Programming Interface (API) (1) abstracts away some details of the ABI through the use of libraries.

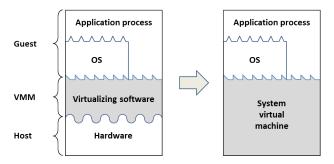

Given the multiple abstraction layers, a virtual machine for a particular abstraction layer is defined as the simulation of the interface beneath it. This definition is shown in Figure 2.2 [21] where a process virtual machine uses the "virtualization software" to simulate the ABI or API layers that the process uses. The figure also shows the virtualization software separating the *host* from the *guest*. More specifically, the virtualization software runs on top of the *host* and the *guest* runs on top of the virtualization software.

Special consideration is given to system virtual machines (Figure 2.3) that virtualize the ISA because they have been heavily researched since the 1960's and are used in this

Fig. 2.3.: System VM [21]

dissertation. In this case, the virtualization software is known as a the *Virtual Machine Monitor* or VMM; it is also known as a *hypervisor*. There are two research directions, emulators and virtual machines. Goldberg [22] defined emulators as efficient "simulators for dissimilar machines" and virtual machines as "efficient simulators for multiple copies of a machine on itself". Therefore, what distinguishes an emulator from a virtual machine is the fact that virtual machines simulate themselves, while emulators simulate other machines.

This distinction between emulators and virtual machines is important; however, the definitions have not been universally applied. For example, the Java Virtual Machine [23] and Dalvik Virtual Machine [24] are emulators according to the definitions, but are known as virtual machines. Since emulators can be considered as a special type of virtual machine [25], virtual machine will henceforth be used to describe the generic concept. Hardware virtualization and hardware virtual machines will be used to describe virtual machines that simulate themselves. In short, emulators and hardware virtual machines are two different types of virtual machines.

#### 2.1.1 Hardware Virtualization

There are three properties of hardware virtualization: efficiency, resource control and equivalence [26]. Efficiency requires the guest-issued instructions in the user ISA (interface (4) in Figure 2.1) to be executed directly on hardware and resource control dictates that the guest-issued instructions in the system ISA (3) must be mediated by the VMM.

Equivalence requires that any program should have the same execution behavior in the virtual machine as it would on real hardware<sup>1</sup>; this is also known as transparency.

Machines with these properties have been developed in the past [22], but it was only until recently that hardware virtualization for the x86 and ARM architectures became available.

The x86 architecture uses a ring-based access control model to separate the user ISA from the system ISA. Since the system ISA is associated with the most privileged ring (Ring 0), the resource control property requires the VMM to either run at Ring 0 while the guest executes at a lower protection level or the VMM to reside in a more privileged ring [27]. The first solution is not ideal since privileged guest instructions must be trapped and emulated [28], which reduces performance. The second solution is realized by introducing a new guest execution mode (non-root mode in Intel platforms [29] and guest mode in AMD platforms [30]) with its own distinct set of protection rings and CPU states [27]. A similar technology has been introduced for the ARM architecture [31]. Intel nomenclature will be used in the rest of this dissertation for consistency; however, the concepts apply to AMD and ARM as well.

<sup>&</sup>lt;sup>1</sup>Timing and resource availability problems are assumed not to exist

The relationship between root mdoe and non-root mode is similar to the one between the Operating System (OS) and a process. In order to execute a guest, the VMM (executing in *root* mode) first instantiates a Virtual Machine Control Structure (VMCS) (one per guest) that is used to maintain the state of the guest CPU (i.e., the non-root mode state) as well as control guest access to resources. Once instantiated and loaded, the VMM can use the vmlaunch instruction to enter non-root mode for the first time.

The guest continues to execute in non-root mode until an access violation (as configured in the VMCS) occurs which leads to a *VMExit*. As part of the VMExit event, the non-root mode CPU state and *exit reason(s)* are saved into the VMCS and the CPU is transitioned back into root mode. The VMM can then read the exit reason using the new vmread instruction, address the violation, update the guest CPU state (in the VMCS) using the new vmwrite instruction as necessary and continue executing the guest using the vmresume instruction. vmresume will load the guest CPU state from the VMCS and transition back into non-root mode. More detailed information can be found in Intel's Software Developer's Manual, Volume 3C [32].

Two-Dimensional Paging Virtual memory is a virtualization technique that exposes a consistent representation of memory to processes [21] and even to guests in virtual machines [25]. Paging and segmentation are two virtual memory implementations that are supported by the x86 architecture in a hardware Memory Management Unit (MMU). Segmentation is controlled through special registers, which have been virtualized as part of the Intel VT [27,29] and AMDV [30] hardware virtualization extensions.

Paging is implemented using memory-resident page tables that map virtual addresses to physical addresses. Since physical memory is shared between the guest and the host, access to the page tables by the guest must be mediated by the VMM (the resource control property), which can degrade performance. The concept of Two-Dimensional Paging (TDP) was introduced to reduce the number of transitions from non-root mode to root mode due to guest page faults [33].

Two page tables are used in TDP, one for the host and one for the guest. A first level page table is used by the guest to maintain mappings between its virtual addresses (guest virtual addresses or GVA) to its physical addresses (guest physical addresses or GPA). The guest has full control over this page table and handles the corresponding page faults. A second level page table is used to translate the guest physical addresses to host physical addresses (HPA). Page faults at this level (TDP faults) are handled by the VMM in root mode. In a way, the guest physical addresses are host virtual addresses (HVA).

During execution in non-root mode, a GVA will first be translated into a GPA using the first level page table. If a page fault occurs, then the guest OS's page fault handler will be invoked to handle the fault. If the translation is successful, then the GPA will be translated into a HPA using the second level page table. If a TDP fault occurs, then the CPU will automatically transition from non-root mode into root mode where the VMM can handle the fault. Once handled, the VMM will transition the CPU back into non-root mode to continue executing the guest.

TDP has been implemented as Extended Page Tables in Intel [29], Nested Page Tables in AMD [34] and System MMU in ARM v7-A architectures [31].

#### 2.1.2 The QEMU Emulator

QEMU [7,8] is a whole-system emulator that includes a number of subsystems: CPU emulator, emulated devices, generic devices, machine descriptions, debugger and user interface. Its many subsystems have been used as the basis for a number of commercial virtualization software products including KVM, Xen [35,36], VirtualBox [37], and the Android emulator [38]. Hence, QEMU is considered to be mature; emulation bugs are rare. The full documentation can be found on the project's webpage at http://www.qemu.org. Further discussions on QEMU will be focused on the CPU emulator subsystem. For brevity, QEMU will refer to the CPU emulator unless otherwise noted.

QEMU uses Dynamic Binary Translation (DBT) to emulate different instruction set architectures (e.g., x86, ARM and PowerPC). In brief, software emulation based on DBT works as follows. When the emulator is about to execute a block of guest code for the first time, it translates that code block into a piece of translated code in the host's ISA. The translated block is also stored into a code cache to improve performance. When the same code block needs to be emulated in the future, the emulator skips the translation procedure, directly fetches the translated code from the code cache and executes it. Older versions of QEMU (version 0.9.1 and older) used a target-specific translator called DynGen [7] that directly translates guest instructions into host instructions. Newer versions use TCG (Tiny Code Generator), which first translates guest instructions into an intermediate representation (TCG-IR), then compiles the TCG-IR blocks into host instructions for execution.

In either case, special care is needed to emulate memory accesses. The *softmmu* is a software implementation of the Memory Management Unit, which uses the guest's page tables to translate guest virtual addresses to guest physical addresses. To speed up the address translation, the *software Translation Look-aside Buffer (TLB)* is implemented as a cache for the address translation results. Since QEMU is a user-space program, the guest's physical memory is mapped into the QEMU process' virtual memory space. Thus, as an optimization, QEMU's software TLB caches GVA to HVA (in the QEMU process' context) translations instead of GVA to GPA translations.

QEMU is designed to be fast. Consequently it deviates from a real CPU in at least the following ways. First, a block-by-block translation procedure is introduced; this is in contrast to the instruction-by-instruction procedure used in real hardware. This translation procedure is normally invisible to the emulated execution, except when the block being translated crosses the page boundary and the following page is not present in the page table. This naturally leads to a page fault; however, there is a timing difference. The page fault occurs at the first instruction of the block in QEMU instead of at the instruction that crosses the page boundary - the expected behavior - in real hardware.

Second, for efficiency, QEMU performs a lazy calculation of flags: a flag is calculated only when it is needed. Take the following x86 instructions for example: "cmpl \$1, %eax; jz 0x401020;". On real hardware, the zero flag will be set or cleared after the cmpl instruction is executed. That is, if the eax register is 1 then the ZF bit in the EFLAGS register will be set. If eax is not 1 then ZF will be cleared. In QEMU, EFLAGS is not calculated when the first instruction executes. Additionally, on the second instruction, only ZF is calculated to determine which branch to take, the other flags are not calculated until

they are needed or at the end of a block. This lazy approach is good for efficiency but can be exploited to detect emulation.

Third, again for efficiency, interrupts are checked and served only at the block boundary. In contrast, on real hardware, interrupts may happen at any time. As a result, timing differences due to interrupt handling can be observed using a sequence like "rdtsc; mov "keax, "kebx; rdtsc;." Since the rdtsc instruction stores the current time stamp counter (a count of the number of clock cycles since the CPU has been reset) into the eax register, the sequence effectively stores the before and after counts into the ebx and eax registers respectively. By looping the sequence until the number of CPU cycles is greater than a relatively large threshold (e.g., the number of cycles to execute an interrupt handler), the presence of an interrupt in between the instructions can be detected. An emulator that only issues interrupts at the block boundary will remain in the loop endlessly, whereas a real CPU will eventually exit when an interrupt occurs within the sequence.

In addition to the above discrepancies that are unique to dynamic binary translation, several more are common due to emulation difficulties. First of all, some special-purpose instructions (e.g., System Management Mode and Trusted Execution Technology instructions) are hard to emulate and thus have not been implemented in software. As an example, QEMU 0.9.1 did not simulate the privileged "Resume from System Management Mode" instruction rsm. As a result, a malware sample that execute an rsm instruction will receive an illegal instruction exception, which is incorrect.

Accurate CPU timestamp emulation is difficult as well. For simplicity, QEMU fetches the timestamps from the host. On the one hand it will address the interrupt detection example discussed above, but on the other hand it introduces a different detection

technique. Since guest instructions are translated into one or more host instructions, emulation consumes more CPU cycles than real hardware. The slowdown can also be used for emulation detection.

Finally, the logic of checking for and raising exceptions in the hardware is fairly complex and thus the software emulation of this logic is often error-prone [9].

## 2.1.3 The Kernel Based Virtual Machine (KVM)

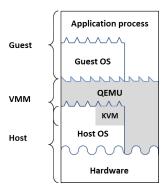

KVM is a virtual machine monitor that has been integrated into the Linux Kernel since version 2.6.20 and supports a number of hardware virtualized architectures including Intel VT, AMDV and ARM virtualization. Unlike other VMMs (such as VirtualBox and Xen), KVM is more of an accelerator than a full fledge virtualization solution. It abstracts away the details of the different virtualization extensions and exports a uniform interface through the "/dev/kvm" device. It is up to a user-space application to manage the guest resources. In this way, user-space virtualization solutions such as QEMU can use KVM to attain efficiency, resource control and equivalence. The notional architecture is depicted in Figure 2.4.

Fig. 2.4.: System Virtual Machine using KVM and QEMU

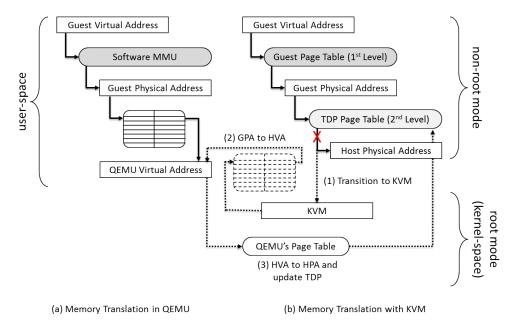

Fig. 2.5.: Memory translation in QEMU without KVM (a) and with KVM and TDP (b)

When KVM is paired with QEMU (the system emulator), the CPU emulator, software MMU and soft TLB are effectively disabled. The CPU emulator is no longer needed because guest instructions execute natively on real hardware in non-root mode and the software MMU and TLB are replaced with TDP. Using TDP with QEMU introduces a complication though.

Since the guest's physical memory space is mapped into the QEMU process' virtual memory space (i.e., GPA to HVA), it is incompatible with the EPT tables that translates GPA to HPA. The multi-stage process depicted in Figure 2.5 is used to address this issue. First, the QEMU process reports the mappings (the table with solid lines) between GPAs and HVAs to KVM (the table with dotted lines). Then, when a TDP fault occurs, KVM takes the TDP faulting address (a GPA) and translates it into the corresponding HVA (2). The HVA is subsequently translated into a HPA using the QEMU process' page table and the new GPA to HPA entry is added to the EPT table (3).

MMU-Notifiers Since QEMU runs as a user level process, its memory can be remapped and swapped to disk by the kernel. Consequently, this leads to inconsistencies in the EPT tables since they continue to the old physical page frame until updated. KVM uses MMU-Notifiers to prevent these kinds of problems. MMU-notifiers are callback functions that kernel modules (such as KVM) can register with the Linux MMU subsystem. In this way, the registered modules are notified of any changes to the page tables before the changes are committed. In the case of KVM, the MMU-notifier callback functions ensure that the EPT tables are consistent with QEMU's page tables.

### 2.2 Dynamic Malware Analysis

Malware analysis is an important step towards defending against malware. Given a piece of unknown malware, the objective of malware analysis is to reverse engineer it and quickly reveal its inner workings so that countermeasures can be implemented. Malware analysis techniques can be separated into two categories depending on whether the sample is executed during analysis. It is not executed in static analysis and is executed in dynamic analysis. Egele et al. [6] outlined the differences between static and dynamic analysis and provided motivations for the latter.

In general, static analysis has the advantage of code coverage, but obfuscation techniques can be used to hide the code and thus make static analysis less productive. On the other hand, dynamic analysis has the advantage of being unaffected by obfuscation since the code must be de-obfuscated during execution. However, it has the disadvantage of only being able to analyze the execution path taken - that is, it lacks code coverage.

Researchers have presented techniques for exploring multiple execution paths at runtime, but they are not perfect solutions [39–41]. In the end, static and dynamic analysis are complementary techniques that are used together. This dissertation focuses on dynamic analysis.

There are three different implementation strategies, User/Kernel Space, Emulator and Hardware Virtualization<sup>2</sup>, each with their advantages and disadvantages [6].

DynamoRIO [42], Pin [43,44], Valgrind [45] and SR-Dyninst [46] are powerful dynamic instrumentation tools for analyzing user-level programs. They cannot be used to analyze kernel malware. Cobra [47] is a malware analysis platform implemented in a Windows kernel module. It uses a technique called localized execution to instrument and inspect malware behavior. The localized execution technique is, in spirit, similar to dynamic binary translation.

The advantage of virtualization based analysis over User/Kernel Space implementations is *isolation*. Since the analysis tools are implemented at the VMM and the samples execute in the less privileged guest, virtualization isolates the tools from the samples. This allows the tools to analyze privileged malware (ones that execute in the guest kernel) while at the same time making it difficult for the malware to disrupt analysis [6].

The main disadvantage is the loss of semantic contextual information since the analysis component is moved out of the box. Virtual Machine Introspection [17–19] has been used to bridge the semantic gap. Many virtualization based analysis platforms have been implemented using emulation [41,48–59] and hardware virtualization [60,61]. These platforms provide the basic functionality to *introspect* (i.e., read and interpret the guest

<sup>&</sup>lt;sup>2</sup> "Virtual Machine" is replaced with "Hardware Virtualization" as discussed in Section 2.1

state) and *instrument* (i.e., intercept and write the guest state) the malware samples executing within the virtual machine. Analysis *plugins* that implement different dynamic analysis techniques (e.g., Function Call Monitoring, Function Parameter Analysis, Information Flow Tracking, Instruction Trace and Autostart Extensibility Points) are loaded onto the platforms to perform the desired analysis function.

Between the two virtualization based implementation strategies, emulation has the additional benefits of flexibility for analysis plugin development and efficiency for fine-grained analysis. In hardware virtualization, the VMM is required to be a privileged program so it can manage privileged system resources such as the TDP page table.

Emulators such as QEMU can be implemented in user-space. Thus, the analysis plugins built on top of emulators can benefit from user-space libraries making them more flexible.

As an example, the Linux kernel does not have an interface to read and write files from kernel [62,63]. In V2E, the log is written to disk by a user-space program through the use of a shared memory buffer between the VMM's (kernel's) memory space and the program's memory space.

Emulators are also more efficient for fine-grained analysis such as instruction tracing [6]. Tracing an instruction using hardware virtualization requires a transition from non-root mode to root mode and then back for every single instruction - a technique known as single stepping - which can degrade performance. A test of single stepping in KVM showed an approximately 3000 times slowdown in performance.

There is a major disadvantage of emulation though. Emulators lack transparency.

# 2.2.1 Transparency

Since it is extremely difficult (if not completely infeasible) to emulate every aspect of real hardware, malware can take advantage of these discrepancies to detect the emulated environment and stay dormant to avoid analysis. Some of the problems were raised in the QEMU section, but the general problem of emulation detection and mitigation techniques has been investigated extensively [9–12].

EmuFuzzer [10] and PokeEmu [9] are two noteworthy projects that sought to discover emulation bugs. EmuFuzzer discovered bugs in a randomized fashion using fuzz testing and PokeEmu is a follow-on work that discovers them systematically. PokeEmu uses symbolic execution [64] to explore all instruction emulation paths in two different emulators and generate a set of input-output behaviors that covers 95% of x86 instructions emulated. The set was then used to automatically generate a collection of programs that, given the same input, produces different output when executed on different emulators and real hardware. Over sixty thousand such programs were generated to identify differences between QEMU and real hardware. The differences were found in registers, memory, floating point registers and exception behavior; however, it is unknown whether all of the differences can be corrected in QEMU. It follows that the transparency problem remains unless all of these differences can be patched.

To tackle the problem of transparency from a different perspective, Dinaburg et al. [60] formally defined transparency/equivalence, proved that, except for timing differences, hardware virtualization achieves perfect transparency and implemented a new analysis

platform called Ether. However, Ether, being a hardware virtualization based implementation, is not as flexible or efficient as emulation based implementations.

In order to successfully emulate anti-emulation malware, Balzarotti et al. [65] used an automatic method to detect the anti-emulation behavior by comparing how a piece of malware behaves on real hardware and how it behaves in an emulated environment.

Similarly, Kang et al. [66] used a differential analysis method that compares two execution traces, one from Ether and the other one from QEMU. By performing trace alignment, this technique is able to automatically detect the root cause for the divergence and generate a patch (e.g., disable the emulation-detection code) for the malware. The iterative nature of this approach limits its scalability though. New traces and patches must be generated for each and every anti-emulation check.

#### 2.3 Android

Android is a popular mobile system that is installed in millions of devices and accounted for more than 50% of all smart phone sales in the third quarter of 2011 [67]. It has been the target of most mobile malware [3] and recent research has shown that malicious applications exist in both the official and unofficial marketplaces with a rate of 0.02% and 0.2% respectively [68].

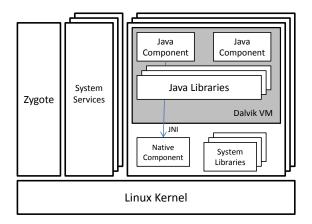

Figure 2.6 illustrates the architecture of the Android system from the perspective of a system programmer. At the lowest level, the Android system uses a customized Linux kernel to manage various system resources and hardware devices. System services, native applications and Apps (short for applications) run as Linux processes. In particular,

Fig. 2.6.: Overview of Android System

"Zygote" is the parent process for all Android Apps. Each App is assigned its own unique user ID (uid) at installation time and group IDs (gids) corresponding to requested permissions. These uids and gids are used to control access to system resources (e.g., network and file system) like on a normal Linux system.

All Apps can contain both Java and native components. Native components are simply shared libraries that are dynamically loaded at runtime. The Dalvik virtual machine (DVM), part of a shared library named libdvm.so, is then used to provide a Java-level abstraction for the App's Java components. At the same time, the Java Native Interface (JNI) is used to facilitate communications between the native and Java sides. As an aside, multiple layers of abstraction for Apps is not limited to Android. Windows Store applications have a similar structure. Those applications can be implemented in C++, C# or other languages in the .NET Framework [69]. C++ programs are compiled into native code while C# programs are interpretted using the Common Language Runtime (a virtual machine similar to JVM [70,71]).

To create a Java component, an App developer first implements it in Java, compiles it into Java bytecode, and then converts it into Dalvik bytecode. The result is a Dalvik executable called a dex file. The developer can also compile native code into shared libraries (.so files) with JNI support. The dex file, the shared libraries and any other resources, including the AndroidManifest.xml file that describes the App and its requested permissions, are packaged together into an apk file for distribution.

For instance, DroidKungFu is a malicious puzzle game found in alternative marketplaces that has both native and Java components [72]. Its Java component exfiltrates sensitive information and awaits commands from the bot master. Its native component is used as a shell to execute those commands and it also includes three resource files that are encrypted exploits targeting known vulnerabilities - adb setuid exhaustion and udev [73] - in certain versions of Android.

Android Software Development Kit (SDK) Like Linux, there are Android ports for both the ARM and x86 ISAs. Android Apps that only have Java components do not have to worry about the underlying architecture since all Java code is interpreted using the Dalvik Virtual Machine. Native components must be compiled for use on the target ISA though.

The entire process of developing, targeting and testing Android applications is supported by the Android Software Development Kit or SDK [74]. Noteworthy components of the SDK are the Android emulator and prebuilt virtual Android devices. Cross compilers for compiling the native components into their respective target ISAs are included as well. The Android emulator is based on newer versions of QEMU that use the TCG. A virtual

Android device is a virtual machine configured with virtual sensor devices (e.g., GPS) and a build of the Android software platform. The prebuilt virtual devices represent generic phone configurations based on the ARM and x86 ISAs. A software developer can always create virtual Android devices with different profiles such as one for an ARM based tablet. Nonetheless, the Android emulator is used to emulate different virtual Android devices to facilitate application testing and debugging. In short, emulation based Android analysis is already provided as part of the SDK. What is missing is the ability to analyze malware.

# 2.3.1 Android Malware Analysis

Like malware analysis on the desktop environment, Android malware analysis techniques can fall into two categories: static and dynamic. For static analysis, the sample's dex file can be analyzed by itself or it can be disassembled and further decompiled into Java using tools like dex2jar and ded [75]. Standard static program analysis techniques (such as control and data flow analysis) can then be performed. As static analysis can give a complete picture, researchers have demonstrated this approach to be effective for many malware samples [68,76].

However, static analysis is known to be vulnerable to code obfuscation techniques. In fact, the Android SDK includes a tool named Proguard [77] for obfuscating Apps and so obfuscated Apps should be common. Android malware may also generate or decrypt native components or Dalvik bytecode at runtime making static analysis of these dynamic components difficult. Indeed, DroidKungFu dynamically decrypts the exploit payloads and executes them to root the device. Moreover, researchers have demonstrated that bytecode

randomization techniques can be used to completely hide the internal logic of a Dalvik bytecode program [78]. Static analysis also falls short for exploit diagnosis, because a vulnerable runtime execution environment is needed to observe and analyze an exploit attack, and pinpoint the vulnerability. All in all, like for analyzing desktop malware, static analysis is insufficient by itself.

The Android SDK includes a set of tools, such as *adb* and *logcat*, to help developers debug their Apps. With JDWP (Java Debug Wire Protocol) support, the debugger can even exist outside of the device. However, just like how desktop malware detects and disables debuggers, malicious Android Apps can also detect the presence of these tools, and then either evade or disable the analysis. The fundamental reason is that the debugging components and malware reside in the same execution environment with the same privileges. Once again, virtualization based malware analysis has the advantage of isolation.

Despite the fact that Android is based on Linux, it is not straightforward to take the same desktop analysis approach used for Linux and apply it to Android malware due to the semantic gap problem. In Android, there are two levels of semantic information that must be rebuilt. In the lower level, Android is a Linux operating system where each App is encapsulated into a process. These processes can execute native code and this level is called the *native level*. Within each App process, a virtual machine (known as the Dalvik Virtual Machine) provides a runtime environment for the App's Java components. This second level is called the *Java level*.

Previous Virtual Machine Introspection research [17–19] only supports introspecting the native level but not the Java level components. Therefore, an emulation based dynamic analysis platform for Android malware must reconstruct semantic knowledge at two levels:

1) native level semantics that understand the activities of the malware process and its native components; and 2) Java level semantics that comprehend the behaviors in the Java components.

TaintDroid [79] and DroidBox [80] (based on TaintDroid) are examples of dynamic analysis tools for analyzing the Java components of Android Apps. TaintDroid is implemented as a modified Dalvik Virtual Machine. When installed onto a virtual Android device, it can be used to complement currently available emulation based analysis platforms for desktop malware. In this way, both the Java and native executions can be analyzed. The limitation is that they must be analyzed separately. Neither tool has information about the other and thus cannot collaborate. There are two approaches to surmount this limitation. Either a new messaging infrastructure is created between TaintDroid and the emulator or a single platform is introduced to not only bridge the two semantic gaps but also seamlessly bind the two views with the execution context so that malware with cooperating native and Java components can be analyzed at once.

Bouncer [81] is a recently announced dynamic analysis tool used by Google to test

Android Apps prior to accepting them into the official Android Market. Oberheide et

al. [82] determined that Bouncer is based on the Android emulator, but the details on what

it is capable of (e.g., whether it seamlessly binds the Java and native contexts together for

analysis) remains unknown. Bouncer is proprietary.

### 2.4 Taint Analysis

Taint analysis is one of the fundamental dynamic analysis techniques [6] and has been demonstrated to be crucial in many malware analysis projects [49,51,66,83]. It is also known as dynamic information flow tracking, taint tracking, definedness tracking, and data flow and control flow tracking. The technique is based on noninterference [20] and has been used in many different research areas such as policy enforcement, exploit diagnosis, malware analysis, vulnerability analysis, test case generation [64], memory analysis [84,85] and information flow quantification [86].

In taint analysis, data is labeled as either tainted or untainted and taint propagates from one data item to the next if information flows from a tainted source to the destination data item. Taint analysis has been implemented as a source translator [87–90] (e.g., compiler), a library [91–93] (e.g., Java String), in an instrumentation library [84,94–97] (e.g., PIN), in a virtual machine or interpreter [79,98–101] (e.g., Dalvik VM), in processor emulators [16,56,59,102–104] (e.g., QEMU), and even in hardware [105–111]. Common to all of these taint propagation tools is the use of a taint propagation policy that governs what data is tainted, how the labels are represented and when data should be tainted. In other words, a taint propagation policy is a set of rules that define when and how taint should be propagated.

Taint propagation policies have been heavily researched. There are three common design considerations: analysis-granularity, taint-granularity and special case support.

Analysis-granularity determines which type of operations propagates taint. One taint analysis implementation might propagate taint at the C statement level while another

propagates taint at the x86 instruction level. The advantage of the x86 instruction level implementation is it can track taint through all x86 programs (including those compiled from C programs); however, the disadvantage is the loss of high level semantic information (i.e., the semantic gap problem).

The range of analysis-granularity designs in the literature matches well with the different levels of programming languages. Researchers have defined propagation policies for high-level languages such as C [87] and Java [91–93,99], scripting languages such as PHP [89], PERL [101] and JavaScript [90,100], low level languages such as x86 assembly [56,84,94,103,104] and even at the gate level [108].

It is also common practice to implement taint propagation through an intermediate language [56,59,84,94,104] with simpler semantics and a reduced instruction set than through the language or instruction set (e.g., x86 and ARM) the IR emulates. The emulation code can range from a single instruction, to a basic block of instructions, to functions and beyond.