#### **Syracuse University**

#### SURFACE

Electrical Engineering and Computer Science -Dissertations

College of Engineering and Computer Science

12-2012

#### Methodology for Standby Leakage Power Reduction in Nanometer-Scale CMOS Circuits

Jae Woong Chun Syracuse University

Follow this and additional works at: https://surface.syr.edu/eecs\_etd

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Chun, Jae Woong, "Methodology for Standby Leakage Power Reduction in Nanometer-Scale CMOS Circuits" (2012). Electrical Engineering and Computer Science - Dissertations. 328. https://surface.syr.edu/eecs\_etd/328

This Dissertation is brought to you for free and open access by the College of Engineering and Computer Science at SURFACE. It has been accepted for inclusion in Electrical Engineering and Computer Science - Dissertations by an authorized administrator of SURFACE. For more information, please contact surface@syr.edu.

#### **Abstract**

In nanometer-scale CMOS technology, leakage power has become a major component of the total power dissipation due to the downscaling of threshold voltage and gate oxide thickness. The leakage power consumption has received even more attention by increasing demand for mobile devices. Since mobile devices spend a majority of their time in a standby mode, the leakage power savings in standby state is critical to extend battery lifetime. For this reason, low power has become a major factor in designing CMOS circuits.

In this dissertation, we propose a novel transistor reordering methodology for leakage reduction. Unlike previous technique, the proposed method provides exact reordering rules for minimum leakage formation by considering all leakage components. Thus, this method formulates an optimized structure for leakage reduction even in complex CMOS logic gate, and can be used in combination with other leakage reduction techniques to achieve further improvement.

We also propose a new standby leakage reduction methodology, leakage-aware body biasing, to overcome the shortcomings of a conventional Reverse Body Biasing (RBB) technique. The RBB technique has been used to reduce subthreshold leakage current. Therefore, this technique works well under subthreshold dominant region even though it has intrinsic structural drawbacks.

However, such drawbacks cannot be overlooked anymore since gate leakage has become comparable to subthreshold leakage in nanometer-scale region. In addition, BTBT leakage also increases with technology scaling due to the higher doping concentration applied in each process technology. In these circumstances, the objective of leakage minimization is not a single leakage source but the overall leakage sources. The proposed leakage-aware body biasing technique, unlike conventional RBB technique, considers all major leakage sources to minimize the negative effects of existing body biasing approach. This can be achieved by intelligently applying body bias to appropriate CMOS network based on its status (on-/off-state) with the aid of a pin/transistor reordering technique.

# Methodology for Standby Leakage Power Reduction in Nanometer-Scale CMOS Circuits

By

#### Jae Woong Chun

B.S., Electrical Engineering, Konkuk University, 2002 M.S., Electrical Engineering, Konkuk University, 2004

#### **DISSERTATION**

Submitted in partial fulfillment of the requirements for the

Degree of Doctor of Philosophy in Electrical and Computer Engineering

In the Graduate School of Syracuse University

December 2012

## Copyright © 2012 Jae Woong Chun All Rights Reserved

## **Table of Contents**

| Abstracti                                                                                    |

|----------------------------------------------------------------------------------------------|

| Table of Contentsv                                                                           |

| List of Tablesix                                                                             |

| List of Figuresxiii                                                                          |

| Chapter 1 Introduction1                                                                      |

| 1.1 Analysis of Steady States in a CMOS Transistor                                           |

| 1.2 Analysis of the Effect of Pin/Transistor Reordering on Leakage Current 3                 |

| 1.3 Effective Body Bias for Standby Leakage Power Reduction in Nanometer-Scale CMOS Circuits |

| 1.4 Dissertation Outline4                                                                    |

| Chapter 2 Background6                                                                        |

| 2.1 Standby Leakage Components6                                                              |

| 2.1.1 Subthreshold Leakage6                                                                  |

| 2.1.2 Gate Leakage8                                                                          |

| 2.1.3 Band-to-Band Tunneling Leakage                                                         |

| 2.2 Standby Leakage Reduction Techniques11                                                   |

| 2.2.1 Leakage Reduction by Stacking Effect                                                   |

| 2.2.2 Leakage Reduction by Sleep Transistor                                                  |

| 2.2.3 Leakage Reduction by Increasing the Threshold Voltages                        | . 20 |

|-------------------------------------------------------------------------------------|------|

| Chapter 3 Analysis of Steady States in a CMOS Transistor                            | . 24 |

| 3.1 Introduction                                                                    | . 24 |

| 3.2 Possible Steady States for CMOS Transistors                                     | . 25 |

| 3.2.1 Sources of Leakage Currents in a CMOS Transistor under Different B Conditions |      |

| 3.3 Steady State Components in On- and Off-State network                            | . 37 |

| 3.3.1 Steady state components in on-state CMOS network                              | . 37 |

| 3.3.2 Steady state components in off-state CMOS network                             | . 40 |

| 3.4 Main Steady States in a CMOS Circuit                                            | . 42 |

| 3.5 Summary                                                                         | . 43 |

| Chapter 4 Analysis of the Effect of Pin Reordering on Leakage Current               | . 44 |

| 4.1 Introduction                                                                    | . 44 |

| 4.2 Leakage Reduction through Pin Reordering                                        | . 48 |

| 4.2.1 A MOS Transistor Stacks in Off-state Network                                  | . 57 |

| 4.2.1.1 Non-Stacking Effect Case                                                    | . 57 |

| 4.2.1.2 Stacking Effect Case                                                        | . 59 |

| 4.2.2 A Combination of Serial and parallel MOS Structures in Off-st<br>Network      |      |

| 4.2.2.1 Limitation of Using Pin Reordering in a Complex CMOS Gate                   | . 73 |

| 4.3 Summary                                                                         | . 74 |

| Chapter 5 Leakage Reduction through Transistor Reordering for a Complex CMOS Gate                  |

|----------------------------------------------------------------------------------------------------|

| 5.1 Introduction                                                                                   |

| 5.2 Transistor Reordering in Pull-Down Network                                                     |

| 5.2.1 Transistor Reordering in Conducting Block Binding                                            |

| 5.2.2 Transistor Reordering in Non-Conducting Block Binding                                        |

| 5.3 Transistor Reordering in Pull-Up Network                                                       |

| 5.3.1 Transistor Reordering in Non-Conducting Block Binding                                        |

| 5.3.2 Transistor Reordering in Conducting Block Binding                                            |

| 5.4 Procedure of Transistor Reordering for Leakage Reduction in Complex CMOS gates                 |

| 5.5 Summary                                                                                        |

| Chapter 6 Effective Body Bias for Standby Leakage Power Reduction ir Nanometer-Scale CMOS Circuits |

| 6.1 Introduction109                                                                                |

| 6.2 Body Bias Effects on Leakage Components of CMOS Transistor 114                                 |

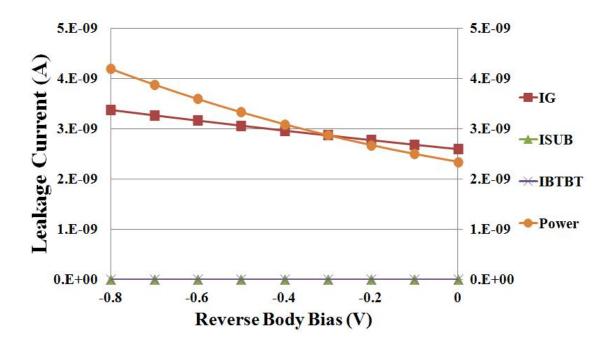

| 6.2.1 RBB Effects on Leakage Components                                                            |

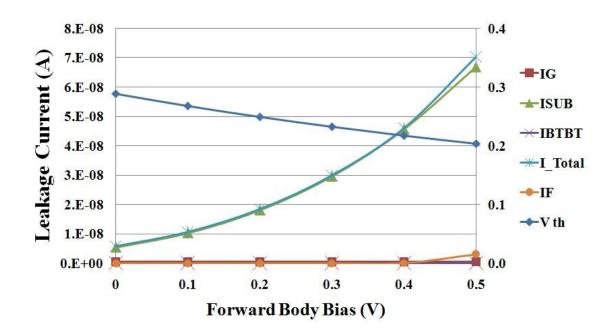

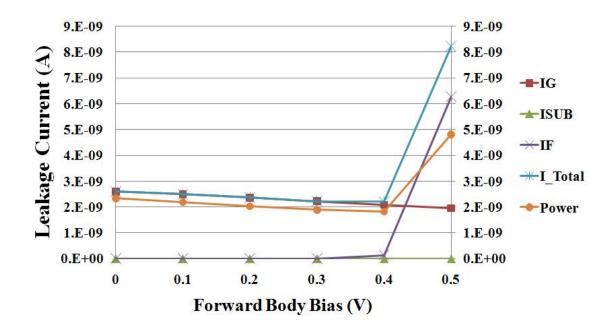

| 6.2.2 FBB Effects on Leakage Components                                                            |

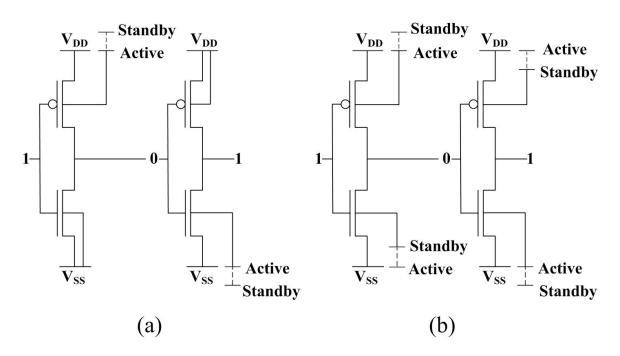

| 6.3 Leakage-aware Body Biasing Technique                                                           |

| 6.3.1 Same Gate Input State in CMOS Logic Gate                                                     |

| 6.3.2 Different Gate Input States in CMOS Logic Gate                                               |

| 6.3.3 Summary                                                                                      |

| 6.4 Summary                          | 136 |

|--------------------------------------|-----|

| Chapter 7 Conclusion and Future work | 138 |

| 7.1 Summary and Conclusion           | 138 |

| 7.2 Future work                      | 139 |

| Bibliography                         | 141 |

## **List of Tables**

| Table 1: Logic values and node voltages (V) of each transistor in 3-input OAI-21 gate with input (ABC) = "001"28                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2: Logic values and node voltages (V) of each transistor in 2-input NAND gate with input (AB) = " $10$ ", and NOR gate with input (AB) = " $11$ "30                                                                             |

| Table 3: Logic values and node voltages (V) of each transistor in 3-input AOI-21 gate with input (ABC) = "110"                                                                                                                        |

| Table 4: Logic values and node voltages (V) of each transistor in pull-down network of 4-input AOAI-211 gate with input (ABCD) = "0100"33                                                                                             |

| Table 5: Logic values and node voltages (V) of each transistor in pull-up network of 4-input OAI-31 gate with different input vectors                                                                                                 |

| Table 6: Steady state components, node voltages (V) and gate leakage current (nA) in different ON-state CMOS networks of Figure 18                                                                                                    |

| Table 7: Leakage current (nA) of two-input NAND gate                                                                                                                                                                                  |

| Table 8: Leakage current (nA) of two transistor stacks with different input vectors53                                                                                                                                                 |

| Table 9: Leakage current (nA) and node voltage (V) for three transistor stacks with different input vectors in non-stacking effect case                                                                                               |

| Table 10: Leakage current (nA) for S3 <sub>N/P</sub> in different bias voltages (V)59                                                                                                                                                 |

| Table 11: Variation of threshold voltage (V) and subthreshold leakage current (nA) with source voltage (V) in S3 <sub>N</sub> : V <sub>G</sub> =V <sub>B</sub> =0, V <sub>D</sub> =V <sub>DD</sub> =1.1V and W/L=4 in 65nm technology |

| Table 12: Leakage current (nA) and node voltage (V) for three transistor stacks with different input vectors in stacking effect case                                                                                                  |

| Table 13: The main factors of the subthreshold leakage for PDN three transistor stacks with different gate input states in stacking effect case                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 14: Leakage savings and saving ratio with application of pin reordering for leakage reduction in three transistors stacks                                                                            |

| Table 15: A comparison of leakage ratio between subthreshold and gate leakage in stacking and non-stacking cases with different gate input states in three transistors stacks                              |

| Table 16: Leakage current (nA) and steady state components for AOI-21 and OAI-21 logic gates in off-state network with different input vectors under different gate input states                           |

| Table 17: Leakage current (nA) and steady state components for XOR (XNOR) logic gate in off-state network with different input vectors                                                                     |

| Table 18: Leakage current savings (%) obtained through pin reordering                                                                                                                                      |

| Table 19: Leakage current savings (%) obtained through transistor reordering 76                                                                                                                            |

| Table 20: Comparison of leakage current (nA) considering without Irg and with Irg in off-state network of OAI-4211 gate with input: abcdefgh (ABCD) = 00011000 (0011)                                      |

| Table 21: Comparison of leakage current (nA) considering without Irg and with Irg in different transistor orders in off-state network of OAI-4211 gate with input: abcdefgh (ABCD) = 00011000 (0011).      |

| Table 22: Comparisons of percentage leakage reduction obtained without IRG and with IRG in different transistor orders in off-state network of OAI-4211 gate with input: abcdefgh (ABCD) = 00011000 (0011) |

| Table 23: Leakage current (nA) in different conducting-block orders of CBB in OAI-4211 gate                                                                                                                |

| Table 24: Leakage current (nA) and the bias voltages between the nodes in on-<br>and off-transistors under different locations of conducting block                                                         |

| Table 25: Delta leaky of conducting blocks in CBB of OAI-4211 gate 88                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 26: Leakage current (nA) in different non-conducting-block orders of NCBB in OAI-4211 gate                                                                                                                                                |

| Table 27: Gate leakage current (nA) and the bias voltages (V) between the nodes under different locations of non-conducting block (NCB)90                                                                                                       |

| Table 28: Subthreshold leakage current (nA), V <sub>th</sub> (V) and V <sub>DS</sub> (V) in different widths of non-conducting block (NCB)                                                                                                      |

| Table 29: Delta leaky of non-conducting blocks in NCBB of OAI-4211 gate 92                                                                                                                                                                      |

| Table 30: Comparison of leakage current (nA) considering without IRG and with IRG in off-state network of AOI-4211 gate with input: abcdefgh (ABCD) = $01111101 (0101)$ ; abcd(A)= $01111(0)$ , ef(B)= $11(1)$ , g(C)= $0(0)$ , h(D)= $1(1)$ 94 |

| Table 31: Comparison of leakage current (nA) considering without IRG and with IRG in different transistor orders in off-state network of AOI-4211 gate with input: abcdefgh (ABCD) = 01111101 (0101)                                            |

| Table 32: Comparisons of percentage leakage reduction obtained without Irg and with Irg in different transistor orders in off-state network of AOI-4211 gate with input: abcdefgh (ABCD) = 01111101 (0101)                                      |

| Table 33: Leakage current (nA) in different non-conducting-block orders of NCBB in AOI-4211 gate                                                                                                                                                |

| Table 34: Gate leakage current (nA) and the bias voltages (V) between the nodes under different locations of non-conducting block (NCB)                                                                                                         |

| Table 35: Subthreshold leakage current (nA), V <sub>th</sub> (V) and V <sub>DS</sub> (V) in different widths of non-conducting block (NCB)                                                                                                      |

| Table 36: Delta leaky of non-conducting blocks in NCBB of AOI-4211 gate 101                                                                                                                                                                     |

| Table 37: Leakage current (nA) in different conducting-block orders of CBB in AOI-4211 gate                                                                                                                                                     |

| Table 38: Leakage current (nA) and the bias voltages between the nodes in on-<br>and off-transistors under different locations of conducting block                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 39: Delta leaky of conducting blocks in CBB of AOI-4211 gate 106                                                                                             |

| Table 40: RBB effects on standby leakage current (nA) in S3 <sub>N</sub> (32nm) 115                                                                                |

| Table 41: RBB effects on standby leakage current (nA) in S2 <sub>N</sub> (32nm) 117                                                                                |

| Table 42: Leakage power (nW) difference between ZBB and RBB at $V_R$ =- $V_{DD}$ 118                                                                               |

| Table 43: FBB effects on standby leakage current (nA) in S3 <sub>N</sub> (32nm) 119                                                                                |

| Table 44: FBB effects on standby leakage current (nA) in S2 <sub>N</sub> (32nm) 121                                                                                |

| Table 45: Leakage power (nW) difference between ZBB and FBB at $V_F$ =0.4V 122                                                                                     |

| Table 46: Leakage power (nW) comparison under different steady states 123                                                                                          |

| Table 47: Comparison of leakage power (nW) and savings (%) in different body biasing techniques in Inverter                                                        |

| Table 48: Comparison of leakage power (nW) and savings (%) in different body biasing techniques in 2- input NAND and NOR gates under same input logic value. 129   |

| Table 49: Comparison of leakage power (nW) and savings (%) in different body biasing techniques in 2- input NAND and NOR gates under different input logic values. |

| Table 50: Leakage power savings (%) obtained through pin/transistor reordering in different body biasing techniques                                                |

| Table 51: Comparisons of average leakage power savings (%) in different body                                                                                       |

| biasing techniques                                                                                                                                                 |

## **List of Figures**

| Figure 1: Gate tunneling current flows and components                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2: Two-Input NAND Gate. 12                                                                                                                               |

| Figure 3: (a) logic gate parts of circuit block when predetermined input vector applied in standby mode (b) stack forcing applied to non-stacked logic gates 14 |

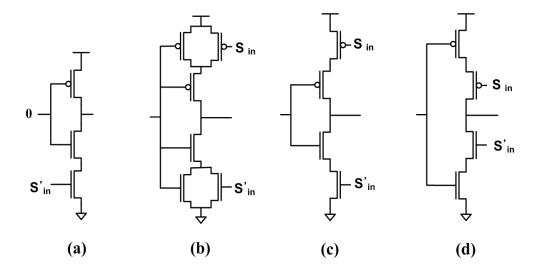

| Figure 4: (a) Original Inverter (b) LECTOR Inverter (c) GALEOR Inverter 15                                                                                      |

| Figure 5: (a) single-V <sub>th</sub> stacking (b) Sleepy stack (c) Power gating (d) Drain gating.                                                               |

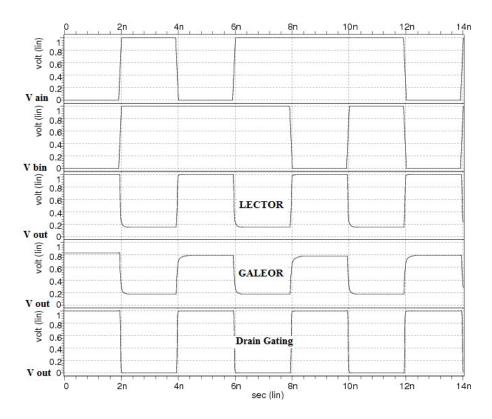

| Figure 6: Transient characteristics of two-input NAND gate in LECTOR, GALEOR and Drain Gating simulated by HSPICE [23]                                          |

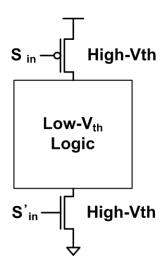

| Figure 7: Multi-Threshold CMOS (MTCMOS)                                                                                                                         |

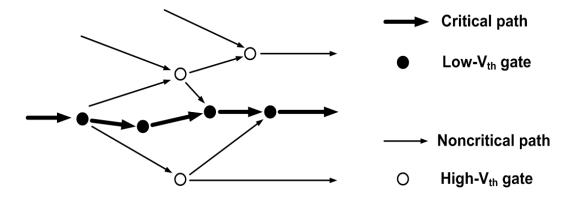

| Figure 8: Dual threshold voltage technique.                                                                                                                     |

| Figure 9: Reverse Body Biasing. 22                                                                                                                              |

| Figure 10: All possible bias conditions for CMOS transistors                                                                                                    |

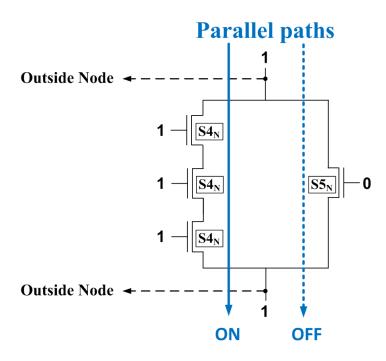

| Figure 11: Pull-down network structure in the presence of S5 <sub>N</sub>                                                                                       |

| Figure 12: (a) 3-input OAI-21 gate (b) Input: ABC = 001                                                                                                         |

| Figure 13: (a) 2-input NAND gate with input (AB) =10 (b) 2-input NOR gate with input (AB) =11                                                                   |

| Figure 14: (a) 3-input AOI-21 gate (b) Input: ABC = 110                                                                                                         |

| Figure 15: Pull-down network structures in the presence of S6 <sub>N</sub>                                                                                      |

| Figure 16: (a) 4-input AOAI-211 gate (b) Input: ABCD = 0100                                                                                                     |

| Figure 17: Pull-up network of OAI-31 gate with different input vectors (a) ABCD=0111 (b) ABCD=0101 (c) ABCD=0011                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

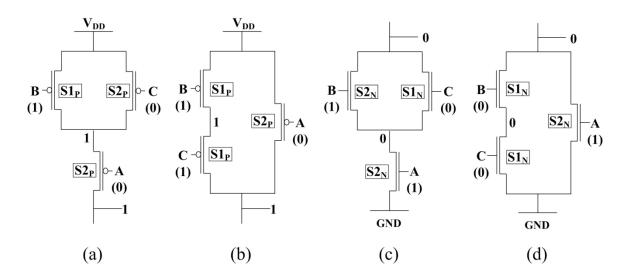

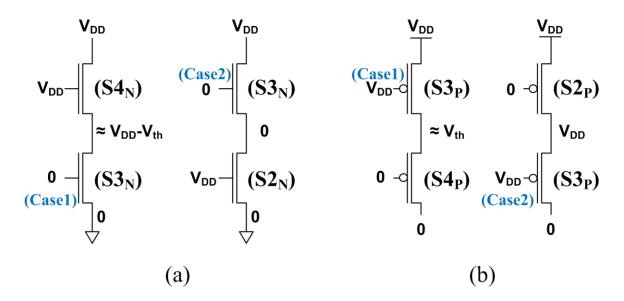

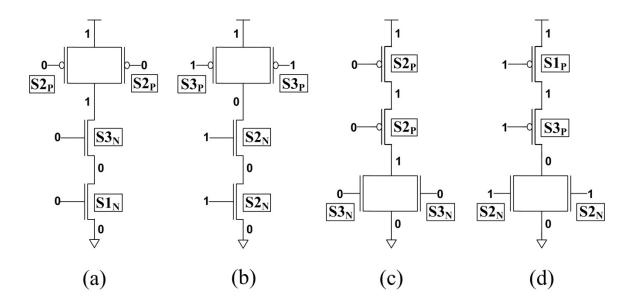

| Figure 18: Steady state components in on-state pull-up/-down network: Case1 ((a and (c)) and Case2 ((b) and (d))                                                                                                                                                      |

| Figure 19: Steady state components of Inverter: (a) input=0 (b) input=VDD 42                                                                                                                                                                                          |

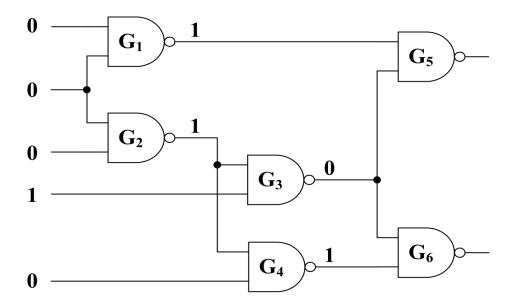

| Figure 20: MCNC benchmark circuit C17 [43]                                                                                                                                                                                                                            |

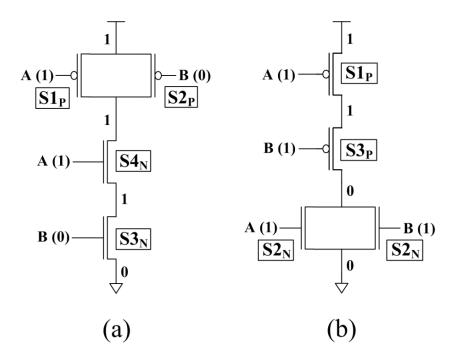

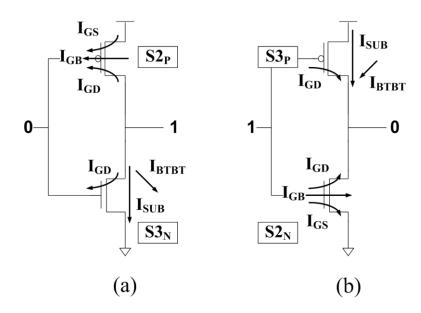

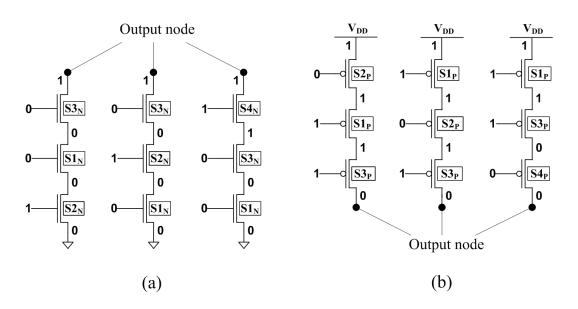

| Figure 21: Steady states in off-state network: (a) NMOS (b) PMOS                                                                                                                                                                                                      |

| Figure 22: Comparison of Steady states in two transistor stacks with different input vectors: (a) Pull-down (b) Pull-up                                                                                                                                               |

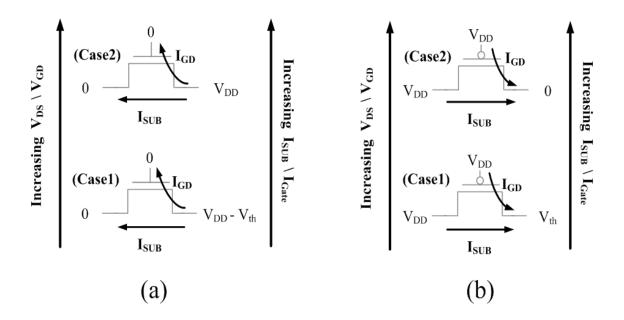

| Figure 23: Leakage comparison of S <sub>SUB</sub> in different bias voltage conditions: (a) NMOS (S <sub>3N</sub> ) (b) PMOS (S <sub>3P</sub> )                                                                                                                       |

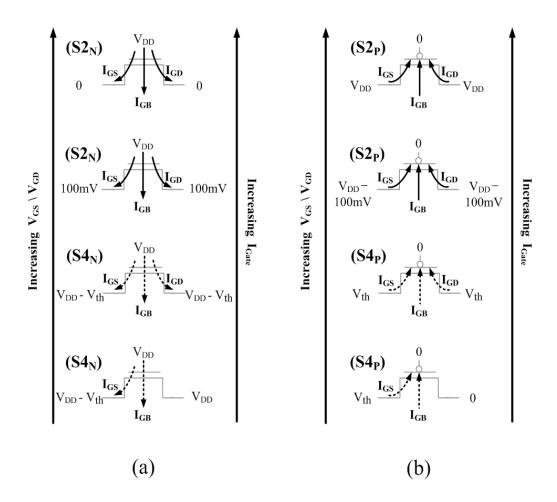

| Figure 24: Leakage comparison of conducting transistors: (a) NMOS (b) PMOS.53                                                                                                                                                                                         |

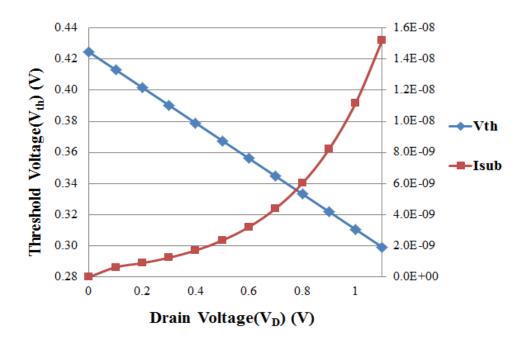

| Figure 25: Leakage current and threshold voltage trends as a function of V <sub>D</sub> in S3 <sub>N</sub> with V <sub>G</sub> = V <sub>S</sub> =V <sub>B</sub> =0, V <sub>DD</sub> =1.1 and W/L=4 in 65nm technology. The unit of right side of Y-axis is Ampere (A) |

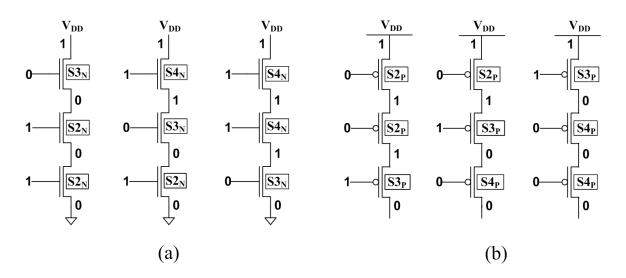

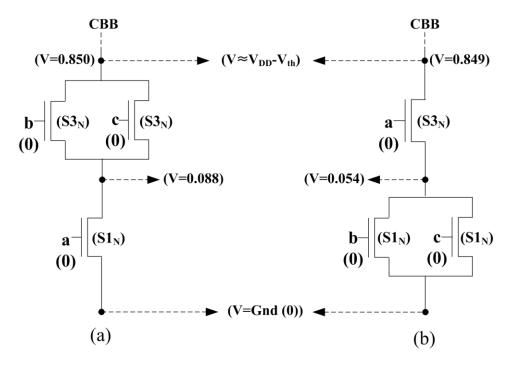

| Figure 26: Possible input vectors of non-stacking effect case in three transistor stacks in different gate input states: (a) PDN (NMOS) (b) PUN (PMOS)                                                                                                                |

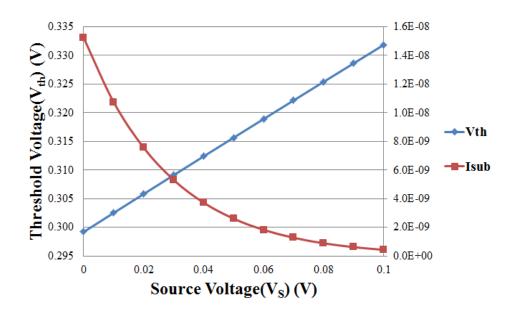

| Figure 27: Leakage current and threshold voltage trends as a function of Vs in S3 <sub>N</sub> with V <sub>G</sub> =V <sub>B</sub> =0, V <sub>D</sub> = V <sub>DD</sub> =1.1V and W/L=4 in 65nm technology. The unit of right side of Y-axis is Ampere (A)            |

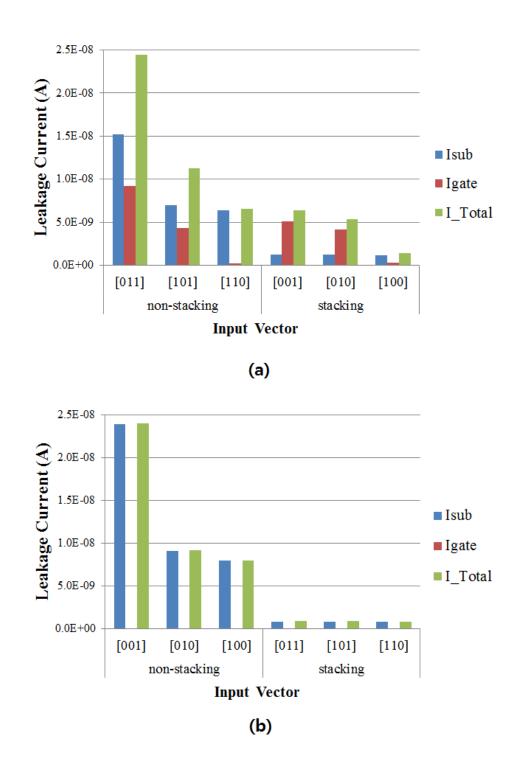

| Figure 28: Variation of leakage current with different input vectors for a stack of three transistors. (a) Pull-down network. (b) Pull-up network                                                                                                                     |

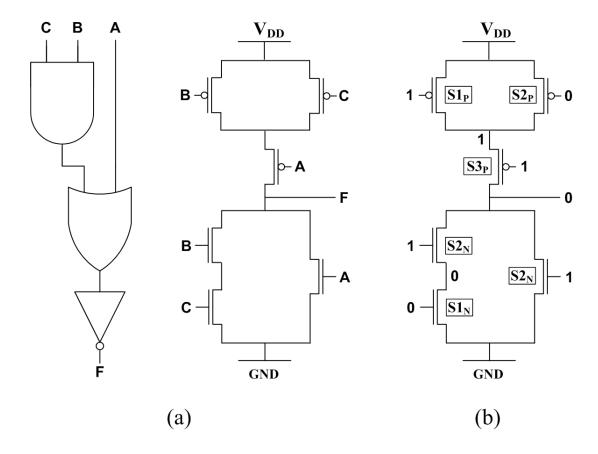

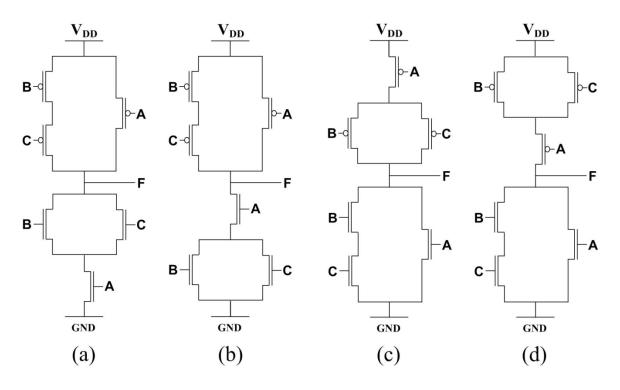

| Figure 29: 3-input OAI-21 gate with different pull-down structures ((a) Type1, (b) Type2), and 3-input AOI-21 gate with different pull-up structures ((c) Type1, (d) Type2)                                                                                           |

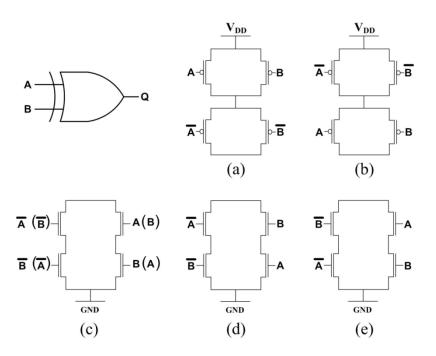

| Figure 30: 2-input XOR gate with different input positions in PUN ((a) Type1, (b) Type2) and PDN ((c) Type3, (d) Type4, (e) Type5)      |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| Figure 31: 2-input XNOR gate with different input positions in PUN ((a) Type1, (b) Type2) and PDN ((c) Type3, (d) Type4, (e) Type5)71   |

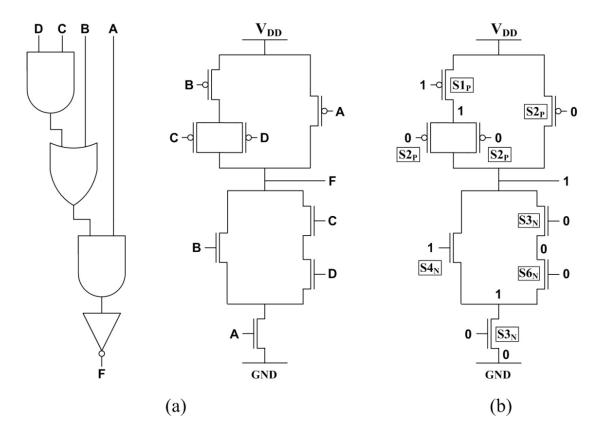

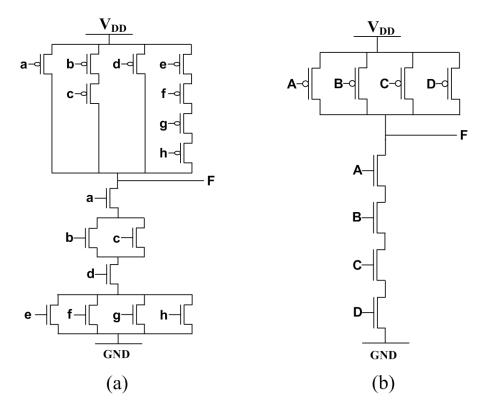

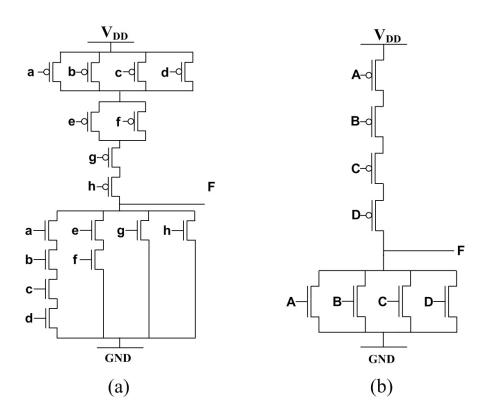

| Figure 32: OAI-4211 gate (a) and its simplified formation (b)                                                                           |

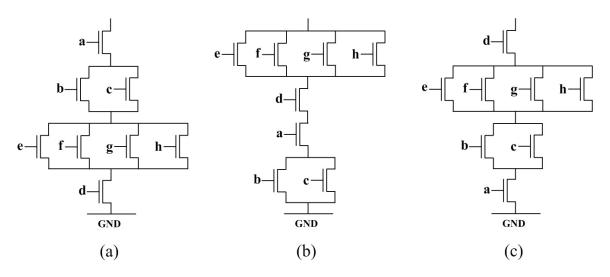

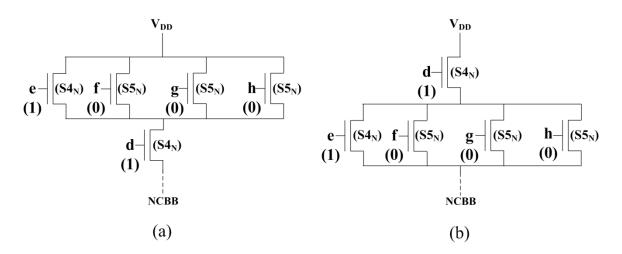

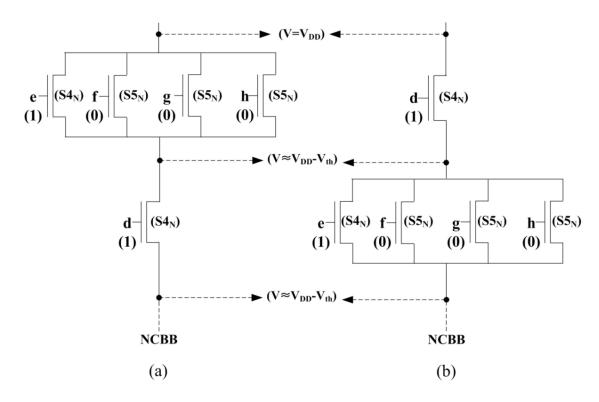

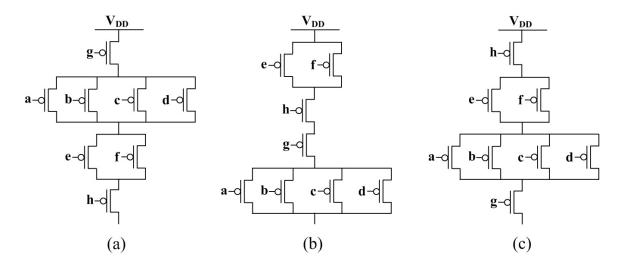

| Figure 33: Various formations of pull-down network in OAI-4211 gate; simplified form input: (a) "ABDC" (b) "DCAB" (c) "CDBA"            |

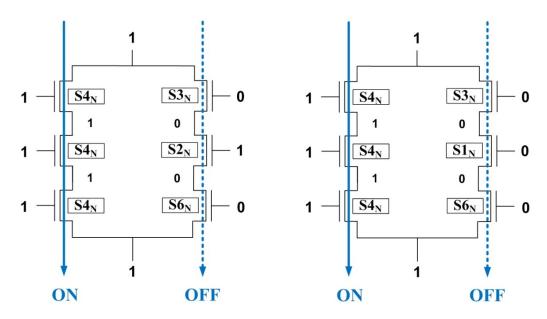

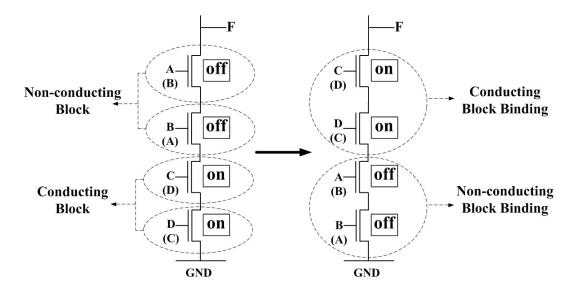

| Figure 34: Transistor reordering for leakage reduction in off-state network when the simplified input (ABCD) of OAI-4211 gate is "0011" |

| Figure 35: Different conducting block orders in CBB of OAI-4211 gate: (a) "DC" (b) "CD"                                                 |

| Figure 36: Different conducting-block orders in CBB of OAI-4211 gate: (a) "DC" (b) "CD"                                                 |

| Figure 37: Different non-conducting block orders in NCBB of OAI-4211 gate: (a) "BA" (b) "AB"                                            |

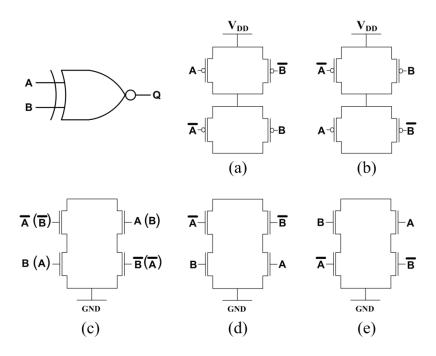

| Figure 38: AOI-4211 gate (a) and its simplified formation (b)                                                                           |

| Figure 39: Various formations of pull-up network in AOI-4211 gate; simplified form input: (a) "CABD" (b) "BDCA" (c) "DBAC"              |

| Figure 40: Transistor reordering for leakage reduction in off-state network when the simplified input (ABCD) of AOI-4211 gate is "0101" |

| Figure 41: Different non-conducting block orders in NCBB of AOI-4211 gate: (a) "BD" (b) "DB"                                            |

| Figure 42: Different conducting-block orders in CBB of AOI-4211 gate: (a) "AC" (b) "CA"                                                 |

| Figure 43: Reverse Body Biasing                                                                                                         |

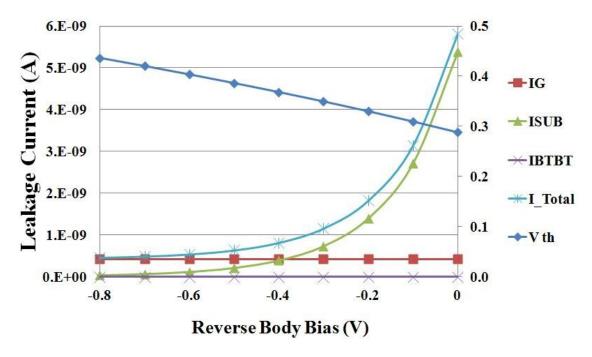

| Figure 44: Standby leakage currents and threshold voltage of S3 $_{\rm N}$ (32nm with VDD=0.9V and W/L=4) as a function of VR, and the unit of right side of Y-axis is voltage (V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 45: Standby leakage currents and power of S2 <sub>N</sub> (32nm with $V_{DD}$ =0.9V and W/L=4) as a function of V <sub>R</sub> , and the unit of right side of Y-axis is power (W) 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 46: Standby leakage currents and threshold voltage of S3 $_{\text{N}}$ (32nm with VDD=0.9V and W/L=4) as a function of VF, and the unit of right side of Y-axis is voltage (V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 47: Standby leakage currents and power of S2 <sub>N</sub> (32nm with $V_{DD}$ =0.9V and W/L=4) as a function of V <sub>F</sub> , and the unit of right side of Y-axis is power (W) 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

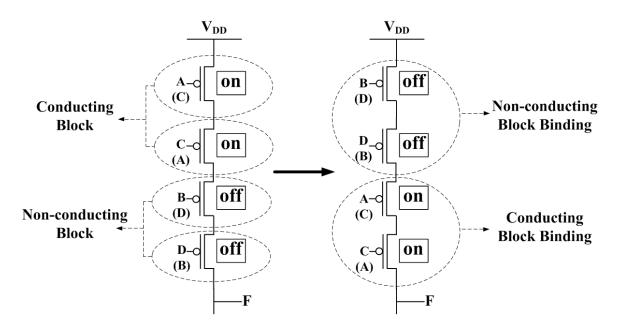

| Figure 48: (a) RBB-off (b) Hybrid Body Biasing (HBB)12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

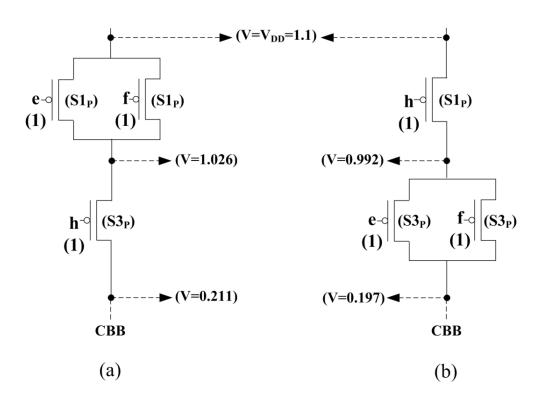

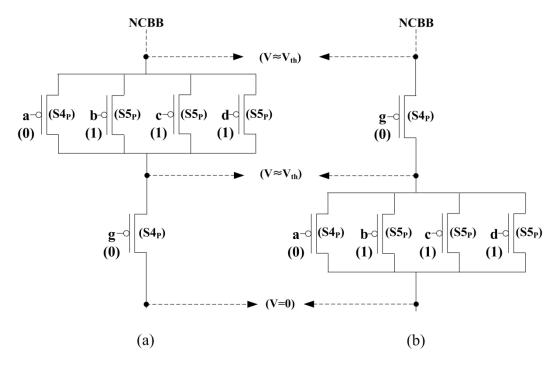

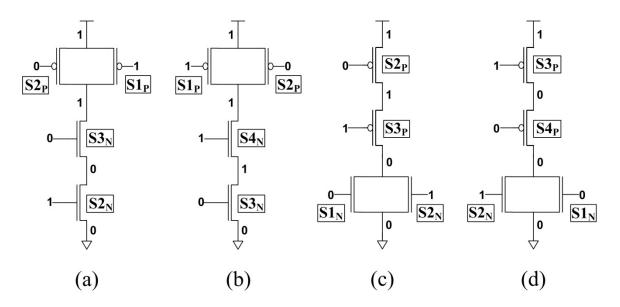

| Figure 49: Steady states of a 2-input NAND ((a) and (b)) and NOR ((c) and (d) gates in same gate input states: input=00 ((a) and (c)), input=11 ((b) and (d)) 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 50: Steady states of a 2-input NAND ((a) and (b)) and NOR ((c) and (d) gates in different gate input states: input=01 ((a) and (c)), input=10 ((b) and (d) and |

## Chapter 1

## Introduction

As CMOS technology and supply voltage ( $V_{DD}$ ) are scaled down, gate oxide thickness and threshold voltage must also be reduced to maintain reasonable short channel effects and to achieve the desired performance improvement, respectively. Despite the use of a lower power supply voltage in each technology generation, the leakage power increases exponentially due to the reduced gate length, gate oxide thickness and threshold voltage [1].

With technology downscaling, subthreshold leakage current exponentially increases as threshold voltage reduces. Previously, subthreshold leakage was the dominant leakage component, and thereby conventional leakage reduction techniques focus primarily on subthreshold leakage alleviation, whereas the effect of gate leakage current was neglected. However, downscaling of gate oxide thickness ( $T_{OX}$ ) produces significant gate tunneling leakage current, which has become a major leakage component in CMOS circuits [1], [2]. Furthermore, as the  $T_{OX}$  scales below 2nm, gate tunneling leakage current increases drastically, and thus gate leakage becomes a dominant leakage component [2]-[5] since the gate

tunneling leakage current strongly depends on  $T_{OX}$  [6], [7]. Thus, circuit-level techniques, which used to only suppress subthreshold leakage, need to reevaluate in nanometer-scale technologies since subthreshold leakage is not the only serious leakage source in nanometer-scale era.

In this thesis, we focus on leakage behavior of CMOS circuits, and propose general leakage reduction methods for standby leakage power reduction. In the following, proposed techniques are described in more details.

#### 1.1 Analysis of Steady States in a CMOS Transistor

In this work, we provide an in-depth study and analysis of the possible steady states of both PMOS and NMOS transistors in a CMOS circuit. Based on this fundamental analysis, we point out problems related to previous steady state model, and provide an accurate steady state model in CMOS circuits. Further, we propose the five distinct types of steady states based on leakage components of a single transistor to better understanding of leakage behavior, and present the major leakage sources of each network (on- and off-state network) in CMOS circuits by analyzing the components of steady states in on- and off-state CMOS

network. Finally, we define the main steady states of CMOS transistors since main steady states are found in every CMOS logic gate unlike other steady states.

## 1.2 Analysis of the Effect of Pin/Transistor Reordering on Leakage Current

In this research, we first discuss how gate and subthreshold leakage varies with input vector of CMOS gate. And then we investigate the opportunities for reducing gate and subthreshold leakage simultaneously by using pin reordering, and point out the problems and limitations associated with existing pin reordering technique when applying this technique to pull-up network of CMOS circuits and complex CMOS logic gates. To solve these problems, we propose a novel pin and transistor reordering technique for leakage reduction. The proposed method provides an optimized formation for leakage reduction, and can be used in combination with other leakage reduction techniques to achieve further improvement.

## 1.3 Effective Body Bias for Standby Leakage Power Reduction in Nanometer-Scale CMOS Circuits

Reverse Body Biasing (RBB) technique [8]-[12] has become one of the most widely used circuit design technique for leakage power reduction. It utilizes the body effect of CMOS gates by manipulating the threshold voltage in standby mode. In this research, we analyze the RBB technique from a structural point of view, and address the problems associated with overall leakage savings due to the lack of awareness of other than subthreshold leakage. To solve these problems, we propose the leakage-aware body biasing methods which take into account not only the subthreshold leakage but also gate and BTBT leakage, resulting in enhanced the effectiveness of body biasing for leakage power reduction.

#### 1.4 Dissertation Outline

The remainder of the thesis is organized as follows. Chapter 2 briefly reviews major leakage current components, and a number of commonly used leakage reduction techniques. Chapter 3 describes the possible bias conditions for CMOS transistors in a circuit. The analysis of the effect of pin reordering on leakage

reduction is presented in Chapter 4. Chapter 5 describes the proposed transistor reordering method for leakage power reduction. Chapter 6 describes the proposed leakage-aware body biasing methodologies in association with pin/transistor reordering technique. Finally, conclusion and future work are presented in Chapter 7.

## Chapter 2

## **Background**

In this chapter, we briefly review the leakage sources in CMOS transistors, and existing leakage power reduction techniques. This chapter is helpful for understanding the remainder of this thesis.

#### 2.1 Standby Leakage Components

In nanometer-scale CMOS devices, the main components of leakage currents are subthreshold leakage ( $I_{SUB}$ ), gate tunneling leakage ( $I_{G}$ ), and reverse biased junction BTBT leakage ( $I_{BTBT}$ ). We describe the effect of scaling trends on these three main leakage components in this subchapter.

#### 2.1.1 Subthreshold Leakage

The subthreshold leakage is a current flowing between drain and source terminals of CMOS transistor when the gate voltage is below the subthreshold voltage. This subthreshold leakage increases exponentially with technology

scaling due to reduced threshold voltage. The subthreshold current of a MOSFET device can be expressed as [7], [19]:

$$I_{SUB} = \mu \frac{W_{eff}}{L_{eff}} \sqrt{\frac{q\varepsilon_{si}N_a}{2\Phi_s}} V_T^2 \left(1 - \exp\left(\frac{-V_{DS}}{V_T}\right)\right) \exp\left(\frac{V_{GS} - V_{th}}{nV_T}\right)$$

(1)

where  $\mu$  is the electron surface mobility q is the electronic charge,  $\varepsilon_{si}$  is the silicon permittivity,  $N_a$  is the doping concentration in the substrate,  $V_T = kT/q$  is the thermal voltage; k is the Boltzman constant, T is the absolute temperature, and  $\Phi_s$  is the surface potential,  $V_{DS}$  is the drain-source voltage,  $V_{GS}$  is the gate-source voltage,  $V_{th}$  is the threshold voltage and n is the subthreshold swing parameter.

$I_{SUB}$  depends on the transistor threshold voltage ( $V_{th}$ ), gate-to-source ( $V_{GS}$ ) and drain-to-source voltages ( $V_{DS}$ ), and temperature (T). When the MOSFET is off-state ( $V_{GS} = 0V$ ), reduction of the threshold voltage causes subthreshold current to increase exponentially as shown in (1). The threshold voltage equation considering the body effect is given by [19]:

$$V_{th} = V_{fb} + 2\Psi_B + \frac{\sqrt{2\varepsilon_{si}qN_a(2\Psi_B + V_b)}}{C_{ox}}$$

(2)

where  $V_{fb}$  is the flat band voltage,  $\Psi_B$  is the difference between Fermi potential and intrinsic potential in the substrate and equal to (kT/q)ln(Na/ni), where ni is the intrinsic carrier concentration,  $V_b$  is the substrate (body) bias voltage and  $C_{ox}$  is the gate oxide capacitance. The RBB scheme has been used to reduce the subthreshold leakage by applying reverse body bias which increases the  $V_b$  – a phenomenon known as body effect. On the other hand, forward body bias decreases  $V_b$ , and thereby increases the subthreshold leakage by reducing the threshold voltage.

#### 2.1.2 Gate Leakage

In nanometer-scale MOSFET device, gate-oxide thickness becomes thinner with technology scaling in order to control short channel effects and increase the transistor driving strength. The aggressive scaling in the gate-oxide thickness  $(T_{ox})$  causes gate tunneling current to exponentially increase since the gate leakage is a strong exponential function of the oxide thickness as shown in (3). The gate tunneling current density  $(J_g)$  is given by [19], [20]:

$$J_g = A \left(\frac{V_{ox}}{T_{ox}}\right)^2 exp \left(\frac{-T_{ox} B \left(1 - \left(1 - \frac{V_{ox}}{\phi_{ox}}\right)\right)^{\frac{3}{2}}}{V_{ox}}\right)$$

where  $A = \frac{q^3}{16\pi^2 \hbar \phi_{ox}}$  and  $B = \frac{4\sqrt{2m^*} \phi_{ox}^{\frac{3}{2}}}{3\hbar q}$  (3)

where  $V_{ox}$  is the voltage drop across the gate oxide,  $T_{ox}$  is the gate oxide thickness,  $\phi_{ox}$  is the barrier height for tunneling electron,  $\hbar$  is the reduced Plank's constant, and  $m^*$  is the electron effective mass.

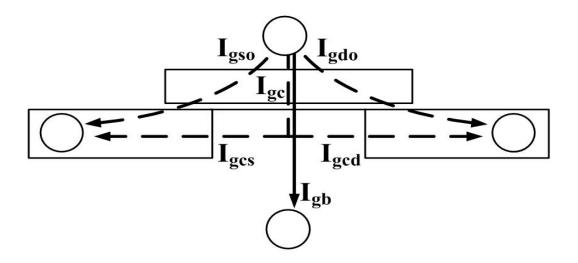

Figure 1: Gate tunneling current flows and components.

Figure 1 shows the components of  $I_G$  between gate and source/drain diffusion regions ( $I_{gso}$  and  $I_{gdo}$ ), between gate and bulk ( $I_{gb}$ ), and between gate and channel ( $I_{gc}$ ), which is further partitioned between the source and drain terminals by  $I_{gc} = I_{gcs} + I_{gcd}$  [6]. Hence, the gate tunneling currents can be divided by the current flows; gate to source ( $I_{GS} = I_{gso} + I_{gcs}$ ), gate to drain ( $I_{GD} = I_{gdo} + I_{gcd}$ ) and gate to body ( $I_{GB} = I_{gb}$ ). Hence,  $I_{G}$  is equal to the sum of the  $I_{GD}$ ,  $I_{GB}$  and  $I_{GS}$ .

#### 2.1.3 Band-to-Band Tunneling Leakage

As CMOS technology scales down, substrate doping concentration increases in order to reduce the short channel effects. Therefore, heavily doped n+drain/source and p-type substrate yield high electric field across the reverse-biased p-n junction, which produces significant current flows through the junction, and the BTBT current density is expressed as [19], [20]:

$$J_{btbt} = \frac{\sqrt{2m^*}q^3 \, \xi \, V_{app}}{4\pi^3 \, \hbar^2 \, E_g^{\frac{1}{2}}} \, exp\left(-\frac{4\sqrt{2m^*}E_g^{\frac{3}{2}}}{3q\hbar\xi}\right)$$

where  $\xi = \sqrt{\frac{2q \, N_a N_d \, (V_{app} + V_{bi})}{\varepsilon_{si} \, (N_a + N_d)}}$  (4)

where  $\xi$  is the electric field at the junction,  $E_g$  is the energy bandgap,  $V_{app}$  is the applied reverse voltage across the junction,  $V_{bi}$  is the built-in voltage and  $N_a$  and  $N_d$  are the doping concentration of p and n side. As shown in (4), when substrate doping concentration increases, BTBT current exponentially increase with the increase of the electric field at junction.

#### 2.2 Standby Leakage Reduction Techniques

In this subsection, we review previous circuit design techniques for leakage reduction in CMOS circuits.

#### 2.2.1 Leakage Reduction by Stacking Effect

Stacking of series-connected transistors reduces the subthreshold leakage currents when more than one transistor in the stack is turned off, which is known as stacking effect [17]. It yields a positive potential at the intermediate node of off-transistors, which has three effects: 1) gate-to-source voltage (VGS) of upper transistor becomes negative; 2) reverse biased body-to-source voltage (VBS) of upper transistor induces larger body effect; 3) reduced drain-to-source voltage

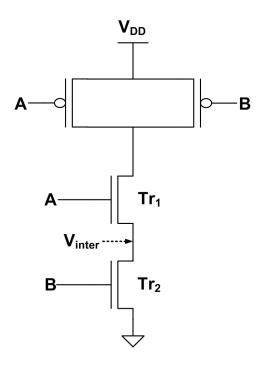

(V<sub>DS</sub>) of upper transistor causes less drain-induced barrier lowering (DIBL). Therefore, the subthreshold leakage current reduces exponentially under stacking effect. For instance, considering the two-input NAND gate (see Figure 2) with stacking effect case (AB="00"), the positive potential at the intermediate node (Vinter > 0) between off-transistors (Tr1 and Tr2) causes the negative V<sub>GS</sub> and V<sub>BS</sub> of upper transistor (Tr1), and reduction in V<sub>DS</sub> of Tr1. Due to the stacking effect, leakage in a logic gate depends on the applied input vector during standby periods since it determines the number of off-transistors in the stack. In the following, existing techniques are described in more details.

Figure 2: Two-Input NAND Gate.

The input vector control (IVC) technique [16]-[18] is presented to find minimum leakage vector (MLV) which finding the input pattern that maximizes the number of off-transistors in all stacks across the circuit during standby periods. Leakage reduction can be achieved up to 39% savings if input vector control is used [18]. Implementing the predetermined vector (MLV) during standby mode is done by adding static latches at the inputs of the circuit [17].

The IVC technique does not guarantee that all logic gates of a circuit block are working under stacking effects due to the inverter and logic correlation between gates. Inherently, an inverter does not present the stacking effects since both networks (pull-up and pull-down) consist of a single transistor, and some logic gates did not benefit from IVC as shown in Figure 3 (a) which shows the sample path of the circuit block. For this reason, stack forcing technique [21] was introduced. The main objective of this technique is to increase the number of logic gates in stacking effects; a non-stacked transistor is changed into a stack of two transistors by replacing a single transistor with two transistors of the same size. Hence, stack forcing technique guarantees two off-transistors for every off-input of the gate, which reduces leakage currents as shown in Figure 3 (b). This technique, however, reduces the drive current due to the iso-input load

requirement, resulting in increased delay. Therefore, stack forcing technique can be used only for paths that are non-critical.

Figure 3: (a) logic gate parts of circuit block when predetermined input vector applied in standby mode (b) stack forcing applied to non-stacked logic gates.

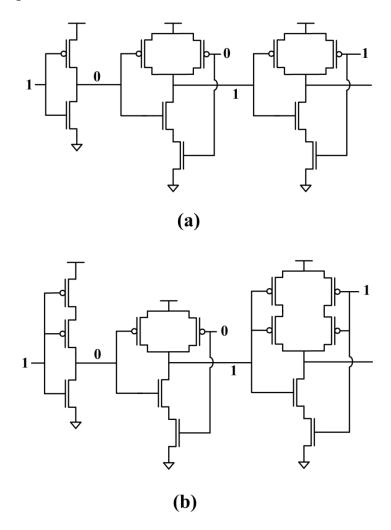

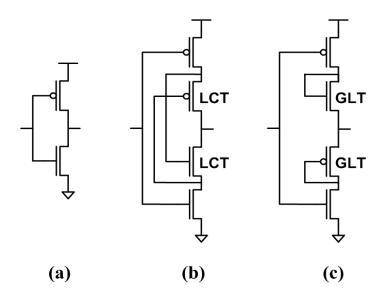

Another technique to reduce leakage power through stacking effects is LECTOR [22], which uses two extra transistors called leakage control transistors (LCTs) inserted in series between pull-up network and pull- down network in each CMOS gate as shown in Figure 4 (b). Leakage control transistors cause increase in resistance of the path from supply voltage (V<sub>DD</sub>) to ground since one of the LCTs is always near its cutoff region, thereby decreasing leakage current. However, this technique suffers from signal quality with technology scaling down to deep submicron era due to the LCTs [23].

Figure 4: (a) Original Inverter (b) LECTOR Inverter (c) GALEOR Inverter.

GALEOR technique [24] has the same structure as LECTOR except that the locations of extra transistors (referred to as Gated Leakage Transistors (GLTs)) are switched as shown in Figure 4 (c). PMOS GLT is located between pull-down network and output and NMOS GLT is located between pull-up network and

output. The effectiveness of this technique, however, reduced as technology scaling because of the signal quality problems [23].

#### 2.2.2 Leakage Reduction by Sleep Transistor

There are many ways to use a sleep transistor, but the basic idea is to increase the resistance by inserting the extra transistors (sleep transistors) in series between the power supply and ground, thereby reducing the standby leakage currents. The sleep transistors are turned on when circuits are in active mode and turned off when circuits are in standby mode. In the following, existing techniques are described in more details.

Figure 5: (a) single-V<sub>th</sub> stacking (b) Sleepy stack (c) Power gating (d) Drain gating.

In [25], the circuit is evaluated based on predetermined minimum leakage input vector, and additional leakage control transistors are inserted in the non-critical paths where only one transistor is originally turned "OFF" as shown in Figure 5 (a), and thereby reduce the subthreshold leakage. The extra transistor is turned on during the regular mode of operation and turned off during the idle mode of operation.

Sleepy stack technique [26] is an upgraded version of the stack forcing technique, using additional sleep transistors inserted parallel to one of the transistors in each set of two stacked transistors (forced stack), which is shown in Figure 5 (b). The sleep transistors of the sleepy stack operate in a way similar to the sleep transistors used in the sleep transistor technique where sleep transistors are turned on during active mode and turned off during sleep mode. As compared to the stack forcing technique, parallel connected sleep transistors cause the decrease in resistance of the path, thereby decreasing the propagation delay during active mode while stacked transistors suppress leakage current during standby mode. Sleepy stack technique, however, comes with some delay and significant area overheads since every transistor is replaced by three transistors.

Power gating [27] technique uses additional transistors, called sleep transistors, which are inserted in series between the power supply and pull-up (PMOS) network and/or between pull-down (NMOS) network and ground to reduce the standby leakage currents as shown in Figure 5 (c). The sleep transistors are turned "ON" when circuits are in active mode and turned off when circuits are in standby mode. By disconnecting the logic networks from the power supply and/or ground using sleep transistors, this technique reduces the leakage power in standby mode.

Figure 6: Transient characteristics of two-input NAND gate in LECTOR, GALEOR and Drain Gating simulated by HSPICE [23].

Another technique to reduce leakage power by using sleep transistor is the drain gating technique [23] reduces the leakage current by inserting extra sleep transistors between pull-up and pull-down networks. This technique introduced to overcome the limitations of LECTOR and GALEOR techniques. When applied to sub-45nm process technologies, both LECTOR and GALEOR techniques suffer a significant problem; that is, the low signal is very much higher than 0 volt. In addition, GALEOR causes high signal much lower than the VDD. Such phenomena make the use of both techniques unfeasible. A typical case for a 2input NAND gate using 45nm technology is shown in Figure 6, where the low signal is 0.2V for both LECTOR and GALEOR, and the high signal for GALEOR is 0.8V, rather than 0V and 1V, respectively. Similar troubling behaviors are consistently observed for all other gate types such as NOR, OR, AND, XOR. To make things worse, the problems become even more severe as process technology scales down such as in 32nm and 22nm process technologies [23]. As shown in Figure 5 (d), a PMOS sleep transistor(s) is placed between pull-up network and network output and an NMOS sleep transistor(s) is placed between network output and pull-down network. During active mode, both sleep transistors are turned on to reduce the resistance of conducting paths, thereby

reducing performance degradation. During standby mode, both sleep transistors are turned off to produce stacking effect which reduces leakage current by increasing resistance of the path from power supply to ground. By applying two turned-on sleep transistors in active mode, drain gating produces exact logic levels as shown in Figure 6 due to less resistance of the path from VDD to ground than that of LECTOR and GALEOR which always have one turned-on LCT/GLT and the other near cutoff region LCT/GLT, thus preventing exact logic state. Furthermore, the drain gating technique has less leakage current than LECTOR and GALEOR techniques because, in standby mode, two turned-off sleep transistors (drain gating) yield more resistance to the path from VDD to ground than the combined effect of a near cutoff region LCT/GLT and a turned-on LCT/GLT.

# 2.2.3 Leakage Reduction by Increasing the Threshold Voltages

Increasing the threshold voltage is one of the effective ways to reduce the leakage current. There are several ways to achieve this [28]: (1) increase a doping

concentration; (2) increase a gate oxide thickness; and (3) apply a reverse body bias voltage. In the following, existing techniques are described in more details.

Figure 7: Multi-Threshold CMOS (MTCMOS).

Multi-threshold voltage CMOS (MTCMOS) [28]-[32] uses high-threshold devices as sleep transistors while low-threshold devices are used to implement the logic as shown in Figure 7. In practice, one sleep transistor per gate is used, but larger granularities are also used, which require fewer but larger sleep transistors. Typically, the NMOS sleep transistor is preferable because the onresistance of NMOS is smaller than that of PMOS at the same width; hence, NMOS has size advantage over PMOS. This technique, however, comes with area and performance penalties.

Figure 8: Dual threshold voltage technique.

Dual threshold voltage technique [33]-[35] assigned different threshold voltages depending on whether a gate is on critical or non-critical path as shown in Figure 8. Low threshold voltage on the critical path is used to maintain the performance, while high threshold voltage assigned along non-critical path reduces the leakage current.

Figure 9: Reverse Body Biasing.

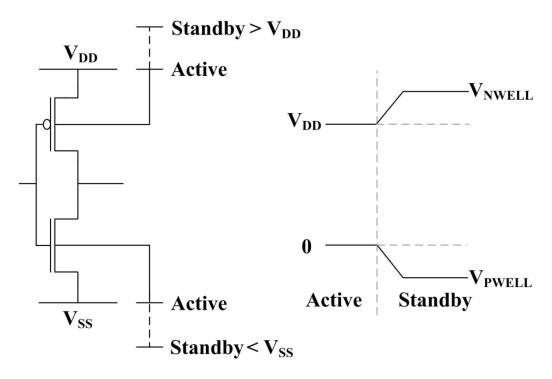

Reverse boy biasing (RBB) [8]-[12] is an effective way of reducing the leakage in standby mode by increasing the threshold voltages of MOS transistors (making the substrate (body) voltage higher than supply voltage for PMOS transistors and lower than ground for NMOS transistors); reverse biasing body-to-source junction of a MOS transistor widens the bulk depletion region and increases the threshold voltage. Reverse body bias is applied to suppress the leakage current when circuits are in standby mode, and is removed to restore the nominal performance of the transistors when circuits are in active mode as shown in Figure 9.

Adaptive body biasing (ABB) techniques have been introduced [36]-[40] in order to alleviate the impact of die-to-die and within-die parameter variations on microprocessor frequency and leakage. The aim of this technique is to meet the delay and power constraints in each die through post-silicon tuning; forward body bias is applied to the slow and less leaky devices to boost the performance while reverse body bias is applied to the fast and highly leaky devices to reduce the leakage. Therefore, effect of parameter variations is mitigated by post-silicon tuning, results in reducing the process variations impact as well as improving the total yield.

### Chapter 3

### **Analysis of Steady States in a CMOS**

### **Transistor**

#### 3.1 Introduction

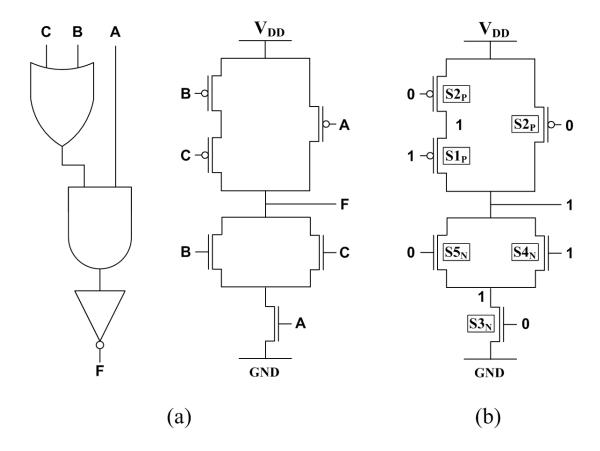

Rao *et al.* introduced six different steady states of MOS transistors for gate leakage estimation [41]. However, they made an overly simplified assumption that PMOS transistor has the same character as NMOS transistor. Such an assumption has led to a misleading conclusion that PMOS transistor has the counterpart of each steady state of NMOS transistor; that is, both NMOS and PMOS transistors have the same number (six) of steady states.

In this chapter, we first explore possible steady states of both PMOS and NMOS transistor in a CMOS circuit, and demonstrate that possible steady states of PMOS transistor is not six but five. And then we present the five distinct types of steady states based on leakage components of a single transistor, and analyze the components of steady state transistor in on- and off-state CMOS network. Finally, we define the main steady states of a CMOS transistor.

#### 3.2 Possible Steady States for CMOS Transistors

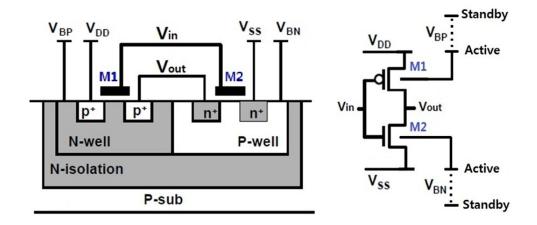

Figure 10: All possible bias conditions for CMOS transistors.

A single transistor has four terminal nodes: gate (G), drain (D), source (S) and body (B). The NMOS and PMOS body connected to ground (logic 0) and VDD (logic 1) respectively. The body and gate nodes have full logic values (either VDD or ground) in steady state conditions, while the other nodes (drain and source) have either at or close to full logic values depending on circuit structures.

Figure 10 shows the major leakage currents of eleven steady states in NMOS (S1<sub>N</sub>-S6<sub>N</sub>) and PMOS (S1<sub>P</sub>-S5<sub>P</sub>) transistors. The logic values "1" and "0" are represented by the high and low level of each terminal node. The direction of

current flows for MOS transistor is determined by voltage between gate and source (VGS), gate and drain (VGD), gate and body (VGB), drain and body (VDB), drain and source (VDS), and source and body (VSB).

Among four nodes in MOS transistor, drain and source nodes are dependent nodes since their logic values determined by either logic value of gate node or by circuit structure:

- In conducting (on) MOS transistor, gate node of NMOS (PMOS) transistor connected to V<sub>DD</sub> (ground). In this condition, the dependent nodes (drain and source nodes) are only determined by gate node. Hence, a source node has the same logic value as a drain node (S2<sub>N</sub>, S4<sub>N</sub>, S2<sub>P</sub> and S4<sub>P</sub> in Figure 10)

- In non-conducting (off) MOS transistor, gate node of NMOS (PMOS) transistor connected to ground (VDD). In this condition, dependent nodes are determined not only by gate node, but also by circuit structure. Intuitively, in a non-conducting transistor, it is clear that one of dependent nodes is 0 regardless of the other dependent node (either 1 or 0). This behavior works well under most circumstances of non-conducting transistor; this is shown as S1N, S3N, S6N, S3P and S5P in Figure 10.

However, in certain cases (S5<sub>N</sub> and S1<sub>P</sub> in Figure 10), dependent nodes are not determined by gate node but by circuit structure, resulting in both drain and source nodes being 1 even though the transistor is in an off-state.

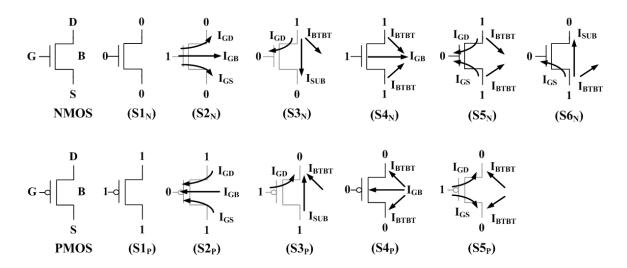

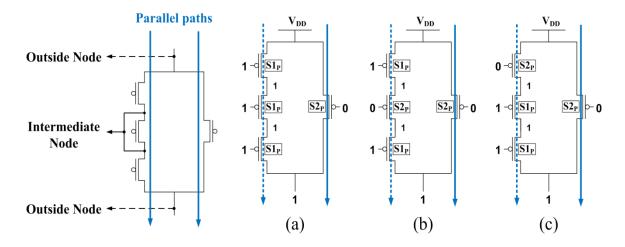

Figure 11: Pull-down network structure in the presence of S5<sub>N</sub>.

Let us first consider an NMOS case. S5<sub>N</sub> will exist only if all of the following conditions are met: (1) logic value of outside nodes in parallel structure is 1 (high), which means that at least one of paths in parallel structure is "on"; (2) at least one of paths in parallel structure contains an off-transistor, and hence this path is "off"; this is shown in Figure 11.

Figure 12: (a) 3-input OAI-21 gate ( $F = \overline{A(B+C)}$ ) (b) Input: ABC = 001.

Table 1: Logic values and node voltages (V) of each transistor in 3-input OAI-21 gate with input (ABC) = "001".

| Network | Input | State            | No      | de Volt | age   | Logic value |      |      |  |

|---------|-------|------------------|---------|---------|-------|-------------|------|------|--|

| retwork | прис  |                  | $V_{D}$ | $V_{G}$ | Vs    | D           | G    | S    |  |

|         | A     | S <sub>2</sub> P | 1.1     | 0       | 1.1   | high        | low  | high |  |

| PUN     | В     | S <sub>2</sub> P | 1.1     | 0       | 1.1   | high        | low  | high |  |

|         | С     | S1 <sub>P</sub>  | 1.1     | 1.1     | 1.1   | high        | high | high |  |

|         | A     | S3 <sub>N</sub>  | 0.846   | 0       | 0     | high        | low  | low  |  |

| PDN     | В     | S5 <sub>N</sub>  | 1.1     | 0       | 0.846 | high        | low  | high |  |

|         | С     | S4 <sub>N</sub>  | 1.1     | 1.1     | 0.846 | high        | high | high |  |

Note that in the case described by condition (1), non-conducting transistors need to be located in the bottom of serial structure in order to have a high logic value at the bottom node of outside nodes. Hence, S5<sub>N</sub> exists only in a combination of serial and parallel MOS structures, which can be found in complex (compound) CMOS logic gates. For instance, Figure 12 (a) shows a 3-input OAI-21 gate ( $F = \overline{A(B+C)}$ ) implemented with complex CMOS logic. Figure 12 (b) shows the particular input vector of OAI-21 gate which meets the conditions for the existence of S5<sub>N</sub> case. Table 1 lists the corresponding bias voltage and logic value of each node in Figure 12 (b); PUN and PDN stand for pull-up network and pull-down network, respectively.

In this chapter, all experimental data are conducted by HSPICE using the default 65nm PTM [42] at room temperature (standby mode).

Figure 13: (a) 2-input NAND gate with input (AB) =10 (b) 2-input NOR gate with input (AB) =11.

Table 2: Logic values and node voltages (V) of each transistor in 2-input NAND gate with input (AB) = "10", and NOR gate with input (AB) = "11".

| Gate  | Network Input |     | State                       | Node    | ge      | Logic value |      |      |      |

|-------|---------------|-----|-----------------------------|---------|---------|-------------|------|------|------|

| type  | Network       | при | State                       | $V_{D}$ | $V_{G}$ | Vs          | D    | G    | S    |

|       | DIINI         | A   | S1 <sub>P</sub>             | 1.1     | 1.1     | 1.1         | high | high | high |

| NAND2 | PUN           | В   | S2P                         | 1.1     | 0       | 1.1         | high | low  | high |

| NAND2 | PDN           | A   | S4 <sub>N</sub>             | 1.1     | 1.1     | 0.847       | high | high | high |

|       |               | В   | S3 <sub>N</sub>             | 0.847   | 0       | 0           | high | low  | low  |

|       | PUN           | A   | S1 <sub>P</sub>             | 0.990   | 1.1     | 1.1         | high | high | high |

| NODO  |               | В   | S <sub>3</sub> <sub>P</sub> | 2.13E-6 | 1.1     | 0.990       | low  | high | high |

| NOR2  | PDN           | A   | S2 <sub>N</sub>             | 2.13E-6 | 1.1     | 0           | low  | high | low  |

|       |               | В   | S2 <sub>N</sub>             | 2.13E-6 | 1.1     | 0           | low  | high | low  |

Figure 14: (a) 3-input AOI-21 gate ( $F = \overline{A + BC}$ ) (b) Input: ABC = 110.

Table 3: Logic values and node voltages (V) of each transistor in 3-input AOI-21 gate with input (ABC) = "110".

| Network | т ,   | State                       | No      | age     | Logic value |      |      |      |

|---------|-------|-----------------------------|---------|---------|-------------|------|------|------|

|         | Input |                             | $V_{D}$ | $V_{G}$ | $V_{S}$     | D    | G    | S    |

| PUN     | A     | S <sub>3</sub> <sub>P</sub> | 2.81E-5 | 1.1     | 1.1         | low  | high | high |

|         | В     | S1 <sub>P</sub>             | 1.1     | 1.1     | 1.1         | high | high | high |

|         | С     | S2 <sub>P</sub>             | 1.1     | 0       | 1.1         | high | low  | high |

|         | A     | S2 <sub>N</sub>             | 2.81E-5 | 1.1     | 0           | low  | high | low  |

| PDN     | В     | S2 <sub>N</sub>             | 2.81E-5 | 1.1     | 3.00E-5     | low  | high | low  |

|         | С     | S1 <sub>N</sub>             | 3.00E-5 | 0       | 0           | low  | low  | low  |

Now, let us consider the PMOS case. Unlike NMOS case (S5N), S1P can exist in non-complex CMOS logic gate, and thus it also present complex CMOS logic gate. To elucidate this, we consider two-input NAND and NOR gates as illustrated in Figure 13. S1P can be existed not only parallel structure (Figure 13 (a)) but also serial structure (Figure 13 (b)). Table 2 lists the corresponding bias voltage and logic value of each transistor in Figure 13. Note that the first non-conducting transistor from output node presents the S3N and S3P in off-state pull-down and pull-up network, respectively. Figure 14 shows the presence of S1P in complex CMOS logic gate (3-input AOI-21). Table 3 lists the corresponding bias voltage and logic value of each transistor in Figure 14.

Figure 15: Pull-down network structures in the presence of S6<sub>N</sub>.

Figure 16: (a) 4-input AOAI-211 gate ( $F = \overline{A(B + CD)}$ ) (b) Input: ABCD = 0100.

Table 4: Logic values and node voltages (V) of each transistor in pull-down network of 4-input AOAI-211 gate with input (ABCD) = "0100".

| Input Stat | C1 1            | N     | ode Volta | Logic value |      |      |      |

|------------|-----------------|-------|-----------|-------------|------|------|------|

|            | State           | VD    | $ m V_G$  | Vs          | D    | G    | S    |

| A          | S3 <sub>N</sub> | 0.846 | 0         | 0           | high | low  | low  |

| В          | S4 <sub>N</sub> | 1.1   | 1.1       | 0.846       | high | high | high |

| С          | S3 <sub>N</sub> | 1.1   | 0         | 0.237       | high | low  | low  |

| D          | S6n             | 0.237 | 0         | 0.846       | low  | low  | high |

Additionally, S6N will exist under the same structural formation in the presence of S5N except for the number of off-transistors in off-path; S6N will exist only if the off-path has at least two off-transistors connected in series as shown in Figure 15. Note that S6N and S3N always coexist with each other. S6N and S3N exist only in complex logic gate just like the S5N case. For instance, Figure 16 (a) shows a 4-input AOAI-211 gate  $F = \overline{A(B+CD)}$  implemented with complex CMOS logic. Figure 16 (b) shows the particular input vector of AOAI-211 gate which meets the conditions for the existence of S6N case. Table 4 lists the corresponding bias voltages and logic values of each node in Figure 16 (b).

An important point to note is that the counterpart of S6N does not exist in the PMOS transistor unlike other steady states; on-transistors of PMOS (S2P and S4P) are the counterparts of on-transistors of NMOS (S4N and S2N), and off-transistors of PMOS (S1P, S3P and S5P) are the counterparts of NMOS (S5N, S3N and S1N). To demonstrate this, we apply the same conditions for the existence of S6N to the PMOS case (Figure 17). It is shown that logic values of the all intermediate nodes are not 0 (low) but 1 (high), and thus, PMOS transistor has not six but five steady states unlike the assumption made in previous work [41]; experimental data is shown in Table 5.