#### **Syracuse University**

#### **SURFACE**

Electrical Engineering and Computer Science -Dissertations

College of Engineering and Computer Science

12-2011

## State-Based Techniques For Designing, Verifying And Debugging Message Passing Systems

Rajaa Khaled Algudah Syracuse University

Follow this and additional works at: https://surface.syr.edu/eecs\_etd

Part of the Computer Engineering Commons

#### **Recommended Citation**

Alqudah, Rajaa Khaled, "State-Based Techniques For Designing, Verifying And Debugging Message Passing Systems" (2011). Electrical Engineering and Computer Science - Dissertations. 313. https://surface.syr.edu/eecs\_etd/313

This Dissertation is brought to you for free and open access by the College of Engineering and Computer Science at SURFACE. It has been accepted for inclusion in Electrical Engineering and Computer Science - Dissertations by an authorized administrator of SURFACE. For more information, please contact surface@syr.edu.

#### **ABSTRACT**

Message passing systems support the applications of concurrent events, where independent or semi-independent events occur simultaneously in a nondeterministic fashion. The nature of independence, random interactions and concurrency made the code development of such applications complicated and error-prone. Conventional code development environments or IDEs, such as Microsoft Visual Studio, provide little programming support in this regard. Furthermore, ensuring the correctness of a message passing system is a challenge. Typically, it is important to guarantee that a system meets its desired specifications along its construction process. Model checking is one of the techniques used in software verification which has proven to be effective in discovering hidden design and implementation errors. The required advanced knowledge of formal methods and temporal languages is one of the impediments in adopting model checking by software developers. To integrate model checking environments and conventional IDEs, this dissertation proposes a multi-phase development framework that facilitates designing, verifying, implementing and debugging state-based message passing systems. The techniques and design principles of the proposed framework focus on improving and easing the software development experience. In the first phase, a two-level design methodology is proposed through using abstract high-level communication blocks and hierarchical state-behavioral descriptions that were developed in this research. In the second phase, a new method based on choosing from a pre-determined set of patterns in concurrent communication properties is proposed to facilitate collecting the essential specifications of the system where the atomic propositions are linked with the

system design. A complex property can be attained by hierarchically nesting some of these patterns. A procedure to automatically generate formal models in a model checker (MC) language is proposed. Once the model that contains both the design and the properties of the system are generated, a model checker is used to verify the correctness of the proposed system and ensure its compliance with specifications. To help in locating the source of an undesired specification, if any, a procedure to map a counter example generated by the MC to the original design is presented. In the third phase, a skeleton code of the design specification is generated in a general programming language such as Microsoft C#, Java, etc. moreover, the ability to debug the generated code using a conventional IDE while tracing the debugging process back to the original design was established. Finally, a graphical software tool that supports the proposed framework is developed where SPIN MC is used as a verifier. The tool was used to develop and verify several case studies. The proposed framework and the developed software tool can be considered a key solution for message passing systems design and verification.

# STATE-BASED TECHNIQUES FOR DESIGNING, VERIFYING AND DEBUGGING MESSAGE PASSING SYSTEMS

by Rajaa Khaled Alqudah

B.S., Yarmouk University, 2003 M.S., Northeastern University, 2007

Dissertation

Submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Computer Engineering

Syracuse University

December 2011

Copyright © Rajaa Khaled Alqudah 2011

All Rights Reserved

## **Contents**

| Li | List of Figures |          |                                              |      |  |  |  |  |

|----|-----------------|----------|----------------------------------------------|------|--|--|--|--|

| Li | List of Tables  |          |                                              |      |  |  |  |  |

| A  | cknov           | vledgme  | ents                                         | X    |  |  |  |  |

| 1  | Intr            | oductio  | n                                            | 1    |  |  |  |  |

|    | 1.1             | Backg    | round                                        | . 5  |  |  |  |  |

|    |                 | 1.1.1    | Message Passing Systems                      | . 5  |  |  |  |  |

|    |                 | 1.1.2    | Software Verification                        |      |  |  |  |  |

|    |                 | 1.1.3    | Model Checking                               | . 7  |  |  |  |  |

|    | 1.2             | Motiva   | ations and Contributions                     | . 13 |  |  |  |  |

|    | 1.3             | Disser   | tation Outline                               | . 17 |  |  |  |  |

| 2  | Rev             | iew of L | iterature                                    | 18   |  |  |  |  |

|    | 2.1             | Model    | Checking in Software Verification            | . 18 |  |  |  |  |

|    |                 | 2.1.1    | Modeling System Specifications               | . 19 |  |  |  |  |

|    |                 | 2.1.2    | Systems Properties                           | . 21 |  |  |  |  |

|    |                 | 2.1.3    | Model Checking Tools                         | . 21 |  |  |  |  |

|    | 2.2             | Debug    | ging multi process applications              | . 25 |  |  |  |  |

| 3  | A F             | ramewo   | ork for Message Passing Systems Development  | 31   |  |  |  |  |

|    | 3.1             | Overvi   | iew                                          | . 31 |  |  |  |  |

|    | 3.2             | Systen   | n Design                                     | . 33 |  |  |  |  |

|    |                 | 3.2.1    | High-Level Block Design                      |      |  |  |  |  |

|    |                 | 3.2.2    | State-Behavioral Description                 | . 38 |  |  |  |  |

|    |                 | 3.2.3    | Comparing to Petri Nets                      | . 42 |  |  |  |  |

|    |                 | 3.2.4    | Hierarchical Designed-For-Verification CEFSM |      |  |  |  |  |

|    | 3.3             | Concu    | rrent Property Specifications                | . 47 |  |  |  |  |

|    |                 | 3.3.1    | Pattern based properties                     | . 48 |  |  |  |  |

|      | 5.1.3 PROME                                                                              | LA Model Generation                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 5.1.2 Modelin                                                                            | g TCP                                                                                                                                                                                                                                                                                                                                                                                 | 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.1  | Transmission Co                                                                          | ontrol Protocol (TCP)                                                                                                                                                                                                                                                                                                                                                                 | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Case | Study                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                     | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.8  | Summary                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                       | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                       | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.5  |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                       | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | 4.4.2 Built-in                                                                           | Properties                                                                                                                                                                                                                                                                                                                                                                            | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | 4.4.1 User spe                                                                           | ecific LTL Properties                                                                                                                                                                                                                                                                                                                                                                 | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.4  | Verification                                                                             |                                                                                                                                                                                                                                                                                                                                                                                       | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                       | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                       | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                     | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.3  |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                       | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | - •                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                       | 76<br>78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | C                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                       | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |                                                                                          | 66 6                                                                                                                                                                                                                                                                                                                                                                                  | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.1  | Summary                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                       | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                       | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                       | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.4  |                                                                                          | on and Verification                                                                                                                                                                                                                                                                                                                                                                   | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | 3.5<br>3.6<br>3.7<br>MPS<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>Case | 3.5 Code Generation 3.6 Debugging 3.7 Summary  MPS Verification and 4.1 Model Designer 4.2 Property Editor 4.3 Model Generation 4.3.1 Translation 4.3.2 Timers in 4.3.2 Timers in 4.3.4 Correction 4.4.4 Verification 4.4.1 User specification 4.4.2 Built-in 4.5 Error Localization 4.6 Code Generation 4.7 Debugging 4.8 Summary  Case Study 5.1 Transmission Company 5.1.1 TCP con | 3.5 Code Generation 3.6 Debugging . 3.7 Summary  MPS Verification and Debugging Tool 4.1 Model Designer 4.2 Property Editor 4.3 Model Generation . 4.3.1 Translation Steps 4.3.2 Timers in PROMELA 4.3.3 LTL Properties in PROMELA 4.3.4 Correctness of the PROMELA Model Generation 4.4 Verification 4.4.1 User specific LTL Properties 4.4.2 Built-in Properties 4.5 Error Localization 4.6 Code Generation 4.7 Debugging . 4.8 Summary  Case Study 5.1 Transmission Control Protocol (TCP) 5.1.1 TCP connection management |

## **List of Figures**

| 1.1  | Model Checking Example                                                       | 9          |

|------|------------------------------------------------------------------------------|------------|

| 1.2  | A Kripke structure for two processes that preserve mutual exclusion [10] 1   | 0          |

| 1.3  |                                                                              | 1          |

| 1.4  | Until Operator                                                               | 1          |

| 1.5  |                                                                              | 4          |

| 1.6  |                                                                              | 6          |

| 2.1  | Time line for a Call waiting requirements [38]                               | 22         |

| 2.2  | 1                                                                            | 22         |

| 2.3  | SPIN Architecture                                                            | 24         |

| 2.4  | Parallel Debugger Architecture [51]                                          | 29         |

| 3.1  | J                                                                            | 3          |

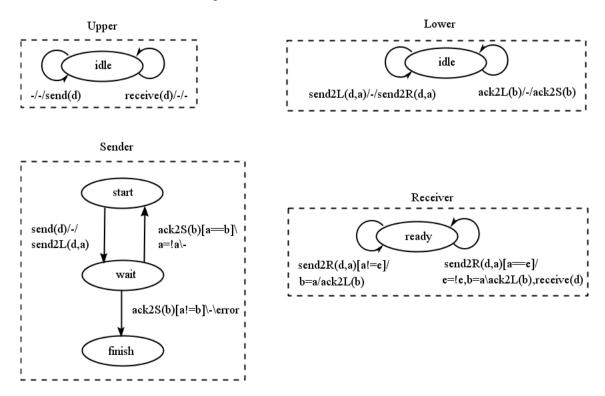

| 3.2  | High-Level Block Design of a simple reliable transfer protocol               | 36         |

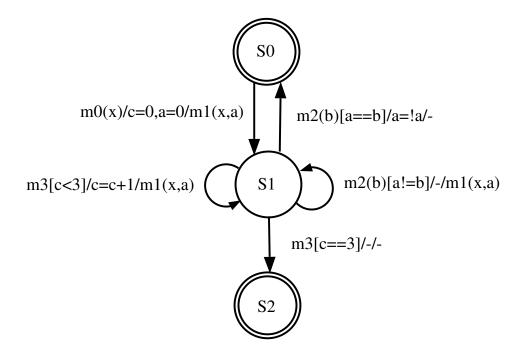

| 3.3  | DV-CEFSM Example                                                             | 11         |

| 3.4  | The state behavioral design of the four blocks in the Simple Reliable Trans- |            |

|      |                                                                              | 12         |

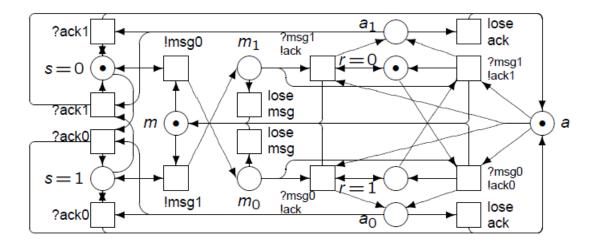

| 3.5  | Simple Reliable Transfer Protocol in Petri Net                               | 14         |

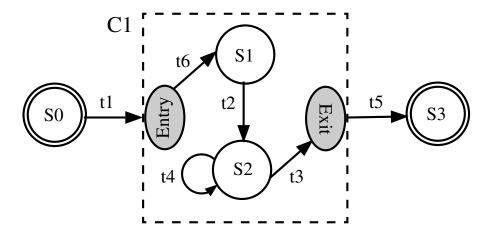

| 3.6  | An Example of Hierarchical CEFSM                                             | <b>!</b> 7 |

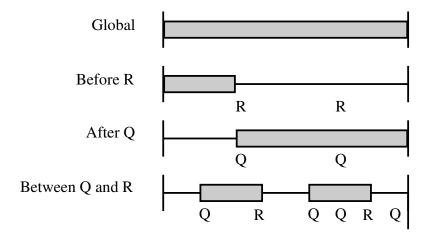

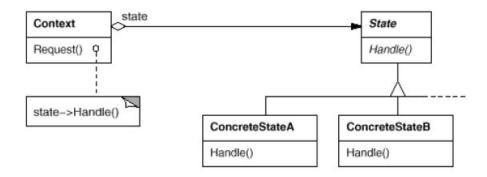

| 3.7  | Event-Based Specification Pattern Ranges [62]                                | 19         |

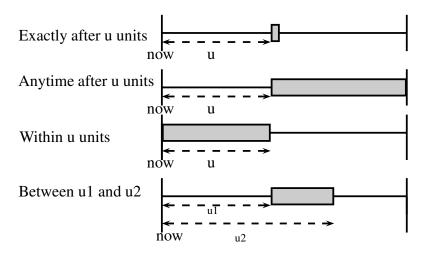

| 3.8  | Relative time Pattern Ranges                                                 | 8          |

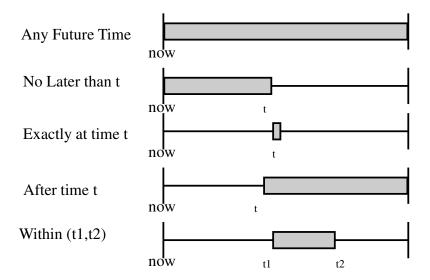

| 3.9  | Absolute time Pattern Ranges                                                 | 59         |

| 3.10 | State Design Pattern Structure [64]                                          | 68         |

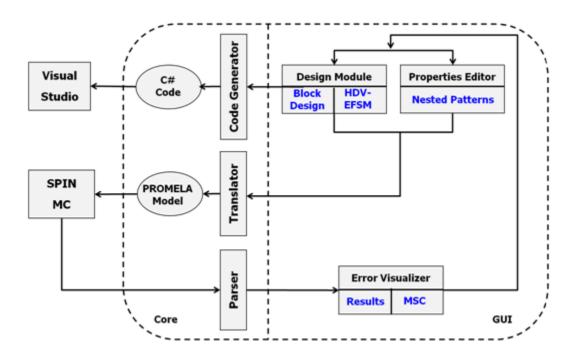

| 4.1  | Proposed tool                                                                | 73         |

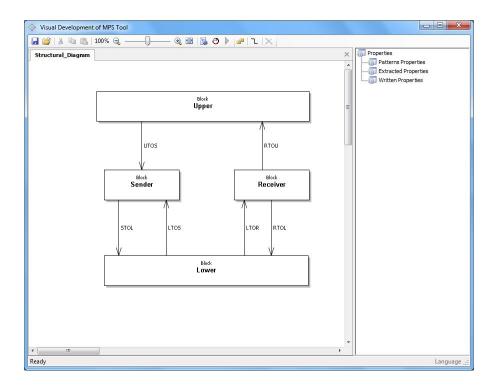

| 4.2  | High-Level Block diagram of the simple reliable transfer protocol            | 74         |

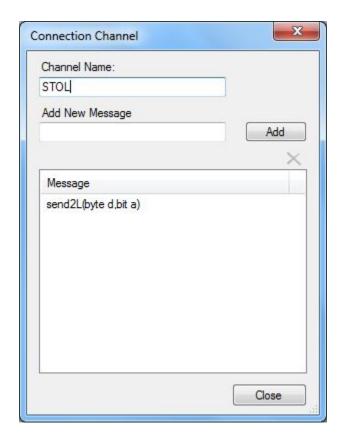

| 4.3  | Channel Editing Form                                                         | 75         |

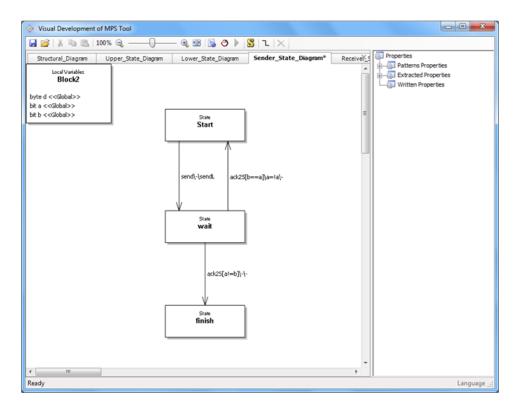

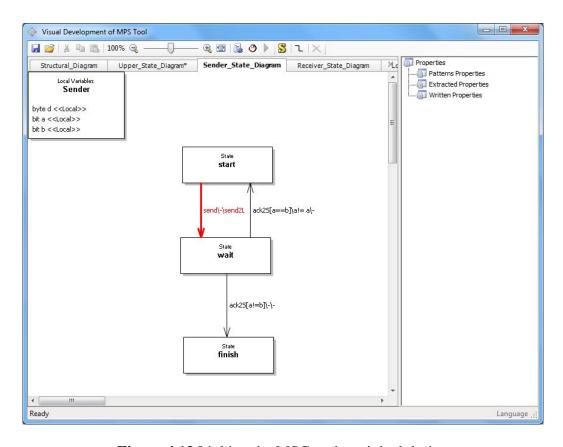

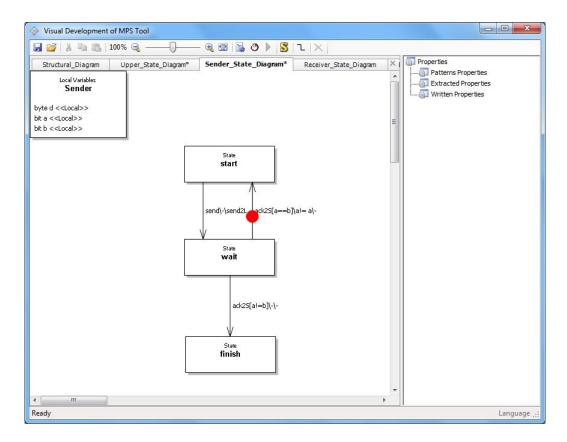

| 4.4  | State-Behavioral diagram for Sender Block                                    | 6          |

| 4.5  | Form to add local variables                                                  | 77         |

| 4.6  | $\boldsymbol{\mathcal{U}}$                                                   | 78         |

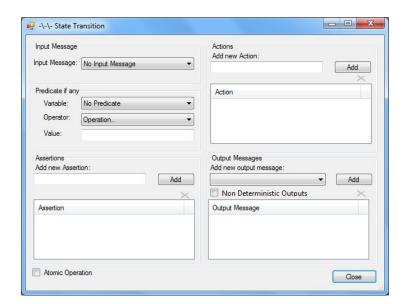

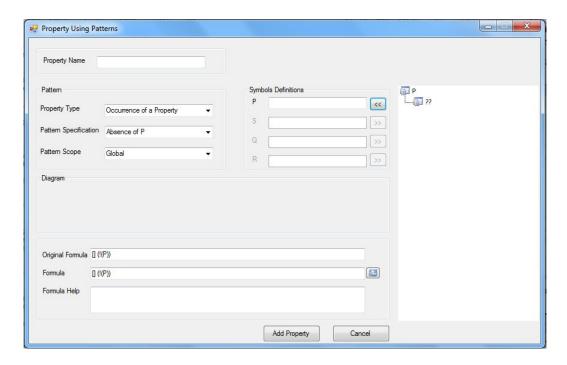

| 4.7  | Property Using Patterns Form                                                 | 79         |

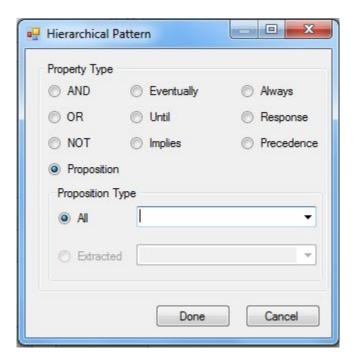

| 4.8  | Form to build the property hierarchically                   |

|------|-------------------------------------------------------------|

| 4.9  | Form to add timers                                          |

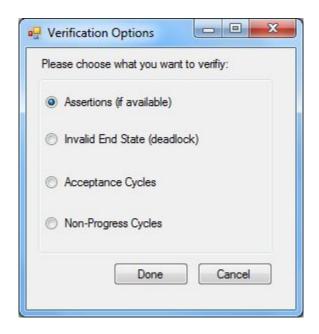

| 4.10 | Verification Options                                        |

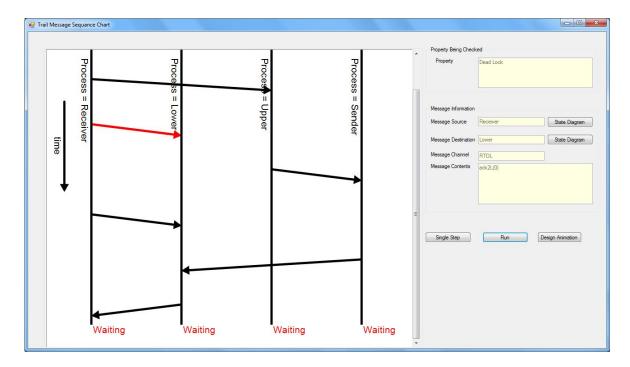

| 4.11 | The Trail Message Sequence Chart                            |

| 4.12 | Linking the MSC to the original design                      |

| 4.13 | Inserting a break point to a state transition in the design |

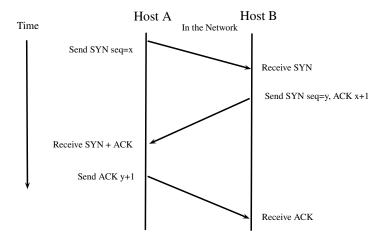

| 5.1  | TCP three-way handshaking [76]                              |

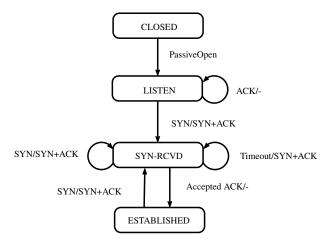

| 5.2  | State diagram of TCP Server                                 |

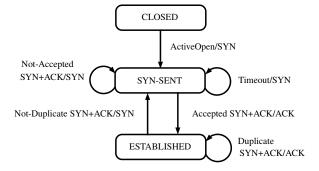

| 5.3  | State diagram of TCP Client                                 |

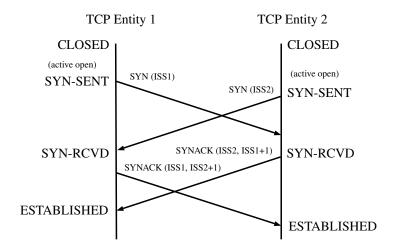

| 5.4  | Simultaneous TCP three-way handshaking [76]                 |

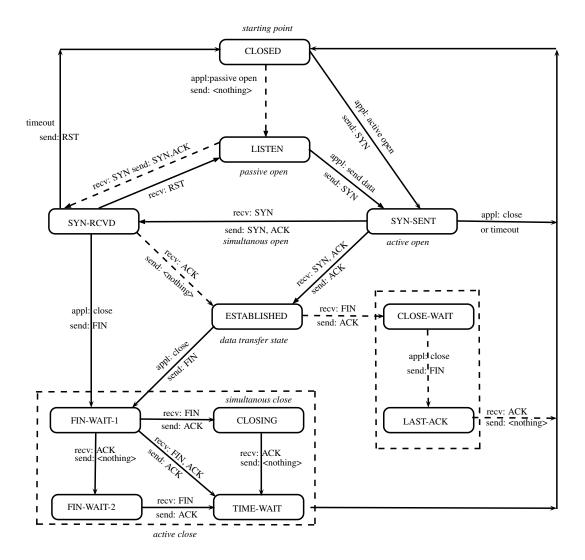

| 5.5  | Finite State Diagram of TCP [76]                            |

| 5.6  | Structural Diagram of TCP                                   |

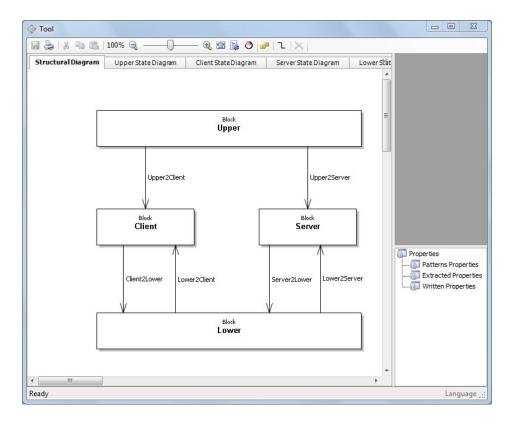

| 5.7  | Building Structural Diagram of TCP                          |

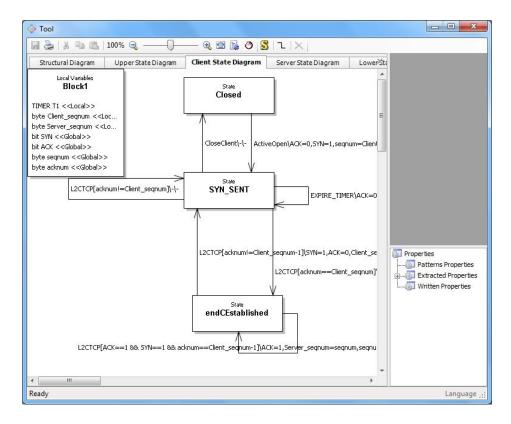

| 5.8  | Behavioral Diagram of TCP Client                            |

## **List of Tables**

| 3.1  | Never Pattern LTL Mapping                                 | 50 |

|------|-----------------------------------------------------------|----|

| 3.2  | Invariant Pattern LTL Mapping                             | 51 |

| 3.3  | Existence Pattern LTL Mapping                             | 52 |

| 3.4  | At-Most-K Existence Pattern LTL Mapping where <i>K</i> =2 | 53 |

| 3.5  | Recursive Exactly-K Existence Pattern for Global Scope    | 54 |

| 3.6  | Exactly-K Existence Pattern LTL Mapping where K=2         | 54 |

| 3.7  | At-Least-K Existence Pattern LTL Mapping                  | 55 |

| 3.8  | Sub-Set Existence Pattern LTL Mapping                     | 55 |

| 3.9  | Response Pattern LTL Mapping                              | 56 |

| 3.10 | Precedence Pattern LTL Mapping                            | 56 |

| 3.11 | Sequence of Events Pattern LTL Mapping                    | 57 |

| 3.12 | Set of Events Pattern LTL Mapping                         | 57 |

#### **ACKNOWLEDGMENTS**

The success of this research endeavor has been due to the help and support of many professors, friends, and family members. First, I wish to extend my gratitude to my dissertation advisor, Dr. C. Y. Roger Chen, for giving me the opportunity to study under his guidance and for his mentoring contributions towards my growth as a graduate student, researcher, and as a person, in addition to his encouragement, valuable comments and suggestions that helped shape this research work. I would like to also thank Dr. James Fawcett and Dr. Dan Pease who provided valuable insights and comments throughout this research. I am also thankful to the dissertation committee members for their help and time.

I am thankful to my friends who have contributed a great deal towards my success and completion of this dissertation. I am forever grateful to my parents for their sacrifices that paved the way towards the successful completion of my education. Finally, I would like to thank my husband Emad and my lovely daughter Jude for their standing by my side throughout this time and for their long patience.

## **Chapter 1**

## Introduction

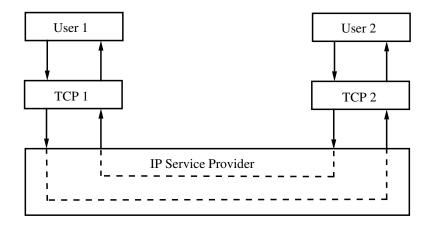

Message Passing Systems (MPS), such as multi-thread or multi-process based programming environments, support the applications of concurrent events, where independent or semi-independent events occur simultaneously in a nondeterministic fashion. Communication protocols, such as the Transmission Control Protocol (TCP), are typical examples of such applications where a set of rules govern the syntax, semantics and synchronization of communication between nodes via a network. Typically, this communication happens to achieve a reliable transfer of data from one node to another. The design, verification, development and debugging of Message Passing Systems (MPS) tend to be a difficult task and subject to errors that are not common in single-process applications. Most of these

errors come from the non-deterministic nature of events during the execution. Deadlocks and race conditions are examples of these errors just to mention few. Conventional code development environments or IDE, such as Visual Studio, provide little programming support or assistance in this regard. A large body of research has focused on techniques that can help verifying and validating software systems, examples can be found in [1–5].

Software testing is a common technique in which experiments are conducted on the actual system before deployment to assure its compliance with requirements. For testing to be effective it requires checking all the possible inputs and states; this is a costly and time-consuming process that makes it impractical in most cases. Moreover, even a heavily tested system may have errors that hardly appear or are impossible to replicate. Limitations in time and resources encouraged industry to find different methods to verify their systems other than dealing with the actual system.

Formal verification is a technique in which the correctness of the system is proven or disproven using mathematical and formal methods [6]. One approach of formal verification is model checking. Model checking is a technique to automatically test if a model of a system meets a given specification by exhaustively exploring all the possible executable paths. Using model checking in the verification process requires building a model of the system in some formal language accepted by the MC in addition to writing the requirement specifications as temporal logic formulas. Building a model and writing temporal properties

require knowledge in the model checker programming language and a strong mathematical background. These obstacles prevent using the model checking technique widely in the software development process.

From the other hand, debugging is a process conducted to discover bugs that may reside in a software system by allowing the programmer to monitor the execution of the system, pause it, set some breakpoints and check the values in memory or even change it at runtime. This technique uses stop-the-world [7] approach which may be useful for debugging single process applications but not sufficient for multi-process applications. To our best knowledge, there is no debugger tool that helps developers in debugging distributed systems by providing a high-level picture of the current state of the application execution, visualizing all the interactions between processes, and reasoning about processes. Several attempts exist in the literature to facilitate using model checking techniques in software verification and to fill the existing gap between existing model checkers and the development environments.

There is a need for a comprehensive framework to help software developers design, verify, implement and debug their systems without the need to learn all the mathematical details of formal verification. To address this problem, a multiple phase approach for developing, verifying and debugging state-based message passing systems is proposed in this dissertation. The target system is described using a two-level design approach: abstract communication blocks level and hierarchical state-behavioral specification level. A procedure

to automatically generate formal models in a MC language is proposed. Moreover, a new method based on choosing from a pre-determined set of patterns in concurrent communication properties is proposed to facilitate collecting the essential specifications of the system. Once the model and the properties of the system are generated, a model checker is used to verify the correctness of the proposed system and ensure its compliance with specifications. In case of any inconsistencies found, the error source will be automatically localized using an algorithm that was developed for this purpose. A skeleton code of the system that includes the correct design specifications is generated in a general programming language i.e. Microsoft C#, Java, etc., moreover, the ability to debug the generated code using a conventional IDE, such as Visual Studio, while tracing the debugging process back to the original design is established.

The proposed approach was successfully implemented in the form of a tool support that was developed in Microsoft C# where SPIN model checker was used as the verification engine. Several case studies are presented to show this frame work effectiveness. The following section gives a background about message passing systems, software verification and model checking.

1.1 Background 5

### 1.1 Background

#### 1.1.1 Message Passing Systems

Message Passing is a model of communication in a distributed system where messages are sent from one node to another. In general, the purposes of this communication can be one of the following: resource sharing, concurrency, scalability, transparency, openness or fault-tolerance [8]. A message is a collection of data objects that can be managed by a process and delivered to the destination. Usually, the communication between processes is governed by rules that should be followed to ensure the success of the communication. These rules are called communication protocols.

#### 1.1.2 Software Verification

As software systems are being widely involved in everyday life, the need for reliable systems is critical and the failure is unacceptable. The process for checking if a software system meets its specification is called software verification. Many techniques can be used to verify the correctness of a software system. Simulation, testing, deductive verification and model checking are among these techniques. While simulation is a technique in which experiments are conducted on an abstraction or model of the system, testing, on the other hand, is a technique in which experiments are conducted on the actual system before the

deployment. Verifying the correctness of a system using simulation or testing requires checking all of its possible inputs and states which is time-consuming and impractical in most cases. Moreover, even a heavily tested system can have errors that hardly appear and are impossible to replicate. When an error is detected, it is often difficult to spot since, in most cases, the sequence of events leading to this error cannot be reconstructed.

Deductive verification involves using axioms and proof rules to verify the correctness of a system. This method, which can be used for infinite and finite state systems, is not fully automatic and needs to be done by experts in logical reasoning since a lot of user interaction and guidance for the theorem proving tool is required. Moreover, using this technique is a time-consuming process which may last from days to months to prove a single protocol or circuit. Consequently, the use of this method is limited to highly sensitive systems such as security protocols.

The most widely used verification technique is Model checking [6] which is an automated method in which the system to be verified is modeled as a finite state machine and the specifications to be proven are written as temporal logic properties.

1.1 Background 7

#### 1.1.3 Model Checking

Given a finite-state model of a system and a logical property, model checkers check whether this property holds for that model or not by exploring all the possible executions paths of the state machine and checking if the property being tested holds. In case the property fails, a counterexample is generated in the form of a sequence of states.

The logical properties of a system can be classified into two major categories, safety and liveness properties. The safety property specifies what should not ever happen or what should always happen. In model checking, a counterexample of safety property is a list of states where the last state contradicts the property. Conversely, the liveness property specifies what should eventually happen. A counterexample is a loop that does not contain a state with a specified property [6].

One restriction of using model checking is the number of states in the system to be verified. Since the model checker uses an exhaustive search of the state space of the system and the number of states can grow exponentially with respect to the number of values, the state space of a system can be very large, or even infinite. Thus it is impossible to explore the entire state space with the limited resources of time and memory. This problem is called "state explosion problem".

In many cases, model checker tools are able to find errors that cannot be found by simulation. This is due to two major reasons; first, model checkers examine all possible executions of the system while simulators examine a relatively small part of these executions. Second, writing the temporal properties in formal language can help the designer in clarifying ambiguities in the system's specifications.

To use model checker, the behavior of the target system should be presented by some formal structure. Usually, the behavior of the system is represented by a Kripke Structure proposed in [9]. Kripke structure is a graph such that its nodes are the states of the system and its edges are the state transitions. Formally, a Kripke structure M is a 4-tuple M=(S, I, R, L) where S is a finite set of states,  $I \subseteq S$  is a set of the initial states,  $R \subseteq S \times S$  is a transition relation where  $\forall s \in S, \exists s' \in S$  such that  $(s,s') \in R$  and  $L: S \to 2^{AP}$  is a labeling function that maps each node to a set of properties that hold in the corresponding state where AP is a set of atomic propositions, i.e., boolean expressions over variables, constants or predicate symbols. A path in the structure M from a state s is an infinite sequence of states  $\pi = s_0 s_1 s_2 ...$  such that  $s_0 = s$  and  $R(s_i, s_{i+1})$  holds for all  $i \ge 0$ .

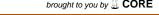

As an example, Figure 1.1 gives the pseudo code of two processes competing at some shared resource. Only one process at a time can use this resource. This problem is known as mutual exclusion [10]. Each process has a program counter where 1 represents the critical section. Any process can access the shared resource only if this process is in its critical

1.1 Background 9

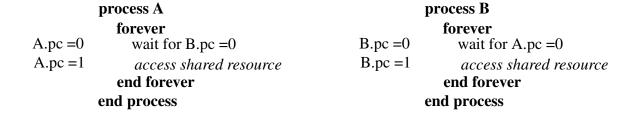

section. For this system, there are four states  $S=00,\ 01,\ 10,\ 11$ . Let us assume that the starting state is where both processes are in position 0, i.e., I=00. The transitions between states are specified by two rules, the next state will be the initial state unless the current state is already the initial state and the initial state can transit to either state 01 or 10. Thus  $R=(00,01),\ (00,10),(10,00),(01,00),(11,00)$ . Figure 1.2 gives a graphical representation of the Kripke structure of this system. The sequence 00,01,00,10,00,01...is an initialized path such that each process takes its turn to enter its critical section and use the shared resource. This system satisfies the property of safety since at most one process can be in its critical section at a time and nothing bad will happen.

**Figure 1.1** Model Checking Example

The properties of a system should be formulated as temporal logic expressions. Linear Temporal Logic (LTL) is a specification language that is used for describing sequences of transitions between states in a system. LTL is an extension of classical logic which inherits Boolean variables and Boolean operators (negation  $\sim$ , conjunction  $\wedge$ , disjunction  $\vee$  and implication  $\rightarrow$ ) from propositional logic. In addition, LTL has the following temporal

**Figure 1.2** A Kripke structure for two processes that preserve mutual exclusion [10]

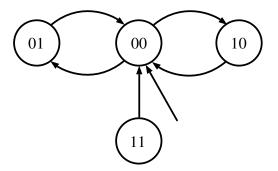

operators: **X** for next time, **F** for eventually or in future, **G** for globally and **U** for until. These operators describe properties of a path through a structure. The formula  $\mathbf{X}p$  requires that the property p holds in the next state of the path. Figure 1.3(a) and 1.3(b) show a path for which  $\mathbf{X}p$  does and does not hold respectively. In both cases each state is labeled with the properties that hold in it. The formula  $\mathbf{F}p$  holds along a path if p holds at some state on the path.  $\mathbf{F}p$  holds in both paths in Figure 1.3 since, in both cases, the first state already holds p. The formula  $\mathbf{G}p$  holds along a path if p holds in all the states of the path. Clearly, the path in Figure 1.3(a) satisfies  $\mathbf{G}p$  while the path in Figure 1.3(b) does not, since p does not hold in the second state. The formula  $p\mathbf{U}g$  holds if there is a state on the path where q holds and, at every preceding state on the path, p holds. Figure 1.4(a) and (b) show a path in which  $p\mathbf{U}g$  does and does not hold respectively.

1.1 Background 11

Figure 1.3 Next Operator

Figure 1.4 Until Operator

Going back to the example in Figure 1.1, the global operator G can be specified as  $G \sim (c_1, c_2)$ , where  $c_i$  labels the states where process i is in its critical section. Literally, this can be translated to English as follows: it is not possible for both  $c_1$  and  $c_2$  to be true at the same state. For the same example, the property which says that the first process will eventually reach its critical section can be formalized using the eventually operator as F. This property does not hold since the system may loop between the initial state OO and the state OO and never reach OO.

A Kripke structure M satisfies a temporal formula f, if and only if all the initialized paths of the structure satisfy the formula. Formally,  $M \models f$ , iff  $\pi \models d$  for all the initialized paths  $\pi$  of M. The relation  $\models$  is defined recursively as follows:

$$\pi \models p \quad iff \quad \pi \in L(\pi(0))$$

$$\pi \models \mathbf{X} f$$

if  $\pi_1 \models f$

$$\pi \models \mathbf{G} f$$

if  $f$   $\pi_i \models f$  for all  $i \geq 0$

$$\pi \models \mathbf{F} f \quad iff \quad \pi_i \models f \text{ for some } i \geq 0$$

$$\pi \models f\mathbf{U}q$$

iff  $\pi_i \models q$  for some  $i \geq 0$  and  $\pi_i \models f$  for all  $0 \leq j \leq i$

Using model checkers in verifying software systems can catch a range of logical and functional design errors, especially errors related to concurrency and multi-threading issues such as:

- Deadlock and starvation

- Race conditions

- Locking and priority problems

- Resource allocation errors

- Violation of system bounds (memory, stack ..)

- Redundancy

In order to use model checker on the verification process, two things are required from the user. The first is to learn how to build logic models i.e., how to extract a model from the

**13**

software code to verify. The second is to learn how to use abstraction to solve the problem of space explosion. The third is to learn how to formalize requirements in LTL. Examples of available model checkers are Blast [11] Chess [12] and SPIN [13].

#### 1.2 Motivations and Contributions

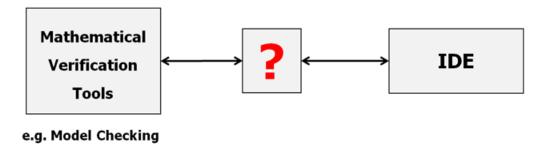

This research was motivated by the fact that a gap exists between model checking environments and conventional integrated development environments (IDEs). This gap prevents a simultaneous, efficient and effective benefit from both of these environments in the software development process. Figure 1.5 shows a schematic representation of this gap. On one hand, model checking is an efficient technique to ensure the correctness of a system before deployment. Using model checking requires building a model of the system in some formal language accepted by the MC in addition to writing the requirement specifications as temporal logic formulas. Building a model and writing temporal properties require knowledge in the model checker specification language and a strong mathematical background. These are obstacles for the majority of developers which in turn prevent model checking techniques from being widely used in the software development process. On the other hand, IDEs provide a debugging ability which enables the user to monitor and pause the execution of a system, set breakpoints and check the values in memory at runtime. Even though, debuggers are useful in single process applications, the nature of independence, random interaction and concurrency made the debugging of multi-process applications not a sufficient practice. Current debuggers are not able to provide a high-level picture of the

current state of a multi-process application, visualize the interactions between processes or link the implementation code to the original design.

Figure 1.5 Motivation

In this research, the need for a comprehensive engineering development environment to help software developers design, verify, implement and debug their systems without the need to learn all the mathematical details of formal verification was realized. To address this problem, a multiple phase approach for developing and verifying message passing systems is proposed. The target system is described using a two-level design approach: an abstract communication blocks level and a hierarchical state-behavioral specification level. A procedure to automatically generate formal models in a MC language is proposed. On the other hand, a new method based on choosing from a predetermined set of patterns in concurrent communication properties is proposed to facilitate collecting the essential specifications of the system.

Once the model and the properties of the system are generated, a model checker is used to

15

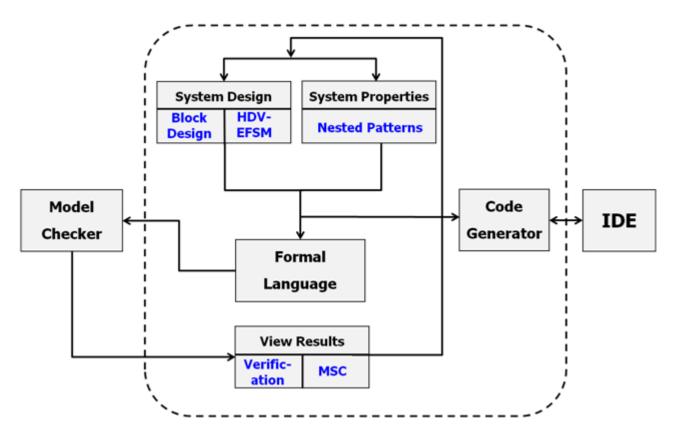

verify the correctness of the proposed system and ensure its compliance with specifications. In case of any inconsistencies found, the error source will be automatically localized using an algorithm that was developed for this purpose. A skeleton code of the system that includes the correct design specifications is generated in a general programming language i.e. Microsoft C#, Java, etc. Finally, the ability to debug the code using a conventional IDE while tracing the debugging process back to the original design was established. Figure 1.6 shows a schematic diagram of the proposed framework. A graphical software tool that supports the proposed framework is developed where SPIN MC is used as a verifier. The tool was used to develop and verify several case studies. The proposed framework and the developed software tool can be considered as a key solution for message passing systems design, verification and debugging.

The main contributions of this research can be summarized in the following points:

- A comprehensive framework to help software developers design, verify, implement

and debug their systems without the need to learn all the mathematical details of

formal verification.

- A multi-level graphical approach to design state-based message passing systems.

- A Hierarchical Designed-for-Verification extended finite state machine (HDV-EFSM)

to assist in designing complex systems with too many states.

- A set of hierarchical event-based and time-based patterns for concurrent properties

Figure 1.6 Framework Architecture

is proposed along with a mapping between these patterns to linear temporal logic (LTL).

- A tool environment to support the proposed approach where SPIN model checker was used as a verification engine along with a formal approach for translating the design system to PROMELA language (the input of SPIN) and to a general programming language e.g., C# or Java.

- A procedure to integrate an IDE to the developed tool during the debugging mode and switch between the graphical system design and its code implementation.

### 1.3 Dissertation Outline

The rest of this dissertation is organized as follows. A related literature review of software verification, model checking and debugging multi-process applications is given in Chapter 2. Chapter 3 presents in details the proposed approach to the design, verification and debugging of message passing communication systems. Chapter 4 introduces the software tool developed based on the proposed approach. The tool was implemented in Microsoft Visual C# and includes the design, verification, implementation and debug phases. Case studies will be presented in Chapter 5. Finally, the dissertation conclusions and future work are discussed in Chapter 6.

## Chapter 2

## **Review of Literature**

Different approaches have been proposed in literature to model, verify and debug software systems. This chapter presents a state-of-the-art survey of these topics.

### 2.1 Model Checking in Software Verification

Model checking is a technique used to verify the correctness of systems. Different approaches have been proposed in literature to model check software systems. These approaches differ mainly in the following three aspects: the system modeling technique, the formalization of the system properties and the used model checker engine. The following subsections discuss these classifications.

#### 2.1.1 Modeling System Specifications

Using a model checker to verify the correctness of a system requires building a model of the system in a formal language accepted by the model checker. Different approaches have been proposed to generate such a model. The following subsections discuss these approaches.

#### 2.1.1.1 Hand-Written Formal Modeling

This approach requires writing a formal model in the model checker specification language by hand [14–16]. This approach is error-prone and needs advanced knowledge of the MC language.

#### 2.1.1.2 Extraction from Code

This approach is based on extracting a verifiable model from the implementation of the system. This can be done either manually as in [17–20] or automatically as in [21, 22]. The manual extraction is time-consuming and needs advanced knowledge in the modeling languages. On the other hand, the automatic extraction is a more efficient technique, but has the problem of ensuring that the extracted abstract model is a correct mapping to the actual system. Most of these techniques use a level of abstraction based on the properties to be verified such that a model that captures only the details relevant to that property needs to be extracted. AX, stands for Automatic eXtractor [22], extracts models from C programs at an abstraction level defined by the user. Java PathFinder [21], on the other hand, translates

programs written in Java to models in PROMELA which can be verified using SPIN. Other examples can be found in [23,24].

#### 2.1.1.3 High-Level Modeling

This approach uses higher level diagram-based or text-based architecture specifications languages to describe the system then converts the result to the language of the model checker. Shi and He [25] use Petri-Net to describe the system behavior. Wright and Garlen [26] use Communication Sequential Processes (CSP). Even though, these languages are rich in describing the behavior of a concurrent system, using these languages requires advanced knowledge in the languages syntax and semantics. CHARMY [27], Bose [28] and vUML [29] used standard unified modeling language (UML) class and sequence diagrams to describe the specifications of a system. Byun [30] presented pattern-based development methodology to design such systems.

#### 2.1.1.4 Direct Code Model Checking

Other studies proposed model checkers that can work directly with the implementation code without requiring building a model. CMC [31], for example, is a model checker that works directly with unmodified C or C++ implementation without requiring any intermediate steps. Other tools are SLAM [32], JPF [33] and Verisoft [34].

#### 2.1.2 Systems Properties

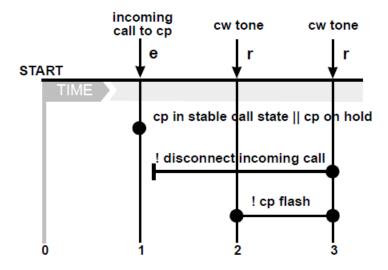

To verify the correctness of a system using model checking its properties should be expressed in temporal languages that are accepted by the MC such as Linear Temporal Language (LTL), Computational Tree Logic (CTL), CLT\* and mu-calculus. LTL is the most popular one which is used in CBabel [16], vUML [29] and CHARMY [27]. It is well known that writing and understanding properties in these languages is not an easy task since a strong background in these formal languages is required [35]. On the other hand, some studies exist in literature that proposed visual graphical notations to build these properties. Ramakrishna et al. [36] used Real-Time Future Interval Logic (RTFIL) diagrams. Damm and Hare [37] used Live Sequence Chart (LSC). Activity diagram is used by Bose [28]. Smith et al. [38] proposed Timeline Editor which is a visual specification formalism to place a series of events on a timeline. Figure 2.1 shows a time line for a call waiting requirements.

### 2.1.3 Model Checking Tools

Different model checkers are presented in literature and used to model check software systems. Examples of available model checkers are Blast [11] Chess [12] and SPIN [13]. In this review SPIN model checkers will be discussed. SPIN [13] is one of the most powerful model checkers that can be used to verify the correctness of concurrent systems and can check either hand-built or mechanically generated models. SPIN differs from other model checkers in offering a number of options to speed up the model checking process and save

Figure 2.1 Time line for a Call waiting requirements [38]

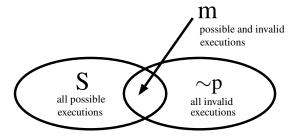

memory. Moreover, SPIN supports asynchronous modeling which is a main property of message passing systems. Let L(S) be a set of possible behavior of a system S and L(p) is a set of the valid or desirable behaviors of the system, model checking tries to prove that  $L(S) \subseteq L(p)$  i.e. everything possible is also valid. On the other hand, SPIN's verification engine tries to prove that  $L(S) \cap L(\sim p) = \phi$ . From Figure 2.2, if m is an empty set then S satisfies p, on the other hand if m is not an empty set then there are one or more counter examples that shows how S violates p.

Figure 2.2 SPIN MC Principle

23

Systems to be verified using SPIN are described in PROMELA (*Process Meta Language*), which supports the modeling of asynchronous distributed algorithms. Properties to be verified are expressed as Linear Temporal Logic (LTL) formulas. The major target of PROMELA is to be a system description language, not an implementation language. This language focuses in the modeling of process synchronization rather than mathematical computations and on the description of concurrent software systems rather than hardware circuits. The syntax of PROMELA is similar to C language but simplified; no pointers, no real datatypes such as float or real and no functions. No notion of time and clock exist in PROMELA.

In PROMELA, system components are modeled as processes which communicate via channels or through shared memory represented as global variables. Given a PROMELA model as input, SPIN generates a C program which conducts system verification by scanning the state space using a depth-first search (DFS) algorithm. Two types of properties can be checked in this stage, first; liveness properties such as non-progress cycles and eventual reception of messages, second; safety properties such as invalid end states, assertions, unspecified message receptions and absence of deadlock. Other specific properties can be checked by writing Linear Temporal Logic (LTL) formulas. SPIN converts an LTL expression to a never claim which is just another process that is executed in lock-step where a step from the never claim process executes after each step from the system. When an error is found, SPIN saves the trace of steps led to the invalid state.

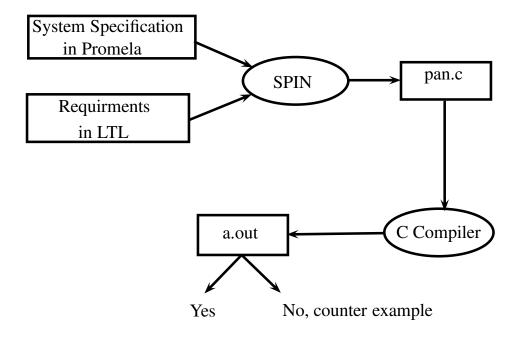

Figure 2.3 shows an overall architecture of SPIN. The inputs for SPIN are the specification model written in PROMELA and the properties to be verified written in LTL. SPIN will generate a verifier in C language called pan.c. This file should be complied and run.

In addition to model checking, SPIN can also operate as a simulator, following one possible execution path through the system and presenting the resulting execution trace to the user. All Spin software is written in ANSI standard C, and is portable across all versions of Unix, Linux, cygwin, Plan9, Inferno, Solaris, Mac, and Windows [13]. SPIN uses different approaches to cope with the state-space expulsion problem. These approaches include state-vector compression, bit-state hashing and partial order reduction.

Figure 2.3 SPIN Architecture

### 2.2 Debugging multi process applications

The problems of testing software were first mentioned few decades ago; since that time the complexity of software, the available memory and computer speed have been increased but software is basically still developed and tested in the same way. It is not possible to predictably produce reliable software.

Testing is a common method to validate software systems. The process starts by unit test which is the isolation of a single module or process in the system and verify its correctness. Once this test passed, a system integration test is done with a group of unit tests to build the whole system step-by-step. For sequential software systems, this method can be used even it is very time-consuming. In distributed software systems, concurrency problems may prevent proper execution of the system while making testing a hard task. Concurrency can cause race conditions, starvation, deadlock or delay problems.

Debugging is a process of discovering any bugs that may reside in a software system to make it behaves as expected. Debuggers are tools which help the programmer to monitor the execution of the system, pause it, set some breakpoints and check the values in memory or even change it at runtime. This technique uses stop-the-world [7] approach which may be useful for debugging single process applications but not sufficient for distributed applications. Several methods for helping the developers in debugging distributed software systems are proposed in literature. The known methods for debugging parallel applica-

tions can be divided into three main categories [39]: Automated verification of correctness, Comparative debugging and Interactive debugging.

The first category is based on automated correctness verification where a specific conditions of the system are checked while the application is executing. These conditions may include the correctness of calls of libraries that control the parallel execution and message exchange, the correct synchronization of processes and threads when shared data are used, and so on. This kind of debugging is done fully automated; the user is not involved in any stage of this process. Types of errors that can be detected using this debugging technique are: Parallelism specifications, deadlocks, incorrect parameters, incorrect access of shared data, use of uninitialized variables and other errors. Examples of debuggers of this type are: Intel Message Checker [40], MPI debugger in the DVM system [41], HP Visual Threads [42], and Intel Thread Checker [43].

The second category is called Comparative debuggers where a comparison of several runs of the same program is conducted by analyzing the traces collected in the course of the execution. Example of this type of debuggers is DVM system [44].

The third category is called Interactive debuggers where an interaction between the user and the debugger is allowed in any stage of the execution of the application by setting break points, step-by-step execution, testing and displaying values of particular variables. Examples of this type of debuggers are: TotalView [45], TDB [46], P2D2 [47], DDBG [48] and Allinea DDT [49].

27

This review will focus on the third type of debuggers, the Interactive debuggers for distributed programming. Allinea DDT is fully integrated with Microsoft Visual Studio which gives full control of parallel and multi-threaded applications as well as MPI applications. It is able to debug programs written in C, C++, C-Sharp, Python, FORTRAN and all .Net languages [49]. TotalView is a dynamic source code and memory debugger for C, C++ and FORTRAN applications written for Linux, UNIX and Mac OSX platforms. It can debug one or many processes and/or threads with complete control over program execution. TotalView does not support C-Sharp programs and Windows Operating System [45]. While both TotalView and DDT debuggers provide the developer with detailed information about the running processes in the application, no one provides a high-level picture of the current state of the application execution.

A debugger for flow graph based Dynamic Parallel Scheduled (DPS) parallelization framework is presented in [50]. The flow graph is used to provide both a high level and a detailed picture of the current state of the application execution. The parallel nature of DPS application is presented as an acyclic directed graph that specifies the dependences between messages and computations, where vertices represent serial computations and edges represent messages transfers. A later study by the same authors of [50] extends the concept of debugging DPS applications to debug MPI applications [51]. They designed a debugger that displays a message-passing graph of the execution of an MPI application which provides a higher level view of its communication patterns. This debugger provides the following features for the user: hiding/unhiding part of the processes, attaching regular

debugger to a process, changing the contents of a message at run time, reordering the messages to check for race conditions, displaying the contents of message queues at any point and setting conditional breakpoints.

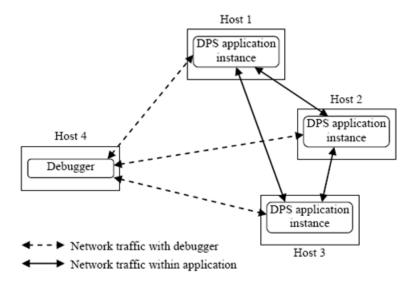

Figure 2.4 describes the system proposed in [51]. The Debugger is a standalone program which the parallel application should connect before startup. Each application has a hock with the debugger, which sends and receives from the debugger. The communications between the debugger and the processes are as follows:

- Each process will notify the debugger upon startup

- For every message a process sends, the process will first notify the debugger by sending the message contents and then waits for an acknowledgment

- When the debugger acknowledges the process, the process sends the message to the destination.

- When the process wants to do any operation i.e., processing the message, it will first

notify the debugger and waits for acknowledgment

Microsoft Visual Studio 2008 includes a debugger with multi-threaded debugging support. It provides a "Threads" window which lists all of the current threads in the system. From this window the developer can freeze or resume a thread, switch the current active thread, examine thread state and examine the state of local variables within the thread. This win-

**Figure 2.4** Parallel Debugger Architecture [51]

dow acts as the command center for examining and controlling the different threads in an application. Visual Studio 2010 supports the debugging of parallel applications by being able to present the state of the application anytime during the execution in the debugging mode across the different parallel execution units. It has task and thread windows to show the status of the processes and/or threads at any points in addition to stack view window which will show graphically the execution path of individual tasks [52].

HP proposed Causeway [53], a debugger for message-passing distributed systems. Their approach debugs the system by generating data traces that can be processed offline i.e. postmortem debugging. This way of debugging generates large amount of tracing data which required effective searching techniques to find a bug. In [54] a live distributed debugger is proposed for debugging stream applications. It allows the user to limit the amount of

tracing data depending in which part of the system is under investigation. The results are presented as visual graphical models. These debugging tools generate data traces while the system is running and help the user displays these data in different formats. These tools do not provide any help for the developer in reasoning about the cause and the solution of any residence bug.

# Chapter 3

# A Framework for Message Passing

# **Systems Development**

Verifying that a software system satisfies its required properties is important. This chapter presents in details an approach to formally verify and debug message passing communication systems using model checking.

# 3.1 Overview

As mentioned before, in order to verify the correctness of a system using model checking, a model of the system should be built in some language accepted by the model checker and the specifications to be verified should be given as temporal logic formulas. Building a model and writing temporal properties require advance knowledge in these languages

and strong mathematical background which are not always available among the majority of software developers. These obstacles prevent using model checking technique widely in the software development process [55].

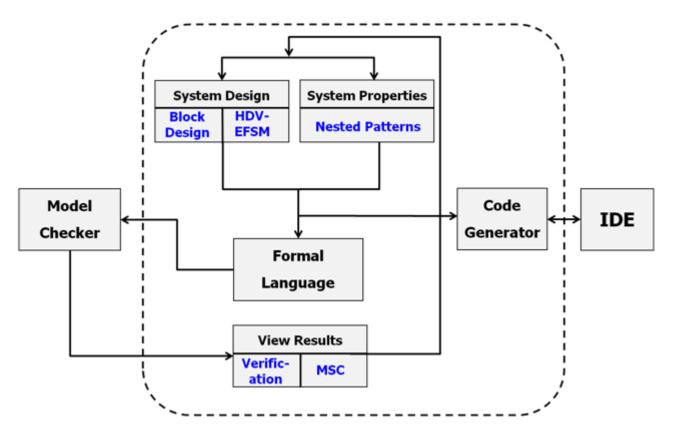

This research aims to facilitate using model checking in software verification by proposing a multi-phase approach. These phases are: system design phase, properties specification phase, verification phase, code generation phase and debugging phase. The message passing system is described using a two-level design approach: abstract communication blocks level and hierarchical state-behavioral specification level. A procedure to automatically generate formal models in a model checker language is proposed. A new method based on choosing from a pre-determined set of patterns in concurrent communication properties is proposed to facilitate collecting the essential specifications of the system. Once the model and the properties of the system are generated, a model checker is used to verify the correctness of the proposed system and ensure its compliance with specifications. In case of any inconsistencies found, the error source will be automatically localized using an algorithm that was developed for this purpose. A skeleton code of the system that includes the correct design specifications is generated in a general programming language i.e. Microsoft C#, Java, etc. Moreover, the ability to debug the code using a conventional IDE while tracing the debugging process back to the original design was established. Figure 3.1 illustrates the proposed framework. The following subsections describe these phases in details.

Figure 3.1 Framework Summary

# 3.2 System Design

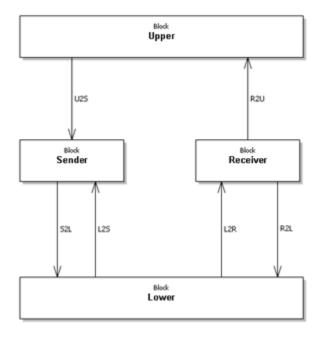

A formalism to model the specifications of a Message Passing System (MPS) structure and interactions is required. A two-level design approach is proposed where the design of the system is decomposed into high-level block description and state-behavioral description. An MPS-Block Diagram was proposed to provide a high-level abstract architecture of the system in the form of blocks and communication channels between these blocks. In the state-behavioral description, the internal behavior of the high-level blocks is described using a modified finite state machine diagram. To easily explain the proposed approach, a

simple example will be discussed and used as a sample use case through this chapter.

## **Example: Simple Reliable Transfer Protocol**