# University of New Hampshire University of New Hampshire Scholars' Repository

#### **Doctoral Dissertations**

Student Scholarship

Winter 1993

# A massively parallel SIMD processor for neural network and machine vision applications

Michael A. Glover University of New Hampshire, Durham

Follow this and additional works at: https://scholars.unh.edu/dissertation

#### **Recommended** Citation

Glover, Michael A., "A massively parallel SIMD processor for neural network and machine vision applications" (1993). *Doctoral Dissertations*. 1853. https://scholars.unh.edu/dissertation/1853

This Dissertation is brought to you for free and open access by the Student Scholarship at University of New Hampshire Scholars' Repository. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of University of New Hampshire Scholars' Repository. For more information, please contact nicole.hentz@unh.edu.

# **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 313/761-4700 800/521-0600

.\*

· · · · ·

# A MASSIVELY PARALLEL SIMD PROCESSOR FOR NEURAL NETWORK AND MACHINE VISION APPLICATIONS

^

$\mathbf{B}\mathbf{Y}$

Michael A. Glover BSEE University of Texas at Austin, 1980 MSE University of Texas at Austin, 1984

#### DISSERTATION

Submitted to the University of New Hampshire

in Partial Fulfillment of

the Requirements for the Degree of

Doctor of Philosophy

in

Engineering

December, 1993

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

UMI Number: 9531250

٨

UMI Microform 9531250 Copyright 1995, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

# UMI

300 North Zeeb Road Ann Arbor, MI 48103

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

This dissertation has been examined and approved.

Dissertation Director, W. Thomas Miller III Professor of Electrical Engineering

Michael J. Carter, Associate Professor of Electrical Engineering

Filson H. Glanz, Professor of Electrical/Engineering

William Wren Stine, Associate Professor of Psychology

OR See

Lee L. Zia, Associate Professor of Mathematics

11/10/93

Date

DEDICATION

^

To Hannah, Caitlin, and Carol

#### ACKNOWLEDGEMENTS

~

I would like to thank Dr. T. Miller, Dr. M. Carter, Dr. F. Glanz, Dr. L. Zia, and Dr. W. Stine for their help and support. I would like to thank D. C. Current for his sponsorship of this project. I would like to thank Paul Panish, Wayne Sanborn, and Dave Buck for the work they did on the prototype. I would finally like to thank my family, Hannah, Caitlin, and Carol, for their patience and support.

# TABLE OF CONTENTS

~

| DEDIC   | ATION      | Niii                                    |

|---------|------------|-----------------------------------------|

| ACKNO   | OWLE       | DGEMENTSiv                              |

| LIST O  | F FIGU     | URES xii                                |

| LIST O  | F TAB      | sLES xiii                               |

| ABSTR   | ACT .      | xiv                                     |

| Chapter | 1          |                                         |

| INTRO   | DUCT       | 'ION1                                   |

| Chapter | 2          |                                         |

| REVIE   | <b>WOF</b> | PAST WORK5                              |

| 2.1     | Com        | putational Tasks in Neural Networks5    |

| 2.2     |            | alling and Computation8                 |

| 2.3     | Sour       | ces of Parallelism in Neural Networks10 |

| 2.4     | Meas       | sures of Neural Network Performance12   |

|         | 2.4.1      | External Measures12                     |

|         | 2.4.2      | Internal Measures13                     |

| 2.5     | Exan       | nple Neural Networks14                  |

| 2       | 2.5.1      | Nearest Neighbor                        |

|         | 2.5.2      | Content Addressable Memory15            |

|         | 2.5.3      | Local Basis Functions15                 |

|         | 2.5.4      | Kohonen Network                         |

| -       | 2.5.5      | ART16                                   |

|         | 2.5.6      | CMAC17                                  |

| 2       | 2.5.7      | Multilayered Perceptrons                |

| 2.6 | Neur   | al Network Hardware                              | 18 |

|-----|--------|--------------------------------------------------|----|

|     | 2.6.1  | Traditional Computers                            | 18 |

|     | 2.6.2  | DSP Microprocessors                              | 19 |

|     | 2.6.3  | MIMD Parallel Computers                          | 19 |

|     | 2.6.4  | Vector Supercomputers                            | 20 |

|     | 2.6.5  | Massively Parallel SIMD Supercomputers           | 20 |

|     | 2.6.6  | Siemens SYNAPSE-1 Systolic Array Using MA16 Chip | 21 |

|     | 2.6.7  | CMAC Board                                       | 21 |

|     | 2.6.8  | CNAPS 1064 Chip                                  | 22 |

|     | 2.6.9  | Intel 80170 ETANN Chip                           | 22 |

|     | 2.6.10 | Intel Ni1000 Chip                                | 23 |

|     | 2.6.11 | Hitachi 8 Megabit Chip                           | 23 |

|     | 2.6.12 | Analog Radial Basis Function Chip                | 24 |

|     | 2.6.13 | ATT Bell Labs ANNA Chip                          | 24 |

|     | 2.6.14 | ATT Bell Labs NET32K Chip                        | 25 |

|     | 2.6.15 | Neocognitron CCD Chip                            | 25 |

|     | 2.6.16 | Optical Network                                  | 26 |

| 2.7 | Com    | parison of Thesis to Previous Techniques         | 26 |

,.

# Chapter 3

| HARD | WARE  | 3                            | 27 |

|------|-------|------------------------------|----|

| 3.1  | Cont  | troller                      | 29 |

|      | 3.1.1 | Host Interface Port          | 29 |

|      | 3.1.2 | Controller CPU               | 29 |

|      | 3.1.3 | Internal Data Memory         | 30 |

|      | 3.1.4 | Internal Program Memory      | 30 |

|      | 3.1.5 | External Program Memory      | 30 |

|      | 3.1.6 | Timer                        | 31 |

|      | 3.1.7 | Controller Bus               | 31 |

| 3.2  | PE A  | Array                        | 33 |

|      |       | PE Page                      |    |

|      |       | 2.1.1. DRAM Memory Array     |    |

|      |       | 2.1.2. A, B, and M Registers |    |

|      |       |                              |    |

| 3.       | 2.1.3. A and B Tap Pointers | 35 |

|----------|-----------------------------|----|

| 3.2.2    | PE Instruction Register     | 37 |

| 3.2.3    | PE Array Instruction Set    |    |

| 3.3 Swi  | tch                         | 42 |

| 3.3.1    | Switch Connection to Pages  | 43 |

| 3.3.2    | Switch Slice                | 44 |

| 3.3.3    | Switch Setup                | 45 |

| 3.3.4    | Switch Operation            | 46 |

| 3.3.5    | Shifting Data in a Page     | 47 |

| 3.4 Inpi | ıt-Output Port              | 47 |

,

# Chapter 4

| LOGICAL M | 1ACHINE                                        | 49 |

|-----------|------------------------------------------------|----|

| 4.1 Lo    | gical Machine                                  | 50 |

| 4.1.1     | Logical PE                                     | 51 |

| 4.1.2     | Logical Switch                                 | 54 |

| 4.2 Dat   | a Organization                                 | 54 |

| 4.2.1     | An Integer is Formed from Bits                 | 54 |

| 4.2.2     | A Vector is Formed from Integers               |    |

| 4.2.3     | Vectors may be Longer than the Machine is Wide | 58 |

| 4.2.4     | Vectors and Virtual PEs                        | 61 |

| 4.3 PE    | Programming                                    | 61 |

| 4.3.1     | PE Instruction Set                             | 62 |

| 4.3.2     | The Instruction Set is Functionally Complete   | 63 |

| 4.3.3     | PE Programming Techniques                      | 63 |

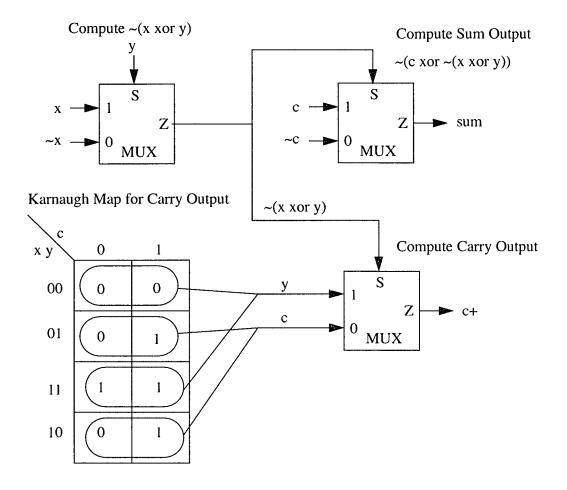

| 4.3.4     | A Program to Add Two Bits                      | 67 |

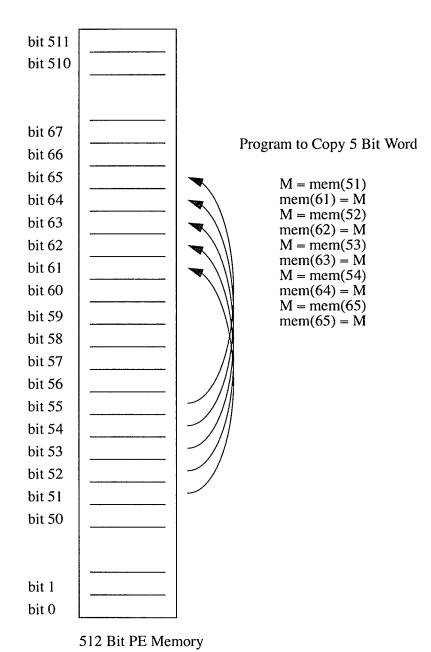

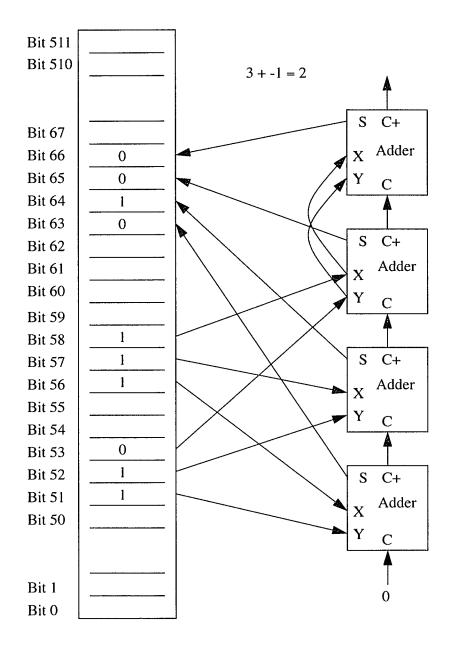

| 4.3.5     | Bit Serial Arithmetic                          | 68 |

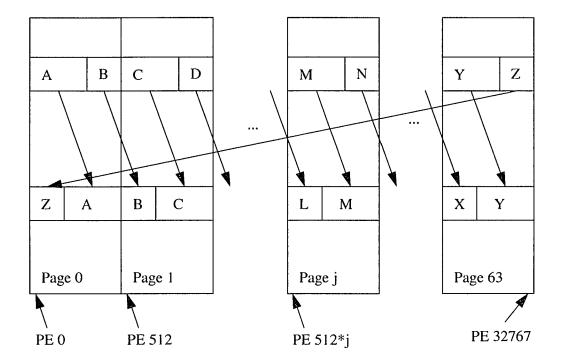

| 4.3.6     | Align and the Switch                           | 71 |

| 4.4 Vec   | ctor Instruction Set                           | 73 |

| 4.4.1     | Read a Word from a Vector                      | 75 |

| 4.4.2     | Write a Word to a Vector                       | 75 |

| 4.4.3     | Write a Constant to a Vector                   | 76 |

| 4.4.4     | Copy a Vector                                  | 76 |

| 4.4.5  | Arithmetic Shift of a Vector77                         |

|--------|--------------------------------------------------------|

| 4.4.6  | Bitwise NOT of a Vector                                |

| 4.4.7  | Bitwise OR of a Vector and a Vector                    |

| 4.4.8  | Bitwise AND of a Vector and a Vector                   |

| 4.4.9  | Bitwise XOR of a Vector and a Vector                   |

| 4.4.10 | Bitwise OR of a Vector with a Scalar                   |

| 4.4.11 | Bitwise AND of a Vector with a Scalar                  |

| 4.4.12 | Bitwise XOR of a Vector with a Scalar                  |

| 4.4.13 | Logical NOT of a Vector                                |

| 4.4.14 | Negate a Vector                                        |

| 4.4.15 | Absolute Value of a Vector                             |

| 4.4.16 | Add a Vector to a Vector                               |

| 4.4.17 | Subtract a Vector from a Vector                        |

| 4.4.18 | Add a Scalar to a Vector                               |

| 4.4.19 | Subtract a Scalar from a Vector                        |

| 4.4.20 | Subtract a Vector from a Scalar                        |

| 4.4.21 | Multiply a Vector by a Vector                          |

| 4.4.22 | Multiply a Vector by a Scalar90                        |

| 4.4.23 | Subroutine to Divide                                   |

| 4.4.24 | Divide a Vector by a Vector                            |

| 4.4.25 | Divide a Vector by a Scalar                            |

| 4.4.26 | Divide a Scalar by a Vector                            |

| 4.4.27 | Modulo a Vector by a Vector94                          |

| 4.4.28 | Modulo a Vector by a Scalar94                          |

| 4.4.29 | Modulo a Scalar by a Vector95                          |

| 4.4.30 | Compare if a Vector is EQUAL to a Vector95             |

| 4.4.31 | Compare if a Vector is NOT EQUAL to a Vector96         |

| 4.4.32 | Compare if a Vector is GREATER OR EQUAL to a Vector97  |

| 4.4.33 | Compare if a Vector is GREATER than a Vector           |

| 4.4.34 | Compare if a Vector is EQUAL to a Scalar98             |

| 4.4.35 | Compare if a Vector is NOT EQUAL to a Scalar99         |

| 4.4.36 | Compare if a Vector is GREATER than a Scalar100        |

| 4.4.37 | Compare if a Vector is GREATER OR EQUAL to a Scalar101 |

| 4.4.38 | Compare if a Vector is LESS than a Scalar102           |

•

^

| 4.4.39    | Compare if a Vector is LESS OR EQUAL to a Scalar | 103 |

|-----------|--------------------------------------------------|-----|

| 4.4.40 \$ | Select Elements from Two Vectors                 | 104 |

| 4.4.41    | Align a Vector                                   | 105 |

| 4.4.42 \$ | Subroutine to Test All Processors                | 106 |

| 4.4.43    | Global OR                                        | 107 |

| 4.4.44    | Global AND                                       | 108 |

| 4.4.45    | Global MAX                                       | 109 |

| 4.4.46    | Global MIN                                       | 110 |

| 4.4.47    | Global SUM                                       | 111 |

| 4.4.48 I  | First Nonzero Element in a Vector                | 112 |

| 4.4.49    | Create Vector with Element Indices               | 113 |

^

# Chapter 5

| C++ F | PROGRA | AMMING ENVIRONMENT              | 115 |

|-------|--------|---------------------------------|-----|

| 5.1   | I C++  | Class Background                | 115 |

| 5.2   | 2 MM   | _VECTOR Class                   | 116 |

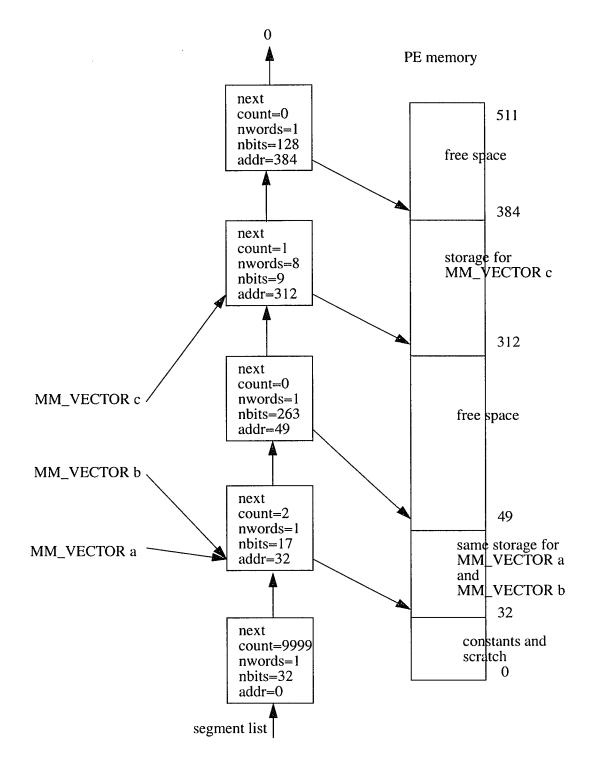

| 5.3   | 3 PE N | Леmory Heap                     | 117 |

| 5.4   | 4 MM_  | _VECTOR Implementation          | 118 |

| 5.5   | 5 Heap | o Garbage Collection            | 121 |

| 5.6   | 5 Over | rloaded Operators and Functions | 121 |

|       | 5.6.1  | constructor                     | 122 |

|       | 5.6.2  | function helper constructor     | 122 |

|       | 5.6.3  | copy constructor                | 122 |

|       | 5.6.4  | destructor                      | 122 |

|       | 5.6.5  | operator[]                      | 123 |

|       | 5.6.6  | set the value of an element     | 123 |

|       | 5.6.7  | operator=                       | 123 |

|       | 5.6.8  | operator+                       | 123 |

|       | 5.6.9  | operator                        | 124 |

|       | 5.6.10 | operator- negate                | 124 |

|       | 5.6.11 | operatorl                       | 124 |

|       | 5.6.12 | operator&                       | 125 |

|       | 5.6.13 | operator^                       | 125 |

|       |        |                                 |     |

| 5.6.14    | operator<<125                     |

|-----------|-----------------------------------|

| 5.6.15    | operator>>126                     |

| 5.6.16    | operator*126                      |

| 5.6.17    | operator/126                      |

| 5.6.18    | operator%126                      |

| 5.6.19    | operator==127                     |

| 5.6.20    | operator!=127                     |

| 5.6.21    | operator<=127                     |

| 5.6.22    | operator<128                      |

| 5.6.23    | operator>=128                     |

| 5.6.24    | operator>128                      |

| 5.6.25    | align function128                 |

| 5.6.26    | select function129                |

| 5.6.27    | truncate function                 |

| 5.6.28    | operator~129                      |

| 5.6.29    | operator!130                      |

| 5.6.30    | abs function130                   |

| 5.6.31    | index function130                 |

| 5.6.32    | sum function130                   |

| 5.6.33    | or function131                    |

| 5.6.34    | and function131                   |

| 5.6.35    | minimum function131               |

| 5.6.36    | maximum function131               |

| 5.6.37    | first function131                 |

| 5.7 C++   | Programming Considerations        |

| Chapter 6 |                                   |

| RESULTS   |                                   |

| 6.1 Vect  | or Instruction Set Performance138 |

| 6.2 Perfe | prmance and the Host144           |

,

| 6.3 | Com   | parison to Other SIMD Machines       | 144 |

|-----|-------|--------------------------------------|-----|

| 6.4 | Mille | er-Scalera Neural Network Benchmarks | 149 |

|     | 6.4.1 | Nearest Neighbor Search              | 150 |

| 6.4.2    | Radial Basis Function Neural Network    | 151 |

|----------|-----------------------------------------|-----|

| 6.4.3    | Kohonen Neural Network                  | 151 |

| 6.4.4    | Multilayer Perceptron                   | 152 |

| 6.4.5    | Discussion of Miller-Scalera Benchmarks | 153 |

| 6.5 Disc | sussion of Performance Limitations      | 153 |

| 6.5.1    | SIMD Instruction Set Inefficiencies     | 154 |

| 6.5.2    | Switch Inefficiencies                   | 154 |

| 6.5.3    | Global Operation Inefficiencies         | 155 |

| 6.5.4    | Controller Inefficiencies               | 155 |

| 6.5.5    | Host Inefficiencies                     | 156 |

| 6.5.6    | System Memory                           | 156 |

| 6.5.7    | Data Input-Output Bottleneck            | 157 |

^

# Chapter 7

| CONCLU | JSION                              |  |

|--------|------------------------------------|--|

| 7.1    | The MM32k SIMD Processor Array     |  |

| 7.2    | Future Work                        |  |

| 7.     | 2.1 MM32k Improvements             |  |

| 7.     | 2.2 Neural Network Implementations |  |

| REFERE | NCES                               |  |

# LIST OF FIGURES

^

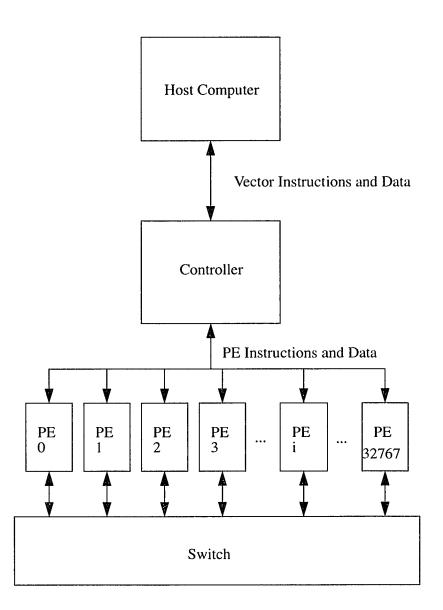

| Figure 3.1 MM32k Block Diagram                     |     |

|----------------------------------------------------|-----|

| Figure 3.2 Controller                              |     |

| Figure 3.3 PE Array                                |     |

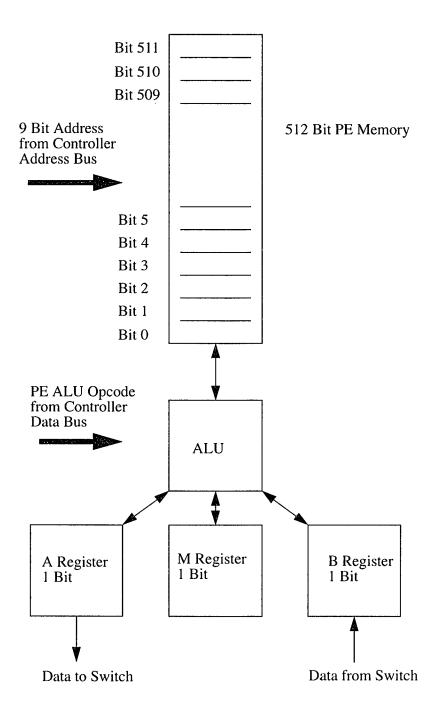

| Figure 3.4 PE Page                                 |     |

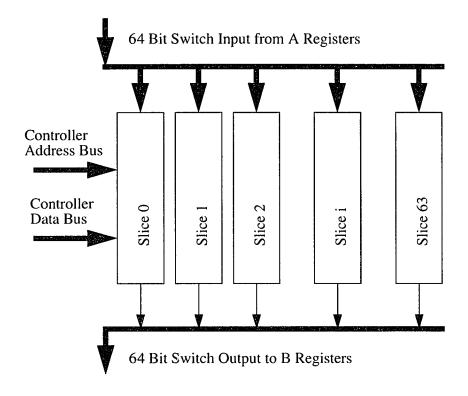

| Figure 3.5 Crossbar Switch                         | 43  |

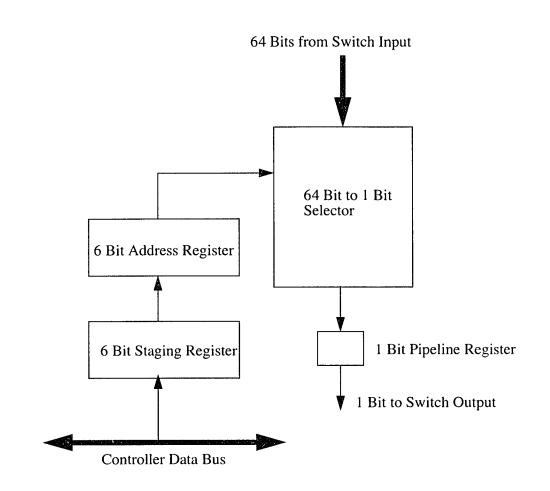

| Figure 3.6 Crossbar Switch Slice                   | 45  |

| Figure 4.1 Logical Machine                         | 50  |

| Figure 4.2 Processing Element                      | 53  |

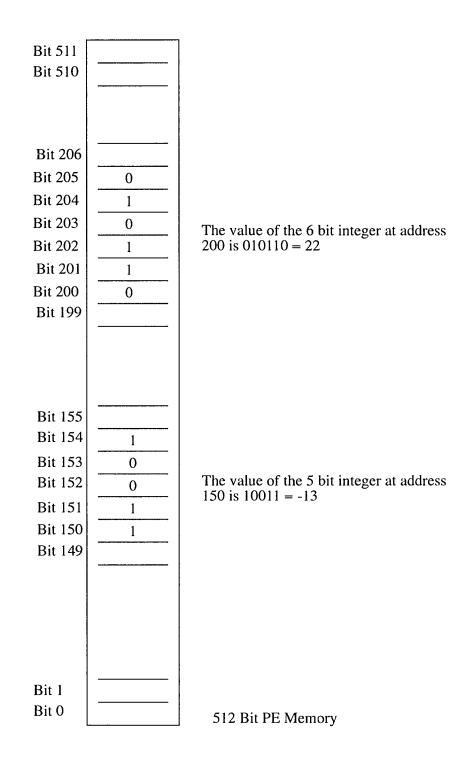

| Figure 4.3 Data Format in PE Memory                | 56  |

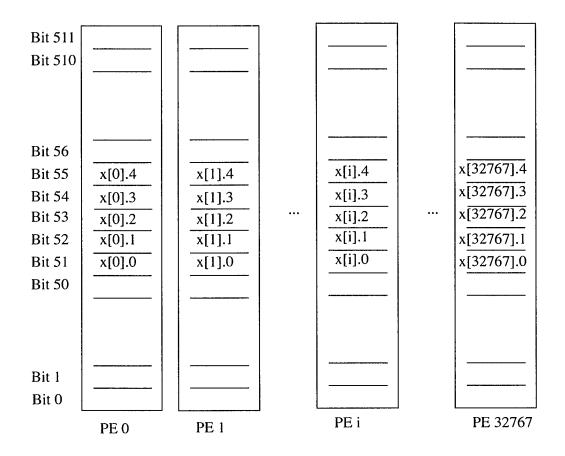

| Figure 4.4 Vector Format Across PEs                | 58  |

| Figure 4.5 Vector Longer than 32768                | 60  |

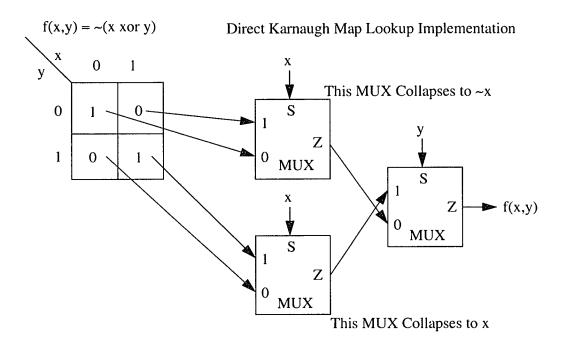

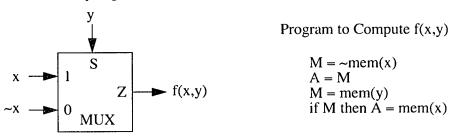

| Figure 4.6 PE Program to Compute ~(x XOR y)        | 65  |

| Figure 4.7 PE Program to Implement a One Bit Adder | 67  |

| Figure 4.8 PE Program to Copy a Word               | 69  |

| Figure 4.9 PE Program to Add Two Three Bit Numbers | 71  |

| Figure 4.10 Align Operation                        | 73  |

| Figure 5.1 MM_VECTOR Heap                          | 120 |

## LIST OF TABLES

~

| Table 6.1 MM32k Vector Performance          | 139 |

|---------------------------------------------|-----|

| Table 6.2 Performance Across Hosts          | 144 |

| Table 6.3 Other SIMD Computers              | 148 |

| Table 6.4 Nearest Neighbor Performance      | 150 |

| Table 6.5 Radial Basis Function Performance | 151 |

| Table 6.6 Kohonen Performance               | 152 |

| Table 6.7 Multilayer Perceptron Performance | 153 |

.

## ABSTRACT

~

# A MASSIVELY PARALLEL SIMD PROCESSOR FOR NEURAL NETWORK AND MACHINE VISION APPLICATIONS

by

Michael A. Glover

University of New Hampshire, December, 1993

This thesis describes the MM32k, a massively parallel SIMD computer which is easy to program, high in performance, low in cost and effective for implementing highly parallel neural network architectures. The MM32k has 32768 bit serial processing elements, each of which has 512 bits of memory, and all of which are interconnected by a switching network. The entire system resides on a single PC-AT compatible card. It is programmed from the host computer using a C++ language class library which supports variable precision vector arithmetic. The MM32k also supports direct video input and output for machine vision applications.

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

## Chapter 1

#### **INTRODUCTION**

Biological neural networks achieve complex behavior from large numbers of simple neurons. Artificial neural networks take their inspiration from biological networks in that they also can achieve complex behavior from large numbers of simple operations. However, for some artificial neural network architectures, the number of simple operations is so large that the network cannot be implemented in an acceptable amount of time or for an acceptable cost. This thesis describes a massively parallel computer called the MM32k which can implement highly parallel artificial neural networks much faster and more cost effectively than is possible on existing computers.

Local basis function networks are a class of neural networks which are easy to train and have good generalization properties. Included in this class are Kohonen networks, ART networks, nearest neighbor algorithms, content addressable memory, and radial basis function networks. Networks of this class have a large number of neurons, inside each which is stored an exemplar from the training set. To perform recall, all neurons are searched against the input vector and the one with the best match or a weighted sum of those matching is returned as the network response. As the capacity and accuracy of the network goes up, so does the number of neurons and therefore the amount of time required to perform the search, making the network impractical for many time sensitive applications.

A design goal of the MM32k was to speed up the implementation of local basis function type networks by performing the search and sum operations in parallel. The MM32k processor is a <u>single instruction multiple data</u> (SIMD) parallel processor with 32768 processing elements. Each processing element has 512 bits of memory and a one bit wide <u>arithmetic and logic unit</u> (ALU). All are linked together by an interconnection net-

work. The basic advantage of the MM32k is that one processor can be assigned to each neuron in the network and all neurons can operate in parallel. Together, the processing elements can perform billions of operations per second on suitable neural network algorithms.

In the past, special purpose neural network hardware has been designed to implement neural networks and has achieved very high performance on the particular network for which it was designed. Frequently though, the flexibility of the hardware was compromised in favor of performance and the machine was unable to perform different but related algorithms. A second design goal of the MM32k was to obtain as much performance as possible while retaining as much flexibility as possible.

If the flexibility of the MM32k is to be fully exploited, then there must be effective tools for programming it. A third design goal was to implement an effective programming language. A good programming language should expose the underlying architecture of the machine to the programmer without requiring undue worry about the hardware details. A good language should structure the programmer's thinking by facilitating the natural expression of the problem in a way that can be efficiently executed by the machine. The MM32k solves this problem using a C++ class library which abstracts the MM32k as a machine for doing computation on long vectors of integers.

The MM32k is hosted by a standard PC-AT computer and is interfaced via the standard bus. The C++ class library is built on top of commercial C++ programming tools for the PC, rather than being a MM32k specific cross compiler. The C++ program runs on the host and controls the MM32k via the ISA bus. This means that ordinary C++ language programming can be mixed with MM32k programming and that all the familiar host computer programming tools including compilers, linkers, editors, optimizers, and debuggers can be taken advantage of to program the MM32k.

The general organization of this thesis is as follows:

Chapter 2 discusses computational issues in implementing neural networks including generic computational tasks, signalling, sources of parallelism, and performance measures. It also describes neural networks which are appropriate for implementation on the MM32k. It describes existing hardware on which neural networks have been implemented and shows how the MM32k is different.

Chapter 3 describes the MM32k hardware. It describes the component parts of the MM32k computer, which include the controller, the processing element array, and the switch, and describes the functions they perform. It covers the basic SIMD processing element instruction set which is visible to the MM32k controller.

Chapter 4 describes the MM32k firmware. It describes how the MM32k hardware is viewed to form a logical machine with 32768 processing elements and how that machine is programmed to perform vector arithmetic. It describes the vector instruction set which is visible to the host computer.

Chapter 5 describes the MM32k C++ class library. It describes how the MM32k can be abstracted by a class called MM\_VECTOR which represents a vector of integers and how it can be programmed by manipulating variables of that class from a C++ program running on the host. It describes the overloaded C++ arithmetic operators available to the MM\_VECTOR class.

Chapter 6 discusses the performance of the MM32k. The performance of the MM32k executing individual C++ class library operators is measured. The MM32k is compared in a general way to other SIMD parallel computers and its performance on some neural network algorithms is compared to traditional serial computers. Performance limitations and improvements are also discussed.

Chapter 7 is a summary of the thesis. It reviews the MM32k and affirms that the machine is effective at implementing neural networks. It discusses other applications at which the MM32k could be effective and identifies future work.

.•

#### Chapter 2

#### **REVIEW OF PAST WORK**

The purpose of this chapter is to review existing hardware implementations of neural networks. To do this, it first reviews the computational tasks common to most neural networks. It then reviews signalling and computation techniques used in implementing neural networks. It then lists sources of parallelism which an implementation might exploit. It lists measures of neural network performance to provide a framework for the evaluation of an implementation. It then lists example neural networks at which the MM32k would be effective at implementing. It then describes existing neural network hardware. Finally, it shows how the processor described in this thesis differs from existing implementations. When this chapter refers to a neural network, it is referring to an artificial neural network, unless otherwise noted.

## 2.1 Computational Tasks in Neural Networks

This section lists computational tasks which are common to neural networks. It does not distinguish between tasks performed during recall and during learning and is also not intended to a cover all neural networks, because new networks and variations on old networks are being created all the time. Rather, it is intended to give a broad overview of the types of computations which a general purpose neural network engine should be able to perform. The computational requirements of some are put into a uniform framework by Kung [1989].

Neural networks must have some form of memory in which to store weights. Each neuron has its own set of weights and collectively they form the internal representation of the function which the network has learned. The more weights, the more the network can

potentially learn. Weights have been stored in digital <u>static random access memory</u> (SRAM) cells [Hammerstrom, 1990], digital <u>dynamic random access memory</u> (DRAM) cells [Watanabe, 1993], analog <u>charge coupled device</u> (CCD) cells [Chuang, 1990], <u>electrically erasable programmable read only memory</u> (EEPROM) cells [Intel, 1991], photographic film [Lu, 1991], and chemicals in biological synapses [Llinas, 1988].

Neural networks must have some way in which the weights can be set. If the weights can be adjusted while the network is running, then the network can potentially be trained on line, instead of off line. Some networks require a probabilistic weight update [Melton, 1992].

Data must be moved around between the network input, the neurons, and the network output to implement the connections in a neural network. Either individual physical paths can be constructed for each connection, or fewer paths can be shared over time. Depending upon the topology, the resources devoted to connections can dominate the system. Connections have been implemented electrically with wires, optically with holograms and lenses [Krishnamoorthy, 1992], and biologically with axons and dendrites [Llinas, 1988].

The basic arithmetic operation of the neurons in many networks is to compute a dot product between an input vector and a weight vector. A dot product requires many multiply and add operations. Addition operations are usually relatively fast and inexpensive to implement, but multiplication can be slow, more expensive, or more difficult to implement, depending upon the technology used. In some networks, this dot product will be normalized, which requires a division. The dot product has been computed using digital arithmetic, using pulse modulation [Hamilton, 1992], by using analog transistor circuits [Intel 1991], and by using a photographic film and light [Lu, 1991].

The basic operation of the neurons in some networks is the computation of the dis-

tance between an input vector and a weight vector. This distance can be a euclidean distance, a city block distance, or some approximation. The distance differences may be weighted. Depending upon how it is implemented, the metric can require some combination of addition, subtraction, absolute value, comparison, multiplication, and square root. Addition and subtraction are relatively easy to implement, but absolute value and comparison are more difficult and multiplication and square root are more difficult and expensive still. The distance metric has been computed using digital computer arithmetic and using analog transistor circuits [Anderson, 1992].

The dot product or distance metric of each neuron is fed into a nonlinear activation function, which determines the output of the neuron. The simplest form of an activation function is a unit step function, where the output is one if the input is greater than a threshold value and zero otherwise. A variation on this is to allow the threshold to be gradual so that the output is one or zero for an input which is much greater than or less than the threshold value, respectively, and makes a gradual transition in between. The derivative of the output would then exist everywhere. This function has been computed by digital computer arithmetic, by lookup tables [Hammerstrom, 1990], and by analog transistor circuits [Intel, 1991].

In some networks, the sum of all neuron outputs must be formed and in others, the neuron with the maximum output must be selected and the outputs of the other neurons suppressed. These operations can be difficult because they are global and require some form of communication between all neurons in a particular layer. This operation can take time which is linear, logarithmic, or fixed relative to the number of neurons in a layer, depending upon implementation. Global operations have been computed using digital and analog [Lazzaro, 1988], electrical circuitry.

In some networks, a boolean predicate will be evaluated at each neuron and the neu-

ron will subsequently be active or inactive depending upon the outcome. The predicate may be an arbitrary function of the weights and the inputs and may use arbitrary arithmetic operators and functions.

#### 2.2 Signalling and Computation

All networks must move and compute with the data using some signalling scheme. The best scheme for a particular network depends upon whether the information is continuous or discrete, upon how it is stored, upon how it is sent, and upon how it is used in computation. Many systems are hybrid and combine different schemes to take advantage of the strengths of both.

Neural networks have been implemented using digital floating point arithmetic. An advantage is that the implementor has a large amount of dynamic range and accuracy. Networks using it can be implemented simply using common computers and <u>digital signal processing</u> (DSP) microprocessors. Digital signals are relatively immune to noise. One disadvantage is that addition and particularly multiplication use a lot of silicon resources and another is that it uses a lot of memory for data which frequently has only five significant bits of precision.

Neural networks have been implemented using digital fixed point arithmetic. An advantage is that it requires less silicon to implement than digital floating point and is usually faster. The disadvantages are that the implementor must be concerned with dynamic range and that it can waste memory.

Digital floating point and digital fixed point have been implemented in a bit serial fashion [Hwang, 1984]. In bit serial implementations, the data paths of the memory, ALU, and interconnections are all one bit wide and computations are performed one bit at a time. The advantage is that only as many bits need be stored and processed as are needed by the problem. The disadvantage is that the parallelism of bits across a word is lost.

The amplitude of a signal can be encoded as the duty cycle or frequency of a digital pulse stream [Hamilton, 1992]. The advantages are that data paths can be one bit wide and can be implemented using digital devices. Multiplication can be done with an AND gate. The signals can be converted to an analog voltage using an integrator. The disadvantage is that a signal cannot be directly stored in a memory, limiting the flexibility of a system. Another disadvantage is that the accuracy of the scheme is limited and it is susceptible to noise. The same input presented twice may yield two different outputs.

The advantage of analog electrical circuits is that a given amount of silicon has a higher information processing bandwidth than with digital circuits [Intel, 1991]. Multiplication and addition can be done cheaply. However, accuracy is limited to around six bits and some nonlinear functions are difficult to achieve. Analog electrical circuits can be susceptible to noise and so the behavior of the network may not be deterministic, which complicates testing and debugging. It is sometimes difficult to implement some functions in the presence of semiconductor fabrication process variation. An analog signal can be stored in a capacitor, but will decay if not refreshed periodically, limiting the general usefulness of this technique. Analog weights are not easily updated and the network must usually be trained off line.

All of the digital and analog techniques listed above may in theory be implemented optically. Optical networks can potentially move a large amount of data very quickly in parallel. They can also potentially take advantage of free space interconnect using lenses and holograms [Krishnamoorthy, 1992]. Addition can be performed by integrating the photons which fall on a sensor. Multiplication can be performed by directing a beam of light through an attenuator such as a piece of film or a liquid crystal light modulator [Lu, 1991]. Correlation, which is equivalent to a dot product, can be performed using only lenses and an attenuator. The disadvantage is that the technology for manipulating optical signals is very

poorly developed compared to that for electrical signals. Many optical neural networks use optics as a large fast correlation engine.

Biological signalling is the signalling technology of living organisms. Human beings and animals can easily perform many useful tasks which computers cannot. Biology is worthy of mention here because it is clearly successful and, to a greater or lesser degree, is the inspiration for artificial neural network computation. In a human brain, there are 10 billion neurons, each of which is connected to 10000 others for a total of 100 trillion connections. Each neuron can fire up to 1000 times a second giving a potential total of 100 quadrillion connections per second. When a neuron fires, a pulse travels down an axon which spreads into a series of terminal fibers. The tip of each terminal fiber terminates at a synapse on another neuron. The neuron might learn by increasing the transmission efficiency of the synapse, which is analogous to changing the value of a weight. A pulse arriving at a synapse can induce the neuron to fire or inhibit it from firing. This model of biological neurons is greatly simplified and is included only to indicate that on some level, biological neural networks are similar to artificial neural networks. The functioning of individual biological neurons is relatively well understood when compared with the functioning of higher level operations. The human brain is described by Sholl [1956], and human and nonhuman nervous systems in general by Llinas [1988].

#### 2.3 Sources of Parallelism in Neural Networks

There is parallelism in common places across different types of neural networks. This is because most types of networks are made up of a large number of simple but identical neurons. One way to go faster is to build hardware which will operate in parallel on the same network. Another way is to take advantage of the vector nature of most neural computation and build more efficient hardware, for example by pipelining. In any network, there is a limit in the available parallelism, and once the limit is reached, any further speed increase must come through improvements in the hardware technology.

There is parallelism across the nodes in a layer of a network since they all compute at the same time. All nodes are independent and so their computations may proceed independently. A separate piece of hardware may be assigned to each node.

There is parallelism across the inputs of a node. Whether the node computes a dot product or a distance metric, all of the inputs may be processed in parallel to form partial sums. There is more parallelism in that the complete sum may be formed using a tree of adders, although it takes log(n) steps, where n is the number of inputs. If the sum is performed using analog circuits, the fan-in of the tree is usually small enough that the sum can be performed in a single step.

If the network is implemented digitally using word parallel arithmetic, there is parallelism across the bits of a word. This form of parallelism is traditionally exploited by most digital computers in operation today. A separate piece of hardware may be assigned to each bit. Word parallel arithmetic must actually be performed in a bit serial fashion since a carry bit must usually propagate across all bits or at least through a fast carry tree. However, since the propagation times are usually shorter than a single cycle, this serial aspect of word parallel arithmetic may be ignored.

Some types of networks require the global sum, OR, AND, or maximum of neuron outputs to be computed. This is listed separately from parallelism across neurons because the time to perform global operations is logarithmic in the number of neurons. The base of the logarithm depends upon the implementation technology and is frequently two in digital implementations, but may be as large as the number of neurons in analog technology or by using a digital wire OR, yielding single step computation.

If more than one result from the network is desired, then parallelism can be exploited by assigning hardware for each result to be computed or by pipelining computations through a single set of hardware. Pipelining shortens the critical paths in the circuit and allows the system clock to run faster, although it requires a little extra hardware and introduces latency.

#### 2.4 Measures of Neural Network Performance

~

This section attempts to list different ways in which neural network performance can be measured. The first group, recalls per second, recall latency, quality of recall, recall capacity, training speed, and number of training presentations, are externally oriented and indicate the useful performance of a network implementation in the context of its application. The remaining measures, connections per second, connection updates per second, connections per second per weight, internal storage capacity, and internal precision, are internally oriented and indicate the amount of internal computation going on in a network implementation.

## 2.4.1 External Measures

The number of recalls per second indicates how many outputs per second the implementation can perform and therefore indicates how much useful work is performed. The number and precision of input and output vectors should be considered, but this measure does not attempt to look inside the network.

There may be latency in some implementations due to pipelining or data set parallelism. In this case, the time to process an input may be longer than the interval at which inputs are presented to the network. In real time control problems where the network is used to close a control loop, this latency can slow down the effective response rate of the controller.

The quality of recall indicates the usefulness of the network output in the context in which it is being used. If emulating a function, it may be the mean squared error over the

useful range of the function. If performing a classification, it may be the error rate of the classifier. This measure is included here because it is often possible to trade off other network performance measures to improve the quality of the network result.

The recall capacity is measured in bits and indicates how much information the network can store. A network must adapt its internal weights to learn and mimic a function which may be simple or complicated. Since the network has finite internal storage, there is a limit to the complexity of the function which can be represented.

The training speed indicates how quickly the network can be trained. It is usually measured as total time to achieve a certain level of performance. Some network hardware can only perform recall, but cannot perform a training algorithm and must trained off line. Some network types have required months to train and others can be trained trivially.

Some networks require multiple presentations of the same training set of data. On each presention, the network improves its performance. If a network is designed to be trained by online observation, then the rate at which data is collected may limit the training rate.

#### 2.4.2 Internal Measures

<u>Connections per second</u> (CPS) indicates how may connections are evaluated per second when the network is being used for recall. In some networks, each connection corresponds to an element of a dot product and involves a multiplication of the neuron input with a weight. In other networks, each connection corresponds to a dimension of a distance metric where the weights correspond to the center of the neuron receptive field. Neurons often have a nonlinear squashing function applied. This time is usually folded into the connections per second measure.

<u>Connection updates per second</u> (CUPS) indicates how many connections can be updated per second while the network is being trained. In some types of networks, all

weights are incrementally modified on each training cycle and training can become long while in other types, training time is small.

<u>Connections per second per weight</u> (CPSPW) indicates how may times a particular connection is evaluated per second. The number of CPSPW tends to be constant for a particular implementation technology, so this measure allows different technologies to be compared.

Internal storage capacity is the amount of memory internal to the network and is measured in bits. The memory in some networks is analog, but this can be represented as the number of significant bits above noise. This measure puts an upper bound on the recall capacity and allows different implementation technologies to be compared.

All network inputs, outputs, internal connections, and weights have an inherent precision which is usually expressed in bits. This measure is listed here because whenever the speed of a computation is listed, it is also appropriate to indicate how much information was involved. For instance, weights can be 32 bit floating point values or one bit boolean values.

#### 2.5 Example Neural Networks

This thesis describes a SIMD parallel computer with 32768 processing elements. With this architecture come a unique set of advantages and disadvantages. This section will focus on those neural networks which can be implemented efficiently on the MM32k.

#### 2.5.1 Nearest Neighbor

A nearest neighbor network stores the training examples in its memory. When asked to recall a value, is searches the items stored in its memory and returns the output value of the item which is closest to the input vector. The distance metric can be euclidean distance which requires multiplication, but city block and other distance metrics can be used which are faster to compute. An advantage of nearest neighbor is that it is easy to train, because

the network is trained when the training set is placed into the neurons. A disadvantage is that all items in the memory must be searched in order to return a value. One way to reduce the number of items in the memory is to only store exemplars, or representative examples. A variation on nearest neighbor is K nearest neighbor. In K nearest neighbor, the average or consensus of the K nearest items is returned. In this type of network, there is parallelism across neurons, across the elements of the distance metric, across the bits of the elements of the distance metric, and across the neurons as the maximum is selected. Nearest neighbor algorithms were not originally developed as neural network algorithms, but are similar in form and function to local basis function networks and are considered as such. Nearest neighbor algorithms are described in more detail in Duda [1973].

#### 2.5.2 Content Addressable Memory

Content addressable memory is very similar to nearest neighbor. The weights of each neuron contain the elements of each training vector, only the elements are not restricted to be numerical values, but may be a string of characters. To recall a value, an arbitrary test is made on the elements of all training examples and those meeting the test are selected. Some or all of the elements of the selected neurons may be returned as outputs. If no neurons respond the recall effort has failed. The set of elements which participate in the test and the set which are outputs is arbitrary and may overlap. In this type of network , there is parallelism across neurons, across independent parts of the arbitrary test, across the bits of elements tested, and across neurons as the results are returned. Content addressable memory is described in more detail in Foster [1976]. Content addressable memory is also known as associative memory and is described as such by Potter [1992].

#### 2.5.3 Local Basis Functions

The neurons of a local basis function network store a center vector and an output amplitude as weights. The neuron output is the amplitude value weighted by a distance function which is unity when the input vector is near the neuron center and drops off to zero as the input vector moves away. Each neuron is said to have a local response. The output of the network is the sum of the outputs of the neurons. Intuitively, the centers of the neurons correspond to the centers of the training set. A modification to the basic algorithm is that a width weight vector can be added to vary the rate at which the distance function drops off as the input vector moves away. This allows a single neuron to represent more than one point in the training set. Another modification is that the distance function can be normalized and the network output is a weighted average of the neuron outputs. In this type of network, there is parallelism across neurons, across the elements of the distance metric, across the bits of the elements of the distance metric, and across the neurons as the global sum is computed. Local basis function networks are described by Moody [1988], Broomhead [1988], and Moody [1989].

#### 2.5.4 Kohonen Network

The neurons of a Kohonen network store a center vector and an output value or label. To perform recall, the neuron closest to the input vector is identified and the output which it contains is returned. The input vector is normalized to unit length before being presented to the network. During training, all neurons are on a two dimensional grid. For each training input, the neuron with a weight vector closest to the input vector is selected. Then all neurons near the selected neuron on the grid are modified to be more similar to the input. In this type of network, there is parallelism across neurons, across the elements of the distance metric, across the bits of the distance metric elements, across the neurons as the maximum is selected, and across the neurons near the selected neuron. The Kohonen network is described by Kohonen [1984].

## 2.5.5 ART

The neurons of an adaptive resonance theory (ART) network store a weight vector.

To perform recall, each neuron computes the dot product between the input vector and the weight vector. If the match is not close enough, the selected neuron is disabled and the process is repeated. In this type of network, there is parallelism across neurons, across the elements of the dot product, across the bits of the dot product elements, and across the neurons as the maximum is selected. The ART network is described by Carpenter [1988].

#### 2.5.6 CMAC

A <u>cerebellar model arithmetic computer</u> (CMAC) network implements virtual neurons which are regularly spaced on a grid. To perform recall, the input vector is split into a family of input vectors which are near by the original input vector in the input space. Each of these vectors is mapped through a hash table and selects a neuron which can be implemented in a table in ordinary computer memory. The network returns the average of the physical neuron outputs. An advantage of CMAC is that it is a local basis function type network which can be implemented efficiently on a traditional serial computer. In this type of network, there is parallelism across the family of input vector, across the hash function generation, and across the selected elements of the physical memory which form the average which is returned. The CMAC algorithm is described by Albus [1975] and Miller [1990].

#### 2.5.7 Multilayered Perceptrons

The neurons of a multilayered perceptron network store a weight vector and a threshold value. During recall, the neurons compute the dot product of the weight vector with the input vector and apply a threshold function, whose transition is given by the threshold weight. The output of the threshold function is between zero and one and is passed to the next layer in the network. This network is presented here for completeness, but is not implemented efficiently on the MM32k because of the large number of multiplications and inter-neuron communication operations. In this type of network, there is parallelism across neurons, across the elements of the dot products, across the bits of the elements of the dot

product, and across the layers of the network if the implementation is pipelined. Multilayered perceptron networks are described in McClelland [1986].

#### 2.6 Neural Network Hardware

The purpose of this section is to describe the computing hardware on which neural networks have been implemented in the past. This hardware sits on a continuum with flexible but slow systems at one end and fast but inflexible systems at the other. The most flexible systems are the general purpose computers and microprocessors. Less flexible, but more powerful are vector processors such as DSP microprocessors and vector supercomputers. More powerful still are the SIMD and MIMD parallel computers. The most powerful are the specialized neural network architectures which have hardwired algorithms and sometimes nondigital processing techniques. These systems give the best cost effectiveness but are frequently ineffective on neural network problems which are only incrementally different. A design goal of the MM32k is to achieve high performance without giving up flexibility.

## 2.6.1 Traditional Computers

Traditional computers can be used to implement neural networks. They are usually built around one of the popular general purpose microprocessors. Examples include the Sparc series, the Motorola 680x0 series, the Intel 80x86 series, the MIPS R4000 series, and the Digital Equipment Corporation Alpha series. The advantages are that they are cheap, have good programming tools, and are easy to work with. These computers utilize bit level parallelism and a moderate amount of pipelining on the instruction stream. They are capable of CPS measures in the neighborhood of one to ten million. Most are good at integer arithmetic and some are better than others at floating point arithmetic. They usually have a lot of weight memory and good weight memory density because it is implemented with

DRAMs. They are presented here because they are a popular choice.

# 2.6.2 DSP Microprocessors

Neural networks have been implemented on board level systems available which utilize <u>digital signal processing</u> (DSP) type microprocessors. The DSP microprocessors are distinguished from traditional computers in several ways. First, these machines have a multiply-accumulate unit and autoincrementing address generation hardware which allows them to evaluate a dot products at one partial sum per instruction. Second, they usually have a Harvard type architecture, with separate data and program memories, so that instruction fetch may be overlapped with data fetch. Third, they are relatively difficult to program at an assembly language level and are not efficient executing a higher level language. The DSP microprocessor chips frequently contain both data memory and program memory internally and are low in cost. Some types have 16 bit data paths and perform fixed point calculations and others have 32 bit data paths and perform floating point calculations. They can achieve 10 to 40 million multiply-accumulate operations per second. The Texas Instruments TMS320x0 series, described by Texas Instruments [1992], is representative of DSP microprocessors.

#### 2.6.3 MIMD Parallel Computers

Neural networks have been implemented on <u>multiple instruction multiple data</u> (MIMD) parallel computers. A MIMD parallel computer is a set of ordinary computers which can communicate through an interconnection network. The neural network computation and weight storage is spread across the nodes of the MIMD computer. The topology of the interconnection network does not have to match the topology of the neural network, although it should efficiently support it. The <u>Ring Array Processor</u> (RAP), described by Morgan [1990], is representative. It is a group of TMS320C30 32 bit floating point micro-processors, each with 16 megabytes of DRAM memory, 256 kilobytes of fast SRAM mem-

ory, and each capable of 32 megaflops while performing multiply-accumulate operations. The microprocessors are interconnected in a ring topology, which is expandable. Up to 40 microprocessors have been operated in a single system for a measured performance of 574 million connections per second. A system is a collection of VME bus cards, each with four DSP microprocessors, and all connected to and hosted by a Unix workstation.

#### 2.6.4 Vector Supercomputers

Neural networks have been implemented on vector supercomputers. These systems are optimized for 32 bit or 64 bit floating point vector arithmetic. The architectural advantage is that the arithmetic and logic unit can be deeply pipelined and is sometimes replicated. They are usually implemented using exotic logic technology running at an extremely high clock rate. They usually have large amounts of main memory and require vectors to be 50 to 100 elements long before the vector instruction overhead is a small part of computation. They can achieve 100 million to 10 billion floating point operations per second of performance. They are very expensive. They are programmable in high level languages by using vector libraries. The series of computers manufactured by Cray Research is representative. The first Cray machine, the Cray 1, is described by Russell [1978], although higher performance models have superceded it.

### 2.6.5 Massively Parallel SIMD Supercomputers

Neural networks have been implemented on massively parallel <u>single instruction</u> <u>multiple data</u> (SIMD) supercomputers. These systems have 1024 to 65536 simple processors, each with memory and an arithmetic and logic unit. All processors are interconnected through a switching network and all processors execute the same instructions at the same time using different data. Economics or available problem set parallelism, not technology usually limits the number of processors which can be built in a single machine. Processors usually have data paths which are one bit wide and do bit serial arithmetic. These computers are typically built around a custom chip which implements 16 processors with the processor memory being implemented using standard memory chips. Like vector supercomputers, these machines are usually very large and expensive, although they are more cost effective in appropriate applications. For a SIMD parallel computer to be effective, the network must have enough parallelism to keep all of the processors busy and the required connections must be efficiently implementable by the switching network. Example SIMD parallel computers are the <u>Distributed Array Processor</u> (DAP), described by Active Memory Technology [1989], the <u>Massively Parallel Processor</u> (MPP), described by Potter [1985], the <u>Connection Machine 1</u> (CM-1), described by Hillis [1985], and the Maspar series, described by Nickoll [1990].

### 2.6.6 Siemens SYNAPSE-1 Systolic Array Using MA16 Chip

,\*

The SYNAPSE-1 system is an all digital systolic array of processors. A systolic array is similar to a SIMD computer in that it is an interconnected array of processors which receive the same instructions at the same time. It is different in that the data is not located at each processor, but is pumped across the array from an external memory. This system contains 32 processors organized into eight MA16 chips and interconnected in a two dimensional mesh. The system can compute 5.1 billion 16 by 16 bit connections peak using a 40 megahertz clock although it cannot fetch weights from the weight memory at this rate. It can perform both recall and training and is supported by a C++ class library which abstracts the elementary operations of the chip. The core area of each chip is 98 square millimeters, contains 488 thousand transistors, and is implemented in 0.8 micrometer CMOS. This system is described by Ramacher [1991], and Ramacher [1993].

#### 2.6.7 CMAC Board

This board implements the CMAC algorithm with a combination of a fixed point DSP microprocessor, static RAM memory, and programmable gate arrays. The number of

16 bit inputs can be from one to 512 and the number of 16 bit outputs can be from one to eight. Up to eight independent virtual CMACs can be simultaneously stored on a single card. The CMAC algorithm contains a large number of virtual connections and physically implements only the small fraction of those which are nonzero. Networks with 32 inputs and eight outputs can be implemented in less than one millisecond making the board ideal for robotic control problems. The board can perform both recall and training and is described by Miller [1990].

1

#### 2.6.8 CNAPS 1064 Chip

The CNAPS chip has 64 processors and is intended to be part of a SIMD parallel processor optimized for neural networks. Each processor has a fixed point ALU which operates at a 25 megahertz rate for a total of 1.6 billion 16 bit by 8 bit multiply-accumulate operations per second. Each processor has 4096 bytes of SRAM memory for a total of 256 kilobytes per chip, which can be configured as 1, 8, or 16 bit weights. The peak memory bandwidth is 3.2 gigabytes per second. A total of 80 processors are fabricated on each chip and each local memory of each processor has redundant rows. Bad processors and bad rows are switched out to increase the yield of the manufacturing process and reduce the cost of the chip. Usually four chips are mounted together with a controller to form a system, although more chips can be added. The chip can perform both recall and training and is supported by a compiler for the C\* parallel programming language. The chip is all digital, is implemented in 0.8 micrometer CMOS, is 26.2 by 27.5 millimeters, and is described by Hammerstrom [1990].

#### 2.6.9 Intel 80170 ETANN Chip

The Intel 80170 <u>Electrically Trainable Analog Neural Network</u> (ETANN) chip is designed to perform dot products. It contains 64 neurons, each with 128 synapses and a sigmoid function. The weights are stored in nonvolatile analog EEPROM cells with six bits of precision. All inputs, outputs, and computations are analog. The chip has internal feedback circuitry and can be configured to implement multilayer and hopfield networks. Multilayer networks can also be formed by cascading multiple chips. The chip has only 64 physical inputs, which must be multiplexed in time to connect to the 128 synapses, and 64 outputs. It can achieve over two billion connections per second during recall and has provision to support learning at 100 thousand connection updates per second. The chip is described by Intel [1991].

,\*

#### 2.6.10 Intel Ni1000 Chip

The Intel Ni1000 chip is designed to compute radial basis function type neural networks. It implements 1024 neurons, each of which computes a city block distance metric between a 256 dimensional five bit input vector and 256 five bit weights. Neurons within a specified radius of the input vector are selected and a six bit classification label is returned. Estimation of class probability distribution functions is also supported by using a weight on the output of each neuron. The chip contains a microcontroller and can be programmed to implement other algorithms. The chip can perform a classification every 50 microsecond in pipelined mode for a total of five billion connections per second. All weights are stored in nonvolatile digital EEPROM memory so they are not lost when the chip is powered down. This chip is all digital and is described by Scofield [1991] and Intel [1993]. It is currently under development.

# 2.6.11 Hitachi 8 Megabit Chip

This proposed chip is built around an 8 megabit DRAM, is all digital, and will perform dot products. The memory has 16384 data lines and cycles in 1500 nanoseconds for a gross memory bandwidth of 1.3 gigabytes per second. This data is multiplexed into 256 eight bit by eight bit multiply-accumulators which can perform 1.37 billion connections per second. The memory array can hold up to one million eight bit weights. The chip is to be implemented in 0.5 micrometer CMOS, will be 15.4\*18.6 millimeter, will operate at 1.5 volts, and will dissipate 75 milliwatts when operating. The weights are trained off line. A one sixteenth slice of this chip has been fabricated and tested. The chip is described by Watanabe [1993].

#### 2.6.12 Analog Radial Basis Function Chip

This chip implements a radial basis function type network with eight inputs 159 neurons, and four outputs. For each neuron, distance differences are computed on a per axis basis and a gaussian function is applied to each difference. The outputs of the gaussians are then summed and compared to a threshold. If the comparison difference is greater than zero, the comparison difference squared is returned as the weight associated with the neuron, otherwise zero is returned. A weighted average of neurons outputs is computed and returned as the output of the network. The distance metric is not truly radial in a multidimensional sense. In two dimensional space, the basis function of a neuron covers the union of two stripes instead of the insides of a circle. This chip is unique in that it does this with analog instead of digital circuitry. The weights are implemented with charges on capacitors and are trained off line. This chip is described by Anderson [1992].

#### 2.6.13 ATT Bell Labs ANNA Chip

This analog-digital hybrid chip implements 4096 physical synapses and is designed to implement dot products. The synaptic weights have six bits of precision and are stored as analog charges which are periodically refreshed. The input vector has three bit elements. The multiplication is done by a multiplying digital to analog converter. To form a dot product, the results are summed in analog and converted back to digital by a three bit analog to digital converter. The chip is flexible and can be configured to have from 16 neurons with 256 inputs to 256 neurons with 16 inputs. The chip can store over 130 thousand connections and compute 5 billion connections per second. The weights are trained off line. The chip measures 4.5 by 7 millimeters, is fabricated in 0.9 micrometer CMOS, and contains 170 thousand transistors. This chip is described by Boser [1991].

^

# 2.6.14 ATT Bell Labs NET32K Chip

This analog-digital hybrid chip implements 32768 one bit connections in 256 neurons and is designed to implement dot products. Each neuron has 128 one bit digital weights which are multiplied by 128 one bit digital inputs from an input vector. The one bit products are summed and compared using an analog circuit. All neurons receive the same input vector. The chip is not restricted to dealing with binary inputs and outputs. The sum at each neuron can be scaled by 1, 1/2, 1/4, or 1/8 and added to the scaled sums of the neighboring neurons to produce a single larger composite neuron. In this way, the input vectors can have up to four bits of precision, although some weights must be set to zero and are wasted. The composite output can be detected with different thresholds by using the threshold detectors of each of the individual neuron threshold detectors to produce an output vector with up to 3 bits of precision. The chip can cycle in 100 nanoseconds giving a performance of 320 billion one bit connections per second. It has a high degree of flexibility from a simple analog design, but has no provision for training the weights on line. The chip measures 4.5 by 7 millimeters, is fabricated in 0.9 micrometer CMOS, contains 412 thousand transistors and is described by Graf [1991].

### 2.6.15 Neocognitron CCD Chip

This chip implements the neocognitron neural network using analog CCD processing. It applies a seven by seven spatial filter to the pixels of an image to search for features. The filter is a 49 point dot product. The chip contains a 775 stage CCD tapped delay line for holding and shifting six lines of 128 pixel values each plus seven pixels of the following line. There are 49 multiplying digital to analog converters and an analog summer which produce an output pixel each time the delay line is shifted. Each multiplying digital to analog converter has storage for 20 weights of eight bits so that 20 different features can be computed without reloading weights. The device occupies 29 square millimeter and performs over one billion operations per second when clocked at 10 megahertz while using less than one watt of power. It is described by Chuang [1990].

#### 2.6.16 Optical Network

Neural networks can be built from optical components. The most common use is to perform a dot product by multiplying in the spatial frequency domain. This dot product is equivalent to a correlation. A lens performs a Fourier transform on an image which is then projected onto a light attenuator where a point by point multiplication is performed. The attenuator is implemented by a piece of film or a liquid crystal light modulator and holds the fourier transform of the pattern which is to be correlated. A second lens then performs another fourier transform on the signal to return it to its original domain and form the correlation of the original image with the pattern image. The correlation image is then searched for a peak to obtain the best matching pattern. This technique is used by Wunsch [1991] to implement the ART1 network.

#### 2.7 Comparison of Thesis to Previous Techniques

The processor described in this thesis is unique in several ways. First and most significantly, it is unique in that it is far more cost effective than other SIMD designs on suitable problems. This design implements 2048 processing elements on a single chip where typical SIMD designs implement 16 processing elements on five chips. The ALU and instruction set of the processing elements are also unique. The software support is unique in that it dynamically varies the precision of computation on a bit basis at run time, where most processors bind the precision on a byte basis at compile time.

#### Chapter 3

.

### HARDWARE

The purpose of this chapter is to describe the hardware of the MM32k. The chapter after it describes a logical machine which can be implemented with the hardware and the chapter after that describes how that logical machine can be programmed using a C++ class library. This chapter will describe the capabilities of the hardware in enough detail to show that it can support the model in the next chapter.

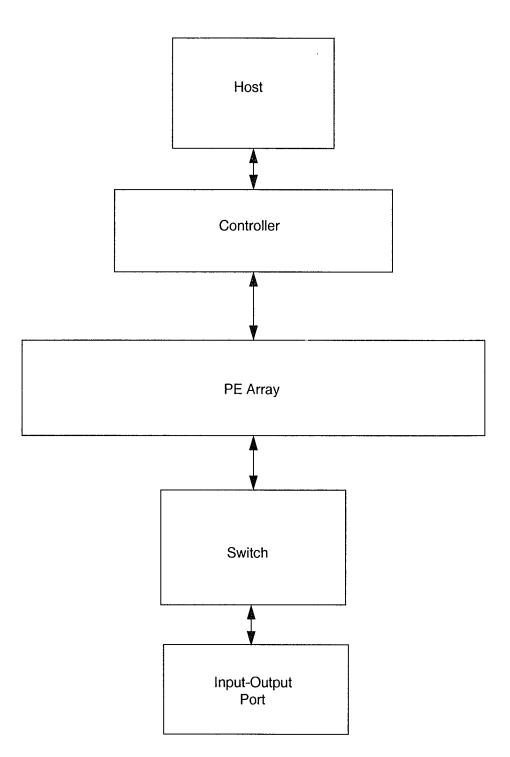

The hardware is divided into four parts, the <u>processing element</u> (PE) array, the switch, the input-output port, and the controller. The PE array contains the memory and ALUs of the SIMD machine. The switch allows the PEs to exchange data. The input-output port allows data to be transferred in to and out of the machine at high speed. The purpose of the controller is to receive and execute instructions from the host. A block diagram of the system is given in the next figure.

~

Figure 3.1 MM32k Block Diagram

### 3.1 Controller

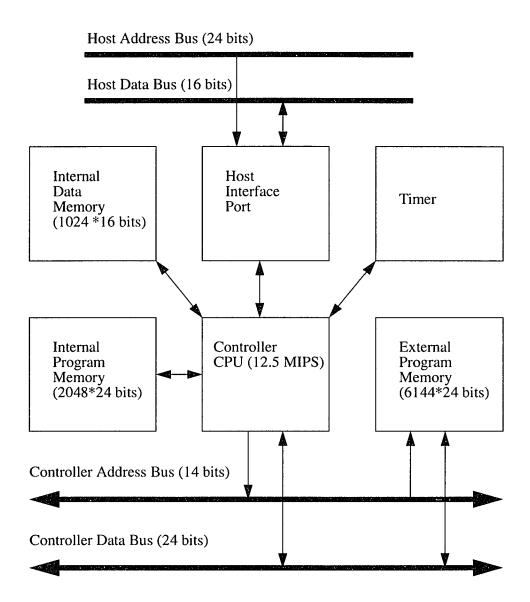

The purpose of the controller is to receive and direct the execution of SIMD operations requested by from the host computer. It is shown in the next figure. The controller is an Analog Devices ADSP2111, which is a single chip 16 bit DSP microprocessor with internal data memory, internal program memory, an internal timer, an interrupt system, and an interface to the host computer. Internally, the controller has a Harvard type architecture, but externally has a single bus, to which external program memory, the PE array, and the switch are connected.

# 3.1.1 Host Interface Port

The <u>host interface port</u> (HIP) allows the controller to communicate with the host. The HIP, which is integrated onto the DSP chip, consists of six 16 bit bidirectional data registers and two status and control registers. The controller can configure the HIP so that an interrupt is generated when the host computer writes data to or reads data from the registers. The controller is reset and booted via the HIP. A complete copy of the controller microcode is downloaded from the host and placed into program memory during this process.

#### 3.1.2 Controller CPU

The controller <u>central processing unit</u> (CPU) has an ALU, a shifter, a <u>multiply accu-</u> <u>mulate</u> (MAC) unit, two address generators, program control mechanisms, and duplicate register sets. It usually executes an instruction in a single 80 nanosecond cycle, providing a 12.5 megahertz instruction rate. The ALU allows it to perform 16 bit arithmetic and logic operations. The shifter allows it to logically and arithmetically shift and mask 16 bit data. The MAC block allows it to perform single cycle multiply and accumulate operations. The two address generators allow it to specify two autoincremented addresses to reference data and program memory and can also implement circular buffers with zero overhead. The program control mechanism supports subroutine calls, interrupts, and zero overhead looping. For example, a loop with a body of one instruction will execute at a rate of one cycle per iteration. This makes it easy to code the loops associated with bit serial arithmetic. The data registers associated with the ALU, the shifter, and the MAC are duplicated, so context switching may be performed quickly during an interrupt.

#### 3.1.3 Internal Data Memory

The internal data memory is 1024 words of 16 bits. It contains a 100 word queue of instructions from the host, implemented as a circular buffer. Instructions are placed in the queue in response to interrupts to the DSP microprocessor from the HIP, caused by the host writing data into the HIP registers. To reduce the overhead, instructions are always enqueued in groups of 6 words. Data memory also contains working variables associated with the execution of instructions. Since it is internal to the DSP microprocessor, data memory can be accessed without causing a cycle on the controller bus.

## 3.1.4 Internal Program Memory

The internal program memory is 2048 words of 24 bits and holds native instructions for the DSP microprocessor. It is loaded by the host system when the MM32k is booted via the HIP. Data may also be kept in program memory, and fetched in parallel with data from the data memory without adding cycles to a DSP instruction. Since it is internal to the DSP microprocessor, program memory may be accessed without causing a cycle on the controller bus. This is important because instructions to the PE array are issued over the controller bus.

# 3.1.5 External Program Memory

The external program memory is 6144 words of 24 bits and was added because the 2048 words of internal program memory are not enough to support the complete MM32k instruction set. It is attached to the DSP via the controller bus and therefore DSP instruc-

tions executed out of it require a controller bus cycle. This is important because it can prevent the DSP from issuing PE array instructions over the controller bus, slowing down the MM32k.

# 3.1.6 Timer

The timer is internal to the DSP and can be programmed to interrupt the DSP at regular intervals. It can also be read by a DSP program, giving a real time clock. The timer interrupts are used to trigger the refresh of the DRAM arrays which make up the PE array.

#### 3.1.7 Controller Bus

The controller bus is the bus of the DSP microprocessor and allows it to communicate with the PE array, switch, input-output port, and external program memory. The data path is 24 bits wide, although the bottom 8 bits are only used for external program memory transfers. The address path is 14 bits wide. The PE array memory is mapped onto the controller bus so it may be read and written in response to instructions from the host. The controller issues instructions to the PE array by writing a 16 bit word into a 512 word segment of its external data memory address space. The offset in the segment specifies a nine bit address in PE memory, which has 512 bits, and the 16 bit data specifies the operation to be performed. The switch configuration is set by writing to registers which are located in the switch chip and mapped onto the controller bus.

...

Figure 3.2 Controller

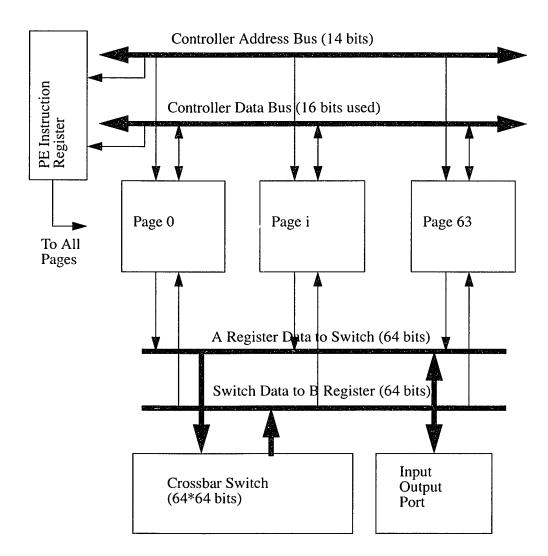

### 3.2 PE Array

This sections describes the PE array, which is the computational engine of the MM32k. It is composed of 32768 processing elements, or PEs. The PE array contains a total of 2 megabytes of memory, organized as 512 bits attached to each PE. The 2 megabytes of PE memory is mapped onto the controller bus. The PE array is connected to the switch via two 64 bit wide data paths, one to and the other from the switch. The PE array instruction register is also on the controller bus. The PE array is shown in the next figure.

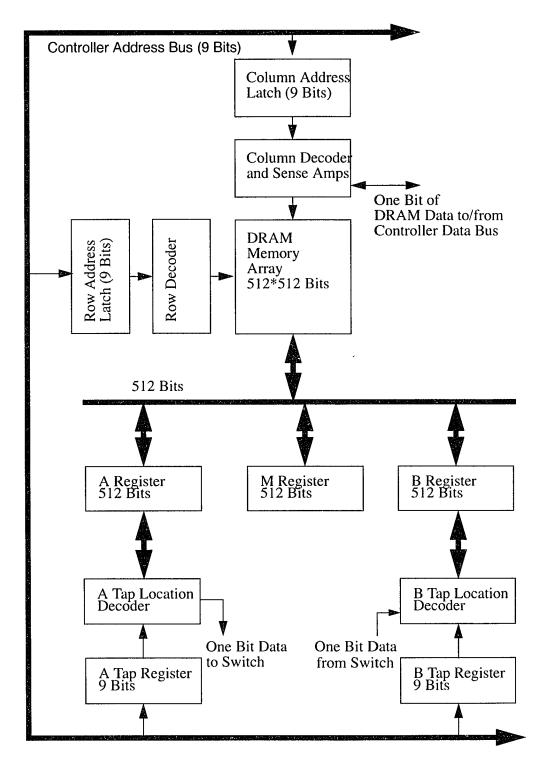

# 3.2.1 PE Page

The PEs are organized into 64 pages, numbered 0 to 63, each implementing 512 individual PEs. Each page contains 262144 bits of DRAM memory, implemented in a 512 by 512 array. Each page also contains three 512 bit registers, called the A register, the B register, and the M register. There is also an A tap pointer register and a B tap pointer register associated with each page, which direct bits from the A register to the switch, and form the switch into the B register. There are four pages implemented per integrated circuit and a total of 16 integrated circuits in the PE array.

,\*

Figure 3.3 PE Array

3.2.1.1 DRAM Memory Array

The DRAM memory array for each page contains 262144 bits and is organized as

34

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.