### University of New Hampshire Scholars' Repository

Doctoral Dissertations Student Scholarship

Fall 2016

# ASSESSING AND IMPROVING THE RELIABILITY AND SECURITY OF CIRCUITS AFFECTED BY NATURAL AND INTENTIONAL FAULTS

Hoda Pahlevanzadeh University of New Hampshire, Durham

Follow this and additional works at: https://scholars.unh.edu/dissertation

#### Recommended Citation

Pahlevanzadeh, Hoda, "ASSESSING AND IMPROVING THE RELIABILITY AND SECURITY OF CIRCUITS AFFECTED BY NATURAL AND INTENTIONAL FAULTS" (2016). *Doctoral Dissertations*. 1364. https://scholars.unh.edu/dissertation/1364

This Dissertation is brought to you for free and open access by the Student Scholarship at University of New Hampshire Scholars' Repository. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of University of New Hampshire Scholars' Repository. For more information, please contact nicole.hentz@unh.edu.

# ASSESSING AND IMPROVING THE RELIABILITY AND SECURITY OF CIRCUITS AFFECTED BY NATURAL AND INTENTIONAL FAULTS

#### BY

#### HODA PAHLEVANZADEH

Bachelor of Science, Tehran Azad University, 2008 Master of Science, University of Colorado, Boulder, 2012

#### DISSERTATION

Submitted to the University of New Hampshire in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

in

Electrical and Computer Engineering September, 2016

This thesis/dissertation has been examined and approved in partial fulfillment of the requirements for the degree of PhD in Electrical Engineering by:

Dr. Thesis/Dissertation Director, Qiaoyan Yu, Assistant Professor (Electrical and Computer Engineering)

Dr. W. Thomas Miller III, Professor (Electrical and Computer Engineering)

Dr. Nicholas J. Kirsch, Associate Professor (Electrical and Computer Engineering)

Dr. Edward Song, Assistant Professor (Electrical and Computer Engineering)

Dr. May-Win Thein, Associate Professor (Mechanical Engineering)

On June 13 2016

Original approval signatures are on file with the University of New Hampshire Graduate School.

#### **Dedication**

I would like to dedicate this dissertation to:

my parents Hassan and Nasrin, my sister Azadeh, my husband Majid, and my daughter Yasmin.

#### Acknowledgment

I would like to thank my parents Dr. Hassan Pahlevanzadeh and Nasrin Attaran-Rezai for believing in, supporting, and providing me the best educational opportunities over the years.

I thank my beloved husband Dr. Majid Ghayoomi for all his emotional support that helped me to conquer my fears, all his encouragement that kept me moving, and all his great advices that made this journey smooth.

I thank my advisor Prof. Qiaoyan Yu for the research opportunity and advice, and express my sincere gratitude to the rest of my thesis committee: Prof. W. Thomas Miller III, Prof. Nicholas J. Kirsch, Prof. Edward Song, and Prof. May-Win Their for their insightful comments and advices.

A special thanks goes to Prof. May-Win Thein for being such a supportive and caring person that helped me through the most difficult times. I am very grateful that her spiritual support motivated me to continue and finish my studies.

I also thank the Department of Electrical and Computer Engineering for the teaching assistantship opportunity throughout my studies at the University of New Hampshire that helped me improve my teaching skills.

Last but not least, I thank my fellow groupmates Jaya Dofe and Mohammd Raashid Ansari for the academic and emotional support, and of course for all the fun we have had.

#### **Table of Contents**

| DEDIC         | ATION                                                                         | III |

|---------------|-------------------------------------------------------------------------------|-----|

| ACKNO         | OWLEDGMENT                                                                    | IV  |

| LIST O        | F TABLES                                                                      | X   |

| LIST O        | F FIGURES                                                                     | XI  |

| ABSTR         | ACT                                                                           | XIV |

| СНАРТ         | ER 1. INTRODUCTION                                                            | 16  |

| 1.1. C        | hallenges of Natural Faults' Impact                                           | 16  |

| 1.1.1.        | Soft Errors from Space to Ground                                              |     |

| 1.1.2.        | Impact of Altitude on SER                                                     | 18  |

| 1.1.3.        | Impact of Technology Scaling on SER                                           | 19  |

| 1.1.4.        | Increasing the Importance of Soft Errors in Combinational Logic               | 21  |

| <b>1.2.</b> C | hallenges of Intentional Faults' Impact                                       | 22  |

| 1.2.1.        | Cryptosystems Security Threat                                                 |     |

| 1.2.2.        | Similarity of Intentional Faults to Natural Faults                            | 27  |

| 1.3. U        | nified Reliability and Security countermeasure                                | 28  |

| <b>1.4.</b> O | rganization of the Thesis                                                     | 29  |

| СНАРТ         | ER 2. BACKGROUND                                                              | 31  |

| 2.1. N        | atural Faults                                                                 | 31  |

| 2.1.1.        | Reliability                                                                   | 31  |

| 2.1.2.        | Soft Error Mechanism                                                          | 31  |

| 2.1.3.        | Different Types of Soft Errors                                                | 33  |

| 2.1.4.        | Estimation of SER <sub>SET</sub>                                              | 33  |

| 2.1.5.        | Estimating SER for Single and Multiple SET pulse widths                       | 35  |

| 2.2. Ir       | ntentional Faults                                                             | 35  |

| 2.2.1.        | Cryptosystems Security Protection                                             |     |

| 2.2.2.        | Impact of Existing Countermeasures for Fault Attack on Cryptosystem Security. | 36  |

| 2.3. | Ad   | vanced Encryption Standard                                                                                            | 38  |

|------|------|-----------------------------------------------------------------------------------------------------------------------|-----|

| 2.4. | Co   | rrelation Power Analysis                                                                                              | 39  |

| 2.4  | .1.  | Hamming Weight and Hamming Distance Power Models                                                                      | 40  |

| 2.4  | .2.  | Pearson's correlation coefficient                                                                                     |     |

| 2.4  | .3.  | Correlation Power Analysis on AES                                                                                     | 41  |

| 2.5. | Pa   | rtial Guessing Entropy                                                                                                | 44  |

| 2.6. | CR   | C Codec                                                                                                               | 45  |

| 2.6  | 5.1. | CRC Mechanism                                                                                                         | 45  |

| 2.6  | 5.2. | Error detection in CRC                                                                                                | 47  |

| СНА  | PTE  | R 3. SYSTEMATIC ANALYSES FOR LATCHING PROBABILITY OF                                                                  |     |

| SINC | FLE- | EVENT TRANSIENTS                                                                                                      | 49  |

| 3.1. | Int  | roduction                                                                                                             | 49  |

| 3.2. | Pro  | oposed Model for the Probability of Being in Latching Window                                                          | 52  |

| 3.2  |      | Definitions Used in Proposed Analytical Model                                                                         |     |

| 3.2  |      | Error Categories.                                                                                                     |     |

|      |      | Uncertain Errors                                                                                                      |     |

|      |      | Sure Errors                                                                                                           |     |

|      |      | Silent Errors                                                                                                         |     |

| 3.3. | Ov   | erall Probability of Latching SET Pulse                                                                               | 57  |

| 3.4. | Ac   | curacy of Proposed Model                                                                                              | 58  |

|      | .1.  | · · · · ·                                                                                                             |     |

| 3.4  | .2.  | Verification on Logic Network with Logical Masking                                                                    |     |

| 3.5. | Ex   | perimental Results                                                                                                    | 64  |

| 3.5  | .1.  | Impact of Logic Delay on Soft Error Rate                                                                              | 64  |

| 3.5  | 5.2. | Impact of SET Injection Timing on Soft Error Rate                                                                     | 66  |

| 3.6. | Co   | nclusion                                                                                                              | 68  |

| FOR  | CIR  | CR 4. A NEW ANALYTICAL MODEL OF SET LATCHING PROBABILIT<br>CUITS EXPERIENCING SINGLE- OR MULTIPLE-CYCLE SINGLE-EVENTS | ENT |

| 4.1. | Int  | roduction                                                                                                             | 70  |

| <ul> <li>4.2.2. Our Main Contributions</li> <li>4.3. Proposed Latching Window Masser</li> <li>4.3.1. Latching Single-Cycle SETs .</li> <li>4.3.2. Latching Multiple-Cycle SET</li> <li>4.4. Fast SET Injection Approach for</li> <li>4.5. Experimental Results</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | sking Probabilitys                                                          | 73 74 76 77                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------|

| <ul> <li>4.3. Proposed Latching Window Masses</li> <li>4.3.1. Latching Single-Cycle SETs</li> <li>4.3.2. Latching Multiple-Cycle SET</li> <li>4.4. Fast SET Injection Approach for</li> <li>4.5. Experimental Results</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | sking Probabilitys                                                          | <b> 74</b><br>76<br>77      |

| <ul> <li>4.3.1. Latching Single-Cycle SETs.</li> <li>4.3.2. Latching Multiple-Cycle SET</li> <li>4.4. Fast SET Injection Approach for</li> <li>4.5. Experimental Results</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | r SET Assessment                                                            | 76<br>77                    |

| <ul><li>4.3.2. Latching Multiple-Cycle SET</li><li>4.4. Fast SET Injection Approach for</li><li>4.5. Experimental Results</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | r SET Assessment                                                            | 77                          |

| 4.4. Fast SET Injection Approach for 4.5. Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | r SET Assessment                                                            |                             |

| 4.5. Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             | 81                          |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                             |                             |

| 4.5.1. Experiment Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                             |                             |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                             |                             |

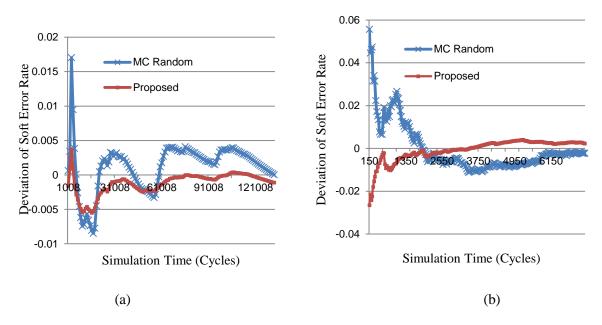

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | osed Analytical Model                                                       |                             |

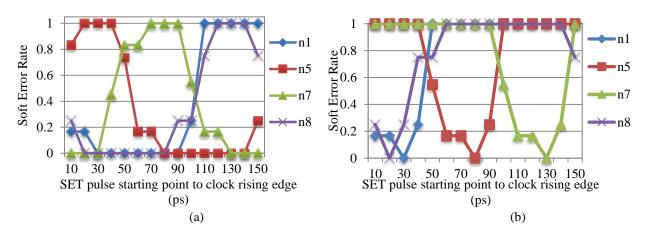

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | s on Latching Window Masking                                                |                             |

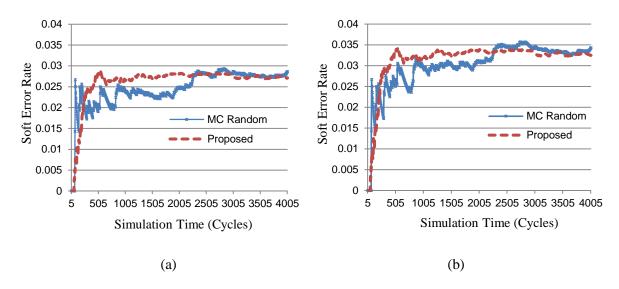

| 4.5.4. Simulation Time Reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                             | 95                          |

| 4.6. Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                             | 96                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                             |                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                             |                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                             | $\alpha$                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                             |                             |

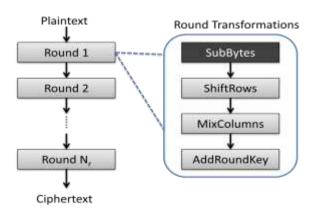

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | nanisms for AES                                                             | 101                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                             | 101                         |

| <ul><li>5.2.3. Correlation Power Analysis (</li><li>5.3. Our Objective and Experimenta</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nanisms for AES                                                             | 101 102                     |

| <ul><li>5.2.3. Correlation Power Analysis (</li><li>5.3. Our Objective and Experimenta</li><li>5.3.1. Study Objective</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | nanisms for AES                                                             | 101 102 102                 |

| <ul><li>5.2.3. Correlation Power Analysis (</li><li>5.3. Our Objective and Experimenta</li><li>5.3.1. Study Objective</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | nanisms for AES                                                             | 101 102 102                 |

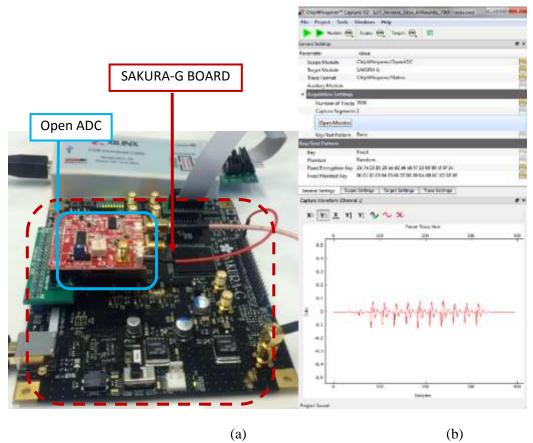

| <ul><li>5.2.3. Correlation Power Analysis (Constitution of the State o</li></ul> | nanisms for AES                                                             | 101 102 102 103             |

| <ul> <li>5.2.3. Correlation Power Analysis (6</li> <li>5.3. Our Objective and Experimenta 5.3.1. Study Objective</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nanisms for AES                                                             | 101 102 102 103 104         |

| <ul> <li>5.2.3. Correlation Power Analysis (Construction)</li> <li>5.3. Our Objective and Experimenta Solution Solution</li></ul>  | nanisms for AES  CPA)  I Setup  xperiments  n AES                           | 101 102 102 103 104         |

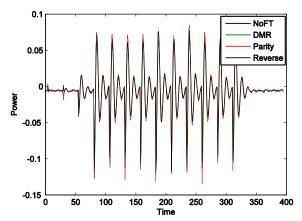

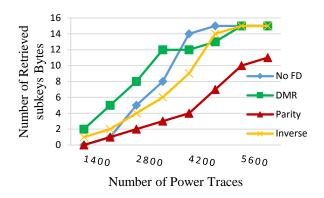

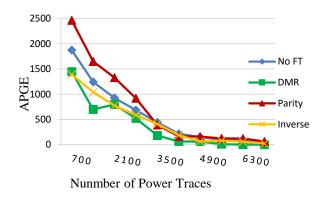

| <ul> <li>5.2.3. Correlation Power Analysis (Construction)</li> <li>5.3.1. Study Objective and Experimenta Study Objective</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nanisms for AES  CPA)  I Setup  Experiments  n AES  Traces of Different FDs | 101 102 102 103 104 104 105 |

| <ul> <li>5.2.3. Correlation Power Analysis (Control of State 1988)</li> <li>5.3.1. Study Objective and Experimental State 2089.</li> <li>5.3.2. Hardware and Software for Experimental Results for CPA of State 2089.</li> <li>5.4.1. Comparison of Single Power State 2089.</li> <li>5.4.2. Key Retrieval Speed Comparison 5.4.3. Impact of Power Models in Control of Power Models</li></ul> | nanisms for AES  CPA)  I Setup  Experiments  Traces of Different FDs.  son. | 101 102 102 103 104 105 108 |

| 6.1. | In    | troductiontroduction                                                       | 113   |

|------|-------|----------------------------------------------------------------------------|-------|

| 6.2. | Re    | elated Work and Our Contributions                                          | 114   |

| 6.2  | .1.   | Related work                                                               | 114   |

| 6.2  | .2.   | Our Contributions                                                          | 117   |

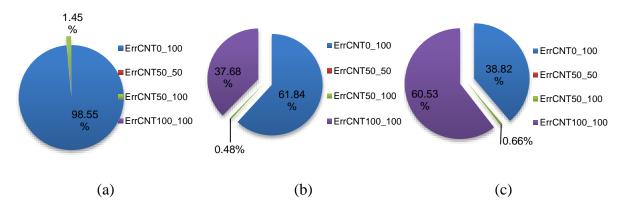

| 6.3. | Oı    | ır Systematic Assessment                                                   | 118   |

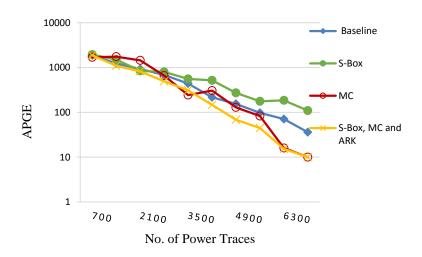

| 6.5  | .1.   | Impact of Hardware Redundancy based Fault Detection Mechanisms on CPA      | Key   |

| Re   | triev | ral Speed                                                                  | 118   |

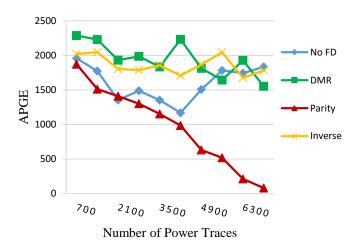

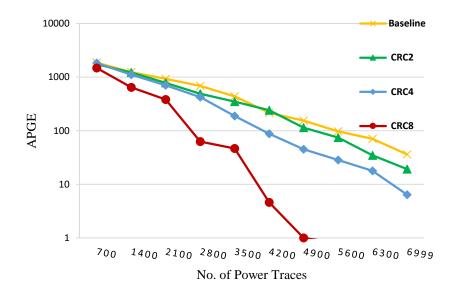

| 6.5  | .2.   | Impact of Information-Redundancy based Fault Detection Mechanisms on CP.   | A Key |

| Re   | triev | al Speed                                                                   | 120   |

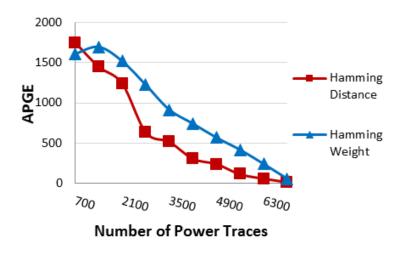

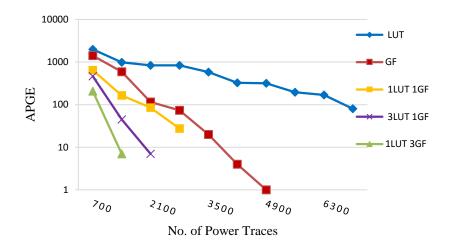

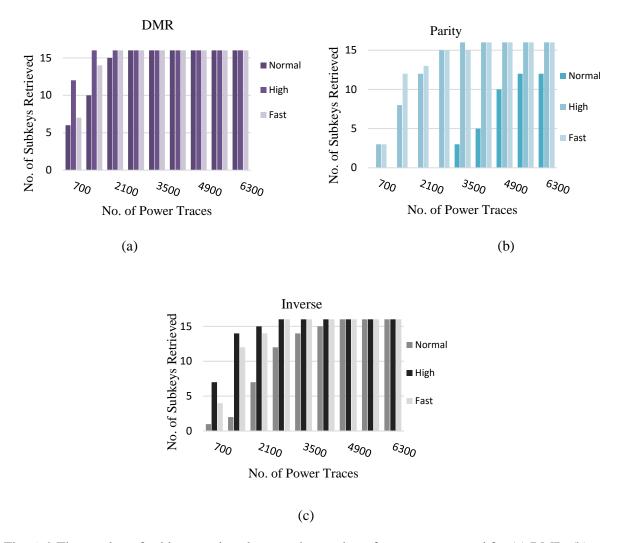

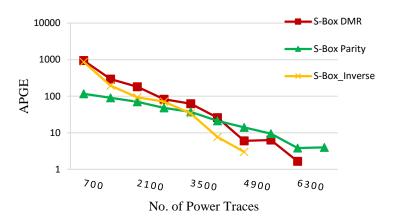

| 6.5  | .3.   | Impact of S-Box Implementation Methods on CPA Key Retrieval Speed          | 124   |

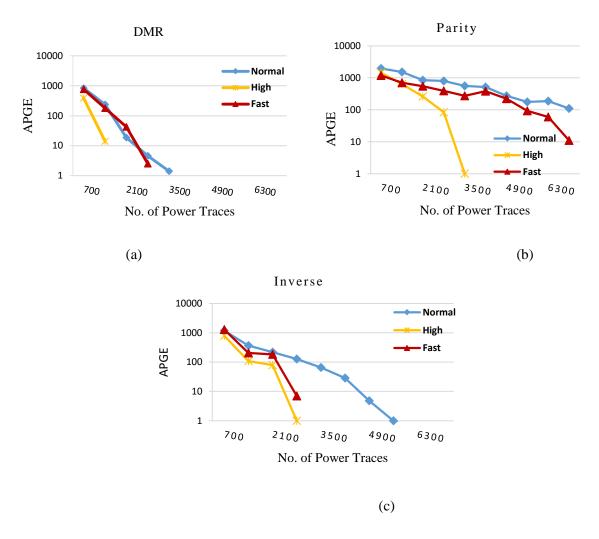

| 6.5  | .4.   | Impact of Synthesis Tool Optimization Strategy on CPA Key Retrieval Speed. | 126   |

| 6.5  | .5.   | Impact of Heterogeneous-Redundancy based Fault Detection Mechanisms on     | CPA   |

| Eff  | icie  | ncy                                                                        | 128   |

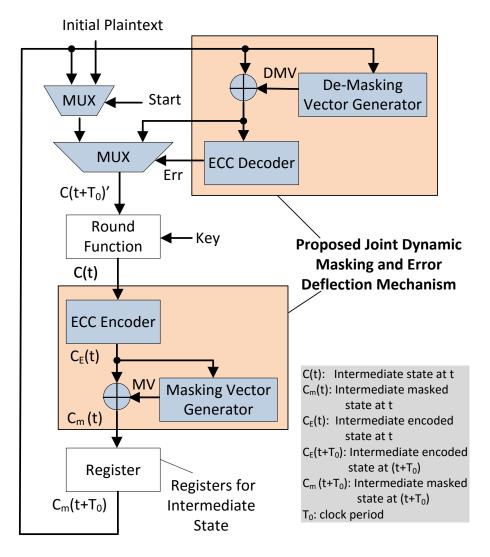

| 6.4. | Pr    | oposed Countermeasure against the Combination of CPA and FA Attacks        | 130   |

| 6.6  |       | Proposed Method Description                                                |       |

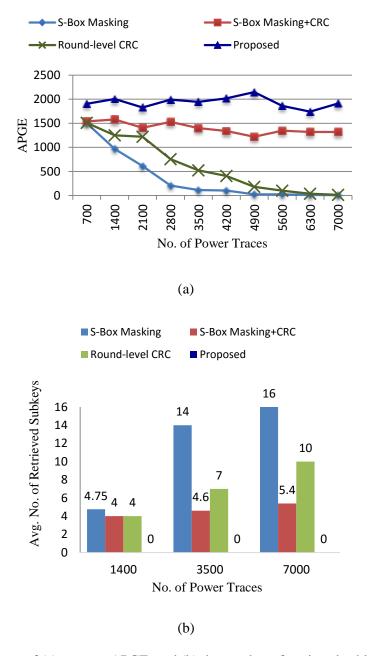

| 6.6  | .2.   | Evaluation of the Resistance to CPA Attacks                                | 132   |

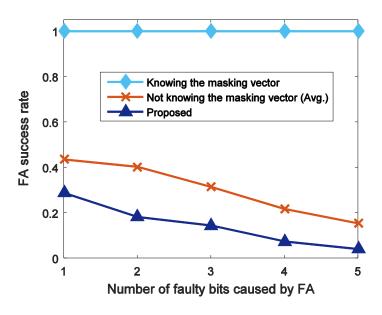

| 6.6  | 5.3.  | Evaluation of the Resistance to FA Attacks                                 | 134   |

| 6.6  | .4.   | FPGA Cost                                                                  | 135   |

| 6.5. | Co    | onclusions                                                                 | 135   |

| СНА  | PT1   | ER 7. DYNAMIC CRC FOR RELIABLE AND SECURE SYSTEMS                          | 137   |

| 7.1. | IN    | TRODUCTION                                                                 | 137   |

| 7.2. | PF    | RELIMINARIES                                                               | 138   |

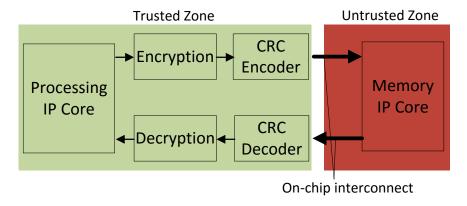

| 7.2  |       | Abstract of Target System                                                  |       |

| 7.2  | .2.   | Symbols and CRC Encoding Algorithms                                        |       |

| 7.2  | .3.   | Attack Model                                                               |       |

| 7.3. | SE    | CCURITY VULNERABILITY OF THE EXISTING WORK                                 | 141   |

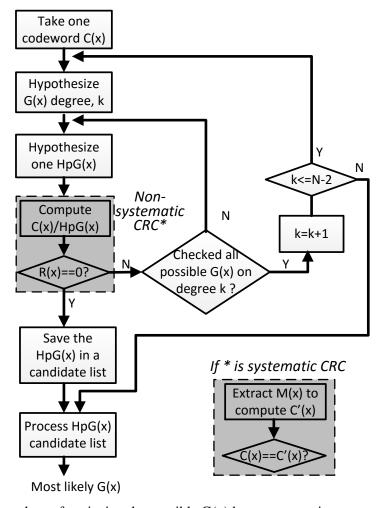

| 7.3  |       | Theoretical Analysis                                                       |       |

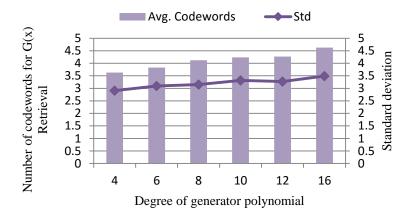

| 7.3  |       | Number of Codewords Needed for G(x) Retrieval                              |       |

| 7.4. | PF    | ROPOSED DYNAMIC POLYNOMIAL ALTERNATION METHOD                              | 146   |

| 7.4  |       | Method Overview                                                            |       |

| 7.4  | .2.   | Selection of Multiple Generator Polynomials                                | 150   |

| <b>7.5.</b> | DEPENDENT FACTORS OF PROPOSED METHOD AGAINST REVERSE                    |     |

|-------------|-------------------------------------------------------------------------|-----|

| ENGI        | NEERING ATTACK                                                          | 152 |

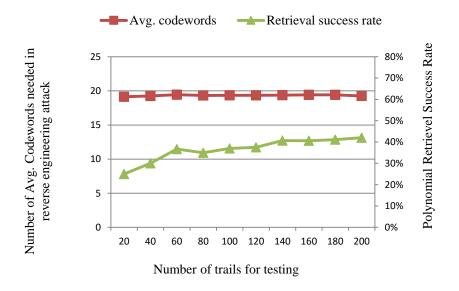

| 7.5.1       | Number of Trails in G(x) Examination                                    | 152 |

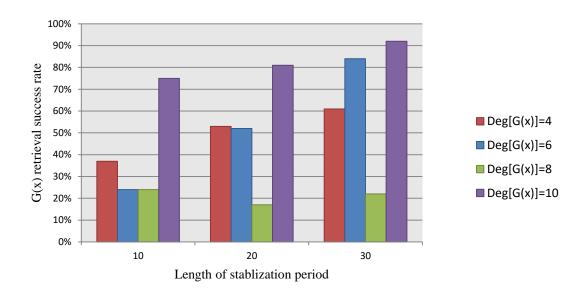

| 7.5.2       | 2. Stabilization Period                                                 | 153 |

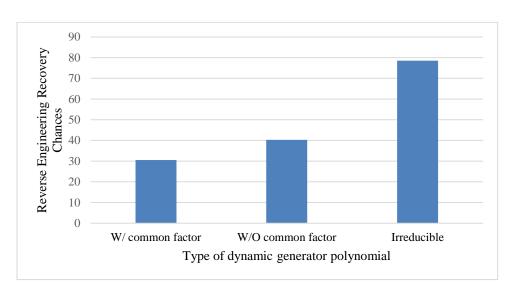

| 7.5.3       | 3. Combination of Different Irreducible Polynomials                     | 154 |

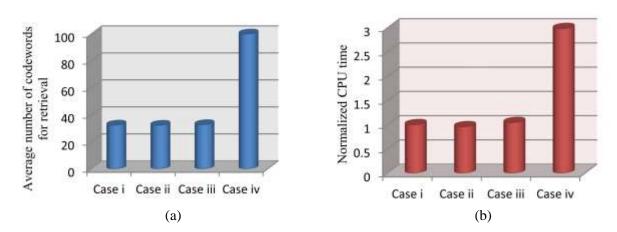

| 7.5.4       | •                                                                       |     |

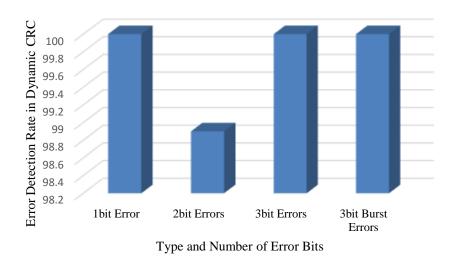

| 7.6.        | ERROR DETECTION RATE OF THE PROPOSED DYNAMIC CRC                        | 157 |

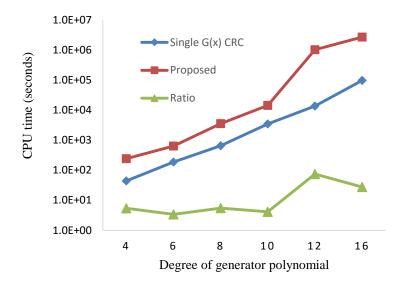

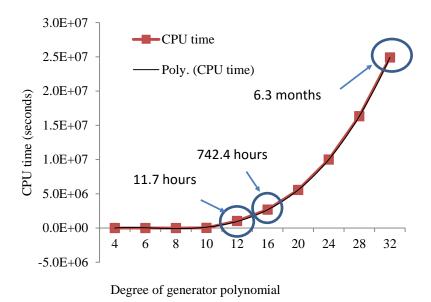

| 7.7.        | TIME COST AND HARDWARE OVERHEAD                                         | 159 |

| 7.7.1       | 1. Time Cost                                                            | 159 |

| 7.7.2       | 2. Hardware Cost Comparison                                             | 160 |

| 7.8.        | CONCLUSION                                                              | 161 |

| СНАР        | TER 8. CONCLUSION AND FUTURE WORK                                       | 162 |

| 8.1.        | Error Latching Probability Assessment by a Systematic Analyses Method   | 162 |

| 8.2.        | CPA Resistance Assessment of AES with Different Fault Detection methods | 163 |

| 8.3.        | Dynamic CRC to Thwart Reliability and Security Vulnerability            | 164 |

| REFE        | RENCES                                                                  | 166 |

#### **List of Tables**

| Table 3. 1 Accuracy of proposed model                                                                     | 61  |

|-----------------------------------------------------------------------------------------------------------|-----|

| Table 3. 2 Probability of no logical masking                                                              | 63  |

| Table 3. 3 Accuracy of proposed model                                                                     | 64  |

| Table 4. 1 Latching probabilities for the multiple-cycle SETs leading to different soft error categories. | 80  |

| Table 6. 1 Hardware cost of hardware-redundancy based FDs.                                                | 120 |

| Table 6. 2 Hardware cost of CRC based fault detection methods                                             | 124 |

| Table 6. 3 Hardware cost of s-box implementation in FPGA                                                  | 125 |

| Table 6. 4 Hardware cost mixcolumns DMR FD with different FDs for S-Box                                   | 129 |

| Table 6. 5 FPGA cost for different countermeasures.                                                       | 135 |

| Table 7. 1 Symbols Used in This Work                                                                      | 139 |

| Table 7. 2 A presentation of extracting the check bits for reverse engineering.                           | 141 |

| Table 7. 3 Retrieval of reducible G(x) using brute-force method.                                          | 143 |

| Table 7. 4 Retrieval of irreducible G(x) using brute-force method                                         | 144 |

| Table 7. 5 G(x) Retrieval Process for the Proposed Multiple Polynomials through four codewords            | 152 |

#### **List of Figures**

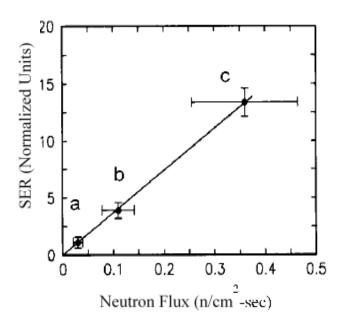

| Fig. 1. 1 The cosmic ray component of the SER as a function of altitude (a) Durham NH (Sea level), (l        | b)   |

|--------------------------------------------------------------------------------------------------------------|------|

| Boulder CO (1.6 km), (c) Leadville CO (3.1 km)                                                               |      |

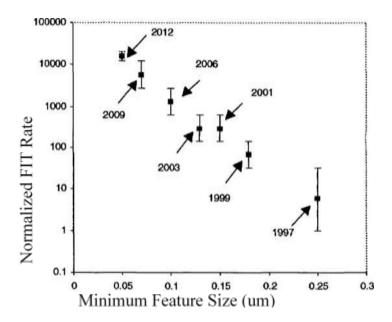

| Fig. 1. 2 Scaling trend for the FIT/Mbit of SRAM and dynamic logic arrays, predicted in 1999                 |      |

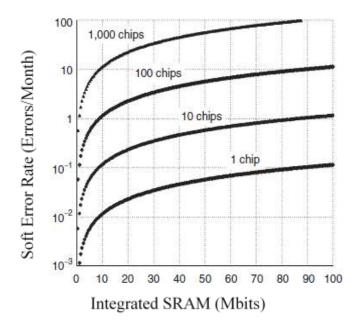

| Fig. 1. 3 Monthly system soft-error rate as a function of the number of chips in the system and the amount   |      |

| of embedded SRAM per chip                                                                                    |      |

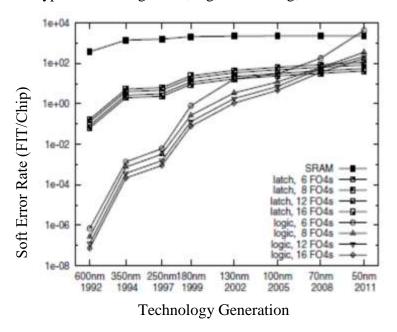

| Fig. 1. 4 SER of individual circuits                                                                         |      |

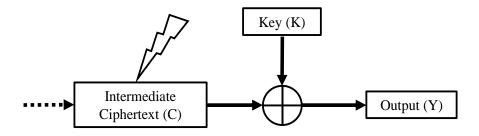

| Fig. 1. 5 Fault attack on the intermediate ciphertext of a cryptographic algorithm.                          |      |

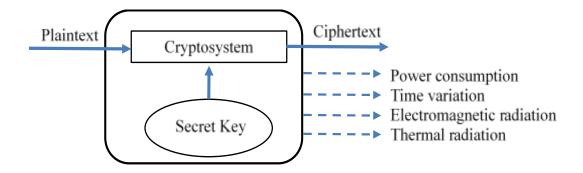

| Fig. 1. 6 Block cipher implementation with secondary outputs                                                 |      |

| Fig. 1. 7 Power trace related to the 10 rounds of AES-128 encryption operation [26]                          |      |

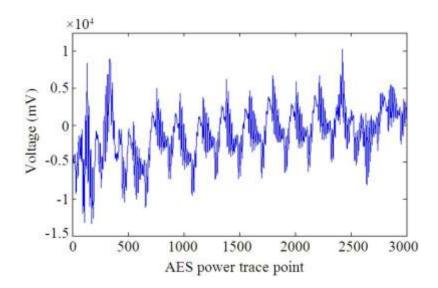

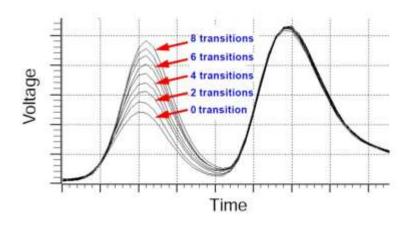

| Fig. 1. 8 Variations in voltage due to bit transitions [25].                                                 |      |

| Fig. 1. 9 Laser fault injection equipment [13]                                                               |      |

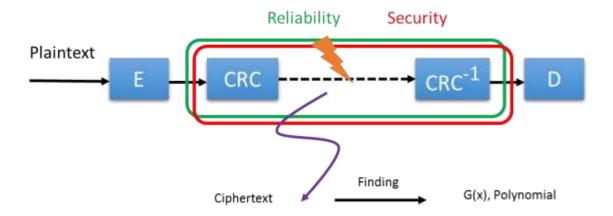

| Fig. 1. 10 Security threat in a unified countermeasure.                                                      |      |

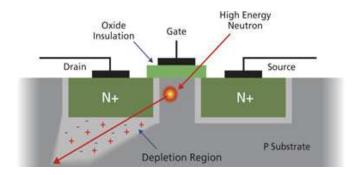

| Fig. 2. 1 High energy charged particle hitting the substrate of an NMOS                                      |      |

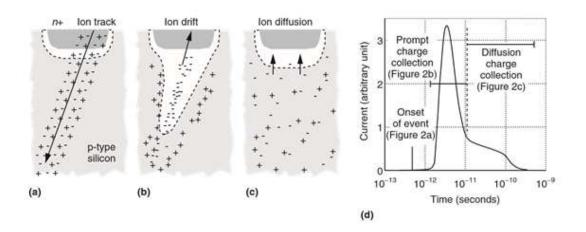

| Fig. 2. 2 Three stages of the soft error mechanism: (a) ionization, (b) funneling, (c) diffusion, and (d) to |      |

| corresponding current pulse [6].                                                                             |      |

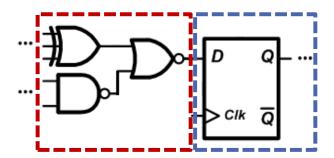

| Fig. 2. 3 Soft errors striking the combinational logic (on the left) or the memory element (on the right)    | . 33 |

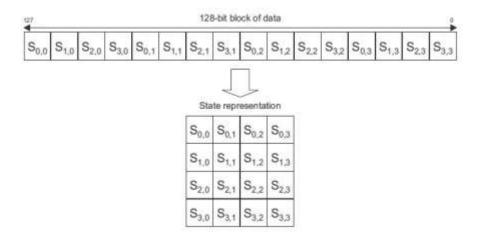

| Fig. 2. 4 State representation of 128-bit data blocks [85].                                                  |      |

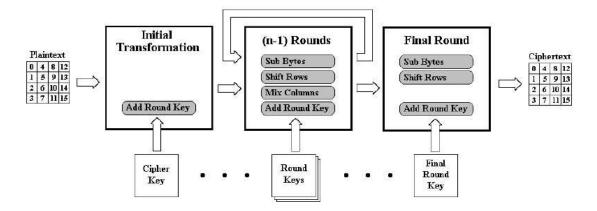

| Fig. 2. 5 AES Algorithm [86].                                                                                |      |

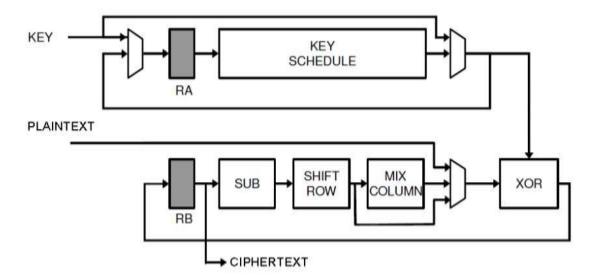

| Fig. 2. 6 AES implementation [32]                                                                            | 42   |

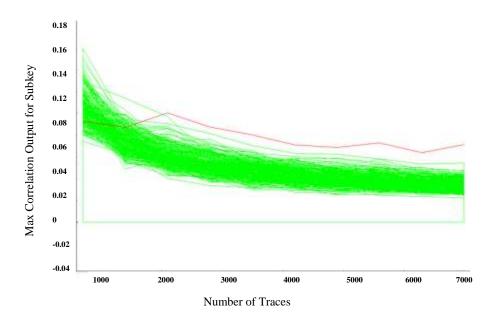

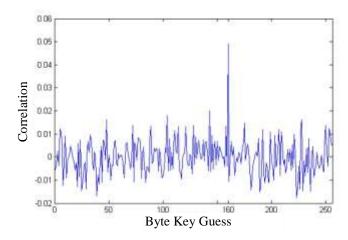

| Fig. 2. 7 The correlation coefficient versus the number of traces for one retrieved subkey                   | 44   |

| Fig. 2. 8 The correct subkey guess is found at the 160th guess in AES algorithm [29]                         | 44   |

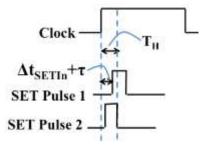

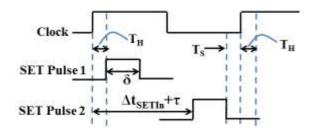

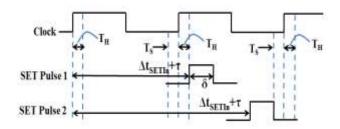

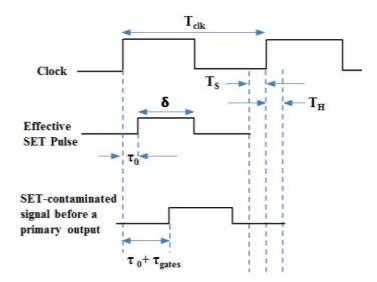

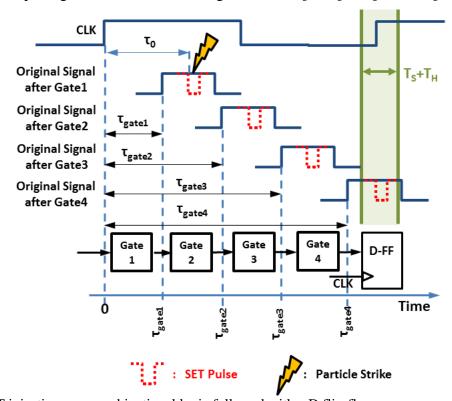

| Fig. 3. 1 General definitions for SET injection in this work                                                 | 52   |

| Fig. 3. 2 SET boundaries of the pulse latched by current cycle                                               | 52   |

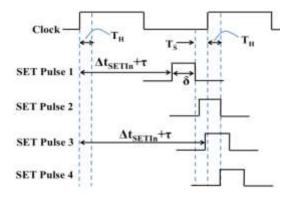

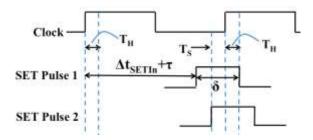

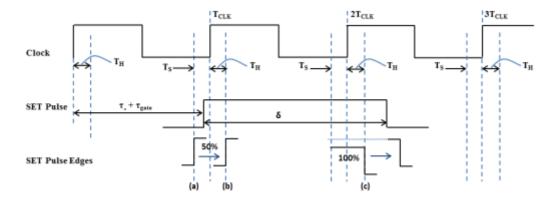

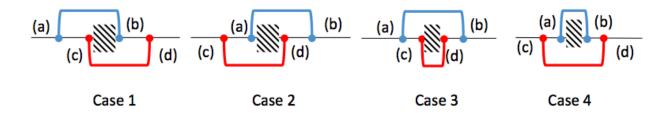

| Fig. 3. 3 Boundaries of SET pulse partially latched by next clock cycle                                      | 54   |

| Fig. 3. 4 Boundaries of SET pulse fully latched by next clock cycle                                          | 56   |

| Fig. 3. 5 SET pulse boundaries for silent error in the first clock cycle                                     | 56   |

| Fig. 3. 6 SET pulse boundaries for silent error in the second clock cycle                                    |      |

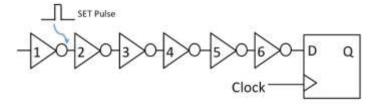

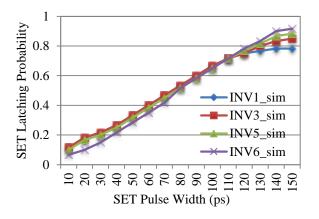

| Fig. 3. 7 Inverter chain followed with a D flip-flop.                                                        | 59   |

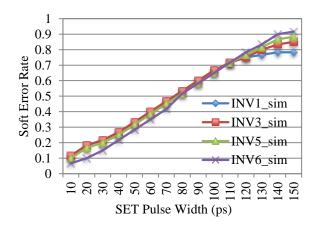

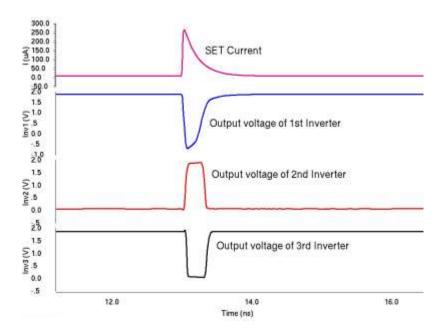

| Fig. 3. 8 Simulated soft error rate for the inverter chain.                                                  |      |

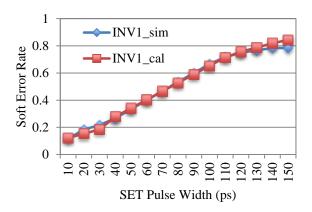

| Fig. 3. 9 Comparison of simulated and derived soft error rates for the inverter 1 in Fig. 7.3                |      |

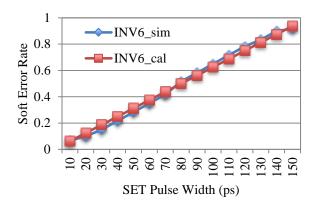

| Fig. 3. 10 Comparison of simulated and derived soft error rates for the inverter 6 in Fig. 7.3               |      |

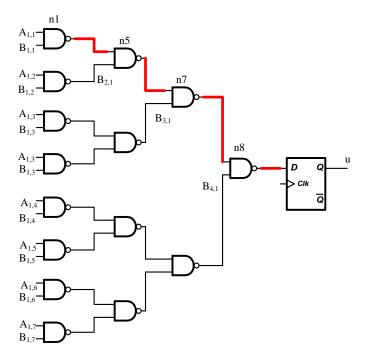

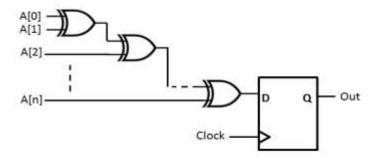

| Fig. 3. 11 A NAND gate network.                                                                              |      |

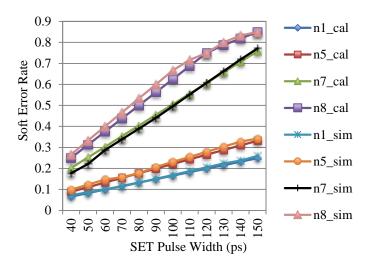

| Fig. 3. 12 Soft error rate comparison between the proposed soft error model and simulation results for       |      |

| NAND network.                                                                                                |      |

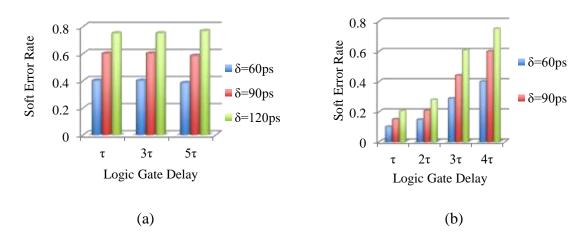

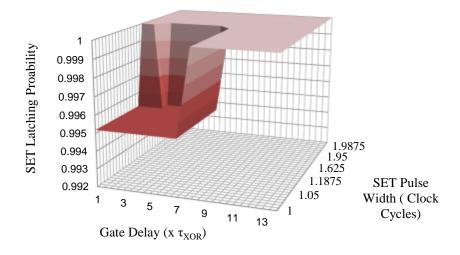

| Fig. 3. 13 Impact of logic gate delay and pulse width on soft error of the circuits. (a) Inverter chain      |      |

| (without logical masking). (b) NAND network (with logical masking).                                          | 65   |

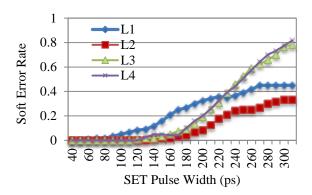

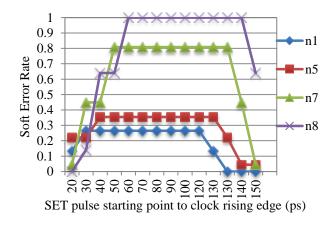

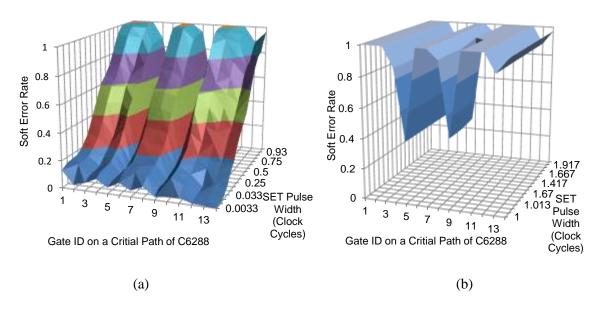

| Fig. 3. 14 Impact of SET pulse width and SET injection location on soft error rate for an ITC'99             |      |

| benchmark circuit, b02.                                                                                      | 66   |

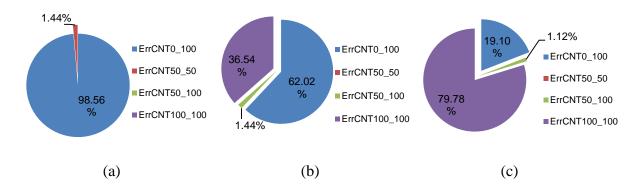

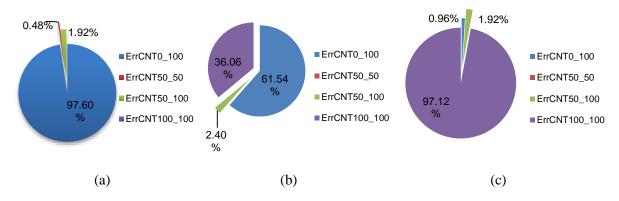

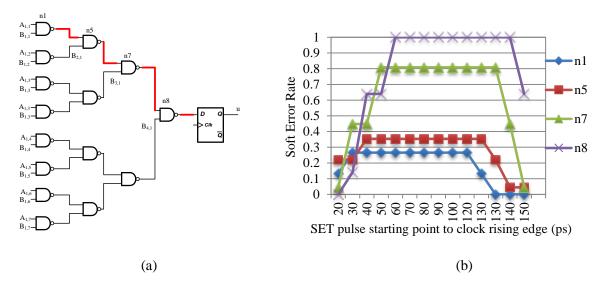

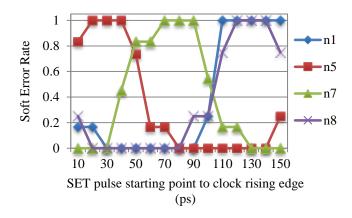

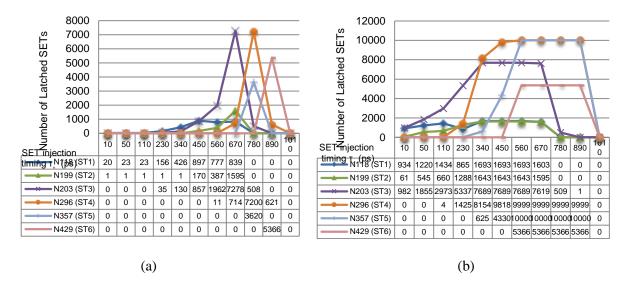

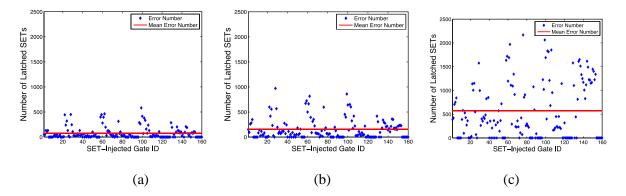

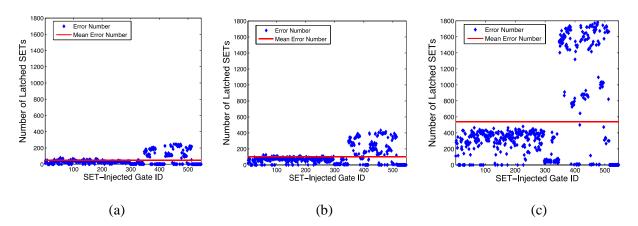

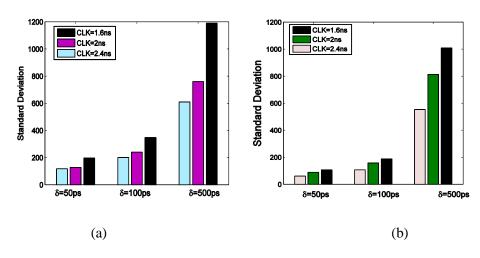

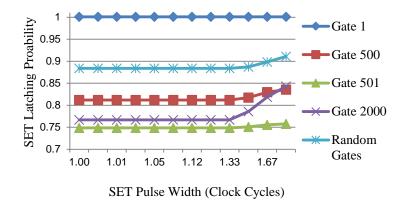

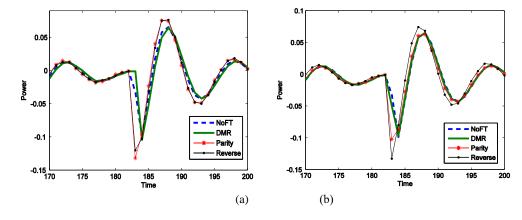

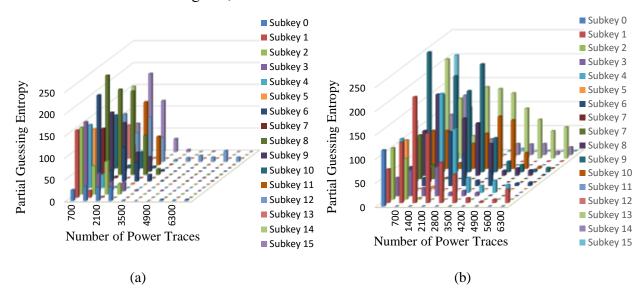

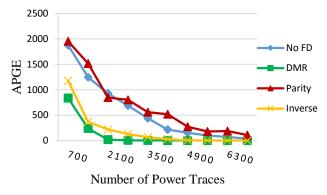

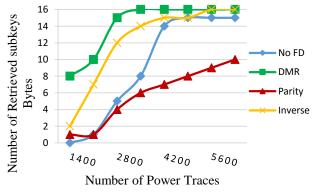

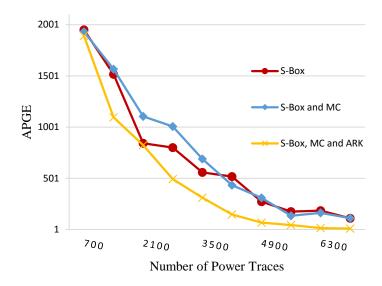

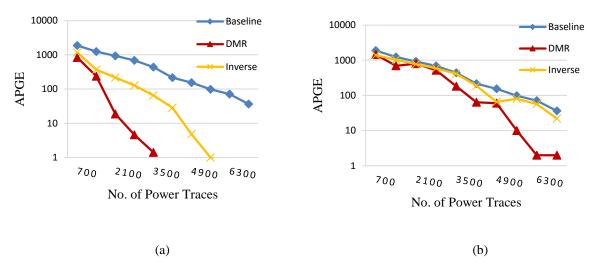

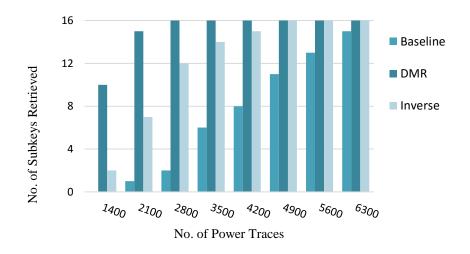

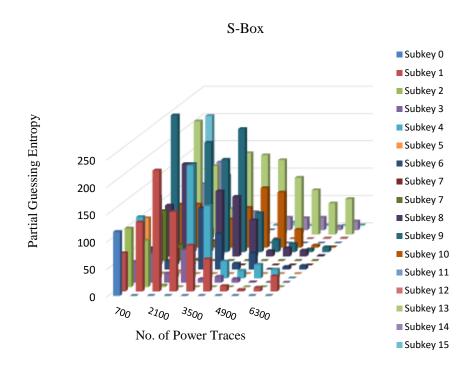

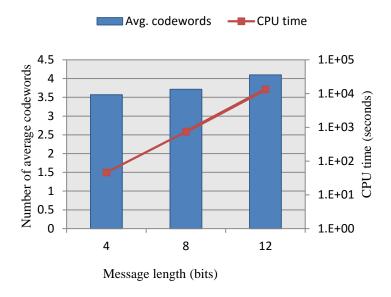

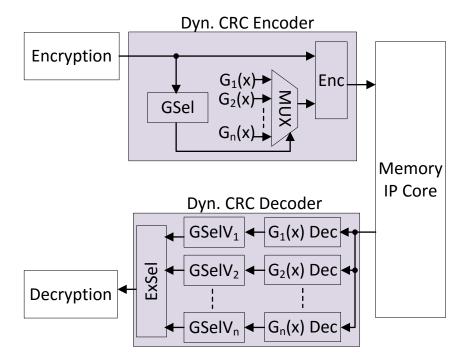

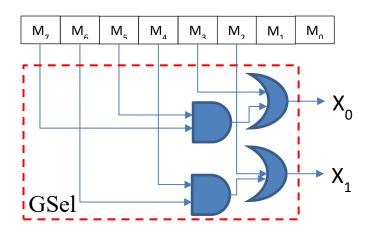

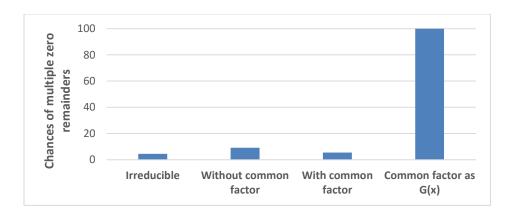

| Fig. 3. 15 Impact of SET pulse injection timing on soft error rate of NAND network                           |      |