## University of New Hampshire University of New Hampshire Scholars' Repository

Master's Theses and Capstones

Student Scholarship

Winter 2007

# Prototype mixed-signal hardware for public safety radio interoperability

Timothy Edwood Bond University of New Hampshire, Durham

Follow this and additional works at: https://scholars.unh.edu/thesis

#### **Recommended** Citation

Bond, Timothy Edwood, "Prototype mixed-signal hardware for public safety radio interoperability" (2007). *Master's Theses and Capstones*. 323. https://scholars.unh.edu/thesis/323

This Thesis is brought to you for free and open access by the Student Scholarship at University of New Hampshire Scholars' Repository. It has been accepted for inclusion in Master's Theses and Capstones by an authorized administrator of University of New Hampshire Scholars' Repository. For more information, please contact nicole.hentz@unh.edu.

## **PROTOTYPE MIXED-SIGNAL HARDWARE**

## FOR

## PUBLIC SAFETY RADIO INTEROPERABILITY

BY

## TIMOTHY EDWOOD BOND

BSEE, University of New Hampshire, 2005

#### THESIS

Submitted to the University of New Hampshire

in Partial Fulfillment of

the Requirements for the Degree of

Master of Science

in

Electrical & Computer Engineering

December, 2007

UMI Number: 1449578

#### UMI Microform 1449578

Copyright 2008 by ProQuest Information and Learning Company. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

This thesis has been examined and approved.

e k

Thesis Director, Andrew L. Kun, Assistant Professor of Electrical Engineering

WERNS

W. Thomas Miller, III, Professor of Electrical Engineering

William H. Lenharth, Research Associate Professor of Electrical Engineering

12/12/57

Date

# **DEDICATION**

This thesis is dedicated to my mother for her consistent love, help, and support throughout all levels of my life and education.

"... that in all things he [Christ] might have the preeminence."

-

Colossians 1:18

"... whatsoever ye do, do all to the glory of God"

- I Corinthians 10:31

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

## **ACKNOWLEDGEMENTS**

I would first like to thank my thesis advisor, Dr. Andrew L. Kun, for the time he has devoted to helping me with this project and the guidance he has provided in the writing of this thesis.

I also would like to express my gratitude to Dr. W. Thomas Miller, III and Dr. William Lenharth for the additional assistance that they have provided to me on the project and for serving on my thesis committee, offering both their time and ideas for its revision and completion.

I would also be remiss were I not to express my appreciation to the entire CATLab team for their assistance and collaboration during my time on this project.

Finally, I would like to thank my family and friends for their prayers and support while I have been at UNH.

# **TABLE OF CONTENTS**

| DEDICATION       | iii |

|------------------|-----|

| ACKNOWLEDGEMENTS | iv  |

| LIST OF TABLES   | Х   |

| LIST OF FIGURES  | xii |

| LIST OF ACRONYMS | xvi |

| ABSTRACT         | xix |

### CHAPTER

-

#### PAGE

| I.  | INTRODUCTION                                             | 1   |

|-----|----------------------------------------------------------|-----|

|     | CATLab - Project54 Overview                              | 1   |

|     | The Problem of System Gateways                           | 1   |

|     | Goals of the System Gateway Interoperability Solution    | 4   |

|     | Mixed-Signal Hardware Audio Baseband Switch Approach     | 8   |

| II. | BACKGROUND                                               | .13 |

|     | Public Safety Radio Interoperability and the Need for it | 13  |

|     | Some Current Interoperability Solutions and Shortcomings | .15 |

|     | Common Radio Systems                                     | 15  |

|     | Commercial Services                                      | .18 |

|     | Software Defined Radio                                   | 19  |

|      | The System Gateway Approach                             | 23 |

|------|---------------------------------------------------------|----|

|      | Audio Baseband Switch                                   | 23 |

|      | Voice-Over-IP                                           | 25 |

|      | Software Defined Radio as a System Gateway Patch        | 26 |

| III. | SYSTSEM HARDWARE DESIGN                                 | 29 |

|      | System Hardware Elements                                | 29 |

|      | The In-Car Microphone                                   |    |

|      | The Radios                                              |    |

| IV.  | ANALOG AND SWITCH MATRIX HARDWARE DESIGN                | 34 |

|      | Introduction to the Analog Prototype Hardware Design    | 34 |

|      | Differential Audio Speaker Inputs                       | 37 |

|      | Meeting Audio Summers and Input Switch Matrix           | 40 |

|      | Microphone Input Buffers                                | 44 |

|      | Output Audio Buffers and Output Switch Matrix           | 45 |

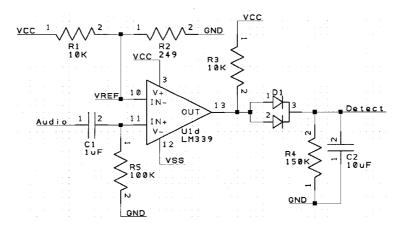

|      | Push-to-Talk Signal Detection                           | 47 |

|      | Robust System Design Constraint and the Shutdown Relays | 51 |

|      | Power Circuits and Voltage Supplies                     | 54 |

| V.   | DIGITAL PTT MAPPING AND SWITCH CONTROL                  | 57 |

|      | Overview of PTT Signals and Their Origins               |    |

|      | Discrete Logic versus a CPLD                            | 58 |

|      | CPLD Digital Logic PTT Mapping Implementation           | 59 |

| VI.  | DIGITAL CONTROL HARDWARE & FIRMWARE                     | 64 |

|      | The Main Digital Control Hardware                       | 64 |

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

| The Embedded Microcontroller65                                        |

|-----------------------------------------------------------------------|

| Usage of a Microcontroller65                                          |

| Introduction to the 8051 Microcontroller Family                       |

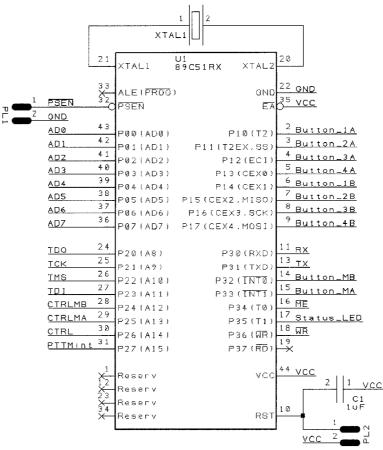

| AT89C51RC2 Microcontroller Connections                                |

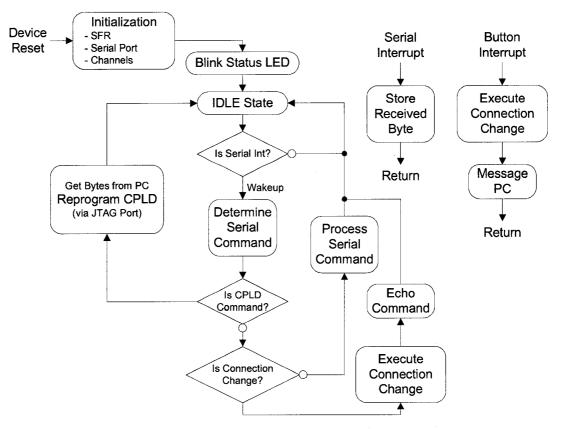

| General MCS51 Firmware Implementation Overview69                      |

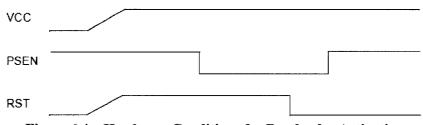

| Bootloader for In-System Programming Flexibility72                    |

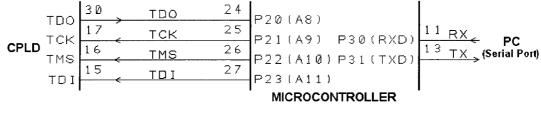

| JTAG Interface Programming of the CPLD76                              |

| TAP Interface and the JTAG Protocol76                                 |

| XSVF versus SVF Programming Files77                                   |

| Microcontroller Based JTAG Programming80                              |

| Control Signal Buffering85                                            |

| VII. MIXED-SIGNAL PCB DESIGN CONSIDERATIONS                           |

| Prototype PCB Layout                                                  |

| Revision A Power Supply Noise and Heat Dissipation                    |

| Revision B Digital Interference and Crosstalk with the Analog Audio95 |

| Field Programmable Analog Arrays105                                   |

| Final Version PCB Layout Improvements106                              |

| VIII. DEVICE OPERATION & USER INTERFACES109                           |

| General Operation Overview109                                         |

| Manual Control Head User Interface110                                 |

| Remote/Software User Interface114                                     |

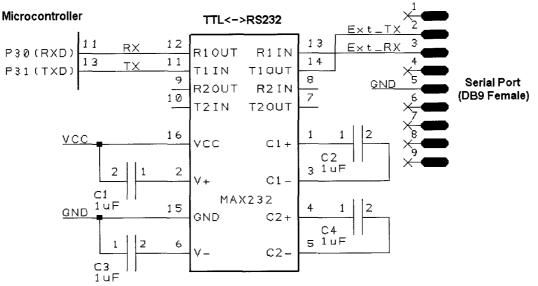

| RS232 Serial Communications Port114                                   |

| Serial Commands & Responses117                                        |

|     | Hardware Command Feedback                       | 120 |

|-----|-------------------------------------------------|-----|

|     | Interaction with a P54 Control Application      | 121 |

| IX. | PROTOTYPE DESIGN ANALYSIS                       | 125 |

|     | Performance Summary & Specifications            | 125 |

|     | Power Supply Specifications                     |     |

|     | Device Connection Specifications                |     |

| •   | Channel Speaker Input Screw Terminals           | 128 |

|     | Main System Microphone Screw Terminals          | 129 |

|     | Main System Microphone Rotary Switch Connectors | 129 |

|     | Channel Output Screw Terminals                  | 130 |

|     | Power Connectors                                | 130 |

|     | Button Connections                              | 131 |

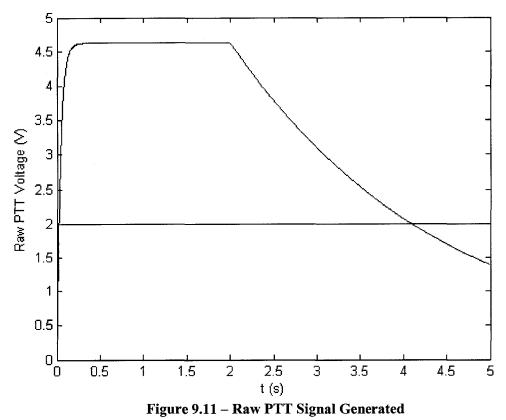

|     | LED Connections                                 | 132 |

|     | Reset and Programming Headers                   | 132 |

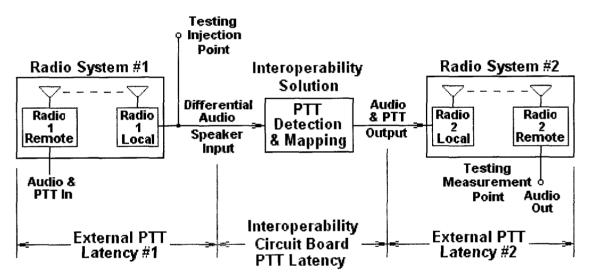

|     | Audio Signal & PTT Generation Latency           | 133 |

|     | The Latencies & Their Effects                   | 133 |

|     | Varying the PTT Generation Parameters           | 135 |

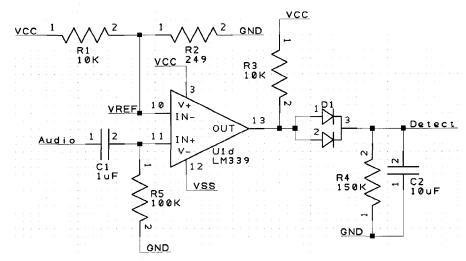

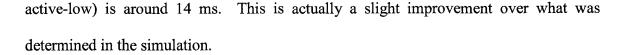

|     | PTT Generation Circuit Test                     | 140 |

|     | Connection and Signal Level Issues              |     |

|     | Future Design Ideas and Enhancements            |     |

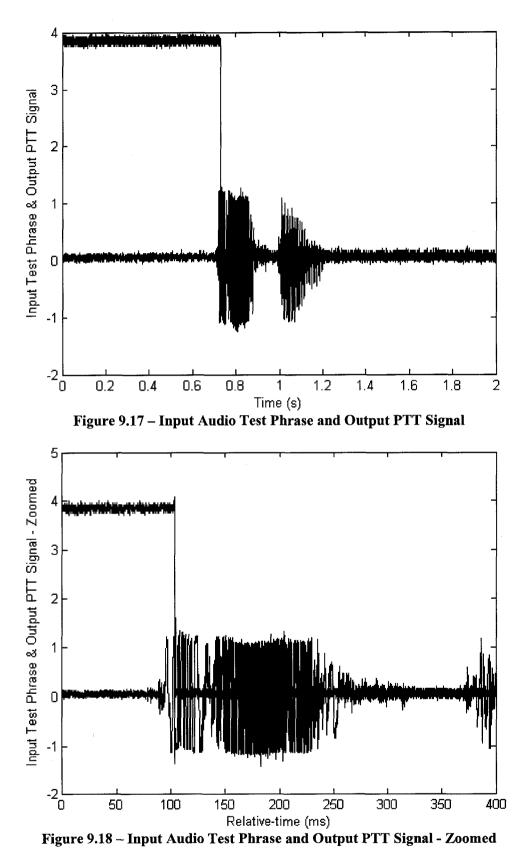

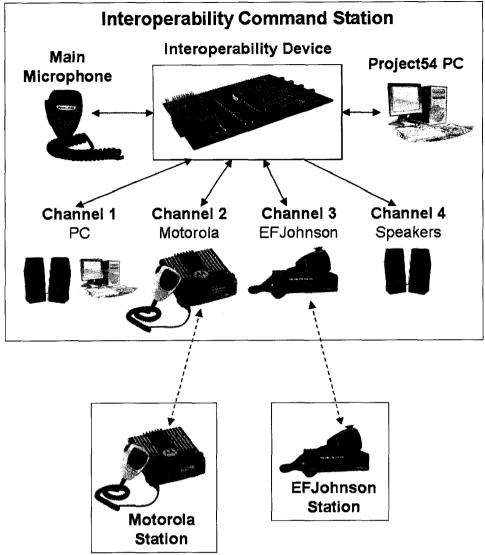

| X.  | SYSTEM MOCKUP TESTING                           | 150 |

|     | The Setup of the Test                           | 150 |

|     | Test Scenarios                                  |     |

| PTT Latency Problems                                 | 155 |

|------------------------------------------------------|-----|

| XI. CONCLUSION                                       | 161 |

| REFERENCES                                           | 163 |

| APPENDICES                                           | 170 |

| APPENDIX A - XILINX CPLD VHDL CODE                   | 171 |

| APPENDIX B - MICROCONTROLLER FIRMWARE BOOTLOADER     | 176 |

| APPENDIX C - MCS51 ASSEMBLY FIRMWARE                 | 178 |

| APPENDIX D - CPLD JTAG PROGRAMMING                   |     |

| APPENDIX E – REVISION C PCB DESIGN INFORMATION       |     |

| APPENDIX F – PTT SIMULATION & TESTING MATLAB SCRIPTS | 193 |

| APPENDIX G – DEMONSTRATION OF THE MOCKUP TESTING     | 196 |

# LIST OF TABLES

| Table 4.1 – Original Supply Current Estimates                         | 55  |

|-----------------------------------------------------------------------|-----|

| Table 6.1 - UART Communications Port Settings                         | 74  |

| Table 6.2 - Intel HEX Frame Format                                    | 75  |

| Table 6.3 – XSVF Command Set and Design Support                       | 84  |

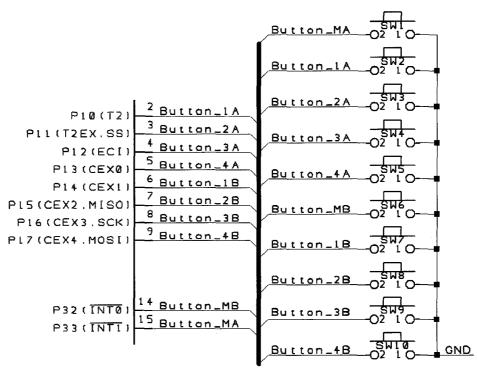

| Table 8.1 - Button Port Pin Channel-Meeting Assignments               | 113 |

| Table 8.2 - Communications Port Settings                              | 116 |

| Table 8.3 – Available Serial Port Commands                            | 117 |

| Table 8.4 – Serial Port Responses                                     | 119 |

| Table 9.1 – Power Supply Voltage Specifications                       | 126 |

| Table 9.2 – Power Supply Current Specifications                       | 127 |

| Table 9.3 – MATLab Simulation Circuit Parameters                      | 136 |

| Table 10.1 – EFJohnson DB15 Harness Connections                       | 152 |

| Table 10.2 – Interoperability Circuit Board Harness Connections       | 152 |

| Table 10.3 – Motorola DB25 Harness Connections                        | 153 |

| Table 10.4 – Test Scenario Results                                    | 154 |

| Table 10.5 – Interoperability Circuit Board & External #2 PTT Latency | 158 |

| Table C.1 – MCS51 Assembly MRCM Code Folder File Contents             | 178 |

| Table C.2 – XSVF Assembly Code Folder File Contents                   | 180 |

| Table E.1 - Easy-PC Design File Contents.                             | 186 |

| Table E.2 – Revision C Basic Parts List                               | 188 |

| Table E.3 - Revision C Detailed Part | ts Identification List |  |

|--------------------------------------|------------------------|--|

| Table F.1 – Mockup Testing Script    |                        |  |

# **LIST OF FIGURES**

| Figure 1.1 – Lack of Radio Interoperability in Public Safety          | 2  |

|-----------------------------------------------------------------------|----|

| Figure 1.2 – Four Radio Interoperability Mega-System Block Diagram    | 4  |

| Figure 1.3 – Interoperability Device Diagram                          | 9  |

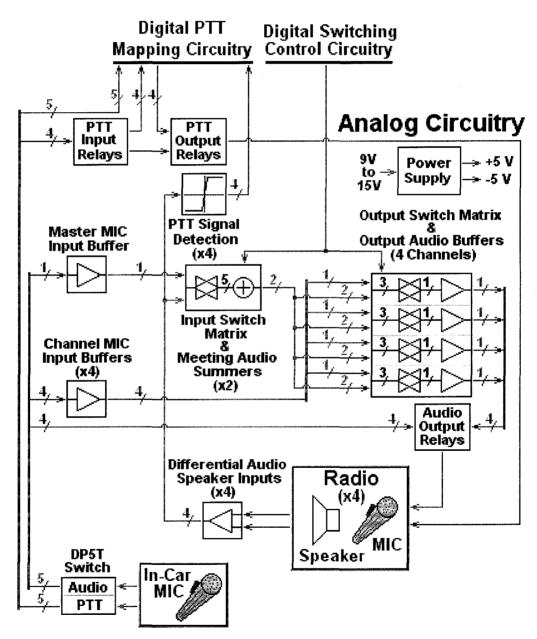

| Figure 3.1 – System Hardware Block Diagram                            | 30 |

| Figure 4.1 – Analog Hardware Block Diagram                            | 35 |

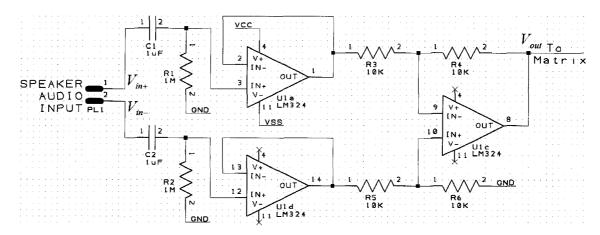

| Figure 4.2 – Differential Audio Speaker Input Circuit                 | 38 |

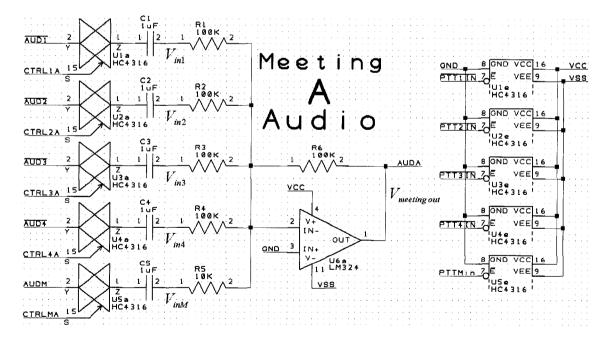

| Figure 4.3 – Input Switch Matrix and Inverting Meeting Summer Circuit | 40 |

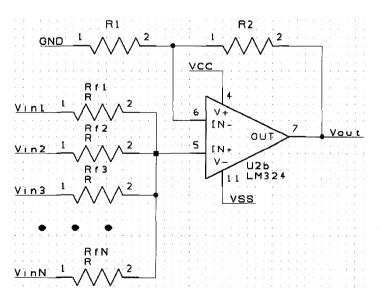

| Figure 4.4 – Rejected Non-Inverting Summer Circuit                    | 43 |

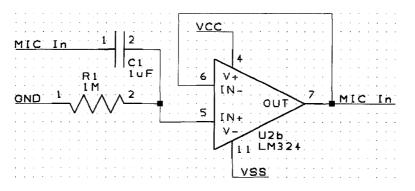

| Figure 4.5 – Microphone Input Buffer Circuit                          | 45 |

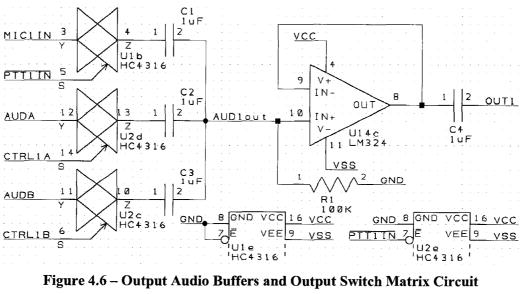

| Figure 4.6 – Output Audio Buffers and Output Switch Matrix Circuit    | 45 |

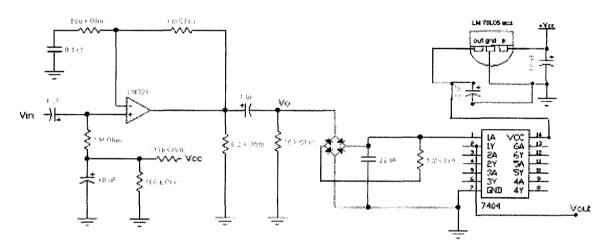

| Figure 4.7 – John Mock's PTT Generation Circuit                       | 48 |

| Figure 4.8 – Modified PTT Signal Generation Circuit                   | 49 |

| Figure 4.9 – Shutdown Relays for System Bypassing                     | 52 |

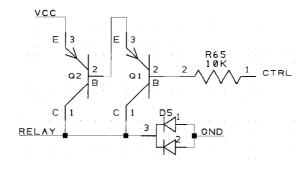

| Figure 4.10 – Shutdown Relays' Control Drive Circuitry                | 53 |

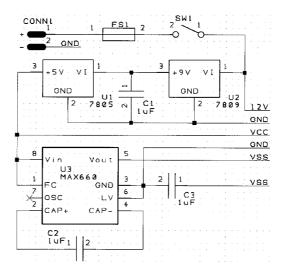

| Figure 4.11 – Power Supply Circuitry                                  | 54 |

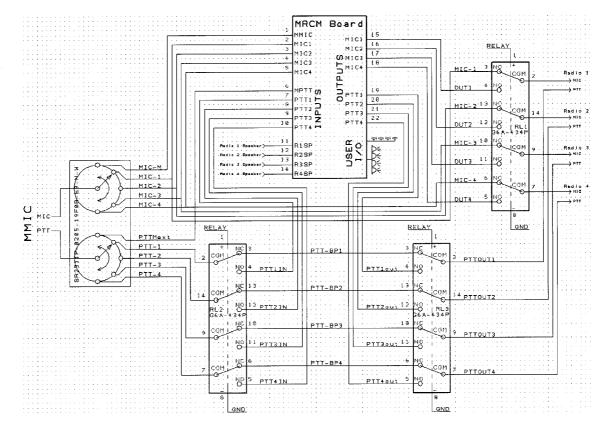

| Figure 5.1 – CPLD Pin-out Circuit Diagram                             | 62 |

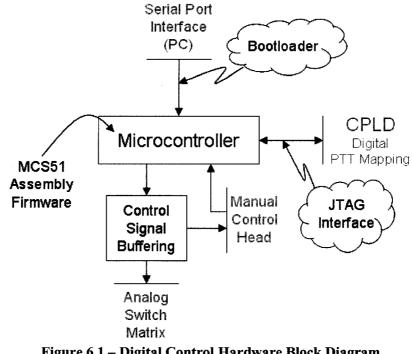

| Figure 6.1 – Digital Control Hardware Block Diagram                   | 64 |

| Figure 6.2 – Microcontroller Pin Connection Diagram                   | 69 |

| Figure 6.3 – Block Diagram of Microcontroller Firmware                | 70 |

| Figure 6.4 – Hardware Conditions for Bootloader Activation            | 73 |

| Figure 6.5 – Sample Portion of an SVF File78                          | 8 |

|-----------------------------------------------------------------------|---|

| Figure 6.6 – Sample Portion of an XSVF File78                         | 8 |

| Figure 6.7 – Sample Portion of an ASCII Readable XSVF File            | ) |

| Figure 6.8 – Required Hardware Interfaces81                           | 1 |

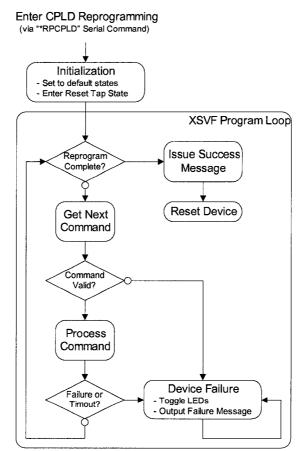

| Figure 6.9 – Block Diagram of Microcontroller JTAG Interface Firmware | L |

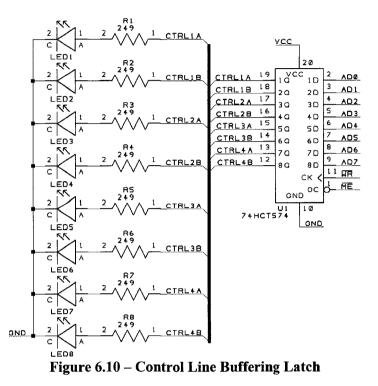

| Figure 6.10 – Control Line Buffering Latch                            | 6 |

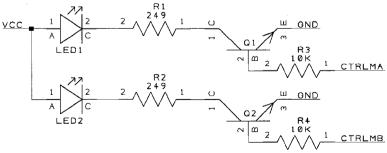

| Figure 6.11 – Master Microphone Control Line Buffering Transistors    | 6 |

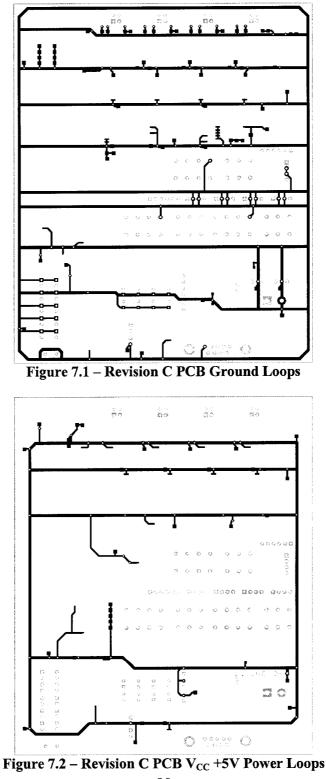

| Figure 7.1 – Revision C PCB Ground Loops90                            | ) |

| Figure 7.2 – Revision C PCB VCC +5V Power Loops90                     | 0 |

| Figure 7.3 – Revision C PCB VSS -5V Power Loops91                     | 1 |

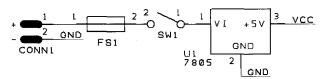

| Figure 7.4 – Original Revision A Power Supply Circuit93               | 3 |

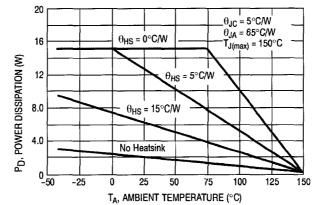

| Figure 7.5 – ON Semiconductor Worse Case Power Dissipation Curves     | 5 |

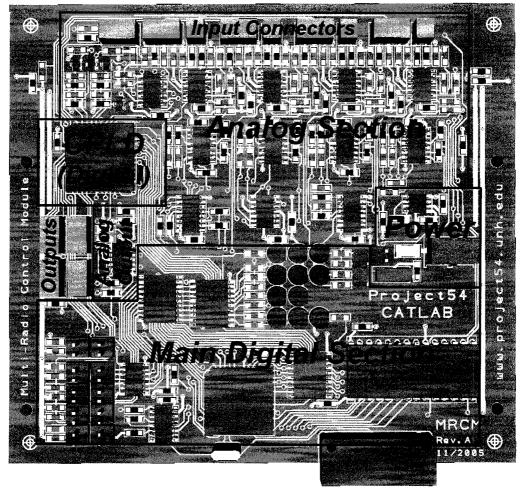

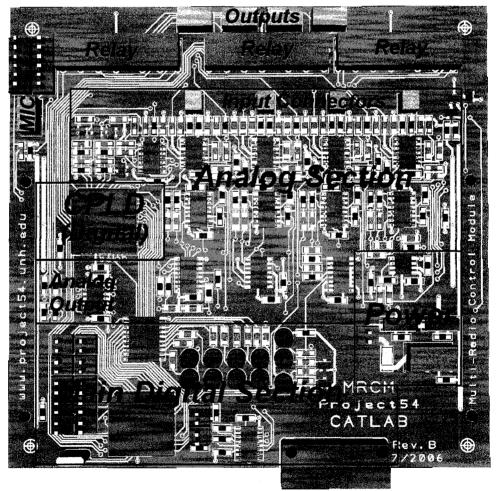

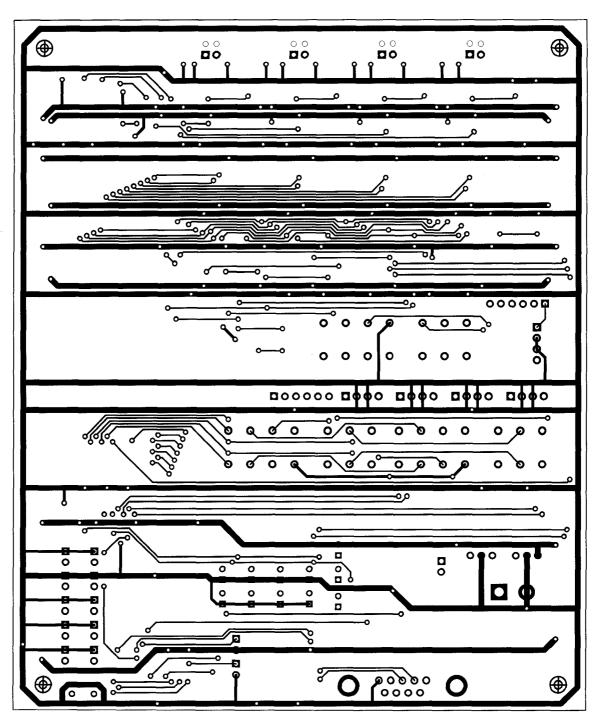

| Figure 7.6 – Revision A PCB Layout Image96                            | 5 |

| Figure 7.7 – Revision B PCB Layout Image97                            | 7 |

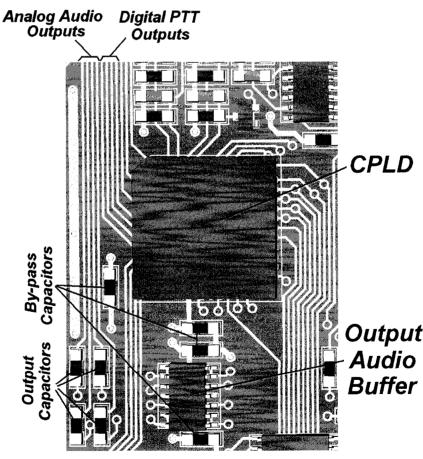

| Figure 7.8 – Zoomed in View of the Revision B PCB Layout Image        | 8 |

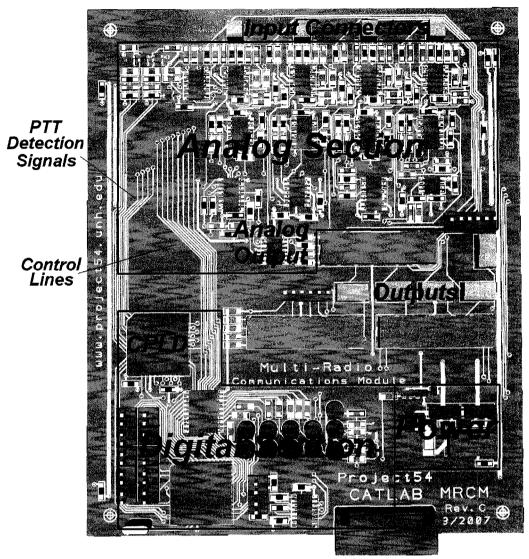

| Figure 7.9 – Revision C PCB Layout Image103                           | 3 |

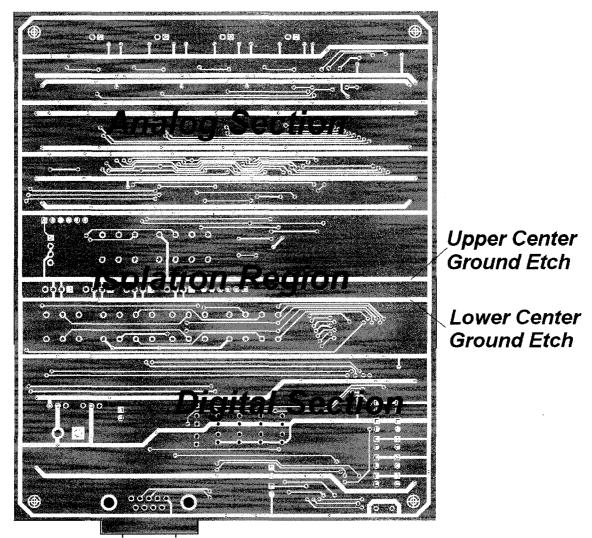

| Figure 7.10 – Revision C Bottom Side Ground Etch Division104          | 4 |

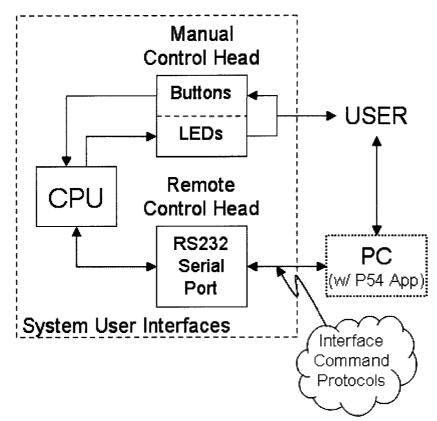

| Figure 8.1 – Block Diagram of the User Interfaces110                  | 0 |

| Figure 8.2 – Button Interface Circuit11                               | 1 |

| Figure 8.3 – Sample Button & LED Grid Layout112                       | 2 |

| Figure 8.4 – TTL to RS232 Conversion and Serial Port Circuit115       | 5 |

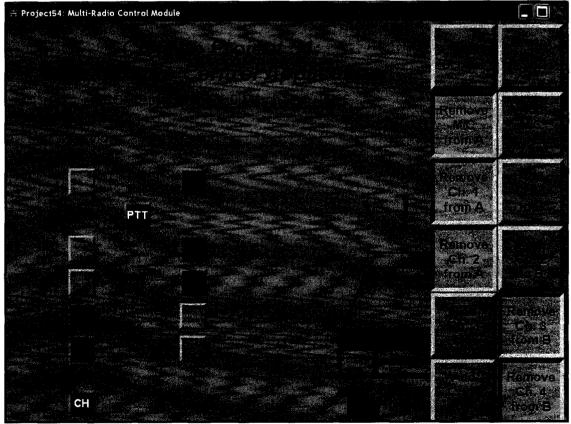

| Figure 8.5 – Test P54 Application for Device Control122               | 2 |

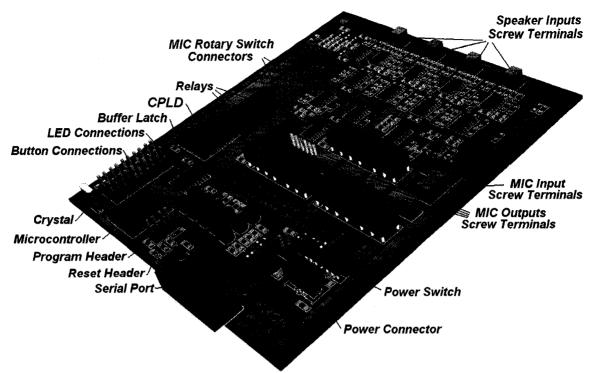

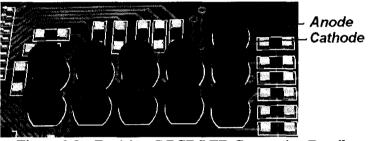

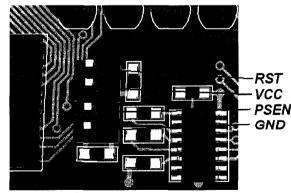

| Figure 9.1 – Crucial Elements of the Revision C PCB128                | 8 |

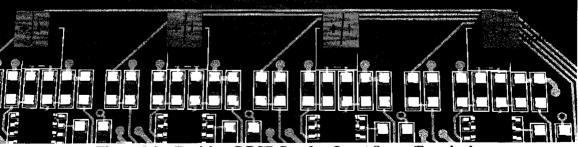

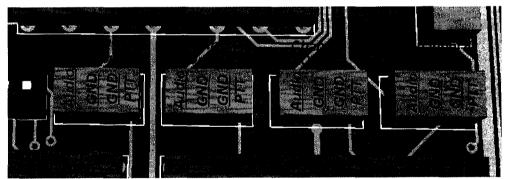

| Figure 9.2 – Revision C PCB Speaker Input Screw Terminals128                |

|-----------------------------------------------------------------------------|

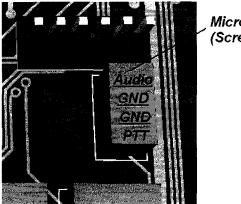

| Figure 9.3 – Revision C PCB System Microphone Connection129                 |

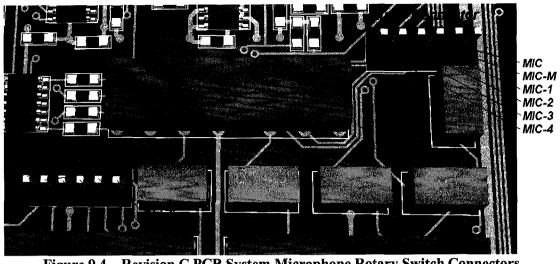

| Figure 9.4 – Revision C PCB System Microphone Rotary Switch Connectors130   |

| Figure 9.5 – Revision C PCB Channel Output Screw Terminals130               |

| Figure 9.6 – Revision C PCB Power Connections                               |

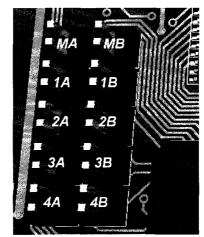

| Figure 9.7 – Revision C PCB Button Connection Details                       |

| Figure 9.8 – Revision C PCB LED Connection Details                          |

| Figure 9.9 – Revision C PCB Reset and Program Headers                       |

| Figure 9.10 – PTT Signal Generation Circuit                                 |

| Figure 9.11 – Raw PTT Signal Generated137                                   |

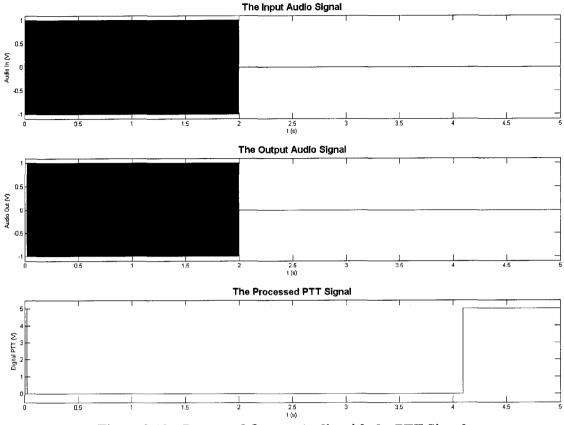

| Figure 9.12 – Input and Output Audio with the PTT Signal                    |

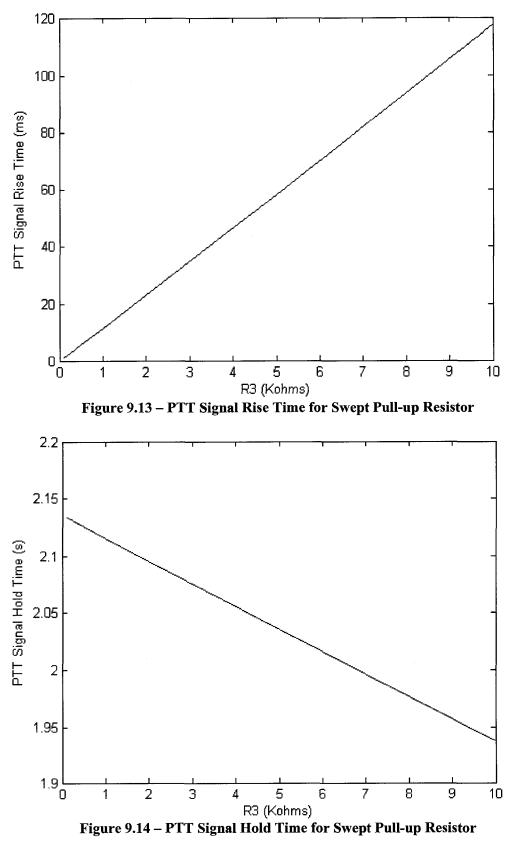

| Figure 9.13 – PTT Signal Rise Time for Swept Pull-up Resistor               |

| Figure 9.14 – PTT Signal Hold Time for Swept Pull-up Resistor139            |

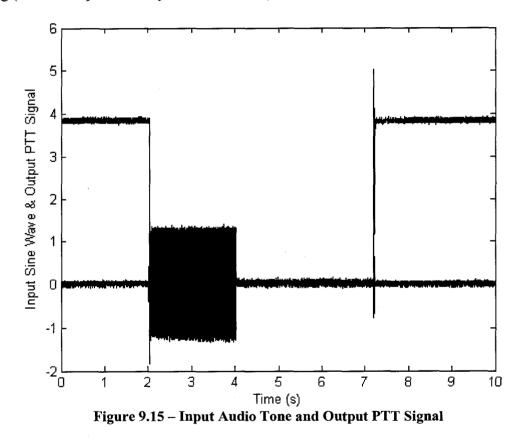

| Figure 9.15 – Input Audio Tone and Output PTT Signal140                     |

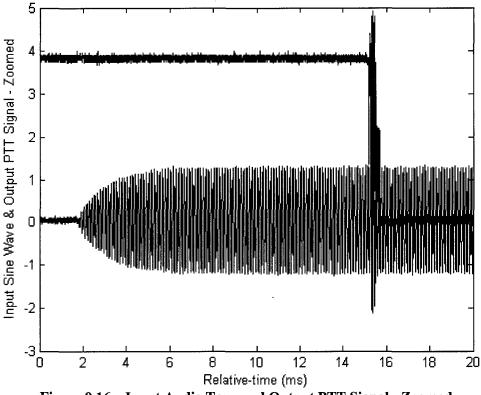

| Figure 9.16 – Input Audio Tone and Output PTT Signal - Zoomed141            |

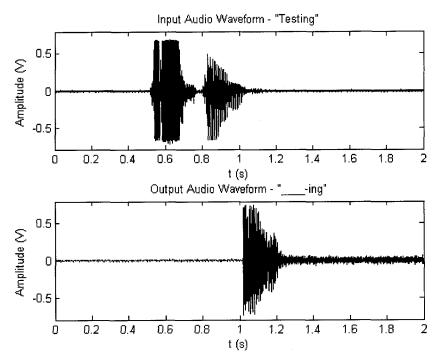

| Figure 9.17 – Input Audio Test Phrase and Output PTT Signal142              |

| Figure 9.18 – Input Audio Test Phrase and Output PTT Signal - Zoomed142     |

| Figure 10.1 – Block Diagram of the Mockup Testing System151                 |

| Figure 10.2 – Diagram of Potential PTT Latency Sources156                   |

| Figure 10.3 – Ninth Trial Input and Output Audio159                         |

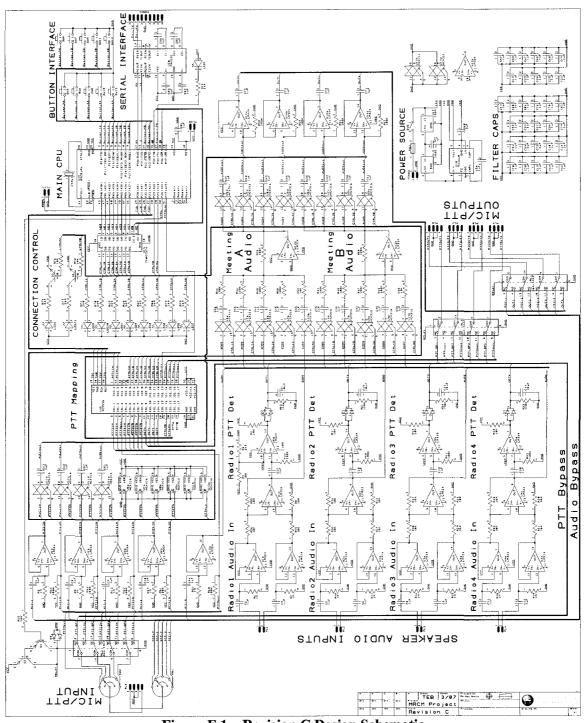

| Figure E.1 – Revision C Design Schematic                                    |

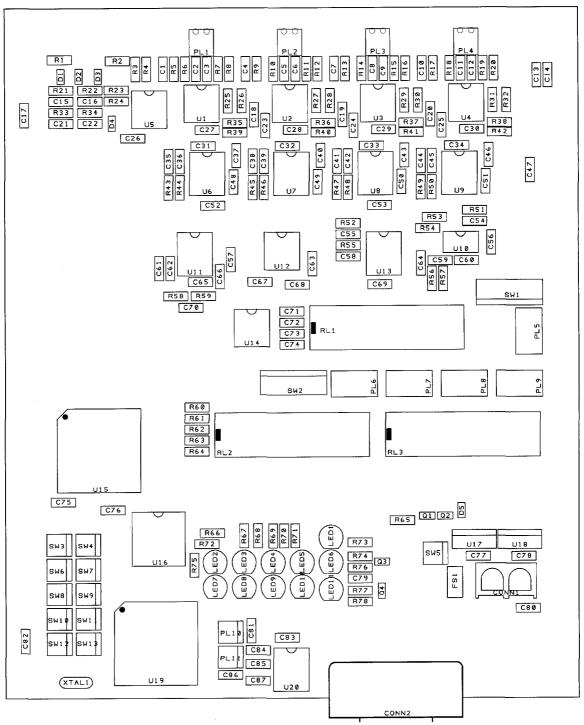

| Figure E.2 – Revision C Component Layout Diagram190                         |

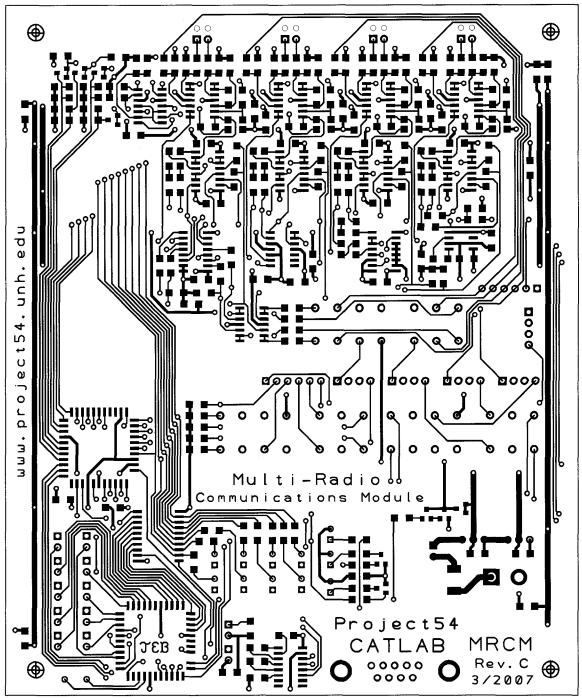

| Figure E.3 – Revision C PCB Top Copper Physical Layout (viewed from top)191 |

,

| Figure E.4 – Revision C PCB Bottom Copper Physical Layout (viewed from top) | 192 |

|-----------------------------------------------------------------------------|-----|

| Figure F.1 – Image of the Interoperability Device Operator Station          | 196 |

| Figure F.2 – Image of the EFJohnson Radio Operator Station                  | 197 |

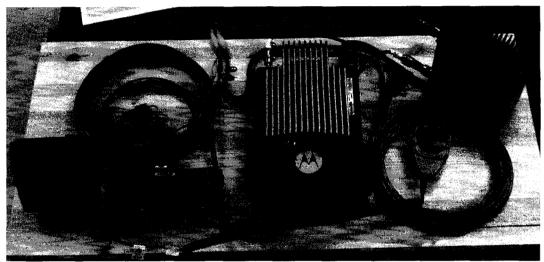

| Figure F.3 – Image of the Motorola Radio Operator Station                   | 197 |

# LIST OF ACRONYMS

| AC    | Alternating Current                                |

|-------|----------------------------------------------------|

| ADC   | Analog to Digital Converter                        |

| AGC   | Automatic Gain Control                             |

| APCO  | Association of Public Communications Officers      |

| ASCII | American Standard Code for Information Interchange |

| CAB   | Configurable Analog Block                          |

| CMOS  | Complementary Metal Oxide Semiconductor            |

| COTS  | Commercial Off-the-Shelf                           |

| CPLD  | Complex Programmable Logic Device                  |

| CPU   | Central Processing Unit                            |

| DC    | Direct Current                                     |

| DCE   | Data Circuit Terminating Equipment                 |

| DIP   | Dual In-line Package                               |

| DSP   | Digital Signal Processing                          |

| DTE   | Data Terminal Equipment                            |

| DTR   | Data Terminal Ready                                |

| EMI   | Electro-Magnetic Interference                      |

| EOF   | End-of-File                                        |

| FCC   | Federal Communications Commission                  |

| FM    | Frequency Modulation                               |

| FPAA  | Field Programmable Analog Array            |

|-------|--------------------------------------------|

| FPGA  | Field Programmable Gate Array              |

| GSM   | Global System for Mobile Communication     |

| GUI   | Graphical User Interface                   |

| I/O   | Input / Output                             |

| IC    | Integrated Circuit                         |

|       | 0                                          |

| IDB   | Intelligent Transportation System Data Bus |

| IF    | Intermediate Frequency                     |

| ISP   | In-System Programming                      |

| ISR   | Interrupt Service Routine                  |

| JTAG  | Joint Test Action Group                    |

| MIC   | Microphone                                 |

| OPAMP | Operational Amplifier                      |

| РС    | Personal Computer                          |

| РСА   | Programmable Capacitor Array               |

| РСВ   | Printed Circuit Board                      |

| PLD   | Programmable Logic Device                  |

| PROM  | Programmable Read Only Memory              |

| PSTN  | Public Switched Telephone Network          |

| РТТ   | Push-to-Talk                               |

| RAM   | Random Access Memory                       |

| RC    | Resistor-Capacitor                         |

| RF    | Radio Frequency                            |

|       |                                            |

- RTS Request-to-Send

- **RX** Receive

- **SDR** Software Defined Radio

- SFR Special Function Registers

- SMT Surface Mount Technology

- SNR Signal-to-Noise Ratio

- SOC System-on-a-Chip

- **SVF** Serial Vector Format

- TAPTest Access Port

- **THD** Through Hole Device

- TX Transmit

- **USART** Universal Synchronous Asynchronous Receiver Transmitter

- VAD Voice Activity Detection

- VHDL VHSIC Hardware Description Language

- VHSIC Very High-Speed Integrated Circuits

- VoIP Voice Over Internet Protocol

- VOX Voice Operated Switch

- WTC World Trade Center

- XSVF Xilinx Serial Vector Format

## ABSTRACT

# PROTOTYPE MIXED-SIGNAL HARDWARE FOR PUBLIC SAFETY RADIO INTEROPERABILITY

by

## Timothy Edwood Bond University of New Hampshire, December, 2007

In performing their required duties public safety personnel from differing departments often need to communicate with one another using their in-car radios. However, in many cases, especially involving small departments, this interoperability doesn't exist.

This research develops a low-cost, low-complexity, yet high performance solution to the public safety radio interoperability problem. This is done through custom, mixedsignal hardware that can be placed in a command vehicle. The analog front-end routes audio signals between radios while the digital portion manages user interaction and controls the analog switching matrix.

A prototype circuit design has been developed and tested within the laboratory using two common radio systems: EFJohnson and Motorola. The preliminary results have shown successful operation as a system gateway between the two radio systems with good performance regarding audio signal latency and minimizing the push-to-talk signal generation delay.

## **CHAPTER I**

#### INTRODUCTION

#### CATLab - Project54 Overview

Project54, a project of the Consolidated Advanced Technologies Laboratory (CATLab), is a collaborative research and development effort between the University of New Hampshire and the New Hampshire Department of Safety supported by the U.S. Department of Justice. The project entails the introduction of advanced technologies to the New Hampshire State Police and other public safety and law enforcement agencies [1]. The goal of this effort is to allow officers to execute their responsibilities more efficiently and in a safer manner [2].

#### **The Problem of System Gateways**

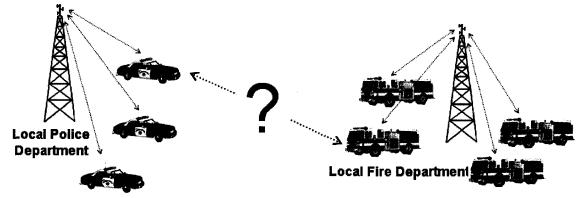

In performing their required duties it is often necessary that public safety personnel, including police, fire, ambulance, and others, from different departments, be able to communicate with one another while still being able to use their familiar, in-car radio systems. However, this interoperability between divergent radios systems, frequently from different manufacturers, often does not exist, especially in cases involving smaller departments. Public Safety Radio Interoperability is an important issue as multiple agencies often need to have this ability to communicate but have incompatible communications equipment which can lead to detrimental communication breakdowns, as illustrated in Figure 1.1. However, solutions the like purchasing of new inter-compatible/interoperable systems is costly and impractical as training would additionally be required. Further, others that involve the use of common channels would severely limit the band space available to each party in non-interagency activities. For these and other reasons the System Gateway general solution presents a number of tantalizing opportunities.

Figure 1.1 – Lack of Radio Interoperability in Public Safety

However, in the solutions that are currently available for system gateways numerous problems do exist. In general they are often too expensive, overly complicated to operate, have limited performance, or have some combination of all three of these shortcomings. For example, previous attempts using Voice-Over-IP (VoIP) have largely been unsuccessful due to the failures of the systems to function well in real time and the inflexibility of the systems, particularly in field-based operations. Note that a Personal Computer (PC), which adds to the cost and complexity, may not always be available or in operation at the field site. Further difficulties arise from the lack of dependability in solutions involving commercial network systems, such as the internet, for audio transmission. Another shortcoming that is common to some of the products available is that, in the attempt to design a high performance system, the result can be cumbersome and illfitted for use in the center console area of a small command vehicle. The ACU-1000 for example is 5.25" by 19" by 11". This is much too large for a typical in-vehicle installation. Note similarly that solutions like VoIP, Software Defined Radio (SDR), and others have additional computational and processing hardware (such as Push-to-Talk generation circuitry) that can be quite large when taken as a whole system. This again can present problems for their use and field-deployment.

Also, for those few systems that have been created with a lower price tag for smaller departments, key features are often left out or the performance is unacceptable. This includes aspects such as ease of controllability which, as a hidden cost, then requires additional financial expenditures for training and/or system set up and configuration. Performance, such as the latency of the audio signal exchange, is major area that is hit in some of the available prototype designs that are coming to market. The biggest effect is found in digital software based approaches such as VoIP and SDR which involve the use of signal buffers that can significantly impair the course of a conversation.

The cost and complication issues in particular, of the majority of available systems, mean that small, local departments are often unable to capitalize on modern interoperability technologies. Instead, these more common solutions tend to focus on advanced features that, while essential for large-scale disasters, are superfluous for local issues and coordination on the small scale. There is therefore a real dearth of inexpensive, yet moderately high performance, public safety gateway solutions targeted for applications involving temporary patches to be used in major, locally-defined crises.

#### Goals of the System Gateway Interoperability Solution

The main goal of this work is to develop and test a System Gateway prototype communications bridge as a solution to the broader public safety radio interoperability problem. The solution must also meet a number of basic demands and solve some of the typical system gateway issues that are present in previous attempts.

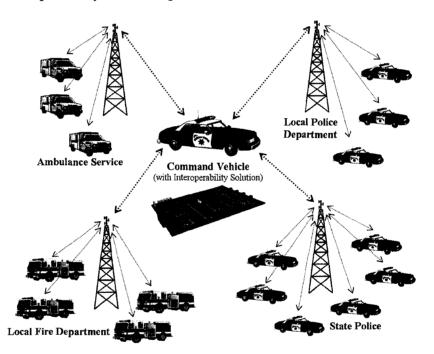

Figure 1.2 shows the basic interoperability goal that the system will be designed to achieve. Note that in the original mega-system there are four distinct radio systems that are unable to communicate with each other. However, these are then bridged through the interoperability solution operated from a command vehicle.

Figure 1.2 - Four Radio Interoperability Mega-System Block Diagram

In order to properly meet the needs of a small, public safety department it was decided that the interoperability solution must support four separate radio systems that can be connected as both audio inputs and outputs. The reason for selecting the number four is that this would enable support for the local police department, the ambulance service, the local fire department, and the state police or some other assisting agency thereby fulfilling the most commonly needed configurations. This four system arrangement is also shown in Figure 1.2

The command vehicle, which is the only unit that has the radios for all four radio systems, is able to communicate with each individually. The individual radio system connections that the operator has in the command vehicle are referred to in this work as radio audio channels or simply **Channels**. Through the use of the interoperability device the operator is able to connect the radio systems or channels together so that they are able to communicate with each other as well as the operator. When channels are connected together they form groups of radio systems that are called, in this thesis, **Meetings**.

Note that in practical terms the maximum number of meetings that are necessary for a four radio system interoperability device is two. Therefore, an additional goal of the design is that it supports the simultaneous operation of two meetings. This will allow four major configuration modes. The first three configuration modes are similar involving two, three, or four channels all connected to a single meeting with the other meeting unused. In this way, the operators using the radio systems of these channels will be able to communicate with each other. The fourth case entails using both meetings at the same time with two channels connected to each. Note that there will be no cross communication or interference between the meetings and their respective channels.

Another important goal for the system gateway is that the final solution be adaptable and flexible to various situations that might arise. This is in terms of both the connection of the radios and in the control of the overall solution. As mentioned previously, the system must be designed to support up to four radios and two meetings

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

simultaneously. The arrangement of connections between the four channels must be completely configurable to allow for each channel to be connected to each meeting.

With regards to how the system is controlled, note that some upper end models currently available on the market can be controlled through manual control heads, RS232 serial ports, IP connections, and even phone line interfaces. Therefore, a goal of this work is that the system be controllable through two primary means: a manual control head allowing direct interaction with the interoperability system and remote software control through an RS232 serial communications port. The added control flexibility of two separate control mechanisms will improve the ability of the operator to establish the necessary communications bridges with little or no training and also to have options available should one of the control methods fail due to lost infrastructure.

With both manual and serial port control options working in parallel, very little technical expertise or training should be required. Furthermore, by interfacing with a main Project54 software program, on an optionally connected PC or laptop, the device should be capable of quickly tapping into the benefits of the common interface approach used by the Project54 system thus allowing for a unified control of all the connected radio systems.

It is also critical that the safety personnel in charge of the system still be able to maintain communication with all the various parties that are being connected together via the interoperability solution. This should include both the ability to address any given radio system specifically and independently at any time and also to be able to actively communicate with a group of radio systems. All this must be done without disrupting the interoperability connections for the radio systems users and also in such a manner as to minimize the interface complexity for the operator. Thus, in the interests of simplifying the interface for the officer, the car should only have one microphone for the entire interoperability system. This microphone must be able to alternate between addressing each of the individual radios or the groups of radios that are assigned to meetings via a simple rotary switch or similar means. The microphone will also need to automatically bypass the circuit board during a power down or system crash to prevent it from tying up the attached radios. The basic, single radio system communication options for the operator must also still function even if the interoperability solution used is not in operation, either due to failure or shutdown.

The system also must meet a number of constraints for use by public safety. First, in the interest of being applied for used by the smaller, local department market the design must be low cost. In the modest production volume of 100 units the price should be in the couple of \$100 range, fully assembled. This low cost constraint also includes the idea that there must be a minimal amount of overhead required for its use, that the solution be designed for ease of installation, and that little operator training be needed. This can be a major issue for small departments who often do not have their own technical staff nor the funding to support such operations. Therefore, being simple to set up and control is a very important feature.

Another constraint on the system is that it be designed for mobile, in-car applications. As such it must be relatively small, i.e. able to fit in the center console area of a vehicle. A target size would then be a maximum of 6" square with a low profile. Also, with the in-car application it must be able to be powered from the car's battery power supply, around 13.8 V DC, with some flexibility on the input voltage range. It

must also be fit for operation in a real-time, field based setting. This includes consideration that operational performance delays due to using the system should be minimized so as not to negatively impact the performance of public safety personnel. (Note that the requirement that it operate in a small setting allows limitations to be placed on the number of individual radios that must be supported at one time.)

Also, as part of a larger in-car system it is important that the solution be robust and produce only a minimal amount of its own electro-magnetic interference (EMI) that could severely impact co-located radio transmitters/receivers. As part of being a robust design it is also important how the solution acts in the event of its own failure. Therefore, some form of automatic isolation must be included in the design so that a crash does not cause all of the attached radios to jam. This can again be especially critical for the small department market where system redundancy is not always available and there is therefore a susceptibility to a single point of failure.

#### Mixed-Signal Hardware Audio Baseband Switch Approach

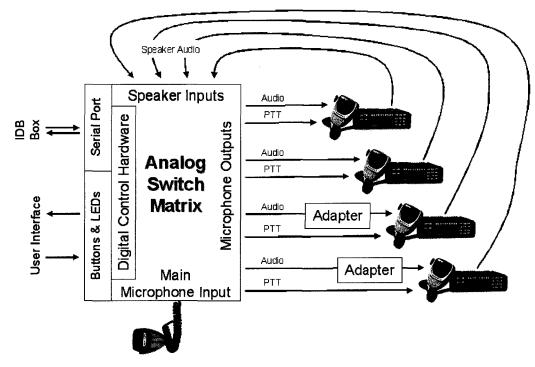

In this research we proposed the development of a small scale, mixed-signal, hardware-based solution to the interoperability problem, in the form of an audio baseband switch, system gateway. By working at the audio baseband, this allows the proprietary aspects of the radios to be largely avoided and brings the design down from radio frequency (RF) signals to the lower audio frequency level. The basic idea is that the designed solution will act as an analog bridge between the audio signals from each radio system, connecting outputs from some systems to the inputs of others. A basic diagram of the system design approach is shown in Figure 1.3. Note that *Chapter II - Background*

provides some Background Information on the more general Public Safety Interoperability Problem and works that have attempted to deal with it in the past.

Figure 1.3 – Interoperability Device Diagram

In the first step we proposed the use of dedicated hardware for the implementation of the system gateway design. It was hypothesized that by pursuing a dedicated hardware solution the overall latency of the system would be reduced and the performance level thereby improved. It was also surmised that there would be a greatly reduced cost overhead with the hardware approach when compared to other solutions making it more desirable for smaller departments that heretofore have been largely ignored in the market. This is the case as many PC based implementations still need some specialized external interface hardware, such as PTT generation and Analog to Digital Converter (ADC) circuitry; all of which consume financial resources and space. This approach would also limit the design to a single printed circuit board (PCB) with some small adapter cables. The resulting small size would make it ideal for positioning within a cruiser or similar command vehicle. A high level description of the hardware utilized is given in *Chapter III – System Hardware Design*. Note that it will encompass the fundamentals of all of the various hardware aspects involved in the design.

The second step taken involved making a decision on the form of hardware that would be employed in order to implement the front-end routing of the audio signals. We proposed that the routing of the audio signals be done using analog circuitry. By doing this there should be virtually no latency when compared to the more common digital approaches which utilize ADCs and often have internal data buffers and processing times based on the internal processing unit speeds. Note that through the use of general purpose analog components, instead of the more expensive digital general processors, such as PCs with sound cards, the cost benefit also should further be realized. The reduced cost, with an increase in the latency performance, should make this a much better fit for the general public safety community. Details on the design of the analog hardware circuitry are contained in *Chapter IV - Analog and Switch Matrix Hardware Design*. It provides circuit design and operation details and also discusses some of the decisions made in selecting between design alternatives.

Also critical to the success of this project, considering its target audience of small departments in need of immediate interoperability solutions, is the fact that the system is designed to be both easy to set up and easy to control. However, committing to analog hardware will reduce the flexibility of the system. To compensate for this, and thus add some extra abilities to the operator's arsenal, we proposed that the system would be controlled by digital, microcontroller-based, back-end hardware. It was believed that this

would accomplish the desired goal of making the solution adaptable to a myriad of situations. In addition, all of the back-end digital control hardware that is run by firmware was designed to be field upgradeable, if necessary, via a standard RS232 communications port. *Chapter V - Digital PTT Mapping and Switch Control* is concerned with the implementation of the digital PTT mapping and PTT control signal generation circuitry within a Complex Programmable Logic Device (CPLD). Details on the microcontroller that forms the heart of the digital hardware used to control the analog switching matrix, as well as the firmware it employs, are covered in *Chapter VI - Digital Control Hardware & Firmware*. This chapter also provides details on the in-system programmability options that are available for most of the digital hardware.

The next step involved the actual creation of the prototype PCB. With the presence of both digital and analog sub-circuits in the completed design it was essential that proper care be taken to manager the interaction and interference between the high speed logic and sensitive audio paths. *Chapter VII – Mixed-Signal PCB Design Considerations* addresses these issues, and broader ones associated with general PCB design. It also examines the steps taken to correct them both in this work and in previous mixed-signal designs.

Having gone through the development steps of the prototype design it was then necessary to provide basic operational procedures as well as to test the performance of the system. *Chapter VIII - Device Operation & User Interfaces* presents the necessary information for controlling the radio connections through the various means available. This includes a manual, hardware-based control head and a software-based serial communications port. Finally, having a fully operational prototype, it was necessary to test the system's operation as an interoperability system gateway device. Chapter IX - Prototype Design Analysis looks at the basic performance of the device and also notes some areas for future development. This also includes some design enhancements that could be used to further improve the system. Chapter X - System Mockup Testing presents some of the interoperability testing scenario results for the complete interoperability system.

Concluding remarks are made in *Chapter XI - Conclusion* on the use of the system, involving the designed prototype circuit board and accompanying firmware, for solving the Public Safety Radio Interoperability Problem and it eventual field deployment.

## **CHAPTER II**

#### BACKGROUND

#### Public Safety Radio Interoperability and the Need for it

Interoperable Communications Systems, in the context of public safety, have been defined as "communications systems which enable public safety agencies to share information amongst local, State, Federal, and tribal public safety agencies in the same area via voice or data signals" [3]. Prompt, reliable communication, or interoperability, between the police, fire, rescue, emergency support personnel, and others is well documented as an essential component of the public safety sphere in modern times. In many cases however public safety agencies remain unable to communicate with each other using their own radio systems thereby severely limiting this desired goal of full interoperability.

Further, the strict definition of public safety, "any State, local, or tribal government entity, or nongovernmental organization authorized by such entity, whose sole or principal purpose is to protect the safety of life, health, or property", can also be expanded to encompass others who have a vested interest in or who are critical to the operation of the public safety functions. This might include public/private transportation personnel, corrections facility staff-members, private business security/safety personnel, and even political leadership who may need to communicate with the public or make critical decisions as quickly as possible – consider the recent tragedy in the Tallmansville,

West Virginia Saco Mine mining accident on January 2nd, 2006 where the death of 11 miners was initially falsely reported by company heads and the state's governor resulting in significant public outcry [4, 5].

While disasters obviously cannot be completely avoided or eliminated, the speed and efficiency with which they are responded to can greatly reduce their impact. Interoperability is one of the major factors controlling the response to the situation. By allowing all aspects of public safety to communicate with one another coordination can be increased and the correct people notified and in position when and where it is most beneficial. This interagency cooperation is especially helpful in large-scale events/disasters which may involve agencies from wide geographical areas.

The 'National Task Force on Interoperability', in its report 'Why Can't We Talk? Working Together To Bridge the Communications Gap To Save Lives', outlined five principle reasons for this failure to communicate [6]:

- Incompatible and aging communications equipment

- Limited and fragmented funding

- Limited and fragmented planning

- Lack of coordination and cooperation

- Limited and fragmented radio spectrum

Engineering solutions to the wider interoperability problem typically focus their attention on the first, second, and fifth obstacles. The planning and coordination/cooperation encompassed by the third and fourth issues must rather be dealt with on an individual level through interacting local, state, and/or federal leadership, administrative personnel, and other forms of management. The engineering solutions designed are principally accomplished through a hardware addition/modification remedy that can be implemented to facilitate the physical aspect of interoperability between users while minimizing the cost that is often associated with such a venture. This role is largely secondary to and contingent upon the success of the administrative actions and solutions.

#### Some Current Interoperability Solutions and Shortcomings

#### Common Radio Systems

The AGILE Interoperability Strategies for Public Safety program, of the National Institute of Justice, outlines in its report, 'Guide to Radio Communications Interoperability Strategies and Products', three primary means for establishing interoperability between organizations and agencies [7]. The first of these involves the usage of the same radio system by all agencies/jurisdictions concerned. This, while arguably the most complete method available, allowing for both the exchange of voice audio and data, is also the most costly, both in financial terms and in the use of the available spectral bands. Note that currently agencies, even within the same jurisdiction, may utilize completely different radio systems. For one or more groups to change over to match the others would require the investment of significant capital, both for in-car radios and for such infrastructure as additional radio towers in certain deficient regions. This cost proves too high a burden, particularly in the context of widely scattered agencies in rural localities. In fact, on the state-wide scale, such an attempt has been described as "prohibitive and unrealistic" [8]. Further challenge to this arrangement comes from the limited and severely fragmented frequency bands that the FCC has currently allocated for public safety agencies. Spectral bandwidth in the public safety domain is highly desirable and there is significant competition for what is available. Also, there are currently 10 major bands available for public safety usage: 25-50 MHZ (HF and VHF), 150-174 MHz (VHF), 220-222 MHZ, 450-470 MHz (UHF), 470-512 MHz (UHF), 764-776 MHz (700 MHz), 794-806 MHz (700 MHz), 806-824 MHz (800 MHz), 851-896 MHz (800 MHz), and 4.94-4.99 GHz [6]. However, the two 700 MHz frequency bands are still occupied by Analog Broadcast Television channels which are to be cleared out with the transition to Digital  $TV^1$ . Therefore, while designated as public safety spectra, they are not currently available for public safety use nor are there many radio systems on the market currently capable of operating in the 700 MHz bands [8].

Additional complications arise through the concept that by uniting all agencies to work with the same type of radio the frequency bands in which that equipment operated would undoubtedly become significantly over-crowded. Concerns could also appear in cross-jurisdictional interoperability where certain radio frequencies may perform better in the rural vs. urban geographic areas [7]. The solution chosen by many departments to reduce the effects of these two spectral problems is simply to use two or more different radios in each car at the same time. This is obviously very financially expensive as it requires redundant systems. However, perhaps more critical is the additional workload

<sup>&</sup>lt;sup>1</sup> This transition will not be enacted until February 18<sup>th</sup>, 2009 at which time the FCC will have authority under 'The Digital Television Transition and Public Safety Act of 2005' (Conference Report: 109-362 in Congressional Record H12641-12737) to reclaim the frequency bands and, in addition to auctioning some of the reclaimed spectrum off, allocate some for use by public safety [9].

that it places on the officer who in many cases already must deal with an over-crowded cruiser. With no common interface to operate all of the divergent radio systems, the driver must focus a proportionately large amount of their attention on the radios. This can be quite distracting during some of the more consuming actions an officer is faced with in the execution of their duties. Due to the diverse radio interfaces few multi-radio interfacing devices exist and those that do are often either quite expensive or in early prototype stages. Some preliminary work also being carried out by Project54 is an effort involving the creation of a software-based audio baseband patch. Some of the early design implementation and testing, which is outlined in [10], entailed the creation of a unified interface for an officer to control multiple radio systems. Thus the officer is able to selectively broadcast over all of the connected radios using a single Project54 microphone and also hear the audio coming from any radios via a common set of speakers. In this prototype the different radios did not have the ability to rebroadcast on each other. Note that this early solution has since been extended to a more useful, complete system gateway patch.

Use of the shared, common radio system methodology exclusively for major emergencies has been implemented in some recent events. For example, in the September 11<sup>th</sup>, 2001 attacks at the Pentagon the 'Greater Metropolitan Washington Area Police and Fire/Rescue Services Mutual Aid Plan' (COG Mutual Aid Plan) and the 'Northern Virginia Mutual Aid Agreement' (NOVA) were quickly activated in order to deal with the situation. What made this event less of a disaster was that there had been preplanning and that the departments were able to communicate with one another via the emergency radio system – in other words, because of interoperability. Even agencies responding from outside the mutual aid region, without appropriate equipment, were able to communicate. This is because "agencies responding from outside of the area covered by the agreements were given portables from a limited supply maintained by Arlington County and, ... Motorola, a private vendor" [11]. This is obviously an adequate solution for large disasters; however it does require significant investment of capital to create these radio stashes, a cost that may make it too difficult to enact in some areas.

This success is in stark contrast to the events that unfolded at the World Trade Center (WTC) in New York City on the same day. While the attacks at the Pentagon were met by an interoperable public safety task force, those in New York had no such benefit. Instead, the fire department in particular was faced with "little reliable radio communication that morning, could not keep track of all the firefighters who entered the towers, and were unable to reach them as the threat of a collapse became unmistakable" [12]. As a result of these communications faults it seems that "non-interoperability was at least partially responsible for the loss of 343 firefighters" [11]. Such catastrophic losses may have been prevented with even a basic interoperability system structure.

#### **Commercial Services**

The problem with the ideal solutions have already been described and may prohibit some from working towards interoperability, at least for the time being. For this reason, other stop-gap solutions to interoperability have also been designed. One is the use of commercial services, at least at command levels. This however can also prove expensive and may not be expandable to large scale events with many personnel. Furthermore, the greatest flaw comes in the fact that it depends on commercial services which may more easily become congested or damaged. Such was also the case in the WTC attack "with telecommunications equipment destroyed in some cases, or simply too congested" [13]. Public safety cannot risk using equipment that can be overloaded by other customers and thus made unavailable but rather must have priority access to wireless communications that are available at all times, ideally with built in redundancy, for mission critical communications. The result is that generic commercial services, while useful as an augmentation, cannot be solely relied upon by public safety. Those commercial services that are used must have equipment dedicated to public safety and that can also be deemed highly reliable [6].

#### Software Defined Radio

Another even more promising and potentially permanent solution is SDR with the inherent ability to be able to insure interoperability simply by uploading a new software program to a set of universal and default hardware. However, it faces many of the common challenges of requiring some, often expensive, external hardware. The main difference from other approaches is that SDR actually can replace an existing radio system completely and connect directly to the antenna. The result is that rather than dealing with low frequency audio-band signals, the SDR is working with high frequency radio signals that can range from 25 to 900 MHz and even some in the gigahertz range. The biggest advantage to this is that a complete, well developed SDR solution essentially represents the ultimate in public safety radio interoperability by allowing officers to quickly and easily transition between disparate radio frequency bands, modulation schemes, and even proprietary encryption/encoding (with the availability of proper

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

firmware/software). In fact, in the FCC's recent loosening of constraints on SDR systems it cited two of the primary reasons for doing this as being that "Software defined radios could allow more efficient use of the spectrum by facilitating spectrum sharing and ... their ability to be programmed could also enhance interoperability between different radio services" [14]. Furthermore, the nature of SDR permits the use of over-the-air downloads in order to upgrade systems to the latest version instead of enacting costly hardware change-outs through maintenance personnel [15].

However, the SDR device does have a major disadvantage in that it must operate well above the carrier frequency in terms of the analog to digital conversion (or at least an IF frequency for systems using front-end, software controlled hardware instead of connecting directly to the antenna). This means that it requires an extremely high sampling rate and a fast processing unit/path capable of handling significant amounts of data in a very short time. This leads to some distinct problems involving tradeoffs between desirable features when working in a real-time application. These relate to the price, power consumption, and performance of the SDR system [16]. (The size of, or real-estate taken up by, the system is also important but is often incorporated into these other tradeoffs.)

First consider the tradeoff between system performance and power consumption. To operate well in real-time (i.e. have an acceptable level of performance) the SDR must operate at high frequencies. However, operating at higher frequencies typically entails higher power consumption due to switching of CMOS circuits. Such may not be an issue with a base station but can become of critical importance when dealing with handheld devices such as portable radios [15, 16]. Power consumption even bears consideration in mobile (car-based) applications where battery usage is less of a concern but can still be an issue when it becomes excessive.

Another performance tradeoff occurs with the cost of purchasing the system. To obtain a better systems often cost significantly more. This is especially true in developing technologies like SDR where businesses are still trying to justify and recoup research and development expenditures. Considering that funding is a concern for public safety, replacing all pre-existing radios is impractical. However, SDR does present a slight cost advantage feature to public safety. Public safety radio systems are traditionally more expensive than commercial models (such as Cellular and Personal Communications Services) largely due to economies of scale and the fact that public safety is a niche market [8]. However, with the arrival of SDR it is postulated that the public safety industry, and others, should be able to capitalize on the flexibility of the system and use the same base hardware with only minor variations for licensing and encryption [15].

One attempt to complete a real-time SDR solution has been made by the Vanu Corporation with its 'Vanu Software Radio Virtual Patch Prototype' [17]. As the name implies the goal of the prototype was not to produce a complete radio replacement but to develop a switch that worked at radio frequencies instead of the audio baseband. This type of interoperability solution belongs to a more general class of System Gateways which are discussed in further depth in The System Gateway Approach section.

Other systems have also been made that attempt to use reconfigurable hardware for the signal processing of an SDR to improve throughput. In this arrangement there are two principle means of implementing the front-end design. One entails the use of "softhardware" or Field Programmable Gate Arrays (FPGA) while the other, more traditional SDR, uses true software through high speed embedded processors, most often designed specifically for Digital Signal Processing/Processor (DSP) applications [18]. (Note that the Vanu solution is much closer to the traditional processor solution but is at a higher level than an embedded solution.) The possibilities of faster computational speeds due to the soft-hardware paths of FPGAs have given this solution significant advantages. In addition, technological advancements in recent years have led to a modest decrease in the physical size and power consumption of these circuits which has further increased their appeal. However, before widespread application can be made, some improvements are still necessary.

Sandbridge Technologies, Inc. has recently been working on the development of a specialized DSP processor, the Sandblaster Convergence Platform [16]. Their goal is to push the envelope in designing a DSP chip for SDR applications by minimizing power consumption while also improving through-put and operational speed. In order to accomplish such an SDR solution they have chosen, instead of building on a generic base system as Vanu did, to operate with a specialized, reprogrammable hardware structure. The attempt appears to have been successful with significant power savings over other DSP processor based solutions.

The SDR solution obviously presents a number of significant benefits including widespread device interoperability, field upgradeability, and cost sharing with wider markets. Its main faults, relating to power consumption, cost, and implementation size for a given level of performance, that in the past have limited its release in a real-time, practical platform, are also rapidly being overcome through technological advancements.

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

Particularly promising opportunities have also arisen with the use of modern FPGAs, DSP Processors, and System-on-a-Chip (SoC) implementations. However, further development is still needed before implementations using SDR can be performed on the desired scale.

## The System Gateway Approach

#### Audio Baseband Switch

The final modern interoperability solution to be discussed is the use of System-to-System Gateways. The most common of these is the Audio Baseband Switch which, in its most primitive form, simply takes the audio output of one radio and feeds it to the audio input of another. In this manner the communications on each are shared despite differences in spectrum, proprietary coding, and further obstacles that may confront other solutions. Similarly, the cost of the hardware involved can be much smaller than the alternatives of replacing entire systems as the preexisting infrastructures are left undisturbed. This includes the radio systems in each cruiser or safety personnel vehicle which then eliminates the need, not only for new radio equipment, but also additional training in that new equipment. The only modification would occur at the designated base station or control vehicle where radios from each system must be provided for the implementation of the radio patch. Note that with a true audio baseband switch, signals on one radio system are automatically rebroadcast on the other radio system(s) and each officer need only manage a single radio, while the command/base station vehicle or location is the only place where all the radio systems must be represented.

23

There are, however, some distinct disadvantages to use of a gateway interoperability solution. The most significant is that since each group still transmits on its original system rather than only on a special, shared channel, more spectral bands are occupied by one meeting group [7]. In fact, each new agency needs to bring in its own radio frequency band to use or else go on that of some other group, with which they are already compatible. But this solution would still be helpful in linking a smaller agency's network to a large interoperable structure without any prior system overhead. This is especially true for cases where a low-cost, temporary solution is needed in a major, locally defined crisis.

A second flaw is that the use of a baseband audio gateway will inherently mean that digital data sent over the radio waves, which typically has a higher bandwidth, will not be able to be exchanged between systems over the audio-band limited radio speakers and microphones. Thus, the interoperability will only be in terms of the lower frequency audio [7]. This might be avoided with some larger systems that supply an extra port to capture/transmit the digital video, image, and alternate data that is required between systems. Note however that such a device may also need to cope with proprietary data signaling as not all radio devices hold to the same universal standard. In any case, the need to at least supply the public safety community with a low-cost audio interoperability solution is significant enough to outweigh concerns that such a system might not allow the exchange and transference of digital data.

One audio gateway already on the market is the ACU-1000 designed by JPS -Raytheon. The ACU-1000 has a number of advanced features including the capability to interface up to 12 radios, telephones, and other diverse communications equipment (24 with the connection of a second ACU-1000 chassis). It also can be controlled manually, via RS232, or over an IP connection thereby facilitating ease of use and application during any public safety event [19]. It should also be noted that the ACU is the flagship product in a family that includes the ACU-T Tactical Intelligent Interconnect Unit, the MCK-1000 Mobile Communications Kit, and the TRP-1000 Transportable Radio among others. This gives the public safety management force some options in the selection of needed equipment [20]. The largest fault for such devices, however, is the significant cost. By way of example, the ACU-1000 is in the range of \$100,000; outside the reach of many small agencies and beginning to approach the cost of simply upgrading current equipment [21]. Other concerns, such as required technical expertise requirements and latency are also important in considering a local department level solution to the interoperability problem. These will be mentioned further in discussion on the course taken in this thesis.

#### Voice-Over-IP

Another recent attempt to implement the basic System Gateway design approach has arisen with VOIP. By leveraging existing internet-type standards, it holds the possibility of radios that can be automatically set to work together simply by designing a universal interface to already existing standards.

The VOIP solution has however presented a number of flaws including the dependence on an internet network structure which may or may not be dependable in an emergency. Alternative, dedicated networks could be developed but would largely be impractical with the increased infrastructure overhead that would have to be borne solely

by the controlling public safety agency. Issues have also been examined that explore the effects of dropped packets, jitter, and other IP constraints that limit its use in real-time applications. In typical internet transactions delays or dropped packet, which may need to be resent after detection, present little problem to the end user. However, in mission critical applications, particularly during events when public infrastructure might already be overloaded (as in the World Trade Center attacks on 9/11), these delays and failures are unacceptable. Furthermore, there is a significant amount of pre-incident overhead planning that would be needed for proper implementation. This includes details as to who would control the VOIP main server and who could connect to it. Lastly, the VOIP solution requires computational hardware overhead. This usually includes some form of digitization board. It is more common to use a PC with a sound card, however this can be somewhat expensive as a channel of the sound card is required for each radio or otherwise some form of analog switching hardware must be included. Other issues also arise in the need for special hardware to generate the Push-to-Talk signals needed by the radios [22]. Combined with set up difficulties this option may not be reasonable for most public safety interoperability needs.

#### Software Defined Radio as a System Gateway Patch

The SDR solution to radio interoperability also has an application within the broader System Gateway approach. While it does require an additional change in hardware in the short term, it would not be difficult to have the controlling software unit (for example a PC) map the audio signals between various software radios configured to work with the pre-existing infrastructures. This has the added benefit of making the need for radios at the connection site unnecessary and also allows for greater versatility in connecting systems together on the fly.

The aforementioned 'Vanu Software Radio Virtual Patch Prototype', being developed by the Vanu Corporation as a complete real-time SDR patch solution, is one such SDR based System Gateway [17]. However, while the attempt appears to have been reasonably successful it does present some of the limitations that are typical for SDR methods that utilize true software to perform all signal processing. First, the software program is coded to only support FM, APCO Project 25, and GSM waveforms. Other signaling schemes, including proprietary forms, still need to have their protocols applied to the structure. This could present coding difficulties especially for small departments that utilize obscure/obsolete radio systems. However, this is a challenge that all SDR solutions face [23].

The second issue relates to the aforementioned cost and power consumption vs. performance issues. The Vanu solution is designed to operate using adaptable, softwarecontrolled, front-end hardware followed by processor boards having analog to digital converters (ADC). The outputs of the processors are fed into a computer for processing in terms of modulation and coding. All DSP is then handled in pure software, versus the traditional approach of using digital signal processors and FPGAs [17]. While this does work, and it has the advantage of placing the full processing power of a computer at the designer's disposal to increase flexibility, it has some significant drawbacks. First is the need for somewhat expensive, "wideband and waveform-independent" radio frequency (RF) and digital front-end hardware. Secondly, the attempt to obtain flexibility by using a full computer processor further adds cost to the system. (For the prototype designed, which supported only two radios, the system required a 1.2-GHz Intel Pentium III processor.) Both of these factors also mean the system utilizes significant amounts of power (especially if the system was ever to be used as an independent SDR solution) and takes up a great deal of space [23].

Another shortcoming is that in using sampling hardware it was necessary to operate with buffered data blocks 1024 elements long. This created delay problems resulting in latency of approximately 21.3 ms just on the front-end hardware side. As a result the round trip latency through the interoperability system alone will most likely be a minimum of 50 ms and possibly more depending on the performance of the computer's processor. This creates problems for communications equipment which may need to be interfaced to the system, such as a Global System for Mobile Communications (GSM) device which is specified to have a 42 ms maximum round-trip latency [23].

Finally, the system designed was only able to support one connection between two radios. This is largely due to the computation intensity required of the PC for DSP processing. The solution is therefore both expensive and cumbersome making it prohibitively large for rapid field deployments that may be required for a faster interoperability solution. Also, that the system is scalable to more than two channels with the addition of supplementary RF hardware and processing units was assumed and not attempted. Moreover, it is not known whether the PC can adequately handle the added loads [23]. Thus, while the Vanu SDR solution is optimal in a number of ways and presents significant opportunities for future research, its current application through the use of a computer for processing is somewhat limited.

# **CHAPTER III**

# SYSTEM HARDWARE DESIGN

#### **System Hardware Elements**

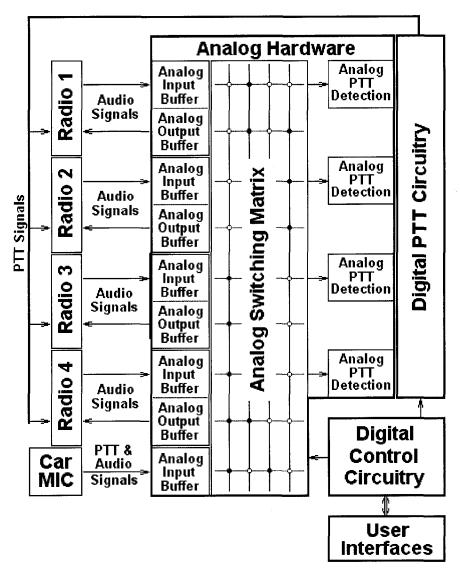

In order to improve the latency performance, while also reducing size and cost, it was decided that the system would be designed mostly in dedicated hardware. The hardware is divided into thee main parts, each of which are shown in Figure 3.1. They are the Analog Hardware, the Digital PTT Circuitry, and the Digital Control Circuitry. A high level summary of the fundamental aspects of each is given here but analyzed in more depth in the following chapters.

The main interaction with the four radios of the system is performed through the Analog Hardware. It serves three primary purposes. The first of these is the buffering and appropriate scaling of the input and output audio signals. Another purpose of the analog circuitry is the detection and generation of the PTT signals that are needed by the Digital PTT Circuitry. Lastly, and as it primary function, portions of the analog hardware form the Analog Switch Matrix that actually connects the various radios together to create conditional interoperability. The Analog Hardware passes audio signals between each radio and receives audio from the In-Car Microphone. It also sends raw PTT signals to the Digital PTT Circuitry and receives control signals from the Digital Control Circuitry hardware.

Figure 3.1 – System Hardware Block Diagram

The primary function of the Digital PTT Circuitry hardware is to route the digital PTT signals received from the In-Car Microphone and the Analog PTT Detection circuits to the appropriate radio microphone PTT inputs. Determination of the appropriate routing is determined by the conditions specified by the connection control signals received from the Digital Control Circuitry. The PTT mapping hardware can also be reprogrammed through an interface with the control hardware which greatly increases its flexibility.

The final hardware section of the system is the Digital Control Circuitry. Its main aspect is the digital microcontroller which manages the execution of two primary functions. The first is the control of the Analog Switch Matrix and the Digital PTT Circuitry in the mapping of the audio and PTT signals. This involves the management of control signals for the switching elements and digital logic variables. The second function of the Digital Control Circuitry is the management of the User Interfaces. The User Interface is broken down into two parts. One is the manual, hardware-based control head (which is largely implemented in the Digital Control Circuitry). The other is the (optional) software interface which connects to the system via the serial port communications hardware. (Note that the serial port communications hardware is actually discussed in the context of the user interfaces in *Chapter VIII – Device Operations & User Interfaces.*)

## **The In-Car Microphone**

Rather than have four in-car microphones, as well as any meeting microphone(s), that the operator must juggle in order to communicate with all the channels, the approach taken utilized only a single, main system microphone in order to simplify operations. The single microphone can be physically switched between five settings - one for a direct connection to each of the channels and one for connection to an interoperability meeting. When connected as a channel microphone the audio will only be broadcast to that individual channel. When activated it will also temporarily break the channel's audio feed from any meeting it might be connected to and thereby allow the operator to use it like any normally operating microphone. The selection of the microphone to act as the Master Microphone is the more versatile setting that will allow the operator to use it within the interoperability context. It broadcasts directly onto either Meeting A or Meeting B and thus out to any channels that are connected to them. Selection of the meeting is done by connecting the Master Microphone to the desired meeting just as any channel would be connected. (The Master Microphone input can really be treated as another speaker audio input to the system in addition to the four from the channels.) Note that the Master Microphone has override priority over any audio arriving on a meeting from one of the channel sources.

The Master Microphone has a manually keyed push-to-talk button, however, it is also equipped with a firmware controlled PTT in parallel with the manual one. This will enable the Project54 program, or some similar software attached through a serial port, to engage the Master Microphone. This permits the system to use text-to-speech synthesized voice directly over the airwaves if desired by a future P54 application or to use the Project54 in-car microphone in place of the generic interoperability device microphone.

The microphone employed by the system should be a passive microphone. This means that no power need be supplied to the microphone and that the signal output levels will be quite low (on the order of 200-300 mV). From an interface perspective the microphone contains both a single-ended audio signal and an active low PTT signal. A ground reference line for one or both of the audio and PTT signals should also be provided. (Note that the microphone used in the laboratory and system testing was a Whelen model that was passive and very simple with only four lines – Audio, PTT, and a reference 'ground' for each.

#### **The Radios**

The System is capable of supporting up to four different radios. In order to make the design as universal as possible very few assumptions were made as to what signal and control lines are available on the radios. The base line signals that it was decided would always be available for any given radio were: the speaker audio output (potentially differential), the microphone audio input, and the microphone active-low PTT input. Note that in some cases this may entail the removal of a radio's normal microphone and/or speaker in order to connect it up to the interoperability system. However, in other cases, auxiliary ports that provide the same signal functions might also be available. Note that the microphone audio input and speaker audio output of the radio connect respectively to the analog output buffers and analog input buffers of the interoperability circuit board. The radio microphone PTT input similarly connects to the channel PTT outputs of the Digital PTT Circuitry.

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

# **CHAPTER IV**

# ANALOG AND SWITCH MATRIX HARDWARE DESIGN

#### Introduction to the Analog Prototype Hardware Design

The main functional aspect of the prototype design is the analog front-end and switching matrix hardware. These analog aspects entail the actual manipulation and controlled routing of the audio signals that are needed by the radio inputs and outputs. Figure 4.1 shows a block diagram of the analog circuitry that was used. Note that the control interface with the digital microcontroller and the digital PTT mapping circuitry as a signal source and destination are also included in the diagram to show the interaction with the rest of the prototype system.