# University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

5-2019

# Model Development and Assessment of the Gate Network in a High-Performance SiC Power Module

William Austin Curbow University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the <u>Electronic Devices and Semiconductor Manufacturing Commons</u>, <u>OS and Networks</u> <u>Commons</u>, <u>Power and Energy Commons</u>, and the <u>VLSI and Circuits</u>, <u>Embedded and Hardware</u> <u>Systems Commons</u>

## **Recommended** Citation

Curbow, William Austin, "Model Development and Assessment of the Gate Network in a High-Performance SiC Power Module" (2019). *Theses and Dissertations*. 3189. https://scholarworks.uark.edu/etd/3189

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact ccmiddle@uark.edu.

# Model Development and Assessment of the Gate Network in a High-Performance SiC Power Module

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

by

William Austin Curbow University of Arkansas Bachelor of Science in Electrical Engineering, 2014

# May 2019 University of Arkansas

This thesis is approved for recommendation to the Graduate Council.

Juan Carlos Balda, Ph.D. Thesis Director

Simon Ang, Ph.D. Committee Member Roy McCann, Ph.D. Committee Member

Yue Zhao, Ph.D. Committee Member

#### ABSTRACT

The main objective of this effort is to determine points of weakness in the gate network of a highperformance SiC power module and to offer remedies to these issues to increase the overall performance, robustness, and reliability of the technology. In order to accomplish this goal, a highly accurate model of the gate network is developed through three methods of parameter extraction: calculation, simulation, and measurement. A SPICE model of the gate network is developed to analyze four electrical issues in a high-speed, SiC-based power module including the necessary internal gate resistance for damping under-voltage and over-voltage transients, the disparity in switching loss between paralleled devices due to propagation delay, a high-frequency oscillatory behavior on gate voltage due to die-to-die interactions, and current equalization in the kelvin-source signal path. In addition, the analysis of parameter variance between paralleled MOSFETs and the effects of mismatched threshold voltage and on-state resistance on switching loss and junction temperature are investigated. Finally, three Miller Clamp topologies are simulated and assessed for effectiveness culminating in a solution for parasitic turn-on in high dv/dt systems such as those utilizing high-performance SiC power modules.

# TABLE OF CONTENTS

# CHAPTER 1

| INTR | ODU                                                   | JCTION                                                              |  |  |

|------|-------------------------------------------------------|---------------------------------------------------------------------|--|--|

| 1.1  | Importance of Reliable Power Semiconductor Packaging1 |                                                                     |  |  |

| 1.2  | Nex                                                   | xt Generation Power Modules Using Wide Bandgap Power Semiconductors |  |  |

| 1.3  | Issu                                                  | ues in Silicon Carbide Power Modules                                |  |  |

| 1.4  | Pro                                                   | posed Solution7                                                     |  |  |

| 1.5  | Obj                                                   | ectives of Thesis                                                   |  |  |

| 1.6  | Org                                                   | anization of Thesis                                                 |  |  |

| 1.7  | Ref                                                   | erences                                                             |  |  |

| CHA  | PTEI                                                  | R 2                                                                 |  |  |

| PARA | ASIT                                                  | IC ELEMENTS OF THE GATE NETWORK                                     |  |  |

| 2.1  | Gat                                                   | e Driver to PCB Interconnects                                       |  |  |

| 2.1  | .1                                                    | Calculations                                                        |  |  |

| 2.1  | .2                                                    | Measurement                                                         |  |  |

| 2.1  | .3                                                    | COMSOL Simulations                                                  |  |  |

| 2.2  | Gat                                                   | e & Kelvin-Source PCB                                               |  |  |

| 2.2  | .1                                                    | Calculations                                                        |  |  |

| 2.2  | 2                                                     | Measurements                                                        |  |  |

| 2.2  | .3                                                    | COMSOL Simulations                                                  |  |  |

| 2.3  | Gat                                                   | e & Kelvin Source Wire Bonds                                        |  |  |

| 2.3  | .1                                                    | Calculations                                                        |  |  |

| 2.3  | .2                                                    | Measurements                                                        |  |  |

| 2   | .3.3                                                                       | COMSOL Simulations                                        | 39 |  |  |

|-----|----------------------------------------------------------------------------|-----------------------------------------------------------|----|--|--|

| 2.4 | Co                                                                         | nclusion                                                  | 43 |  |  |

| 2.5 | Ref                                                                        | ferences                                                  | 45 |  |  |

| CH  | APTE                                                                       | R 3                                                       |    |  |  |

| GA  | TE NE                                                                      | ETWORK MODELING AND ANALYSIS                              | 46 |  |  |

| 3.1 | Par                                                                        | asitic Elements of the Gate Network                       | 46 |  |  |

| 3   | .1.1                                                                       | Lumped-Element Parasitic Model Overview                   | 46 |  |  |

| 3   | .1.2                                                                       | Die-to-die Parasitic Inductances                          | 48 |  |  |

| 3   | .1.3                                                                       | Parasitic Resistance and Capacitance Considerations       | 50 |  |  |

| 3.2 | Saf                                                                        | e-Operating-Area and Stability Criteria                   | 51 |  |  |

| 3   | .2.1                                                                       | Gate-to-Source Over-Voltage Deterrence                    | 52 |  |  |

| 3   | .2.2                                                                       | Propagation Delay Between MOSFET Positions                | 57 |  |  |

| 3   | .2.3                                                                       | Oscillatory Behavior and Stability Criteria               | 64 |  |  |

| 3   | .2.4                                                                       | Kelvin-Source Resistors                                   | 67 |  |  |

| 3.3 | Ref                                                                        | ferences                                                  | 72 |  |  |

| CH  | APTEI                                                                      | R 4                                                       |    |  |  |

| PAI | RAME                                                                       | TER VARIANCE EFFECTS                                      | 73 |  |  |

| 4.1 | SiC                                                                        | C MOSFET Parameters: Threshold Voltage (V <sub>TH</sub> ) | 73 |  |  |

| 4.2 | 4.2       SiC MOSFET Parameters: On-State Resistance (R <sub>DS-ON</sub> ) |                                                           |    |  |  |

| CH  | APTE                                                                       | R 5                                                       |    |  |  |

| MII | LLER                                                                       | CLAMP TOPOLOGIES FOR SIC POWER MODULES                    | 84 |  |  |

| 5.1 | The                                                                        | eoretical Background                                      | 84 |  |  |

| 5.2 | 5.2 External Miller Clamp                                                  |                                                           |    |  |  |

| 5.3 | Internal Miller Clamp                                 | 1  |

|-----|-------------------------------------------------------|----|

| 5.4 | Individual Miller Clamp per MOSFET Position9          | 13 |

| 5.5 | References                                            | 6  |

| CHA | TER 6                                                 |    |

| CON | CLUSION AND FUTURE WORK                               | 17 |

| 6.1 | Conclusion                                            | 17 |

| 6.2 | Future Work                                           | 8  |

| 6.2 | 1 MOSFET Binning or Sorting Algorithm Development     | 98 |

| 6.2 | 2 Experimental Testing of the Individual Miller Clamp | )8 |

# LIST OF FIGURES

| Figure 1. Total New Investment in Clean Energy by Country or Region 1                    |

|------------------------------------------------------------------------------------------|

| Figure 2. Common Power Modules Ranging from 10 A to 3600 A and 600 V to 6.5 kV [5] 2     |

| Figure 3. Performance Improvements of SiC over Si-based Inverters [10]                   |

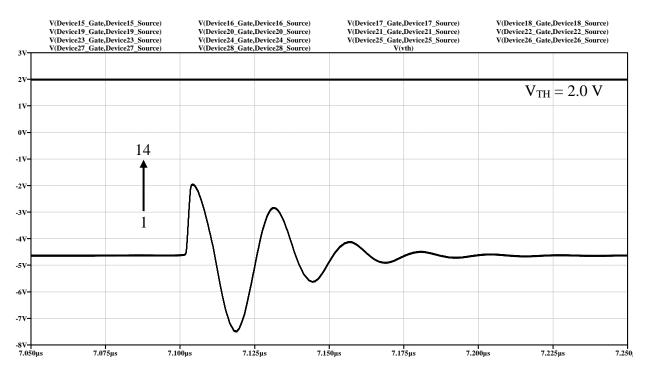

| Figure 4. High-Frequency Oscillatory Gate Voltage during Turn-Off of SiC Power Module 6  |

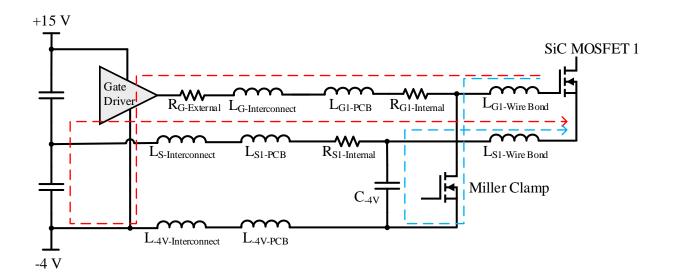

| Figure 5. Gate Impedance Network Model with Parasitics and Tunable Components            |

| Figure 6. Simplified Circuit of Gate Driver and Power MOSFET with Clamping Device [18] 8 |

| Figure 7. Gate Driver to PCB Interconnect                                                |

| Figure 8. Cross-Section of Gate-Source Connector Portraying Mutual-Inductance            |

| Figure 9. Inductance Measurement Fixture and Agilent's Precision LCR Meter 19            |

| Figure 10. Manufacturer's 3D Model vs. 3D Model Optimized for COMSOL 21                  |

| Figure 11. Constructed Mesh of Gate Source Connector                                     |

| Figure 12. Magnetic Flux Density and Current Density of Gate Source Connector            |

| Figure 13. Gate Kelvin PCB Layout (Top) and Estimated Area for Calculations (Bottom) 26  |

| Figure 14. Gate Kelvin PCB Mounted on Substrate Assembly                                 |

| Figure 15. Mesh Construct for Solving COMSOL Electromagnetic Simulation of PCB 29        |

| Figure 16. Current Density of First Position Shorted at Wirebond Pads                    |

| Figure 17. Magnetic Field (A/m) Surrounding Wirebond Pads and Shorting Resistor          |

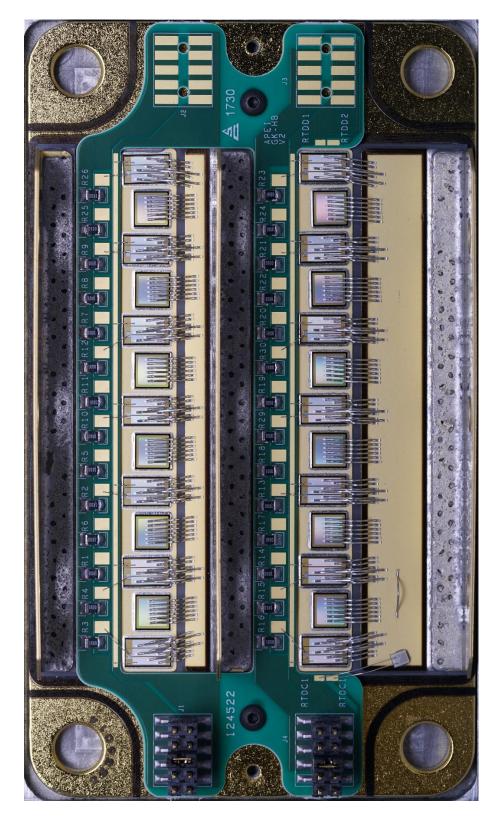

| Figure 18. CAS325M12HM2 Gate Network PCB on Substrate Assembly with Wirebonds 37         |

| Figure 19. 0.005" Diameter Gate and Source Wirebonds Modeled in Solidworks               |

| Figure 20. Last Position of Meshed 3D CAD Model in COMSOL                                |

| Figure 21. Current Density and Magnetic Flux Density of Wirebonds                        |

| Figure 22. Current Density of Last Position and Proximity Effect of Wirebonds            |

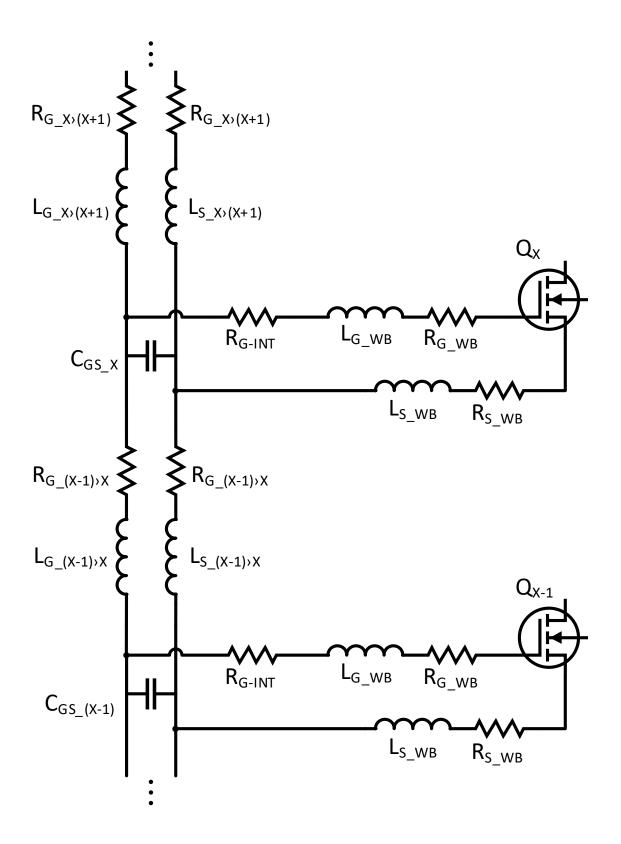

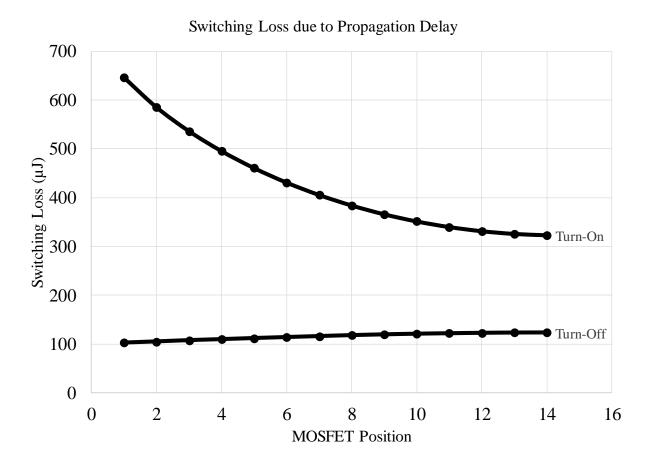

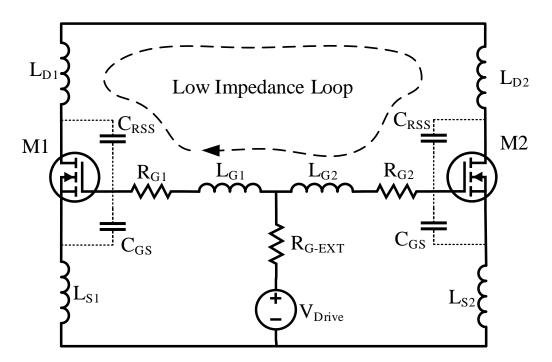

| Figure 23. Lumped-Element Parasitic Model of Two MOSFET Positions                                              |

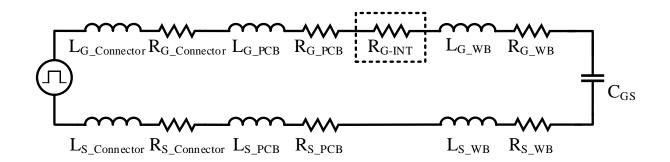

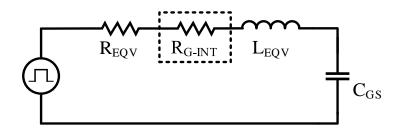

|----------------------------------------------------------------------------------------------------------------|

| Figure 24. Series RLC Circuit of Last MOSFET Position                                                          |

| Figure 25. Equivalent Series RLC Circuit of Last MOSFET Position                                               |

| Figure 26. Verification of R <sub>G-INT</sub> in the Series RLC Circuit of Last MOSFET Position                |

| Figure 27. Verification of R <sub>G-INT</sub> in the Full Gate Network Model                                   |

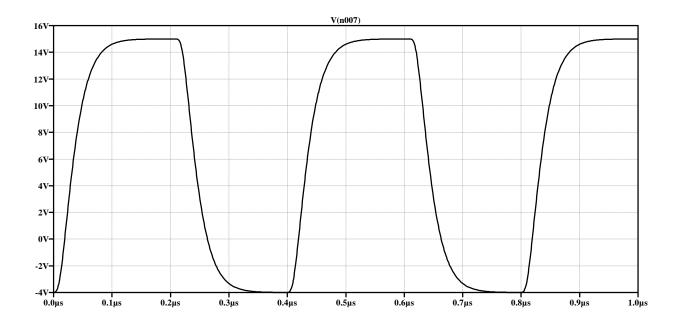

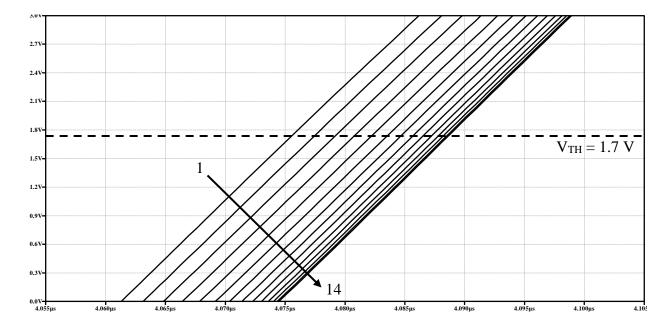

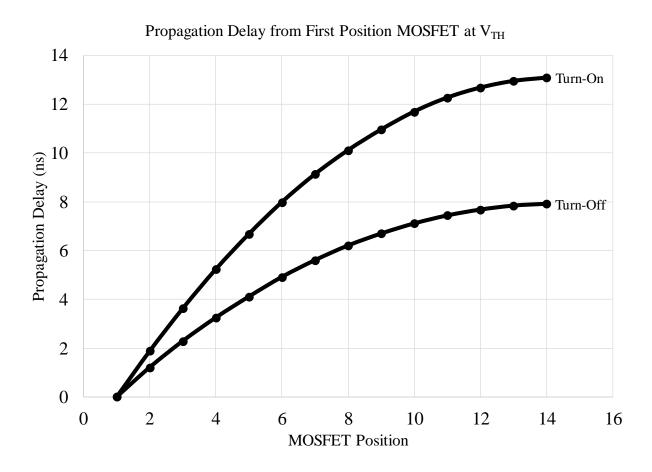

| Figure 28. Zoomed Turn-On Transient of each MOSFET's $V_{GS}$ at the Threshold Voltage 58                      |

| Figure 29. Propagation Delay of each MOSFET for Turn-On and Turn-Off Transitions 59                            |

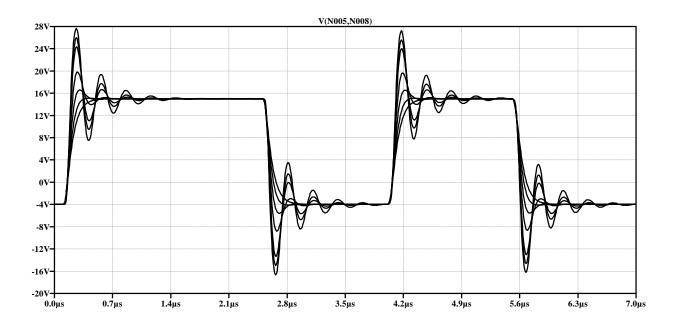

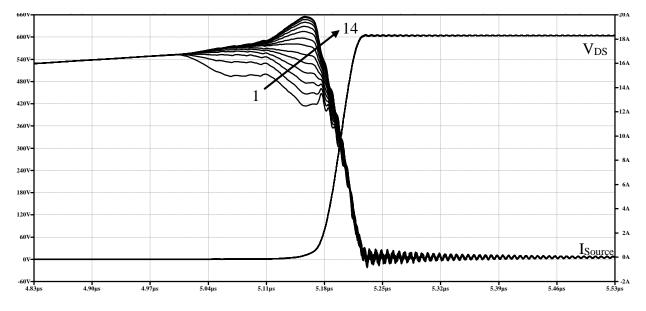

| Figure 30. Turn-Off Transition of 14 Paralleled MOSFETs in Power Module                                        |

| Figure 31. Turn-On Transition of 14 Paralleled MOSFETs in Power Module                                         |

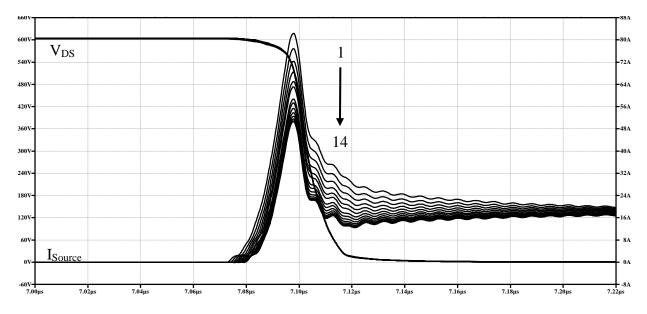

| Figure 32. Individual MOSFET Switching Loss Values during Turn-On and Turn-Off                                 |

| Figure 33. Low-Impedance Path of Two Parallel MOSFETs Capable of Inducing Parasitic Self-                      |

| Oscillations                                                                                                   |

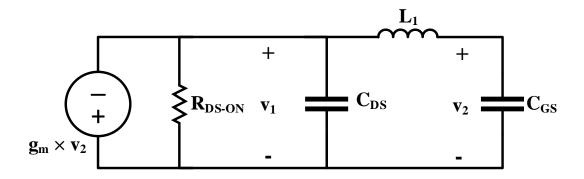

| Figure 34. Colpitts Oscillator Formed from Two Paralleled MOSFETs                                              |

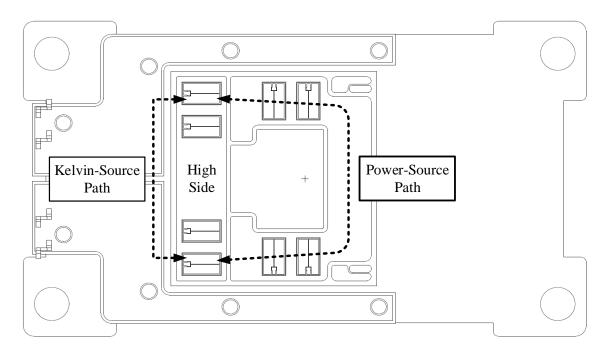

| Figure 35. Kelvin-Source Current Path vs. Power-Source Current Path                                            |

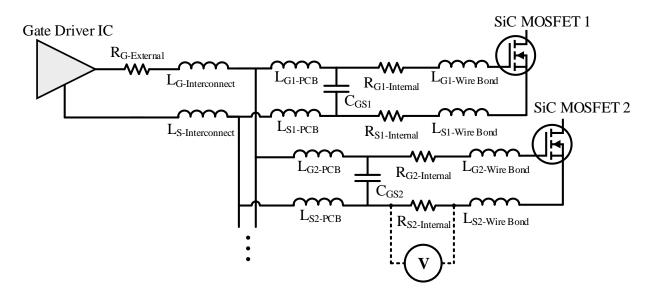

| Figure 36. Kelvin-Source Current Measurement Circuit                                                           |

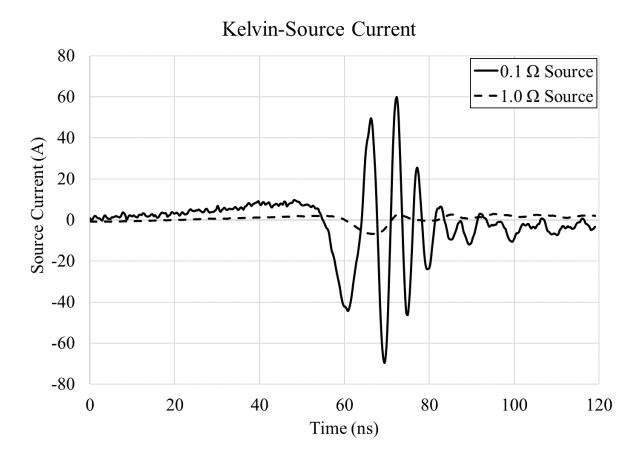

| Figure 37. Kelvin-Source Current for Two Values of R <sub>S-Internal</sub>                                     |

| Figure 38. Parameter Variance Test Fixture for 3-Pin, TO-247 Discrete Devices                                  |

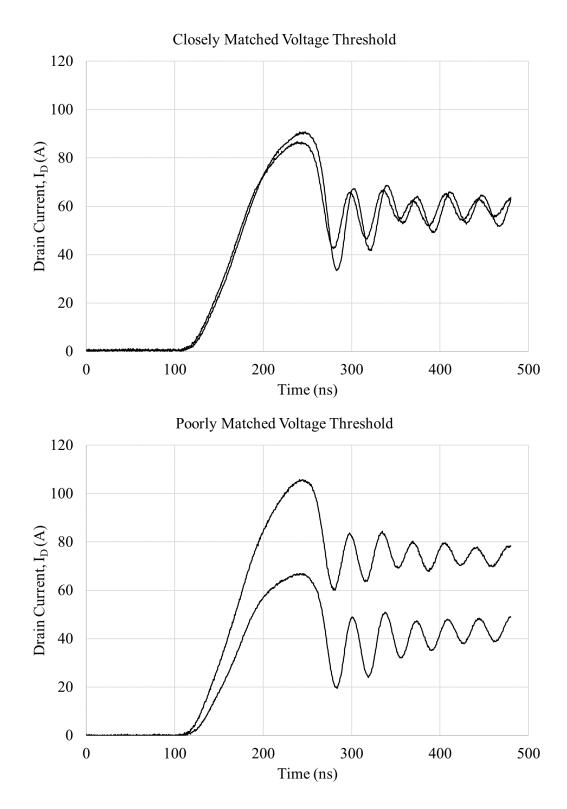

| Figure 39. Measured Turn-On Current for Parallel MOSFETs with Closely Matched (Top) and                        |

| Poorly Matched (Bottom) Threshold Voltages                                                                     |

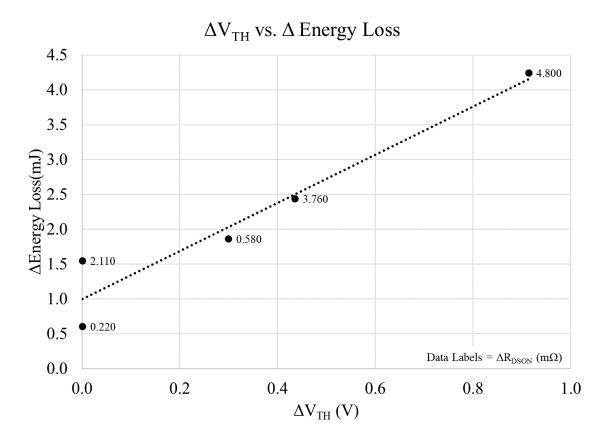

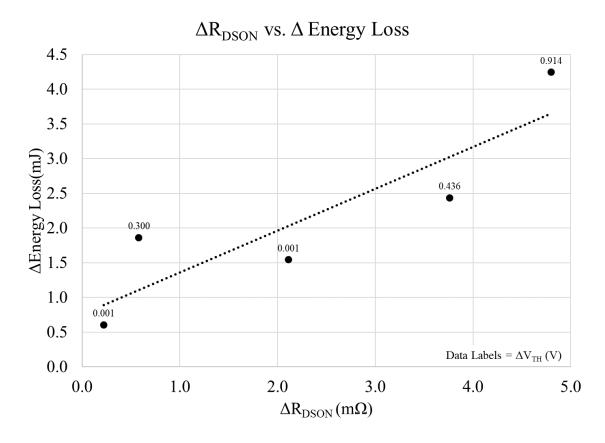

| Figure 40. Measured $\Delta$ in Energy Loss vs. $\Delta$ in V <sub>TH</sub> between Two Parallel MOSFETs       |

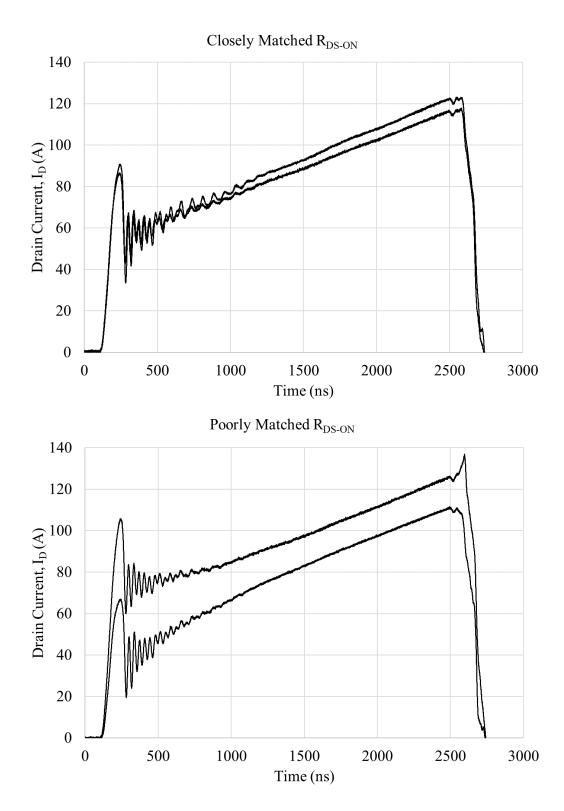

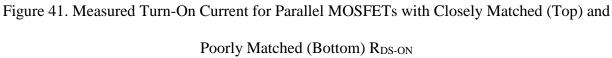

| Figure 41. Measured Turn-On Current for Parallel MOSFETs with Closely Matched (Top) and                        |

| Poorly Matched (Bottom) R <sub>DS-ON</sub>                                                                     |

| Figure 42. Measured $\Delta$ in Energy Loss vs. $\Delta$ in R <sub>DS-ON</sub> between Two Parallel MOSFETs 81 |

| Figure 43. Miller Charge-Up Phenomenon in High dv/dt Half-Bridge Systems                     |

|----------------------------------------------------------------------------------------------|

| Figure 44. Double-Pulse Testing with No Miller Clamp                                         |

| Figure 45. High-Side V <sub>GS</sub> with No Miller Clamp During Low-Side Turn-On (Control)  |

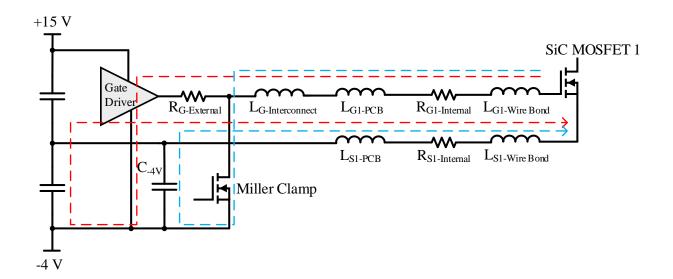

| Figure 46. Schematic of External Miller Clamp Illustrating Difference in Current Paths       |

| Figure 47. High-Side V <sub>GS</sub> with External Miller Clamp During Low-Side Turn-On      |

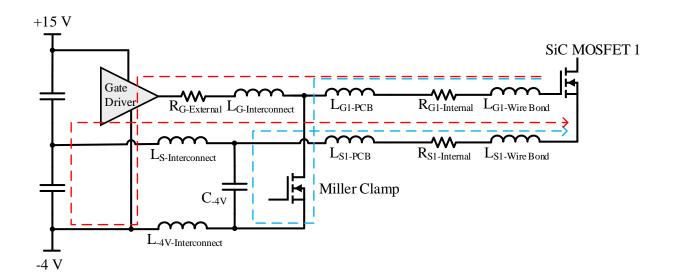

| Figure 48. Schematic of Internal Miller Clamp Illustrating Difference in Current Paths       |

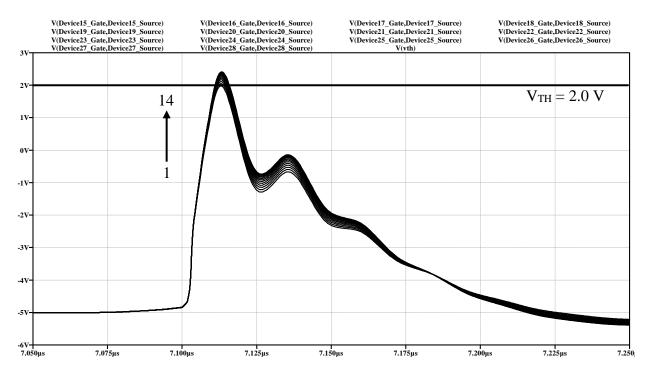

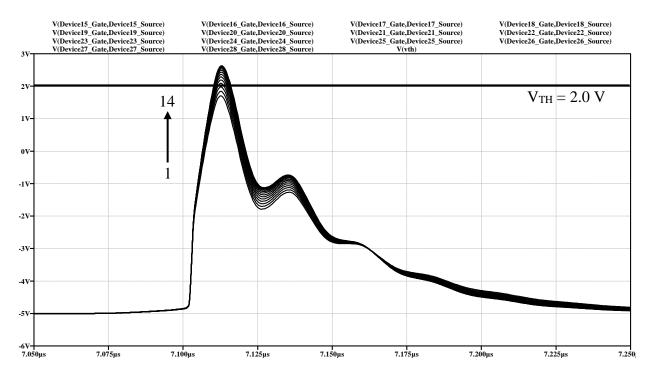

| Figure 49. High-Side $V_{GS}$ with Internal Miller Clamp During Low-Side Turn-On at 420 A 92 |

| Figure 50. Schematic of Individual Miller Clamps Illustrating Difference in Current Paths 93 |

| Figure 51. High-Side V <sub>GS</sub> with Individual Miller Clamp During Low-Side Turn-On    |

# LIST OF TABLES

| Table 1. Distance between Conductors with Corresponding Mutual-Inductance | 17 |

|---------------------------------------------------------------------------|----|

| Table 2. Self-Inductance, Mutual-Inductance, and Total Pin Inductance     | 18 |

| Table 3. Self-Inductance Calculation of Gate Kelvin PCB                   | 26 |

| Table 4. Self-Inductance Calculation of Wirebonds of Varying Length       | 34 |

| Table 5. Mutual-Inductance Calculation of Wirebonds of Varying Length     | 35 |

| Table 6. Inductance Measurement of Gate Kelvin PCB                        | 36 |

| Table 7. Comparison of Inductance Extraction Methods                      | 44 |

| Table 8. Die-to-die Parasitic Inductance Values                           | 49 |

| Table 9. Critical Damping for Three Common SiC MOSFETs                    | 55 |

| Table 10. Stability Verification for Three Common SiC MOSFETs             | 66 |

| Table 11. Simulated $\Delta V_{TH}$ vs. Energy Loss                       | 74 |

| Table 12. Miller Capacitance Ratio for Three Common SiC MOSFETs           | 86 |

# **CHAPTER 1**

## **INTRODUCTION**

# 1.1 Importance of Reliable Power Semiconductor Packaging

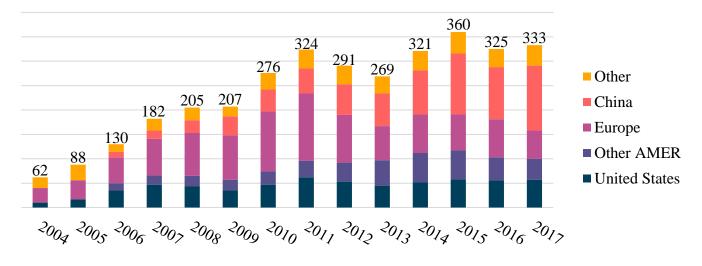

Electrical energy supplied roughly 40% of the world's power requirements in 2013 and has been increasing rapidly as countries migrate to renewable energy sources [1]. Global investment in clean energy has increased immensely in the past fifteen years from approximately \$62 billion dollars spent on renewables in 2004 to a staggering \$333 billion dollars in 2017. As of late, the world's leader in renewable investment, China, has increased its spending on alternative energies by 24% in the past year as shown in Figure 1. In addition, The United States now generates 18% of its electricity from renewable energies while its reliance on coal has decreased from 48% in 2008 to only 30% in 2017 [2]. This clear global trend marks an incredibly important shift in energy production and will have a massive impact on the surrounding industries.

Alternative energy sources such as solar, wind, and hydropower are made possible with the use of power electronics, which is the general term for the systems capable of converting and controlling

Figure 1. Total New Investment in Clean Energy by Country or Region

the flow of electrical energy [3]. At the core of these power electronics lies the power semiconductor, which is traditionally a silicon transistor capable of processing high magnitudes of voltage and current. Even with efficiency ratings of 96% to 99% for modern switch-mode power electronics systems [4], it is not feasible to use a single power semiconductor device per switch position in a system. To meet the requirements of the high-power systems responsible for converting energy obtained from renewables to consumable power on the grid, multiple power semiconductor devices must be operated in parallel inside an electronic package commonly referred to as a power module.

A power module is described as one or more power semiconductor devices in a package, in which the package and connection technology are just as important as the characteristics of the power semiconductor [3]. During construction and operation of a power module, there exist many mechanical, electrical, and thermal factors, which have a large impact on the performance and reliability of a system. According to Infineon, for this technology to be applied, the power modules

Figure 2. Common Power Modules Ranging from 10 A to 3600 A and 600 V to 6.5 kV [5]

must be robust and durable; moreover, in traction applications, lifetimes of 20 years or more are required with the need for a high-power cycling capability [3]. A few common silicon-based power modules from Infineon are displayed in Figure 2 [5].

Recently, power electronics are being utilized in applications such as motor drives for industry and HVAC, for traction drives in electric vehicles, and for data centers, which now consume over two percent of the United States and Europe's electricity consumption [1]. With these innovative utilizations of power electronics, it is crucial that the fundamental building blocks of these systems, the power modules, be durable, robust, and reliable for the countless energy conversion applications that the future will bring [4].

## **1.2** Next Generation Power Modules Using Wide Bandgap Power Semiconductors

The demands for high-performance power electronics are quickly surpassing the voltage rating, efficiency, and power density limitations governed by the intrinsic properties of silicon-based power semiconductors. Fortunately, a higher-performing alternative is growing in adoption and therefore becoming increasingly better understood, more reliable, and less expensive [6]. This next generation power semiconductor is Silicon Carbide (SiC), which is considered a wide bandgap semiconductor and exhibits an increase in bandgap energy of nearly three times that of silicon.

There are four main elements that differentiate SiC power semiconductors from silicon: bandgap, field strength, thermal conduction, and electron mobility [7]. The first, bandgap energy, allows the technology to operate at a higher junction temperature, which in turn allows the entire system to process more power in less space [8]. Next, SiC's much higher field strength enables high blocking voltages, low leakage currents, and a smaller drift region. This allows SiC to have a greatly reduced specific on-state resistance for an equivalent blocking voltage to Si; moreover, it

allows SiC to operate at voltages that were considered impossible in power electronics with Si technology. Third, the thermal conductivity of SiC is 3.7 W/cm·K while silicon exhibits roughly 1.6 W/cm·K [9]. This increase in thermal conductivity leads to higher current-carrying capability and more power-dense electronics. Finally, the higher electron mobility as well as the higher electron saturation velocity allows for higher frequency operation [7]. As commonly known, the increase in switching frequency of a power system directly influences the size of passive components and greatly increases power density.

As described in SiC versus Si—Evaluation of Potentials for Performance Improvement of Inverter and DC–DC Converter Systems by SiC Power Semiconductors, one of the most tangible advantages of SiC is the significantly reduced switching loss [11]. This is partially due to the lack of the current tail found in Si IGBT devices and the ability to eliminate reverse recovery through

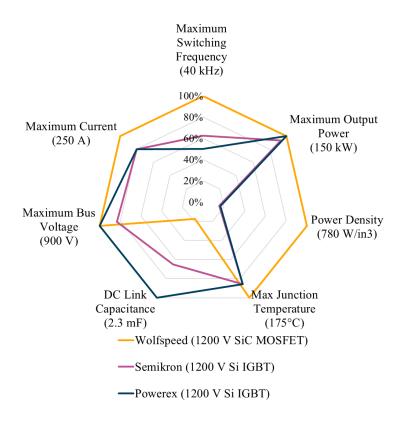

Figure 3. Performance Improvements of SiC over Si-based Inverters [10]

the use of an anti-parallel SiC Schottky diode [9]. Figure 3 portrays three technology demonstrating inverters: one using Wolfspeed's 1200 V SiC MOSFETs and the other two using silicon IGBT technology. As clearly illustrated in the figure, the SiC inverter exceeds the Si versions in switching frequency rating, maximum current rating, power density, maximum bus voltage, maximum junction temperature rating, and requries the lowest DC link capacitance [10]. The large improvements over silicon make SiC a perfect candidate for future power modules and power electronic technology. As stated by Joseph Carr, et al., "This is particularly true at medium-voltage levels where fast switching devices based on silicon are nonexistent and where new and ultra-efficient converter systems are required for future energy distribution networks." [12]. Considering the need for power electronics to unleash the full potential of alternative energy sources as discussed in the previous section, SiC is the suitable semiconductor technology to fill the current voids in power conversion systems.

## 1.3 Issues in Silicon Carbide Power Modules

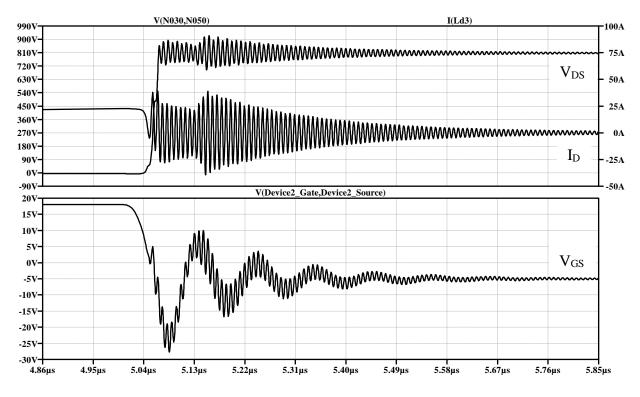

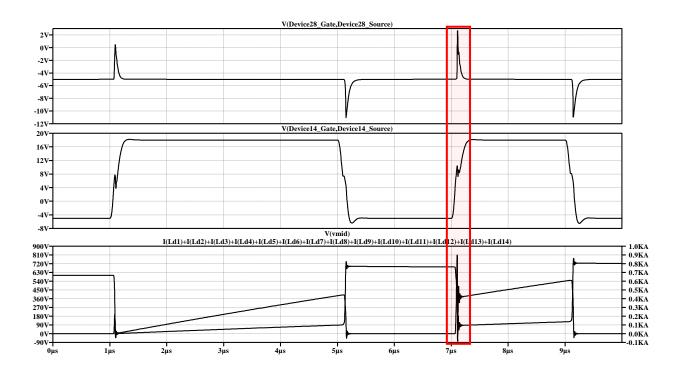

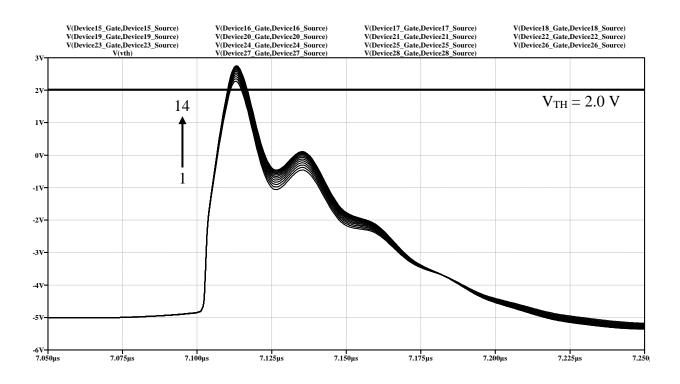

Significant advancements in semiconductor technology do not come without inherent challenges. The same fast-switching behavior that permits power-dense and high-efficiency converters carries with it negative side-effects that need to be well understood when designing power modules and systems using wide bandgap technology [13]. One key side-effect under investigation in this effort is a high-frequency oscillatory behavior measured on the gate node of SiC power modules when operated at high-speeds (large dv/dt and di/dt). Under extreme circumstances this phenomenon can become unstable and destroy the switch position in the power module. An example of these high-frequency oscillations can be seen in Figure 4, which was obtained during double-pulse testing in a clamped inductive load simulation. The gate voltage waveform exhibits frequencies greater than 100 MHz that begin to grow rapidly during the turn-off of the module. This event

Figure 4. High-Frequency Oscillatory Gate Voltage during Turn-Off of SiC Power Module

would likely be destructive in a real-world test as the high-frequency oscillations cause parasitic turn-on and a brief shoot-through event. A greater understanding of the variables at play during this transition are necessary to reliably utilize the wide bandgap technology.

While manufacturers are currently able to produce SiC in six-inch-diameter wafers commercially with eight-inch-diameter wafers being demonstrated in development, it is still very difficult to obtain a silicon carbide wafer without defects [14]. To combat the defect density issues plaguing SiC materials, MOSFET manufacturers design relatively small chip areas when compared to silicon devices [11]. This process greatly increases the device yield from a SiC wafer and is extremely advantageous to decrease the high cost associated with SiC MOSFETs. Although a small chip area is beneficial to yield and to cost, it comes as a tradeoff for a higher on-state resistance and therefore a decreased current-carrying capability [14].

For the smaller area SiC MOSFETs to be used in high-power electronic systems, many devices must be operated in parallel to produce a single switch position. This practice is commonly carried out inside a power module where a single substrate and baseplate assembly can provide low-impedance connections between the MOSFETs. The downside of many paralleled devices in a single power package stems from the wafer variations of critical parameters such as transconductance and threshold voltage [15]. During a high-speed (large dv/dt or di/dt) event, any discrepancies in turn-on threshold can lead to one MOSFET turning on first and experiencing the full system current before its paralleled counterparts turn on [13] [16]. This can lead to premature device failure and negatively affect the reliability of the power module.

## **1.4 Proposed Solution**

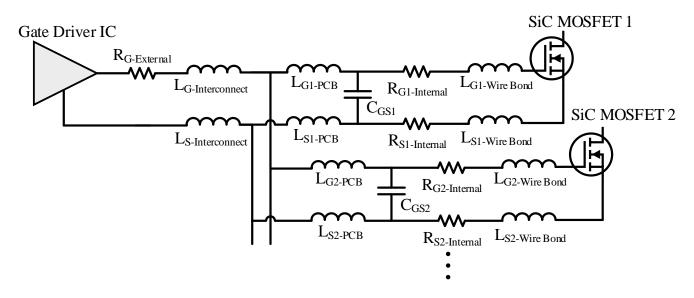

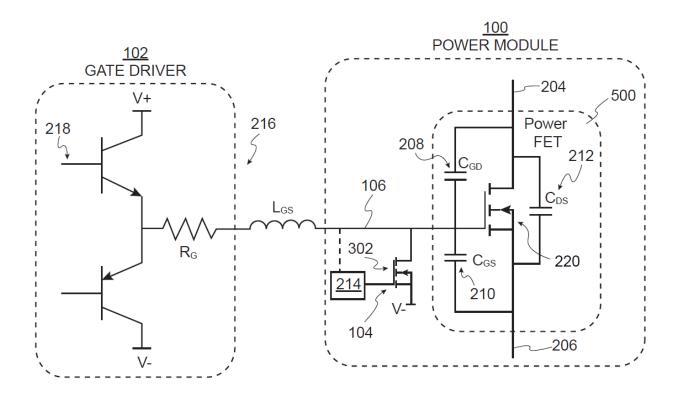

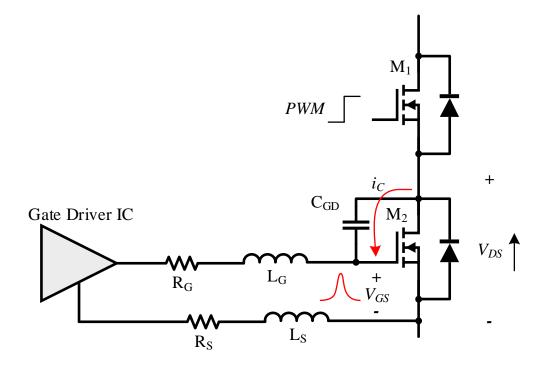

There are three planned components of the solution to the issues described in Section 1.3. The first includes the reduction of parasitic inductance on the gate and source connection PCB internal to the SiC power module. The second consists of transitioning from a single internal gate resistor per MOSFET in the power module to an impedance network comprised of a gate resistor, a source resistor and an optional gate-source capacitor per MOSFET. Finally, with the likely additional resistance necessary to combat the high-frequency oscillations, an active clamping circuit, also known as a Miller Clamp, will be added to each new impedance network of the MOSFETs' gate and source kelvin connections [13] [15] [17]. This theory is supported in literature as stated by Andrew Lemmon et al., "In the case that the reduction of switching speed is accomplished by increasing the value of the series gate resistance, this solution also increases the risk of Miller turnon (and shoot-through in half-bridge circuits). Clearly, better techniques are needed to reduce the susceptibility of applications to self-sustained oscillation without

Figure 5. Gate Impedance Network Model with Parasitics and Tunable Components

Figure 6. Simplified Circuit of Gate Driver and Power MOSFET with Clamping Device [18]

trading away the low-loss switching behavior that is one of the major attractions of WBG devices." [13] The proposed objectives for this thesis intend to provide solutions for these issues concerning the current state of wide bandgap technology.

The importance of a low inductance gate connection is well known in high-speed power electronics as stated by Sadik et al., "...when increasing the switching speeds, it was found that the gate oxide was exposed to voltages exceeding the recommended operation values. This could lead to reliability issues, particularly when high switching speeds are targeted. Moreover, a poorly designed gate-drive connection leading to high parasitic inductance in the gate loop can also be harmful for the device immunity." [15] It is critical to guarantee that all of the MOSFETs in a power package maintain a safe operating gate voltage. The lumped-element, parasitic model and associated simulations will provide clarity into this matter.

Figure 5 illustrates the proposed shift from a single gate resistor per MOSFET internal to the SiC power module to individual gate impedance networks optimized for high reliability, maximum switching speed, and simple drive requirements. Figure 6 displays the active clamping circuit that will be utilized as an integral part of the gate and source impedance network. The clamping circuit will directly connect the gate of the MOSFET to the kelvin source connection; therefore, any gate or source resistors used in the network are bypassed, and a very-low-impedance path is created [3] [18]. The clamping circuit also has the ability to hold the gate to a known negative potential again bypassing any gate or source resistors in the network [18]. Both revisions of the gate and source connection PCB are proposed to be investigated during this effort.

#### **1.5 Objectives of Thesis**

The chief objective of this thesis is to investigate the gate network parasitics of a silicon carbide power module, the CAS325M12HM2, featuring a large quantity of paralleled SiC MOSFETs in

order to increase performance, to eliminate instabilities, and to simplify the gate drive requirements. This objective will be achieved through the following process:

- Accurately model the parasitics in the gate and source connection network of a highperformance SiC MOSFET power module.

- Develop a method for acquiring properly sized gate resistor, source resistor, and gatesource capacitor values to compensate the network.

- 3) Advance the technology described in the author's patent filing, [18], by expanding the use of the Miller Clamping device to each MOSFET inside the SiC power module.

- Validate the gate impedance network performance and reliability improvements via simulation results in a clamped inductive load test setup.

#### **1.6** Organization of Thesis

This thesis will be comprised of six chapters starting with an introduction and theoretical background in Chapter 1. The lumped-element, parasitic model of the gate network in a state-of-the-art SiC power module will be obtained through theoretical calculations, physics simulations, and laboratory measurements in Chapter 2. In Chapter 3, the lumped-element model will be used to conduct circuit simulations to determine oscillation-eliminating gate resistance values in the power module. Chapter 4 will investigate the effects of parameter variances in SiC MOSFETs on switching performance. Three topologies of Miller Clamp circuits will be investigated and assessed in Chapter 5. Chapter 6 will contain the conclusions and discussions of future work.

# 1.7 References

- [1] ABB Communications, "Power Electronics: The Hidden Technology that Makes the Modern World Run," 14 May 2013. [Online]. Available: http://www.abb.com/cawp/seitp202/85b14cadbc1d544bc1257b5b003de5af.aspx.

[Accessed 26 May 2018].

- [2] Bloomberg New Energy Finance, "2018 Sustainable Energy in America Factbook," The Business Council for Sustainable Energy, 2018.

- [3] A. Volke and M. Hornkamp, IGBT Modules: Technologies, Driver and Application, Munich: Infineon Technologies AG, 2011.

- [4] S. M. Shinde, K. D. Patil, S. S. Khairnar and W. Z. Gandhare, "The Role of Power Electronics in Renewable Energy Systems Research and Development," in *Second International Conference on Emerging Trends in Engineering and Technology*, Nagpur, India, 2009.

- [5] Infineon, "Power Products," Infineon, [Online]. Available: https://www.infineon.com/cms/en/product/power/. [Accessed 26 May 2018].

- [6] P. Friedrichs, "Silicon Carbide Power Semiconductors New Opportunities for High Efficiency," *IEEE Conference on Industrial Electronics and Applications (ICIEA), Singapore*, 2008.

- [7] Microsemi PPG, "Gallium Nitride (GaN) versus Silicon Carbide (SiC) in The High Frequency (RF) and Power Switching Applications," [Online]. [Accessed 27 May 2018].

- [8] Y. Solbakken, "Si vs SiC Devices," 9 December 2016. [Online]. Available: https://www.switchcraft.org/learning/2016/12/9/si-vs-sic-devices. [Accessed 26 May 2018].

- [9] J. Biela, M. Schweizer, S. Waffler and J. Kolar, "SiC versus Si—Evaluation of Potentials for Performance Improvement of Inverter and DC–DC Converter Systems by SiC Power Semiconductors," *IEEE Transactions on Idustrial Electronics*, vol. 58, no. 7, pp. 2872 -2882, 2011.

- [10] W. A. Curbow, D. Martin, B. McPherson, S. Minden, J. Hayes and T. McNutt, "A High-Power-Density, SiC-Based, 150 kW Inverter," in APEC 2018, San Antonio, Texas, 2018.

- [11] I. Kortazar, I. Larrazabal, D. Ortega and M. K. Das, "Analysis of the Impact of Silicon Carbide modules in Wind and Traction Applications," in *PCIM Europe 2017*, Nuremberg, Germany, 2017.

- [12] J. A. Carr, D. Hotz, J. C. Balda, H. A. Mantooth, A. Ong and A. Agarwal, "Assessing the Impact of SiC MOSFETs on Converter Interfaces for Distributed Energy Resources," *IEEE Transactions on Power Electronics*, vol. 24, no. 1, pp. 260 - 270, 2009.

- [13] A. Lemmon, M. Mazzola, J. Gafford and C. Parker, "Instability in Half-Bridge Circuits Switched With Wide Band-Gap Transistors," *IEEE Transacations on Power Electronics*, vol. 29, no. 5, pp. 2380 - 2392, 2014.

- [14] J. Senzaki, S. Hayashi, Y. Yonezawa and H. Okumura, "Challenges to Realize Highly Reliable SiC Power Devices," in 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, 2018.

- [15] D.-P. Sadik, J. Colmenares and P. Ranstad, "Analysis of Parasitic Elements of SiC Power Modules with Special Emphasis on Reliability Issues," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 4, no. 3, pp. 988 - 995, 2016.

- [16] K. Puschkarsky, T. Grasser, T. Aichinger, W. Gustin and H. Reisinger, "Understanding and Modeling Transient Threshold Voltage Instabilities in SiC MOSFETs," in *Reliability Physics Symposium (IRPS)*, Burlingame, CA, USA, 2018.

- [17] T. Funaki, "A Study on the Self Turn-On Phenomenon of Power MOSFET Induced by the Turn-Off Operation of Body Diodes," *IEICE Electronics Express*, pp. 1-6, 2014.

- [18] W. A. Curbow and D. Martin, "Power Modules Having An Integrated Clamp Circuit and Process Thereof". United Stated Patent 62/462,552, 23 February 2017.

- [19] N. Mohan, T. Undeland and W. Robbins, Power Electronics: Converters, Applications, and Design, Hoboken, NJ: John Wiley & Sons, Inc., 2003.

## **CHAPTER 2**

#### PARASITIC ELEMENTS OF THE GATE NETWORK

This chapter presents the procurement of the parasitic elements in the gate-source network of a high-performance SiC power module. The three elements consist of finite material resistance, gate-source capacitance, as well as mutual and self-inductance. Each of the three parasitics are crucial for obtaining an accurate model of the gate-source network for the power module; therefore, three methods of obtaining the values are discussed in this chapter. The methods include theoretical calculations, simulations using the computer software COMSOL, and physical measurements of the circuit in a laboratory. Furthermore, the gate-source network is separated into three distinct sections: the first consists of the gate driver connector, the second is made up of the parallel planes inside the gate-source PCB, and the third comprises of the gate wirebond as well as the kelvin source wirebond. The values obtained in this chapter are used extensively in the simulations portrayed in the following chapter.

## 2.1 Gate Driver to PCB Interconnects

The first section is comprised of the gate driver to gate-source PCB interconnect. Cree's CAS325M12HM2 features two Samtec connectors, which deliver the gate signals down to the PCB inside the power module. These connectors are composed of ten, vertical, 10 µm flash-gold, aluminum pins. The square pins are 0.51 mm on each side with 2 mm spacing. Five of the pins are designated for the gate connection while the other five pins are designated for the kelvin source connection. Figure 7 indicates the area of interest for this section.

Figure 7. Gate Driver to PCB Interconnect

## 2.1.1 Calculations

To calculate the overall parasitic inductance of the gate-source connector, two phenomena must be considered: the self-inductance of each pin and the mutual-inductance between the adjacent pins. The first component of the inductance, the self-inductance is identical between the ten pins of the connector. The equation governing the self-inductance of a wire with length l and radius ris given by the equation below [1]. The length and radius are in millimeters while the resulting inductance is in nanohenries.

$$L_{s} = 0.2 \left[ l \ln \frac{l + \sqrt{l^{2} + r^{2}}}{r} - \sqrt{l^{2} + r^{2}} + \frac{l}{4} + r \right]$$

(nH) (2.1)

The length of each pin is approximately 11.86 mm. The pins have a square cross-section; therefore, a worst-case radius running from the center of the square to the center of one of the sides is used. This provides a radius of 0.255 mm. Using equation 2.1 to calculate the self-inductance

of a single pin, the value is found to be 9.02 nH. This result is assumed to be valid based on the common assumption of approximately 1 nH/mm for wires of this size [2].

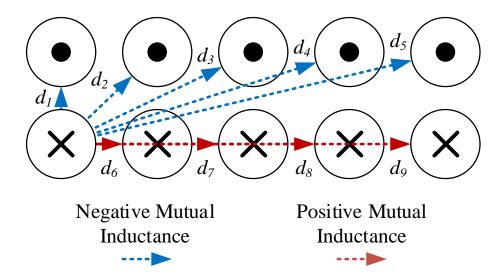

The self-inductance of the connector is only a part of the actual inductance seen by the gate driver. The remaining piece, the mutual-inductance, commonly works in favor of the system impedance by providing a cancellation of a portion of the self-inductance. Two parallel conductors with currents flowing in opposite directions exhibit a negative mutual-inductance dependent on two parameters of the conductors: their length and their separation distance [2]. Conversely, if two parallel conductors have currents flowing in the same direction, they exhibit a positive mutual-inductance. These two effects are precisely what occurs in the gate driver connector. The polarity of the mutual-inductance determines if the overall inductance of the element will increase or decrease. This effect is easily visualized in Figure 8 where half of the conductors carry current from the gate driver to the power module ( $\times$ ) while the other five pins carry current from the power module back to the gate driver ( $\cdot$ ). Therefore, to determine the total mutual-inductance of a single pin, every other conductor's effect on the pin in question must be considered.

For example, consider the bottom-left (BL) pin of the gate-source connector shown in Figure 8. The other nine pins contribute a unique amount of either positive or negative mutual-inductance, which sum to attain the total mutual-inductance. The other four bottom-row pins contribute positive mutual-inductance while the five top pins contribute negative mutual-inductance. Equation 2.2 narrates this process.

$$M_{BL} = M(d_6) + M(d_7) + M(d_8) + M(d_9)$$

$$- \left( M(d_1) + M(d_2) + M(d_3) + M(d_4) + M(d_5) \right)$$

(2.2)

Figure 8. Cross-Section of Gate-Source Connector Portraying Mutual-Inductance

The mutual-inductance of each pin is modeled with Equation 2.3 where l is the length of a pin in millimeters and d is the distance between the two pins in question also in millimeters [1].

$$M(d_n) = 0.2 \left[ l \ln \frac{l + \sqrt{l^2 + d_n^2}}{d_n} - \sqrt{l^2 + d_n^2} + d_n \right]$$

(nH) (2.3)

The distance between each pin is calculated simply with the Pythagorean theorem as the pins are aligned in a 2 mm by 2 mm grid. Using the acquired distances shown in Table 2 as well as a pin length of 11.86 mm, each pin's mutual-inductance contribution is calculated and the results are displayed in Table 2 for the bottom-left conductor. Each of the components are summed to find the total mutual-inductance that the bottom-left pin experiences with Equation 2.2. As each pin is affected by five anti-parallel conductors and only four parallel conductors, the overall mutual-inductance of any pin is negative. This leads to a decrease in the total amount of inductance that the gate-source connector exhibits.

| Distan | Distance (mm) |                    | ictance (nH) |

|--------|---------------|--------------------|--------------|

| $d_1$  | 2             | M <sub>1</sub> (-) | 3.878        |

| $d_2$  | $2\sqrt{2}$   | M <sub>2</sub> (-) | 3.204        |

| $d_3$  | $2\sqrt{5}$   | M <sub>3</sub> (-) | 2.397        |

| $d_4$  | $2\sqrt{10}$  | M4 (-)             | 1.865        |

| $d_5$  | $2\sqrt{17}$  | M <sub>5</sub> (-) | 1.512        |

| $d_6$  | 2             | $M_{6}(+)$         | 3.878        |

| $d_7$  | 4             | ${ m M}_{7}(+)$    | 2.584        |

| $d_8$  | 6             | $M_{8}(+)$         | 1.941        |

| $d_9$  | 8             | ${ m M}_{9}(+)$    | 1.550        |

Table 1. Distance between Conductors with Corresponding Mutual-Inductance

The final step for calculating the total inductance of the conductor consists of combining the mutual-inductance and the self-inductance of each pin, simplifying each side of the conductor into a single inductance by considering the five paralleled conductors, and ultimately summing the two inductances from each side of the connector. The first step is displayed in Table 2 where the self-inductance of each pin is summed with its mutual-inductance component to give way to the effective inductance of each pin. Pins in the same column exhibit an equal mutual-inductance component and have an equal effective inductance; therefore, the outcome for only the bottom row of pins is shown.

$$L_{Row} = \left[\sum_{x=1}^{5} \frac{1}{L_{eff}(x)}\right]^{-1}$$

(2.4)

The effective inductances of each pin are then paralleled with the simple calculation of paralleled inductors as shown in Equation 2.4. Using this equation, the inductance of one row of five pins is 1.301 nH. Considering the other row of five pins, the total calculated inductance of the gate-source connector is 2.602 nH.

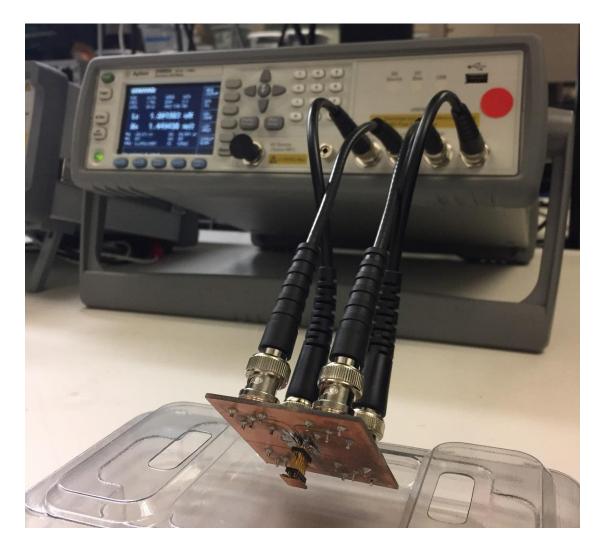

#### 2.1.2 Measurement

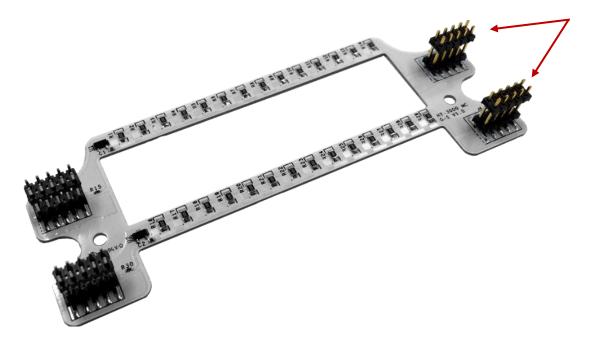

The inductance calculation obtained in the previous section must be validated through measurement to ensure that it is an acceptable value to create an accurate gate network model. In order to measure such a miniscule inductance value, extremely precise equipment must be utilized. The equipment chosen for this procedure is Agilent's E4980A 1 MHz precision LCR meter. Per the user manual, the absolute measurement accuracy in the 1 nH - 10 nH range is between 1% and 10% at a measurement frequency of 1 MHz. This is the highest operating frequency of this precision LCR meter, and it is the frequency at which all the measurements are obtained. When measuring inductances in the few-nanohenry range, it is impossible to obtain accurate results with the standard 4-wire alligator-clip probes. The small movements of the wires during open and short calibration nullify the corrections and generate nonsensical results. To attain meaningful results from this equipment, an inductance measurement fixture must be designed. This fixture keeps the coaxial wires and device under test (DUT) in the same position during each calibration as well as during the actual measurement, which ensures the most accurate results.

| Pin Number (x)    | $L_{s}$ (nH) | $M_x$ (nH) | $L_{eff-x}$ (nH) |

|-------------------|--------------|------------|------------------|

| 1 (Bottom-Left)   | 7.4296       | -2.9041    | 4.5255           |

| 2 (Bottom-LC)     | 7.4296       | -2.2689    | 5.1606           |

| 3 (Bottom-Center) | 7.4296       | -2.1583    | 5.2713           |

| 4 (Bottom-RC)     | 7.4296       | -2.2689    | 5.1606           |

| 5 (Bottom-Right)  | 7.4296       | -2.9041    | 4.5255           |

Table 2. Self-Inductance, Mutual-Inductance, and Total Pin Inductance

The four measurement signals required by the LCR meter include two force connections and two kelvin connections. This is a common 4-wire technique designed to eliminate error from the measurement of the wires connecting the device under test. A relatively large current can flow through the force connections during the test; furthermore, this current induces a voltage drop across the finite resistance of the conductors. Using the 4-wire technique, this voltage drop is not included in the inductance measurement as the true measurement is performed at the terminals of the DUT through the other two conductors. This is commonly known as a kelvin connection.

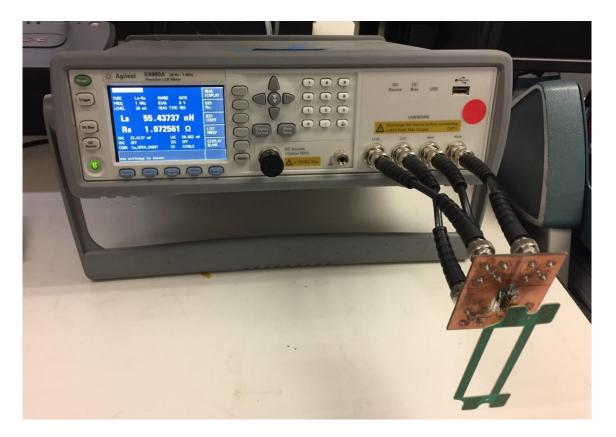

Figure 9. Inductance Measurement Fixture and Agilent's Precision LCR Meter

Another requirement of the inductance measurement test fixture is an easily accessible method to calibrate the LCR meter. Calibration is performed via an open measurement followed by a short measurement across the location of the DUT. Following the calibration procedure, the test fixture is prepared to accurately measure the gate-source connector. Finally, the feet of the connector are soldered onto the test fixture in the same area where the short measurement is conducted. The connector is open at the top and therefore must be linked to complete the current loop. As seen in Figure 9, a small piece of copper is used to connect the two rows of pins on the open end of the connector. As soon as the measurement loop is closed, the inductance and series resistance values are displayed for the test condition of 1 MHz and 20 mA of force current. The values obtained from this measurement are 2.097250 nH and 1.847527 m $\Omega$ . The percent error between the calculated value and the measured value is 19.4%, which is obtained using Equation 2.5.

$$Error \% = \left[\frac{L_{measured} - L_{calculated}}{L_{calculated}}\right] \times 100$$

(2.5)

While the error percentage is rather high, the measured value is only 0.69 nH from the theoretical calculations. This level of accuracy is acceptable when considering the extremely low values of inductance provided by this piece of the system. When taking into account the larger parasitic inductances of the system, this small discrepancy between measured and calculated values is considered in the noise floor. In the next section, a physics-based simulation provides another take on the parasitic inductance of the gate-source connector.

#### 2.1.3 COMSOL Simulations

To determine whether the calculation or the measured value of parasitic inductance is more accurate, a third method, COMSOL Multiphysics Simulator, is used. COMSOL is a powerful multi-physics solver capable of modeling electromagnetics, structural mechanics, fluid and heat transfer, as well as chemical reactions. For this investigation, an electromagnetic physics solver is utilized focusing on magnetic and electric fields, which allows for parasitic inductance, capacitance, and resistance extraction of a 3D CAD model.

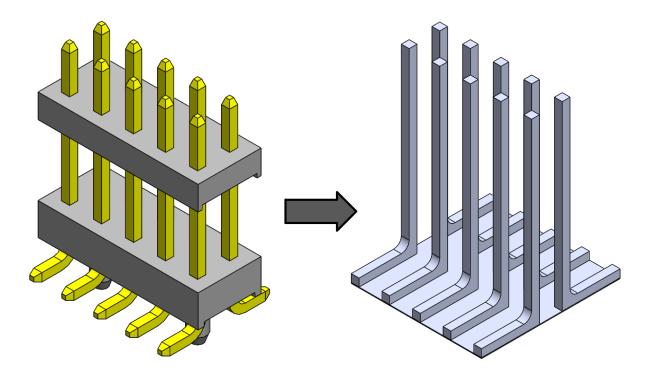

The first step of the simulation procedure comprises generating a model optimized for use with COMSOL. A Solidworks model is provided by Samtec, the manufacturer of the gate source connector, but the model contains unnecessary information that greatly lengthens the time required to simulate the connector. Only the required information pertinent to the inductance measurement needs to be included in the model. For this reason, the plastic, structural pieces are removed from

Figure 10. Manufacturer's 3D Model vs. 3D Model Optimized for COMSOL

the model as well as the chamfered ends of the pins. Figure 10 illustrates the manufacturer's model of the connector and the modified model that is simulated in COMSOL. Additionally, the simulation requires a closed path for the current to flow just as described during the measurement process. For this reason, a flat plane is added to the model to create a path for current to flow from the bottom of one side of the pins to the bottom of the other set of pins. The plane is displayed in Figure 10.

Figure 11. Constructed Mesh of Gate Source Connector

Next, the model must be meshed into an array of much smaller shapes, which are used by the physics solver to obtain a solution for the system. In COMSOL, meshing the 3D model is the most important step to creating an accurate and efficient model to simulate. If the mesh elements are too small, the solver will take an extremely long time to solve the system or the solver may never converge; however, if the mesh elements are too large, the result of the simulation may be inaccurate. The constructed mesh for the gate source connector is shown in Figure 11. Areas that are very thin such as the bottom copper plane have a very fine mesh while the larger pins have a coarser mesh. This mesh is created with COMSOL's automatic mesh settings set to fine, which yielded very good results. As this is a relatively simple model, the solver takes less than an hour to achieve a numerical solution with a 0.001 rated accuracy.

After the model has been meshed appropriately, the material of the domains must be selected, a ground and source boundary must be defined, and a stationary or frequency solver must be selected. The materials used for this simulation are copper for the rows of pins and the bottom plane while the remaining domains are set to air with both materials optimized for electromagnetic simulation. The ground boundary is defined as the top faces of five of the pins in one row while the source terminal is defined as the top faces of the other five pins. The source terminal is defined as a current source and is set to 1 A. Finally, a frequency domain solution is required to obtain the inductance; therefore, the solver is set to the frequency domain with a value of 1 MHz in order to match the point at which the measurements are obtained, and the simulation setup is complete.

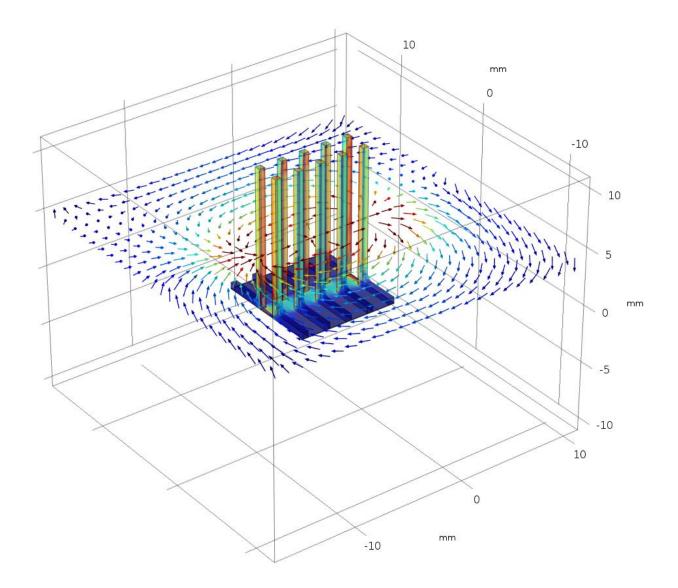

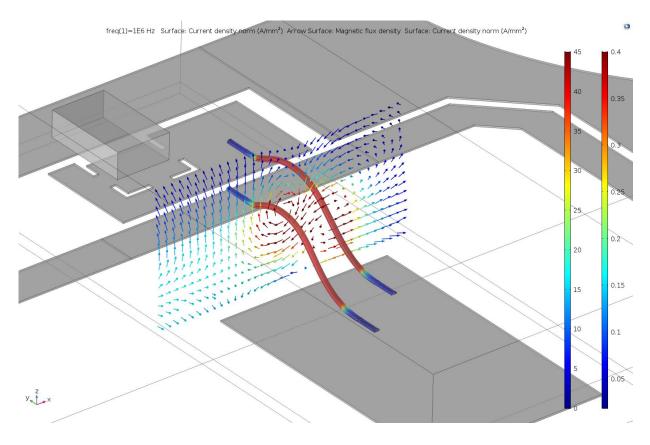

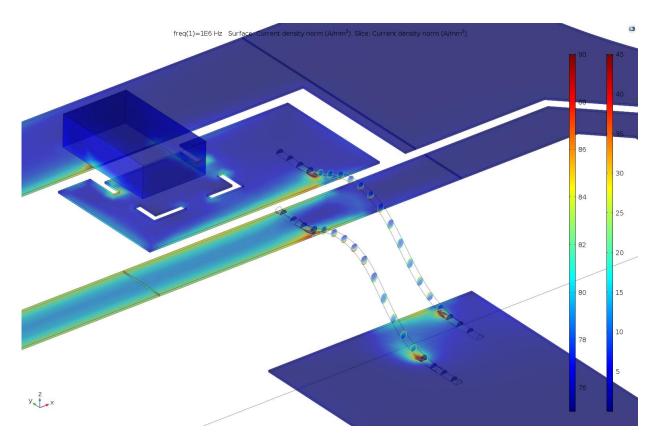

After the solution converges and a result is obtained, COMSOL offers a myriad of visual aids to effectively portray the data. As seen in Figure 12, the surface of the connector contains the current density data in A/mm while the arrow-surface on a cut-plane in the air domain portrays the

Figure 12. Magnetic Flux Density and Current Density of Gate Source Connector magnetic flux density ( $\mu$ T). These results are helpful for visualizing the current flow and magnetic fields in the simulation. If the current or field does not appear as expected, the model should be re-meshed and solved again. Finally, a global expression is defined to find the parasitic inductance and resistance. The values obtained from this simulation are 2.6114 nH and 1.3840 m $\Omega$ , which match very closely to the calculated value. The percent error between the calculated value and the simulated value is 0.35% as per Equation 2.5.

# 2.2 Gate & Kelvin-Source PCB

The largest contributor to the parasitic inductance of the gate-source network is the printed circuit board (PCB). This section is the physically largest portion of the system and offers the most area for improvement between the existing design and one optimized for low-inductance routing. The current layout is composed of a single-layer containing multiple copper planes. One plane makes up the gate net, another creates the kelvin source net, and the remaining shapes create the wirebond locations for each MOSFET as displayed in Figure 13. As these planes are all on a single copper layer, they exhibit little benefit from flux cancelation in the form of mutual-inductance. As in the previous section, the three methods of parasitic extraction: calculation, measurement, and simulation are described in the following sections.

## 2.2.1 Calculations

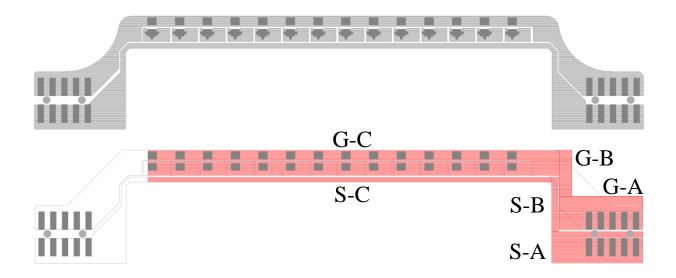

To apply standard inductance calculations to the planes of the PCB, small modifications of the shapes must be made to allow the equations to apply. Instead of the 45° corners and angled sections of the planes, a rectangular approximation is created to allow Equation 2.6 to be applied. The rectangular approximations for the shapes are shown in Figure 13, and each rectangle is labeled as either G for gate net or S for source net with an A, B, or C identifier.

As with the gate-source connector, the first element to calculate is the self-inductance and is governed by the straight rectangular trace inductance approximation shown in Equation 2.6 [3].

$$L = \frac{\mu_0 l}{2\pi} \left[ \ln\left(\frac{2l}{w+h}\right) + \frac{w+h}{3l} + 0.50049 \right] (\text{H})$$

(2.6)

Assuming a fixed height or copper thickness of 0.017526 mm, the remaining width and length for each rectangle are measured in Allegro PCB and are displayed in Table 3. Using these measurements, the self-inductance of each rectangle can be calculated. These values are also

Figure 13. Gate Kelvin PCB Layout (Top) and Estimated Area for Calculations (Bottom)

included in Table 3. As expected, the planes create a large amount of parasitic inductance with the total self-inductance calculated as 155.519 nH. As the geometry of the copper was approximated for ease of calculation, there is likely to be a higher error percentage between the calculated and the measured or simulated values. Next, the mutual-inductance is calculated to close this section.

| Segment | Width (mm) | Length (mm) | Height (mm) | Inductance (nH) |

|---------|------------|-------------|-------------|-----------------|

| G-A     | 5.594      | 14.224      | 0.017526    | 6.416           |

| G-B     | 2.159      | 7.868       | 0.017526    | 4.046           |

| G-C     | 4.318      | 69.850      | 0.017526    | 55.794          |

| S-A     | 5.334      | 15.494      | 0.017526    | 7.350           |

| S-B     | 1.143      | 9.271       | 0.017526    | 6.144           |

| S-C     | 0.889      | 68.580      | 0.017526    | 75.770          |

| Total   |            |             |             | 155.519         |

Table 3. Self-Inductance Calculation of Gate Kelvin PCB

The mutual-inductance between two equal parallel conductors can be calculated with Equation 2.7 [3]. This calculation is appropriate for this application because the two shapes have an equal amount of separation for their entire length.

$$M = \pm \frac{\mu_0 l}{2\pi} \left[ \ln \left( \frac{l}{s} + \sqrt{1 + \frac{l^2}{s^2}} \right) - \sqrt{1 + \frac{s^2}{l^2}} + \frac{s}{l} \right] (H)$$

(2.7)

There are only two variables necessary for the mutual-inductance calculation: conductor separation, *s*, and the length of the conductors, *l*. The separation is a constant 10 mils between the shapes, which is equal to 0.254 mm. The length is total sum of the G rectangles and is 93.218 mm. Applying Equation 2.7 produces a mutual-inductance value of -104.4 nH, which is a substantial portion of the self-inductance. Finally, summing the individual components of the total inductance, the self-inductance of 155.519 nH and the mutual-inductance of -104.427 nH, a value of 51.092 nH is obtained. When compared to the 2.6 nH provided by the input connector from the first section, the PCB delivers significantly more parasitic inductance to the system. The next subsection compares the theoretical calculations to the measured values.

#### 2.2.2 Measurements

The DUT in this section is the printed circuit board, but to obtain the inductance measurement from the PCB, the connector from the first section is needed for connection to the fixture. After the measurement is complete, the inductance of the connector is subtracted from the measurement to compare directly with the theoretical calculation value. Like the procedure in the previous measurement section, the custom, inductance extraction fixture is used to calibrate the LCR meter with an open measurement and a short measurement. After fixture compensation, the DUT is prepared by soldering a piece of copper across the farthest wirebond pads in order to complete the

Figure 14. Gate Kelvin PCB Mounted on Substrate Assembly

loop. The PCB is soldered to the bottom of the gate-source connector and the fixture is connected to the LCR meter and can be seen in Figure 14. Also shown in Figure 14, the inductance measurement is 55.437 nH for the gate-source connector and the PCB. To ensure accurate results, an additional parasitic extraction tool is utilized to verify the results from the Agilent LCR meter. Keysight's E4990A impedance analyzer provided the second measurement, and at 1 MHz, the value of 54.161 nH is obtained. To directly compare the acquired measurement value to the calculations, the measured gate-source connector value must be subtracted from the total measurement value.

$$\frac{55.437 \text{ nH} + 54.161 \text{ nH}}{2} - 1.903 \text{ nH} = 52.896 \text{ nH}$$

(2.8)

As shown in Equation 2.8, the two measured values are averaged, and the gate connector inductance is subtracted to find the total inductance of 52.896 nH for the PCB. When compared to the calculated value, of 51.092 nH, the difference is only 1.80 nH and the error percentage is 3.4%. The small amount of error between the two methods of parasitic extraction reassure the methods in this investigation; moreover; in the next section, the COMSOL simulations provides another take on the parasitics of the gate-source PCB.

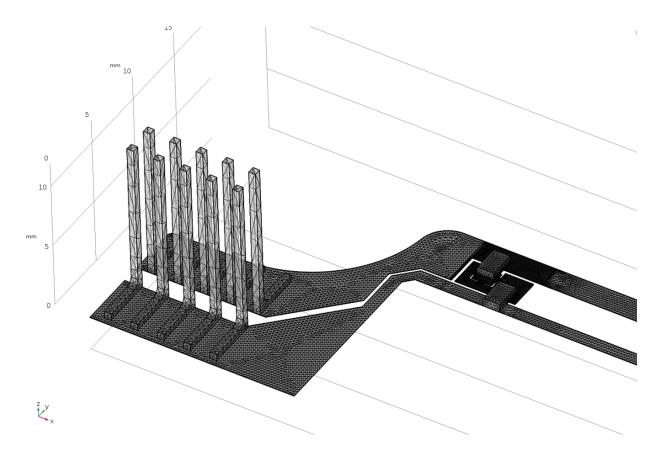

#### 2.2.3 COMSOL Simulations

Following a similar procedure to the connector simulation, the first step of modeling the PCB in COMSOL is to create a 3D model optimized for simulation. The process includes removing any unnecessary information such as plastic mechanical features or floating conductive elements that

Figure 15. Mesh Construct for Solving COMSOL Electromagnetic Simulation of PCB

will render the system unsolvable. Using the layout software, Allegro PCB, a DXF file is generated, which contains the exact dimensions of the copper traces of the PCB. This file is easily imported into Solidworks as a sketch and is extruded to the correct copper thickness of 1 oz. or 0.0014 inches. A rectangle equivalent to the size of an 0805-resistor is drawn and extruded to the correct height and added to the model in place of the gate resistor. For this model, the gate source connector is added as well to complete the basic 3D CAD model.

There are as many as fourteen MOSFETs in parallel in the HT-3000 power module under investigation. It is necessary to determine the inductance to each position to create an accurate parasitic model for circuit simulation. For this reason, the simulation begins with the first position inside the module as shown in Figure 15. The 0805-resistor part created previously is re-used to close the current loop at the first MOSFET position, which is closest to the input connector. The last element necessary to simulate the model using COMSOL is an appropriately sized air domain. For this model, two air domains are used to increase the accuracy of the simulation while decreasing the required simulation time. A small air domain is created around the elements that exhibit fine features such as the resistor pad with thermal relief connections while a larger air domain surrounds the entire 3D model.

Next, the generated 3D model is meshed with a procedure enhanced for large, thin planes such as copper traces in a PCB. Each face of the model is meshed independently with a free-triangular mesh set to an appropriately selected element minimum and maximum dimension size; in particular, the domains with tight spacing require mesh element dimensions with a much smaller minimum size than the larger domains. After the top faces of the PCB have been completed, the meshes are copied to their equivalent bottom-side face. Finally, the two corresponding meshed faces of the PCB are swept together and distributed into three-dimensional shapes for simulation.

After the PCB has been successfully meshed, the small air domain is meshed with a free-tetrahedral mesh algorithm with dimension size set to extremely fine and the large air domain is meshed with dimension size set to normal. The meshed model, which is shown in Figure 15 is now ready for electromagnetic simulation.

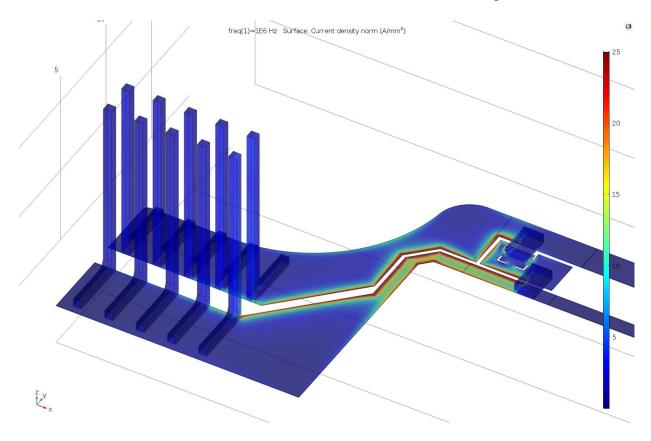

The simulation takes several hours to converge to the set relative tolerance of 0.001. After the simulation is complete, the parasitic inductance is determined by adding a global evaluation expression comprising of the imaginary component of the impedance divided by the angular frequency. For the first position, an inductance of 19.696 nH was obtained. This procedure is repeated for the final MOSFET position to compare to the simulated inductance to the calculated and measured values to determine if the simulation method is accurate. Starting from the 3D CAD model in Solidworks, the small air domain, the resistors, and the wirebond pads are moved to the

Figure 16. Current Density of First Position Shorted at Wirebond Pads

Figure 17. Magnetic Field (A/m) Surrounding Wirebond Pads and Shorting Resistor

last position on the gate-source PCB. The mesh parameters are updated with the correct boundaries and domains, and the simulation is conducted. The results of the simulation for the final position indicate that the inductance is 52.976 nH. These results match the measured values very well with an error percentage of 0.15%. The simulation method is verified as an effective parasitic extraction technique again through this experiment. Additionally, COMSOL is an extremely valuable visualization tool as illustrated in Figure 17, which portrays the magnetic field around the resistor and wirebond pads of the model. The streamline tool is used to visualize the field, and a rainbow color chart is applied to show the magnitude of the field.

## 2.3 Gate & Kelvin Source Wire Bonds

In stark contrast with the previous section, the wirebond is a much smaller contributor of parasitic inductance to the gate network. That being stated, due to the long and narrow geometry of the wirebond, and because there are two wirebonds per MOSFET, the parasitic inductance is non-negligible. The major variable governing the inductance of the wirebond is the length, which varies widely between the different switch positions. For this reason, it is difficult to achieve a low error percentage between the measured and calculated values while the simulated value matches the measured results closely. As in the previous two sections, the three methods of parasitic extraction: calculation, measurement, and simulation are described in the following sections.

## 2.3.1 Calculations

Two methods for calculating the inductance of a wirebond will be evaluated in this section. The first, the straight wire inductance approximation, is simply governed by the length and the radius of the wire. For this case, the wire is a 5 mil wirebond, which has a radius of 0.0635 mm. For both methods of calculating inductance, the length will be swept from 5 mm to 50 mm in 5 mm increments. The equation governing the straight wire inductance approximation is shown below in Equation 2.9 [3]. The results of this method are displayed in Table 5 on the next page.

$$L = \frac{\mu_0}{2\pi} \times l \left[ \ln\left(\frac{l}{r} + \sqrt{1 + \frac{l^2}{r^2}}\right) - \sqrt{1 + \frac{r^2}{l^2}} + \frac{r}{l} + \frac{1}{4} \right] (\text{H})$$

(2.9)

For the next method, Kazimierczuk in *High-Frequency Magnetic Components*, has approximated the inductance of a wirebond with Equation 2.10. Again, the equation's parameters are wirebond radius and length, but the equation is far simpler than the straight wire approximation. As

| Length (mm) | Radius (mm) | Straight Wire<br>Inductance (nH) | Wirebond Approximation<br>Inductance (nH) | Error<br>Percentage |

|-------------|-------------|----------------------------------|-------------------------------------------|---------------------|

| 1           | 0.0635      | 0.55                             | 0.54                                      | 2.26                |

| 2           | 0.0635      | 1.37                             | 1.36                                      | 0.92                |

| 3           | 0.0635      | 2.29                             | 2.28                                      | 0.55                |

| 4           | 0.0635      | 3.28                             | 3.27                                      | 0.39                |

| 5           | 0.0635      | 4.32                             | 4.31                                      | 0.29                |

| 10          | 0.0635      | 10.02                            | 10.00                                     | 0.13                |

| 15          | 0.0635      | 16.24                            | 16.22                                     | 0.08                |

| 20          | 0.0635      | 22.80                            | 22.78                                     | 0.06                |

| 25          | 0.0635      | 29.61                            | 29.59                                     | 0.04                |

Table 4. Self-Inductance Calculation of Wirebonds of Varying Length

portrayed by the results in Table 5, both methods for calculating the inductance of a wirebond are extremely similar with the error percentage shrinking with increasing wirebond length.

$$L \approx \frac{\mu_0}{2\pi} \times l \left[ \ln \left( \frac{2l}{r} \right) - \frac{3}{4} \right]$$

(H) (2.10)

As there commonly exist multiple wirebonds leading to and from a semiconductor device, it is critical to examine the inductive effects shared by two parallel wirebonds [2]. For this study, the two wirebonds are used to connect the designated gate and source pads on the PCB to the corresponding gate and kelvin source locations on the MOSFETs. The mutual-inductance between two parallel wirebonds is given by Equation 2.11.

$$M = \pm \frac{\mu_0 l}{2\pi} \left[ \ln \left( \frac{2l}{s} \right) + \frac{s}{l} - 1 \right]$$

(H) (2.11)

The two parameters controlling the mutual-inductance are s, the separation between the two bonds, and l, the length of the bonds.

| Length (mm) | Separation<br>(mm) | Mutual-Inductance<br>(nH) | Wirebond Self-<br>Inductance (nH) | Total-<br>Inductance (nH) |

|-------------|--------------------|---------------------------|-----------------------------------|---------------------------|

| 3           | 1                  | 0.675                     | 2.279                             | 1.604                     |

| 3           | 2                  | 0.459                     | 2.279                             | 1.820                     |

| 3           | 3                  | 0.416                     | 2.279                             | 1.863                     |

| 4           | 1                  | 1.064                     | 3.269                             | 2.205                     |

| 4           | 2                  | 0.709                     | 3.269                             | 2.560                     |

| 4           | 3                  | 0.585                     | 3.269                             | 2.684                     |

| 5           | 1                  | 1.503                     | 4.309                             | 2.807                     |

| 5           | 2                  | 1.009                     | 4.309                             | 3.300                     |

| 5           | 3                  | 0.804                     | 4.309                             | 3.505                     |

Table 5. Mutual-Inductance Calculation of Wirebonds of Varying Length

The mutual-inductance contributes about 1 nH for a 4 mm wirebond when the two bonds have 1 mm - 2 mm of separation. This value is not significant in regard to the total system inductance, but it is slightly over one-third of the self-inductance, which will greatly affect the die-to-die inductance for the circuit model in the next chapter. According to the wirebond profile for the HT-3000 module, the gate and source wirebonds are approximately 3800  $\mu$ m and 4000  $\mu$ m respectively. For this reason, 4 mm calculation values are used for comparing to the measured and simulated values in the next sections.

### 2.3.2 Measurements

As it is extremely difficult to accurately measure inductances in the few-nanohenry range, the wirebonds are placed in their intended locations in an empty module, and the entire gate-source loop is measured. This will ensure the wirebonds have accurate separation and length related to their actual operation. The inductance extraction fixture from the previous two measurement

sections is the appropriate tool to extract the full gate-source loop inductance. As there can be up to fourteen MOSFETs in parallel in one switch position in this module, the inductance to each position is measured independently. These results are used to generate the die-to-die parasitic values.

To begin, a clean gate-source PCB is populated with 0  $\Omega$  gate resistors and the gate-source connectors. A completed substrate and baseplate assembly provides a base for the PCB and creates a realistic air domain for the measurement. The LCR meter is compensated with an open measurement and a short measurement to ensure that the result does not include the inductance of the fixture. After fixture compensation, the first MOSFET position of the module is wirebonded

| Position | Low-Side<br>Inductance (nH) | Low-Side<br>Resistance (mΩ) | High-Side<br>Inductance (nH) | High-Side<br>Resistance (mΩ) |

|----------|-----------------------------|-----------------------------|------------------------------|------------------------------|

| 1        | 22.55                       | 63.78                       | 20.67                        | 65.42                        |

| 2        | 25.95                       | 72.89                       | 24.11                        | 71.88                        |

| 3        | 28.47                       | 74.68                       | 25.95                        | 76.34                        |

| 4        | 32.43                       | 87.64                       | 29.09                        | 82.58                        |

| 5        | 34.70                       | 87.79                       | 33.28                        | 90.73                        |

| 6        | 38.87                       | 97.23                       | 35.98                        | 95.21                        |

| 7        | 41.17                       | 103.69                      | 38.50                        | 101.08                       |

| 8        | 44.20                       | 107.03                      | 41.66                        | 107.43                       |

| 9        | 46.69                       | 112.26                      | 45.69                        | 116.60                       |

| 10       | 50.50                       | 122.98                      | 48.16                        | 120.82                       |

| 11       | 53.16                       | 126.05                      | 50.58                        | 122.64                       |

| 12       | 56.78                       | 136.32                      | 55.26                        | 133.73                       |

| 13       | 60.33                       | 141.48                      | 58.28                        | 140.87                       |

| 14       | 61.93                       | 140.83                      | 60.29                        | 143.57                       |

Table 6. Inductance Measurement of Gate Kelvin PCB

Figure 18. CAS325M12HM2 Gate Network PCB on Substrate Assembly with Wirebonds

from the designated pads on the PCB directly to the substrate rather a bare die. The gate network loop is completed through the short on the substrate. The wirebonded module subassembly is displayed in Figure 18. The measurement is taken at 1 MHz with the maximum source current available on the Agilent LCR meter, 20 mA. The process is repeated for each of the 14 MOSFET positions on the high-side and low-side of the module, and the results are displayed in Table 6.

Examining the last position's inductance value, the connector, PCB, and wirebonds measurement results in an inductance of 60.29 nH for the high-side as shown in Equation 2.12.

$$L_{Connector} + L_{PCB} + L_{G-Wirebond} + L_{S-Wirebond} = 60.29 \text{ nH}$$

(2.12)

The measurement of only the PCB and connector produce 55.437 nH as shown in Equation 2.13.

$$L_{Connector} + L_{PCB} = 55.437 \text{ nH}$$

(2.13)

This equates to a shared inductance of 4.853 nH for the gate and source wirebonds.

$$L_{G-Wirebond} + L_{S-Wirebond} = 60.29 \text{ nH} - 55.437 \text{ nH}$$

(2.14)

= 4.853 nH

Assuming that the inductance of the gate wirebond is equal to the source wirebond, the sum of the two bonds can be split into two equal parts as shown in Equation 2.15.

$$L_{G-Wirebond} = L_{S-Wirebond} = \frac{4.853 \text{ nH}}{2} = 2.427 \text{ nH}$$

(2.15)

Comparing to the calculated results for a 4 mm wirebond, this result places the spacing between 1 mm and 2 mm, which is exactly as expected; therefore, the measurement process is proven valid.

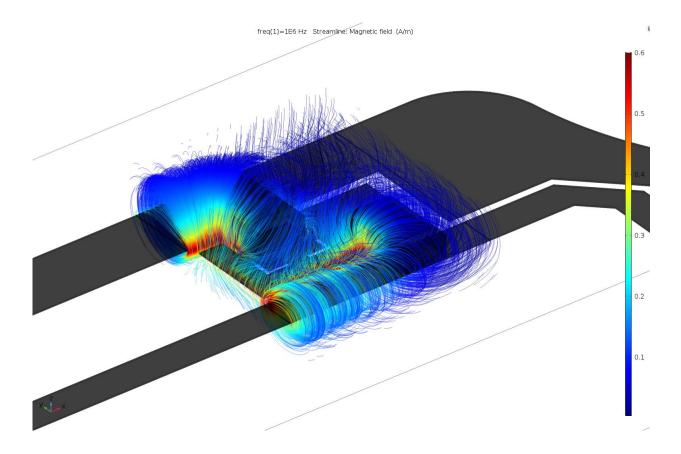

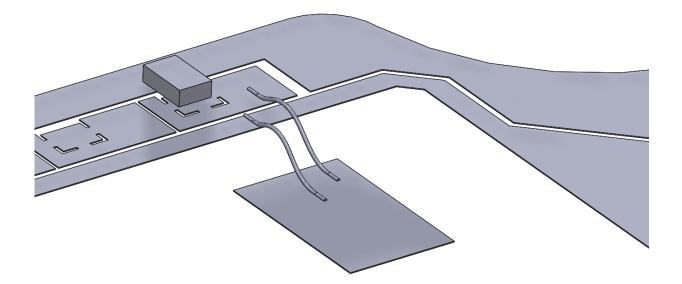

#### 2.3.3 COMSOL Simulations

The verification of the measurements begins with the formation of a 3D CAD model optimized for accurate and fast simulations. As the measurements for this section were conducted on the entire gate loop, and the previous sections' measurements were subtracted away to obtain the wirebond's inductance contribution, the same procedure is repeated for the simulation. Therefore, starting with the 3D model from the connector and PCB, a wirebond and MOSFET must be added to complete the gate loop.

First, to create the wirebond, two lines are drawn to represent the feet of the bonds. They are placed 2 mm apart on the z-axis to simulate the difference in height of the MOSFET on the substrate and the wirebond pads on the top of the PCB. Next, with the help of a few construction lines, a spline is drawn in between the two feet to simulate the approximate shape of a wirebond. A plane is added to the drawing at the end of one of the feet, and a circle with a diameter of 5 mils

Figure 19. 0.005" Diameter Gate and Source Wirebonds Modeled in Solidworks

is added to represent the diameter of the bond. The circle is swept along the spline to give the bond its 3-dimensional form, and the two ends are sliced in create flat feet that will connect to the pads and the MOSFET.

To complete the gate loop, the gate and source bonds must have a conductive path between them. While the gate would be more accurately modeled with a capacitor, the simulation demands a short between the gate and source. To satisfy this requirement, the MOSFET bare die is modeled as a simple rectangle with a depth matching the copper thickness of the PCB and is defined as copper material in COMSOL. With the two additional parts modeled, the assembly is updated to include a wirebond from the gate wirebond pad on the PCB to the MOSFET model, which is placed 2 mm below the PCB, and a source wirebond is added from the MOSFET up to the PCB as shown in Figure 19. The gate loop and 3D model are now complete, and the model is ready to be imported into COMSOL for meshing.

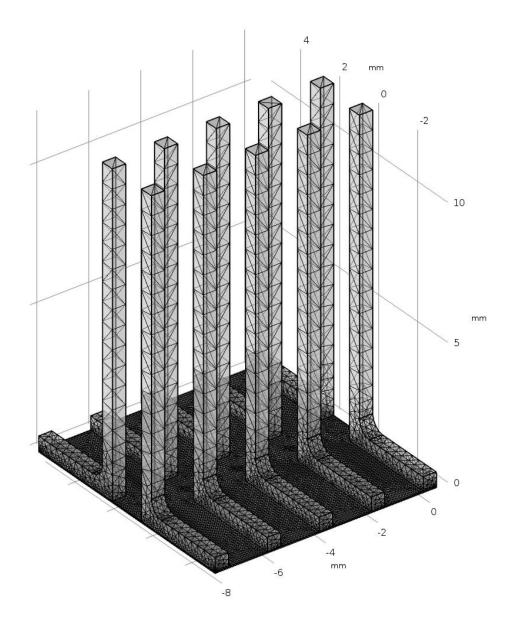

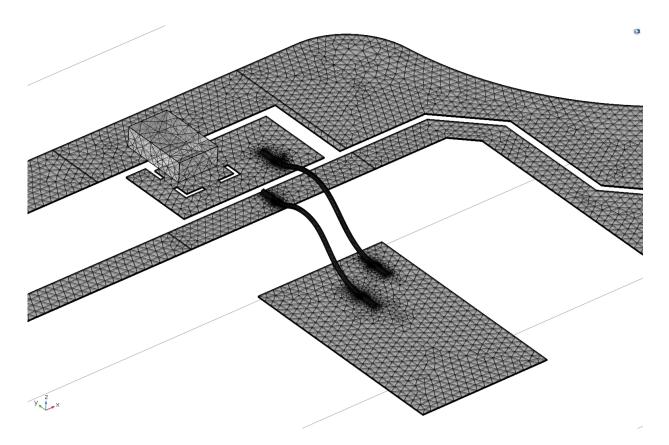

The model is meshed with a technique enhanced for large, thin planes like those found in this model's PCB. Each face of the model is meshed independently with a free-triangular mesh, the face is then copied to its equivalent bottom-side face, and the two corresponding meshed faces are swept together and distributed into three-dimensional shapes for simulation. After the PCB trace meshes are defined, the wirebonds are meshed with an extremely fine free-tetrahedral mesh. This domain sets the minimum element size for the air domain around it; therefore, similar to the PCB simulation, a small air domain is place around the tightly spaced, last position of the model. This small air domain creates a transition from the small mesh elements of the wirebonds and thermal reliefs to a large element size for the majority of the air domain. This significantly decreases the time required to mesh the system and increases the accuracy in the tightly spaced area. The completed mesh for this model is illustrated in Figure 20.

Figure 20. Last Position of Meshed 3D CAD Model in COMSOL

Finally, the simulation is conducted with 1 A of source current at 1 MHz. The simulation took approximately four days to converge due to the extremely fine size of the mesh elements as well as the high-frequency source, but the results proved to be worth the wait. Generating a global evaluation for the inductance of the gate loop resulted in a value of 60.292577 nH, which perfectly matches the high-side, last-position's inductance value of 60.29 nH. Again, the FEA simulation proves to be an effective method for extracting the parasitic inductance.