### University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

12-2018

# Development of a Rapid Fatigue Life Testing Method for Reliability Assessment of Flip-Chip Solder Interconnects

Cody Jackson Marbut University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the <u>Computer-Aided Engineering and Design Commons</u>, <u>Electrical and Electronics</u> <u>Commons</u>, <u>Electro-Mechanical Systems Commons</u>, <u>Manufacturing Commons</u>, <u>and the Power and</u> <u>Energy Commons</u>

#### **Recommended** Citation

Marbut, Cody Jackson, "Development of a Rapid Fatigue Life Testing Method for Reliability Assessment of Flip-Chip Solder Interconnects" (2018). *Theses and Dissertations*. 3101. https://scholarworks.uark.edu/etd/3101

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

#### Development of a Rapid Fatigue Life Testing Method for Reliability Assessment of Flip-Chip Solder Interconnects

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Mechanical Engineering

by

Cody Jackson Marbut University of Arkansas Bachelor of Science in Mechanical Engineering, 2016 University of Arkansas Bachelor of Science in Chemistry, 2016

> December 2018 University of Arkansas

This thesis is approved for recommendation to the Graduate Council.

David Huitink, Ph.D. Thesis Director

Xiangbo Meng, Ph.D. Committee Member

Simon Ang, Ph.D. Committee Member Ashok Saxena, Ph.D. Committee Member

#### Abstract

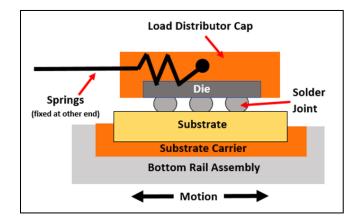

The underlying physics of failure are critical in assessing the long term reliability of power packages in their intended field applications, yet traditional reliability determination methods are largely inadequate when considering thermomechanical failures. With current reliability determination methods, long test durations, high costs, and a conglomerate of concurrent reliability degrading threat factors make effective understanding of device reliability difficult and expensive. In this work, an alternative reliability testing apparatus and associated protocol was developed to address these concerns; targeting rapid testing times with minimal cost while preserving fatigue life prediction accuracy. Two test stands were fabricated to evaluate device reliability at high frequency (60 cycles/minute) with the first being a singledirectional unit capable of exerting large forces (up to 20 N) on solder interconnects in one direction. The second test stand was developed to allow for bi-directional application of stress and the integration of an oven to enable testing at elevated steady-state temperatures. Given the high frequency of testing, elevated temperatures are used to emulate the effects of creep on solder fatigue lifetime. Utilizing the mechanical force of springs to apply shear loads to solder interconnects within the devices, the reliability of a given device to withstand repeated cycling was studied using resistance monitoring techniques to detect the number of cycles-to-failure (CTF). Resistance monitoring was performed using specially designed and fabricated, device analogous test vehicles assembled with the ability to monitor circuit resistance in situ. When a resistance rise of 30 % was recorded, the device was said to have failed. A mathematical method for quantifying the plastic work density (amount of damage) sustained by the solder interconnects prior to failure was developed relying on the relationship between Hooke's Law for springs and damage deflection to accurately assess the mechanical strength of tested devices.

# Acknowledgements

I would like to thank Dr. Huitink for the opportunity to discover new things about myself, and for challenging me to push the boundaries of my knowledge and abilities.

## **Table of Contents**

| 1. | Introduction                                                                           | 1 |

|----|----------------------------------------------------------------------------------------|---|

| 2. | Review of Accelerated Testing Methods for Accessing Reliability of Electronic          |   |

|    | Packages                                                                               | 3 |

|    | 2.1. Common Accelerated Testing Methods                                                | 5 |

|    | 2.1.1. Thermal Cycling                                                                 | 5 |

|    | 2.1.2. Thermal Shock                                                                   | 8 |

|    | 2.1.3. Power Cycling 10                                                                | ) |

|    | 2.1.4. Challenges with Above Methods 12                                                | 2 |

|    | 2.2. Additional Testing Methods 1.                                                     | 3 |

|    | 2.2.1. Thermo-Mechanical 13                                                            | 3 |

|    | 2.2.2. Mechanical 16                                                                   | 5 |

|    | 2.3. Summary of Techniques                                                             | 5 |

|    | 2.4. References                                                                        | 9 |

| Ap | pendix: IEEE Reprint Authorization                                                     | 5 |

| 3. | Rapid Solder Interconnect Fatigue Life Test Methodology for Predicting Thermomechanica | 1 |

|    | Reliability 30                                                                         | 5 |

|    | 3.1. Abstract                                                                          | 5 |

|    | 3.2. Introduction                                                                      | 7 |

|    | 3.2.1. Accelerated Environmental Testing                                               | 7 |

|    | 3.2.2. Acceleration Models for Life Prediction                                         | 0 |

|    | 3.3. Materials and Methods                                                             | 1 |

|    | 3.4. Experimental Methods                                                              | 8 |

|    | 3.5. Simulation Results                                                                | 2 |

|    | 3.6. Discussion and Results                                                              | 59  |

|----|------------------------------------------------------------------------------------------|-----|

|    | 3.7. Conclusion                                                                          | 62  |

|    | 3.8. Acknowledgements                                                                    | 62  |

|    | 3.9. References                                                                          | 62  |

| 4. | Rapid Fatigue Testing with in situ Resistance Monitoring for Failure Detection in Flip-C | hip |

|    | Solder Interconnects                                                                     | 66  |

|    | 4.1. Test Apparatus 1: One-Directional Translation                                       | 66  |

|    | 4.2. Test Apparatus 2: Bi-Directional Translation                                        | 68  |

|    | 4.3. Mechanical Cycling With Test Configurations                                         | 71  |

|    | 4.4. Reliability Evaluation with Test Apparatus 1                                        | 72  |

|    | 4.5. Elevated Temperature Testing with Apparatus 2                                       | 79  |

|    | 4.5.1. Dummy Die Test Chip                                                               | 79  |

|    | 4.5.2. <i>in situ</i> Resistance Monitoring at Elevated Temperatures                     | 83  |

| 5. | Failure Mechanics Analysis: Fatigue and Creep Induced Microstructural Changes            | 89  |

|    | 5.1. References                                                                          | 95  |

| 6. | Summary and Conclusions                                                                  | 96  |

|    | Appendix A: Load Calibration and Test Procedures                                         | 100 |

|    | Appendix B: Tabulated Data for Elevated Tests                                            | 102 |

|    | Appendix C: Test Vehicle Design and Fabrication                                          | 104 |

|    | Appendix D: Test Equipment Fabrication                                                   | 107 |

### List of Tables

| Table 2-1: Comparison of Accelerated Testing Methods                                       | 26  |

|--------------------------------------------------------------------------------------------|-----|

| Table 3-1: Comparison of Common Reliability Testing Methods                                | 39  |

| Table 3-2: Properties of Sn63/Pb37 Solder (@ 25 °C)                                        | 48  |

| Table 3-3: Darveaux's Constants for Sn63/Pb37                                              | 57  |

| Table 3-4: Conversion Coefficient of Thermal Cycling to Mechanical Cycling (@ 22°) Max Sho | ear |

| Stress Amplitude of Mechanical Cycling Test (MPa)                                          | 58  |

| Table 4-1: Results of Experimental Fatigue Tests with Apparatus 1                          | 72  |

| Table 4-2: Calculated Damage Accumulation for Dummy Die Units                              | 78  |

# List of Figures

| Figure 2-1: Results of CTE mismatch 4                                                               |

|-----------------------------------------------------------------------------------------------------|

| Figure 2-2: Interfacial cracking in solder interconnect 7                                           |

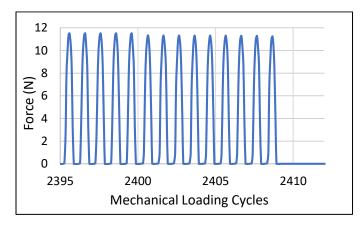

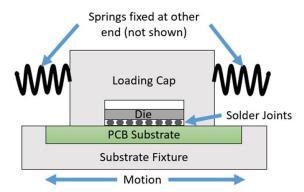

| Figure 3-1: Loading condition for cyclic reliability tests                                          |

| Figure 3-2: Representative plot for loading cycles for Sn63/Pb37 solder joints. Separation during   |

| 2409th cycle                                                                                        |

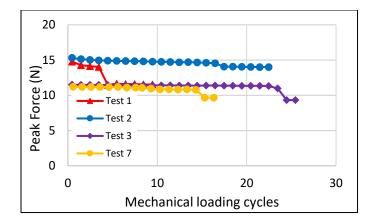

| Figure 3-3: Peak force vs cycles for 4 identical test devices                                       |

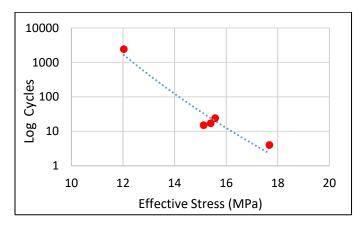

| Figure 3-4: Log plot of cycles to failure vs work-averaged effective stress                         |

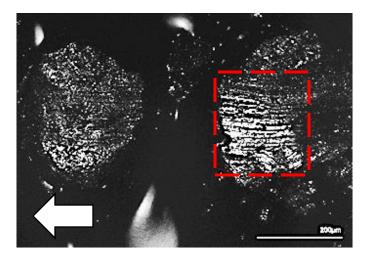

| Figure 3-5: Confocal microscope with laser source image showing crack fronts with smearing in       |

| the direction of slip (arrow) on die-side solder bumps 50                                           |

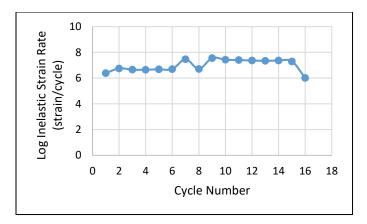

| Figure 3-6: Effective plastic strain rate as a function of cycles for test vehicle 7 (Sn63/Pb37) 51 |

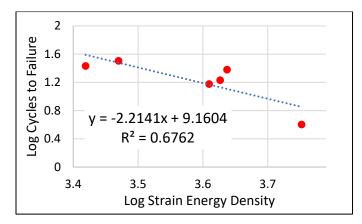

| Figure 3-7: Log-log plot of isothermal CTF and strain energy density 51                             |

| Figure 3-8: Thermal fatigue life prediction as a function of strain energy density                  |

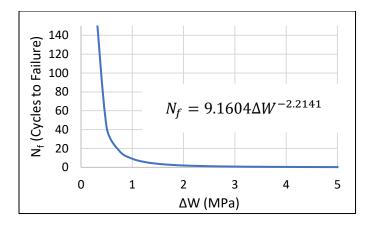

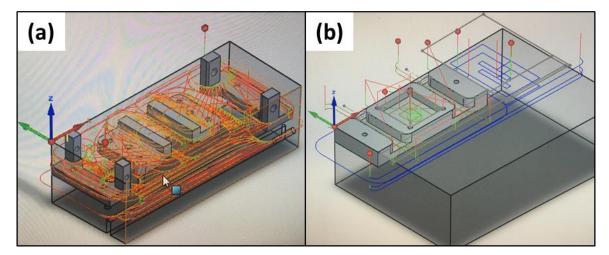

| Figure 3-9: Equivalent stress distribution at the most critical solder joint during (a) temperature |

| cycling and (b) shear load cycling 53                                                               |

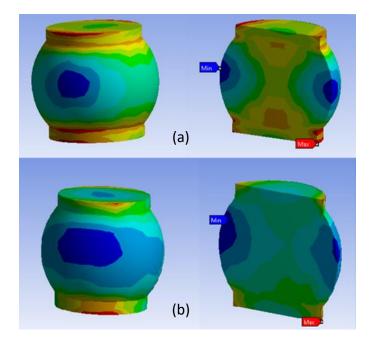

| Figure 3-10: (a) Temperature profile and plastic work densities per unit time for five thermal      |

| cycling ranges (b) Force profile and plastic work densities for cyclic shear loading 54             |

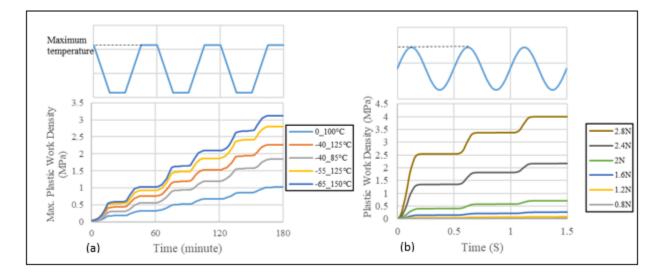

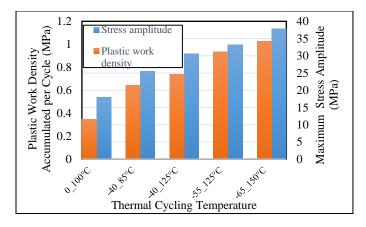

| Figure 3-11: Calculated plastic work density accumulated per cycle and maximum stress amplitude     |

| during thermal cycling for different temperature ranges 55                                          |

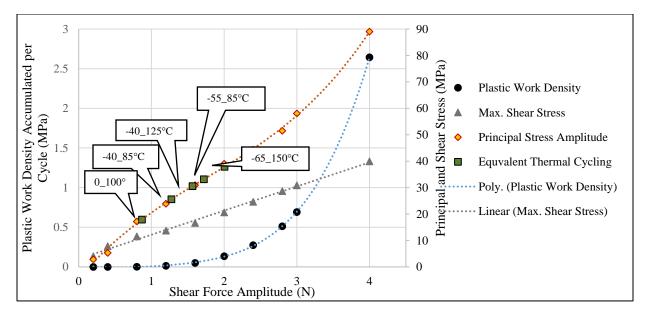

| Figure 3-12: Calculated change in plastic work density per cycle and maximum principal stress       |

| amplitude during shearing force cycling (at room temperature, 22°C)                                 |

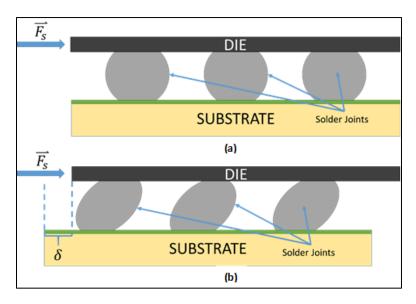

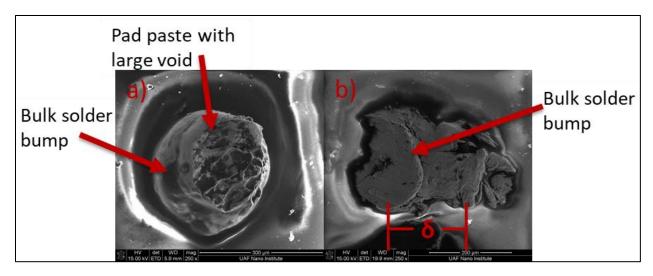

| Figure 4-1: (a) Position of solder joints in untested sample. (b) Deformation of solder joints and  |

| die deflection ( $\delta$ ) after prolonged stress cycling                                          |

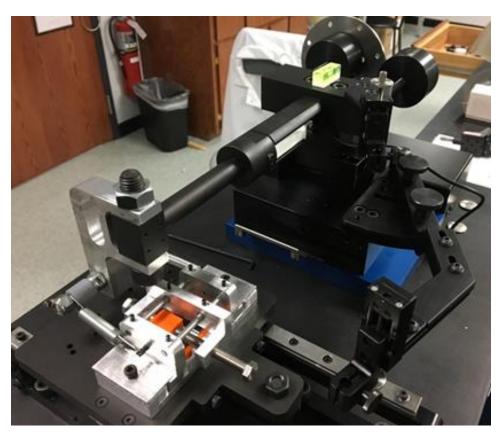

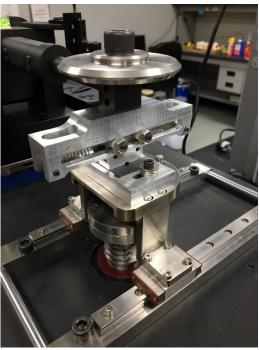

| Figure 4-2: Test apparatus 1 and tribometer instrumentation                                         |

| Figure 4-3: Schematic of the loading configuration for the second design iteration                    |

|-------------------------------------------------------------------------------------------------------|

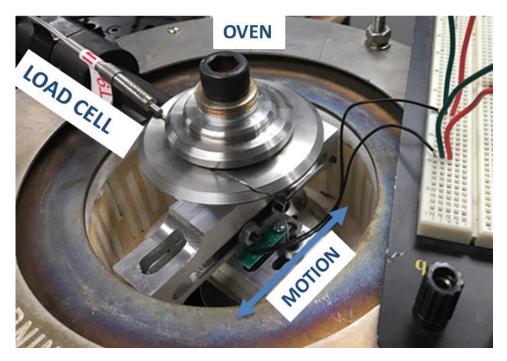

| Figure 4-4: Test Apparatus 2 with load cell and resistance monitoring circuitry                       |

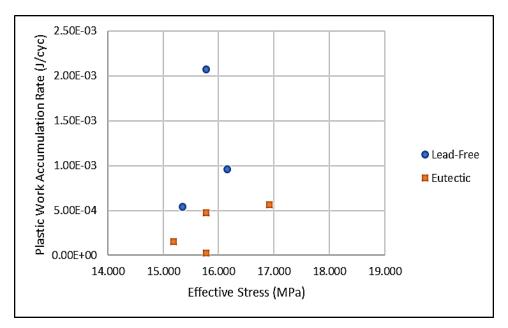

| Figure 4-5: Plastic work accumulation rate versus effective stress                                    |

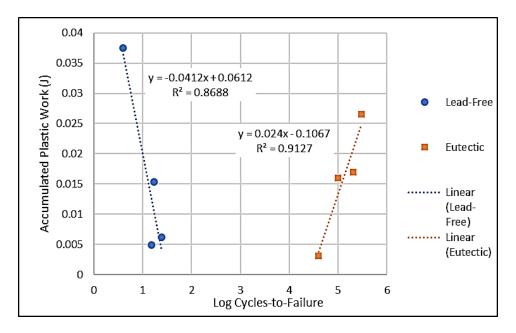

| Figure 4-6: Accumulated plastic work versus log CTF 75                                                |

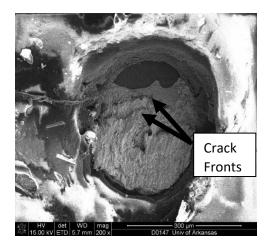

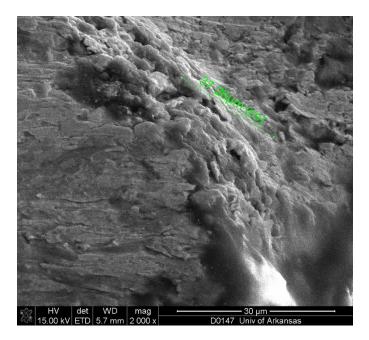

| Figure 4-7: Top view SEM image of a Sn42/Bi57.6/Ag0.4 joint of a Si MOSFET. Multiple crack            |

| fronts are visible                                                                                    |

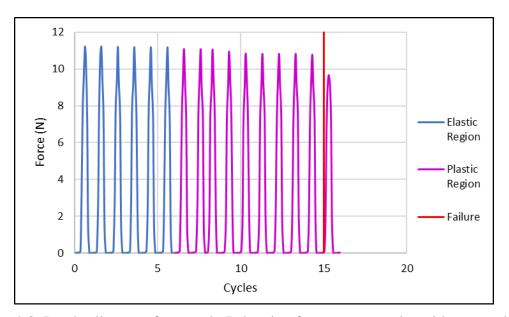

| Figure 4-8: Load cell output for sample 7 showing force versus cycles with accumulation (plastic)     |

| region shown                                                                                          |

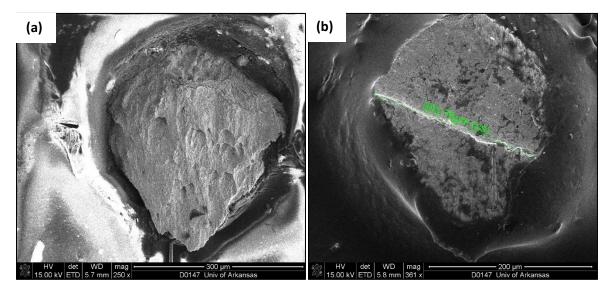

| Figure 4-9: Top view SEM image of (a) deformation of chip-side joint in Sn42/Bi57.6/Ag0.4             |

| solder paste of sample 2. (b) Bulk crack in Sn63/Pb37 material of die-side joint of sample 11 78      |

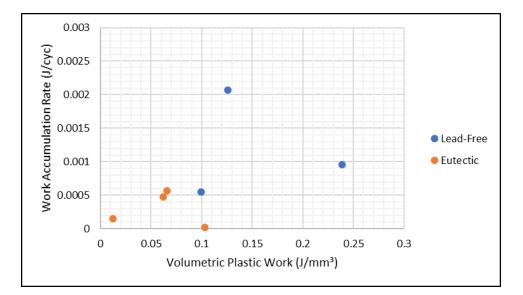

| Figure 4-10: Volumetric Plastic work accumulation versus accumulation rate                            |

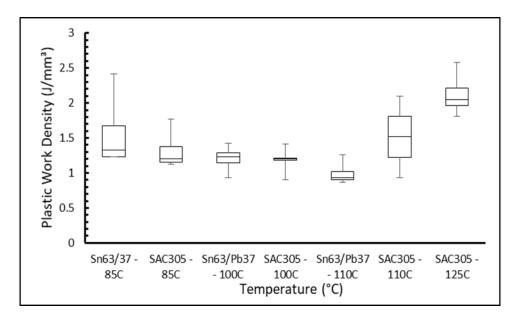

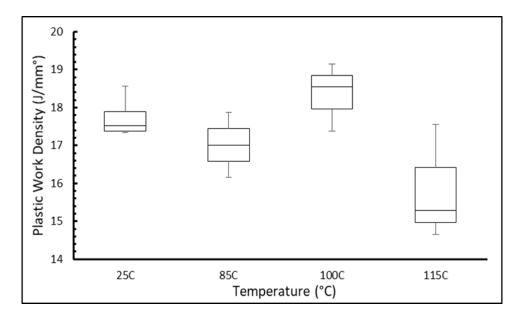

| Figure 4-11: Plastic work density with temperature                                                    |

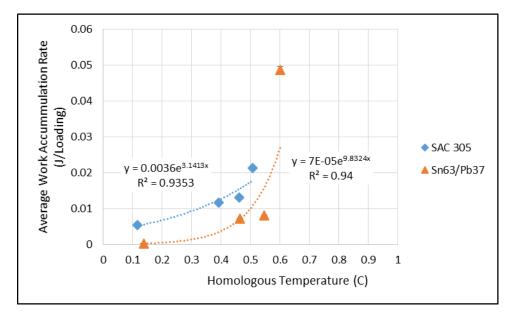

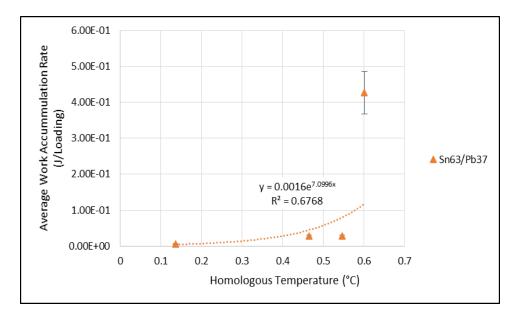

| Figure 4-12: Work accumulation rate with increasing temperature                                       |

| Figure 4-13: SEM Top view of (a) SAC 305 solder joint after failure when tested at 85 C. (b) SAC      |

| 305 solder joint after failure when tested at 115 C                                                   |

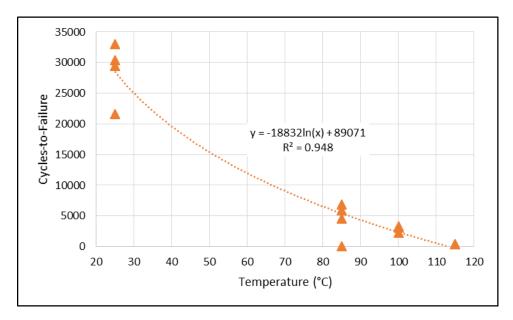

| Figure 4-14: Cycles-to-failure for all TV2 units at test temperatures                                 |

| Figure 4-15: Plastic work density with respect to temperature for tested TV2 units                    |

| Figure 4-16: Average plastic work accumulation rate changes with temperature                          |

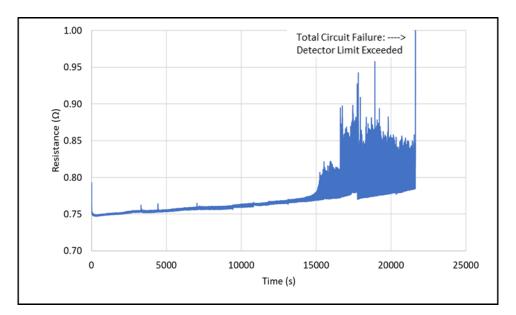

| Figure 4-17: in situ resistance plot for 25 °C Test 1. Failure coincides with total circuit breakdown |

| exceeding resistance detection limit (500 $\Omega$ )                                                  |

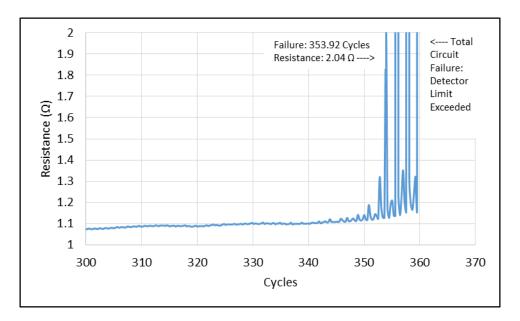

| Figure 4-18: in situ resistance plot for 115 °C Test 1. Greater than 30% increase occurs at 353.92    |

| cycles and prior to total circuit breakdown                                                           |

| Figure 5-1: Intergranular cracking in a Sn63/Pb37 joint from a TV2 unit tested at 25 °C tested at     |

| 85 C                                                                                                  |

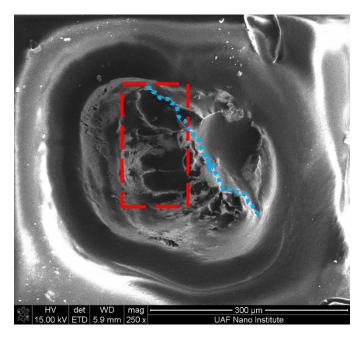

| Figure 5-2: Top view SEM image of the fracture surface for a SAC305 joint which failed when                                    |

|--------------------------------------------------------------------------------------------------------------------------------|

| tested at 85 °C. Elongated microvoids (dashed box) and a brittle crack front (dotted line) are visible                         |

| indicating both ductile and brittle failure behavior                                                                           |

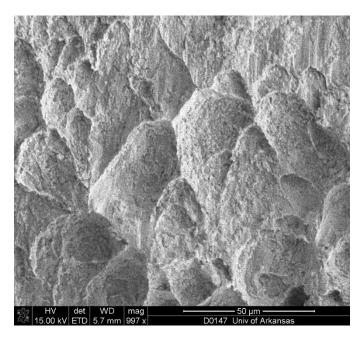

| Figure 5-3: Elongated dimples in the fracture surface of a Sn63/Pb37 interconnect tested at 115 $^{\circ}$ C                   |

| which are artifacts of microvoid formation within the material                                                                 |

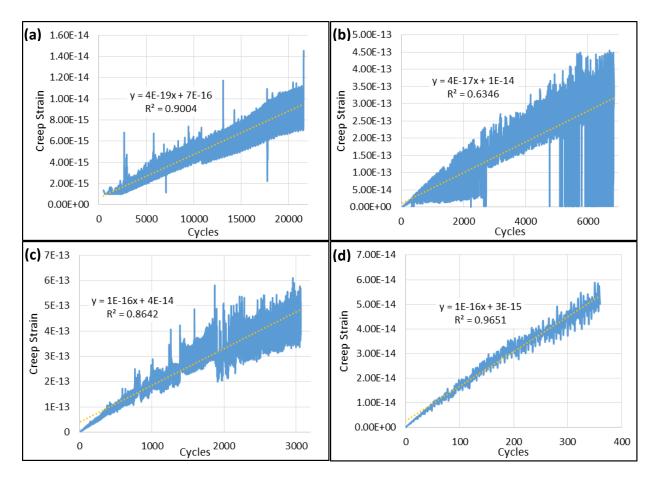

| Figure 5-4: Creep strain curves for TV2 devices tested at (a) 25 $^{\circ}$ C (b) 85 $^{\circ}$ C (c) 100 $^{\circ}$ C and (d) |

| 115 °C. The trendline denotes the rate of increase in creep strain as testing progressed, high slopes                          |

| indicate high strain rate acceleration                                                                                         |

| Figure A1: Fully assembled Test Apparatus 2 with Dummy Die calibration cartridge installed. 100                                |

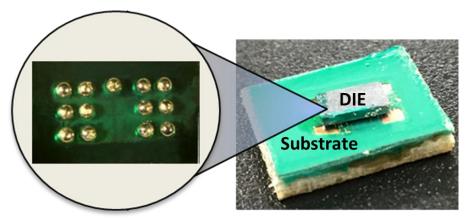

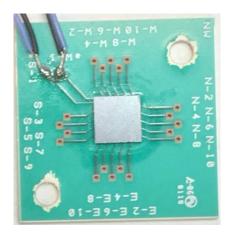

| Figure C1: Test Vehicle Mk. I. "Dummy Die" of a POETS designed Flip-chip MOSFET developed                                      |

| by Sayan Seal and Dr. Alan Mantooth 104                                                                                        |

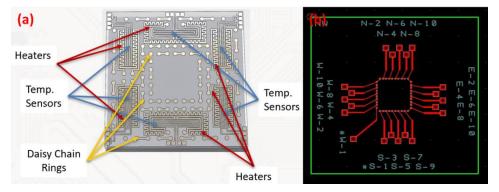

| Figure C2: (a) Die side features (b) PCB design for test vehicle 2 105                                                         |

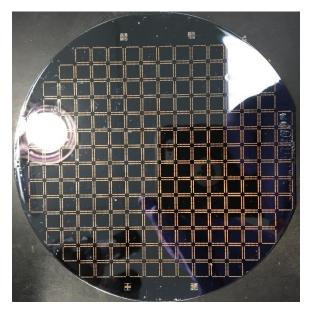

| Figure C3: TV2 wafer after SU-8 deposition and patterning 106                                                                  |

| Figure C4: Temporary fixture for solder bumping. Ceramic tiles were used to allow the device to                                |

| be slid out of the tweezers and placed directly in the reflow oven without being picked up 106                                 |

| Figure C5: Assembled TV2 device with resistance monitoring leads 107                                                           |

#### **List of Publications**

Chapter 3 -

C. J. Marbut, M. Montazeri and D. R. Huitink, "Rapid solder interconnect fatigue life test methodology for predicting thermomechanical reliability," Transactions on Device and Materials Reliability, vol. 18, no. 3, p. 412-421, June 2018.

#### **List of Unpublished Papers**

Chapter 2 -

C. J. Marbut and D. R. Huitink, "Review of Accelerated Testing Methods for Accessing Reliability of Electronic Packages," Journal of Electronic Packaging, pending, 2019

#### 1. Introduction

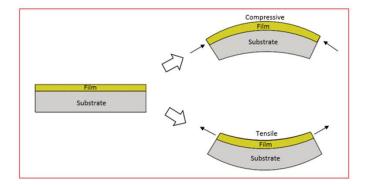

The exponentially growing dependence upon electronics in many aspects of everyday life and in the world economy has placed great importance on electronics reliability. In the case of flip-chip devices such as ball-grid arrays (BGA), the critical components for determining reliability are most often the solder interconnects that join the die and substrate which endure thermomechanically induced stresses during operation. These stresses are induced through a phenomenon known as "coefficient of thermal expansion (CTE) mismatch", where large differences in CTE for the dissimilar materials of the package result in non-uniform expansion rates across the device. For the interconnects, the result of this non-uniformity are induced tensile or compressive stresses which lead to elastic and plastic deformation within the joints. Creep and fatigue induced crack nucleation and propagation weakens the mechanical integrity of the joints while simultaneously degrading electrical performance. Extensive cracking leads to increased electrical resistance within the circuit and once the plastic deformation (damage) becomes severe, the resistance increases will exceed sustainable levels and the device will cease to function correctly or even at all, a situation know as device death.

Current accelerated testing methods for assessing fatigue lifetime (useful life) of electronic packages focus on simulating this CTE mismatch through thermal cycling in an environmental chamber or power cycling induced heat generation using the device itself. In both cases an acceleration factor is used to simulate the manifold cycles of an operational lifetime of the device but on a truncated time scale. These methods have been in use for many decades and are well understood, however, they are also characterized by long test durations, high costs, and difficulty quantifying induced stress levels and mechanistic effects within the devices themselves. To address these weaknesses with traditional testing methods, a new testing

methodology was devised relying on mechanical inducement of stresses within flip-chip solder interconnects through quantifiable means.

A rapidly accelerated test method was created where through the use of springs and cyclic linear translation, shear stresses were induced in the solder interconnects of tested devices to simulate the fatigue behavior of devices under operation or traditional accelerated life testing. Under actual operating conditions, creep and fatigue occur alongside other damage processes such as diffusion, recrystallization, electromigration, and current crowding. With all of these threat factors comingled, it is difficult to define the amount of damage attributed to any one mechanism and quantifying the effects temperature and stress have on damage accumulation behavior becomes obscure. The rapid methodology allows the isolation of stress based failure mechanism to allow for greater understanding of the underlying failure mechanics at work. Extensive reductions in total test duration were also targeted in the design of this method to reduce time for design feedback and costs associated with extended test duration. The ability to conduct tests on actual functioning devices with relevant geometries while monitoring both mechanical fatigue and electrical performance *in situ* was a primary objective for this testing methodology. Additionally, the *in situ* characterization provides a wealth of data for use in assessing and quantifying failure mechanisms and metrics enabling a more holistic understanding of the factors influencing the reliability of a given device.

The following articles are included in this work to elaborate on current state of the art in accelerated testing, the methodology behind this novel accelerated testing method, and the performance of this new approach in practice. These articles were published or are pending publication and were originally written with an eye toward inclusion within this thesis and it is believed that they provide a comprehensive view of the field, the scope and objectives of this testing methodology, and the results that were achieved through its implementation.

# 2. Review of Accelerated Testing Methods for Accessing Reliability of Electronic Packages

Cody J. Marbut and Dr. David R. Huitink

Increasing demand for higher power, small form-factor devices has created new challenges for device reliability optimization. Smaller form factors while simultaneously providing higher power levels mean higher energy density which lead to higher operating temperatures. These temperatures have a very large impact on device reliability because of coefficient of thermal expansion (CTE) mismatch which induces mechanical stresses within the dissimilar materials of the device. These stresses are induced when the CTE of one material is not roughly equal to the CTE of an adjacent material. As these dissimilar materials heat up they will expand at different rates. This expansion will induce tensile or compressive stresses within the device (see Figure 2-1). Solder joints have been shown to be one of the components most vulnerable to these induced stresses. These stresses can cause both elastic and plastic deformation within these joints. The irreversible plastic deformation is predominantly due to creep and fatigue which ultimately leads to crack nucleation. When these cracks propagate across the solder material, the resistance of the joint increases until electrical failure is achieved rendering the device non-functional [[1]-[3]]. Ensuring mechanical reliability of power devices requires designers to engineer against void formation/propagation and evaluate existing devices for fatigue life. Evaluating the fatigue life or operating cycles-to-failure (CTF) is most often done through accelerated testing (AT).

Figure 2-1: Results of CTE mismatch.

Accelerated testing experiments are conducted to collect information regarding predicted lifetimes and prominent failure modes within a given device. These tests are considered "accelerated" because test units are subjected accelerating variable levels far higher than those expected in real-world operating conditions using one or more accelerating variables such as temperature or stress [4]. This is done in an effort to acquire useful reliability data within a reasonable time window for an experiment (hundreds of hours rather than potentially tens-ofthousands of hours in actual operation). Lifetime at these accelerated conditions is then used to predict the operating lifetime (OLT) under standard conditions. Extrapolation of OLT is typically conducted using physically derived or empirically fitted models when a statistically significant amount of previous data is collected with similar test units. The two predominate types of accelerated testing used in industry are "quantitative" and "qualitative" accelerated tests. Quantitative tests are used to obtain failure-time data and degradation distribution for validating prediction models. Qualitative tests are used to test for product weaknesses and to study the root causes of device failure [4].

The primary requirements of an accelerated test are rapid results and accurate simulation or real-world failure mechanisms. For a testing method to yield beneficial results, it must induce causes and symptoms of failure congruent with those observed or expected in devices operating under actual design conditions. In an effort to satisfy these requirements across a wide range of accelerating variables and applications, a large number of testing methods have been devised. Currently, the three most widespread AT methods used in electronic device reliability assessment are thermal cycling, power cycling, and thermal shock testing. Each of these methods has been used in industry quite successfully to develop expectations for device OLT. However, there are limitations to these methods such as duration and expense. To address these limitations, several novel AT techniques have been developed to provide much faster results at lower costs. This paper will examine the strengths and weaknesses of both these traditional and novel techniques for solder joint reliability assessment.

#### 2.1 Common Accelerated Testing Methods

#### 2.1.1 Thermal Cycling

Thermal cycling (TC) tests are conducted to evaluate the reliability of components and interconnects when subjected to mechanical stresses induced by alternating temperature extremes as an approximation of temperature swings during operation [5]. This is done in an effort to simulate the rise from low temperature to high temperature as a device powers on and begins to heat up to peak operating temperature followed by the drop as the device cools to the initial temperature (power off). To conduct the test, the test unit is placed inside a closed environment capable of transferring the device from one zone of high temperature (high setpoint) to another of low temperature (low setpoint). The test unit is made to remain in each zone for a specified dwell (soak) time which is the total time the device is to be at a given temperature for each cycle. The device is subjected to the temperature range for a specified number of cycles or until failure, as defined by the operator, occurs. Standards such as JESD22-A104D specify temperature ranges and soak times for specific certifications and ratings.

Ramp rate, dwell time, temperature range, and total number of cycles may all impact the overall acceleration factor (a metric for determining severity) of the test and their influence is dependent on failure mechanics and material properties involved. Increases in ramp rate can increase the strain rate experienced within the solder joints making ramp rate a useful acceleration variable for detecting weaknesses in the device which have a thermal ratedependence [6]. Typically, a higher ramp rate will result in more damage accumulation over the course of the test. Dwell time serves to ensure that the test unit has reached the desire steadystate temperature. Generally, longer dwell times correspond to higher acceleration factors, especially at higher temperatures. This is due to creep behavior in the solder material which result from the high ratio of steady-state temperature to melting point, called the homologous temperature. Creep can occur if the testing temperature is greater than 0.45 to 0.6 of the absolute melting temperature for the solder material [7]-[11]]. Additionally, longer dwell times lead to longer test durations, a result that is not always desirable in an "accelerated" test. When conducting a temperature cycling test, it is important to note that higher ranges between temperature extremes induce more strain into the device. During testing, failure can be monitored by collecting electrical performance data like resistance, and visual inspection can be used to detect crack formation. Cyclic rates of 1-3 cycles per hour (cph) are common. Depending upon the desired failure mechanism, faster rates can be used. Fatigue, cracking, delamination, ball bond integrity failure, and creep are common among flip-chip devices [[12],[13]].

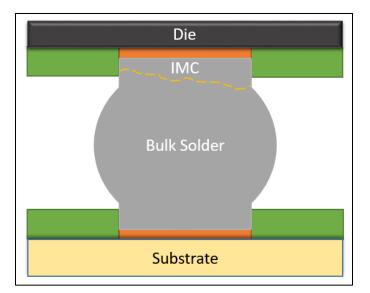

Figure 2-2: Interfacial cracking in solder interconnect.

The most commonly, fatigue cracking occurs between the bulk solder and the intermetallic layer in what is known as the interfacial region. Crack propagation is based upon the micro-structure and mechanical properties of the bulk solder [14]. Recrystallization of Sn is induced by thermal strain and elevated temperature, starting in the highly strained regions before expanding through the bulk material [12]. Due to a network of high-angle grain boundaries which extend through the interconnections and provide favorable propagation paths, recrystallization has been shown to enhance fatigue cracking [[12], [13]]. Recrystallization and dislocation motion are expected to be more thermally active at higher temperatures, causing a drastic decrease in shear strength [15]. The stress/strain distribution within the bulk material undergoing a thermal fatigue process has been shown to be non-uniform. Non-uniformity in the bulk material leads to grain slipping and plastic work accumulation with cycling [[12], [13]]. In moderate thermal stress states, strain can be released through plastic relaxation such as global recrystallization and solder exclusion. Once stress magnitude increases until plastic relaxation is not possible, crack initiation begins in the area of highest stress. Cracks are then propagated

through local recrystallization of solder grains. Thus, it can be said that the damage found in solder interconnections under thermal strain results from dislocation densities in the plasticized regions and increases with the accumulation of internal energy [[12]-[16]].

Thermal cycling has been used to evaluate solder reliability across a vast array of applications, though that list is too long to include here. Experiments of the reliability of all manner of devices from wafer level chip-scale packages (WLCSP) to full-scale power modules have been performed using thermal cycling techniques [[10],[17],[18]]. Sitek et. al. used thermal cycling to compare the reliability of long FR-4 and metal core PCBs, finding that solder interconnects on FR-4 substrates were two times more reliable than those on aluminum core circuit boards [19]. Singh et. al. determined that boards made using high-CTE glass had nearly five times the useful life (5300 cycles to 1100 cycles) of low-CTE glass substrates due to narrower difference between substrate and solder CTE [20]. In efforts to shorten test duration, more accurately simulate real-world conditions, or simply to explore new stress states, many researchers have begun combining thermal cycling with electrical or mechanical stress inducers. Such efforts are discussed in section 2.2.

#### 2.1.2 Thermal Shock

Thermal shock (TS) testing is conducted to evaluate the reliability of electronic devices when exposed to sudden, drastic changes in temperature [21]. The device is transferred between extremes (hot – cold) with a transfer time not exceeding 20 seconds [21]. This ramp time must be short to ensure that the device experiences sudden, rapid temperature change rather than the more gradual temperature gradients seen in TC experiments. The test is designed to bring the device(s) to worst-case load temperature within a specified dwell time as measured by a thermocouple embedded in the body and located at the center of the heat load. The worst-case

load temperature is defined by the nature of the test and must adhere to standard within a specified range. Failure is assessed if parametric limits are exceeded, if hermeticity cannot be demonstrated, or if the device is non-functional after testing [21].

Some researchers have claimed that TS tests are more efficient than TC testing because they exhibit higher ramp rates and shorter MTTF values [[22], [23]]. However, care should be taken when conducting TS tests because failure modes are highly susceptible to thermal gradients that arise in the material [23]. The thermal gradients that develop in TS tests are higher than those created in TC testing. These thermal gradients contribute to buildup of inelastic strain. In a comparative study of thermal cycling and thermal shock tests, de Vries et. al. found that 1.5% of the total plastic strain in TS testing was attributed to inelastic strain [23]. In the case of TC testing, de Vries et. al. found no inelastic strain in the solder material. In TC testing, the primary source of stress is un-equal expansion due CTE mismatch between component materials. The presence of thermal gradients can induce additional stresses within the solder interconnects under TS testing conditions. The magnitude of these additional stresses will be dependent upon the thermal behavior of the test device under TS conditions [23].

Failure mechanism in solder interconnects under TS conditions are similar in many ways to failure mechanisms observed in interconnects stressed under TC conditions. Crack initiation in the interfacial region propagating into the bulk solder material precipitated by intermetallic compound (IMC) growth [[22]-[26]]. Tian et. al. found that this IMC growth was driven primarily by bulk diffusion and grain boundary diffusion within the microstructure of the solder material [26]. The presence of both thermal gradients and diffusion within solder interconnects under TS conditions can obscure or alter the failure mechanisms from those seen in real-world conditions, negatively impacting reliability predictions. Diffusion has been shown to follow

thermal gradients, creating the potential for radically different diffusion paths in some cases [27]. The magnitude of the impact on prediction accuracy would depend on the materials under study and the constraints of the test. Tian et. al., reported that the observed fracture behavior of SAC 305 interconnects transitioned from ductile fracture to brittle fracture modes as the number of TS cycles increased [26]. Anselm and Ghaffarian found that isothermal aging prior to thermal shock testing resulted in improved reliability for tin-lead solder quad flat no lead (QFN) assemblies [28].

#### 2.1.3 Power Cycling

Power cycling (PC) tests are conducted to evaluate the ability of a device to withstand the stresses generated by CTE mismatch and non-uniform temperature distributions created by the on-off operating cycles of the device [29]-[[30]]. Unlike the other tests described above, in PC testing, the device, or internal or external heat source is supplied a current to simulate operating behavior and temperature range in a real-world environment. The power cycle ranges used in this test are designed to simulate the range of usage conditions. Unlike the other traditional tests, PC tests are not always specifically designed as highly accelerated tests or to create harsh conditions. This test is used to verify the performance of the component materials within the device, especially the solder interconnects [29].

The device is run through a prescribed temperature range, for a set number of cycles once the device is powered and the temperature extremes are calibrated. There are four main test types: constant power, variable power, constant cooling, and variable cooling [8]. The failure criteria once again include: parametric limits are exceeded, hermeticity cannot be demonstrated or if the device is non-functional after testing due to mechanical damage [29].

Comparative analysis of power cycling and thermal shock tests has shown that the primary cause of failure was generally the same. Crack nucleation and propagation assisted by recrystallization resulting from energy provided by the mechanical stresses generated during cycling was identified as the primary failure mode for both tests [31]. More detailed analysis revealed some key differences. Under power cycling conditions, IMC growth was accelerated. Researchers linked this to electromigration of Sn and Cu in the solder matrix, resulting in higher Sn flux and increased Cu6Sn5 growth at the anode side of the interconnect [31]. Additionally, recrystallization was seen to occur earlier during power cycling testing. This was attributed to the higher average temperatures, localized heating, and current flow related to PC testing [31]. In comparison with TC testing, higher maximum stresses developed in power cycling tests. This is largely due to the non-uniform temperature distribution common to most devices. Generally, a larger amount of temperature change is experienced by the die than the PCB which is not the case in TC testing. Because a functioning device does not necessarily achieve steady-state temperature distribution, stresses in high temperature regions tend to be more acute because it is more localized [[32]-[34]].

Due to the fact that power cycling typically relies on actual device operation to induce failure, many feel that it is a more accurate method for predicting fatigue life than TC or TS. The justification for this position is, that PC better simulates the real-world temperature gradients a device will experience in actual applications given that the non-uniform temperature distribution found in PC in combination with the different CTE of each component will make the solder material deform differently than in TC testing. PC testing is also considered a less conservative test because the temperature conditions are often much more mild averaged across the device.

#### 2.1.4 Challenges with Common Methods

Each of the traditional accelerated testing methods discussed above have unique advantages making them useful for evaluating solder interconnect fatigue life in certain applications. However, one must be mindful of each method's unique weaknesses and limitations. All three methods are unable to evaluate CTF at rates greater than 6 cycles per hour. In testing that is supposed to be "accelerated", these low cyclic rates lead to significantly long duration tests. Given that it is often expensive to conduct these tests, the total cost of running an experiment over a long period can be prohibitive. Thermal cycling tests in particular are generally quite long in duration with test times of up to 6 months in industry applications. Additionally, care must be taken when using these methods to ensure that the expected failure mechanisms occur according to what is expected or reported in actual applications. Thermal cycling tests have been shown to increase thermal gradients which subsequently cause changes in the diffusion pathways along which microstructural changes occur. These tests are suited to applications where sudden large temperature changes may occur uncommonly, however, their use is limited for evaluating fatigue life under standard operating conditions. TC and TS are generally designed to create harsher than expected conditions, often resulting in overly conservative estimations of device lifetime. These over estimations can lead to unnecessary additional design time and the inclusion of excessive redundancy which increases device complexity and cost. PC is seen by many as the most true-to-life AT method, despite this, its utility is still limited by the relatively low cyclic rate.

Another weakness shared by all three traditional AT methods is less often considered. In each of these methods, thermal, mechanical and chemical processes are all influencing the solder

simultaneously. While this is accurate for simulating actual application conditions, it is nearly impossible to quantify what percentage of the damage was due to only one fatigue factor, and which occurred only as a result of a combination of factors. Physical and metallurgical interactions intersect in thermal environments, stress and diffusion intermingle and it becomes difficult to assign damage to each individual fatigue factor. In the case of power cycling, current effects such as electromigration (EM) also influence solder fatigue. Thus, to develop an understanding of what each threat factor is doing to the solder interconnects, these phenomena must be isolated and studied independently. Once a strong understanding of each is achieved, the greater thermo-electro-mechanical system can be evaluated with new found clarity. To that end, many alternative approaches to damage assessment and fatigue life prediction have been developed to enable new insight into solder interconnect reliability.

#### 2.2 Additional Testing Methods

#### 2.2.1 Thermo-Mechanical

Thermo-mechanical methods seek to develop a better understanding of the relationship between temperature and stress by combining and quantifying thermally and mechanically induced stress in one accelerated test or comparing performance across thermal and mechanical tests. Tests of this nature are useful in determining the magnitude of loads which a device can survive prior to stress induced failure. These tests are often characterized by a multi-point data collection scheme whereby temperature, resistance and stress are all monitored in-situ. This enables real-time study of changes in material strength, electrical performance, and the effects of various temperature gradients such as temperature ramping. Quantifying the magnitude of all these factors within the device as it is induced to fail can help provide new insight into material properties, architectural weaknesses, and design for reliability (DFR) guidelines.

A common alternative approach is to combine a traditional AT, such as thermal cycling, and introduce mechanical load or shock to the device during or after thermal cycling [35]-[37]. Yu et. al. observed that the impact of compressive loads, such as those due to expansion interactions with adjacent components, on solder joint reliability was not thoroughly understood [37]. They designed and fabricated a fixture that applied compressive loads to the package which were then placed in a temperature cycling chamber and cycled from 0 °C to 100 °C with a ramp time of 30 min. and a 15 min. dwell at peak temperatures. Crack propagation through the dieside interfacial region was still identified as the dominant failure mode, being observed in 66.7 % of all samples tested. However, diagonal cracking through the bulk solder material was identified only in the preloaded solder joints. The additional failure mode observed only in the preloaded samples indicated that the crack propagation pathways had been changed as a result of the compressive stress [37].

Karppinen et. al. looked at the combined effects of mechanical shock and power cycling of the reliability of interconnects in handheld devices [38]. The effects of thermal aging as a result of PC were on mechanical shock survivability evaluated for devices ages 1000, 3000, and 5000 power cycles. A 0.5 ms half-sine shock was generated with an initial magnitude of 1440 G. Mechanical shock and PC were conducted both concurrently and consecutively for both boardlevel and product-level testing. The results showed that the thermomechanical loading enhanced the growth of the IMC layer and the coalescence of intermetallic particles inside the bulk solder. The aging effects of PC after 1000 cycles initially improved drop-test performance, but additional cycling led to degraded shock reliability. No significant difference in reliability was observed between the concurrent and consecutive testing method [38].

Other researchers have devoted their efforts to improving traditional AT's themselves by directly addressing their inherent weaknesses such as long duration and slow ramp rates [[39], [40]]. In an effort to reduce the time required to conduct TC experiments, Tunga and Sitaraman proposed using laser moiré interferometry to examine strain contours in a pre-cross-sectioned solder joint [40]. Plastic and ceramic BGA's were cycled from 0 °C to 100 °C with the interferometer mounted on a fixture above the test vehicle inside the temperature chamber. Using the Coffin-Manson predictive model and the deformations observed by the interferometer, strain estimates were calculated and used to assign a predicted reliable lifetime to each package. By reducing the solder material under study and mounting the interferometer in the temperature chamber, the total time to generate life time predictions was reduced [40]. Metasch et. al. designed a system to measure the in-plane and out-of-plane displacement of flip-chip solder interconnects under TC conditions in an effort to get more data out of the traditional method [41]. By integrating the test sample into a frame with force and displacement sensors, they were able to make new observations on the behavior of solder when cycled between two temperature ranges, 10 °C to 90 °C, and -40 °C to 125 °C respectively. Monitoring the point where the material was no longer able to resist 50 % of its initial peak force value, Metasch et. al., found that a 50 % reduction in temperature range leads to 6 times as many cycles before failure [41].

Another common form of thermo-mechanical accelerated testing utilizes elevated isothermal in-situ heating or ex-situ aging to introduce thermal effects into failure mechanisms under more controllable conditions [[42]-[45]]. The rationale of these tests is that the peak stress will occur when an actual device reaches peak operating temperature. Also, solder becomes more vulnerable to deformation and diffusion as homologous temperature increases. So, these tests are designed to simulate that "worst-case" situation of high temperature and mechanical stress.

Fakpan et. al., utilized resistive heating elements to reach a steady-state temperature of 70 °C mounted near a center cracked tension (CCT) sample to evaluate the response of SAC 305 and Sn-37Pb solders to shear stress at elevated temperatures. The results of their experiments showed that the time-dependent creep crack growth rate of SAC 305 was higher than that of the Sn-37Pb solder for both room and elevated temperatures [44]. Lee et. al., evaluated the combined effects of thermal aging through TC with mechanical shock to determine the effect of fatigue life for 1 % and 3 % silver content Sn-Ag-Cu solder materials [45]. A composite board containing nine test vehicles that enabled each location to experience a different shock level and strain level from an input shock of 1500 G with a 0.5 ms half-sine pulse duration. Some of the shock samples were aged isothermally at 150 °C for 500 hours. For comparison, thermal cycling was conducted on aged and unaged samples. They found that more grain boundaries arose from thermal cycling than shock deformation. This was attributed the strength of Sn at the higher strain rates which prevented the storage of as much energy in the microstructure as was stored under TC conditions [45].

#### 2.2.2 Mechanical

While some mechanical testing methods are conducted with a thermal component, many other purely mechanical reliability tests have been developed. Mechanical testing has the advantage of being very fast compared to traditional methods like TC and the characteristics of failure are much easier to interpret because damage is based solely of physics based firstprinciples. This combination of rapid reliability assessment coupled with, in many cases, intuitive failure mechanisms, makes mechanical testing uniquely suited for early design validation through concept prototyping. The added advantage of this is that, design validation does not need to wait until near the end of product development to discover potential weaknesses

because inexpensive, mechanically congruent test vehicles can be easily produced. Several categories of mechanical reliability test exist including; shock, bending, vibration, lap shear, and cycling loading. These categories are discussed below.

#### i) Mechanical Shock

In consumer electronics, JEDEC JESD22-B111 is used as the standard for mechanical shock reliability [[46], [47]]. The standard stipulates that a board containing 15 test devices with a footprint of 132 mm x 77 mm must be subjected to a 1500 G, 0.5 ms pulse shock. Most mechanical shock testing setups utilize a drop-tower to accelerate the device to achieve the desired acceleration prior to impact. Mechanical shock tests are well suited to applications where the device may experience a sudden, high-G impact such as portable electronics and military applications. Lall et. al., evaluated the survivability of electronic missile components under extreme shock conditions of up to 50,000 g [48]. Fu et. al., used mechanical shock tests to compare standard Bi-Sn and resin reinforced Bi-Sn to determine if the resin could be used to overcome the inherent brittleness of Bi containing solder [49].

In their evaluation of aging effects on solder interconnect shock performance, T.-K. Lee et. al. conducted mechanical shock tests at 150 G, 200 G, 250 G, 300 G, and 340 G with isothermal aging profiles of 500 h at 75 °C, 100 °C and 150 °C [49]. Intermetallic growth behavior of both NSMD and SMD solder pads were studied for comparison. The greatest reduction in performance was seen in SMD samples that were aged for 500 H at 75 °C, with a decrease from 3 cycles-to-failure under 200 G shocks to 2 cycles-to-failure under 150 G shocks. For samples aged at 100 °C, the performance level increased to 6 CTF under 150 G loading, while samples aged at 150 °C showed the greatest improvement with 5 CTF under 250 G loadings. In the case of NSMD samples, little difference was seen in performance between aging profiles and test conditions. Thus, SMD pads where more susceptible to performance changes due to isothermal aging. Crack initiation and propagation were found to occur mostly at the substrate side IMC interface where an unstable hexagonal  $Cu_6Sn_5$  microstructure was found to form in the 75 °C aged samples. This unstable microstructure was unique to the 75 °C aging profile and acted as the week interface along which fast crack propagation occurred. Additional testing at elevated, steady-state temperature (100 °C) revealed improved CTF performance for SMD samples in low shock input (100 G and 150 G) regimes [49].

#### ii) Bending

Mechanical bending tests of electronic components in industry are governed by JEDEC standard JESD22B113. Mechanical bending tests are better suited for providing data on relative component performance rather than a discrete pass/fail criterion [50]. Vandevelde et. al., induced mechanical stress into the components by applying four-point bending to the PCB. This bending causes absolute displacement of the top/bottom fiber of the PCB which simulates the expansion mismatch seen between the die and substrate of the device that is observed in TC testing [51]. The dominant failure mode was found to be cracking along the interfacial region of solder joint on the die-side. Experiments were conducted to determine if alternate failure modes would occur at higher loading frequencies but the researchers concluded that bending dwell times of 10 minutes were sufficient.

Given the fact that most solder interconnects fail at the interfacial region between the IMC layer and the bulk solder, Philippi et. al. utilized mechanical bending tests to evaluate the strength of Cu<sub>3</sub>Sn alloy (a common IMC phase) microcantilevers shaped by focused ion beam milling (FIB) to common IMC layer thickness [52]. This was undertaken in an effort of estimate the critical defect size for Cu<sub>3</sub>Sn in based on fracture toughness in bending. The researchers

concluded that critical defect size corresponded to grain size, finding a critical defect size of 258 nm for their samples [52].

#### iii) Vibration

Vibration testing is conducted to evaluate the effects vibration, such as that arising from transportation or operation, has on electronic devices. Vibration can induce stress in solder interconnects and repeated exposure or long duration can lead to fatigue failure. Studies can be conducted to evaluate the device under conditions similar to the end use conditions to evaluate long-term reliability of components in high vibration applications, such as automotive or portable electronics. To perform this test, the components under study are rigidly mounted or restrained by a case with suitable protection for the leads. The case itself is then rigidly fixed to the vibration platform with the leads secured to prevent excessive lead resonance [53]. Vibration is applied (typically with a shaker table) so as to simulate non-shipment vibration conditions to evaluate solder reliability. Standards such as JESD22-B103B.01 [53] dictate standard test conditions for peak-to-peak displacement, peak acceleration (G), cross-over frequency (Hz), and min/max frequencies (Hz). Typically, a complete sweep of frequency range from minimum to maximum and back is conducted in a logarithmic fashion in a period of 4 minutes. JEDEC stipulates a sweep rate of 1 decade/minute with 4 consecutive sweeps in each orientation X, Y, and Z for a total of 12.

Random vibration tests are conducted to evaluate the survivability of electronic devices during shipment. Devices are excited with a Gaussian random vibration which is applied for 30 minutes in each orthogonal axis for a total test duration of 90 minutes [53]. Vibration test parameters should be calibrated against the natural frequencies of the component. Accelerometers can be used to measure the natural frequencies and mode shapes of the test vehicle under the boundary conditions of the test [54]. Typically, the first natural frequencies (1 for each orthogonal axis studied) are used because those frequencies are known to accelerate damage the most [55]. Failure is again often assigned if the test unit ceases to function, resistance spikes, or various visual inspections reveal significant damage. Batieha et. al., cautioned that random vibration test results could be particularly difficult to relate to long term performance [56]. Accelerated vibration testing is known to lead to continuous resonance frequency shifts caused by softening of the PCB, especially at higher amplitudes. Researchers observed a continuous drop in resonant frequency when testing at a 6 G amplitude however at 3 G amplitude, there was no significant change. Batieha et. al., concluded that tests should be limited to amplitude levels at which resonant frequency shifts remain negligible for the duration of the test [56].

Discerning the most common failure mode in solder interconnects under vibrational excitation can be more complicated than traditional thermal-based methods. Typically, fatigue cracking with in the interfacial regions are still the most common [[54]-[56]]. Solder pad cratering has been reported after even moderate cyclic vibration testing, also, intermetallic and bulk solder fatigue comingle. Additionally, brittle fracture was seen to vary more quickly with increasing load amplitude than did ductile fatigue. Due to this behavior, low amplitude testing can be conducted without significant PCB softening but softening occurs at high amplitudes [56]. Zhou et. al., recommended the use of constant amplitude harmonic excitation because the dynamic response of the test vehicle consists of only one mode rather multiple coupled modes [54]. Mode coupling can confuse assignment of failure mechanism to stress resulting from a specific mode shape. Additionally the strain history is harmonic, eliminating the need for cycle counting algorithms and damage accumulation will be constant. Using vibration testing, Chuang

et. al., were able to recommend the use of hypoeutectic alloys in solder applications expecting frequent vibration. Hypoeutectic Sn-Zn alloys did not enhance crack propagation rate unlike near-eutectic and hypereutectic Sn-Zn alloys when exposed to resonant frequencies in the 70 Hz range [57].

iv) Lap Shear

Shearing tests are generally conducted to evaluate the mechanical force or number or cycles at a specific shear magnitude required to destroy the capacity of the interconnect to function electrically. Often, the goal is to simulate the CTE mismatch induced mechanical stresses observed in typical thermal cycles during actual operation. Many types of shear tests are commonly used in industry such as ball impact test (BIT), high speed ball shear test (HSBS), and high speed cold ball pull test (HSCBP) [[58]-[61]]. In the test, individual solder balls receive a high speed mechanical loading which is often applied or even ramped up until the ball separates from the substrate. However, the solder balls in these tests are only joined on one side of the interconnect making the accuracy of predictions made about real applications where a solder column is fused to IMC at each end, suspect [61]. In lap-shear testing, a volume of solder is joined to PCB or other substrates at the top and bottom of the interconnect. These substrates are then pulled apart to generate shear stress within the solder while the shear force is measured with a load cell. The deflection of the solder column can be measured ex-situ by measuring the change in length of the assembly or in-situ using digital image correlation (DIC). Shear stress and shear strain are calculated using force, and deflection data respectively.

Lap-shear tests are very useful for making determinations about process quality and material properties such as solder creep strain response and ultimate shear strength [[61]-[63]]. Choudhury and Ledani evaluated the stress-strain response of Sn-3.5Ag solder which contained a

high fraction of Sn-3.5/Cu intermetallic compounds, finding that strain-to-failure was greatly affected by the presence of IMC's within the interconnect [62]. They reported that IMC volume fractions in the 40 % to 60 % range resulted in a large increase in shear strength (nearly 67 % in the case of 60 % IMC). Additionally, an IMC fraction of 80% was observed to result in a decrease in shear strength compared to 60 % IMC but was still stronger than a 40 % IMC volume fraction [62]. In their study of creep behavior in innolot solder alloy, Tao et. al. confirmed that temperature and applied shear stress greatly affect the material behavior of the solder alloy when conducting lap-shear tests at 25 °C, 75 °C, and 125 °C [63]. Higher creep rates were seen in conditions of high temperature and high applied stress.

Lap-shear tests' utility in assessing reliability and failure in actual applications are limited due to their dependence on using comparatively large volumes of bulk solder in non-practical solder arrangements. Additionally, most lap-shear tests do not account for the cyclic nature of shear stress as seen in device operation. Without the ability to test actual devices across a range of stress magnitudes consistent with those seen in applications due to temperature fluctuation during power cycling, lap-shear tests are ill-suited for providing design optimization guidance or rapid architecture reliability assessment in real world applications.

#### v) Innovative Alternative Techniques

Many additional test methodologies have been devised, with more being developed all the time. These methods seek to achieve more consistent, more accurate, or more rapid solder fatigue results than can be achieved with the traditional methods or other alternative test. Additionally, some of these methods are designed as tools to assist in the breakdown of the solder fatigue system into more easily studied component failure mechanisms. One novel solder fatigue test was developed by J. F. Liu et. al., where small solder samples can be tested using

impact of tensile/compressive loading to determine the effects of mechanical loading on reliability [64]. Observing that standard impact tests can result in varying velocities of the impact plate, Liu et. al. concluded that direct impact is not the best method for testing small solder joints which undergo brittle fracture under tension [64]. To address this, a miniature impact test instrument was designed where the specimen is attached between input and output bars, and impact is administered using a hollow striker which impinges on the back face of the strike plate. Long, thin bars are used to accommodate small samples, and allow for moderate strain rates because a sustained loading pulse is required [64]. Upon impact of the striker, the impact plate achieves a common velocity which generates a tensile pulse in the input bar. As compression commences, a velocity at the impact plate-specimen interface generates a compressive pulse. The recorded input wave is thus the superposition of the two pulses and is measured using strain gauges [64].

Dynamic compressive tests were conducted on small cylindrical 4043 Al specimens for comparison with a traditional Hopkinson bar system, and the results of the miniature impact tester correlated well with the results using the traditional system [64]. In addition to single impact testing, this test apparatus is capable of conducting pure shear testing of devices with the installation of specially designed adaptors. Adaptors were also created to test solder interconnects at loading angles of 0°, 15°, 30°, 45°, 60°, 75°, and 90°. The adaptors can be threaded to the input and output bars and the solder joint specimens are bonded to the adapters using cyanoacrylate adhesive [64].

In an effort to address the need for lap-shear testing machines which were more reasonably scaled to actual solder interconnects, Tao et. al., designed a miniature lap-shear testing unit with a load capacity suited to small samples (such as CSP) with a maximum tensile

force of 2.0 kN and a wide range of cross-head speeds (39 nm/s minimum) [65]. The machine has the capability to conduct tensile and compressive lap-shear tests, as well as, a cyclic loading ability. The sample is attached at one end to a bar which is fixed, and at the other to a motorized bar which provides the stroke that induces stress in the material. The stress is measured by a load cell attached to the fixed end and the shear stress is calculated. Evaluating lap joints of Innolot and SACBiNi solder alloys at different strain rates and temperatures using this setup, Tao et. al., observed decreases in ultimate shear strength (USS) for both alloys. At room temperature with a strain rate of 2.0 x  $10^{-2}$  s<sup>-1</sup>, USS values of 58.9 MPa and 61.1 Mpa were reported for SACBiNi and Innolot respectively, while at 125 °C with a strain rate of 2.0 x  $10^{-4}$  s<sup>-1</sup>, USS was decreased to 26.6 MPa and 29.5 MPa for SACBiNi and Innolot repectively [65]. Examining the microstructure of these joints, rupture was seen to start in the bulk solder material and propagated towards the interface with the thinnest IMC layer. Some vacancies were observed locally at the interface between IMC layers and the solder joint [65]. Higher quantities of Ni and Sb were seen to reduce strength and improve elongation to rupture.

Ohguchi et. al., utilized stepped ramp wave cyclic mechanical loading to evaluate the low-cycle fatigue life of SAC305 and Sn-37Pb solders [67]. Using stepped ramp waves (SW), the researchers were able to quantify creep strain in tensile and cyclic tensile-compressive loading without conducting creep tests. Fatigue tests were conducted using cyclic tension-compression loadings with different periods for a total strain amplitude of  $\pm 5$  % at ambient temperature [67]. For comparison with other fatigue tests, triangular wave (TW) loading was also used. The SW tests were used to obtain stress-strain relations that were then used to evaluate the creep strains generated during the TW tests. Cylindrical ingots of SAC305 (gauge length 18 mm, gauge diameter 8mm) were subjected to a two-step fatigue process. First, TW loading was

used to determine the effect of period on fatigue life of the test units under tension-compression cycling. The tested units were then subjected to SW loading to identify creep deformation strain generated during the TW tests [67].

Four test conditions were selected to evaluate effects of time-in-tension and time-incompression on the stress amplitude and the symmetry between stress-strain response in compression versus in tension [67]. Condition 1 stipulated a time-in-tension of 2 seconds with a time-in-compression of 20 seconds; for condition 2, these values were reversed. Conditions 3 and 4 alternated times of 2 seconds and 200 seconds between tension and compression. The results showed that larger differences in period result in larger differences in maximum absolute stress. Conditions 2 and 4 were seen to have higher stress on the compressive side while conditions 1 and 3 had higher stress on the tensile side. Conditions 3 and 4 were found to exhibit hysteresis loops that had a high degree of asymmetry [67]. Ohguchi et. al., concluded that creep strain accumulated on the side in tension greatly affects fatigue life in solder materials. These tests were performed in a manner quite useful for materials characterization studies, however, the test samples utilized did not adequately represent solder interconnects commonly found in device applications. If the method could be adapted to work with full-scale electronic devices, it may prove a useful method for predicting creep strain response of solder joints.

#### 2.3 Summary of Techniques

Table 2-1 shows a comparison of all the accelerated testing methods outlined above. Of the methods presented here, power cycling is seen by many as the most true-to-life method for generating failure modes consistent with actual operating cycles. This makes PC an attractive option for predicting operating fatigue lifetime. However, PC is still slower than mechanical testing methods. Temperature cycling and thermal shock tests are uniquely susceptible to

diffusion due to the high thermal gradients involved in reaching test temperatures. Additionally, for all three testing methods, understanding the causes behind failure mode characteristics is made difficult because thermal, chemical, mechanical (and in PC electrical) threat variables are involved in interconnect fatigue simultaneously. The lack of this key understanding often results in test parameters which are intentionally pessimistic, creating harsher conditions than those seen in actual operation, leading to overly-conservative lifetime estimates. Thermo-mechanical methods are typically faster due to the use of combined mechanical and thermal stress inducement, leading to higher total stresses. These methods are perhaps the most useful for studying the effects of combined thermal and mechanical threat variables on fatigue lifetime. However, this approach can only produce accurate predictions if the specific mechanical and thermal conditions and how they will interact are known prior to testing so that proper test parameters can be selected. Due to the increased stress state of the system, coupled with mixing stress sources can result in unusual or false failure modes rarely (if ever) seen in actual working devices. Like TC, TS and PC, these methods often report "worst-case", overly-conservative lifetime estimations.

| Comparison of Accelerated Testing Methods |                                                  |               |              |                            |                 |                          |

|-------------------------------------------|--------------------------------------------------|---------------|--------------|----------------------------|-----------------|--------------------------|

| Method                                    | Mech. Stress<br>Inducer                          | Test Duration | Cyclic       | Device Relevant<br>Samples | Design Guidance | Lifetime Prediction Type |

| Temp. Cycling                             | CTE Mismatch                                     | Slow          | ✓            | $\checkmark$               | $\checkmark$    | General Fatigue          |

| Therm. Shock                              | CTE Mismatch                                     | Moderate      |              | $\checkmark$               | $\checkmark$    | General Fatigue          |

| Pwr. Cycling                              | CTE Mismatch                                     | Slow          | $\checkmark$ | $\checkmark$               | $\checkmark$    | General Fatigue          |

| Mech. Shock                               | Shock/Impact                                     | Rapid         |              | $\checkmark$               | $\checkmark$    | Shock Fatigue            |

| Bending                                   | Shear/Tension/C<br>ompression<br>Shear/Tension/C | Moderate      |              |                            |                 | General and/or Bending*  |

| Vibration                                 | ompression                                       | Moderate      |              | $\checkmark$               | $\checkmark$    | Vibration Fatigue        |

| Lap Shear                                 | Shear                                            | Moderate      |              |                            |                 |                          |

| Mech. Cycling                             | Shear                                            | Rapid         | $\checkmark$ | $\checkmark$               | $\checkmark$    | General Fatigue          |

Table 2-1

\* Bending tests can be used to examine bending fatigue lifetime specifically, or to simulate stresses induced by CTE mismatch for comparison with TC or PC methods.

Mechanical testing methods generally have the benefit of shorter test duration which can significantly lower costs and product lead times. In the case of mechanical tests like mechanical shock, vibration, and bending, often the fatigue lifetime predictions are specific to a unique type of stress rather than the more general types of stress found due to CTE mismatch, Mechanical shock is an excellent way to evaluate the ability of a device to survive repeated large impact events. However, using MS to make predictions on general fatigue lifetime of a device due to CTE mismatch when under real-world power cycling or to compare predictions with TC for example is problematic. Impact testing generally creates unique failure modes that are not represented in CTE mismatch failures. Making CTE mismatch fatigue predictions using bending tests can give good results for general fatigue lifetime or for the more specific bending fatigue lifetime depending upon the parameters and intentions of the test. Bending has been used to simulate the stress conditions found in devices under PC and TC conditions to induce the same types of failure mechanisms. When conducted this way, the resulting fatigue life predictions can be considered as more accurate that making the same prediction using MS or vibration. Moreover, if a device is expected to the subjected to bending frequently during its lifetime, bending tests are critical to gaining insight into the overall reliability of the device by considering the impact of the bending itself, but this is less important for non-dynamic situations where bending in not the most prominent stress inducing phenomenon. Similarly, vibration tests are critical if a device is expected to endure vibration often during its useful lifetime but these tests do not create the conditions necessary to produce shear magnitudes and direction consistent with CTE mismatch, unlike mechanical cycling and temperature cycling methods.

Lap shear methods are perhaps the most useful methods for evaluating solder material properties and the effects of the solder processing procedure on interconnect microstructure

because all the damage is due to stresses which are easily understood using physics first principles. This makes damage assessment and responsibility assignment much easier, especially when coupled with the simplistic structure of most lap shear test specimens. Unfortunately, these methods are typically incapable of testing full-scale electronic devices, making them of limited value for generating fatigue lifetime predictions and certainly inferior to mechanical cycling methods where the microstructural changes, as well as actual device lifetime, can both be monitored in situ. The method developed by Liu et. al. is perhaps the most versatile approach discussed given the extensive versatility in testing configurations for generating different types of stress (including shear, tension/compression, and impact) but can only be used on a single small solder interconnect. The stepped ramp-wave approach is particularly useful in examining creep behavior within solder interconnects to determine its effect on fatigue life. It is also capable of providing some guidance as to design considerations, with [67] determining that creep strain accumulated on the side in tension had the greatest impact on lifetime, indicating that special care must be taken in designing the tension-side architecture.

The method discussed throughout the rest of this work was developed to address the weaknesses and limitations of the above reliability evaluation methods. The mechanical cycling method presented in this paper was designed to mimic the cyclic behavior of stresses induced in normal operational power cycling, with the aim of improving accuracy over single cycle tests like lap shear. Additionally, by cycling at high frequency (60 cycles/minute), test duration is significantly reduced enabling a reduction is associated costs. Another goal of this time saving strategy was to create a testing system that could be used to evaluate very early stage device designs to provide reliability analysis of prototypes to enhance the design decision-making process. Designed to test fully functional chip-scale devices and mechanically analogous dummy

chips, the method was designed with device specific adaptation capabilities in mind. The

following section presents a paper published in the IEEE Transactions on Device and Materials

*Reliability* [68], which details the methodology behind the testing procedure.

# 2.4 References

- [1] J. Li, J. Karppinen, T. Laurilla and J. K. Kivilahti, "Reliability of lead-free solder interconnections in thermal and power cycling tests," *Transactions on Components and Packaging Technologies*, vol. 32, no. 2, pp. 302-308, 2009.

- [2] J. Hagberg, J. Putaala, J. Raumanni, O. Salmela and T. Galkin, "BGA Interconnection Reliability in Mirrored Module Configurations," *Transactions on Components*, *Packaging and Manufacturing Technology*, vol. 7, no. 10, pp. 1634-1643, 2017.

- [3] R. Ghaffarian, "Chip Scale Package Implementation Challenges," *in 49th Electronics Components and Technology Conference*, San Diego, CA, 1999.

- [4] E. A. Luis and W. Q. Meeker, "A Review of Accelerated Test Models," *Statistical Science*, vol. 21, no. 4, pp. 552-577, 2006.

- [5] JEDEC, JEDEC Standard for Temperature Cycling, JESD22-A104D, 2005.

- [6] C. Kuper, "Thermal testing and quality assurance of BGA, LCC, and QFN electronic packages," University of New Mexico, 2015.

- [7] H. Cui, "Accelerated temperature cycle test and Coffin-Manson model for electronic packaging," *in Proceedings of the Reliability and Maintainability Symposium*, 2005.

- [8] J. G. Lee, and K. N. Subramanian, "Effects of TMF Heating Rates on Damage Accumulation and Resultant Mechanical Behavior of Sn–Ag based Solder Joints," *Microelectronics Reliability*, Vol. 47, pp. 118-131, 2007.

- [9] S. C. Chaparala, B. D. Roggeman, J. M. Pitarresi, B. G. Sammakia, J.

- [10] Jackson, G. Griffin, and T. McHugh, "Effect of Geometry and Temperature Cycle on The Reliability of WLCSP Solder Joints *Transactions on Components, Packaging and Manufacturing Technology*, Vol. 28, pp. 441-448, 2005.

- [11] K. C. Wu, S. Y. Lin, T. Y. Hung and K. N. Chiang, "Reliability Assessment of Packaging Solder Joints Under Different Thermal Cycle Loading Rates," *Transactions on Device and Materials Reliability*, Vol. 15, pp. 437-442, 2015.

- [12] D. Shnawah, M. Sabri and I. Badruddin, "A review on thermal cycling and drop impact reliability of SAC solder joints in portable electronic products," *Microeletronics Reliability*, vol. 52, no. 1, pp. 90-99, 2012.

- [13] T. T. Mattila, M. Mueller, M. Paulasto-Krockel and K. J. Wolter, "Failure mechanism of solder interconnections under thermal cycling conditions," *in Proceedings of the 3rd Electronics System-Integration Technology Conference*, 2010.

- [14] R. Weglinski, "Highly accelerated stress screening for air-cooled switching power supplies," TDIPower, 2007.

- [15] E. Dalton, G. Ren, J. Punch and M. N. Collins, "Accelerated temperature cycling induced strain and failure behaviour for BGA assemblies of third generation high Ag content Pb-free solder alloys," *Materials and Design*, vol. 154, pp. 184-191, 2018.

- [16] L.-Y. Gao, Z.-Q. Liu and C.-F. Li, "Failure Mechanisms of SAC/Fe-Ni Solder Joints During Thermal Cycling," *Journ. Electronic Materials*, vol. 46, no. 8, pp. 5338-5348, 2017.

- [17] W.-C. Chuang, B. Tsai, W.-L. Chen and J. Su, "Reliability of ball grid array subjected to thermal cycling," in *Proceedings of the 2017 Symposium on Design, Test, Integration and Packaging of MEMS and MOEMS*, 2017.

- [18] K.-C. Wu, S.-Y. Lin, T.-Y. Hung and K.-N. Chiang, "Reliability assessment of packaging solder joints under different thermal cycle loading rates," *Transactions of Device and Materials Reliability*, vol. 15, no. 3, pp. 437-442, 2015.

- [19] J. Sitek, A. Arazna, K. Janeczek, W. Steplewski, K. Lipiec, K. Futera and P. Ciszewski, "Influence of thermal cycling on reliability of solder joints executed on long and metal core PBCs," *Soldering and Surface Mount Technology*, vol. 27, no. 3, pp. 120-124, 2015.