## University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

12-2018

# Stability Analysis of a High-Power Microgrid

David Manuel Carballo Rojas University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd Part of the <u>Electrical and Electronics Commons</u>, and the <u>Electronic Devices and Semiconductor</u> <u>Manufacturing Commons</u>

#### **Recommended** Citation

Carballo Rojas, David Manuel, "Stability Analysis of a High-Power Microgrid" (2018). *Theses and Dissertations*. 3068. https://scholarworks.uark.edu/etd/3068

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

Stability Analysis of a High-Power Microgrid

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

by

### David Carballo Rojas University of Arkansas Bachelor of Science in Electrical Engineering, 2016

#### December 2018 University of Arkansas

This thesis is approved for recommendation to the Graduate Council

Juan Carlos Balda, Ph.D. Thesis Director

Roy A. McCann, Ph.D. Committee Member Simon Ang, Ph.D. Committee Member

#### ABSTRACT

The objective of this thesis is to perform the modeling and stability analysis of a highpower microgrid with multiple parallel-and grid connected voltage source converters using the system parameters from the high-power microgrid testbed at the National Center for Reliable Electric Power Transmission (NCREPT) at the University of Arkansas in order to identify, minimize, if not eliminate, the potential instabilities that can affect the proper operation of the microgrid testbed. To achieve this objective, the mathematical modeling of the high-power microgrid considering the adverse effects of resonances due to interactions among the converter LCL output filters is presented and analyzed. Moreover, the stability range of the high-power microgrid under different conditions is examined using the root locus analysis technique and the theoretical analysis is validated through MATLAB/Simulink<sup>TM</sup> simulations. The results from this analysis are then used to develop general guidelines to avoid resonance and stability issues when connecting power converters into a microgrid.

In addition, a scaled-down prototype of the high-power microgrid testbed at NCREPT, the so-called "mini-NCREPT", is designed and constructed to reproduce some of the issues already encounter in the high-power tested and to developed countermeasures in a laboratory environment without the safety restrictions typical of high-power applications. Furthermore, this scaled-down prototype can be used in future applications to test advanced microgrid control algorithms before deploying them at the high-power microgrid testbed. Finally, an in-depth analysis of the experimental results of the scaled-down prototype is presented and solutions to improve the power quality of the system are suggested.

#### ACKNOWLEDGMENTS

I would like to express my sincere gratitude to my Ph.D. advisor Dr. Juan Carlos Balda for giving me the opportunity to work on this project and for all his support and guidance. I want to extend my gratitude and thankfulness to my committee members Dr. Roy a. McCann and Dr. Simon Ang for all their support. Moreover, I would especially like to thank Vinson Jones for his patience, guidance, and motivation. Vinson was not only the best lab mate I could have asked for but also an amazing friend, and I wish him a future full of happiness and success.

Finally, I would also like to thank my friends and fellow students: Edgar Escala, Rafael Franceschi, Luciano García, Obaid Aldosari, Daniel Schwartz, Jeremy Lingo, Haider Mhiesan, Tyler Adamson, Waleed Alhosaini, Hazzaz Mahmud, Shuang Zhao.....

## DEDICATION

To my beloved parents, Manuel Carballo and Berta Rojas, and all my friends who were always there for me and provided unconditional love and support.

## **TABLE OF CONTENTS**

| CHAP  | TER 1   |                                                        |

|-------|---------|--------------------------------------------------------|

| INTRO | ODUCT   | TION1                                                  |

| 1.1   | Motiv   | ation for this Research Work1                          |

| 1.2   | Object  | tives of Thesis8                                       |

| 1.3   | Organ   | ization of Thesis8                                     |

| 1.4   | Refere  | ences9                                                 |

| СНАР  | TER 2   |                                                        |

| STAB  | ILITY   | ANALYIS OF MULTIPLE GRID-CONNECTED INVERTERS USING     |

| DIFFE | ERENT   | FEEDBACK CURRENTS                                      |

| Abst  | ract    |                                                        |

| 2.1   | Introd  | uction13                                               |

| 2.2   | Model   | ing of the Parallel Inverters14                        |

|       | 2.2.1   | Inverter-Side Current - Mathematical Modeling14        |

|       | 2.2.2   | Grid-Side Current – Mathematical Modeling16            |

| 2.3   | Stabili | ty Analysis and Active Damping17                       |

|       | 2.3.1   | Control Strategy17                                     |

|       | 2.3.2   | Stability Analysis for the Inverter-Side Current Case  |

|       | 2.3.3   | Stability Analysis for the Grid-Side Current Case23    |

|       | 2.3.4   | Filter Design Considerations on the System Stability26 |

| 2.4   | Simula  | ations Results                                         |

| 2.5   | Concl   | usions                                                 |

| 2.6   | Ackno   | owledgments                                            |

| 2.7   | References                                                      | 30         |

|-------|-----------------------------------------------------------------|------------|

| 2.8   | Permissions                                                     | 32         |

| СНАР  | PTER 3                                                          |            |

| MODI  | ELING AND STABILITY ANALYSIS OF GRID-CONNECTED INVE             | RTERS WITH |

| DIFFE | ERENT LCL FILTERS PARAMETERS                                    |            |

| Abst  | tract                                                           | 35         |

| 3.1   | Introduction                                                    |            |

| 3.2   | Modeling of the Parallel Inverters                              |            |

|       | 3.2.1 Grid-Side Current – Mathematical Modeling                 |            |

|       | 3.2.2 Selecting of the LCL Filter Parameters                    | 40         |

|       | 3.2.3 Multiple Resonance Peaks                                  | 41         |

| 3.3   | Stability Analysis of the Parallel Inverters                    | 43         |

|       | 3.3.1 Control Strategy                                          | 43         |

|       | 3.3.2 Stability Analysis for Grid-Side Current                  | 44         |

| 3.4   | Comparison with the Stability Analysis of Identical LCL Filters | 46         |

|       | 3.4.1 Motivation for Comparison                                 | 46         |

|       | 3.4.2 Interactive-Current Stability                             | 48         |

|       | 3.4.3 Common-Current Stability                                  | 49         |

| 3.5   | Simulations Results                                             | 51         |

| 3.6   | Conclusions                                                     | 53         |

| 3.7   | Appendix                                                        | 53         |

| 3.8   | Acknowledgments                                                 | 54         |

| 3.9   | References                                                      | 54         |

| 3.10  | Permi  | ssions                                            | 55 |

|-------|--------|---------------------------------------------------|----|

| СНАР  | TER 4  |                                                   |    |

| DESIC | GN OF  | THE SCALED-DOWN REGEN BENCH PROTOTYPE             | 57 |

| 4.1   | Introd | uction                                            | 57 |

| 4.2   | Desig  | n of the Prototype Power Stage                    | 57 |

|       | 4.2.1  | Scaling-Down the Case Study                       | 57 |

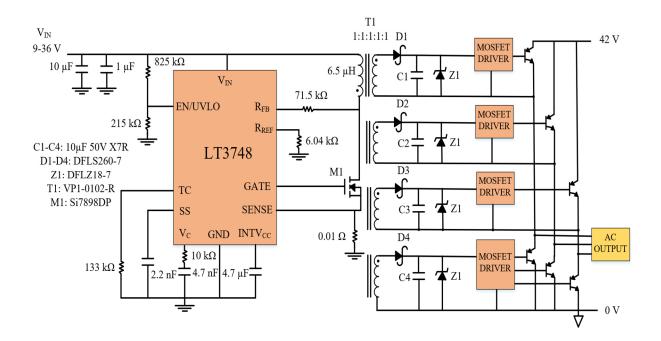

|       | 4.2.2  | Design of the Gate Driving Circuit                | 59 |

|       | 4.2.3  | LCL Filter Interface                              | 62 |

| 4.3   | Sensor | rs and Measurement Conditioning                   | 62 |

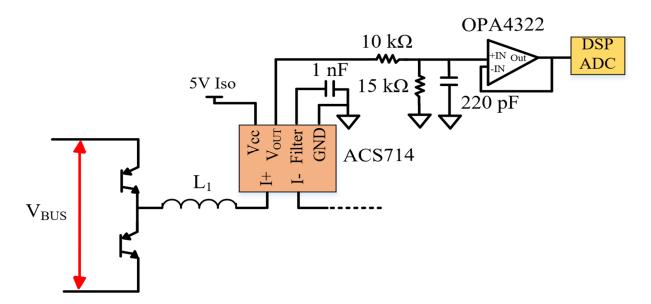

|       | 4.3.1  | Current Sensing Circuit                           | 62 |

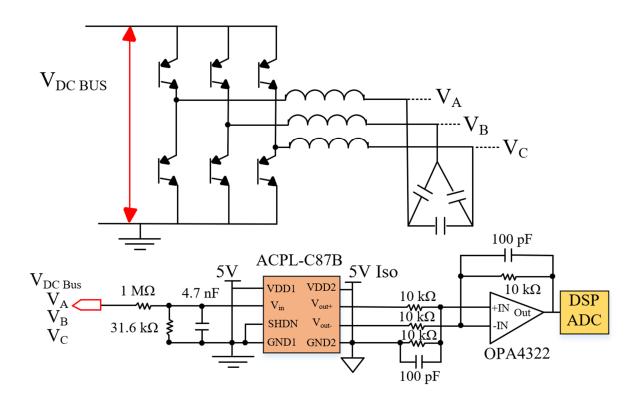

|       | 4.3.2  | Voltage Sensing Circuit                           | 63 |

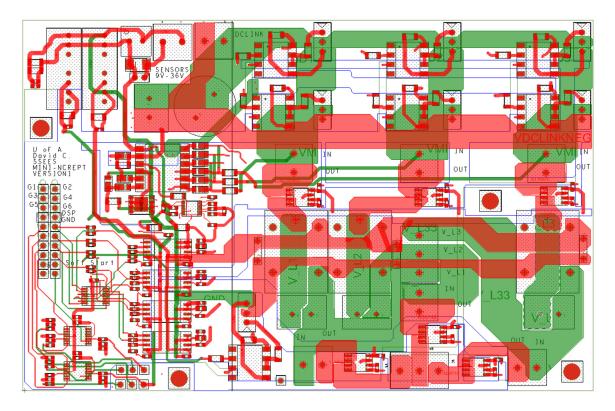

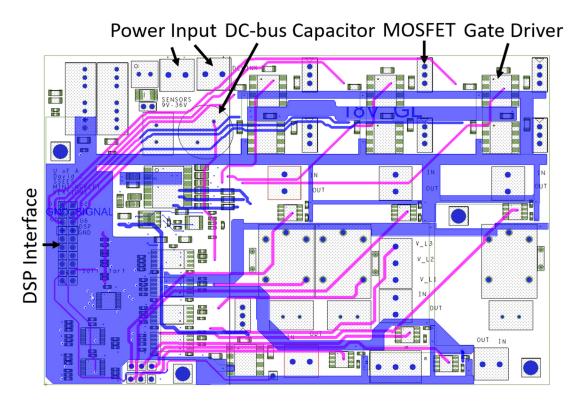

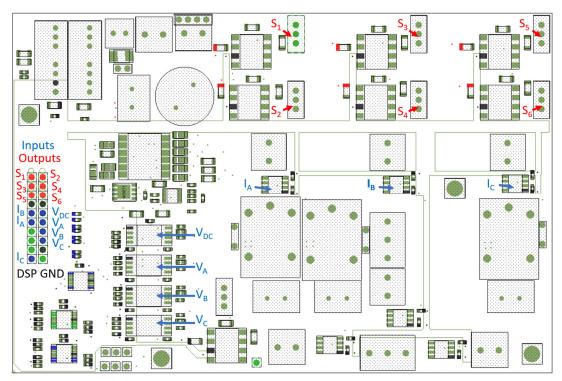

| 4.4   | Desig  | n of the Printed Circuit Board                    | 65 |

| 4.5   | Concl  | usions                                            | 67 |

| 4.6   | Refere | ences                                             | 68 |

| СНАР  | TER 5  |                                                   |    |

| IMPL  | EMENT  | TATION OF THE SYSTEM CONTROL ALGORITHM IN A DSP   | 69 |

| 5.1   | Introd | uction                                            | 69 |

| 5.2   | Deriva | ation of Discrete Functions on the DSP            | 69 |

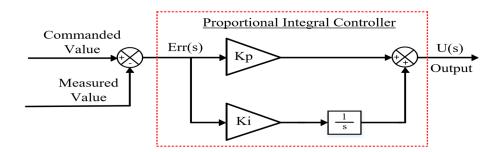

|       | 5.2.1  | Proportional Integral (PI) Controller             | 70 |

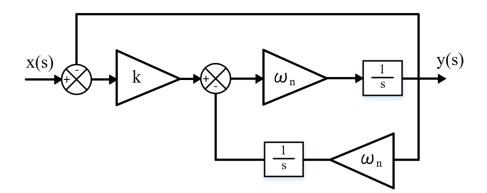

|       | 5.2.2  | Second-Order Generalized Integrator (SOGI) Filter | 71 |

|       | 5.2.3  | DQ0 to α-β Transformation                         | 74 |

| 5.3   | Devel  | oping a Single-DSP System                         | 75 |

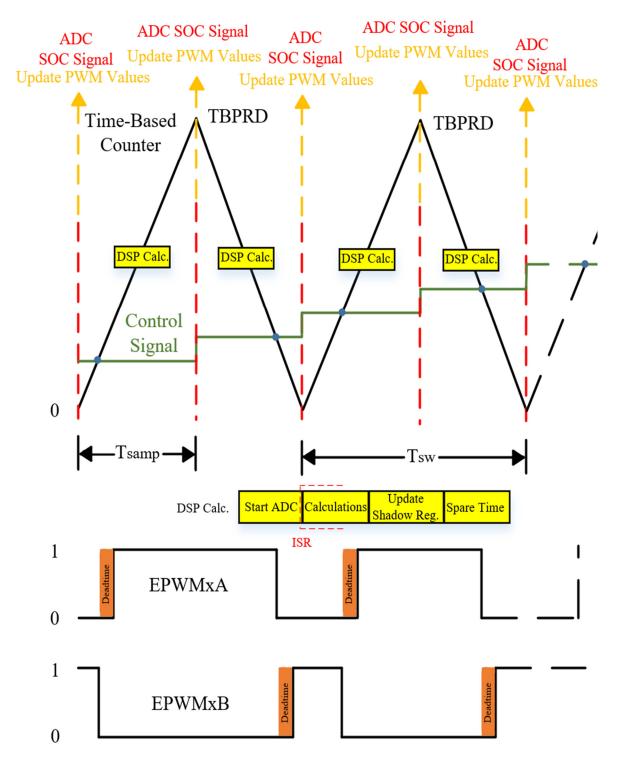

|       | 5.3.1  | Analog-to-Digital Converter Module                | 76 |

|       | 5.3.2   | Enhanced Pulse Width Modulator Module         | 77  |

|-------|---------|-----------------------------------------------|-----|

| 5.4   | Contro  | oller Implementation in the DSP               |     |

|       | 5.4.1   | Scaling of the ADC Results                    | 82  |

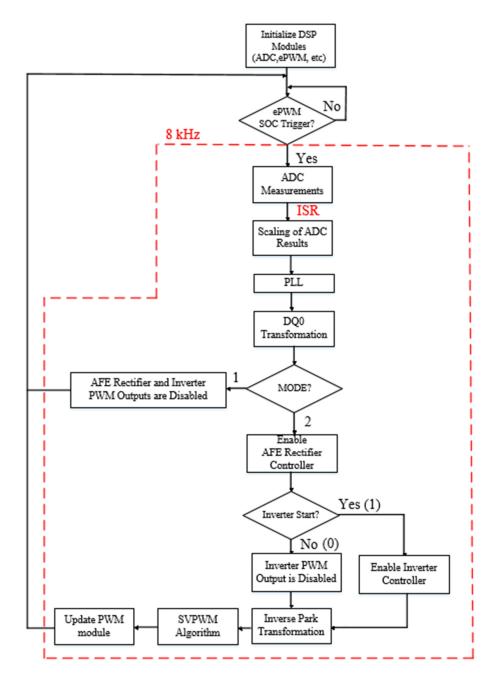

|       | 5.4.2   | DSP Control Flow                              | 83  |

| 5.5   | Concl   | usions                                        |     |

| 5.6   | Refere  | ences                                         | 87  |

| CHAF  | TER 6   |                                               |     |

| TEST  | ING OF  | THE SCALED-DOWN REGEN BENCH PROTOTYPE         |     |

| 6.1   | Introd  | uction                                        |     |

| 6.2   | Testin  | g of a Single Scaled-Down Regen Bench         | 89  |

|       | 6.2.1   | Transient Response of a Single Regen Bench    | 90  |

|       | 6.2.2   | Steady-State Response of a Single Regen Bench | 93  |

| 6.3   | Testin  | g of Two Parallel Scaled-Down Regen Benches   | 94  |

| 6.4   | Concl   | usions                                        |     |

| 6.5   | Refere  | ences                                         | 100 |

| CHAF  | TER 7   |                                               |     |

| CONC  | CLUSIC  | ONS AND RECOMMENDATIONS FOR FUTURE WORK       | 102 |

| 7.1   | Concl   | usions                                        | 102 |

| 7.2   | Recon   | nmendations for Future Work                   | 104 |

| 7.3   | Refere  | ences                                         | 105 |

| APPE  | NDIX A  | A                                             |     |

| DIGIT | CAL SIG | GNAL PROCESSOR CODE                           | 107 |

| A.1   | The M   | Iain.c File                                   |     |

| A.2 The Controller.c File             |                          |

|---------------------------------------|--------------------------|

| APPENDIX B                            |                          |

| MATLAB SCRIPTS                        |                          |

| B.1 Bode Plots of a Single and Two Pa | arallel Regen Benches139 |

## LIST OF FIGURES

| Fig. 1.1: A typical microgrid structure with DG, DS and loads                                        |

|------------------------------------------------------------------------------------------------------|

| Fig. 1.2: Experimental current waveforms for NCREPT in the grid-connected mode for (a) a             |

| single regen bench, and (b) two parallel regen benches                                               |

| Fig. 2.1: Schematic of multiple paralleled grid-connected inverters                                  |

| Fig. 2.2: Current control model (a) s-domain (b) z-domain                                            |

| Fig. 2.3: Root loci of the inverter-side current for interactive (I.C) and common currents (C.C).20  |

| Fig. 2.4: Current control model in z-domain with capacitor-voltage feedforward active damping.       |

|                                                                                                      |

| Fig. 2.5: Root loci of the interactive and common currents for inverter-side feedback with           |

| capacitor-voltage feedforward algorithm                                                              |

| Fig. 2.6: Root loci of the grid-side current for interactive and common currents                     |

| Fig. 2.7: Root loci of the interactive and common currents for grid-side feedback with capacitor-    |

| voltage feedforward algorithm                                                                        |

| Fig. 2.8: Stability range for inverter- and grid-side current feedback for different cases: (a) fs   |

| =fsw without active damping (b) fs =fsw with active damping (c) fs =2fsw without active              |

| damping (d) fs =2fsw with active damping                                                             |

| Fig. 2.9: Current waveforms for (a) inverter-side current feedback (b) grid-side current feedback.   |

|                                                                                                      |

| Fig. 3.1:Schematic of multiple grid-connected inverters with different LCL filter parameters 38      |

| Fig. 3.2: Auxiliary circuit of two parallel inverters with different LCL filters parameters provided |

| that (a) all voltage sources except vo1 are zero, (b) all voltage sources except vo2 are zero 39     |

| Fig. 3.3: Resonance peaks of the paralleled grid-connected inverters                                 |

| Fig. 3.4: Schematic of two paralleled grid-connected inverters with the LCL parameters of (a)        |

|------------------------------------------------------------------------------------------------------|

| inverter A, (b) inverter B                                                                           |

| Fig. 3.5: Multiple current-control loop for the grid-side currents in (a) s-domain, (b) z-domain. 44 |

| Fig. 3.6: Poles of the (a) paralleled inverter system with Kp from Table 3.1, (b) individual         |

| inverter system                                                                                      |

| Fig. 3.7: Poles of the system for (a) maximum value of Kp for the interative stability, (b)          |

| inversely changing the value of Kp for the two inverters                                             |

| Fig. 3.8: Equivalent N-inverter model to measure the common-current stability gains                  |

| Fig. 3.9: Poles of the system for maximum values of Kp for the common-current stability in           |

| Table 3.3                                                                                            |

| Fig. 3.10: Simulation results of (a) multiple paralleled- (b) individual grid-connected inverters    |

| with the values from Table 3.1                                                                       |

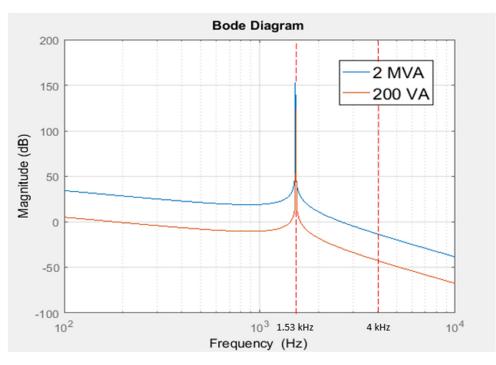

| Fig. 4.1: LCL filter open-loop response of the parameters of Table 4.1                               |

| Fig. 4.2: Schematic of the flyback converter configuration                                           |

| Fig. 4.3: Schematic of ACS714 current sensor configuration                                           |

| Fig. 4.4: Schematic of ACPL-C87B voltage sensor configuration                                        |

| Fig. 4.5: Top (Red), and bottom (Green) layers of PCB board                                          |

| Fig. 4.6: Layer 2 (Blue), and layer 3 (Pink) of PCB board                                            |

| Fig. 5.1: Block diagram for a PI controller                                                          |

| Fig. 5.2: Block diagram of the SOGI filter                                                           |

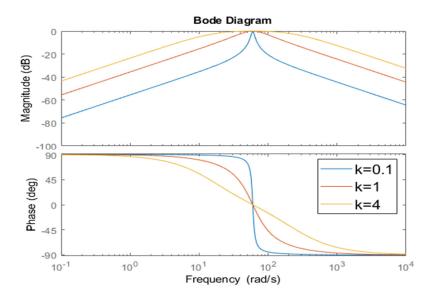

| Fig. 5.3: Bode plot of the SOGI filter transfer function with different values of k                  |

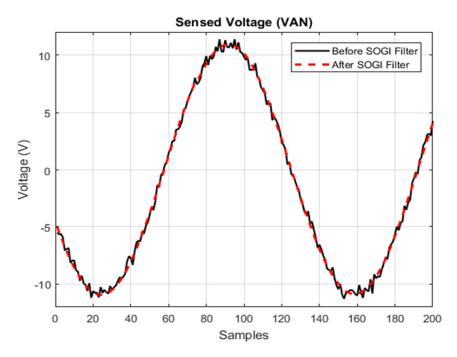

| Fig. 5.4: Effect of the SOGI filter on a voltage waveform                                            |

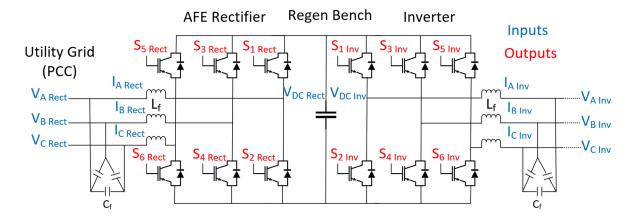

| Fig. 5.5: Schematic of the back-to-back VSCs of a regen bench                                        |

| Fig. 5.6: Mapping of I/O signals of the VSC to the scaled-down prototype board                      | 78             |

|-----------------------------------------------------------------------------------------------------|----------------|

| Fig. 5.7: Operation of the ePWM module                                                              | 81             |

| Fig. 5.8: Flowchart of the DSP processes                                                            | 34             |

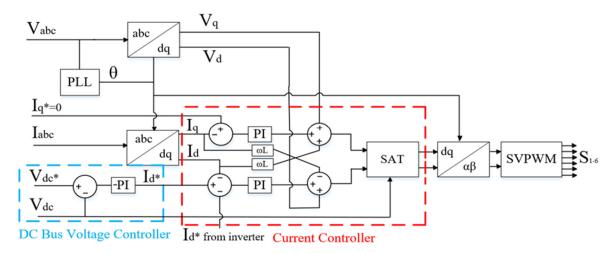

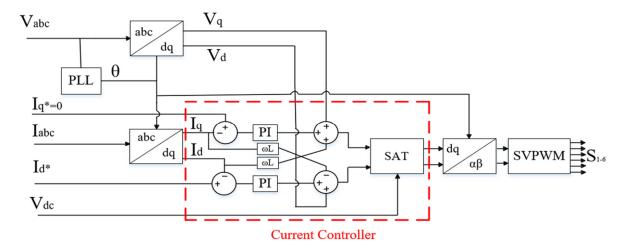

| Fig. 5.9: Control diagram of a grid-connected AFE rectifier                                         | 85             |

| Fig. 5.10: Control diagram of a grid-connected inverter                                             | 86             |

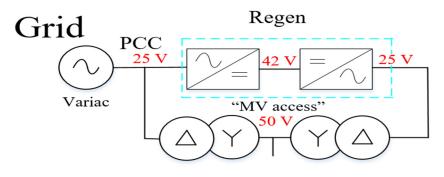

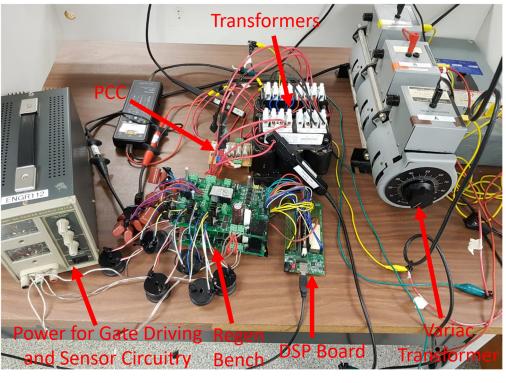

| Fig. 6.1: (a) One-line diagram, and (b) photograph of a single scaled-down regen bench              | 90             |

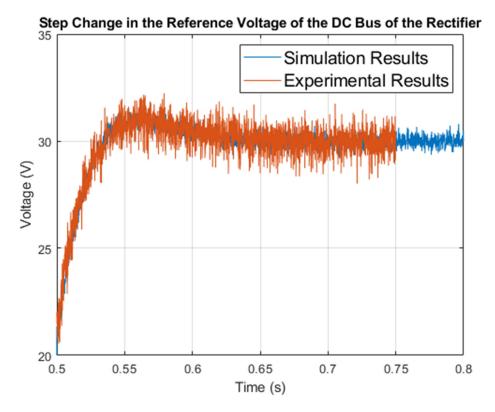

| Fig. 6.2: Step change in the reference voltage of the DC bus of the AFE rectifier                   | 91             |

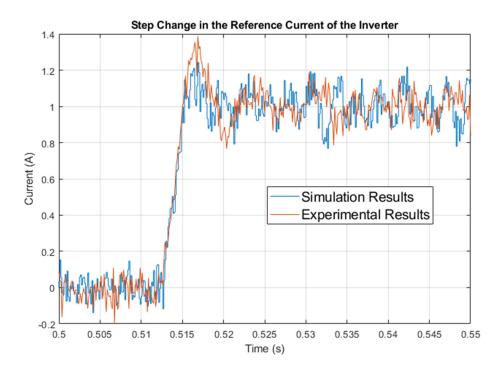

| Fig. 6.3: Step change in reference current of the inverter                                          | 92             |

| Fig. 6.4: Steady-state waveforms of a single regen bench: (a) experimental results, and (b)         |                |

| simulations results                                                                                 | <del>)</del> 3 |

| Fig. 6.5: FFT of the rectifier and inverter currents: (a) experimental results, and (b) simulations | ;              |

| results                                                                                             | 94             |

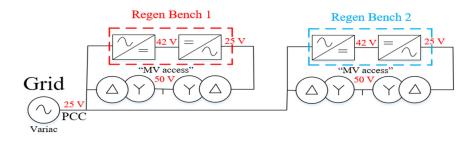

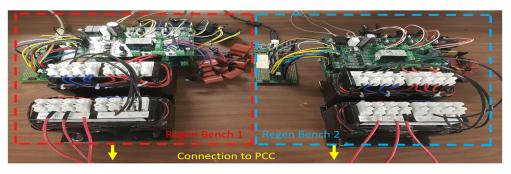

| Fig. 6.6: (a) One-line diagram, and (b) photograph of two scaled-down regen benches                 | 95             |

| Fig. 6.7: Experimental waveforms in steady state of two regen benches                               | 96             |

| Fig. 6.8: FFT of the rectifier and inverter currents for (a) regen bench 1, and (b) regen bench 2.  |                |

|                                                                                                     | <del>)</del> 7 |

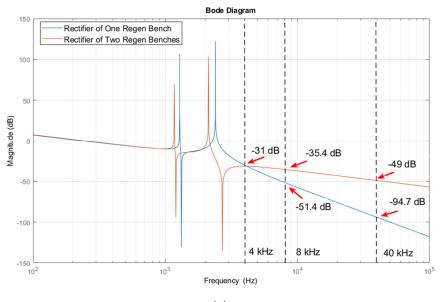

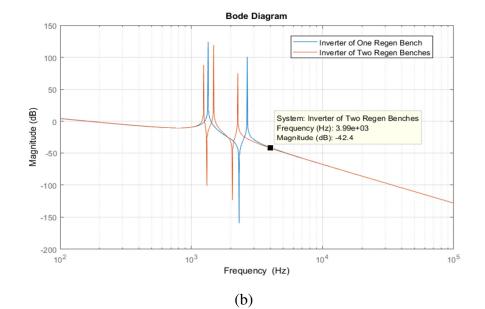

| Fig. 6.9: Schematic of a grid-connected regen bench                                                 | 97             |

| Fig. 6.10: Auxiliary circuit used to derive the transfer function of the rectifier                  | 98             |

| Fig. 6.11: Frequency response of (a) a rectifier and (b) an inverter with a single and two parallel | 1              |

| regen benches, respectively                                                                         | <del>9</del> 9 |

|                                                                                                     |                |

## LIST OF TABLES

| Table 2.1: System Parameters                                              | 20 |

|---------------------------------------------------------------------------|----|

| Table 3.1: System Parameters                                              | 42 |

| Table 3.2: Stability Range                                                | 47 |

| Table 3.3: System Parameters to Test Common Stability                     | 50 |

| Table 4.1: Parameters of the High-Power and Scaled-Down Microgrid Testbed | 58 |

| Table 4.2: Parameters of Scaled-Down Prototype MOSFETs                    | 59 |

| Table 5.1: ADC Module Input Signals                                       | 76 |

| Table 5.2: EPWM Module Output Signals                                     | 78 |

| Table 6.1: PI Controller Values for the Regen Benches                     | 92 |

#### LIST OF PUBLISHED PAPERS

#### CHAPTER TWO

[1] D. Carballo, E. Escala and J. C. Balda, "Stability Analysis of Multiple Grid-Connected Inverters Using Different Feedback Currents," 2018 9th IEEE International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Charlotte, NC, 2018, pp. 1-7.

#### CHAPTER THREE

[2] D. Carballo, E. Escala and J. C. Balda, "Modeling and Stability Analysis of Gridconnected Inverters with Different LCL Filter Parameters," *2018 IEEE Electronic Power Grid (eGrid)*, Charleston, SC, 2018.

#### **CHAPTER 1**

#### **INTRODUCTION**

#### **1.1 Motivation for this Research Work**

Modern society has become heavily reliant on a constant and secure supply of electric energy to the point where access to electricity is deemed as a right and a fundamental necessity [1]. For about one hundred years, the electrical infrastructure has been responsible for this constant delivery of energy. During that time, this infrastructure has remained mainly unchanged. Despite the aging of the electrical grid, the demand for electricity has steadily increased with the growth of the world population. The current electrical infrastructure, however, is not suited for these growing needs and demands, including resiliency in the face of natural and man-made disasters [2].

The existing electric grid has a centralized power generation with a unidirectional power flow where the electricity is generated far away from the load and is distributed through transmission and distribution lines. One of the deficiencies of the current grid is that it suffers from domino-effect failure because of this hierarchical and unidirectional design [3]. This has been seen in the Northeast blackout of 2003 where an overload of the transmission lines cascaded into the collapse of the electric grid for up to two days [4]. Another issue is that the system is somewhat inefficient with 8 percent of the generated energy being lost on the transmission lines and about 20 percent of the generated capacity being only available for peak demand (i.e., being operated only during a small percentage of the time). In addition, the electricity industry has been a contributing cause of greenhouse gas emissions due to the disproportionate use of fossil fuels [3]. Subsequently, innovative solutions, technologies and grid architectures are needed to address these issues and challenges.

In the last decades, the concept of microgrids was developed due to advancements in power electronics as well as innovations in small-scaled distributed power generation [5]. Microgrids offer solutions to the issues affecting the current electrical infrastructure through the integration of distributed energy resources (DERs). These DERs include distributed generation (DG) units with renewable sources like photovoltaic (PV) modules, wind turbines, microturbines, combined cooling, heat and power (CCHP), as well as distributed storage (DS) units such as flywheels, energy capacitors and batteries [1]. The integration of these DERs allows the reduction of carbon emissions due to the use of renewable energy sources instead of fossil fuels, thus, allowing countries to meet their goal of reducing greenhouse gas emission in compliance with the Kyoto protocol [6]. Moreover, since it is generated at the distribution level, the power does not have to "travel" through long transmission lines to reach the final users. Consequently, the system becomes more efficient due to the reduction of transmission losses. Other benefits include: increase of power quality and reliability by supporting and reducing dips in voltage, increase of resiliency, and a potentially decrease on the cost of energy supply [6].

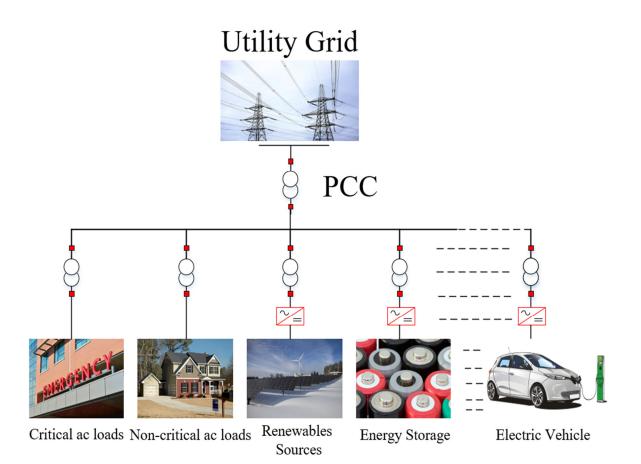

Fig. 1.1 illustrates a typical microgrid structure which comprises a portion of the electric power distribution system and includes various DG, DS, and loads. As seen in the figure, different renewable energy sources and energy storages are connected at the distribution level at the point of common coupling (PCC) to provide power to nearby loads. One of the most promising features of the microgrid is the ability to operate in either grid-connected or islanded mode and to be able to switch between those two modes [7]. In the grid-connected mode, the connection at the PCC is closed; thus, the main grid can provide the deficit power that the microgrid needs for the local loads while the microgrid can trade the excess power generated by the local sources to the main grid [7]. In the islanded mode, the connection at the PCC is

Fig. 1.1: A typical microgrid structure with DG, DS and loads.

opened; thus, the microgrid needs to have enough generating and storing capacities to balance the active and reactive powers demanded by the local loads after being disconnected from the utility system at the PCC [7], [8]. Because of the limited amount of available power in islanded mode, the microgrid might need to apply load shedding schemes to disconnect non-critical loads when an islanded event has been detected. This feature of being able to function autonomously from the macrogrid greatly increases the resiliency of the system since the microgrid can provide power to the local loads regardless of issues on the main grid.

Power electronics converters, as represented by the red boxes in Fig. 1.1, are normally used for the DERs to interface with the microgrid in order to achieve power flow regulation and

power factor correction [9]. The most common topology for these power electronic converters are based on pulse-width-modulation (PWM) voltage-source converters (VSC) [10]. The use of these power electronic converters allows for a better control and flexibility on the operation of the energy sources with respect to conventional rotational machines [5]. However, the output of these VSCs produces high-frequency pulse-width-modulation (PWM) harmonics that are injected into the grid and may damage sensible load and equipment [11]. For this reason, those harmonic components need to be reduced to achieve good power quality at the grid and comply with IEEE standards (IEEE 1547-2018) [12].

An output filter interface is usually placed between the power electronic converter and the point of connection to the microgrid in order to effectively eliminate these switching frequency harmonics [13]. The inductive-capacitive-inductive (LCL) filter has become the most popular choice in grid-connected applications due to a higher attenuation of the PWM switching harmonics, with an overall reduction on the weight and size of the filter when compared with the conventional L- and LC-filters [9]–[11], [13], [14]. However, the integration of this LCL filter increases the control complexity of the DERs because of the introduction of a resonance frequency that can cause instabilities in the microgrid [9], [14]. A detailed analysis and guidelines to avoid the instability caused by the LCL filters of the power converters are proposed in later chapters.

Although the concept of microgrid addresses many of the issues with the current electrical infrastructure, it also brings many challenges. One of the concerns is related to the physical inertia of a microgrid. Unlike bulk power systems, microgrids show an almost negligible physical inertia which could make the system more susceptible to oscillations due to network disturbances [5], [7]. Other challenges are related to the overall control and management

of the microgrid in terms of power sharing, stability, power quality, environmental influence and economic issues [15], [16].

Despite these challenges, microgrids have gained a lot of attention worldwide due to their promising benefits. In fact, many research facilities have begun building microgrid testbeds to demonstrate these benefits, to address some of the existing challenges in control and management of the DERs, and to identify other rising issues and challenges. Usually, these microgrid testbeds are rated in the kVA range and are comprised of different energy sources and storages, variable loads and protecting devices [17]–[19].

In addition, a growing interest is being presented on building and developing high-power microgrids in the MVA range [20]–[22]. These microgrids could have renewable sources with VSC with power ratings ranging from hundreds of kVA to some MVA. However, considering switching losses, heat management and fundamental voltage drops, the control and design of these VSCs as well as their LCL filter poses more restrictions and challenges than their lower-power counterpart [13]. For instance, their switching frequency is limited to a few kHz which usually places the resonance frequency of the LCL filter close to the switching/sampling frequency of the converters [10], [13]. This can place the operation and control of the VSC near an unstable region [14]. Another issue is that coupling between DERs in the grid-connected mode due to the grid impedance can worsen the resonance issues and stability of the system [23]. At lower power, this coupling might be ignored since the parameters of the LCL filter are larger than grid impedance. Nevertheless, this coupling plays a significant role in the stability of the system at higher power since the filter parameters might be on the same order of magnitude as the grid impedance [24].

Considering the growing interest on high-power microgrids and how different factors and restrictions can affect the stability of the system, there is a need for a stability analysis that determines how these different factors and conditions might affect the stable operation of a high-power microgrid. Ultimately, this stability analysis will allow the development of guidelines that can guarantee the stability of a microgrid and can reduce the engineering required to implement these high-power microgrids around the world.

In this thesis, a stability analysis will be performed on the high-power microgrid testbed at the National Center for Reliable Electric Power Transmission (NCREPT) at the University of Arkansas. This high-power testbed allows the parallel operation of three identical 2 MVA rated back-to-back VSC, called regen benches, with the ultimate objective of emulating a microgrid with different grid-connected DERs. A more in-depth description of this high-power microgrid testbed is presented in [25].

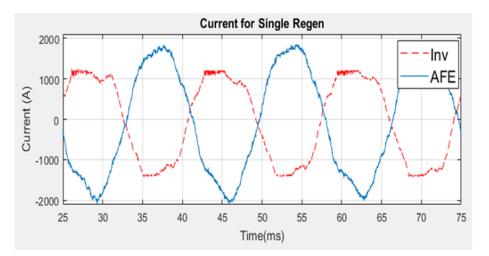

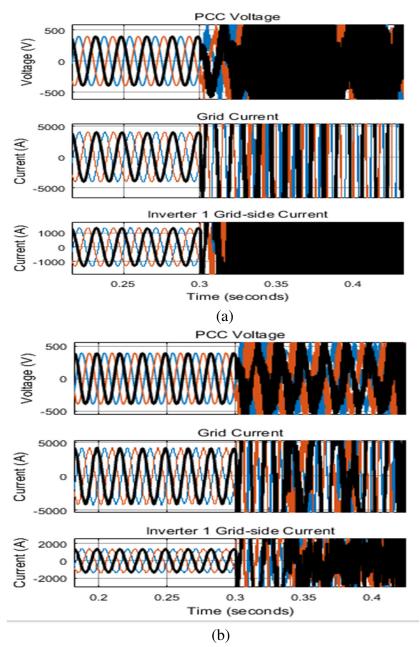

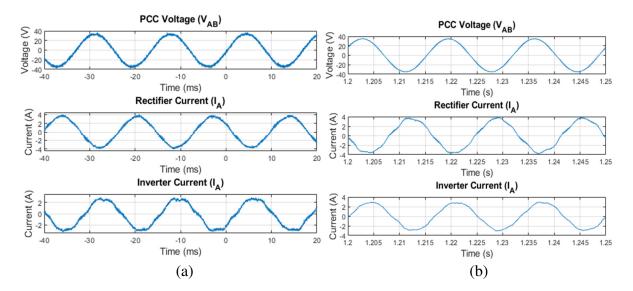

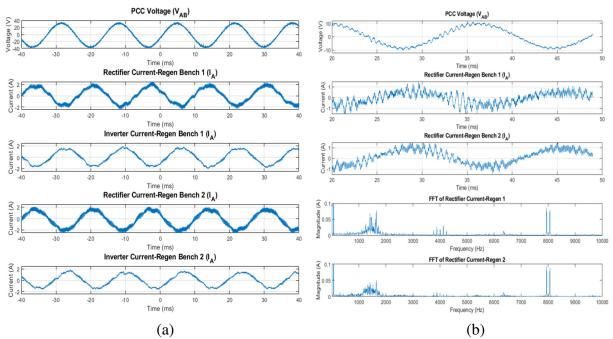

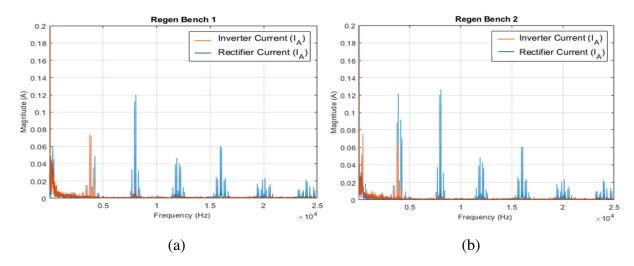

One of the main motivations of performing the stability analysis of the high-power microgrid at NCREPT is that the current control approach of the regen benches causes the system to operate in a near unstable region when multiple VSCs (regen benches) are connected in parallel to the grid. This near unstable operation affects the power quality of the system when the multiple regens inject/extract power into/from the grid. Fig. 1-2 illustrated the operation of a single and multiple regen benches. Fig. 1-2(a) shows that when only one of the regen benches is recirculating power, the current waveforms show acceptable results with mainly low-frequency harmonics. However, the current waveforms become more distorted with high-frequency harmonics when two regen benches are recirculating power at the same time, as illustrated in Fig. 1-2(b). The reason for this instability is that the controller of the regen benches was initially developed following the design guidelines for motor drives. However, the emerging research in

microgrids has shown that these conventional guidelines do not account for the coupling and interactions between VSCs in the microgrid, thus, causing the system to deviate from its expected behavior and causing potential stability issues [23], [26].

Fig. 1.2: Experimental current waveforms for NCREPT in the grid-connected mode for (a) a single regen bench, and (b) two parallel regen benches.

#### **1.2 Objectives of Thesis**

The main objective of this thesis is to perform a stability analysis of a high-power microgrid with multiple parallel- and grid-connected VSCs using the system parameters from the microgrid testbed at NCREPT in order to identify, minimize, if not eliminate, the potential instabilities that can affect the proper operation of the microgrid testbed. To accomplish this goal, the modeling of the high-power microgrid with multiple parallel VSCs whose dynamics are coupled due to the grid inductance is revised and analyzed. Then, the stability regions of the microgrid is determined by analyzing the closed-loop transfer function of the system. Next, changes in the VSCs controller are implemented to improve the range of these regions of stability. Finally, the theoretical analysis is validated through MATLAB/Simulink<sup>TM</sup> simulations.

Another important objective of this thesis is to develop a scaled-down prototype of the high-power microgrid at NCREPT; the so-called "mini-NCREPT". Using this scaled-down prototype will enable to reproduce issues already encountered in the high-power testbed and to develop countermeasures in an environment where a catastrophic failure will not result in expensive damaged components. Moreover, different advanced control algorithms for power sharing, compensation for deviations in voltage and frequency, and economic concerns in the optimal operation of the microgrid can be tested in the scaled-down prototype before deploying them at the high-power microgrid.

#### **1.3 Organization of Thesis**

This thesis is organized as follows: Chapter 2 will develop the mathematical modeling and stability analysis of identical multiple grid-connected VSCs having the same system parameters as the microgrid testbed at NCREPT. Chapter 3 will also develop a similar modeling and stability analysis but with high-power grid-connected VSCs that have different LCL filters

parameters. The design of the scaled-down prototype is documented in Chapter 4 and the implementation of the control algorithm in a microcontroller is presented in Chapter 5. The experimental results of the scaled-down prototype are given in Chapter 6. Finally, conclusions and recommendations for future work are given in Chapter 7.

#### **1.4 References**

- [1] A. Oudalov, T. Degner, F. van Overbeeke, and J. M. Yarza, "Microgrid: Architectures and Control Chapter 2," *Microgrids Architecture and Control*, pp. 1–24, 2003.

- [2] V. C. Gungor *et al.*, "Smart Grid Technologies: Communication Technologies and Standards," in *IEEE Transactions on Industrial Informatics*, vol. 7, no. 4, pp. 529-539, Nov. 2011.

- [3] H. Farhangi, "The path of the smart grid," in *IEEE Power and Energy Magazine*, vol. 8, no. 1, pp. 18-28, January-February 2010.

- [4] G. Andersson *et al.*, "Causes of the 2003 major grid blackouts in North America and Europe, and recommended means to improve system dynamic performance," in *IEEE Transactions on Power Systems*, vol. 20, no. 4, pp. 1922-1928, Nov. 2005.

- [5] N. Pogaku, M. Prodanovic and T. C. Green, "Modeling, Analysis and Testing of Autonomous Operation of an Inverter-Based Microgrid," in *IEEE Transactions on Power Electronics*, vol. 22, no. 2, pp. 613-625, March 2007.

- [6] N. Hatziargyriou, H. Asano, R. Iravani and C. Marnay, "Microgrids," in *IEEE Power and Energy Magazine*, vol. 5, no. 4, pp. 78-94, July-Aug. 2007.

- [7] D. E. Olivares *et al.*, "Trends in Microgrid Control," in *IEEE Transactions on Smart Grid*, vol. 5, no. 4, pp. 1905-1919, July 2014.

- [8] J. M. Guerrero, J. C. Vasquez, J. Matas, L. G. de Vicuna and M. Castilla, "Hierarchical Control of Droop-Controlled AC and DC Microgrids—A General Approach Toward Standardization," in *IEEE Transactions on Industrial Electronics*, vol. 58, no. 1, pp. 158-

- [9] Erika Twining and D. G. Holmes, "Grid current regulation of a three-phase voltage source inverter with an LCL input filter," in *IEEE Transactions on Power Electronics*, vol. 18, no. 3, pp. 888-895, May 2003.

- [10] E. Kantar and A. M. Hava, "LCL-filter design for low-voltage high-power grid-tied voltage-source converter considering various damping methods," 2016 IEEE 17th Workshop on Control and Modeling for Power Electronics (COMPEL), Trondheim, 2016, pp. 1-8.

- [11] D. Yoon, H. Jeong and K. Lee, "The design of an LCL-filter for the three-parallel operation of a power converter in a wind turbine," 2010 IEEE Energy Conversion Congress and Exposition, Atlanta, GA, 2010, pp. 1537-1544.

- [12] IEEE Standard for Interconnection and Interoperability of Distributed Energy Resources with Associated Electric Power Systems Interfaces," in *IEEE Std 1547-2018 (Revision of IEEE Std 1547-2003)*, vol., no., pp.1-138, 6 April 2018

- [13] Z. Qiu and G. Chen, "Study and Design of Grid Connected Inverter for 2 MW Wind Turbine," 2007 IEEE Industry Applications Annual Meeting, New Orleans, LA, 2007, pp. 165-170.

- [14] S. G. Parker, B. P. McGrath and D. G. Holmes, "Regions of Active Damping Control for LCL Filters," in *IEEE Transactions on Industry Applications*, vol. 50, no. 1, pp. 424-432, Jan.-Feb. 2014.

- [15] L. Meng, M. Savaghebi, F. Andrade, J. C. Vasquez, J. M. Guerrero and M. Graells, "Microgrid central controller development and hierarchical control implementation in the intelligent microgrid lab of Aalborg University," 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, 2015, pp. 2585-2592.

- [16] F. Farzan, S. Lahiri, M. Kleinberg, K. Gharieh, F. Farzan and M. Jafari, "Microgrids for Fun and Profit: The Economics of Installation Investments and Operations," in *IEEE Power and Energy Magazine*, vol. 11, no. 4, pp. 52-58, July-Aug. 2013.

- [17] R. H. Lasseter *et al.*, "CERTS Microgrid Laboratory Test Bed," in *IEEE Transactions on Power Delivery*, vol. 26, no. 1, pp. 325-332, Jan. 2011.

- [18] M. Liu, Z. Ding, F. L. Quilumba, W. Lee and D. A. Wetz, "Using a Microgrid test bed to evaluate the strategies for seamless renewable energy integration," 2014 IEEE/IAS 50th Industrial & Commercial Power Systems Technical Conference, Fort Worth, TX, 2014, pp. 1-9.

- [19] J. Eto et al., "Overview of the CERTS Microgrid laboratory Test Bed," 2009 CIGRE/IEEE PES Joint Symposium Integration of Wide-Scale Renewable Resources Into the Power Delivery System, Calgary, AB, 2009, pp. 1-1.

- [20] H. Xie, S. Zheng and M. Ni, "Microgrid Development in China: A method for renewable energy and energy storage capacity configuration in a megawatt-level isolated microgrid.," in *IEEE Electrification Magazine*, vol. 5, no. 2, pp. 28-35, June 2017.

- [21] C. Marnay, N. DeForest and J. Lai, "A green prison: The Santa Rita Jail campus microgrid," 2012 IEEE Power and Energy Society General Meeting, San Diego, CA, 2012, pp. 1-2.

- [22] M. C. Such and G. Y. Masada, "BESS control on an microgrid with significant wind generation," 2017 IEEE Power & Energy Society General Meeting, Chicago, IL, 2017, pp. 1-5.

- [23] M. Lu, X. Wang, P. C. Loh and F. Blaabjerg, "Resonance Interaction of Multiparallel Grid-Connected Inverters With LCL Filter," in *IEEE Transactions on Power Electronics*, vol. 32, no. 2, pp. 894-899, Feb. 2017.

- [24] Y. Liu, C. Farnell, H. A. Mantooth, J. C. Balda, R. A. McCann and C. Deng, "Resonance propagation modeling and analysis of AC filters in a large-scale microgrid," 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, 2016, pp. 143-149.

- [25] Y. Liu, C. Farnell, J. C. Balda and H. A. Mantooth, "A 13.8-kV 4.75-MVA microgrid laboratory test bed," *2015 IEEE Applied Power Electronics Conference and Exposition* (*APEC*), Charlotte, NC, 2015, pp. 697-702.

- [26] J. L. Agorreta, M. Borrega, J. López and L. Marroyo, "Modeling and Control of N-Paralleled Grid-Connected Inverters With LCL Filter Coupled Due to Grid Impedance in PV Plants," in *IEEE Transactions on Power Electronics*, vol. 26, no. 3, pp. 770-785, March 2011.

#### **CHAPTER 2**

## STABILITY ANALYSIS OF MULTIPLE GRID-CONNECTED INVERTERS USING DIFFERENT FEEDBACK CURRENTS

D. Carballo, E. Escala and J. C. Balda, "Stability Analysis of Multiple Grid-Connected Inverters Using Different Feedback Currents," 2018 9th IEEE International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Charlotte, NC, 2018, pp. 1-7.

#### Abstract

Distributed generation is gaining greater penetration levels in distribution grids due to government incentives for integrating distributed energy resources (DERs) and DER cost reductions. The frequency response of a grid-connected single inverter changes as other inverters are connected in parallel due to the couplings among grid inductance and/or inverter output filters. The selection of the inverter- or grid-side currents as feedback control signals is then not trivial because each one has tradeoffs. This paper analyses the system stability for multiple parallel- and grid-connected inverters using the inverter- or grid-side currents as feedback signals. Modeling of both feedback signals is performed using the current separation technique. Moreover, the stability range for different conditions including active damping is analyzed through the root locus technique. The grid-side current has a wider range of stability, but the inverter-side current allows for higher values of the proportional gain near the critical frequency and no extra sensors are needed since measurement of the inverter current is needed for protection in high-power applications.

#### **2.1 Introduction**

Microgrids have several advantages like effective integration of distributed energy resources (DERs) into distribution networks to allow for bidirectional power flows, and reduced transmission and distribution losses. Interfaces between DERs and microgrids are often based on power converters (inverters) with LCL filters that provide a higher damping capability (-60 dB/dec) in comparison with a simple L filter (-20 dB/dec) [1]. However, LCL filters introduce resonance issues that can cause current-controller instability and that can become more severe as more power electronics devices are connected to the grid [2]. The scenario becomes more challenging when DER converters of higher power ratings are used while the voltage levels remain in the low-voltage range (208 V ~ 480 V). This results in a much smaller base impedance value on a per-unit (p.u.) basis, making the filter inductor values on the same order as the grid impedances [1]. Therefore, a stability issue caused by coupling between inverter and grid impedances [1]. Therefore, a stability analysis of the potential interactions between several parallel LCL filters and their effects on current controllers is crucial for satisfactory system performance.

Either the grid- or inverter-side currents can be selected for feedback in a DER current controller. While grid-side currents are usually selected because of direct control of the grid-injected currents, using the inverter-side currents may present some advantages like faster fault current interruption and an inherent damping term in the transfer function [3-4]. The authors of [5] performed a comparison that demonstrated tradeoffs when using these two current-control approaches for only a single inverter. Although the authors of [6-7] presented an analysis on the range of the proportional gain of the current controller for multiple grid-connected inverters, they only considered the grid-side currents for feedback purposes. The work presented here expands

upon the stability analysis in [4-8] to evaluate the stability regions for multiple grid-connected inverters when using the inverter-side currents for feedback with the main goal of determining tradeoffs between these two current-feedback approaches.

This paper is organized as follows: Section 2.2 presents an overview of the modeling of the inverter- and grid-side currents, Section 2.3 evaluates the system stability with and without the use of active damping, Section 2.4 analyzes simulation results, and Section 2.5 provides the main conclusions.

#### **2.2 Modeling of the Parallel Inverters**

#### 2.2.1 Inverter-Side Current- Mathematical Modeling

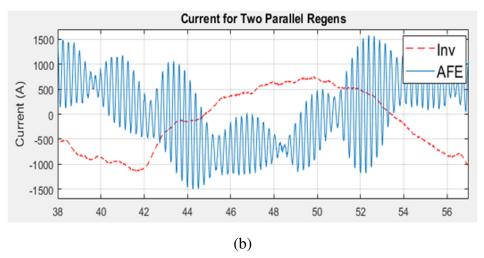

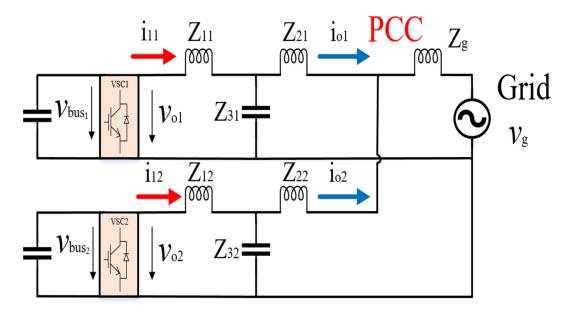

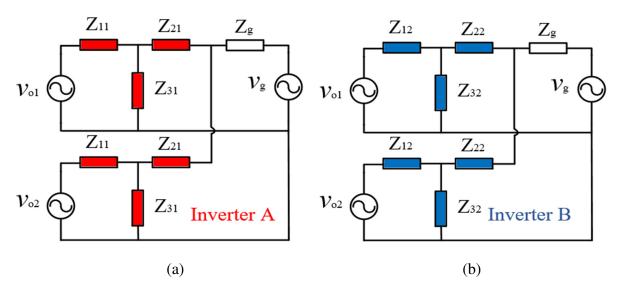

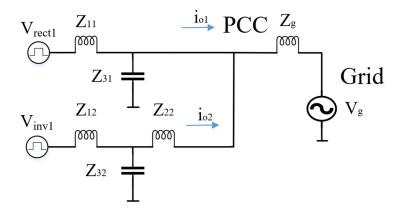

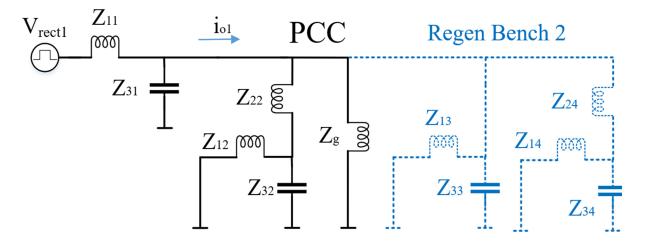

Multiple paralleled grid-connected inverters are illustrated in Fig. 2.1, where  $Z_1$  and  $Z_2$  are the s-domain impedances of the inverter- and grid-side filter inductances,  $Z_3$  is the filter capacitive impedance,  $Z_g$  is the grid impedance, and the second subscript refers to the inverter number. Using the principle of superposition to remove the influence of the grid and the other inverter voltages, and assuming that the inverters are equal (i.e., same LCL filter parameters), the inverter-side currents  $i_{1j}$  (j=1, 2,...n) with respect to the inverter voltages can be written as:

$$\begin{pmatrix} i_{11} \\ i_{12} \\ \dots \\ i_{1n} \end{pmatrix} = \begin{pmatrix} G_{11} & G_{12} & \dots & G_{12} \\ G_{12} & G_{11} & \dots & G_{12} \\ \dots & \dots & \dots & \dots \\ G_{12} & G_{12} & \dots & G_{11} \end{pmatrix} \cdot \begin{pmatrix} v_{01} \\ v_{02} \\ \dots \\ v_{0n} \end{pmatrix}.$$

(1)

where G11 and G12 are calculated as follows [6]:

$$G_{11} = \frac{n-1}{n}G_{inv} + \frac{1}{n}G_{coupling_{inv}},$$

(2)

$$G_{12} = -\frac{1}{n}G_{inv} + \frac{1}{n}G_{coupling_{inv}} \quad , \tag{3}$$

Fig. 2.1: Schematic of multiple paralleled grid-connected inverters.

with  $G_{inv}$  the transfer function of the LCL filter and  $G_{coupling_{inv}}$  the transfer function including the effects of the grid impedance. Both are presented below:

$$G_{inv} = \frac{(Z_3 + Z_2)}{Z_1 Z_2 + Z_1 Z_3 + Z_2 Z_3} = \frac{s^2 + \omega_0^2}{L_1 s(s^2 + \omega_{res}^2)}$$

(4)

$$G_{coupling_{inv}} = \frac{(Z_3 + Z_2 + nZ_g)}{Z_1 Z_2 + Z_1 Z_3 + Z_2 Z_3 + nZ_g (Z_3 + Z_1)} = \frac{s^2 + \omega_{01}^2}{L_1 s (s^2 + \omega_{res1}^2)}$$

(5)

where  $\omega_{res}$  and  $\omega_o$  are the LCL filter resonance and antiresonance frequencies, and  $\omega_{res1}$  and  $\omega_{o1}$  are the resonance and antiresonance frequencies taking into account the coupling with the grid inductance with *n* paralleled inverters (all in rad/s):

$$\omega_{res} = 2\pi f_{res} = \sqrt{(L_1 + L_2)/(L_1 L_2 C_f)},$$

$$\omega_o = 2\pi f_o = \sqrt{1/(L_2 C_f)},$$

$$\omega_{res1} = 2\pi f_{res1} = \sqrt{(L_1 + L_2 + nL_g)/(L_1 (L_2 + nL_g) C_f)},$$

$$\omega_{o1} = 2\pi f_{o1} = \sqrt{1/((L_2 + nL_g) C_f)}.$$

(6)

From (1), the first-inverter-side currents are given by

$$i_{11} = \frac{1}{n}G_{inv}(v_{01} - v_{02}) + \dots + \frac{1}{n}G_{inv}(v_{01} - v_{0n}) + \frac{1}{n}G_{coupling_{inv}}(v_{01} + \dots + v_{0n}).$$

(7)

From (7) the inverter-side currents  $i_{11}$  have two components: the interactive one which circulates between two inverters and the common one that is injected into the grid, as illustrated in Fig. 2.1 [6-7].

#### 2.2.2 Grid-Side Current- Mathematical Modeling

Following the same process as in the previous section and presented in [6], the grid-side currents  $i_{2j}$  (j = 1, 2, ...n) with respect to the inverter voltages can be written like (1)-(3) but with different transfer functions for the LCL filter and the coupling term:

$$G_{11} = \frac{n-1}{n} G_{grid} + \frac{1}{n} G_{coupling_{grid}}$$

(8)

$$G_{12} = -\frac{1}{n}G_{grid} + \frac{1}{n}G_{coupling_{grid}}$$

(9)

$$G_{grid} = \frac{Z_3}{Z_1 Z_2 + Z_1 Z_3 + Z_2 Z_3} = \frac{1}{L_1 L_2 C_f s(s^2 + \omega_{res}^2)}$$

(10)

$$G_{coupling_{grid}} = \frac{Z_3}{Z_1 Z_2 + Z_1 Z_3 + Z_2 Z_3 + n Z_g (Z_3 + Z_1)} = \frac{1}{s L_1 C_f (L_2 + n L_g) (s^2 + \omega_{res1}^2)}$$

(11)

Like (7), the first-grid-side currents can be expressed as:

$$i_{21} = \frac{1}{n}G_{grid}(v_{01} - v_{02}) + \dots + \frac{1}{n}G_{grid}(v_{01} - v_{0n}) + \frac{1}{n}G_{coupling_{grid}}(v_{01} + \dots + v_{0n})$$

(12)

comprising interactive and common currents shown in Fig. 2.1.

#### 2.3 Stability Analysis and Active Damping

#### 2.3.1 Control Strategy

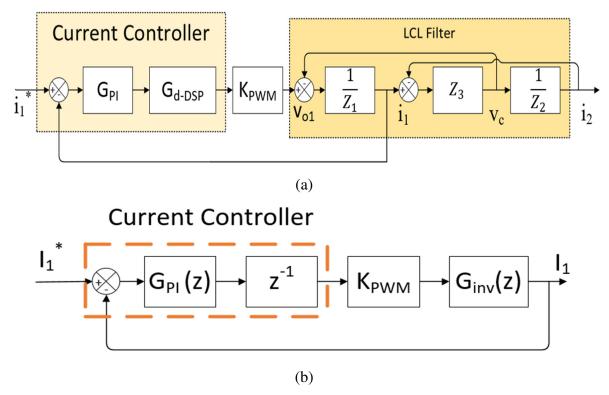

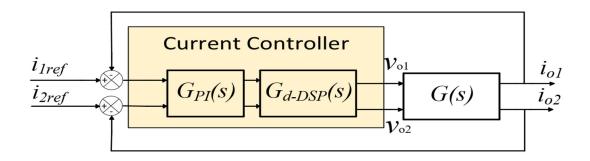

The block diagram of a single current-control loop for the inverter-side current feedback in the s-domain is presented in Fig. 2.2 (a). In the figure,  $i_1^*$  represents the reference current commanded to the controller,  $G_{d-DSP}$  the DSP computational delay,  $K_{pwm}$  the linear response of the inverter with gain of  $K_{pwm} = V_{dc}/\sqrt{3}$  for a space vector modulation implementation, and  $G_{PI}$ the PI controller chosen in this paper:

$$G_{PI}(s) = K_P + \frac{K_i}{s} \tag{13}$$

The current controller in Fig. 2.2(a) as modeled in the z-domain is in Fig. 2.2(b) since the DSP is a discrete system. In the figure, the PI controller in (13) is discretized by applying a Tustin transform with prewarping while a zero-order-hold (ZOH) transform is applied to the transfer function of the LCL filter [2]. Moreover, a sample delay  $z^{-1}$  accounts for the delay of the DSP. Although both figures are shown using the inverter-side current as reference, the same control diagram can be implemented for the grid-side current just by changing the respective current feedback and reference.

Considering the current controller from Fig. 2.2(b) and the result from (7), the closed-loop transfer function for the interactive and common currents are respectively given by:

$$C_{ij} = \frac{1}{n} \frac{G_{inv}(z)H}{(1+G_{inv}(z)H)} (i_{1i}^* - i_{1j}^*)$$

(14)

$$S_{i} = \frac{1}{n} \frac{G_{coupling_{inv}}(z)H}{(1 + G_{coupling_{inv}}(z)H)} (i_{1i}^{*} - i_{1j}^{*})$$

(15)

Fig. 2.2: Current control model (a) s-domain (b) z-domain.

where

$$H = G_{PI}(z)z^{-1}K_{nwm}.$$

(16)

#### 2.3.2 Stability Analysis for the Inverter-Side Current Case

The system stability is determined by applying the root locus analysis to the open-loop forward path of (14) and (15). A system with multiple grid-connected inverters is only stable when the proportional gains of the current controllers are selected such that all values of the transfer functions for the interactive and common currents are inside the unit circle [6-7].

Furthermore, [2] showed that there is relation between a critical frequency of one sixth of the sampling frequency  $f_s$  and the LCL filter resonance  $f_{res}$  (or  $f_{res1}$ ) that will determine whether the system can be stable for a single-loop feedback control. For the inverter-side current control,

the system will only be stable if the resonance frequency is less than the critical frequency (i.e.,  $f_{res} < f_s/6$  and  $f_{res1} < f_s/6$ ).

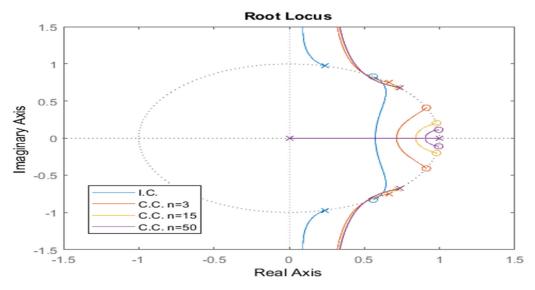

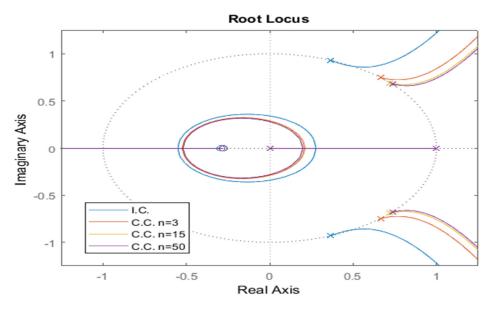

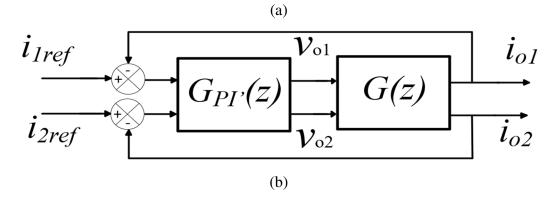

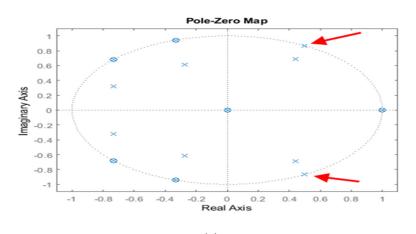

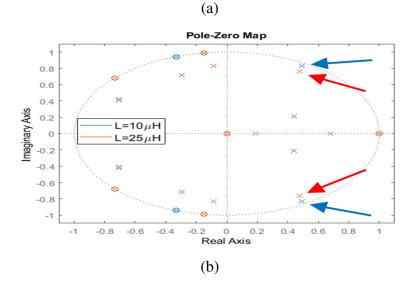

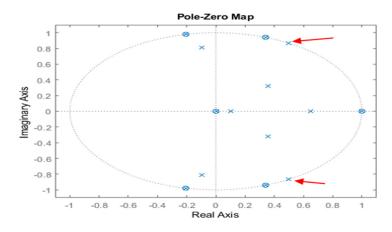

Fig. 2.3 shows the root loci of the interactive and common currents for the inverter-side feedback for different number of inverters using the parameters from the high-power microgrid testbed described in [9] and presented in Table 2.1 for convenience. The resonance frequency  $\omega_{res}$  for the interactive current stability is calculated from (6) and the parameters in Table 2.1. The LCL filter resonance frequency (1.52 kHz) is higher than the critical frequency (1.33 kHz), so the system is interactively unstable for the inverter-side current control. Fig. 2.3 corroborates this since the poles of the LCL filter are placed outside the unit circle for all values of the proportional gain for the interactive current.

However, there is a range where the system is stable for the common current due to a shift in the frequency of the poles and zeroes of the filter resonance and antiresonance frequencies. This stability range for selected number of inverters is given by:

$$K_{p}Range = \begin{cases} 0 < K_{p} < 0.0709, n = 3\\ 0 < K_{p} < 0.0822, n = 15\\ 0 < K_{p} < 0.0844, n = 50 \end{cases}.$$

(17)

From (17), the stable range of the proportional gain increases as the number of inverters increases but converging towards a maximum value. Nonetheless, the entire system will always be unstable since the system is interactively unstable requiring additional damping when using the inverter-side currents.

Fig. 2.3: Root loci of the inverter-side current for interactive (I.C) and common currents (C.C).

| Circuit Parameter      | Formula        | Nominal Value |

|------------------------|----------------|---------------|

| Power Rating           | S <sub>b</sub> | 2.0 MVA       |

| Voltage Rating         | $V_b$          | 480 V         |

| Inverter-Side Inductor | $L_1$          | 20 µH         |

| Grid-Side Inductor     | L <sub>2</sub> | 12.2 µH       |

| Filter Capacitor       | $C_f$          | Δ3x 480 μH    |

| Resonance Frequency    | $f_r$          | 1.52 kHz      |

| Sampling Frequency     | $f_s$          | 8 kHz         |

| Critical Frequency     | $f_s/6$        | 1.33 kHz      |

TABLE 2.1: SYSTEM PARAMETERS

Similarly, the LCL resonance frequency  $\omega_{res1}$  for the common current stability can be calculated from (6). This equation shows that as the number of inverters increase, the resonance frequency decreases. For this reason, increasing the number of inverters could reduce the resonance frequency to a value lower than the critical frequency, making the system commonly stable for the inverter-side current.

#### **Active Damping Control**

A system using inverter-side current feedback with the critical frequency near the resonance frequency would require that the controller provides damping to move the poles of the resonance inside the unit circle. Proposed solutions for adding damping can be broadly classified in passive and active algorithms. The ESRs of the various components are normally small so they might not be able to make the system stable in high-power applications. Adding a passive resistor to damp the resonances introduces high power losses. Thus, the best solution is to use active damping algorithms which will reduce the resonances without introducing power losses [2, 10].

In this paper, the capacitor-voltage feedforward active damping algorithm is implemented [10-12]. The main reason for selecting this scheme is that no additional sensors are needed since the capacitor voltage is usually measured to synchronize the inverters with the grid through the phase-locked loop (PLL) algorithm. Moreover, reduction of large inrush currents during startup and suppression of the grid disturbances can be achieved using this active damping algorithm [11].

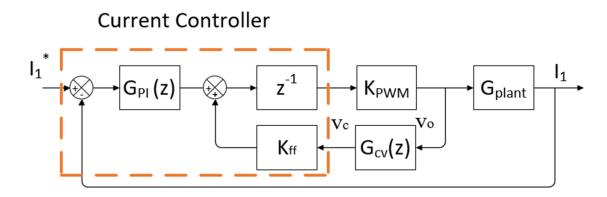

The block diagram of the dual-loop control system for the inverter-side current feedback with capacitor-voltage active damping is illustrated in Fig. 2.4. In this figure,  $K_{ff}$  is the gain of the feedforward control path, and  $G_{cv}(z)$  is the transfer function of the capacitor voltage with respect to the inverter voltage, given by:

$$G_{cv}(s) = \frac{v_c(s)}{v_o(s)} = \frac{1}{L_1 C_f(s^2 + \omega_{res}^2)},$$

$$G_{cv}(z) = ZOH(G_{cv}(s)).$$

(18)

Fig. 2.4: Current control model in z-domain with capacitor-voltage feedforward active damping.

Considering the current controller with this active damping algorithm and the result from (7), the new closed-loop transfer functions for the interactive and common currents are the same ones as (14) and (15) but with a new transfer function for (16), given by:

$$H = \frac{G_{PI}(Z)z^{-1}K_{PWM}}{1 - z^{-1}K_{PWM}K_{ff}G_{cv}(z)} .$$

<sup>(19)</sup>

Using this equation, Fig. 2.5 shows the root loci of the interactive and common currents for the inverter-side current feedback using unit capacitor-voltage feedforward gain (i.e.,  $K_{ff} = 1$ ).

Fig. 2.5: Root loci of the interactive and common currents for inverter-side feedback with capacitor-voltage feedforward algorithm.

Unlike the previous case, the poles of the system are now inside the unit circle for the interactive current. Thus, the system is interactively stable as long as the proportional gain is properly selected from 0 to 0.111. Similarly, the system will continue to have common current stability with a higher range of stability from  $K_p$  varying from 0 to 0.131. Applying this feedforward technique extends the limit of the resonance frequency up to one third of the sampling frequency (i.e.,  $f_r < f_s/3$ ) provided that:

$$\cos(\omega_{res1}T_s) > -\frac{L_1}{2L_1 + 3(L_2 + nL_g)} [11].$$

(20)

#### 2.3.3 Stability Analysis for the Grid-Side Current Case

A system with grid-side feedback will only be stable if the resonance frequencies of both the interactive and common currents are greater than the critical frequency (i.e.,  $f_{res} > f_s/6$ and  $f_{res1} > f_s/6$ ) [2]. Following the same analysis as the case for the inverter-side feedback, it is expected that the system be interactively stable for the grid-side current since the resonance frequency is greater than the critical frequency. Moreover, it is expected that the system be commonly unstable because increasing the number of inverters decreases the resonance frequency  $f_{res1}$  to values lower than the critical frequency. In this case, the system will be unstable when only two inverters are added since the resonance frequency of the LCL filter is initially close to the critical frequency.

Fig. 2.6 shows the root loci analysis when using the grid-side current as feedback. In this case, the values that can be selected for the proportional gain to make the system interactively stable are within:

$$K_p Range = \{0 < K_p < 0.0653\}.$$

(21)

Fig. 2.6: Root loci of the grid-side current for interactive and common currents.

However, the system will be commonly unstable since the poles of the common current are located outside the unit circle regardless of the value of the proportional gain or the number of inverters. Therefore, the entire system is always unstable requiring additional damping. This shows that an inverter employing grid-side-current feedback is in risk of becoming unstable due to the movement of the resonance poles as more inverters are added to grid. Further examination of  $\omega_{res1}$  shows that the resonance frequency will converge to a defined value. As the number of inverters increases,  $nL_g >> L_2$  and  $nL_g >> (L_1 + L_2)$ . Thus,  $\omega_{res1}$  will converge to:

$$\omega_{\min res1} = 2\pi f_{\min res1} = \sqrt{\frac{1}{L_1 C_f}}.$$

(22)

This means that if the minimum resonance frequency in (22) is greater than the critical frequency (i.e.,  $f_{min_{res1}} > f_s/6$ ), the system with grid-side current feedback will no longer be at risk of becoming commonly unstable regardless of the number of inverters in the grid.

Fig. 2.7: Root loci of the interactive and common currents for grid-side feedback with capacitor-voltage feedforward algorithm.

## **Active Damping Control**

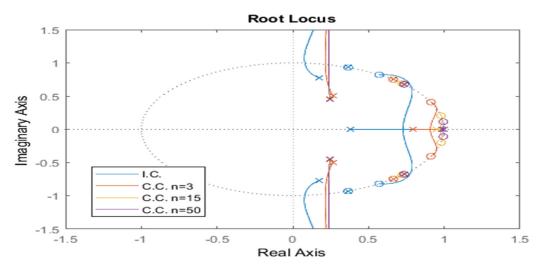

Active damping will be applied to bring the poles of the system inside the unit circle since the system is unstable. Fig. 2.7 shows the root loci of the interactive and common currents for the grid-side-current feedback using the capacitor-voltage feedforward active damping shown in Fig. 2.4.

In this case, the system will continue to have interactive current stability with a higher range of stability from  $K_p$  varying from 0 to 0.101. Similarly, the poles for the common current are now inside the unit circle with a range of stability of:

$$K_{p}Range = \begin{cases} 0 < K_{p} < 0.087, n = 3\\ 0 < K_{p} < 0.0832, n = 15\\ 0 < K_{p} < 0.081, n = 50 \end{cases}.$$

(23)

Applying this feedforward technique changes the system stability range. As was the case with stability of the inverter-side current, the system will now be stable only if the resonance frequency is less than up to one third of the sampling frequency (i.e.,  $f_r < f_s/3$ ) and will become unstable if this limit is exceeded [12]. This means that unlike before, the system is no longer in risk of becoming unstable as more inverters are added to the grid since the maximum resonance frequency (1.52 kHz) is less than one third of the sampling frequency (2.67 kHz).

#### 2.3.4 Filter Design Considerations on the System Stability

The previous sections have shown that the stability of the system will highly depend on the LCL filter resonance frequency. A LCL filter is usually designed to attenuate the overall ripple current amplitude, and the resonance frequency is selected to be less than half of the switching frequency  $f_{sw}$  and ten times greater than the fundamental frequency  $f_g$  (i.e.,  $10f_g < f_{res}(or f_{res1}) < 0.5f_{sw}$ ) [13]. This relation prevents the filter from amplifying switching noises and low order harmonics.

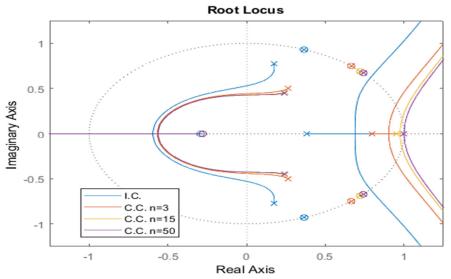

Fig. 2.8 illustrates the different ranges of stability of the system for the inverter- and gridside current feedback considering the constrain imposed on the resonance frequency by the design guidelines of the LCL filter. Fig. 2.8(a) and Fig. 2.8(b) show the stability regions when the sampling frequency is equal to the switching frequency (i.e.,  $f_s = f_{sw}$ ) for a system with and without the capacitor-feedforward algorithm. In this case, the grid-side current feedback will have a wider range of stability since it can be stable over the critical frequency with a single-loop controller and under twice the critical frequency with the implementation of the capacitorvoltage feedforward active damping.

Similarly, Fig. 2.8 (c) and Fig. 2.8 (d) show the stability regions when the sampling frequency is twice the switching frequency (i.e.,  $f_s = 2f_{sw}$ ) for a system with and without the capacitor-feedforward algorithm. In the system with the single-loop controller from Fig. 2.8 (c),

26

Fig. 2.8: Stability range for inverter- and grid-side current feedback for different cases: (a) fs =fsw without active damping (b) fs =fsw with active damping (c) fs =2fsw without active damping (d) fs =2fsw with active damping.

the regions of stability are evenly distributed between the two feedback currents and the selection of the best feedback method will depend on the value of the filter resonance frequency. However, the system will always be stable when the capacitor-feedforward algorithm is implemented in Fig 2.8 (d) for both the inverter- and grid-side current feedback provided that the LCL filter had been properly designed. Despite both feedback currents being stable in this situation, selecting the inverter-side current feedback is overall a better choice than the grid-side current. The main advantage being that no extra sensors are needed since the inverter-side current needs to be measured for switching device protection in high-power applications [1]. In addition, the previous analysis illustrated that the inverter-side current allows for higher values of the proportional gain near the critical frequency for both the interactive and common currents, which translates to a higher bandwidth and faster dynamics for the current controller. By iteratively changing the resonance frequency and examining the root loci, it was found that the inverter-side current feedback have a higher value for the proportional gain when the resonance frequency is lower than about one fifth of the sampling frequency (i.e.,  $10f_g < f_{res} < f_s/5$ ). This means that as the sampling frequency increases, this range increases, as well. Conversely, the grid-side current feedback will always have a fixed range of  $f_s/5 < f_{res} < f_s/4$ . Thus, the inverter-side current will have a wider range where the value of proportional gain can be selected higher than the value of gain for the grid-side current.

## **2.4 Simulation Results**

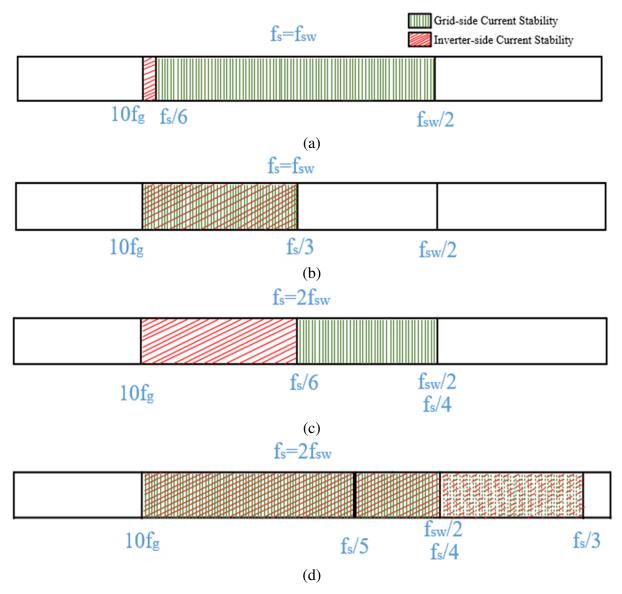

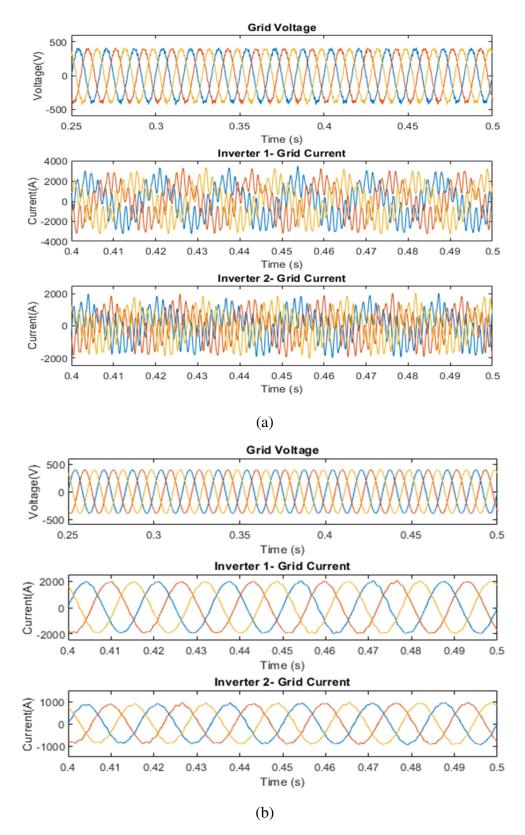

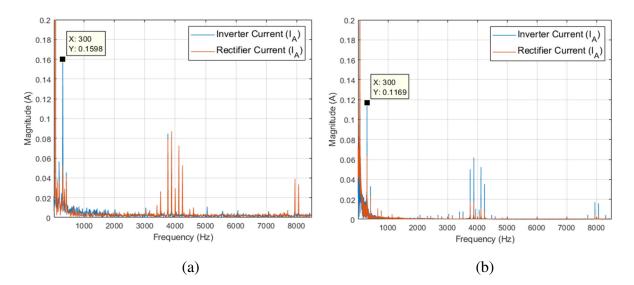

In order to validate the effects of the active damping algorithm based on feedforwardunity capacitor voltage with both the inverter- and grid-side currents as feedback, MATLAB/SIMULINK<sup>TM</sup> is used to model a system consisting of three 2-MVA grid-connected parallel inverters feeding the power grid. All three inverters are set to inject 800 kW to the grid. The capacitor voltage feedforward technique is initially used in both cases and is turned off for all inverters at t = 0.3 s.

Fig. 2.9(a) shows that using the inverter-side current as feedback, the system becomes unstable as the capacitor voltage feedforward term is turned off because the interactive current is

unstable. Similarly, Fig. 2.9(b) reveals that using the grid-side current as feedback, the system becomes unstable as the capacitor voltage feedforward term is turned off because the common current is unstable. As mentioned before, the LCL filter resonance frequency utilized in these cases is very close to the critical frequency and therefore, both cases are unstable without active damping.

Fig. 2.9: Current waveforms for (a) inverter-side current feedback (b) grid-side current feedback.

#### 2.5 Conclusions

This paper performed a stability analysis considering the proportional gain of the current controller for multiple parallel- and grid-connected inverters using the inverter- and grid-side currents as feedback signals. Modeling of the inverter- and grid-side current feedback using the current separation method was performed. Moreover, the system stability range for both feedback-current approaches with and without active damping based on capacitor-voltage feedforward was examined using the root locus analysis, and those ranges of stability were examined considering the limitations given by the LCL filter design procedure. Overall, the analysis revealed that grid-side current feedback is a better choice when the the sampling frequency is the same as the switching frequency because of its wider range of stability. However, the inverter-side current is better when the sampling frequency is twice the switching frequency due to mainly no needing additional sensors. Finally, the theoretical analysis was validated through simulations.

## **2.6 Acknowledgments**

The authors are grateful to the financial support from the NSF I/UCRC Grid-Connected Advanced Power Electronic Systems (GRAPES) under grant IIP-1439700.

## **2.7 References**

- Y. Liu, C. Farnell, V. Jones, K. George, H. A. Mantooth and J. C. Balda, "Resonance propagation of ac filters in a large-scale microgrid," 2015 IEEE 6th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Aachen, 2015, pp. 1-6. doi: 10.1109/PEDG.2015.7223078

- [2] S. G. Parker, B. P. McGrath and D. G. Holmes, "Regions of Active Damping Control for LCL Filters," in IEEE Transactions on Industry Applications, vol. 50, no. 1, pp. 424-432, Jan.-Feb. 2014. doi: 10.1109/TIA.2013.2266892

- [3] Y. Tang, P. C. Loh, P. Wang, F. H. Choo, F. Gao, "Exploring Inherent Damping Characteristic of LCL-Filters for Three-Phase Grid-Connected Voltage Source Inverters," IEEE Trans. Power Electron., vol. 27, no. 3, pp. 1433-1443, Mar. 2012.

- [4] Y. Liu, C. Farnell, H. A. Mantooth, J. C. Balda, R. A. McCann and C. Deng, "Resonance propagation modeling and analysis of AC filters in a large-scale microgrid," 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, 2016, pp. 143-149. doi: 10.1109/APEC.2016.7467865

- [5] J. Dannehl, C. Wessels and F. W. Fuchs, "Limitations of Voltage-Oriented PI Current Control of Grid-Connected PWM Rectifiers With LCL Filters," in IEEE Transactions on Industrial Electronics, vol. 56, no. 2, pp. 380-388, Feb. 2009. doi: 10.1109/TIE.2008.2008774

- [6] M. Lu, X. Wang, P. C. Loh and F. Blaabjerg, "Resonance Interaction of Multiparallel Grid-Connected Inverters With LCL Filter," in IEEE Transactions on Power Electronics, vol. 32, no. 2, pp. 894-899, Feb. 2017. doi: 10.1109/TPEL.2016.2585547

- [7] M. Lu, X. Wang, P. C. Loh and F. Blaabjerg, "Interaction and aggregated modeling of multiple paralleled inverters with LCL filter," 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, 2015, pp. 1954-1959. doi: 10.1109/ECCE.2015.7309936

- [8] J. L. Agorreta, M. Borrega, J. López and L. Marroyo, "Modeling and Control of N -Paralleled Grid-Connected Inverters With LCL Filter Coupled Due to Grid Impedance in PV Plants," in IEEE Transactions on Power Electronics, vol. 26, no. 3, pp. 770-785, March 2011. doi: 10.1109/TPEL.2010.2095429

- [9] Y. Liu, C. Farnell, J. C. Balda and H. A. Mantooth, "A 13.8-kV 4.75-MVA microgrid laboratory test bed," 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, 2015, pp. 697-702. doi: 10.1109/APEC.2015.7104426

- [10] M. Lu, Z. Xin, X. Wang, R. N. Beres and F. Blaabjerg, "Extended stable boundary of LCL-filtered grid-connected inverter based on an improved grid-voltage feedforward control," 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, 2016, pp. 1-7. doi: 10.1109/ECCE.2016.7855103

- [11] X. Li, J. Fang, Y. Tang, X. Wu and Y. Geng, "Capacitor-Voltage Feedforward With Full Delay Compensation to Improve Weak Grids Adaptability of LCL-Filtered Grid-Connected Converters for Distributed Generation Systems," in IEEE Transactions on Power Electronics, vol. 33, no. 1, pp. 749-764, Jan. 2018. doi: 10.1109/TPEL.2017.2665483

- [12] M. Lu and F. Blaabjerg, "Stability identification for grid-connected inverters with LCL filters considering grid-voltage feedforward regulator," 2017 IEEE 18th Workshop on Control and Modeling for Power Electronics (COMPEL), Stanford, CA, 2017, pp. 1-5. doi: 10.1109/COMPEL.2017.8013342

[13] A. Reznik, M. G. Simões, A. Al-Durra and S. M. Muyeen, "LCL Filter Design and Performance Analysis for Grid-Interconnected Systems," in IEEE Transactions on Industry Applications, vol. 50, no. 2, pp. 1225-1232, March-April 2014. doi: 10.1109/TIA.2013.2274612

#### 2.8 Permissions

#### Thesis / Dissertation Reuse

The IEEE does not require individuals working on a thesis to obtain a formal reuse license, however, you may print out this statement to be used as a permission grant:

Requirements to be followed when using any portion (e.g., figure, graph, table, or textual material) of an IEEE copyrighted paper in a thesis:

1) In the case of textual material (e.g., using short quotes or referring to the work within these papers) users must give full credit to the original source (author, paper, publication) followed by the IEEE copyright line © 2011 IEEE.

2) In the case of illustrations or tabular material, we require that the copyright line © [Year of original publication] IEEE appear prominently with each reprinted figure and/or table.

3) If a substantial portion of the original paper is to be used, and if you are not the senior author, also obtain the senior author's approval.

Requirements to be followed when using an entire IEEE copyrighted paper in a thesis:

1) The following IEEE copyright/ credit notice should be placed prominently in the references: © [year of original publication] IEEE. Reprinted, with permission, from [author names, paper title, IEEE publication title, and month/year of publication]

2) Only the accepted version of an IEEE copyrighted paper can be used when posting the paper or your thesis on-line.

3) In placing the thesis on the author's university website, please display the following message in a prominent place on the website: In reference to IEEE copyrighted material which is used with permission in this thesis, the IEEE does not endorse any of [university/educational entity's name goes here]'s products or services. Internal or personal use of this material is permitted. If interested in reprinting/republishing IEEE copyrighted material for advertising or promotional purposes or for creating new collective works for resale or redistribution, please go to <a href="http://www.ieee.org/publications\_standards/publications/rights/rights\_link.html">http://www.ieee.org/publications\_standards/publications/rights/rights\_link.html</a> to learn how to obtain a License from RightsLink.

If applicable, University Microfilms and/or ProQuest Library, or the Archives of Canada may supply single copies of the dissertation.

Copyright © 2018 <u>Copyright Clearance Center, Inc.</u> All Rights Reserved. <u>Privacy statement</u>. <u>Terms and Conditions</u>. Comments? We would like to hear from you. E-mail us at <u>customercare@copyright.com</u> © 2018 IEEE. Reprinted, with permission, from D. Carballo, E. Escala and J. C. Balda, "Stability Analysis of Multiple Grid-Connected Inverters Using Different Feedback Currents," August, 2018.

In reference to IEEE copyrighted material which is used with permission in this thesis, the IEEE does not endorse any of University of Arkansas products or services. Internal or personal use of this material is permitted. If interested in reprinting/republishing IEEE copyrighted material for advertising or promotional purposes or for creating new collective works for resale or redistribution, please go to:

http://www.ieee.org/publications\_standards/publications/rights/rights\_link.html to learn how to obtain a License from RightsLink.

## **Certification of First Author**

I hereby certify that David Carballo Rojas is the first author of the article this chapter is based on and has completed at least 51% of the work described in the article.

Juan Carlos Balda

Signature \_\_\_\_\_

Date \_\_\_\_\_

#### **CHAPTER 3**

# MODELING AND STABILITY ANALYSIS OF GRID-CONNECTED INVERTERS WITH DIFFERENT LCL FILTER PARAMETERS

D. Carballo, E. Escala and J. C. Balda, "Modeling and Stability Analysis of Grid-connected Inverters with Different LCL Filter Parameters," *2018 IEEE Electronic Power Grid (eGrid)*, Charleston, SC, 2018.

## Abstract

Microgrid are gaining popularity due to several advantages like potential for fuel savings and resiliency in case of grid catastrophic failures. In a microgrid, many energy sources like wind and solar farms are connected to the grid through inverters with different power ratings and LCL filter parameters. The inverters incorporated in these systems might have a different frequency response and stability ranges than those inverters with identical LCL filter values. This paper establishes the model and analyzes the stability of a system with multiple paralleled- and grid-connected inverters with different LCL filter parameters using the grid-side currents as feedback signals. The analysis results showed that a method similar to the interactive and common current analysis technique used on inverters with identical LCL filters can be implemented on a system with different LCL filters to calculate the maximum values of the inverters' current controller gains without having to derive the complicated equations of the MIMO system.

35

#### **3.1 Introduction**

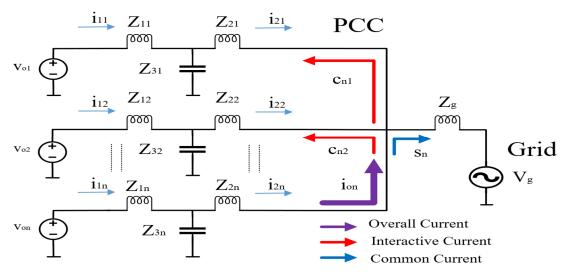

The growing demand for renewable energy sources, such as solar energy, wind energy, and even energy storage has led to higher penetration of distributed energy resources (DERs) into power systems during the past years. As a result, the design of controllers for grid-connected inverters interfacing DERs and the electric grid has become a crucial task. In renewable power plants, hundreds of inverters operate in parallel to expand the total generation capacity [1]. These paralleled inverters are usually connected to the grid through LCL filters which tend to aggravate the system resonance and instability issues due to coupling produced by the grid impedance and converter's current controller dynamic interactions [2].

These instabilities problems due to the coupling of the inverters LCL filters have been studied thoroughly in the literature. Usually in these studies, the inverters are assumed to have identical LCL filter parameters in order to reduce the complexity of the analysis [3-5]. However, a wide variety of energy sources are incorporated in a microgrid; thus, LCL filters with different parameters and power ratings are connected to the point of common coupling (PCC). Consequently, these inverters have different system responses than those inverters with identical LCL filter values. The authors of [6] presented an analysis on the relationship between the resonant frequency and the different numbers of parallel inverters, the LCL filter parameters as well as the inverter's composition ratios. However, an analysis of the system regarding the stability ranges for the current controllers' proportional gain was not performed. The work presented in this paper aims to model and analyze multiple grid-connected inverters with different LCL filter parameters with the ultimate goal of simplifying the stability analysis to determine the proportional gain stability ranges of the inverters.

36

This paper is organized as follows: Section 3.2 addresses an overview of the mathematical modeling of the grid-side currents, Section 3.3 evaluates the system stability, Section 3.4 illustrates a method to reduce the complexity of the system's stability analysis, Section 3.5 analyzes simulation results, and Section 3.6 provides the main conclusions.

#### **3.2 Modeling of the Parallel Inverters**

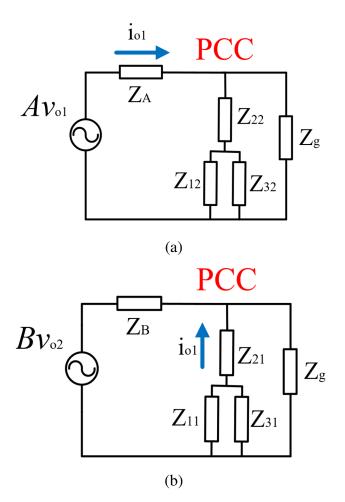

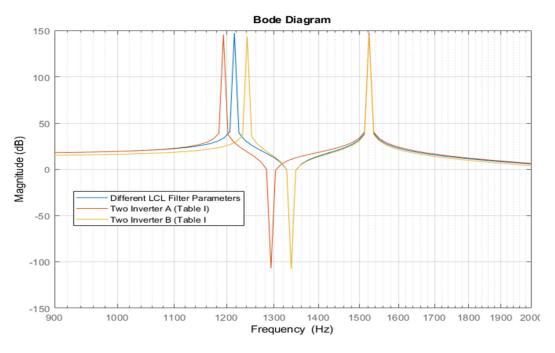

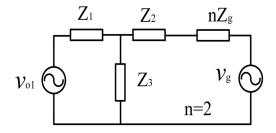

#### 3.2.1 Grid-Side Current- Mathematical Modeling