## University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

12-2018

# Fully Analog Laser Driver With Robust Active Feedback Control

John Petrilli University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd Part of the <u>Electrical and Electronics Commons</u>

## **Recommended** Citation

Petrilli, John, "Fully Analog Laser Driver With Robust Active Feedback Control" (2018). *Theses and Dissertations*. 2970. https://scholarworks.uark.edu/etd/2970

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

Fully Analog Laser Driver With Robust Active Feedback Control

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science In Electrical Engineering

by

## John Petrilli California State University, Fullerton Bachelor of Science in Electrical Engineering, 2014

## December 2018 University of Arkansas

This thesis is approved for recommendation to the Graduate Council.

Roy McCann, Ph.D. Thesis Chair

Omar Manasreh, Ph.D. Committee Member

Hameed Naseem, Ph.D. Committee Member

## Abstract

The objective of this project was to go through a real life engineering development cycle, document and justify the design choices, and use background experience in electronic design and control systems to implement the best design possible. The laser driver implemented in this project is designed for the general use of a large variety of diodes in continuous wave mode, much like off the shelf laser drivers. The design goals included improving upon off the shelf laser drivers by decreasing steady state error, setting time, response time, and overshoot. Many different feedback control systems were evaluated, and a modified PID controller was chosen which was designed to overcome the operational behavior of real-life electronics. The system was designed from the ground up, the electronics were simulated in the time domain, the entire system derived into the Laplace Domain and simulated using Matlab/Simulink. A printed circuit board was designed and assembled to verify performance in a real system.

## Contents

| 1 | Introdu    | uction     |                                       | 1  |

|---|------------|------------|---------------------------------------|----|

| 2 | Develo     | p Specifi  | cations                               | 2  |

|   | 2.1        | Photodio   | de Input Current                      | 2  |

|   | 2.2        | Optical D  | Drift                                 | 2  |

|   | 2.3        | APC Loo    | pp Speed                              | 2  |

|   | 2.4        | Over and   | d Undershoot                          | 3  |

|   |            | 2.4.1      | Startup                               | 3  |

|   |            | 2.4.2      | Step Change                           | 3  |

|   |            | 2.4.3      | Shutdown                              | 3  |

|   | 2.5        | Settling 1 | Time                                  | 3  |

|   |            | 2.5.1      | Startup                               | 3  |

|   |            | 2.5.2      | Step Change                           | 4  |

|   | 2.6        | Settling A | Accuracy                              | 4  |

|   | 2.7        | Current N  | Noise                                 | 4  |

|   | 2.8        | Signal to  | Noise Ratio                           | 4  |

|   | 2.9        | Data She   | eet                                   | 4  |

| • | <b>.</b> . |            |                                       | _  |

| 3 | •          |            | ser Driver                            | 5  |

|   | 3.1        |            |                                       |    |

|   | 3.2        | ACC The    | eory of Operation                     | 6  |

|   | 3.3        | Transient  | t Simulation                          | 7  |

|   | 3.4        | AC Analy   | ysis                                  | 7  |

|   | 3.5        | ACC Las    | er Driver Conclusions                 | 8  |

| 4 | Feedba     | ack Mecha  | anism                                 | 9  |

|   | 4.1        |            | de Background                         | 10 |

|   |            | 4.1.1      | Photo Current                         | 11 |

|   |            | 4.1.2      |                                       | 11 |

|   |            | 4.1.3      |                                       |    |

|   |            |            | · · · · · · · · · · · · · · · · · · · |    |

|   |        | 4.1.4      | Shunt Resistance                      | 11 |

|---|--------|------------|---------------------------------------|----|

|   |        | 4.1.5      | Series Resistance                     | 12 |

|   |        | 4.1.6      | Photodiode Noise                      | 12 |

|   | 4.2    | Photodio   | de Resistor Feedback                  | 13 |

|   |        | 4.2.1      | RC Detector Schematic                 | 13 |

|   |        | 4.2.2      | RC Detector Noise                     | 14 |

|   | 4.3    | Photodio   | de Transimpedance Feedback            | 15 |

|   |        | 4.3.1      | TIA Detector Noise                    | 16 |

|   | 4.4    | Feedbac    | k Mechanism Conclusion                | 16 |

| 5 | Transi | mpedance   | e Amplifier Design                    | 18 |

|   | 5.1    | Transimp   | bedance Amplifier Theory of Operation | 18 |

|   | 5.2    | Choosing   | g the Right Amplifier                 | 19 |

|   |        | 5.2.1      | Amplifiers to Avoid                   | 19 |

|   |        | 5.2.2      | Amplifiers to Consider                | 19 |

|   | 5.3    | Designin   | g the Feedback Network                | 20 |

|   | 5.4    | Compens    | sating for Non-Ideal Situations       | 21 |

|   | 5.5    | Voltage S  | Supply Rails                          | 21 |

|   | 5.6    | TIA Stag   | e 1 Stability                         | 22 |

|   |        | 5.6.1      | Gain and Phase Margin                 | 22 |

|   |        | 5.6.2      | Feedback Factor                       | 23 |

|   |        | 5.6.3      | TIA Noise Performance                 | 25 |

|   |        | 5.6.4      | TIA Stage 2                           | 26 |

|   |        | 5.6.5      | Component Selection                   | 27 |

|   | 5.7    | TIA Desi   | gn Conclusions                        | 28 |

| 6 | APC D  | esign and  | Integration                           | 29 |

|   | 6.1    | APC Blog   | ck Diagram                            | 29 |

|   | 6.2    | Integratio | on                                    | 29 |

|   | 6.3    | Derivatio  | n of System Transfer Function         | 29 |

|   |        | 6.3.1      | Set-Point Circuit                     | 30 |

|   |                       | 6.3.2                                                                                                                 | TIA Stage 1 Transfer Function        | 31                                                              |

|---|-----------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------|

|   |                       | 6.3.3                                                                                                                 | TIA Stage 2 Transfer Function        | 32                                                              |

|   |                       | 6.3.4                                                                                                                 | TIA Transfer Function                | 33                                                              |

|   |                       | 6.3.5                                                                                                                 | Driving Transistor Transfer Function | 33                                                              |

| 7 | Laplac                | ce Simula                                                                                                             | tion with Matlab                     | 36                                                              |

|   | 7.1                   | Current                                                                                                               | Set Point Amplifier                  | 36                                                              |

|   | 7.2                   | Transimp                                                                                                              | pedance Amplifier                    | 37                                                              |

|   |                       | 7.2.1                                                                                                                 | Stage 1                              | 37                                                              |

|   |                       | 7.2.2                                                                                                                 | Stage 2                              | 39                                                              |

|   |                       | 7.2.3                                                                                                                 | Dual Stage Transimpedance Amplifier  | 40                                                              |

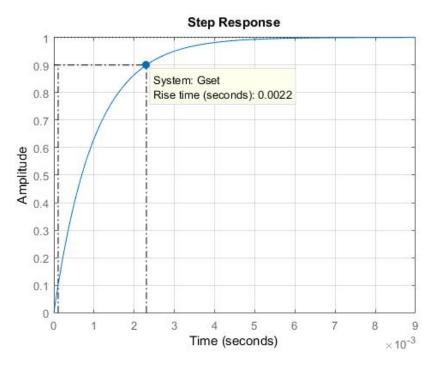

|   | 7.3                   | Driving T                                                                                                             | ransistor                            | 42                                                              |

|   | 7.4                   | Matlab S                                                                                                              | Script                               | 43                                                              |

|   | 7.5                   | APC Sys                                                                                                               | stem Simulation                      | 46                                                              |

|   | 7.6                   | Laplace                                                                                                               | Domain Conclusion                    | 49                                                              |

|   |                       |                                                                                                                       |                                      |                                                                 |

| 8 | Analog                | g Control                                                                                                             | System                               | 50                                                              |

| 8 | <b>Analo</b> g<br>8.1 | -                                                                                                                     | System                               |                                                                 |

| 8 |                       | -                                                                                                                     | •                                    | 50                                                              |

| 8 |                       | Choosin                                                                                                               | g A Control System                   | 50<br>50                                                        |

| 8 |                       | Choosing<br>8.1.1                                                                                                     | g A Control System                   | 50<br>50<br>50                                                  |

| 8 |                       | Choosin<br>8.1.1<br>8.1.2                                                                                             | g A Control System                   | 50<br>50<br>50                                                  |

| 8 |                       | Choosing<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4                                                                          | g A Control System                   | 50<br>50<br>51<br>51                                            |

| 8 | 8.1                   | Choosing<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4                                                                          | g A Control System                   | 50<br>50<br>51<br>51<br>52                                      |

| 8 | 8.1                   | Choosing<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>System I                                                              | g A Control System                   | 50<br>50<br>51<br>51<br>52<br>52                                |

| 8 | 8.1                   | Choosing<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>System I<br>8.2.1                                                     | g A Control System                   | 50<br>50<br>51<br>51<br>52<br>52<br>52                          |

| 8 | 8.1                   | Choosing<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>System I<br>8.2.1<br>8.2.2<br>8.2.3                                   | g A Control System                   | 50<br>50<br>51<br>51<br>52<br>52<br>52                          |

|   | 8.1                   | Choosing<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>System I<br>8.2.1<br>8.2.2<br>8.2.3<br>cal Impler                     | g A Control System                   | 50<br>50<br>51<br>51<br>52<br>52<br>56<br>58                    |

|   | 8.1<br>8.2<br>Practic | Choosing<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>System I<br>8.2.1<br>8.2.2<br>8.2.3<br><b>cal Impler</b><br>Derivativ | g A Control System                   | 50<br>50<br>51<br>51<br>52<br>52<br>56<br>58<br><b>61</b><br>61 |

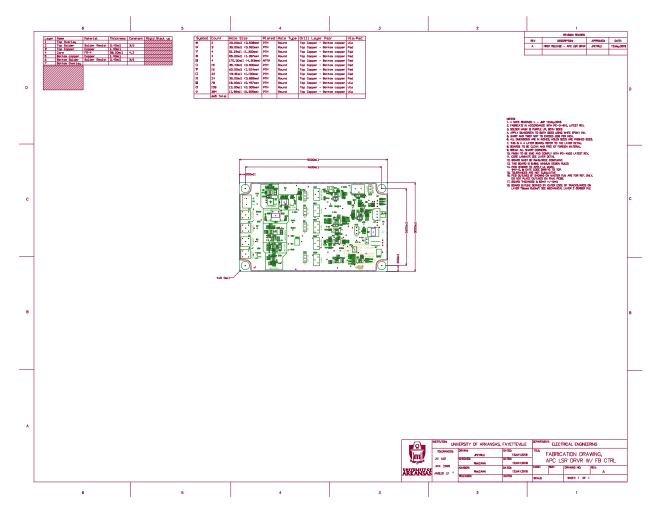

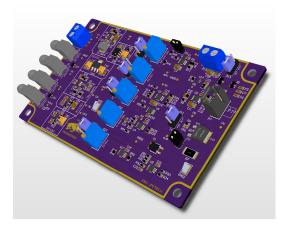

## 10 PCB Design and Fabrication

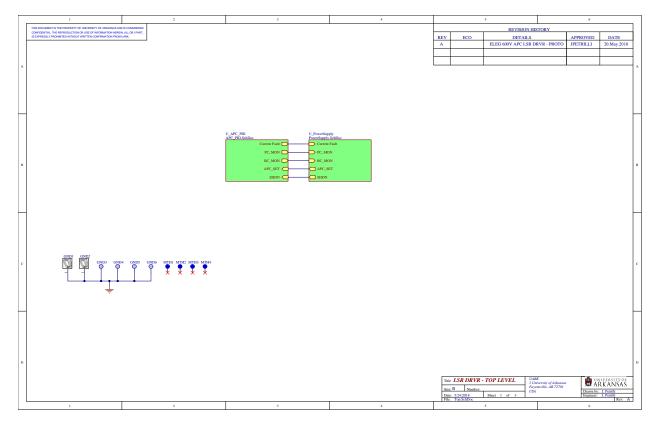

|    | 10.1    | Schemat    | ics                                 | 64 |

|----|---------|------------|-------------------------------------|----|

|    |         | 10.1.1     | Top Level                           | 64 |

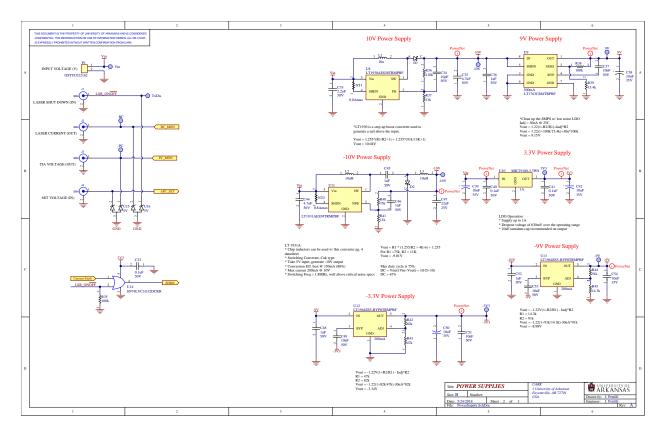

|    |         | 10.1.2     | Power Supplies                      | 65 |

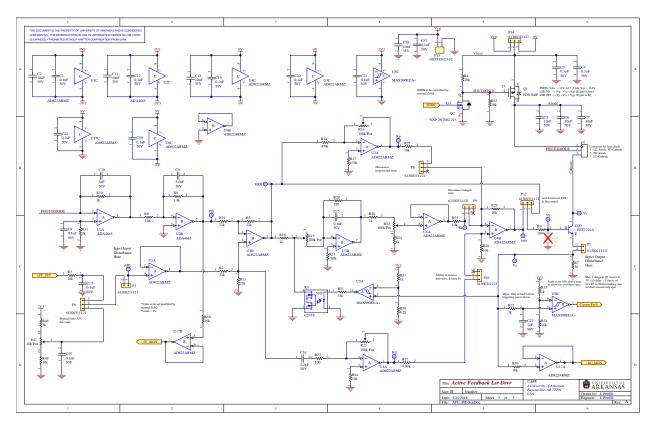

|    |         | 10.1.3     | APC Laser Driver                    | 69 |

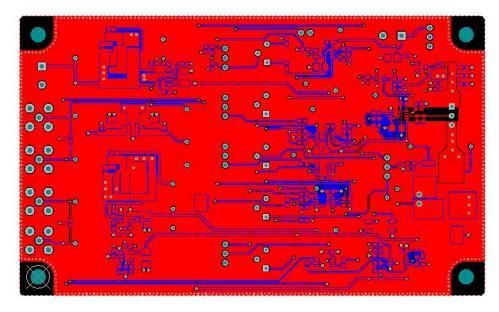

|    | 10.2    | PCB Lay    | out                                 | 71 |

|    |         | 10.2.1     | Design Rules                        | 71 |

|    |         | 10.2.2     | Top and Bottom Pour                 | 71 |

|    |         | 10.2.3     | Power Supplies                      | 72 |

|    |         | 10.2.4     | EMI and Edge Emission Consideration | 73 |

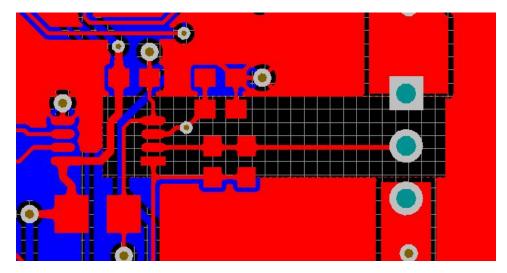

|    |         | 10.2.5     | TIA Layout Technique                | 74 |

|    | 10.3    | Fabricati  | on Files                            | 74 |

|    | 10.4    | Final PC   | B 3D CAD                            | 75 |

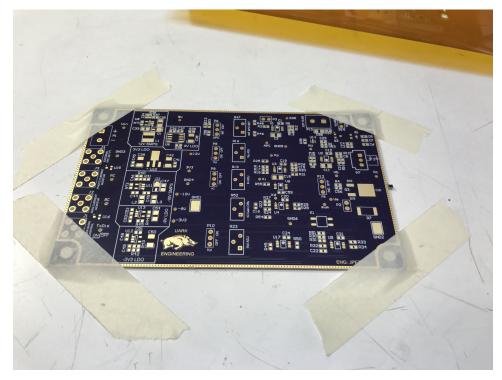

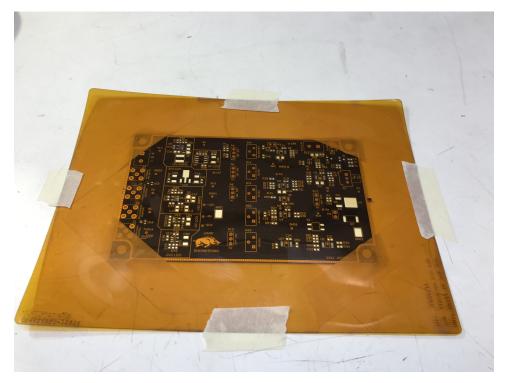

| 11 | PCB A   | ssembly    |                                     | 77 |

|    | 11.1    | Equipme    | nt                                  | 77 |

|    | 11.2    | Prepping   | the PCB                             | 78 |

|    | 11.3    | Applying   | Solder Paste                        | 79 |

|    | 11.4    | Pick and   | Place                               | 81 |

|    | 11.5    | Reflow .   |                                     | 81 |

|    | 11.6    | Finishing  | the Assembly Process                | 82 |

| 12 | Testing | ]          |                                     | 84 |

|    | 12.1    | Equipme    | nt                                  | 84 |

|    | 12.2    | Descripti  | on of Test Setup and Equipment      | 85 |

|    | 12.3    | Initial Po | wer Up                              | 86 |

|    |         | 12.3.1     | Power Supplies                      | 86 |

|    |         | 12.3.2     | Issues Found                        | 87 |

|    | 12.4    | Power St   | upply Specifications                | 88 |

|    |         | 12.4.1     | Single Supply                       | 88 |

|    |         | 12.4.2     | Supply Current at 5V                | 88 |

| 1:   | 2.5   | Laser Bia | IS                                                     | 88 |

|------|-------|-----------|--------------------------------------------------------|----|

|      |       | 12.5.1    | Bias Current Setting Range                             | 88 |

|      |       | 12.5.2    | Bias Off Current                                       | 89 |

|      |       | 12.5.3    | Bias Current Monitor Ratio                             | 89 |

| 1:   | 2.6   | Automatio | c Power Control                                        | 89 |

|      |       | 12.6.1    | Photodiode Input Current                               | 89 |

|      |       | 12.6.2    | Photodiode Voltage Out                                 | 89 |

|      |       | 12.6.3    | Photodiode Current Monitor Ratio                       | 89 |

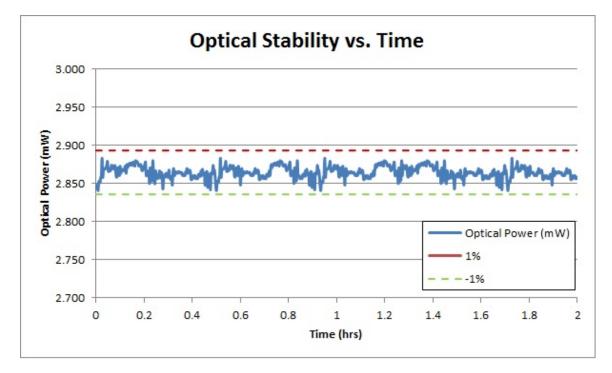

|      |       | 12.6.4    | Optical Drift                                          | 90 |

|      |       | 12.6.5    | Electrical Stability                                   | 90 |

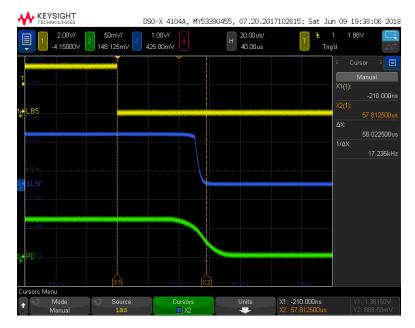

|      |       | 12.6.6    | APC Loop Time Constant                                 | 91 |

| 1:   | 2.7   | Active Fe | edback Controls                                        | 92 |

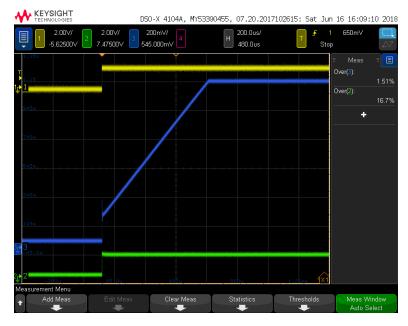

|      |       | 12.7.1    | Startup Overshoot/Undershoot and Startup Settling Time | 92 |

|      |       | 12.7.2    | Shutdown Overshoot/Undershoot                          | 93 |

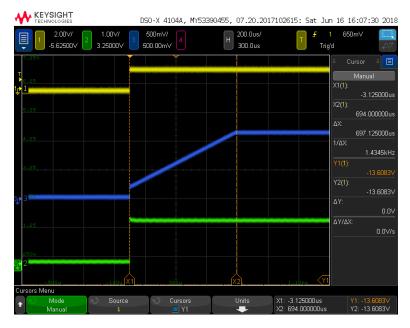

|      |       | 12.7.3    | Step Change Overshoot/Undershoot                       | 94 |

| 1:   | 2.8   | Step Cha  | nge Settling Time                                      | 94 |

|      |       | 12.8.1    | Settling Accuracy                                      | 95 |

| 1:   | 2.9   | Laser Sa  | fety                                                   | 96 |

| 1:   | 2.10  | Turn-Off  | Delay and Overcurrent Protection Delay                 | 96 |

| 1:   | 2.11  | Noise Pe  | rformance                                              | 96 |

| 1:   | 2.12  | Testing C | Conclusion                                             | 97 |

| 13 C | onclu | sion      |                                                        | 97 |

14 References

# List of Figures

| 1                                      | Laser driver data sheet derived from weaknesses in off-the-shelf ICs                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                                            |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2                                      | Automatic Current Control (ACC) laser driver schematic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6                                            |

| 3                                      | ACC laser driver SPICE simulation results of theoretical values vs. simulated values.                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                                            |

| 4                                      | ACC laser driver results graphed from SPICE simulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8                                            |

| 5                                      | Gain and phase margin graph of ACC laser driver derived from SPICE simulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9                                            |

| 6                                      | TO can removed from a laser diode to expose photodiode on the back facet                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10                                           |

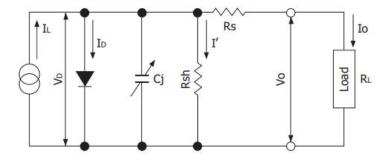

| 7                                      | Equivalent electrical model of a silicon photodiode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10                                           |

| 8                                      | Basic photodiode detector with response equivalent to RC low pass filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13                                           |

| 9                                      | Typical schematic of a transimpedance amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15                                           |

| 10                                     | TIA schematic and current flow used for Laplace and time domain analyses                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18                                           |

| 11                                     | Parametric op-amp search from Linear Technology and Analog Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20                                           |

| 12                                     | Modified TIA schematic to compensate for non-ideal op-amp behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22                                           |

| 13                                     | Gain and phase margin graph of modified TIA derived from SPICE simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23                                           |

| 14                                     | TIA modeled with photodiode equivalent model to account for input impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24                                           |

| 15                                     | Graph of open loop gain vs. feedback factor for modified TIA with photodiode input.                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25                                           |

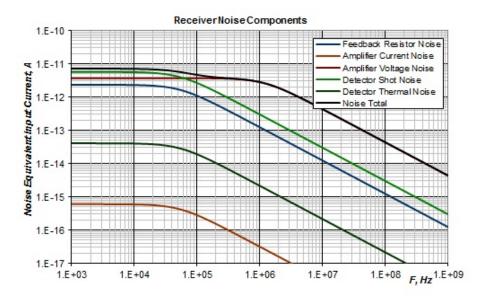

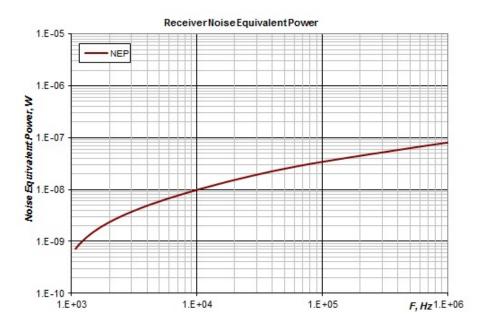

| 16                                     | Noise contributors and magnitude for modified TIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26                                           |

| 17                                     | Noise equivalent power of modified TIA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26                                           |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

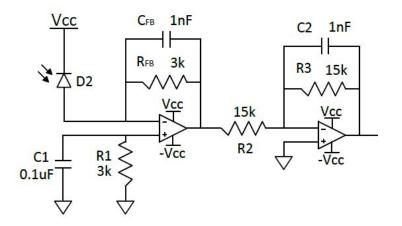

| 18                                     | Dual stage transimpedance amplifier design to be used as the feedback mechanism.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                              |

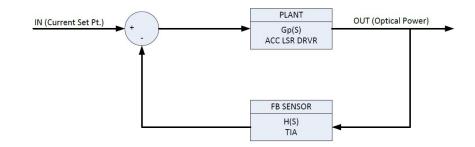

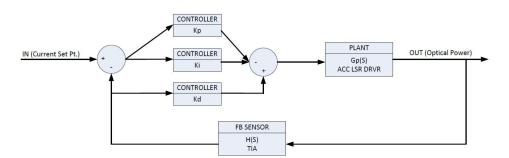

| 18<br>19                               | Dual stage transimpedance amplifier design to be used as the feedback mechanism.<br>Block diagram for automatic power control laser driver feedback system                                                                                                                                                                                                                                                                                                                                                                                       | 27                                           |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27                                           |

| 19                                     | Block diagram for automatic power control laser driver feedback system                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27<br>29                                     |

| 19<br>20                               | Block diagram for automatic power control laser driver feedback system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27<br>29<br>30<br>30                         |

| 19<br>20<br>21                         | Block diagram for automatic power control laser driver feedback system.         Schematic for APC laser driver.         Current set point schematic for transfer derivation.                                                                                                                                                                                                                                                                                                                                                                     | 27<br>29<br>30<br>30<br>31                   |

| 19<br>20<br>21<br>22                   | Block diagram for automatic power control laser driver feedback system.         Schematic for APC laser driver.         Current set point schematic for transfer derivation.         First stage TIA schematic for derivation of transfer function.                                                                                                                                                                                                                                                                                              | 27<br>29<br>30<br>30<br>31<br>33             |

| 19<br>20<br>21<br>22<br>23             | Block diagram for automatic power control laser driver feedback system.       .         Schematic for APC laser driver.       .         Current set point schematic for transfer derivation.       .         First stage TIA schematic for derivation of transfer function.       .         Second stage TIA schematic for derivation of transfer function.       .                                                                                                                                                                              | 27<br>29<br>30<br>30<br>31<br>33<br>34       |

| 19<br>20<br>21<br>22<br>23<br>24       | Block diagram for automatic power control laser driver feedback system.       .         Schematic for APC laser driver.       .         Current set point schematic for transfer derivation.       .         First stage TIA schematic for derivation of transfer function.       .         Second stage TIA schematic for derivation of transfer function.       .         Laser driving transistor schematic for analysis of transfer function.       .                                                                                        | 27<br>29<br>30<br>31<br>33<br>34<br>34       |

| 19<br>20<br>21<br>22<br>23<br>24<br>25 | Block diagram for automatic power control laser driver feedback system.       .         Schematic for APC laser driver.       .         Current set point schematic for transfer derivation.       .         First stage TIA schematic for derivation of transfer function.       .         Second stage TIA schematic for derivation of transfer function.       .         Laser driving transistor schematic for analysis of transfer function.       .         Equivalent electrical model of BJT for deriving the transfer function.       . | 27<br>29<br>30<br>31<br>33<br>34<br>34<br>35 |

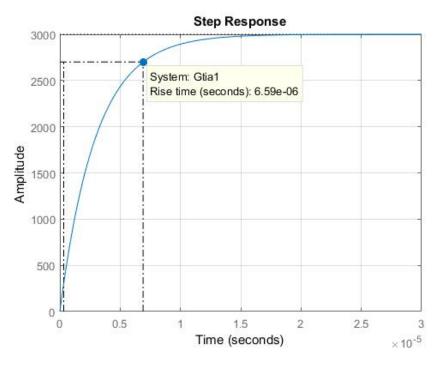

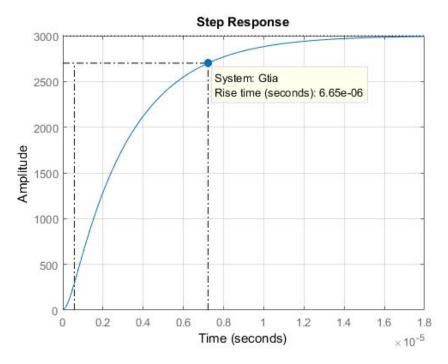

| 29 | First stage of TIA response to step input                                           | 38 |

|----|-------------------------------------------------------------------------------------|----|

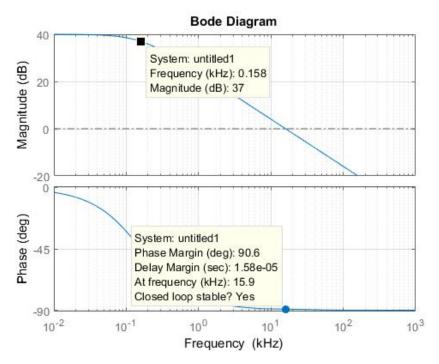

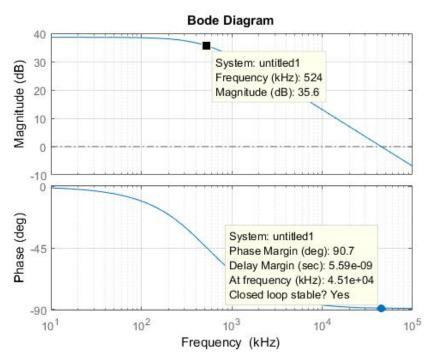

| 30 | First stage of TIA frequency response.                                              | 38 |

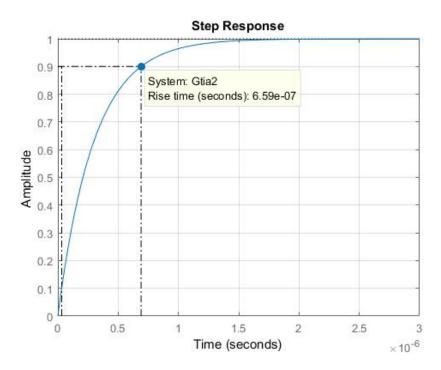

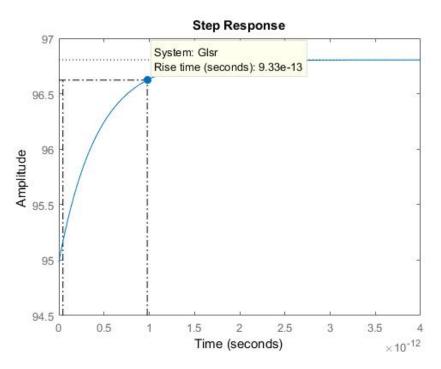

| 31 | Second stage of TIA response to step input                                          | 39 |

| 32 | Second stage of TIA frequency response.                                             | 40 |

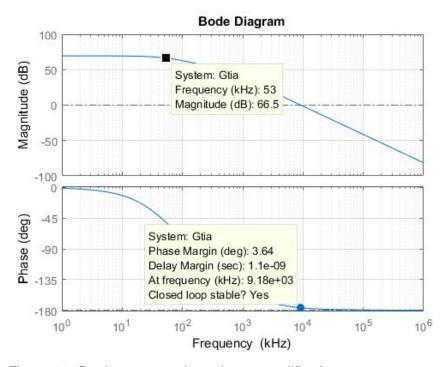

| 33 | Dual stage transimpedance amplifier response to step input.                         | 41 |

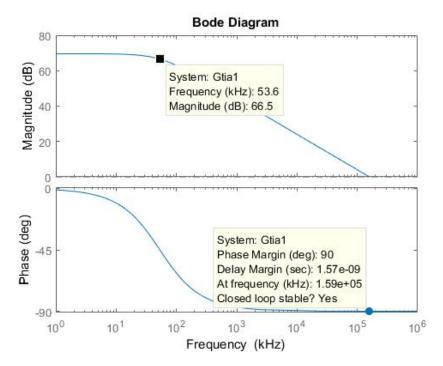

| 34 | Dual stage transimpedance amplifier frequency response.                             | 41 |

| 35 | Driving transistor response to step input.                                          | 42 |

| 36 | Driving transistor frequency response.                                              | 43 |

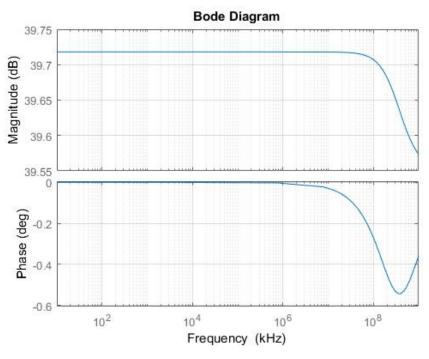

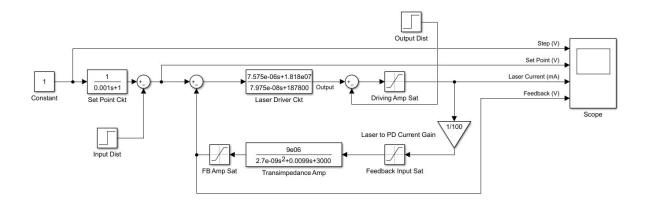

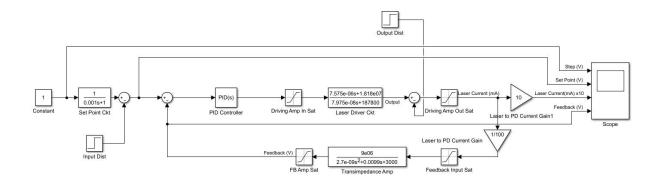

| 37 | Simulink model of automatic power control laser driver                              | 46 |

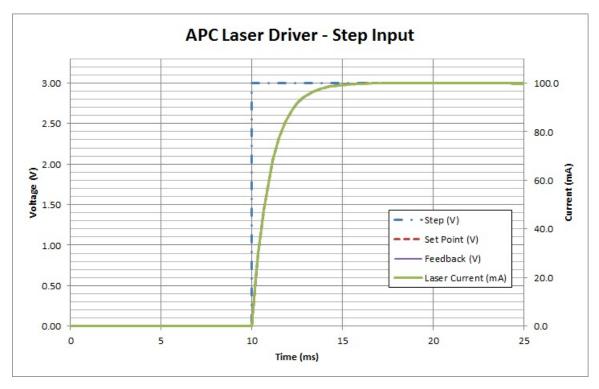

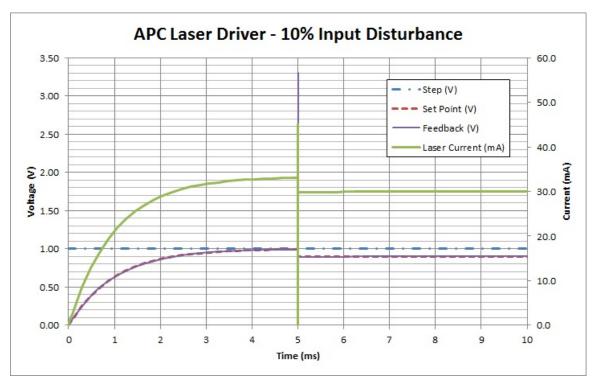

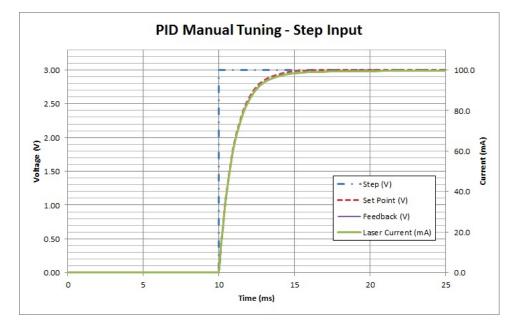

| 38 | Simulink response to step input on APC laser driver system                          | 47 |

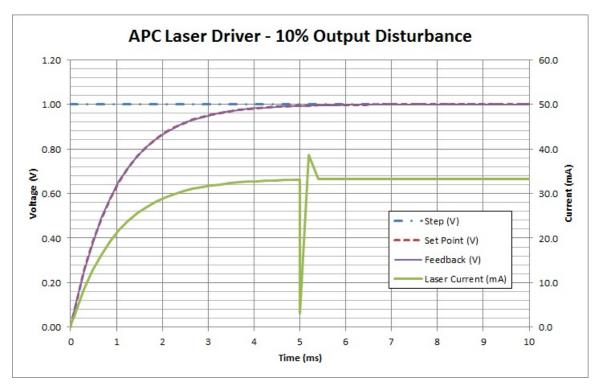

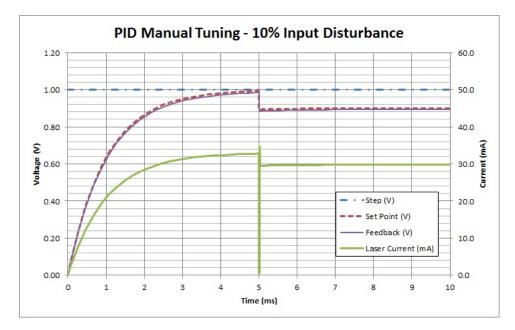

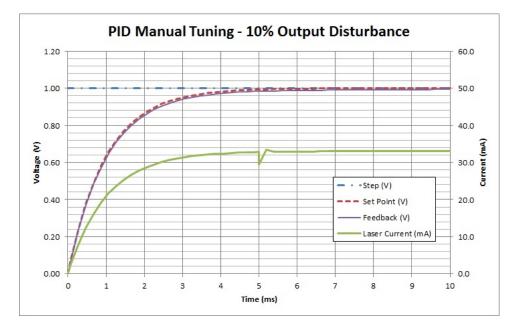

| 39 | Simulink response to output disturbance on APC laser driver system                  | 48 |

| 40 | Simulink response to input disturbance on APC laser driver system.                  | 49 |

| 41 | Simulink response to step input of APC PID for third order hand calculated ITAE     |    |

|    | system                                                                              | 55 |

| 42 | Simulink response to input disturbance of third order hand calculated ITAE system   | 56 |

| 43 | Simulink response to output disturbance of third order hand calculated ITAE system. | 56 |

| 44 | Continuous PID controller integrated into previous APC model                        | 57 |

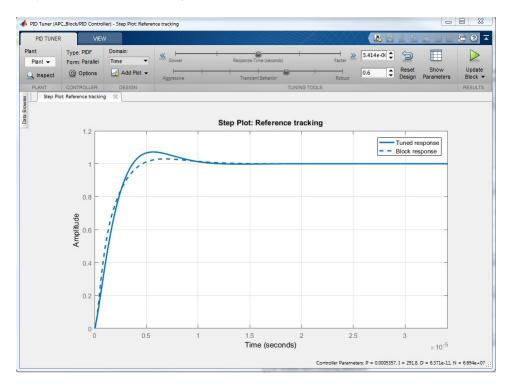

| 45 | Simulink PID block auto-tuning menu                                                 | 57 |

| 46 | Simulink auto-tune step response menu used to trade off robustness for speed        | 58 |

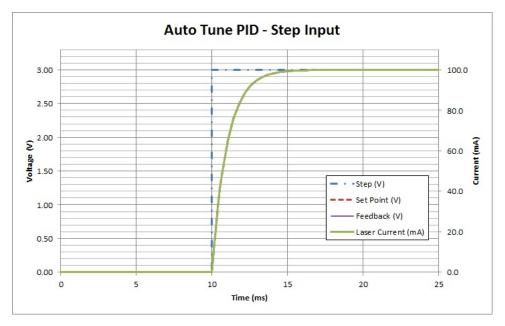

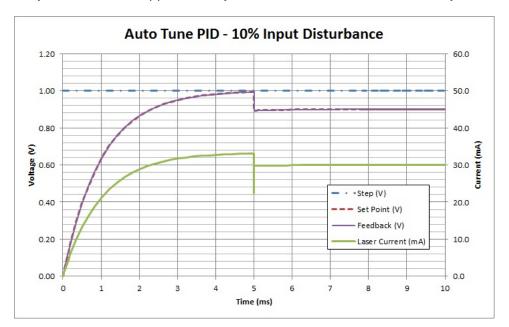

| 47 | Simulink model response to step-up input with auto-tuned PID                        | 59 |

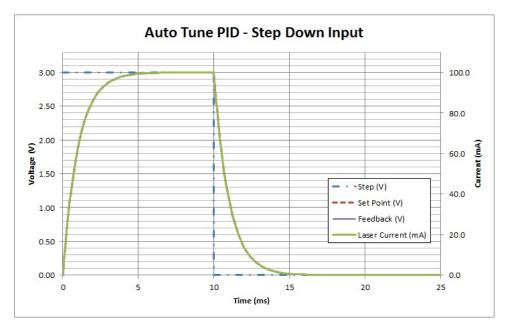

| 48 | Simulink model response to step-down input with auto-tuned PID                      | 59 |

| 49 | Simulink model response to input disturbance with auto-tuned PID                    | 60 |

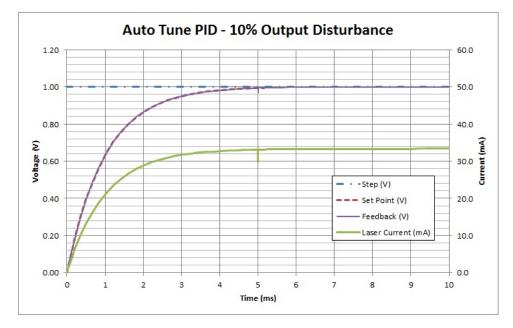

| 50 | Simulink model response to output disturbance with auto-tuned PID                   | 60 |

| 51 | Block diagram of approach used to avoid derivative overrun                          | 62 |

| 52 | Schematic to display approach used to avoid integral windup                         | 63 |

| 53 | Top level hierarchical schematic for PCB design.                                    | 64 |

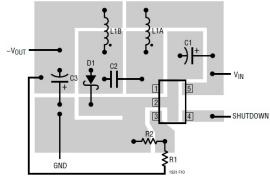

| 54 | Schematic to generate power supplies for driving and controller laser               | 66 |

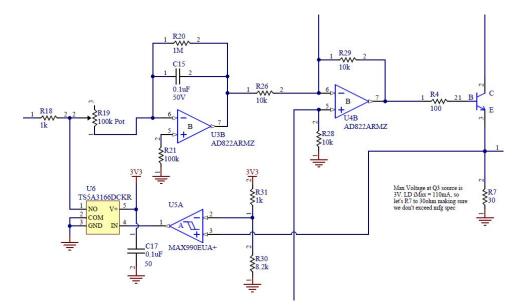

| 55 | Schematic for APC laser driver with a parallel PID control system.                  | 69 |

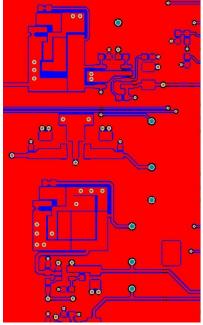

| 56 | Printed circuit board copper pour on top layer                                      | 72 |

| 57 | Printed circuit board copper pour on bottom layer.                                  | 72 |

| 58 | Layout and routing of power supplies to achieve optimal performance.                   | 73 |

|----|----------------------------------------------------------------------------------------|----|

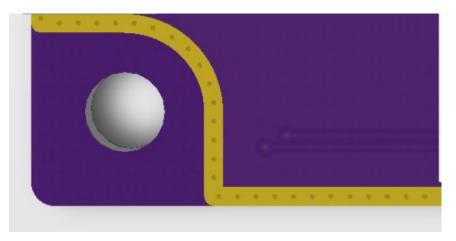

| 59 | Stitching the perimeter of the PCB with vias to mitigate edge radiation and EMI        | 73 |

| 60 | Layout and routing of the TIA to achieve best performance on two-layer PCB             | 74 |

| 61 | Drawing of the PCB to provide information regarding bare board fabrication             | 75 |

| 62 | 3D rendered top view of the PCBA using Altium Designer 2017                            | 76 |

| 63 | 3D rendered bottom view of the PCBA using Altium Designer 2017                         | 76 |

| 64 | 3D rendered angled view of the PCBA using Altium Designer 2017                         | 76 |

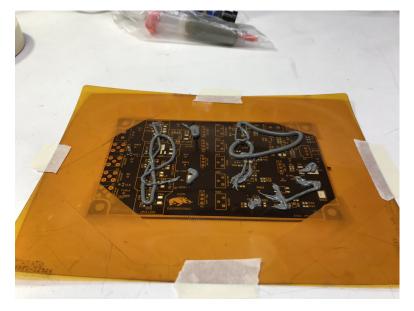

| 65 | Bare PCB taped to ESD safe surface.                                                    | 78 |

| 66 | Solder stencil aligned to bare PCB                                                     | 79 |

| 67 | Solder Paste applied to the aligned solder stencil                                     | 79 |

| 68 | Results from solder paste being spread into stencil openings                           | 80 |

| 69 | PCB with solder paste on surface mount pads.                                           | 80 |

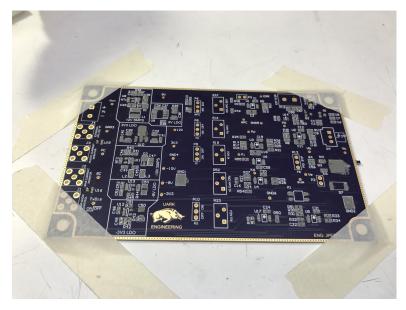

| 70 | All SMT components have been manually placed on PCB and ready for reflow               | 81 |

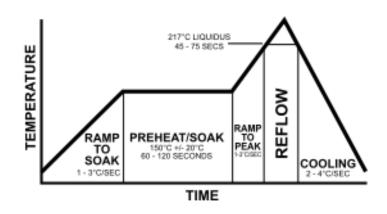

| 71 | Ideal temperature profile for solder reflow.                                           | 82 |

| 72 | Environmental chamber modified to work as reflow oven                                  | 82 |

| 73 | Ultrasonic cleaning of the PCB using 99% isoprophyl alcohol.                           | 83 |

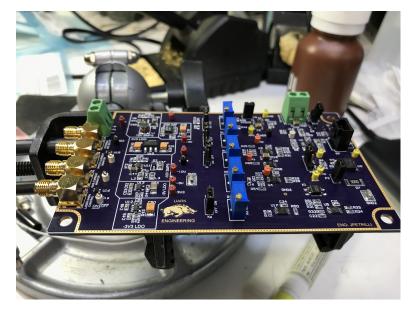

| 74 | Complete assembled PCBA ready for testing                                              | 83 |

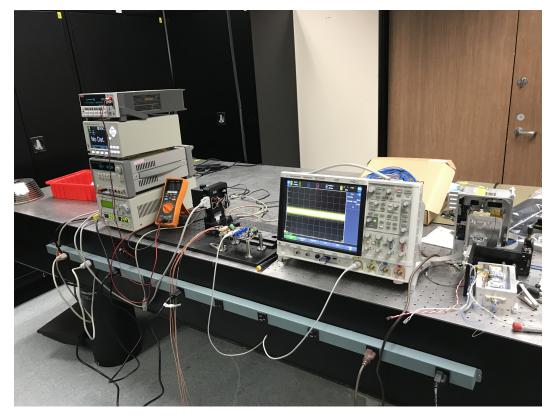

| 75 | Testing station and equipment used during verification of performance                  | 85 |

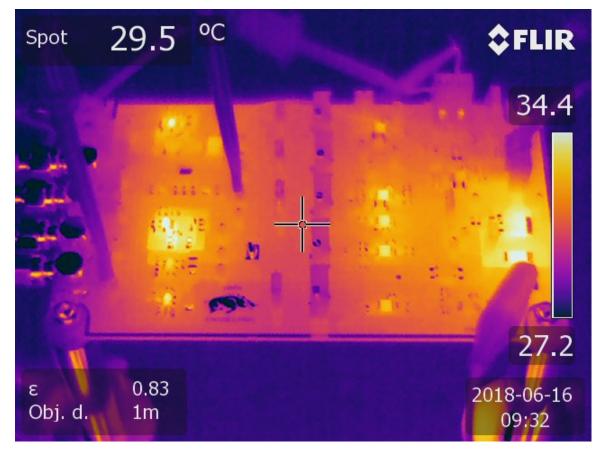

| 76 | Thermal image of PCB on startup.                                                       | 86 |

| 77 | Power supply noise measured with Keysight Technologies 4104A oscilloscope              | 87 |

| 78 | Optical stability measured over a period of two hours using a data acquisition system. | 90 |

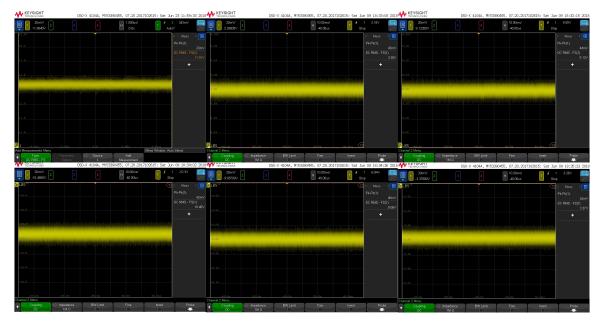

| 79 | Electrical stability measured over a period of two hours using Keysight 4104A scope.   | 91 |

| 80 | Frequency response TIA using Keysight Technologies 4104A oscilloscope                  | 92 |

| 81 | APC PID laser driver response to step-up input                                         | 93 |

| 82 | APC PID laser driver response to step-down input.                                      | 93 |

| 83 | APC PID laser driver response to an output disturbance change in set point             | 94 |

| 84 | APC PID laser driver settling time to an output disturbance change in set point        | 95 |

| 85 | APC PID laser driver response to shutdown and overcurrent fault.                       | 96 |

| 86 | Data sheet specifications vs. test results.                                            | 97 |

#### 1 Introduction

The process for designing and implementing a fully analog control system for driving laser diodes will be outlined and stepped through. Weaknesses in off-the-shelf laser drivers are identified and design goals are created to improve upon these weaknesses. An general analog laser driver must be conceptualized and realized. A robust feedback mechanism must be designed in order to accurately and automatically control the output of the laser. Once the driver and feedback have been designed they can be merged to create a closed loop automatic power control laser driver. This stage is where most off-the-shelf drivers stop, however, taking it one step further and implementing a control system will improve performance with minimal drawbacks. This project will step through design process in detail including electronic design, time domain simulation, frequency domain simulation, derivation of transfer functions, control system simulation, as well as real life testing results.

Laser drivers typically focus on a specific operating conditions such as modulation, stability, low noise, or power. A combination of a closed loop stable modulation laser driver [13] is common for the telecom industry however these drivers are typically low power and do not have the ability to drive lasers with high bias currents as opposed to the design in this paper. Another type of laser driver is modulated with high output power [14] for LiDAR systems, but these laser drivers don't have accurate or stable output powers. Low noise laser drivers are also popular for RF applications [16], and achieving a SNR of 55.2dB on a custom wafer is considered outstanding performance while this project was able to accomplish a SNR of 54 dB with off the shelf components. This research focuses on a non-modulated, closed loop stable, high drive current, low noise, optically stable, feedback controlled laser driver. Sacrificing modulation allows a performance boost of the other parameters as well as breaking into a niche market.

1

#### 2 Develop Specifications

In this chapter the weaknesses and opportunities for improvement for off-the-shelf (OTS) laser drivers are identified, and aggressive design goals are realized for maximum performance improvements.

#### 2.1 Photodiode Input Current

The feedback mechanism used in laser drivers to lock the set point for automatic power control is the output of a photodiode. Typically, OTS drivers can accept current in the range of 100's of micro-amps before saturation. It is speculated that this specification is due to noise, which will be touched upon in later chapters. The low current will improve noise performance, however it does not allow for large laser bias currents. This specification can be improved upon with design a goal of accepting up to 5 milli-amps of photodiode current.

#### 2.2 Optical Drift

This is not a typical specification found in a laser driver IC data sheet because it is a liability to guarantee. The laser used to test the system will be new and not show any degradation, therefore it will be guaranteed that the optical power will not drift more than 2% over a period of 2 hours.

#### 2.3 APC Loop Speed

Typical frequency response of an APC loop for an OTS laser driver is  $80kHz < f_{3dB} < 200kHz$ . The faster the feedback loop the quicker it can respond to the photodiode current and make adjustments to the drive current. Also, this pushes out noise peaks due to resonant frequency. For this specification, faster is not necessarily better, so a loop speed of about 50kHz will be chosen. The lower frequency will improve on noise due to the Photodiode Input Current specification. The control loop will also compensate for the tracking error and steady state error seen by OTS drivers.

## 2.4 Over and Undershoot

There are a variety of situations were overshoot and undershoot can occur. If the bias current of the laser diode is being driven close to the maximum operating point, then overshoot and undershoot can become critical parameters as to not cause any catastrophic damage to the device. Manufacturers for OTS drivers have seemed to conveniently leave these scenarios and specifications out of their data sheets. Since the main goal of this project is design a robust control system, these specifications need to be defined.

## 2.4.1 Startup

The overshoot/undershoot during startup will not exceed 10% of the set point.

## 2.4.2 Step Change

During a step change of 0.1V, the overshoot/undershoot will not exceed 10%

#### 2.4.3 Shutdown

The overshoot/undershoot during shutdown will not exceed 10% of the set point.

## 2.5 Settling Time

The percent overshoot and the settling time are trade offs.

## 2.5.1 Startup

The settling time during startup will not exceed 1ms

## 2.5.2 Step Change

The settling time during a step change of 0.1V will not exceed 500us.

## 2.6 Settling Accuracy

This specification is equivalent to steady state error, and since OTS drivers do not have active feedback control, they can only guarantee about 10%. The integrator in this design will allow us to easily guarantee 2%.

## 2.7 Current Noise

The current noise introduced by the laser driver should be less than  $10nA/\sqrt{Hz}$ . There may be some OTS laser drivers that are specifically designed for low noise operation that are quieter than this, but this specification is better than most.

## 2.8 Signal to Noise Ratio

The SNR isn't a typical specification, but it gives a good overall picture of noise performance for the laser driver. A minimum SNR of 50dB will be the target design goal.

## 2.9 Data Sheet

The analysis of weaknesses from off-the-shelf laser drivers has led to development of the data sheet found in figure 1.

| ANALOG ACTIVE FB CONTROL LASER DRIVER SPECIFICATIONS |                     |                                                |      |     |     |        |  |  |

|------------------------------------------------------|---------------------|------------------------------------------------|------|-----|-----|--------|--|--|

| PARAMETER                                            | SYMBOL              | CONDITION                                      | MIN  | ТҮР | MAX | UNITS  |  |  |

| POWER SUPPLY                                         |                     |                                                |      |     | 1   |        |  |  |

| Single Supply                                        | V <sub>cc</sub>     | Voltage input                                  | 3.75 | 5   | 15  | v      |  |  |

| Supply Current                                       | I <sub>cc</sub>     | Supply current w/o laser bias                  | 50   | 80  | 100 | mA     |  |  |

| LASER BIAS                                           |                     |                                                |      |     |     |        |  |  |

| Bias-Current-Setting Range                           |                     | Range of voltage set points for output current | 0    |     | 3   | V      |  |  |

| Bias-Current-Setting Range                           |                     | Range of laser bias current set points         | 0    |     | 100 | mA     |  |  |

| Bias Off Current                                     |                     | Laser bias during shutdown                     |      |     | 0.5 | mA     |  |  |

| Bias-Current Monitor Ratio                           |                     | Bias current monitor volt/amps reading         |      | 30  |     | V/A    |  |  |

| AUTOMATIC POWER CONTROL                              |                     |                                                |      |     |     |        |  |  |

| Photo Diode Input Current                            | I <sub>PD</sub>     | Range of acceptable input currents for PD      | 0    |     | 1   | mA     |  |  |

| Photo Diode Voltage Out                              | V <sub>PD</sub>     | Range of TIA set points for current control    | 0    |     | 3   | v      |  |  |

| Photo Diode Current Monitor Ratio                    |                     | Photo current monitor volt/mA reading          |      | 0.6 |     | V/mA   |  |  |

| Optical Drift                                        |                     | Amount of optical drift over a 2 hour period   |      | 2   |     | %      |  |  |

| Electrical Stability                                 |                     | Laser bias current drift over a 2 hour period  |      |     | 1   | %      |  |  |

| APC Loop Time Constant                               |                     | Analog feedback loop speed                     |      | 20  |     | us     |  |  |

| ACTIVE FEEDBACK CONTROLS                             |                     |                                                |      |     |     |        |  |  |

| Startup Overshoot/Undershoot                         |                     | Over/under shoot percentage at startup         |      |     | 5   | %      |  |  |

| Shutdown Overshoot/Undershoot                        |                     | Over/under shoot percentage at shutdown        |      |     | 5   | %      |  |  |

| Step Change Overshoot/Undershoo                      | ot                  | Over/under shoot with 0.1V step change         |      |     | 10  | %      |  |  |

| Startup Settling Time                                | T <sub>S-STRT</sub> | Time to reach 2% steady state at startup       |      | 5   |     | ms     |  |  |

| Step Change Settling Time                            | T <sub>S-STEP</sub> | Time to reach 2% steady state from step change |      |     | 1   | ms     |  |  |

| Settling Accuracy                                    |                     | Actual steady state vs theoretical             |      |     | 10  | %      |  |  |

| LASER SAFETY                                         |                     |                                                |      |     |     |        |  |  |

| Turn-Off Delay                                       |                     | Time to turn off from shutdown signal          |      |     | 100 | us     |  |  |

| Overcurrent Protection Delay                         |                     | Time of turn off during over-current           |      |     | 125 | us     |  |  |

| NOISE PERFORMANCE                                    |                     |                                                |      |     |     |        |  |  |

| Current Noise                                        | I <sub>TN</sub>     | Total Current Noise of Laser Driver            |      | 9   |     | nA/√Hz |  |  |

| Signal to Noise Ratio                                | SNR                 | SNR of feedback detection                      | 50   | 56  |     | dB     |  |  |

Figure 1: Laser driver data sheet derived from weaknesses in off-the-shelf ICs.

## 3 Design ACC Laser Driver

An automatic current control (ACC) driver sources a constant current through the users device choice. In order to tackle a daunting task such as designing an APC laser driver, first a stable current source to build off of needs to be designed. A voltage controlled current source was chosen as a starting point because most integrated systems are now mixed signal with digital to analog converters being used to control set points. The particular design used allows for easy adjustment to increase the laser bias current, and allows for a large laser bias without damaging the system. The complexity of this system will increase exponentially once a control system is introduced, so it is important to keep the skeleton of the design simple.

## 3.1 ACC Schematic

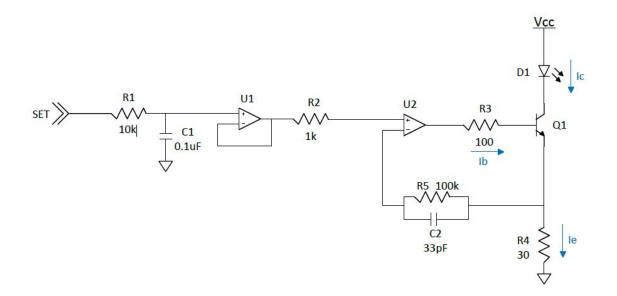

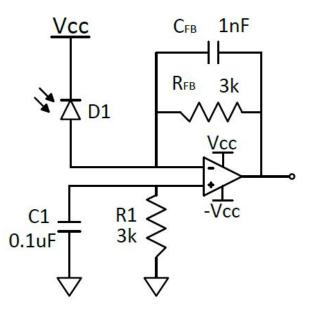

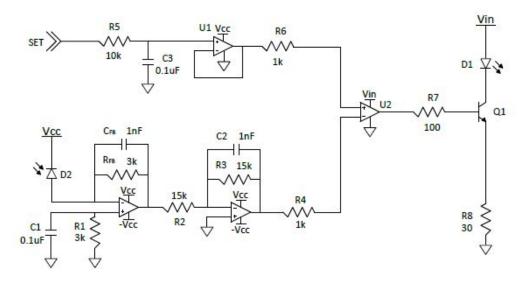

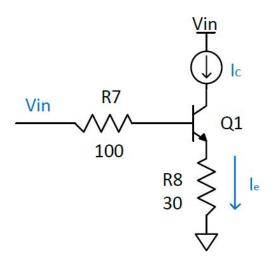

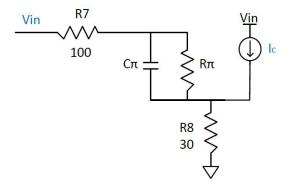

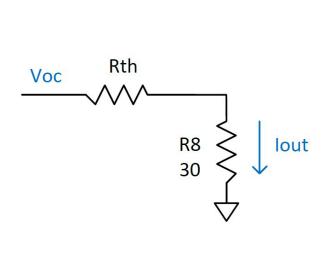

The proposed schematic for the diode driving circuitry is shown in Figure 2.

Figure 2: Automatic Current Control (ACC) laser driver schematic.

## 3.2 ACC Theory of Operation

The off-sheet port 'SET' is the voltage controlled current set point. For this design, the voltage set point varies from 0-3V. 'SET' is put though a passive low pass filter in order to keep the set point stable during small unwanted variations from the voltage input. The low pass filter is fed into a voltage follower buffer to isolate the impedance from the input of the driving amplifier U2. R2 is placed as a bridge between U1 output and U2 non-inverting input serving as a current sink in the case of saturation. Ideally, the input voltage 'SET' will be seen at the non-inverting input of U2 which would make the inverting input want to level out to the same voltage because they are virtually the same node. The feedback is taken from the emitter of the NPN transistor. Since the inverting input wants to be the same as the non-inverting, that means the voltage at the emitter of Q1 will also be the same as 'SET'. The voltage is controlled at the emitter, defining the current through the emitter. The collector current is related to emitter current through beta, meaning the

the diodes bias current is voltage controlled. The feedback network of U2 is chosen to be 50kHz because this is the expected frequency response of the feedback that will be applied at a later time.

## 3.3 Transient Simulation

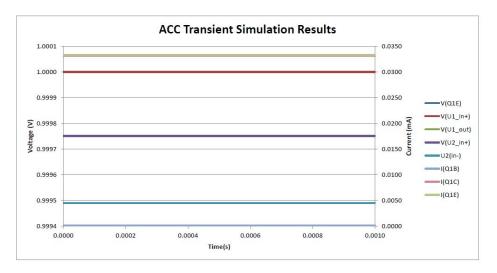

The circuit shown in Figure 2 was simulated with SPICE to derive transient behavior. Figure 3 shows the simulated values vs. the theoretical calculations. Figure 4 graphs the simulations output for the values shown in the table from Figure 3. Figure 3 shows that the calculated values

|        | TRANSIENT SIMULATION 1ms |             |            |       |  |  |  |

|--------|--------------------------|-------------|------------|-------|--|--|--|

| In/Out | Parameter                | Theoretical | Simulation | Units |  |  |  |

| In     | VIN                      | 1.000       | 1.000      | V     |  |  |  |

| Out    | U1 IN+                   | 1.000       | 1.000      | V     |  |  |  |

| Out    | U1 IN-                   | 0.999       | 0.999      | V     |  |  |  |

| Out    | U1 OUT                   | 0.999       | 0.999      | V     |  |  |  |

| Out    | U2 IN+                   | 0.998       | 0.999      | V     |  |  |  |

| Out    | U2 IN-                   | 0.998       | 0.999      | V     |  |  |  |

| Out    | Q1 E                     | 0.998       | 0.999      | V     |  |  |  |

| Out    | le                       | 33.270      | 33.310     | mA    |  |  |  |

| Out    | lc                       | 33.100      | 33.140     | mA    |  |  |  |

| Out    | lb                       | 165.500     | 176.700    | uA    |  |  |  |

Figure 3: ACC laser driver SPICE simulation results of theoretical values vs. simulated values.

are very close to the simulated values. The SPICE model operating points were not evaluated and these differences are the expected reason for the slight variance from the calculations.

## 3.4 AC Analysis

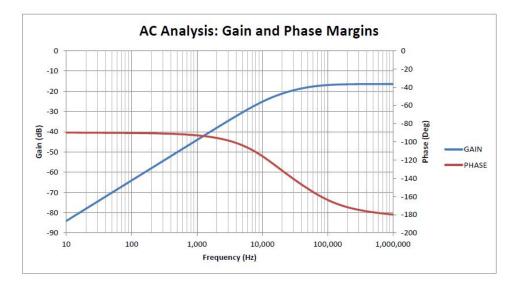

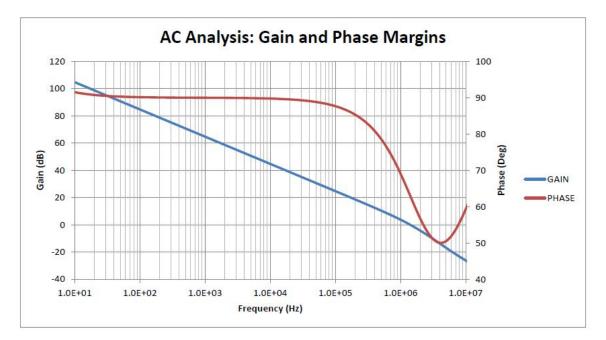

The driving circuitry is going to be used in the final design, so it is important to nip any instability issues in the bud at the early phases of the design. Figure 5 shows the gain margin and phase margin of the driving amplifier.

Figure 5 shows that the driving amplifier is stable through 400kHz, which is plenty for this design which requires 50kHz.

Figure 4: ACC laser driver results graphed from SPICE simulation.

## 3.5 ACC Laser Driver Conclusions

The design of the ACC laser driver has been successful. The stability shows that there is enough margin for the expected frequency response. The design is scalable so the photodiode feedback mechanism can be implemented painlessly. Since this design is going to do a lot more growing, the transfer function of the ACC driver will not be derived.

Figure 5: Gain and phase margin graph of ACC laser driver derived from SPICE simulation.

#### 4 Feedback Mechanism

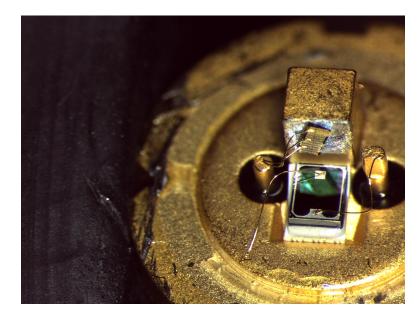

The standard feedback device for laser diodes would be current from a photodiode. Photodiodes are most commonly placed on the back facet of the laser diode, as shown in Figure 6, and used to pick off a constant amount of light. Locking the set point to the photodiode current is the key for stable operation in this design. Since the system has been chosen to be voltage controlled, there are two reasonable methods that can be used to obtain the feedback. First would be to feed the photodiode current through a resistor to obtain a voltage and second would be to use a transimpedance amplifier. In order to make an educated design choice regarding feedback mechanisms, calculations should be made for direct comparison of detector types. This chapter will be used to discuss both options and choose the best design.

Consider the following values for both detectors.

- Photo Current,  $I_L = 1mA$

- Dark Current,  $I_D = 5nA$

- Junction Capacitance,  $C_j = 10pF$

- Shunt Resistance,  $R_{SH} = 10M\Omega$

- Resistance,  $R = 3k\Omega$

- Bandwidth,  $\Delta f = 50 kHz$

- Wavelength,  $\lambda = 635 nm$

Figure 6: TO can removed from a laser diode to expose photodiode on the back facet.

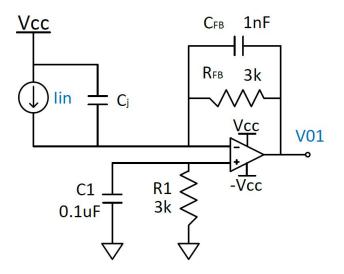

## 4.1 Photodiode Background

The photodiode used in this project is a silicon semi-conductor device. In order to accurately model feedback it is important to derive the equivalent electrical model which is shown in Figure 7 [4].

Figure 7: Equivalent electrical model of a silicon photodiode.

## 4.1.1 Photo Current

From Figure 7,  $I_L$  represents the photo current incident on the detector, or the current to be used as feedback. Ideally, this would be a perfect current source with no leakage, but that is never the case during actual applications.

## 4.1.2 Dark Current

$I_D$  is the dark current which is defined as the electric current flowing in a photoelectric device when there is no incident light [5]. This is similar to leakage current in a standard diode. In many cases the dark current of a photodiode will be upwards of a few nano-amps and can be ignored. It is important to remember that the dark current increases when the reverse bias voltage is increased. The shot noise will also increase with an increase in dark current, which will be discussed in this chapter.

#### 4.1.3 Junction Capacitance

$C_j$  is the junction capacitance and the main contributor to the frequency response of the photodiode. Depending on the size of the active area, this value can range from hundreds of femto-farads to hundreds of pico-farads. The junction capacitance is the product of a very interesting phenomena of P-N junction semi-conductor devices; The boundaries of the depletion region act as a parallel plate capacitor [9]. When the reverse bias voltage on the photodiode is increased the depletion region increases, which will decrease the capacitance. Reverse biasing the photodiode is a trade-off of increased noise vs. increased frequency response.

## 4.1.4 Shunt Resistance

The shunt resistance,  $R_{SH}$ , is the slope of the current-voltage curve of the photodiode at the origin. Ideally the shunt resistance would be infinite, but in practice this value usually sits around  $10M\Omega$ .

11

## 4.1.5 Series Resistance

The series resistance,  $R_S$ , is the resistance of the contact pads, bonding wires, solder pins, and the under depleted silicon [4]. This value is usually in the milli-ohms and by comparison is the least important photodiode parameter for this project.

## 4.1.6 Photodiode Noise

Photodiodes have two main noise sources that the designer needs to be aware of; First is shot noise and second is Johnson Noise [4].

#### 4.1.6.1 Shot Noise

The shot noise is an artifact of the statistical nature of photons arriving at random intervals. This means the number of electron-hole pairs that are feed is random as well as the electrons producing the photocurrent due to recombination [9]. Calculating the shot noise is essentially a way to quantize the fluctuation in photocurrent and dark current. The equation for shot noise can be found in equation 2.

$$I_{SN} = \sqrt{2q(I_L + I_D)\Delta f} \tag{1}$$

#### 4.1.6.2 Johnson Noise

The Johnson noise of a photodiode can be attributed to the shunt resistance. This noise source is found in all resistive elements and is cause by thermal agitation of charge carriers at equilibrium [5]. The equation for Johnson noise can be found in (3).

$$I_{JN} = \sqrt{\frac{4K_B T \Delta f}{R_{SH}}} \tag{2}$$

The total noise of the photodiode is the magnitude of the shot noise and Johnson noise which can be seen in equation 4 [4].

$$I_{TN} = \sqrt{I_{SN}^2 + I_{JN}^2}$$

(3)

## 4.2 Photodiode Resistor Feedback

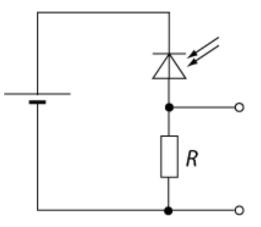

A simple detector can be made using only a photodiode, resistor, and an optional voltage source. An example of this circuit can be seen in Figure 8 [5].

Figure 8: Basic photodiode detector with response equivalent to RC low pass filter.

## 4.2.1 RC Detector Schematic

Due to the equivalent electrical model of a photodiode the output voltage be calculated using equation 5.

$$V_{out} = (I_L - I_D)R\tag{4}$$

The junction capacitance of the photodiode effectively turns this circuit into a low pass filter. The

cutoff frequency for the detector can be found from equation 6 [5].

$$f_{dB} = \frac{1}{(2\pi)(R)(C_j)}$$

(5)

## 4.2.2 RC Detector Noise

The design considerations from above are used in the following calculations. The bandwidth of the RC detector cannot be accurately controlled, so the natural cutoff frequency needs to be calculated applied to the bandwidth for the noise calculations.

$$f_{dB} = \frac{1}{(2\pi)(3e3)(10e - 12)} = 5.3Mhz$$

(6)

$$I_{SN} = \sqrt{(2)(1.6e - 19)(1e - 3 + 5e - 9)(5.3e6)} = 41.2 \frac{nA}{\sqrt{Hz}}$$

(7)

$$I_{JN} = \sqrt{\frac{(4)(1.38e - 23)(300)(5.3e6)}{10e6}} = 93.7 \frac{pA}{\sqrt{Hz}}$$

(8)

$$I_{TN} = \sqrt{41.2e - 9^2 + 93.7e - 12^2} = 41.2 \frac{nA}{\sqrt{Hz}}$$

(9)

Equations 7 - 10 calculated the noise of the RC detector. A parameter called noise equivalent power (NEP) is an industry standard measurement for direct comparison of different detectors and can be found in equation 11 [5].

$$NEP = \frac{I_{TN}}{R_{\lambda}} = \frac{41.2 \frac{nA}{\sqrt{Hz}}}{0.4} = 103 \frac{nW}{\sqrt{Hz}}$$

(10)

The SNR can be calculated now that the NEP is known.

$$SNR = \frac{MaxPower}{NEP} = \frac{2.5mW}{103nW} = 43.8dB \tag{11}$$

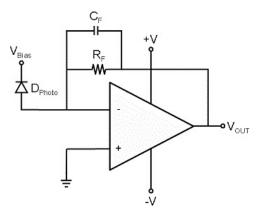

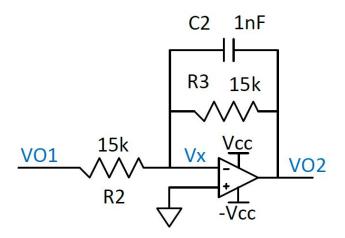

## 4.3 Photodiode Transimpedance Feedback

A basic transimpedance amplifier (TIA) can be seen in figure 9 and will be used for calculations in this section. Due to the equivalent electrical model of a photodiode the output voltage be calcu-

Figure 9: Typical schematic of a transimpedance amplifier.

lated using equation 13.

$$V_{out} = (I_L - I_D)(R_{FB}) \tag{12}$$

The bandwidth of the TIA is less dependent on the junction capacitance, especially if the bandwidth is being decreased. The new bandwidth can be calculated based off the feedback resistor and capacitor as shown in equation 14.

$$f_{dB} = \frac{1}{(2\pi)(R_{FB})(C_{FB})}$$

(13)

## 4.3.1 TIA Detector Noise

The design considerations from above are used in the following calculations. The bandwidth of the TIA will be set to the desired cutoff frequency of 50kHz.

$$I_{SN} = \sqrt{(2)(1.6e - 19)(1e - 3 + 5e - 9)(50e3)} = 4.0 \frac{nA}{\sqrt{Hz}}$$

(14)

$$I_{JN} = \sqrt{\frac{(4)(1.38e - 23)(300)(50e3)}{10e6}} = 9.1 \frac{pA}{\sqrt{Hz}}$$

(15)

$$I_{TN} = \sqrt{41.2e - 9^2 + 93.7e - 12^2} = 4.0 \frac{nA}{\sqrt{Hz}}$$

(16)

Equations 15-17 show that the noise current noise has been decreased by an order of magnitude in comparison to the RC detector.

$$NEP = \frac{I_{TN}}{R_{\lambda}} = \frac{4.0\frac{nA}{\sqrt{Hz}}}{0.4} = 10\frac{nW}{\sqrt{Hz}}$$

(17)

The SNR can be calculated now that the NEP is known.

$$SNR = \frac{MaxPower}{NEP} = \frac{2.5mW}{10nW} = 54.0dB$$

(18)

## 4.4 Feedback Mechanism Conclusion

First thing to note is that the bandwidth of the RC detector will fall outside of the stable range of the laser driving circuit, so the TIA is an absolute necessity for this design. The current noise contribution due to the RC detector will also fall outside of the the current noise specifications stated in Figure 1. The signal to noise ratio of the TIA has an improvement of 10dB over the RC

detector, which isn't a deal breaker by itself, but considering the other issues at hand the TIA is the clear choice for the feedback mechanism.

#### 5 Transimpedance Amplifier Design

A transimpedance amplifier is exactly what the name suggests, a current to to voltage converter. Since the photodiode is a nearly ideal current source, the TIA is a useful analog design to output stable voltage. This chapter will go through the design steps to design a stable and reliable transimpedance amplifier.

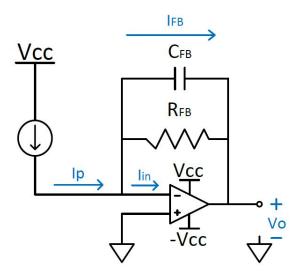

#### 5.1 Transimpedance Amplifier Theory of Operation

The TIA pictured in Figure 10 shows an ideal current source being fed into the inverting input of the op-amp. Section 4.1 showed that photodiodes are close to perfect current sources, so it will be modeled as such. In an ideal op-amp it is well known that the inputs draw no current. Since no current is going into the op-amp, all of the current from the photodiode must go through the feedback network. This means that the output voltage must follow Ohm's Law,  $V_O = -(R_{FB})(I_P)$

Figure 10: TIA schematic and current flow used for Laplace and time domain analyses.

## 5.2 Choosing the Right Amplifier

The key to a stable and reliable TIA is the amplifier choice. Just remember that not all op-amps are created equal. This section is focused on choosing the right component and narrowing down the search.

## 5.2.1 Amplifiers to Avoid

- Instrumentation amplifiers look harmless from the outside, but they often have undesirable traits and caveats. Proceed with extreme caution if an instrumentation amplifier is chosen for a TIA.

- Chopper amplifiers may seem like a good idea because they have a very small offset voltage, but they can have interesting behavior in the frequency domain.

- Bi-Polar amplifiers can be dangerous due to the high input bias current. Input bias current will get pulled across the feedback resistor producing an unwanted gain.

## 5.2.2 Amplifiers to Consider

The type of amplifiers under consideration for the transimpedance amplifier will be general purpose CMOS and JFET. The below list identifies the important design parameters.

- Gain Bandwidth Product < 5MHz

- Input Bias Current < 5pA

- Input Offset Current <5pA

- Supports Dual Supply  $> \pm 5V$

- Unity Gain Stable

- Offset Voltage < 5mV

- Rail to Rail Output

- Current Noise  $< 1nA/\sqrt{Hz}$

The Analog Devices website provides a parametric search option which gave the results shown in Figure 10. The requirement for input offset voltage was increased in order to give more parts to compare. There are 4 parts that meet all of the criteria: ADA4665-2, AD795, LT1462, and LT1464. The GBP for the LT1462 is too low for this design, leaving 3 parts to choose from. Any of these 3 amplifiers would work just fine, however the AD795 only has one operational amplifier per package, so a part with two amplifiers per package will be chosen to accommodate the dual stage TIA. The LT1464 is not a rail to rail amplifier, which is important because ground sensing on the inputs will affect performance. This leaves one part to choose from, which is the ADA4665-2.

| Part #    | Current Noise | los (max) | Rail to Rail | GBP (typ) | Vos (max) | Ibias (max) | Vs span |

|-----------|---------------|-----------|--------------|-----------|-----------|-------------|---------|

|           | (A/rtHz)      | (A)       |              | (Hz)      | (V)       | (A)         | (V)     |

| ADA4665-2 | 50f           | 1p        | Both         | 1.2M      | 4m        | <b>1</b> p  | 16      |

| AD795     | 600a          | 1p        |              | 1.6M      | 500µ      | 2p          | 36      |

| LT1462    | 500a          | 1.2p      |              | 175k      | 800µ      | 2p          | 40      |

| LT1464    | 400a          | 1.2p      |              | 1M        | 800µ      | 2p          | 40      |

| AD820     | 800a          | 10p       | Output       | 1.8M      | 1m        | 10p         | 30      |

| AD822     | 800a          | 12p       | Output       | 1.8M      | 1.5m      | 12p         | 30      |

| AD8663    | 50f           | 35p       | Output       | 540k      | 300µ      | 45p         | 16      |

| AD8667    | 50f           | 35p       | Output       | 540k      | 300µ      | 45p         | 16      |

| AD8657    | 100f          | 40p       | Both         | 230k      | 350µ      | 20p         | 18      |

| LT6003    | 12f           | 80p       | Both         | 2k        | 500µ      | 90p         | 16      |

| LT6004    | 12f           | 80p       | Both         | 2k        | 500µ      | 90p         | 16      |

| LT1495    | 10f           | 100p      | Both         | 2.7k      | 375µ      | 1n          | 36      |

| LT1673    | 10f           | 100p      | Both         | 12k       | 375µ      | <b>1</b> n  | 36      |

| LT1672    | 10f           | 100p      | Both         | 12k       | 375µ      | <b>1</b> n  | 36      |

| LT1494    | 10f           | 100p      | Both         | 2.7k      | 375µ      | 1n          | 36      |

| LT1008    | 20f           | 100p      |              | 1M        | 120µ      | 100p        | 40      |

| OP297     | 20f           | 100p      |              | 500k      | 50µ       | 100p        | 40      |

Figure 11: Parametric op-amp search from Linear Technology and Analog Devices.

## 5.3 Designing the Feedback Network

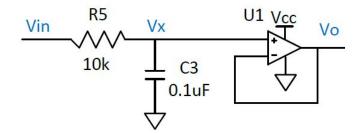

The datasheet from Figure 1 states that the APC loop speed will be 20us which correlates to a speed of 50kHz. Figure 1 also states that the APC loop set range will vary from 0-3V and the maximum photodiode current will be 1mA. This is all the information needed to design the feedback network.

$$f_{APC} = \frac{1}{(2\pi)(R_{FB})(C_{FB})}$$

(19)

$$R_{FB} = \frac{V_{PD-max}}{I_{PD-max}} = \frac{3V}{1mA} = 3k\Omega$$

<sup>(20)</sup>

$$50kHz = \frac{1}{(2\pi)(3k)(C_{FB})} \to C_{FB} = 1nF$$

(21)

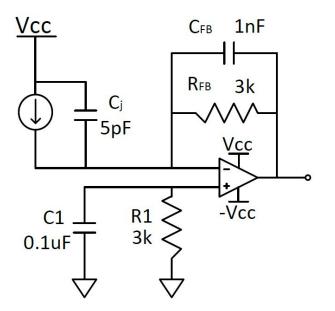

#### 5.4 Compensating for Non-Ideal Situations

In the real world, nothing is ideal so the designer needs to be aware of and compensate for these cases whenever possible. There are two issues with the TIA that need be addressed. First, the opamp does draw some current on the inputs, so balancing the loads seen by the input terminals will balance the input offset current of the amplifier and keep the amplifier from translating this current into the overall gain of the circuit. Second, a small capacitor should be placed at the non-inverting input to ground to help filter out any high frequency noise on the reference input rail. Figure 12 is the TIA design up until this point.

#### 5.5 Voltage Supply Rails

The op-amp chosen, ADA4665-2, is a rail to rail op-amp meaning the inputs can sense Vcc to -Vcc and the output can swing from Vcc to -Vcc. Most rail to rail op-amps can't actually swing the full rail, they usually fall short by about 10mV, so this needs to be taken into consideration. The output needs to swing from 0 to 3V, so the minimum Vcc should be  $\pm 3.3V$ . In this configuration the TIA can sense the reference ground because the negative rail will be pulled to -Vcc.

Figure 12: Modified TIA schematic to compensate for non-ideal op-amp behavior.

## 5.6 TIA Stage 1 Stability

During the general electronic design, the majority of circuitry will be simulated using SPICE. After the electrical design is complete, the entire system will be modeled in the Laplace domain and simulated in Matlab to confirm the performance of the control system.

## 5.6.1 Gain and Phase Margin

The gain and phase vs. frequency can be plotted from the SPICE simulation to derive the gain and phase margins. Figure 13 shows the phase at a gain of 0dB is 62, so the phase margin of this design is 62 degrees. The sweet spot for stability in transimpedance amplifiers is a phase margin between 45 and 90 degrees [7]. The gain margin for this design is infinite as the phase never drops below -180 degrees. The SPICE simulation shows that the raw amplifier design will be stable.

Figure 13: Gain and phase margin graph of modified TIA derived from SPICE simulation.

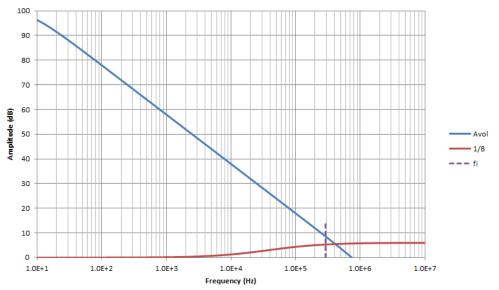

## 5.6.2 Feedback Factor

Like any circuit with an operational amplifier and feedback, the TIA can be broken down into an amplifier with open-loop gain and a feedback network which will include the feedback resistor, capacitor, and the photodiode. The stability analysis in section 5.6.1 simulates the electronics with a perfect current source. This section will focus on analyzing the stability with the introduction of the a photodiode in place of the perfect current source.

Start by mathematically defining the open loop gain of the amplifier for a single pole system.

$$A_{VOL(j\omega)} = \frac{A_{VOL}}{1 + j\frac{\omega}{\omega_{PD}}}$$

(22)

The feedback network comprised of a one pole RC filter, the junction capacitance of the photodiode, and the input capacitance of the op-amp as seen in Figure 14.

$$\beta(j\omega) = \frac{X_{Cin}}{R_{FB}//X_{FB} + X_{Cin}}$$

(23)

Figure 14: TIA modeled with photodiode equivalent model to account for input impedance.

$$\beta(j\omega) = \frac{1 + j\omega R_{FB}C_{FB}}{1 + j\omega R_{FB}(C_{FB} + C_{in})}$$

(24)

Equation 23 and 25 [7] can be used to graph the open loop gain vs. the feedback network to visually determine the stability. The Barkhausen stability criterion states that a closed loop system can become unstable if there is not sufficient phase margin,  $A_{VOL}\beta \ge 1$ . Before graphing the feedback and open loop gain, it is important to find the minimum stable frequency of the feedback. If the system does not provide enough margin then overcompensation should be built into the system to ensure the circuit never becomes unstable [7].

$$f_{min} = \sqrt{\frac{f_{GBWP}}{2\pi R_{FB}(C_{FB} + C_{in})}}$$

(25)

Taking a look figure 15, it is clear that the feedback system is flat when crossing over the roll off of the open loop gain of the amplifier. If the feedback factor was climbing at a rate of 20dB/dec

and the open loop gain was decreasing at a rate of 20dB/dec when they crossed, then the circuit would be doomed to fail and oscillate wildly. This design is showing that the TIA will be stable and approximately 10kHz of overcompensation has been designed in.

**Open Loop Gain vs Feedback Factor**

Figure 15: Graph of open loop gain vs. feedback factor for modified TIA with photodiode input.

#### 5.6.3 TIA Noise Performance